### IMPROVEMENTS IN SPINNAKER SIMULATOR

SpiNNaker – a spiking neural network simulator developed by APT group – The University of Manchester

SERGIO DAVIES 11/03/2010

### Research Areas

• Currently working on:

- Synaptic plasticity: specifically a new version of the STDP algorithm which aims to simplify the original version;

- New simulator framework: Porting Scott's simulator code onto the test chip;

- Graphical User Interface (spinnGUI): condensing all the tools in a nice front-end.

### Synaptic plasticity

- Modification of synapse parameters (i.e.: weight);

- Deletion of synapses with a very low weight;

- Creation of new synapses for each removed synapse;

The last two events are generally referred to as "synaptic rewiring".

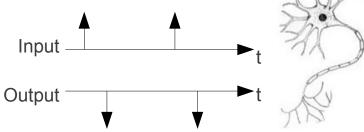

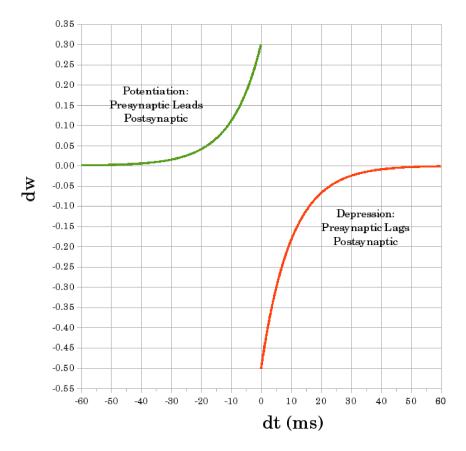

## Synaptic weight modification (1/3)

Weight modification dependent on the sequence of spikes:

Causality in the input – output causes the weight of the

input synapse to increase (+);

Anti-causality in the input – output causes the weight of the input synapse to decrease (-);

## Synaptic weight modification (2/3)

The modification of the synaptic weight is described by an exponential law:

## Synaptic weight modification (3/3)

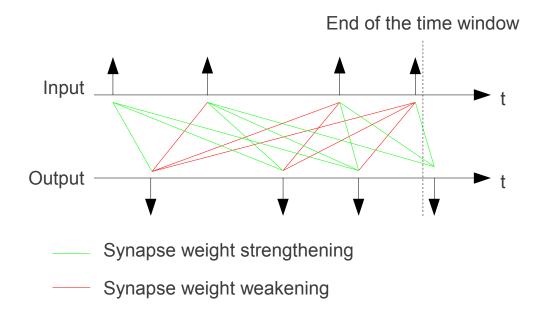

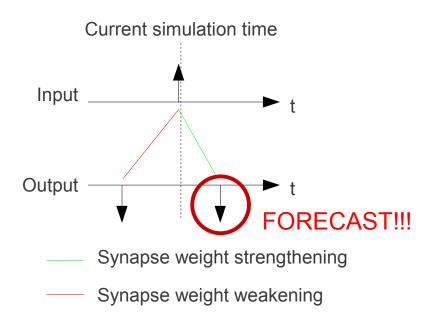

"Spike-Timing-Dependent Plasticity" (STDP) to evaluate the weight of the synapse:

The original algorithm computes the time difference between spikes for all the possible combination of input and output spikes (in a time window).

This algorithm is very complex and needs future information to compute the weight in a specific moment.

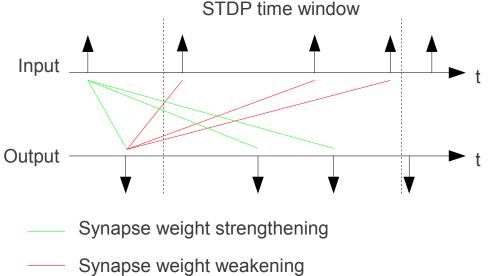

### Deferred event-driven (DED) model

To avoid the need of future parameters the deferred event-driven model has been implemented. The execution is triggered on the arrival of a pre-synaptic spike

When some spikes are pushed out of the STDP time window, the STDP algorithm is triggered.

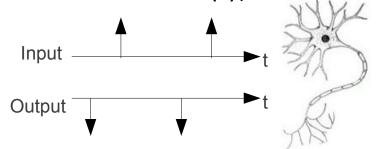

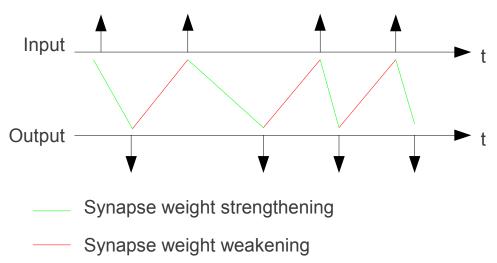

### Simplified STDP

- Disadvantages of the standard STDP: computational power and memory.

- The first simplification takes into account only the nearest sequence of input – output spikes:

Similar to the DED STDP model. Less computations, but similar amount of memory.

### **Forecast STDP**

To avoid the need of memory, a new model for the STDP algorithm has been proposed.

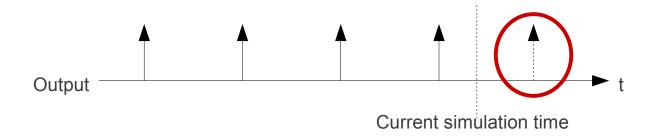

### Running average STDP (1/2)

#### Forecast of the next outgoing spike:

- Running average historical spiking rate

- The future spike time-stamp of a neuron is computed according to an estimated firing rate.

### Running average STDP (2/2)

The estimated firing rate is updated at every outgoing spike according to the previous estimated firing rate and the time between the last two spikes.

$$FR(n) = \frac{1}{2} FR(n-1) + \frac{1}{2} IST(n)$$

#### Where:

- FR(n): firing rate estimated after n outgoing spike

- IST(n): Inter Spike Time between spike n-1 and spike n

Sudden variation of spiking rate doesn't have an immediate effect.

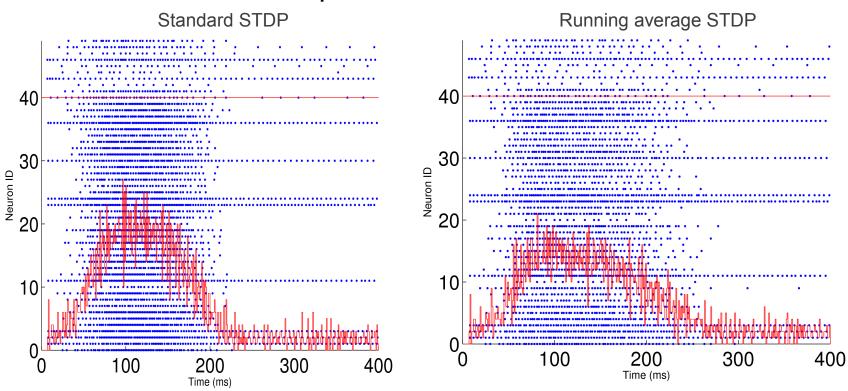

# Running average STDP Simulation

Before the simulator expired, there was the possibility to run only one simulation:

The algorithm has been simulated and compared with the original STDP with a random network of 50 neurons with an input to 10 of these neurons.

The input is characterized by fast and strong spikes.

# Running average STDP Results (1/2)

#### Raster plots of the simulations:

Behaviour seems similar.

# Running average STDP Results (2/2)

Numerical results of the simulation.

Values are ratio between the variation of the synaptic weights in both models.

|    | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   | 11    | 12   |

|----|------|------|------|------|------|------|------|------|------|------|------|-------|------|

|    |      |      |      |      |      |      |      |      |      |      |      |       |      |

| 25 | 0.71 | 0    | 0    | 1.07 | 0    | 0    | 0    | 0    | 0.64 | 0.57 | 0    | 0     | 0    |

| 26 | 0    | 0.62 | 0    | 0    | 0.43 | 0    | 0    | 0    | 0.98 | 0    | 0    | 0.5   | 0.67 |

| 27 | 0    | 0.93 | 0    | 0    | 0.83 | 0    | 0    | 0.8  | 0    | 0    | 0.97 | 0     | 0    |

| 28 | 0    | 0.72 | 0    | 1.08 | 0    | 0    | 0.43 | 0    | 0    | 0.65 | 0    | 0     | 0.66 |

| 29 | 0    | 0.54 | 0    | 0.67 | 0    | 0    | 0    | 0    | 0.9  | 0.44 | 0    | 0     | 0    |

| 30 | 0    | 0    | 0.76 | 1    | 0    | 0    | 0    | 0    | 1.13 | 0.95 | 0    | 0     | 0    |

| 31 | 0.68 | 0    | 0    | 0.6  | 0    | 0    | 0    | 0    | 1.03 | 0    | 0    | 1.1   | 0    |

| 32 | 0.75 | 0    | 0    | 0    | 0    | 0.6  | 0    | 0    | 0.76 | 0    | 0    | 0.76  | 0.77 |

| 33 | 0.51 | 0    | 0    | 0    | 0.68 | 0    | 0.54 | 0    | 0    | 0    | 0    | 0.47  | 0    |

| 34 | 0    | 0    | 0.48 | 0    | 0    | 0.75 | 0    | 0.68 | 0    | 0    | 0    | -1.12 | 0    |

| 35 | 0    | 0    | 0.46 | 0    | 0.79 | 0    | 0.72 | 0    | 0    | 0    | 0    | 0.58  | 0    |

| 36 | 0.76 | 0    | 0    | 0    | 0    | 0.97 | 0    | 1.24 | 0    | 0    | 1    | 0     | 0.8  |

| 37 | 3    | 0    | 0    | 0    | 0    | 0.52 | 0.46 | 0    | 0    | 0    | 0    | 0.64  | 0    |

| 38 | 0.57 | 0    | 0    | 0    | 0    | 0.57 | 0    | 0    | 1    | 0    | 1.07 | 0     | 0.71 |

| 39 | 0    | 0    | 1.11 | 0    | 0    | 0.67 | 1.16 | 0    | 0    | 0    | 0    | 1.12  | 0    |

## Running average STDP Future work

- Raster plots indicate a comparable behaviour.

- Synapse weights table shows the opposite.

WHAT TO BELIEVE???

- We are more interested in the <u>behaviour</u> of the network

- More simulations and study of the parameter is necessary

### New simulator

SoC Designer has expired. Simulations running now on the test chip.

Some adaptations are needed to load data into and to retrieve data from the simulator.

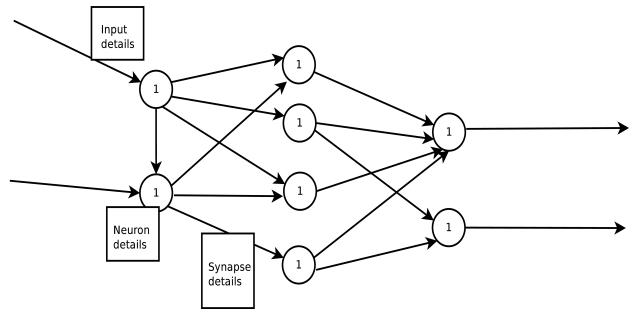

### SpinnGUI

A new front-end for SpiNNaker simulator.

Expandability for new future tools and modules

Portability to various operating systems

Controls the whole tool-chain: from the compilation to the retrieval of simulation results.

### SpinnGUI explained

#### **Expandability:**

- Front-end is modular

- Modules of the simulator are described in XML.

### Portability:

- The Qt framework supports multiple OS.

- The Xerces-C library as well.

## SpinnGUI – State of development

XSD Schema

XML Description

spinnGUI

### SpinnGUI – Future work

A graphical interface to describe the neural network

- Tools to configure the simulation on the chip

- Output analyser tools

•

## Thank you!!!