# Balsa: A Tutorial Guide.

Doug Edwards, Andrew Bardsley, Lilian Janin & Will Toms

## Contents

| 1 | Introdu      | action                                                                                                                                                                                                  | 1     |

|---|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|   | 1.1.         | Introducing Balsa                                                                                                                                                                                       | 1     |

|   | 1.2.         | Tool set and design flow                                                                                                                                                                                | 3     |

|   | 1.3.         | Changes in releases  Deprecated or eliminated constructs/files  New constructs  Changed behaviour  Balsa-mgr  Cost Estimator  Simulation environment  Channel viewer  Back-end technologies  The Manual |       |

|   |              |                                                                                                                                                                                                         |       |

| 2 | Getting      | Started                                                                                                                                                                                                 | 7     |

| 2 | Getting 2.1. | A single-place buffer  Description  Commentary on the code  Reserved words  Compiling the circuit  The synthesised circuit.                                                                             |       |

| 2 |              | A single-place buffer  Description  Commentary on the code  Reserved words  Compiling the circuit                                                                                                       | 7<br> |

| 2 | 2.1.         | A single-place buffer  Description  Commentary on the code  Reserved words  Compiling the circuit  The synthesised circuit.  Two-place buffers  1st design                                              |       |

|   | 2.5.   | Using balsa-mgr  Creating a new project  Compiling a description  Compilation errors  Handshake circuit graph  Circuit cost  Saving Window Contents  Flattened vs non-flattened view         |                                              |

|---|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   | 2.6.   | Simulation.  Adding a test fixture.  Text-only simulation  Graphical Simulation Tools                                                                                                        | 19<br>20                                     |

|   | 2.7.   | Compilation and Simulation Options  Flattened vs hierarchical compilation  Direct Simulation vs Breeze fi Lard  Lard simulation options  Structural vs behavioural simulation                |                                              |

| 3 | The Ba | ılsa Language                                                                                                                                                                                | 29                                           |

|   | 3.1.   | Data Types  Numeric types  Enumerated types  Record types  Array types  Constants  Arrayed channels                                                                                          |                                              |

|   | 3.2.   | Data Typing Issues  Casts  Bit ordering and padding in arrays  Auto-assignment                                                                                                               | 32<br>33                                     |

|   | 3.3.   | Control Flow and Commands Sync Channel assignment Variable assignment Sequence operator Parallel composition Continue and Halt Looping constructs Structural iteration Conditional execution | 35<br>35<br>35<br>35<br>35<br>35<br>36<br>36 |

|   | 3.4.   | Binary/Unary Operators                                                                                                                                                                       | 38                                           |

|   | 3.5.   | Description Structure  File structure  Declarations  Procedures  Shared procedures  Functions  Conditional ports and declarations  Conditional ports                                         |                                              |

|   |        | 1                                                                                                                                                                                            |                                              |

|   |         | Variable ports                          | 41 |

|---|---------|-----------------------------------------|----|

|   | 3.6.    | Examples                                | 42 |

|   |         | Modulo-16 counter                       |    |

|   |         | Removing auto-assignment                | 42 |

|   |         | Modulo-10 counter                       |    |

|   |         | A loadable up/down counter              |    |

|   |         | Sharing hardware                        |    |

|   |         | A "while" loop description              |    |

|   |         | Pitfalls in loop terminations           |    |

|   |         | The danger of "for" loops               |    |

| 4 | Param   | eterised & Recursively Defined Circuits | 49 |

| • | 4.1.    | Summary                                 | 49 |

|   | 4.2.    | Doromotoricad descriptions              | 40 |

|   | 4.2.    | Parameterised descriptions              |    |

|   |         | Pipelines of variable width and depth   |    |

|   |         | ·                                       |    |

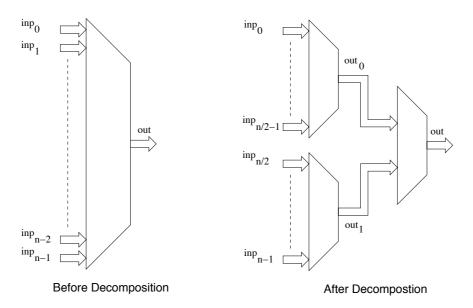

|   | 4.3.    | Recursive definitions                   |    |

|   |         | An n-way multiplexer                    |    |

|   |         | Commentary on the code                  |    |

|   |         | A balsa test harness                    |    |

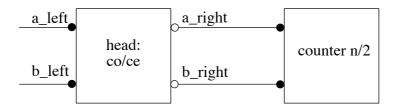

|   |         | Handshake multiplier                    | 52 |

|   | 4.4.    | Pitfalls with Parameterised Procedures. | 53 |

| 5 |         | hake Enclosure                          |    |

|   | 5.1.    | Summary                                 | 55 |

|   | 5.2.    | Systolic counters                       | 55 |

|   |         | A systolic modulo-11 counter            |    |

|   |         | All even cells                          |    |

|   |         | All odd cells                           |    |

|   |         | A decoupled all even cell               |    |

|   |         | Parameterised version                   | 60 |

|   | 5.3.    | Active enclosure                        | 60 |

|   | 5.4.    | Use of enclosed channels.               | 61 |

| 6 | Balsa 1 | Design Examples                         | 65 |

|   | 6.1.    | Summary                                 | 65 |

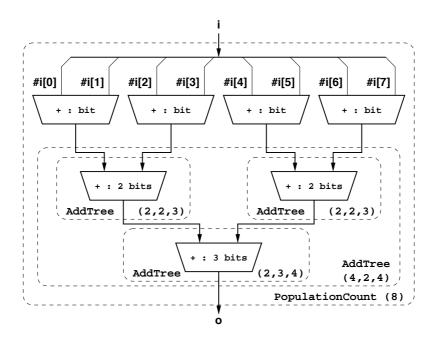

|   | 6.2.    | A Population Counter                    | 65 |

|   |         | Commentary on the code                  |    |

|   |         | Enclosed Selection                      |    |

|   |         | Avoiding deadlock:                      | 67 |

|   |         |                                         |    |

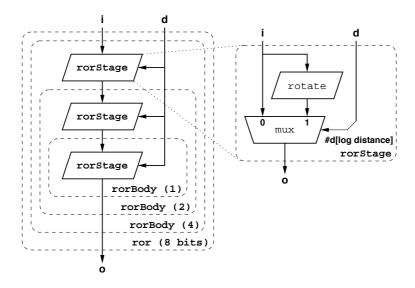

|   | 6.3.    | A Balsa shifter                         |    |

|   |         | Testing the shifter                                                                                                                                             | 69                   |

|---|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

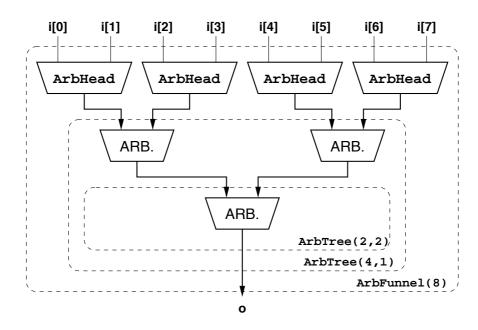

|   | 6.4.    | An Arbiter Tree                                                                                                                                                 | 69                   |

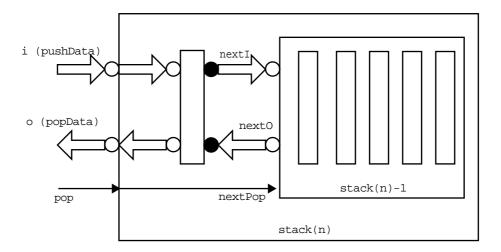

|   | 6.5.    | A Stack Description                                                                                                                                             |                      |

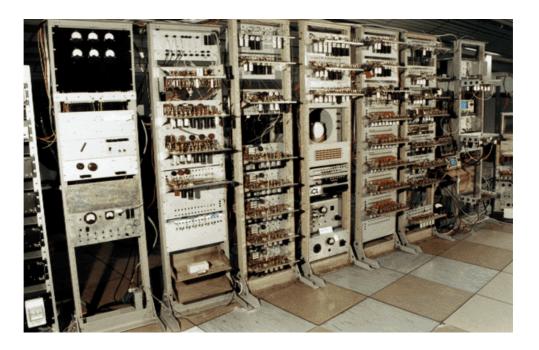

|   | 6.6.    | A Simple Processor – The Manchester SSEM (The Baby)                                                                                                             | 73<br>74             |

|   |         | Decode and excute procedure                                                                                                                                     | 75<br>75             |

| 7 | Buildin | ng test harnesses with Balsa                                                                                                                                    | 77                   |

| - | 7.1.    | Overview Builtin types Builtin Functions Strings                                                                                                                | 77<br>78             |

|   | 7.2.    | Summary of Library Functions.  types.builtin sim.string sim.fileio sim.memory sim.portio                                                                        | 79<br>79<br>80<br>81 |

|   | 7.3.    | Writing your own builtin functions The Balsa and C code Registering the function Compiling HelloWorld Invoking HelloWorld HelloWorld in Verilog Using balsa-mgr | 84<br>84<br>85<br>86 |

|   | 7.4.    | Builtin functions with arguments  Builtin typed arguments  Return values  Functions with parameterised arguments                                                | 89<br>90             |

|   | 7.5.    | Object Reference Counting  Variable assignment  Function objects array                                                                                          | 91                   |

|   | 7.6.    | Predefined types  BalsaString  BalsaFile                                                                                                                        | 92<br>92             |

|   | 7.7.    | Example Custom Test Harnesses  Data Formatting  FileIO  Memory models                                                                                           | 93<br>93<br>95       |

|   |         | A Processor Test Harness                                                                                                                                        | 98                   |

| 8 | Implem  | entations                                                       | 99  |

|---|---------|-----------------------------------------------------------------|-----|

| Ü | 8.1.    | Introduction Technologies Styles                                | 99  |

|   |         | Options                                                         | 100 |

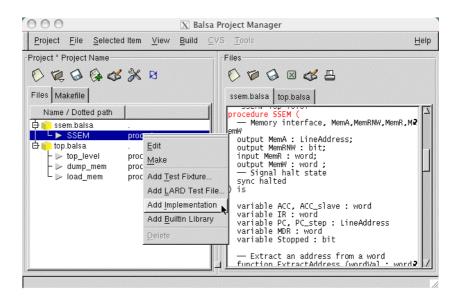

|   | 8.2.    | Creating an implementation                                      | 101 |

| 9 | Adding  | Technologies to Balsa                                           | 103 |

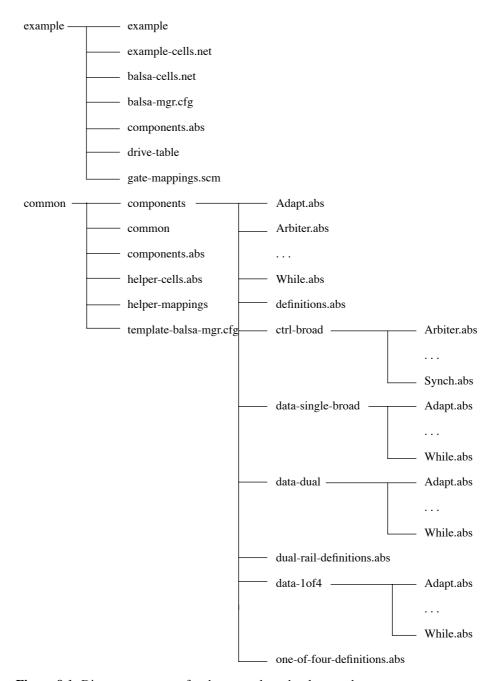

|   | 9.1.    | The Balsa backend  Technologies and Styles  Directory structure | 103 |

|   | 9.2.    | The technology configuration file                               | 105 |

|   | 9.3.    | Handshake component declarations                                |     |

|   | 9.4.    | Handshake component implementation descriptions                 |     |

|   | 9.5.    | Adding a new technology                                         |     |

|   | 9.6.    | The abs language                                                |     |

|   | 9.0.    | Bundles                                                         |     |

|   |         | Channels                                                        |     |

|   |         | Slices                                                          |     |

|   |         | Gate Operators  Example                                         |     |

|   | 9.7.    | Netlists                                                        | 115 |

|   |         | ports:                                                          |     |

|   |         | nets                                                            |     |

|   |         | iinstances attributes                                           |     |

|   | 9.8.    | The BALSATECH environment variable                              |     |

|   | 9.9.    | The ABS Grammar                                                 |     |

|   | 9.9.    | Components                                                      |     |

|   |         | Styles                                                          |     |

|   |         | Gates                                                           |     |

|   |         | Slices                                                          |     |

|   |         | Include                                                         |     |

|   |         | Expressions                                                     |     |

|   | 9.10.   | Netlist Format                                                  | 122 |

|   |         | Netlist                                                         | 122 |

| 0 | Balsa F | Reference                                                       | 125 |

|   |         | Summary                                                         | 125 |

|   | 10.1.   | Balsa programs                                                  | 125 |

| 10.2. Setting the BALSATECH environment variable | 126                                                                                                                                          |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| The Balsa Language Definition                    | 127                                                                                                                                          |

| Summary                                          | 127                                                                                                                                          |

| 11.1. Reserved words                             | 127                                                                                                                                          |

| 11.2. Language Definition                        | 127                                                                                                                                          |

| The Breeze Language Definition                   | 133                                                                                                                                          |

| Summary                                          | 133                                                                                                                                          |

| References                                       | 137                                                                                                                                          |

|                                                  | The Balsa Language Definition  Summary  11.1. Reserved words  11.2. Language Definition  The Breeze Language Definition  Summary  References |

## 1 Introduction

#### 1.1. Introducing Balsa

This document describes version 3.4 of the Balsa system. This release adds significant changes in the capabilities of the simulation tools. File I/O, string handling and memory models are included.

Version 3.3 of the Balsa system was a major upgrade from previous versions although some of the extra functionality had been available in the various snapshots that have been downloadable from the Balsa website. Significant changes were introduced in all aspects of the system: language, simulation environment, back-end target technologies and not least in the documentation itself. Existing users of Balsa shoulf be aware of the changes which are summarised in the section "Changes in releases" on page 4. Whilst most existing Balsa descriptions should compile without problems, changes to the syntax of the while construct may cause existing descriptions not to compile. Most users should not be affected by the changes, since while loops, although available in earlier releases, were not described in the previous version of the manual.

The tools described here can be run on any POSIX environment with X11 and at least 32bit integers (Linux, FreeBSD, MacOS X, Solaris). However, in order to produce a concrete implementation in either silicon or FPGA form, vendor specific tools are required: for example Xilinx design software, or the Cadence design framework with an appropriate cell library technology.

#### What is Balsa?

Balsa is the name of both a framework for synthesising asynchronous (clockless) hardware systems and the language for describing such systems. The approach adopted is that of syntax-directed compilation into communicating Handshaking Components and closely follows the Tangram [1] system of Philips. The advantage of this approach is that the compilation is transparent: there is a one-to-one mapping between the language constructs in the specification and the intermediate handshake circuits that are produced. It is relatively easy for an experienced user to envisage the architecture of the circuit that results from the original description. Incremental changes made at the language level result in predictable changes at the circuit implementation level. This is important if optimisations and design-tradeoffs are to be made easily at teh source level and contrasts with a VHDL description in which small changes in the specification may make radical alterations to the resulting circuit.

## Basic concepts

A circuit described in Balsa is compiled into a communicating network composed from a small (~45) set of Handshake components. The components are connected by *channels* over which

communications or handshakes take place. Channels may have datapaths associated with them (in which case a handshake involves the transfer of data), or may be purely control (in which case the handshake acts as a synchronisation or rendez-vous point).

Each channel connects exactly one *passive* port of a handshake component to to one *active* port of another handshake component. An active port is a port which initiates a communication. A passive port responds (when it is ready) to the *request* from the active port by an *acknowledge* signal

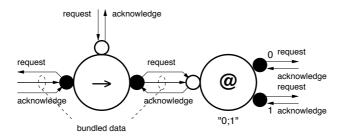

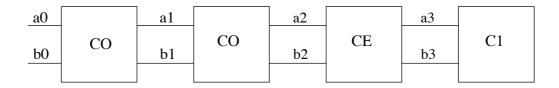

Data channels may be *push* channels or *pull* channels. In a push channel, the direction of the data flow is from the active port to the passive port, corresponding to a *micropipeline* style of communication. Data validity is signalled by request and released on acknowledge. In a pull channel, the direction of data flow is from the passive port to the active port. The active port requests a transfer, data validity is signalled by an acknowledge from the passive port. An example of a circuit composed from handshake components is shown in Fig. 1.1.

Figure 1.1: Two connected handshake components

Here a *Fetch* component, also known as a Transferrer, (denoted by "→") and a *Case* component (denoted by "@") are connected by an internal data-bearing channel. Circuit action is activated by a request to the Fetch component which in turn isues a request to its environment (on the left of the diagram). The environment supplies the demanded data, indicating its validity by the acknowledgement signal. The Fetch component presents a handshake requests and data to the Case component using an active port (shown as a filled circle) which the Case component receives on its passive port (shown as an unfilled circle). Depending on the data value, the Case component issues a handshake to its environment on either the top right or bottom right port. Finally, when the acknowledgement is received by the case component, an acknowledgement is returned along the original channel and terminating this handshake. The circuit is ready to operate once more.

Data follows the direction of the request in this example and the acknowledgement to that request flows in the opposite direction. In this figure, individual physical request, acknowledgement and data wires are explicitly shown. Data is carried on separate wires from the signalling (it is "bundled" with the control although this is not necessary with other data/signalling encoding schemes.

The bundled data scheme illustrated in Fig. 1.1 is not the only implementation possible. Methodologies exist (DI codes, dual rail encoding, NULL Convention Logic [2]) to implement channel connections with delay-insensitive signalling where timing relationships between individual wires of an implemented channel do not affect the functionality of the circuit. Handshake circuits can be implemented using these methodologies which are robust to naive realisations, process variations and interconnect delay properties. Version 3.4 of Balsa supports bundled data, and DI dual rail and 1-of-4 back-ends.

Normally, handshake circuits diagrams are not shown at the level of detail of Fig. 1.1, a channel being shown as a single arc with the direction of data being denoted by an arrow head on the arc and control only channels, comprising only request/acknowledge wires, being indicated by an arc without an arrowhead.

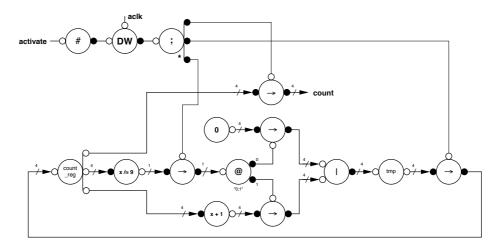

The circuit complexity of handshake circuits is often low: for example, a Fetch component may be implemented using only wires. An example of a handshake circuit for a modulo-10 counter [see

"Removing auto-assignment" on page 42] is shown in Fig. 1.2. The corresponding gate level

Figure 1.2: Handshake circuit of a modulo-10 counter

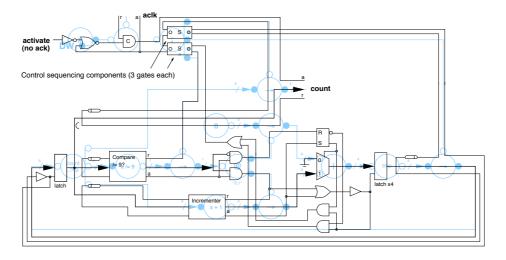

implementation is shown in Fig. 1.3.

Figure 1.3: Gate level circuit of a modulo-10 counter

Note that the compilation function results in circuit fragments in which both input and output ports are active. Since passive ports can only connect to active ports and vice-versa, circuits constructed from compositions of compiled circuit fragments must have their interconnecting ports connected by *passivator* components. A passivator synchronises requests from input and output ports and arranges the overlapping of the two handshakes (one push, one pull) such that the data-valid phases of the two data-validity protocols overlap.

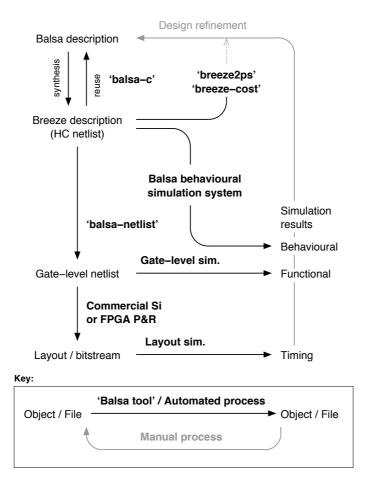

#### 1.2. Tool set and design flow

Balsa comprises a collection of tools, some of the more important are listed below.

- *balsa-c*: the compiler for the Balsa language. The ouput of the compiler is an intermediate language *breeze*.

- *balsa-netlist:* produces a netlist appropriate to the target technology/CAD framework from a Breeze description.

- breeze2ps: a tool which produces a postscript file of the handshake circuit graph.

- breeze-cost: a tool which gives an area cost estimate of the circuit.

- balsa-md: a tool for generating makefiles

- balsa-mgr: a graphical front-end to balsa-md with project management facilities.

- balsa-make-test: automatically generates test harness for a Balsa description.

- breeze-sim: the preferred simualtor working at the handshake component level

- breeze-sim-control: a graphical front-end to the simulation and visualisation environment

Obtainable in separate packages are:

- gtkwave: a waveform viewer

- balsa-verilog-sim: a package which makes Verilog simulation of Balsa descriptions easier by providing wrapper scripts for common simulators and by supporting user-written builtin functions which can be called from Balsa

A balsa-mode is also available for xemacs providing automatic syntax-based indentation of Balsa descriptions

An overview of the Balsa design flow is shown in Fig. 1.4

A Balsa description of a circuit is compiled using *balsa-c* to an intermediate *breeze* description. Most of the Balsa tools are concerned with manipulating the breeze handshake intermediate files. Breeze files can be used by back-end tools implementations for Balsa descriptions, but also contain procedure and type definitions passed on from Balsa source files allowing breeze to be used as the package description format for Balsa.

Behavioural simulation is provided by *breeze-sim*. This simulator allows source level debugging, visualisation of the channel activity at the handshake circuit level as well as producing conventional waveform traces that can be viewed using the waveform viewer *gtkwave*. The target CAD system may also be used to perform more accurate simulations and to validate the design. *breeze-sim* is still under active development: the facilities and user interface provided may be differ in detail from that described in this manual.

#### 1.3. Changes in releases

#### Version 3.4

This release adds "builtin" types [see "Builtin types" on page 77] – file I/O, string handling and memory models are included adding significant changes in the capabilities of the simulation tools.

Interfaces to a number of Verilog simulators have been included.

#### Version 3.3

The changes listed here are the major changes since the first version of the Balsa manual. Some of these changes have however appeared in various snapshots that were published on the Balsa website and some were described a text book [3] produced to promote the European Low-Power Initiative for Electronic System Design.

Figure 1.4: Design Flow

# Deprecated or eliminated constructs/ files

- public and private keywords have been eliminated

- else clauses of while statement are no longer supported

- the keyword local is not required for declarations which immediately follow procedure declarations.

- .sbreeze files are no longer generated as part of the compilation process. A modified .breeze format now replaces both .breeze and .sbreeze files.

## New constructs

- Ports to procedures can now be connected to variables to allow communications on the procedure's ports to perform reads and writes to the variable [see "Variable ports" on page 41].

- a multicast keyword has been added to prefix channel/sync declarations to supress warning about multicast channels. The "-c warn-multicast" option to balsa-c now does nothing it is enabled by default.

- implicants and don't care values may be used more widely in expressions; see "implicants" on page 32, and "case statements" on page 37.

- ports, local and global declarations may be conditional [see "Conditional ports" on page 41].

- new loop constructs have been added [see "Looping constructs" on page 36].

- case statements may be parameterised [see "Conditional execution" on page 37]

- simulation time printing is now supported by the print command [see "Control Flow and Commands" on page 34]

- a bit-array-cast operator, #, has been added as syntactic sugar to simplify array slicing and casting.

- · active input enclosure commands have been added

- the syntax of parameterised procedure calls has changed

## Changed behaviour

- the syntax of the while command has been changed. **Existing programs may no longer compile** [see "Looping constructs" on page 36] for more details.

- should multiple guards be true (in if and while) commands, the earliest command in the guard list is executed previously the command chosen was undefined.

- if commands, ports and declarations now correctly fail to evaluate subsequent commands if an earlier guard is true.

- breeze files must be regenerated they are no compatible with the latest version, sbreeze files are obsolete.

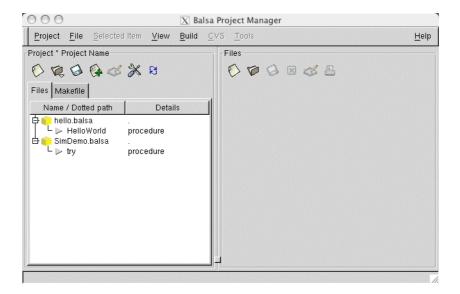

#### Balsa-mgr

The GUI to the Balsa system, balsa-mgr, is now stable and is the recommended way of driving the tool set.

#### **Cost Estimator**

The cost estimator now handles hierarchical circuits correctly.

## Simulation environment

LARD is no longer the recommended functional simulation route. A new simulation engine operating on the breeze description of circuits simulates directly and gives a speed improvement of 25,000 times. Co-simulation with existing lard test harnesses is still possible, but with reduced performance. Lard support for Balsa is no longer part of the main distribution, but is available as a separate package, *balsa-lard*.

## Channel viewer

The LARD channel viewer is now longer used for a graphical representation of channel activity. Although impressive for small demonstration purposes, it was very slow, it was difficult to restrict the view to "important" channels, snapshots could not be saved and restarted etc. The new simulation viewer is based on a conventional waveform viewer derived from GTKWave.

## Back-end technologies

A wide range of backend technologies and styles are supported and easily controlled via balsa-mgr. Users can select between single rail (bundled data), dual rail, 1-of-4 and NCL styles each with different latch implementations. A Xilinx technology and a generic Verilog netlist are distibuted. For users with appropriate licensing arrangements, a number of silicon technologies, e.g. AMS  $0.35\mu m$  and ST  $01.8\mu m$  are available.

#### The Manual

The format of the manual has changed. A more complete definition of the language is included. There is now a section on how to create different back-end technologies and styles. The example descriptions have been extended. The emphasis of the manual has changed: the previous version over-emphasised passive enclosed selection. Many users were misled into believing that this descriptive style was good practice. It is hoped that this version separates the issue of passive versus active ports from that of enclosed handshakes and encourages a more natural style of description.

## Getting Started

#### **Summary**

In this chapter, simple buffer circuits are described in Balsa introducing the basic elements of a Balsa description. The GUI to the Balsa system, *balsa-mgr*, is used to hide the complexity of the underlying command line tools. All the examples illustrated here can be found in the Examples directory of this documentation.

If the Balsa system has been compiled from source, it should only be necessary to include the binary directory in the user's search path. Users using binary only distributions, should source the *apttools.sh* script located in the distribution package.

Previous users of the system should note that since LARD is no longer the preferred simulation route,

#### 2.1. A single-place buffer

#### **Description**

A Balsa description, in buffer1a.balsa, of a byte-wide, single place buffer is:

buffer1a.balsa

## Commentary on the code

This Balsa description builds a single-place buffer, 8 bits wide. The circuit requests a byte from the environment which, when ready, transfers the data to the register. The circuit signals to the environment on its output channel that data is available and the environment reads it when it chooses. The description introduces:

comments: Balsa supports both multi-line and single line comments; both types may be nested.

**modular compilation:** Balsa supports modular compilation. The import statement in this example includes the definition of some standard data types such as byte, nibble, etc. <sup>1</sup>. A full list of the current definitions is given in *<BalsaInstallDir>/share/balsa/types/basic.breeze*. The search path given in the import statement is a dot separated directory path similar to that of Java except multi-file packages are not implemented. The import statement may be used to include other precompiled balsa programs thereby acting as a library mechanism. The import statements must precede other declarations in the files. The import statement is included in this example for completeness only. None of the types defined in *basic.breeze* are actually used this example so the import statement could have been omitted.

procedures: The procedure declaration introduces an object that looks similar to a procedure definition in a conventional programming language. In Balsa, a procedure is compiled to handshake circuit comprising a network of handshake components. The parameters of the procedure define the interface to the environment outside of the circuit block. In this case, the module has an 8-bit input datapath and an 8-bit output datapath. The body of the procedure definition defines an algorithmic behaviour for the circuit; it also implies a structural implementation. In this example, a variable x (of type byte and therefore 8 bits wide) is declared implying that a 8-bit wide storage element will be appear in the synthesised circuit.

The behaviour of the circuit is obvious from the code: 8-bit values are transferred from the environment to the storage variable, x, and then sequential output from the variable to the environment. This sequence of events is continually repeated (loop ... end).

**channel assignment:** the operators "-" and "<-" are channel input and output assignments and imply a communication or handshake over the channel. Because of the sequencing explicit in the description, the variable x will only accept a new value when it is ready; the value will only be passed out to the environment when requested. Note that the channel is always on the left-hand side of the expression and the corresponding variable on the right-hand side.

**sequencing:** The ";" symbol separating the two assignments is not merely a syntactic statement separator, it explicitly denotes sequentiality. The program has been formatted somewhat artificially to emphasise the point. The contents of x are transferred to the output port after the input transfer has completed. Because a ";" connects two sequenced statements or blocks, it is an error to place a ";" after the last statement in a block.

### Reserved words

Care must be take to avoid using Balsa's keywords as variable or procedure names. Usually, this is not a difficult restriction to remember, but a common mistake, especially for beginners experimenting with the language, is to name an input channel in. Unfortunately, in is a reserved word and will generate a Balsa compile error.

## Compiling the circuit

balsa-c bufferla

The description in *buffer1a* is compiled producing an output file *buffer1a.breeze*. This is a file in an intermediate format which can be imported back into other balsa source files (thereby providing a simple library mechanism). The file extension (*.balsa*) of the source filename is optional and contains no special significance to the compilation system. However, if a different file extension is used, the file name including the extension must be given as the argument to the *balsa-c* command. The file extension *.breeze* is of significance to the compilation system

Breeze is a textual format file designed for ease of parsing and therefore somewhat opaque. A primitive graphical representation of the compiled circuit in terms of handshake components can be produced (in *buffer1a.ps*) by:

breeze2ps buffer1a

<sup>1.</sup> there is, of course, no predefined type word

## The synthesised circuit.

The resulting handshake circuit is shown in Figure 2.1. Note that this is not actually taken from the

Figure 2.1: Handshake Circuit for a single place buffer

output of *breeze2ps*, but has been redrawn to make the diagram more readable. Although it is not necessary to understand the exact operation of the compiled circuit, a knowledge of the structure is helpful for an understanding of how to describe circuits which can be efficiently synthesised using Balsa. A brief description of the operation of the circuit is given below. The circuit has been annotated with the names of the various handshake elements.

The port at the top of the *Loop* ("#") component is an *activation* port which *encloses* (see "Handshake Enclosure" on page 55) the behaviour of the circuit. It can be thought of as a reset signal which, when released, initiates the operation of the circuit. All compiled Balsa programs contain an activation port.

The activation port starts the operation of the *Loop* which initiates a handshake with the *Sequencer* (";"). This component first issues a handshake to the left-hand *Fetch* component "→" causing data to be moved to the storage element in the *Variable* element (marked "x" to match the variable name). The Sequencer then handshakes with the right-hand Fetch component causing data to be read from the Variable element. When these operations are complete, the Sequencer completes its handshake with the repeater which start the cycle again.

#### 2.2. Two-place buffers

#### 1st design

Having built a single place buffer, an obvious goal is a pipeline of single buffer stages. Initially consider a two-place buffer; there are a number of ways we might describe this. An obvious way is to define a circuit with two storage elements:

buffer2a.balsa

end

In this example in we explicitly introduce two storage elements, x1 and x2. The contents of the variable x1 are caused to be transferred to the variable x2 by means of the assignment operator ":=". However, transfer is still effected by means of a handshaking communication channel. This assignment operator is merely a way of concealing the channel for convenience.

#### 2nd design

The implicit channel can be made explicit as shown in *buffer2b.balsa*:

buffer2b.balsa

The channel, which was in the previous example, concealed behind the use of the ":=" assignment operator has been made explicit. The handshake circuit produced (after some simple optimisations) is identical to *buffer2a*. The "||" operator is explained in the next example

It is important to understand the significance the operation of the circuits produced by buffer2a and buffer2b. Remember the ";" is more than a syntactic separator: it is an operator denoting sequence. Thus, first the input, i, is transferred to x1. When this operation is complete, x1 is transferred to x2 and finally the contents of x2 are written to the environment. Only after this sequence of operations is complete can new data from the environment be read into x1 again.

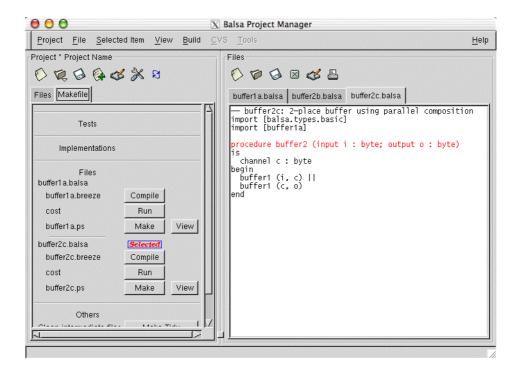

#### 2.3. Parallel composition and module reuse

The operation above is unnecessarily constrained: there is no reason why the circuit cannot be reading a new value into xI at the same time that x2 is writing out its data to the environment. The program in *buffer2c* achieves this optimisation.

```

-- buffer2c: a 2-place buffer using parallel composition

import [balsa.types.basic]

import [buffer1a]

procedure buffer2 (input i : byte; output o : byte) is

channel c : byte

begin

buffer1 (i, c) ||

buffer1 (c, o)

end

```

## Commentary on the code

In the description above, a 2-place buffer is composed from 2 single-place buffers. The output of the first buffer is connected to the input of the second buffer by their respective output and input ports. However, apart from communications across the common channel, the operation of the two buffers is independent

The deceptively simple program above illustrates a number of new features of the balsa language:

**modular compilation:** The import mechanism is used to include the *buffer1a* circuit described earlier.

**connectivity by naming:** The output of the first buffer is connected to the input of the second buffer because of the common channel name (c) in the parameter list in the instantiation of the buffers.

**parallel composition:** The "||" operator specifies that the two units which it connects should operate in parallel. This does not mean that the two units may operate totally independently: in this example the output of one buffer writes to the input of the other buffer creating a point of synchronisation. Note also that the parallelism referred to is temporal parallelism. The two buffers are physically connected in series.

#### 2.4. Placing multiple structures

If we wish to extend the number of places in the buffer, the previous technique of explicitly enumerating every buffer becomes tedious. What is required is a means of parameterising the buffer length (although in any real hardware implementation the number of buffers cannot be variable and must be known before-hand). The for construct together with compile-time constants may be used.

buffer\_n.balsa

```

-- buffer_n: an n-place parameterised buffer

import [balsa.types.basic]

import [buffer1a]

constant n = 8

procedure buffer_n (input i : byte; output o : byte) is

array 1 .. n-1 of channel c : byte

begin

buffer1 (i, c[1]) ||

-- first buffer

buffer1 (c[n-1], o) ||

-- last buffer

for | | i in 1 .. n-2 then

-- buffer i

buffer1 (c[i], c[i+1])

end

end

```

## Commentary on the code

**constants:** the value of an expression (of any type) may be bound to a name. The value of the expression is evaluated at compile time and the type of the name when used will be the same as the original expression in the constant declaration. Numbers can be given in decimal (starting with one of 1...9), hexadecimal (0x prefix), octal (0 prefix) and binary (0b prefix).

**arrayed channels:** procedure ports and locally declared channels may be arrayed. Each channel can be referred to by a numeric or enumerated index [see "Arrayed channels" on page 32], but from the point of view of handshaking, each channel is distinct and no indexed channel has any relationship with any other such channel other than the name they share.

**for loops:** a for loop allows iteration over the instantiation of a subcircuit. The composition of the circuits may either be parallel composition – as in the example above – or sequential. In the latter case, ";" should be substituted for "||" in the loop specifier. The iteration range of the loop must be resolvable at compile time.

A more flexible approach uses parameterised procedures and is discussed later [see "Parameterised descriptions" on page 49].

#### 2.5. Using balsa-mgr

Balsa-mgr is project manager environment which acts as a front-end to the Balsa commands such as balsa-c and breeze2ps. It hides much of the complexity of the various command-line options that more complicated compilation and simulation scenarios demand. The use of the project manager is best illustrated by using it to rerun the compilation of the single place buffer described in <code>buffer1a</code> ["buffer1a.balsa" on page 7]

## Creating a new project

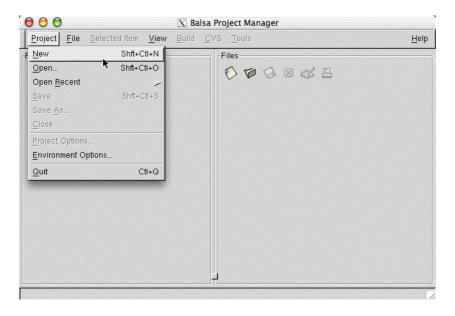

The command balsa-mgr invokes the project manager. Select "Project ⇒ New" from the pull-

Figure 2.2: Creating a new project.

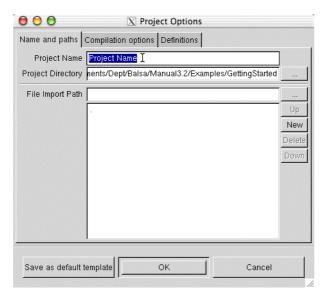

down menu as shown in Figure 2.2 to display the dialogue box shown in Figure 2.3. A default name

**Figure 2.3:** The New Project Dialogue Box.

for the project is generated; this may be over-ridden to something more meaningful. The "Project Directory" text box specifies the root directory: a file named "Project" is created here containing information about the project. The button to the right of the text box activates a file browser for graphically selecting the required directory. The "File Import Path" text box allows the directory in which the source Balsa files reside to be specified. By default, this is the current directory (relative to the root of the project) but may be changed either by directly typing in the text box or by using the

file browser activated by clicking on the button to the right of the text box. More directory import paths can be added by means of the "New" button.

Only one project is allowed per directory but each project may have several compilation targets. The options in the other tabbed panes, "Compilation options" and "Definitions" are described later.

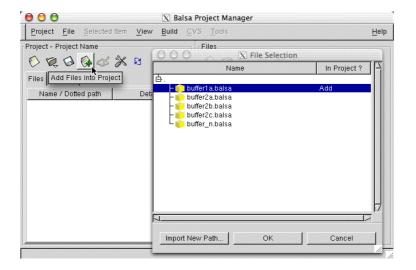

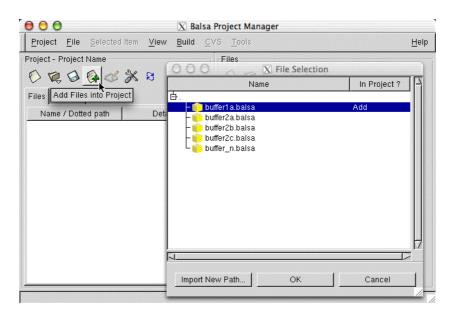

The source files to be compiled must be specified. Either select "Files ⇒ Add Files into Project" from the pull-down menu, or the keyboard accelerator Ctrl-A, or click on the icon as shown in Figure 2.4. Pick *buffer1a.balsa* and click "OK". The filename should appear in the left-hand pane of

Figure 2.4: Adding Files to the Project Manager.

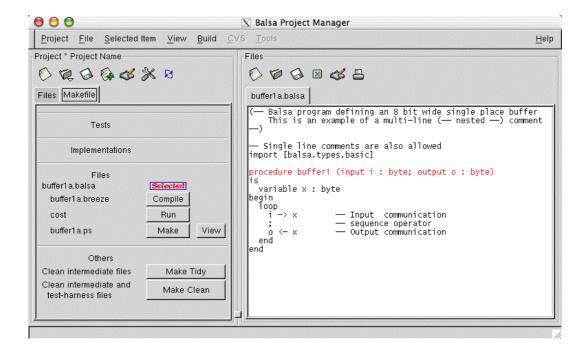

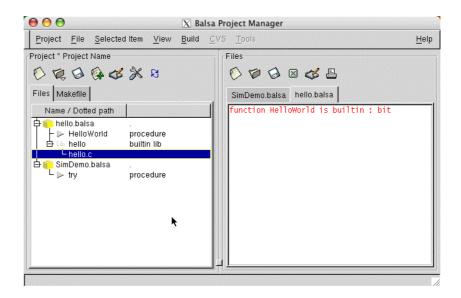

the project manager together with the name of any procedures listed in that file. Clicking on the file or procedure name will cause the contents of the file to be listed in the right hand edit pane as shown in Figure 2.5. The file may be edited in-situ in the pane or by an external editor (defined in the environment options pane assessable by the "Project  $\Rightarrow$  New" pull-down menu) which can be invoked by clicking on the edit icon above the edit pane.

## Compiling a description

Files that have not been compiled will have a warning symbol against them. Users should be aware that until the file has been compiled, the list of procedures displayed uder any filename is the result of a simplistic parsing of the source file and may *occassionally* be misleading: for example procedures that have been commented out and parameterised procedure definitions (see "Parameterised descriptions" on page 49) will be shown erroneously . Further, conditionally declared procedures (see "Conditional ports and declarations" on page 40) are missing. Upon a successful compilation, the procedures will be correctly displayed.

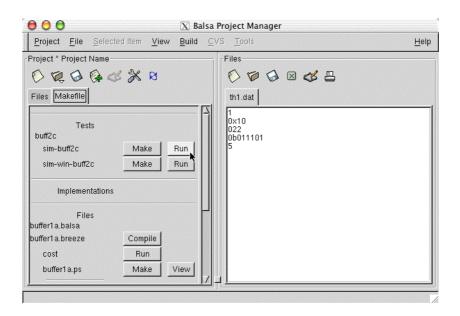

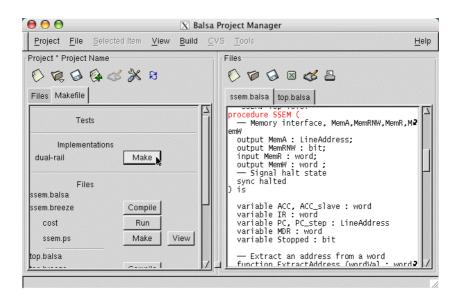

In order to compile the circuit, either middle click on the file name or click on the Makefile tab in the left-hand pane. The new view, Figure 2.6, reveals the actions available. Click on the **Compile** button to compile the description. If the project has been changed since the user last saved it, a save-project dialogue box appears. A new window, the execution window, is spawned which records various stages in the compilation process.

Behind the scenes, balsa-mgr analyses the dependencies in the sources files in the project, creates a Makefile that reflects these dependencies and generates rules in the Makefile to invoke the various Balsa commands. If the initial Balsa description is syntactically incorrect in such a way as to make impossible the determination of dependencies, the Makefile will not be correctly generated.

Figure 2.5: Displaying a file in the Edit Pane.

**Figure 2.6:** The Makefile Pane.

Running Balsa from the command line allows more flexibility than from within balsa-mgr, however balsa-mgr is much more convenient for the majority of tasks. Since describing a GUI is exceptionally tedious, users are encouraged to browse the various icons and pull-down menus themselves. Note that right-clicking in the various panes brings up various context sensitive menus.

## Compilation errors

If errors are found during the compilation of a circuit, the errors, together with the line number and character position of the error, are reported in the output pane of the execution window. Clicking on

the displayed error message causes the offending code to be highlighted in red in the edit pane window.

- 1. Start balsa-mgr and select the project defined previously for the circuit buffer1a

- 2. Add the file *buffer2b* to the project

- 3. Compile the circuit by clicking on the **Compile** button for buffer2b.breeze. The circuit should compile OK

- 4. Change the parallel composition operator "||" to the sequential operator ";".

- 5. Save the file and recompile buffer2b.breeze

- 6. An compile time error should now be reported in the execution window:

buffer2b.balsa:11:16: unbalanced channel usage; can't perform <write> ; <read> on channel

`chan'

7. Click on the message. The offending code should be displayed in red in the edit-pane window on line 11 starting at character position 16. If tabs are used in the source file, the tab size must be known in order for the character position to be correctly reported. VI users may set the value in their ~/.exrc file which is consulted by balsa-c. Alternative, -t <tabsize> may be passed as an option to balsa-c from the Compilation Options pane from the Project Options menu. Quite apart from illustrating the mechanics of error reporting within the balsa-mgr framework, this example demonstrates why designing asynchronous circuits requires a deeper understanding the design process than does the design of synchronous circuits. It is important to realise why the compiler objects to the circuit description. Line 11 contains two statements. In the first, data is output from variable xI to the internal channel chan. The next statement, because of the sequence operator ";" cannot start until the previous statement has completed which requires data to be taken on the channel to be acknowledged. It is this second statement transferring data from the channel chan to the variable x2 which would cause the data transfer on to the channel to be acknowledged. In other words, the first statement is waiting for the second statement, but the second statement can not start until the first has terminated.

In this particular case, the compiler can spot the problem. However, conceptually similar dead-lock situations can arise at higher levels of system specification. In such cases, the circuit will compile satisfactorily, but will deadlock in operation.

8. Correct the error before proceeding further.

## Handshake circuit graph

Click on the **View** button opposite the label "buffer1a.ps". If necessary, the circuit will be compiled and a PostScript viewer will appear displaying the handshake circuit graph just as it did when the viewer was invoked via the command line.

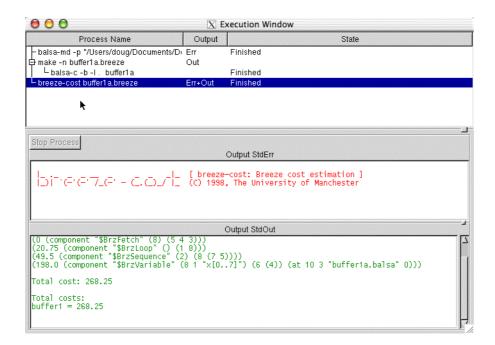

#### **Circuit cost**

The area cost of a circuit may be found by determined by clicking on the **Run** button opposite the **cost** label. Doing so will cause the execution window (Figure 2.7) to display the area cost of the circuit. This cost is only a guideline figure assuming a particular back-end implementation. Nevertheless, the cost figure is useful for gaining quick feedback on how changing the description of a circuit affects its size. The output from breeze-cost needs some interpretation: each handshake circuit is listed together with its cost, name, data width, and the internal channel identifiers to which the component is connected. Note that the cost of the Fetch component is zero. This is because in the back-end assumed for the cost function, a Fetch component is a wire only element.

Figure 2.7: Execution window, showing the cost of buffer1a

#### Saving Window Contents

#### Flattened vs non-flattened view

The ouputs logged in the StdErr or StdOut panes can be edited or saved to a file by right-clicking in the pane. When editing, either the internal editor in the Balsa-mgr edit pane or an external editor as defined in the environment options can be nominated.

When a circuit is composed hierarchically, there is a choice of whether the resulting circuit is generated in a hierarchical or flattened manner. Balsa-mgr allows either representation.

- 1. Start balsa-mgr and select the project defined previously for the circuit buffer1a

- 2. Delete the file *buffer2b* from the project by selecting it in the file pane and right clicking to choose "Delete" from the pop-up menu. This step isn't actually necessary but *buffer2b* is not used again

- 3. Add the file *buffer2c* to the project.

- 4. Click on the Makefile tab in the left-hand pane of the balsa-mgr window. A set of compilation actions for *buffer2c* (see Figure 2.8) has been added to those for *buffer1a*.

- 5. View the handshake circuit by clicking on the **View** button for buffer2c.ps. A hierarchical view of the composed circuit is shown in Figure 2.9.

- 6. Determine the cost of the circuit: a cost of 558.75<sup>1</sup> should be reported. The cost is reported for the total of the hierarchical circuit and for the individual components.

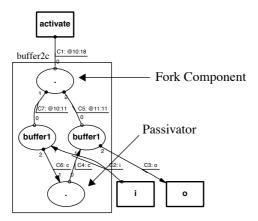

Figure 2.9 shows the extra components required to compose the two instances of the single place buffer. The Fork component activates the two single place buffers in parallel. The Passivator component. The Passivator component connects two active ports: the output port of the first buffer and the input port of the second buffer.

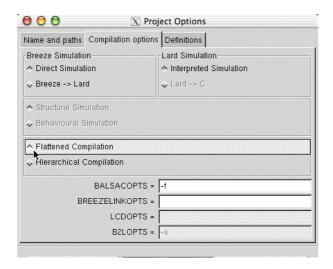

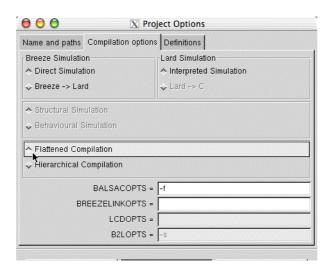

The description of buffer2c can be flattened during compilation by passing the appropriate flag through to the command line of the compilation tool. Balsa-mgr allows this to be done without detailed knowledge of the command line tools.

- 1. Click on the "Project Options" icon or select "Project ⇒ Options" from the pull-down menu.

- 1. The exact cost may vary between different releases of Balsa.

Figure 2.8: Buffer2c actions added to Makefile pane

Figure 2.9: Hierarchical view of buffer2c handshake circuit graph.

- 2. Click on the "Compilation Option" tab on the project dialogue window that appears (see Figure 2.3)

- 3. Check the check-box marked Flattened Compilation in the compilation option pane (see Figure 2.10). The exact layout of this window and the set of options available may be different from that shown because of developments in the Balsa system.

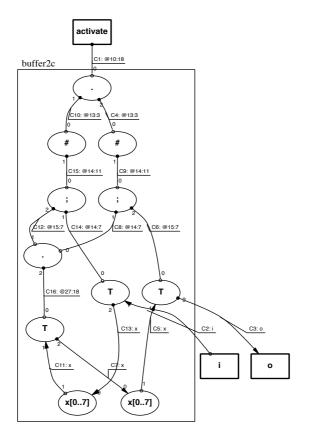

- 4. Rerun the view of the of the handshake circuit graph. A flattened view should be obtained as shown in Figure 2.11.

- 5. Restore the compilation settings to the default "Hierarchical Compilation"

Figure 2.10: The Compilation Options pane

Figure 2.11: Flattened view of buffer2c

#### 2.6. Simulation.

Apart from the various simulation possibilities available once the design has been converted to a silicon layout, there are three strategies for evaluating/simulating the design from Balsa.

#### Default test harness.

A default test harness can be generated. The default test harness exercises the target Balsa block by repeatedly handshaking on all external channels; input data channels receive auser defined value on each handshake, although it is possible to associate an input channel with a data file. Data sent to output channels appears on the output pane of the execution window. Note that if the interface to procedure under test is changed, a new test-harness must be generated. By default, the Makefile can not check this dependency: the test-harness file must either be removed manually or by running make clean.

#### 2. Balsa test harness

If a more sophisticated test sequence is required, Balsa is a sufficiently flexible language in its own right to be able specify most test sequences. A default test harness can then be generated to exercise the Balsa test harness: see "Building test harnesses with Balsa" on page 77.

Custom LARD test harness.

For some applications, it may be necessary to write a custom test harness in a language such as LARD. However, LARD is no longer supported as part of the Basla system.

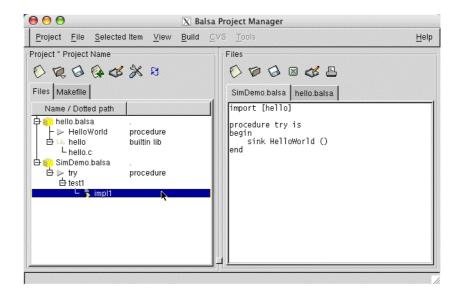

### Adding a test fixture.

To simulate a circuit description. using Balsa's simulation facilities, a test fixture has to be added to the design framework. The easiest way is to automatically generate a default test harness.

- 1. Make sure that buffer2 is selected in the Files pane.

- 2. Pick "Select Item ⇒ Add Test Fixture" from the pull-down menu or right-click in the left-hand "File" pane. A window for creating a text fixture is spawned [Figure 2.12]

Figure 2.12: The test fixtures pane

- 3. Change the name of the test fixture from the default (test1) to something more meaningful, e.g. buff2c

- 4. Select the Port Name "i"

- 5. Change the active radio button in the "Component Type" pane from "input value" to "input from file"

- 6. Some test values (in a variety of representations: decimal, hex and binary) have been provided in the file *th1.dat* in the directory containing the example. Set the value of the filename in the

"Port Value/Filename" text box to *th1.dat* either by typing directly into the text box or by clicking on the file browser button immediately to the right of the text box.

Note that data values can be specified in various notations (binary, octal, hexadecimal, decimal). The format of data files is line based: Only one data items is allowed per line and complex data types values should not be split across lines. Anything after a data item is treated as a comment and is passed to the simulation.

7. Dismiss the window by clicking OK.

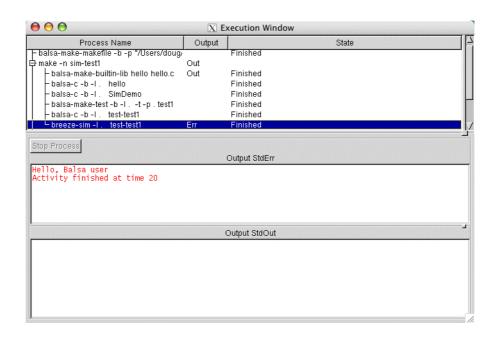

## Text-only simulation

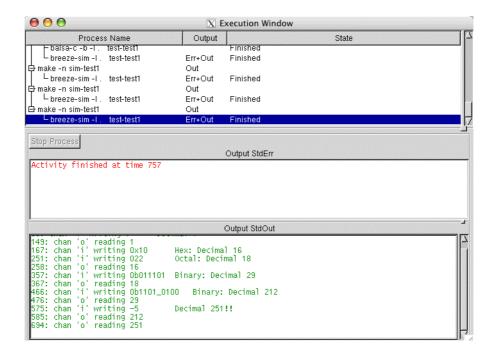

In order to run the test, click on the Makefile tab. The Makefile view shown in Figure 2.15 now

Figure 2.13: Test Harness added to Makefile pane

shows two actions added under the Tests" subpane. Clicking on the **Run** button for sim-buff2c generates the following output in the execution window. The numbers reported on the left hand side of each channel activity are simulation times – either the time at which data is presented at an input channel from the external environment or the time at which data is presented on an output channel to the external environment. Note however that the simulator has a very simplistic timing model, so these values should be treated with caution.

Figure 2.14: The ouput from a text-only simulation

Figure 2.15: Test Harness added to Makefile pane

Capturing output

The contents of the output window of the execution window can be captured by right-clicking in the output pane; alternatively the output can be directed to a file when defining or editing the test harness.

#### Graphical Simulation Tools

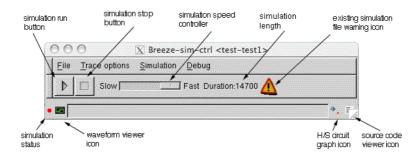

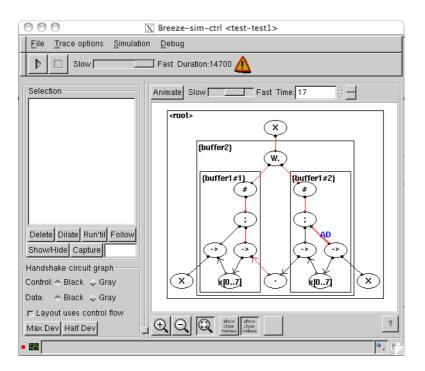

In the previous examples, the output of the simulation is textual appearing in the output pane of the execution window. The simulation may also be viewed in a conventional style waveform viewer or the channel activity can be viewed directly on a representation of the handshake circuit graph. To activate the viewers, switch to the Makefile pane of Balsa-mgr and click on **Run** button for sim-win-buff2c. This will generate any intermediate files required and bring up a window breeze-sim-ctrl (Figure 2.16) which controls the simulations and animations.

Figure 2.16: The Simulator Controller

#### The controller allows:

- a new simulation file for a design to be produced and displayed in a waveform viewer (GTKWave).

- an existing simulation file to be viewed in the GTKWave viewer.

- the speed of the simulation to be varied.

- the handshake circuit graph to be displayed, animated and analysed.

- the source code to be displayed.

- the associations between handshake circuit channels and source code constructs to be displayed.

Breeze-simcontroller icons

- If an existing simulation file is detected when the controller is started, a warning triangle icon is displayed to alert the user to the possibility that this file could be overwritten (the file has the extension of .hhh).

- An existing simulation file may be viewed without it being regenerated by clicking on the

waveform viewer icon at the bottom of the controller window. If the waveform viewer is

active, clicking on the icon kills the viewer.

- The coloured button at the bottom left of the controller window indicates the status of the simulation: red means the simulation is stopped, green that the simulation is running and blue that the simulation is paused.

- A new simulation trace file can be generated and displayed by clicking on the simulation run/pause button at top-left of the controller window. The simulation can be terminated by means of the simulation stop button to the right of the run/pause button. The simulation is displayed in the GTKWave viewer as the simulation file is produced. The speed of the simulation can be slowed down by means of the speed slider control.

- The two icons at the bottom right of the window reveal further functionality: the left icon

reveals a graph of the handshake circuit and the right button opens a window onto the

source code.

Generating the simulation trace

Although breeze-sim-ctrl can be used to view the static handshake circuit (in order, for example, to analyse the associations between the handshake elements and the Balsa description), its aim is to graphically control the simulation process and display the simulation events in various ways. Before any visualisation, it is necessary to generate a simulation trace. The presence of a simulation trace is indicated by the **Duration** indicator, showing the total length of the actual simulation. You can generate a new simulation (.hhh) trace file by running the simulation with the **Play** button. The simulation is generating events very quickly, and the trace file can quickly become very large. If your simulation is too long, you may want to keep the simulation trace short by slowing the simulation speed down with the slider control and by stopping the simulation with the **Stop** button when it reaches the desired size (the **Duration** indicator of the simulation is updated in real time).

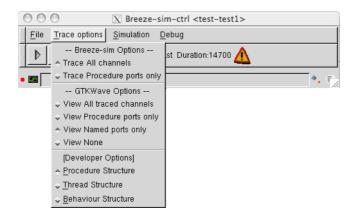

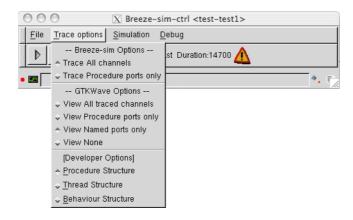

Which simulated events are saved in the trace file can be chosen from the Trace options menu, in the Breeze-sim options section (Figure 2.17). The choice is between tracing all the channels or tracing

Figure 2.17: Trace options menu

only the procedure ports. Tracing all the channels results in a large trace file containing all the necessary information for any kind of visualisation or post-analysis. Tracing only the procedure ports is useful for keeping the trace file small, while still being able to view in GTKWave the events happening at the interface of your procedures. This is often enough for checking that high-level communications are behaving as expected without going into the details of the implementation.

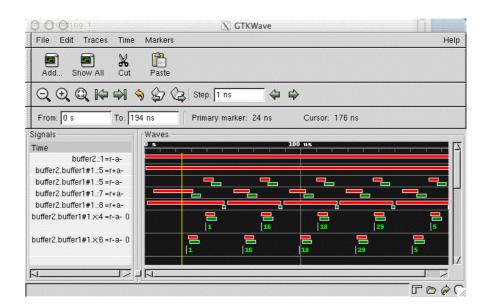

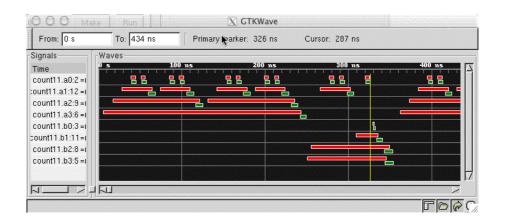

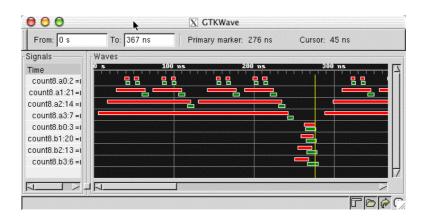

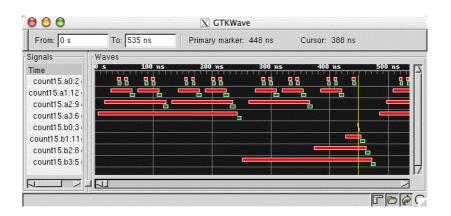

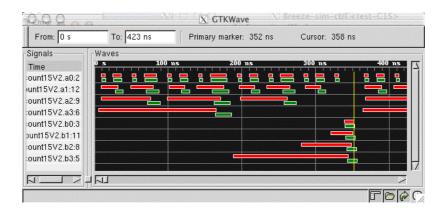

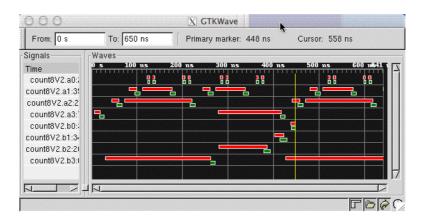

GTKWave, the Waveform Viewer Clicking on the waveform viewer icon or the simulation run button will start the GTKWave viewer (this automatic launch of GTKWave when a simulation is runned is the default behaviour, and can be overriden by placing an empty file named *nogtkwave* in the project directory). A list of channels is displayed in the right-hand pane as shown in Figure 2.18. Request signals are shown in red and

Figure 2.18: Channel viewer window.

acknowledge signals are shown in green. Data bearing channels have the data value displayed under

the request/acknowledge signals. Clicking in this pane will display a vertical timeline cursor in the window.

Which channels are viewed at the launch of GTKWave can be chosen from the Trace options menu, in the GTKWave options section (Figure 2.17). The four possible choices are *View all traced channels*, *View procedure ports only*, *View named ports only* and *View none*. They are self-explanatory, except perhaps the third one: Named ports correspond to all the procedure ports but the activation signals associated to every procedure (these signals do not have any name in the breeze file).

The left-hand pane shows the channel names and the state of the request/acknowledge signals and data values at the cursor point. It is necessary to click in the waveform display pane to get the channel names to display correctly in the first instance. GTKWave is highly configurable: a detailed description of its operation is not given here, rather a summary of its capabilities is provided below.

- The display of the traces passed to the viewer from the simulation controller can be configurable by use of the **add** or **add all** buttons. The former allows signals to be chosen from a pick-list or by a regular expression description together with range specifiers useful for specifying buses.

- Traces can be removed or repositioned by means of the **cut** and **paste** buttons.

- Traces can be sorted in a number of different ways.

- The traces can be zoomed in or out at the mid point of the display window by means of the **zoom** buttons.

- Specific areas of the display can be zoomed by right-click, drag in the display window.

- The display can be stepped by a fixed number of nsecs at a time or by the width of the display window.

- Data may be displayed in a number of formats.

- Markers can be added to the display.

- The various menubars and toolbars can be hidden by means of the icons at the bottom right of the window.

- The various menubars and tool bars are detachable. Click and drag on the gripper at the left-hand end of the bar to detach it. To return it to the window, drag it back to its correct place in the window or, more simply, double click on the gripper.

Viewing and animating the handshake circuit graph.

Note: the features described in this section are experimental and are likely to change in future releases. Not all buttons/controls are described – in the main this is because they are for internal developer use only.

If the handshake circuit graph icon (at the bottom-right corner of the controller window) is clicked, the controller window changes to that shown in Figure 2.19. It shows a graph representation of the handshake circuit compiled, and is intended to display the activity (events) happening on the various channels during the simulation.

First, you might want to change the layout style, especially if your graph does not appear nicely when using the default layout. This is done by selecting the check box entitled "Layout uses control flow", near the bottom left corner of the window. When this check box is selected, the layout hanshake circuit graph is laid out with the control flows going from top to bottom. When the check box is unselected, the graph is laid out based on data flows, with data flowing from top to bottom. The default style (data flow-based) gives a good visualisation of large circuit, especially when associated with the "Control: Gray" button (located above the check box). However, for small circuits, organising the data flow vertically does not always result in a nice layout.

Then, you might want to customise the appearance of the graph. For this, you can:

drag&drop components or groups.

Figure 2.19: Channel tree and handshake circuit graph revealed.

- resize groups with Shift+drag&drop.

- pan the display by dragging the background.

- zoom in/out by using the zoom icons.

- toggle the channel names and their values by using the next toggle icons.

- reduce/develop groups to show their components and sub-groups with middle-click and right-click (Right-clicking on a group reduces/develops its sub-groups; Middle-clicking on a group hides/shows its handshake components. You typically need to use right-click to fully develop groups and middle click to fully reduce them).

- make a group become the main viewed group by using Ctrl+Left click. Ctrl+Shift+click

sets the parent of the selected group to be the main viewed group, and you can use

successive Ctrl+Shift+clicks on successive parents to go back to a higher level view of the

circuit.

On the left, a group of controls offer you to gray some parts of the circuit out, in order to visualise more effectively either the control flow or the data flow. The **Max Dev** button recursively develops every group in the circuit.

Pressing the empty icon button under the graph view develops a new button bar for accessing developpers' functionalities. The first button, "Screen Shot", may be useful to you, as it generates a screenshot.ps file in the current directory, containing a postscript version of the viewed graph (however, the graph is usually not centered on the page and needs post-processing).

The circuit is then animated by clicking on the **Animate** button. The speed of the animation can be modified by means of the slider control next to the button. The animation may be stepped by means of the up/down arrows next to the current time value. As a short-cut, right-clicking on the arrows will take the simulation to the start/end of the animation. This feature is useful for rerunning the animation. The two buttons next to the time-controlling up/down arrows are stepping the animation to the next/previous viewable event.

Clicking on a channel selects it for a list of action available in the left-hand pane entitled "Selection":

- "Delete" unselects a channel(s).

- "Dilate" expands the selection to the surrounding channels.

- "Run'til" runs the simulation until some activity appears on the selected channel(s).

- "Follow" runs until some activity on the channel and then looks for activity on the surrounding channels and expand the selection to those newly activated surrounding channels

When "Capture" is pressed, hovering the mouse over a handshake channel automatically selects it. Associated with the source code viewer, one can quickly see what source code corresponds to each channel.

Finally, the text box next to the Capture button is a search box that selects/unselects all the channels whose name contain the entered string (the search is run when the user presses the Return key). This search box is useful, for example, when dealing with Verilog files generated from the Balsa description: The channel numbers being the same in Verilog and in Breeze, specific Verilog channel numbers can be searched and viewed on the handshake circuit graph (or in the source code viewer, in order to link Verilog back to the original Balsa description).

Debugging a deadlock

If your simulation ends up in an unexpected deadlock, you can try our "deadlock debugging helper", currently in development (i.e. if it does not work for you, it is kind of normal). Select the channel corresponding to the latest event that happened during your simulation and run the deadlock analysis by selecting "Highlight Deadlock" in the Debug menu. It should highlight (and add in the Selection box) a list of channels which are thought to be related to the deadlock. The most useful channels for debugging the deadlock are those where a change of channel activity happens, for example when the string of highlighted channels passes from a channel where no event happened to a channel blocked with a "Request Up" event pending. You can follow this string of highlighted channels and use the source code view to locate the position of some of them, as explained below.

Source Code Viewer Clicking the source code viewer icon brings up a separate (initially empty) window. It is advised to click on "Show All Channel Positions", in order to load every file and colorise keywords according to the handshake channels that are referred to in the compiled circuit. Once the source code window is open, any channel selection from the main window is reported at the bottom of the source code window. A subsequent click on the "Goto Source" button highlights the source code that correspond to the selected channel. In the other way around, it is possible to select channels that correspond to a keyword from the source code by right-clicking after the first letter of the desired keyword and choosing "Select Channels" in the contextual menu (the algorithm searches backwards from the selected character until it finds a matching channel). When the checkbox next to the "Goto Source" button is selected, any newly selected channel will be automatically reported inside the source code, as if the user pressed the "Goto Source" button after selecting the channel. Unselecting "Notebook style" displays every opened file simultaneously, next to each other.

#### 2.7. Compilation and Simulation Options

These options are reached by clicking on the "Project Options" icon or selecting "Project  $\Rightarrow$  Options" from the pull-down menu.s and selecting the compilation pane.

#### Flattened vs hierarchical compilation

As discussed in earlier (see "Flattened vs non-flattened view" on page 16), this option allows a choice of flattening the design during the compilation process or maintaining the hierarchy. A flattened design allows a slightly greater degree of peephole optimisation to take place, but at the expense of exposing the internal channels and losing the hierarchy at later stages of the design process. The hierarchical view is more appropriate for most users and this is the default setting in the balsa-mgr.

#### Direct Simulation vs Breeze ⇒ Lard

Users are strongly recommended to use only the direct simulation route. This uses the new breeze simulation engine and GTKWave channel viewer environment which has been described earlier. Checking the Breeze  $\Rightarrow$  Lard box will enable the old deprecated LARD simulation environment.

## Lard simulation options

If the Breeze ⇒ Lard route is (against all advice) chosen, users have two choices:

**Interpreted Simulation:** This is the default option and works with the existing LARD channel viewer. It is however very slow.

$\mathbf{Lard} \Rightarrow \mathbf{C}$ : This option considerably speeds simulation times (by up to two orders of magnitude compared to an interpreted simulation), but can not be used with the LARD channel viewer, nor can it currently be used under MacOS X. The speed is still significantly slower than the new Breeze simulation engine.

#### Structural vs behavioural simulation

This option only applies to users who are still persisting with the deprecated LARD simulation route. It will be removed in subsequent releases of the Balsa system.

Users may choose whether to use behavioural or structural simulation. Behavioural simulation (the default) is much faster. However the timings are not necessarily representative of relative channel activity. Structural simulation allows the interaction between the handshake components to be explored more accurately and is useful as a teaching aid to understanding the behaviour of fine grained asynchronous circuits. However, as the overall timings are still very approximate, users only interested in functional simulation are recommended to use the behavioural option.

Users may wish to explore the significance of the various options by simulating *buffer2c* with various combinations of switches.

# The Balsa Language

#### **Summary**

The previous chapter introduced Balsa, but was mostly concerned with the auxiliary tools that support the Balsa environment. The language itself is small and in this section most of its major features and constructs are introduced. Later chapters discuss more advanced topics such as parameterisation and recursively defined structures ("Parameterised & Recursively Defined Circuits" on page 49) and the enclosed semantics of the choice operator ("Handshake Enclosure" on page 55). A more formal and complete, BNF style, language description can be found in Table 11.1 on page 127.

#### 3.1. Data Types

Balsa is strongly typed with data types based on bit vectors. Results of expressions must be guaranteed to fit within the range of the underlying bit vector representation. There are two classes of anonymous types: numeric types which are declared with the bits keyword and arrays of other types. Numeric types can be either signed or unsigned. Signedness has an effect on expression operators and casting. Only numeric types and arrays of other types may be used without first binding a name to those types. Balsa has three separate namespaces: one for procedure and function names, a second for variable and channel names and a third for type declarations.

#### **Numeric types**

Numeric types incorporate numbers over the range  $[0, 2^n - 1]$  or  $[-2^{n-1}, 2^{n-1} - 1]$  depending on whether they represent either unsigned or signed and where  $n \in [1, INT\_MAX]$ ; on a 32-bit machine  $n \in [1, 2^{32} - 1]$ . Named numeric types are just aliases of the same range. An example of a numeric type declaration is:

```

type word is 16 bits

```

This defines a new type word which is unsigned (there is no unsigned keyword) covering the range  $[0, 2^{16} - 1]$ . Alternatively, a signed type could have been declared as:

```

type sword is 16 signed bits

```

which defines a new type sword covering the range  $[-2^{15}, 2^{15}, 2^{15}]$ .

Some predefined types are available in *<BalsaInstallDir>/share/balsa/types/basic.balsa*. including byte, nibble, boolean and cardinal as well as the constants true and false. Other predefined

types may be added from time to time. Users are advised to consult the contents of the file in their particular release of the Balsa system.

### Enumerated types

Enumerated types consist of named numeric values. The named values are given values starting at zero and incrementing by one from left to right. Elements with explicit values reset the counter and many names can be given to the same value, for example:

```

type Colour is enumeration

Black, Brown, Red, Orange, Yellow, Green, Blue, Violet

Purple=Violet, Grey, Gray=Grey, White

end

```

The value of the Violet element of Colour is 7, as is Purple. Both Grey and Gray have value 8. The total number of elements is 12. An enumeration can be padded to a fixed size by use of the over keyword:

```

type SillyExample is enumeration

el=1, e2

over 4 bits

```

Here 2 bits are sufficient to specify the 3 possible values of the enumeration (0 is not bound to a name, e1 has the value 1 and e2 has the value 2). The over keyword ensures that the representation of the enumerated type is actually 4 bits.

Occasionally, it is necessary when referring to an element of an enumeration to indicate the type to which that element belongs. The notation Colour'Purple specifically indicates the identifier Purple as being a member of Colour. Most users will never need this notation; about the only time it is required is when using elements of enumerations within casts and even in that case there are more transparent ways of achieving the same effect.

Enumeration types must be bound to names by a type declaration before use.

#### **Record types**

Records are bitwise compositions of named elements of possibly different (pre-declared) types with the first element occupying the least significant bit positions, e.g.:

```

type Resistor is record