## The Thumb instruction set

- Outline:

- O the Thumb programmers' model

- O Thumb instructions

- O Thumb implementation

- O Thumb applications

hands-on: writing Thumb assembly programs

## The Thumb instruction set

#### Outline:

#### the Thumb programmers' model

- O Thumb instructions

- O Thumb implementation

- O Thumb applications

hands-on: writing Thumb assembly programs

#### Thumb is:

- a compressed, 16-bit representation of a subset of the ARM instruction set

- primarily to increase code density

- also increases performance in some cases

- Let is not a complete architecture

- O all 'Thumb-aware' cores also support the ARM instruction set

- therefore the Thumb architecture need only support common functions

**MANCHEstER**

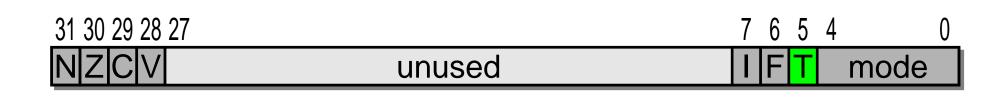

### The Thumb bit

- The 'T' bit in the CPSR controls the interpretation of the instruction stream

- switch from ARM to Thumb (and back) by executing BX instruction

- O exceptions also cause switch to ARM code

- return symmetrically to ARM or Thumb code

- Note: do not change the T bit with MSR!

**MANCHEstER**

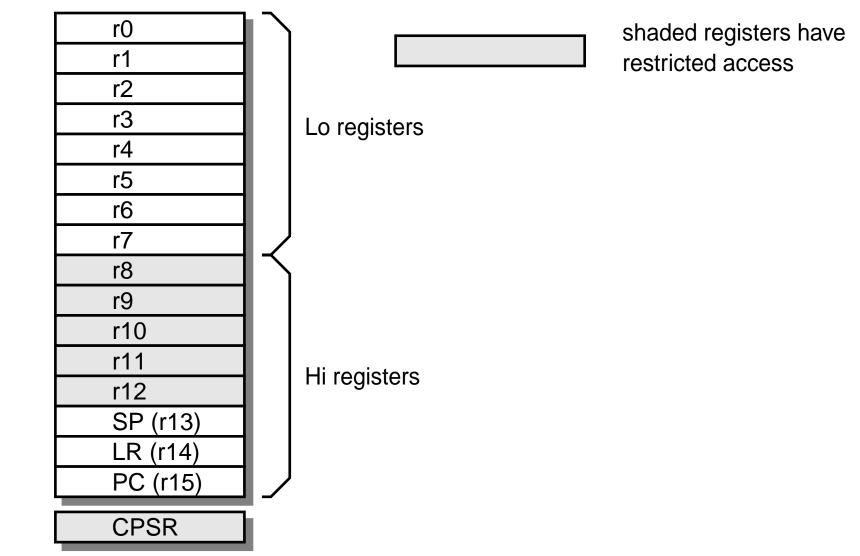

# The Thumb programmers' model

#### MANCHEstER The Thumb programmers' model

- Thumb register use:

- O r0 r7 are general purpose registers

- Image: right of the second second

- in ARM code this is a software convention

- In the second second

- implicitly, as in the ARM instruction set

- a few instructions can access r8 r15

- O the CPSR flags are set by data processing instructions & control conditional branches

# The Thumb programmers' model

- Thumb-ARM similarities:

- O load-store architecture

- with data processing, data transfer and control flow instructions

- O support for 8-bit byte, 16-bit half-word and 32-bit data types

- half-words are aligned on 2-byte boundaries

- words are aligned on 4-byte boundaries

- O 32-bit unsegmented memory

# The Thumb programmers' model

- **Thumb-ARM differences:**

- O most Thumb instructions are unconditional

- all ARM instructions are conditional

- O most Thumb instructions use a 2-address format

- most ARM instructions use a 3-address format

- O Thumb instruction formats are less regular

- a result of the denser encoding

- O Thumb has explicit shift opcodes

- ARM implements shifts as operand modifiers

## The Thumb instruction set

#### Outline:

O the Thumb programmers' model

#### Thumb instructions

- O Thumb implementation

- O Thumb applications

hands-on: writing Thumb assembly programs

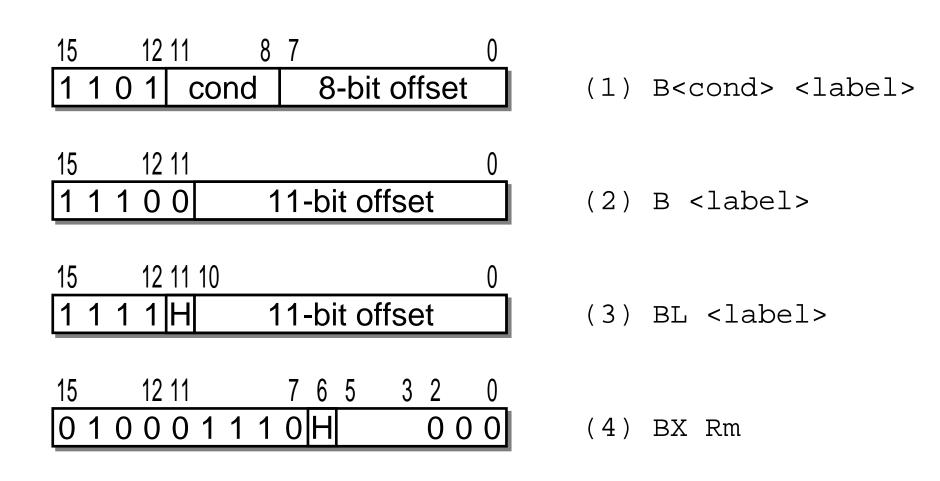

#### **Thumb branch instructions**

## **Thumb branch instructions**

MANCHEstER

- These are similar to ARM instructions except:

- O offsets are scaled to half-word, not word

- range is reduced to fit into 16 bits

- BL works in two stages:

```

H=0: LR := PC + signextend(offset << 12)

H=1: PC := LR + (offset << 1)

LR := oldPC + 3</pre>

```

- the assembler generates both halves

- LR bit[0] is set to facilitate return via BX

## **Thumb branch instructions**

- Branch and eXchange (BX)

- to return to ARM or Thumb caller:

- BX lr ; replaces MOV pc, lr

- Subroutine calls

- O later ARMs support BLX instruction

- O to synthesize BLX or earlier ARM:

```

ADR r0, subr + 1 ; "+ 1" to enter Thumb mode

ADR lr, return ; save return address

BX r0 ; calls subr

return ...;

```

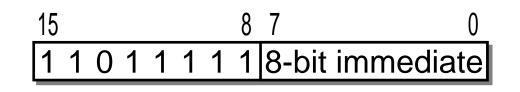

### Thumb software interrupts

The Thumb SWI operates exactly like the ARM SWI

• the (interpreted) immediate is just 8 bits

- Thumb Angel SWI uses value 0xAB

r0 call value is exactly as in ARM code

- the SWI handler is entered in ARM code

- the return automatically selects ARM or Thumb

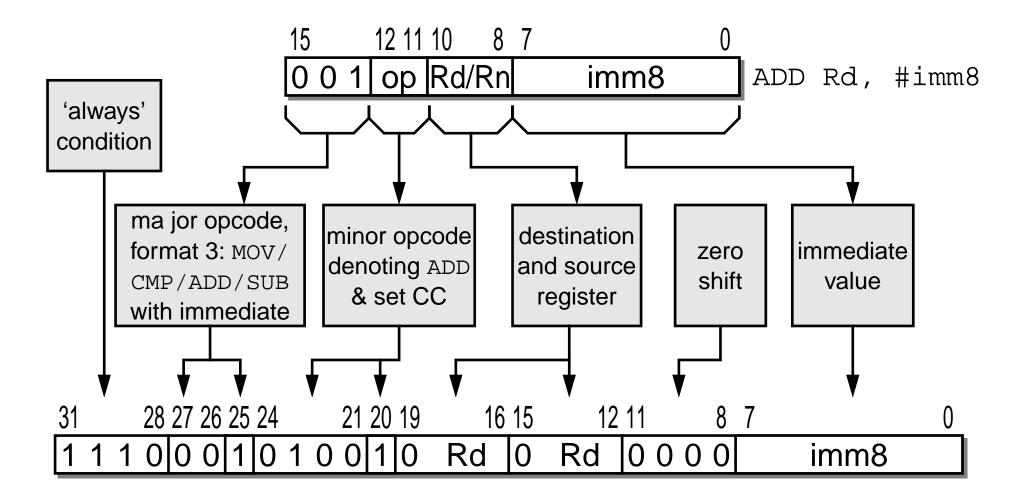

# Thumb data processing instructions

| 15 10 9 8 6 5 3 2 0<br>0 0 0 1 1 0 A Rm Rn Rd                                                                                         | (1) ADD SUB Rd,Rn,Rm            |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 15 10 9 8 6 5 3 2 0<br>0 0 0 1 1 1 A imm3 Rn Rd                                                                                       | (2) ADD SUB Rd,Rn,#imm3         |

| 15 12 11 10 8 7 0<br>0 0 1 op Rd/Rn imm8                                                                                              | (3) MOV CMP ADD SUB Rd/Rn,#imm8 |

| 15       13       12       11       10       6       5       3       2       0         O       O       O       O       main       #sh | (4) LSL LSR ASR Rd,Rn,#shift    |

| MANCHEster<br>1824<br>Thumb data p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | rocessing instructions    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| The Oniversity         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I         O I I         O I I I | (5) <op> Rd/Rn,Rm/Rs</op> |

| 15 10 9 8 7 6 5 3 2 0<br>0 1 0 0 0 1 op DM Rm Rd/Rn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (6) ADD CMP MOV Rd/Rn,Rm  |

| 15 12 11 10 8 7 0<br>1 0 1 0 R Rd imm8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (7) ADD Rd, SP PC, #imm8  |

| 15 876 0<br>10110000A imm7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (8) ADD SUB SP, SP, #imm7 |

**O** In case (6):

MOV does not affect the flags (it can be distinguished using the mnemonic CPY after v6)

## Thumb data processing instructions

- Notes:

- in Thumb code shift operations are separate from general ALU functions

- in ARM code a shift can be combined with an

- → ALU function in a single instruction

- all data processing operations on the 'Lo' registers set the condition codes

- those on the 'Hi' registers do not, apart from CMP which only changes the condition codes

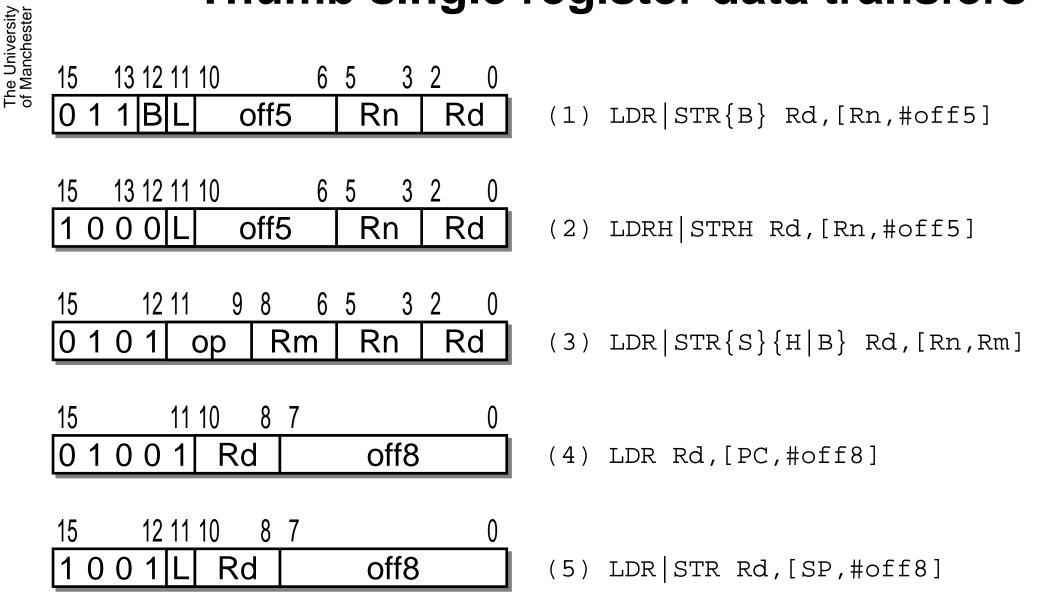

# Thumb single register data transfers

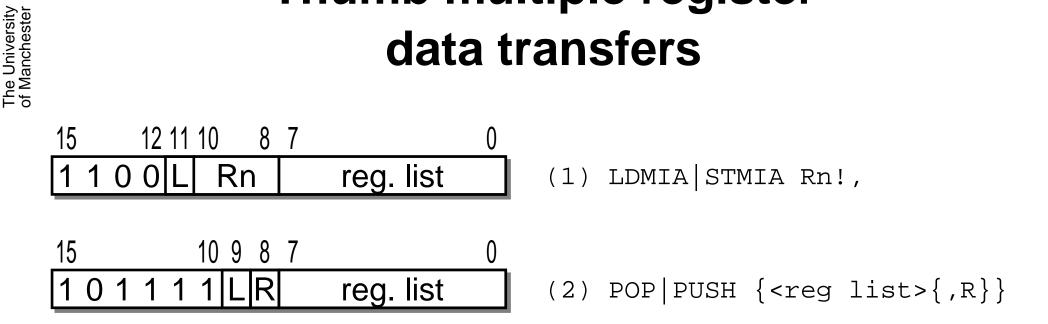

## Thumb multiple register data transfers

These map directly onto the ARM forms:

STMFD SP!, {<regs>{, lr}} PUSH:

LDMFD SP!, {<regs>{, pc}} POP:

note restrictions on available addressing modes compared with ARM code

## **Unique Thumb mnemonics**

#### Most significant differences from ARM:

| PUSH | ; | STMFD sp!, $\{\&\}$                  |

|------|---|--------------------------------------|

| POP  | ; | LDMFD sp!, $\{\&\}$                  |

| NEG  | ; | RSB Rd, Rs, #0                       |

| LSR  | ; | MOV Rd, Rd, LSR <rs #5=""  =""></rs> |

| ASR  | ; | MOV Rd, Rd, ASR <rs #5=""  =""></rs> |

| LSL  | ; | MOV Rd, Rd, LSL <rs #5=""  =""></rs> |

| ROR  | ; | MOV Rd, Rd, ROR Rs                   |

MANCHEstER

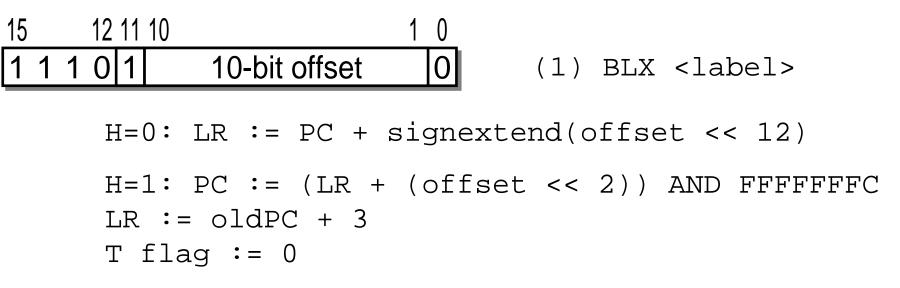

#### **MANCHEstER Newer Thumb instructions (from v5)**

BLX works in two stages; (first is same as BL)

There is also a register-based BLX

2 15 6 Rm 000 (2)  $\mathbf{O}$  $\mathbf{O}$ ()BLX Rm

#### **BKPT** (Breakpoint)

#### MANCHEstER **Newer Thumb instructions (from v6)**

1824

- Mnemonic allowing register moves without affecting flags \_

- O SXTB/SXTH/UXTB/UXTH

- Sign extension (no shifts)

- O REV/REV16/REVSH

- Byte swaps

- O SETEND

- CPSIE/CPSID

- Interrupt enable/disables (no mode changes)

#### More about these in later ARM session.

## **ARM/Thumb interworking**

- The University of Manchester

- BX (Branch eXchange) moves to the mode specified by the address LSB (in register)

- BLX (Branch with Link and eXchange) moves to the other mode (common case)

- the LSB of LR retains the 'parent' mode

- BLX Rm can move to either mode (like BX)

- □ The 'correct' subroutine return is:

- BX LR

- O the routine can then be called from both ARM and Thumb code

## **ARM/Thumb interworking**

#### Calling procedures in other instruction set

O ARM v5 or later

procedure ; ARM or Thumb BLX O ARM v4T from ARM ADR lr, return\_addr ; ADR r0, procedure + 1 ; + 1 sets `T' BX r0 Ì return addr . . . from Thumb LDR r0, =procedure i MOV lr, pc `here' + 4 ; BX r0 ; . . .

MANCHEstER

## The Thumb instruction set

**0**

#### Outline:

- O the Thumb programmers' model

- O Thumb instructions

- Thumb implementation

- O Thumb applications

hands-on: writing Thumb assembly programs

## Thumb decoding

- The original Thumb implementation translated the opcodes into ARM opcodes.

- This means the effect of Thumb and ARM instructions are the same

- Thumb is more restricted (e.g. smaller offsets/immediates)

- One or two new functions (e.g. BL details)

Later implementations decode Thumb directly

**MANCHEstER**

# Thumb - ARM instruction mapping

MANCHEstER

## The Thumb instruction set

The University of Manchester

#### Outline:

- O the Thumb programmer's model

- O Thumb instructions

- O Thumb implementation

- Thumb applications

hands-on: writing Thumb assembly programs

## **Thumb applications**

- **Thumb code properties:**

- 70% of the size of ARM code

- 30% less external memory power

- 40% more instructions

- With 32-bit memory:

- ARM code is 40% faster than Thumb code

- With 16-bit memory:

- Thumb code is 45% faster than ARM code

MANCHEstER

## **Thumb applications**

**MANCHEstER**

- □ For the best performance:

- O use 32-bit memory and ARM code

- □ For best cost and power-efficiency:

- use 16-bit memory and Thumb code

- □ In a typical embedded system:

- use ARM code in 32-bit on-chip memory for small speedcritical routines

- use Thumb code in 16-bit off-chip memory for large noncritical control routines

## Hands-on: writing Thumb assembly programs

#### Explore further the ARM software development tools

• Write Thumb assembly programs

O Check that they work as expected

Follow the 'Hands-on' instructions