# HARDWARE LANGUAGES AND PROOF

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2011

By Dominic Anthony Richards School of Computer Science

## Contents

| Al | Abstract |                                                  | ix   |

|----|----------|--------------------------------------------------|------|

| De | eclara   | tion                                             | xi   |

| Co | opyri    | ght                                              | xiii |

| Ac | cknov    | vledgments                                       | XV   |

| 1  | Intr     | oduction                                         | 1    |

|    | 1.1      | An Explosion of Complexity                       | 1    |

|    | 1.2      | Modern Hardware Design                           | 4    |

|    |          | 1.2.1 The IC Design Flow                         | 7    |

|    |          | 1.2.2 Functional Verification                    | 7    |

|    | 1.3      | Formal Methods                                   | 9    |

|    |          | 1.3.1 Verification by Mathematical Proof         | 9    |

|    |          | 1.3.2 Clean Abstractions and Semantic Elegance   | 11   |

|    | 1.4      | Synopsis                                         | 12   |

|    | 1.5      | Publications and Source Code                     | 14   |

| 2  | Veri     | fying a Network-on-Chip                          | 15   |

|    | 2.1      | Networks-on-Chip                                 | 15   |

|    | 2.2      | SpiNNaker: A Spiking Neural Network Architecture | 16   |

|    |          | 2.2.1 Fault Tolerance and Emergency Routing      | 18   |

|    | 2.3      | Concurrent Haskell                               | 22   |

|    | 2.4      | Specifying a Network-on-Chip                     | 25   |

|    |          | 2.4.1 Packets and Physical Links                 | 25   |

|    |          | 2.4.2 IP Blocks                                  | 25   |

|    |          | 2.4.3 Arbiters                                   | 25   |

|   |      | 2.4.4 Routers                                       | 26 |

|---|------|-----------------------------------------------------|----|

|   | 2.5  | Specifying the SpiNNaker NoC                        | 27 |

|   |      | 2.5.1 Packets and Inter-Chip Links                  | 27 |

|   |      | 2.5.2 ARM Cores                                     | 28 |

|   |      | 2.5.3 NoC Arbiters and Routers                      | 28 |

|   | 2.6  | Verifying the SpiNNaker NoC                         | 32 |

|   | 2.7  | Related Work                                        | 33 |

|   | 2.8  | Summary                                             | 35 |

| 3 | Blue | espec SystemVerilog                                 | 37 |

|   | 3.1  | Syntax and Semantics                                | 37 |

|   |      | 3.1.1 One-Rule-at-a-Time Semantics                  | 39 |

|   |      | 3.1.2 Static Elaboration and Staging                | 39 |

|   | 3.2  | Peterson's Algorithm                                | 40 |

|   | 3.3  | Arbiter Control Circuit                             | 44 |

|   | 3.4  | Summary                                             | 48 |

| 4 | Auto | omated Reasoning for Bluespec SystemVerilog         | 49 |

|   | 4.1  | Automated Reasoning                                 | 49 |

|   | 4.2  | Logics and Decidability                             | 50 |

|   | 4.3  | Propositional, First Order and Higher Order Logic   | 51 |

|   | 4.4  | Temporal Logics                                     | 52 |

|   |      | 4.4.1 Kripke Structures and Computation Trees       | 53 |

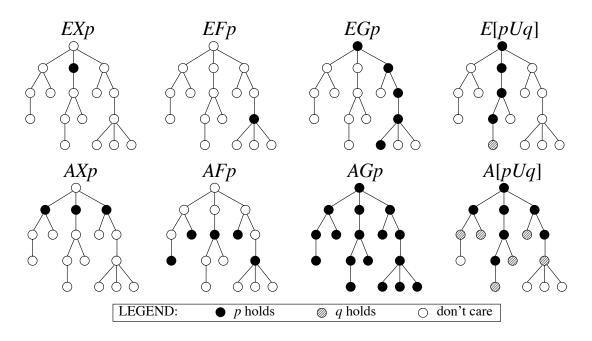

|   |      | 4.4.2 Computation Tree Logic                        | 54 |

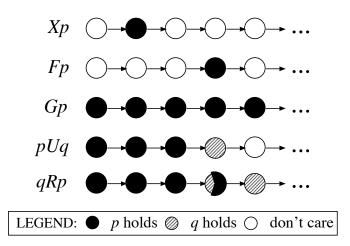

|   |      | 4.4.3 Linear Temporal Logic                         | 56 |

|   | 4.5  | Automatic Proof Tools                               | 56 |

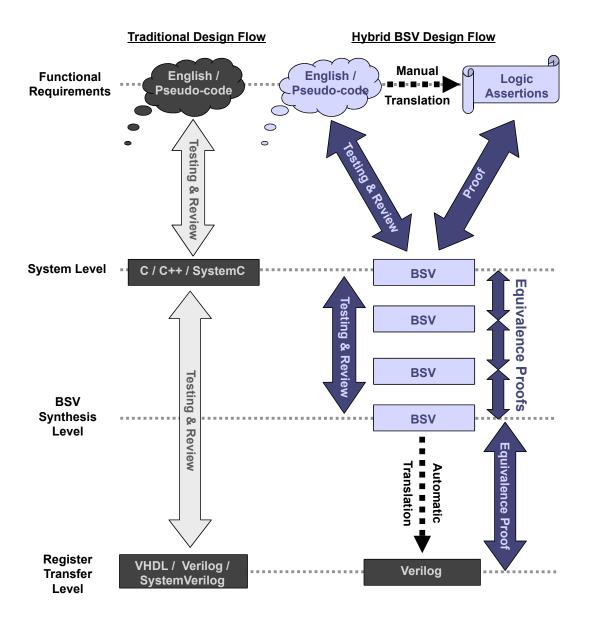

|   | 4.6  | Automated Reasoning in the IC Design Flow           | 57 |

|   | 4.7  | Functional Verification of ESL Specifications       | 59 |

|   |      | 4.7.1 How to Verify a State Machine                 | 61 |

|   |      | 4.7.2 Tools for Scalable State Machine Verification | 62 |

|   | 4.8  | Summary                                             | 63 |

| 5 | Eml  | bedding Bluespec SystemVerilog in the PVS Logic     | 65 |

|   | 5.1  | Embedding BSV in Logic                              | 65 |

|   | 5.2  | Embedding the State of a BSV Module                 | 66 |

|   | 5.3  | Embedding the Semantics of a BSV Module             | 68 |

|   | 5.4  | Embedding Rules: A Primitive Approach    6                 | 59  |

|---|------|------------------------------------------------------------|-----|

|   | 5.5  | Embedding Rules: A Monadic Approach                        | 1   |

|   |      | 5.5.1 Extensional Equivalence                              | 74  |

|   | 5.6  | A Primer on Monads in PVS                                  | 75  |

|   | 5.7  | A Monadic Representation of BSV Methods                    | 9   |

|   |      | 5.7.1 Implicit Conditions                                  | 80  |

|   |      | 5.7.2 Embedding the Methods of the mkReg Module 8          | 80  |

|   |      | 5.7.3 Embedding the Methods of the mkFIFO1 Module 8        | 81  |

|   | 5.8  | Monad Connectors for the BSV Monad                         | 33  |

|   | 5.9  | Monad Transformers                                         | 33  |

|   | 5.10 | Composing Monads to form Rules                             | 37  |

|   | 5.11 | Experimental Results                                       | 88  |

|   | 5.12 | Shallow, Deep and Reflective Embedding                     | )1  |

|   | 5.13 | Summary                                                    | 92  |

| 6 | Veri | fying BSV Designs with the PVS Theorem Prover 9            | )3  |

|   | 6.1  | Model Checking in PVS                                      | 93  |

|   |      | 6.1.1 Limitations of the PVS Model Checker                 | 95  |

|   | 6.2  | Temporal Theorems for BSV Module Instances    9            | 95  |

|   |      | 6.2.1 Theorems for Peterson's Protocol                     | 96  |

|   |      | 6.2.2 Theorems for a Round-Robin Arbiter                   | 98  |

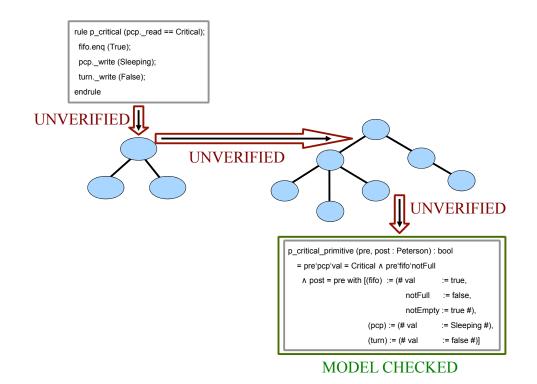

|   | 6.3  | Model Checking BSV Embeddings                              | 99  |

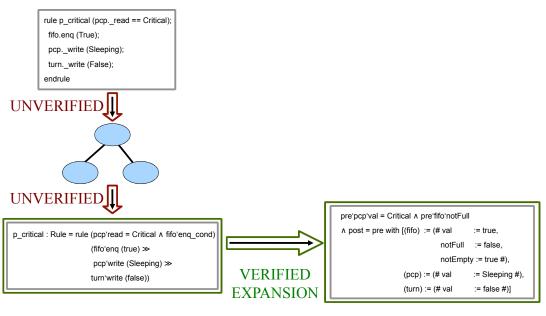

|   |      | 6.3.1 A Worked Example of Proof with Expansion             | )1  |

|   |      | 6.3.2 A Worked Example of Proof with Rewriting             | )3  |

|   | 6.4  | Proof Strategies                                           | )4  |

|   | 6.5  | Experimental Results                                       | )8  |

|   |      | 6.5.1 Proof with Expansion versus Proof with Rewriting 10  | )9  |

|   | 6.6  | Summary                                                    | )9  |

| 7 | Veri | fying BSV Designs with the Symbolic Analysis Laboratory 11 | 1   |

|   | 7.1  | The Symbolic Analysis Laboratory                           | . 1 |

|   | 7.2  | Model Checking with SAL                                    | 2   |

|   | 7.3  | Embedding BSV in the SAL Language                          | .4  |

|   |      | 7.3.1 Primitive Embedding of Rules                         | .6  |

|   |      | 7.3.2 Monadic Embedding of Rules                           | 6   |

|   | 7.4  | Verifying BSV-to-SAL Translation                           | .7  |

|    | 7.5   | Verifying Peterson's Protocol            | 119 |

|----|-------|------------------------------------------|-----|

|    | 7.6   | Verifying an Arbiter Control Circuit     | 121 |

|    | 7.7   | Summary                                  | 121 |

| 8  | Rela  | ated Work                                | 125 |

|    | 8.1   | Monads for Specification and Proof       | 125 |

|    | 8.2   | Guarded Action Languages                 | 126 |

|    |       | 8.2.1 Bluespec SystemVerilog             | 127 |

|    |       | 8.2.2 $TLA^+$                            | 127 |

|    |       | 8.2.3 Unity                              | 129 |

|    |       | 8.2.4 Event-B                            | 130 |

|    |       | 8.2.5 Languages for Model Checking       | 130 |

|    | 8.3   | Functional Hardware Languages            | 131 |

|    |       | 8.3.1 Behavioural Languages              | 131 |

|    |       | 8.3.2 Structural Languages               | 132 |

|    |       | 8.3.3 Synthesis from Logic               | 132 |

|    | 8.4   | Automated Reasoning for Ad Hoc Languages | 132 |

|    |       | 8.4.1 Forte                              | 133 |

|    |       | 8.4.2 RuleBase                           | 134 |

|    |       | 8.4.3 DE2                                | 135 |

|    |       | 8.4.4 AMD                                | 135 |

|    | 8.5   | Summary                                  | 135 |

| 9  | Con   | clusion                                  | 137 |

|    | 9.1   | Concurrent Haskell                       | 137 |

|    | 9.2   | Bluespec SystemVerilog                   | 138 |

|    |       | 9.2.1 Topics for Further Work            | 139 |

|    | 9.3   | Final Thoughts                           | 141 |

| Bi | bliog | raphy                                    | 143 |

# **List of Figures**

| 1.1 | A Typical IC Design Flow, Including Functional Verification     | 6  |

|-----|-----------------------------------------------------------------|----|

| 2.1 | A Mesh NoC Topology                                             | 16 |

| 2.2 | The SpiNNaker System Architecture                               | 17 |

| 2.3 | Organisation of the SpiNNaker Chip                              | 19 |

| 2.4 | Emergency Routing.                                              | 20 |

| 2.5 | Emergency Routing Scenarios                                     | 21 |

| 2.6 | A Grammar of Process Types for Concurrent Haskell               | 22 |

| 2.7 | A Reaction Relation for Concurrent Haskell                      | 24 |

| 2.8 | A component of the SpiNNaker NoC specification.                 | 29 |

| 3.1 | A Test Bench for mkArbiter                                      | 47 |

| 4.1 | A Grammar of Propositional Logic                                | 51 |

| 4.2 | A Grammar of First Order Logic                                  | 52 |

| 4.3 | A Grammar of Computation Tree Logic                             | 54 |

| 4.4 | Computation Tree Logic                                          | 55 |

| 4.5 | A Grammar of Linear Temporal Logic                              | 56 |

| 4.6 | Linear Temporal Logic                                           | 57 |

| 4.7 | Automated Reasoning for BSV: A Conceptual Design Flow           | 58 |

| 4.8 | ITRS 2009 Formal Methods Roadmap                                | 60 |

| 5.1 | Verification of a Primitive Embedding in PVS                    | 71 |

| 5.2 | Monadic Embeddings of the Peterson Rules in PVS                 | 72 |

| 5.3 | Monadic Embeddings of the mkTbArbiter Rules in PVS              | 73 |

| 5.4 | Verification of a Monadic Embedding in PVS                      | 74 |

| 5.5 | A Monadic Embedding of the mkFIFO1 Module                       | 82 |

| 5.6 | Extracts from the Peterson PVS Embedding                        | 89 |

| 5.7 | Monadic Rules and Methods from the PVS Embedding of mkArbiter . | 90 |

| 6.1 | Computation Tree Logic in PVS                               | 94  |

|-----|-------------------------------------------------------------|-----|

| 6.2 | Verification Strategies for Monadic Specifications          | 100 |

| 6.3 | Proof Strategies to Expand Monadic Transition Relations     | 105 |

| 7.1 | The Transition Relation of the Primitive Peterson Embedding | 115 |

| 7.2 | BSV Verification with PVS and SAL                           | 118 |

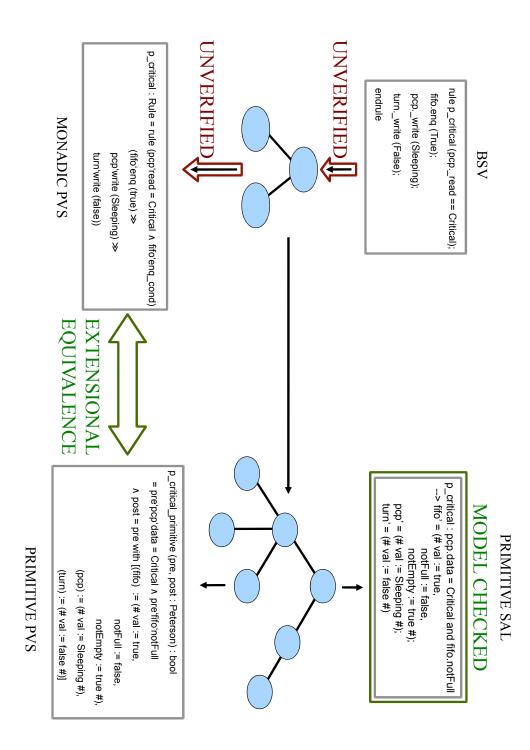

| 7.3 | A BSV Rule and its Embeddings in PVS and SAL                | 120 |

| 7.4 | Extracts from the Primitive Arbiter Embedding               | 122 |

## Abstract

HARDWARE LANGUAGES AND PROOF: A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy by Dominic Richards on 3<sup>rd</sup> April, 2011.

Formal methods play a significant and increasing role in hardware verification, but their effectiveness can be impaired by the *ac hoc* nature of mainstream hardware languages such as VHDL, Verilog and SystemC, which have convoluted semantics that often necessitate contrived proof techniques. This dissertation investigates the application of formal reasoning to hardware architectures expressed in an alternative class of *semantically elegant* languages, which support efficient design, whilst also having been developed with proof techniques in mind.

A network-on-chip architecture belonging to the SpiNNaker many-core processor is specified in Concurrent Haskell, and a hand proof is presented which verifies a novel routing mechanism by mathematical induction.

A subset of Bluespec SystemVerilog (BSV) is embedded in the higher order logic of the PVS theorem prover. Owing to the clean semantics of BSV, application of monadic techniques leads to a surprisingly elegant embedding, in which hardware designs are translated into logic *almost verbatim*, preserving types and language constructs. Proof strategies are written in the PVS strategy language; these automatically verify temporal logic theorems concerning the resulting monadic expressions, by employing a combination of model checking and deductive reasoning. The subset of BSV which is embedded includes module definition and instantiation, methods, implicit conditions, scheduling attributes, and rule composition using methods from instantiated modules.

The aforementioned subset of BSV is also embedded in the specification language of the SAL model checker, and a verification strategy is presented which combines the specialised model checking capabilities of SAL with the diverse proof strategies of PVS.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://www.campus.manchester.ac.uk/medialibrary/ policies/intellectual-property.pdf), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/ regulations) and in The University's policy on presentation of Theses.

## Acknowledgments

Thanks to David Lester for many engaging discussions, and for encouraging a spirit of independence in research. Thanks also to Steve Furber, the SpiNNaker team and the wider Advanced Processor Technologies group for a great deal of good advice. Finally, a special mention to Andrew Bardsley, for sharing his extensive knowledge of programming languages and enthusiasm for Haskell.

To my family, for love and encouragement.

## **Chapter 1**

## Introduction

Without major breakthroughs, design verification will be a non-scalable, show-stopping barrier to further progress in the semiconductor industry. There is hope for breakthroughs to emerge via a shift from ad hoc verification methods to more structured, formal processes.

2009 International Technology Roadmap for Semiconductors

The significant problems we face today cannot be solved at the same level of thinking we were at when we created them.

Albert Einstein

### **1.1 An Explosion of Complexity**

In 1965 – when Integrated Circuit (IC) design was in its infancy and chips contained tens of transistors – Gordon Moore made a bold prediction: the number of transistors that could be fabricated on a chip would grow exponentially, doubling every year for at least the next decade [Moo65]. At the time he was criticised for "unrealistic optimism", but his prediction of exponential growth (with an adjusted time period of  $1\frac{1}{2} - 2$  years) held true for long enough to be termed "Moore's law" in the early 1970s and continues to hold today, an astonishing 45 years later. Those 45 years have been the dawn of the information age: commoditised computing; unprecedented connectivity; surging advances across the sciences ... and all of this fuelled by increasingly powerful – and complex – silicon chips. When Moore made his prediction, chips contained tens of transistors: today, industry giants such as Intel and AMD churn out processors containing several billion, and thousands of smaller vendors produce applicationspecific ICs (ASICs) with transistor counts ranging into the hundreds of millions.

Fabrication technologies now permit such high transistor counts that design innovation is limited by the ability to exploit such potential complexity by arranging the available transistors into correctly functioning designs. As fabrication technologies evolved over the past half century, tools and techniques for designing integrated circuits evolved simultaneously, in order to deliver increased design efficiency, and hence enable the realisation of evermore complex designs: for several decades, however, the rate of increase in design productivity has been consistently outstripped by the rate of increase in transistor densities<sup>1</sup>, causing escalating design team head-counts and spiralling design costs, which are coming to dominate the economics of IC production. Design non-recurring engineering (NRE) costs now frequently exceed manufacturing NRE costs by an order of magnitude [ITR09] and will likely increase further, as long as Moore's law continues to hold and consumers maintain their appetite for evermore complex devices. In particular, design verification techniques are coming under increasing strain; many ASIC teams now employ two or more verification engineers for each designer [ITR09] and there is a real possibility of a "verification bottleneck" in the near future, where the trend of burgeoning device complexity is halted, not by the limits of fabrication technologies, but by the cost of design verification.

IC manufacturers now find themselves in a competitive environment which is increasingly defined by the metric of design efficiency and, in response, are investing heavily in research and development (R&D) for new design and verification technologies. One champion of this R&D effort has been *formal verification* – a mathematical paradigm which is fundamentally more rigorous than traditional testbased approaches. Formal verification has developed over several decades as a sideline in the hardware industry: however, spurred by the ongoing complexity crisis, it now looks set to join the centre-stage. The 2009 International Technology Roadmap for Semiconductors (ITRS '09) [ITR09] – a definitive industry-wide consensus on R&D priorities – found that 9.4% of design errors in the companies it surveyed were identified with formal or semi-formal<sup>2</sup> techniques, and stipulated that this should increase to 45% over the following 15 years. For this to happen, however, a great

<sup>&</sup>lt;sup>1</sup>Design productivity (measured as the number of logic gates per design-year) increased at an average rate of 40% per year between 1990 and 2009, but over the same period the number of transistors that could be fabricated onto a chip increased at 40% – 60% per year, in accordance with Moore's Law (historically doubling every  $1\frac{1}{2}$  – 2 years) [ITR09].

<sup>&</sup>lt;sup>2</sup>Combining formal techniques with traditional *ad hoc* approaches [BAWR07].

deal of innovation will be required in the way that formal methods are applied in the hardware design flow. This dissertation investigates one such innovation: the application of formal reasoning to hardware designs expressed in *semantically elegant* languages...

### **Thesis Contributions**

Hardware is typically designed using *ad hoc* languages such as VHDL [IEE94], Verilog [TM96] and SystemC [Gro02], which have evolved organically over the lifetime of the industry and are therefore well integrated with current design flows, but unfortunately sit poorly with proof-based verification techniques owing to their convoluted, and often ambiguous, semantics [BGG<sup>+</sup>92, Gor95, Klo95, MRH<sup>+</sup>01]. In contrast, an alternative class of semantically elegant languages allows efficient design, whilst also having been developed with formal verification in mind. This dissertation demonstrates the application of proof techniques to hardware designs expressed in two such languages:

- Concurrent Haskell a language for software design which combines functional programming with channel-based concurrency [PJGF96]. It will be used to develop a behavioural specification of a network-on-chip (NoC), for subsequent verification with hand-proof.

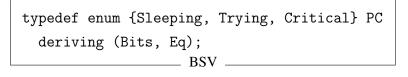

- Bluespec SystemVerilog (BSV) a language for hardware design and synthesis which combines a guarded-action model of concurrency with language constructs from the functional paradigm [Nik04]. A subset of BSV will be embedded in the specification logics of the PVS theorem prover and the SAL model checker, providing access to a wide variety of automated proof techniques.

For both languages, we will find that the combination of functional programming with a clean model of concurrency yields hardware descriptions which are highly amenable to the application of proof. This result is particularly encouraging for BSV, which is a relatively new language that has already been shown to reduce design time when compared to hand-written VHDL or Verilog, whilst producing comparable hardware for many applications [GW08, Nik04, WNRD04] – this dissertation will provide evidence that it is also more amenable to automated reasoning. Furthermore, this insight is timely, because BSV presently has *no* tool support for automated reasoning, placing it very much behind the curve when compared to VHDL and Verilog.

The technical contributions of this thesis are:

- A novel application of lightweight formal methods to the SpiNNaker networkon-chip architecture, which involves behavioural specification in Concurrent Haskell, together with verification by hand-proof.

- A shallow embedding of a subset of Bluespec SystemVerilog in the higher order logic of the PVS theorem prover. A novel application of monadic techniques [Mog89, Wad92b] allows a surprisingly clean embedding, in which BSV designs are translated into logic *almost verbatim*, preserving types and language constructs. The subset which is embedded includes module definition and instantiation, methods, implicit conditions, scheduling attributes, and rule composition using methods from instantiated modules.

- Proof strategies, written in the PVS strategy language, which automatically verify temporal logic theorems concerning the aforementioned monadic expressions, by employing a combination of model checking and deductive reasoning.

- An embedding of the same subset of BSV in the SAL language, which provides access to the wide array of model checking tools in the SAL suite.

Of particular note is the monadic embedding of BSV in the PVS logic. Whilst monads have been used before to address the notoriously messy issue of verifying state-based computation with theorem proving, their application to BSV yields surprisingly clean results. BSV has its roots in a minimalist guarded action language (of the kind used to specify state machines for model checking) and was expanded into a fully-featured hardware language with strong influences from functional programming. As a result, we will see that an environment such as PVS – which combines integrated model checking and theorem proving with a higher order functional specification language – allows the almost verbatim translation of BSV source code to a monadic form which can be directly verified using a combination of model checking and automated deduction.

### **1.2 Modern Hardware Design**

When Gordon Moore made his prediction in the 1960s, hardware designers sat with 'coloured rectangles' and drew transistors by hand on graphical representations of circuits. Through the 1970s and 1980s, transistor counts increased and designers

progressed to *gate level* languages for a large amount of design. These languages abstracted away from individual transistors to the level of logic gates. They hid the detail of transistor-level structure, which made designs more concise and understandable; this increased design productivity by reducing design time, reducing the incidence of errors and making errors easier to spot when they did occur. The new languages were supported by *place and route* tools which automatically compiled gate-level designs down to the transistor level, with a small performance penalty compared to hand-crafted transistor level circuits.

By the mid 1980s, fabrication technologies allowed hundreds of thousands of transistors per chip, and designers added another level of abstraction. Register Transfer Level (RTL) languages provided types such as bounded integers, as well as programming language constructs such as if-then-else statements, case expressions and arithmetic operators. Designs expressed in these languages could be automatically compiled down to gate level using synthesis software. RTL languages gained widespread popularity because they employed simple abstractions to hide the detail of standard circuit components, whilst allowing automatic synthesis of reasonably efficient gate level circuits. Two RTL languages gained widespread acceptance; VHDL [IEE94] and Verilog [TM96].

Alongside the development of RTL languages, tools emerged that raised the level of abstraction further still by synthesizing from high-level imperative languages such as C, C++ and SystemC [Gro02], which allow the functionality of a design to be specified without fully defining the architecture that will produce this functionality. These *high-level synthesis* approaches have seen a strong uptake for some applications, but have not yet seen widespread adoption as a replacement for RTL languages; at present, they do not produce hardware that is consistently competitive with hand-coded RTL (in terms of speed, area and power) for most designs [ITR09, WNRD04].

High-level languages are, however, seeing extensive uptake for another use; to specify design functionality, and produce executable prototypes at an early stage in the design flow. The high level of abstraction provided by languages such as C is referred to as the *system level* or *electronic system level* (ESL) [KMN<sup>+</sup>00]. System level models can be used to experiment with design concepts, and to act as *gold standards* for testing against the RTL designs that are synthesized to hardware.

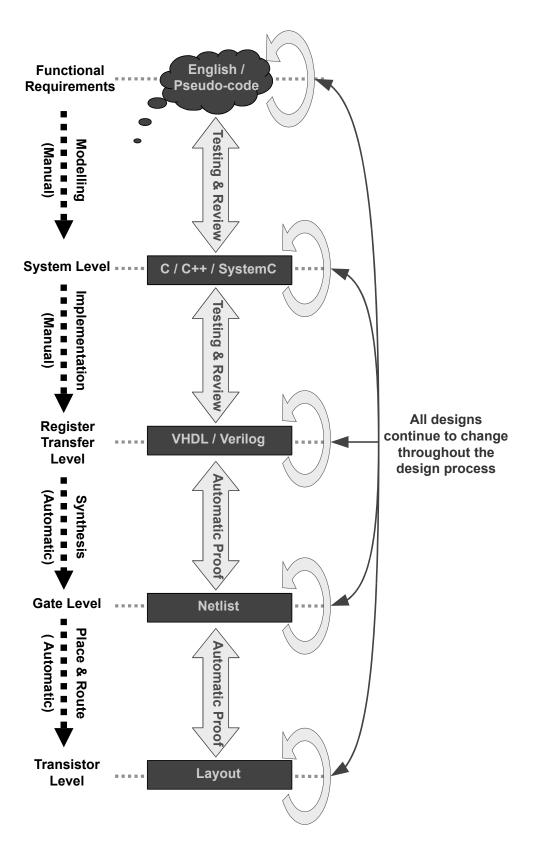

Figure 1.1: A Typical IC Design Flow, Including Functional Verification

#### **1.2.1** The IC Design Flow

Figure 1.1 shows a modern IC design flow, by which simple initial concepts can be transformed into sophisticated IC designs with hundreds of millions of transistors. The design flow begins with a distillation of the design concept into a set of concrete functional requirements, which are typically expressed with a mixture of natural language prose, pseudo-code, tables, diagrams and so-on. This specification may be incomplete and ambiguous, and tends to mature as time passes. Next, an executable system level model is produced to animate the functional requirements at a high level of abstraction; this allows experimentation with the design concept, or rapid prototyping, which can stimulate modifications to the functional requirements. After this, a synthesizable RTL design is produced which implements the system level model in a way that attempts to meet any timing and power constraints. The development of RTL serves as a further exploration of the design concept, which can stimulate changes to the functional requirements and the system level model. From here, a gate level netlist is synthesised from the RTL, and a transistor level layout is then automatically compiled from the gate level design using a *place and route* tool. Finally, in a process called *spinout*, the layout is converted to a mask, which is used in a lithography process to fabricate the actual silicon chip. In order to ensure that the final chip satisfies its timing, power and area constraints, the RTL, netlist and layout can be repeatedly modified before spinout.

### **1.2.2 Functional Verification**

Functional verification is the process of assuring that a transistor level layout is functionally equivalent to its specification of requirements. At present, this is primarily achieved using:

- 1. Testing and design review at the system and register transfer levels.

- 2. Formal equivalence checking at the gate and transistor levels.

Testing and design review are fundamentally limited because they cannot verify designs *rigorously* and *exhaustively*, meaning that bugs can – and do – pass through the verification process undetected:

• Testing involves simulating designs in software. Because of the complexity of modern IC designs, they are typically simulated for only a small fraction of the

possible inputs and system states. Furthermore, as design complexity increases, *test coverage* – the fraction inputs and system states that can feasibly be checked – generally decreases.

• In the design review process, designs are manually compared to specifications written in natural language prose, pseudo-code, tables, diagrams and so-on. However, natural language specifications are often incomplete and ambiguous, and human reasoning can make oversights and draw false conclusions.

Formal equivalence checking does not have these problems; it uses automated proof to establish functional equivalence rigorously for *all* possible inputs. Clearly, this would be preferable at the system and register transfer levels, but the application of automated proof at these levels poses significant challenges (which motivate the present work). Automated proof is currently a secondary activity at the system and register transfer levels; it is applied in restricted areas to provide enhanced error detection, but falls short of a complete solution for functional verification.

As long as we lack the means to achieve rigorous functional verification at the system and register transfer levels, bugs will pass undetected into silicon chips. In fact, they are surprisingly common in modern ICs. For example, the data-sheet for Intel's Core i7 processor lists 136 known errors [Int10]. To illustrate, the first three are:

- 1. MCi\_Status overflow bit may be incorrectly set on a single instance of a DTLB error;

- 2. Debug exception flags DR6.B0-B3 may be incorrect for disabled breakpoints;

- 3. MONITOR or CLFLUSH on the local XAPIC's address space results in hang.

Bugs are currently a fact of life in chip production. Most of the time they are relatively benign, and can be 'worked around' by programmers, but they can also cause serious problems. In 1994 a bug was discovered in the floating point unit of Intel's Pentium processor, which caused Intel to replace the faulty chips on demand, with an eventual cost of almost \$500 million, as well as untold reputational damage [CB00]. Bugs can also be costly when they are discovered before the product is released. Chips often have a marketing lifespan in the order of months before they are superseded by the next generation of ICs fielded by the competition, and bugs found late in the production cycle can delay fabrication, reducing the lifespan of the product or even

rendering it obsolete before it ever enters the marketplace. Worse yet, bugs have the potential to cause tragic consequences; chips are now used in safety critical systems such as nuclear reactors, passenger aircraft and car engines, and a failure in one of these could cause loss of life.

### **1.3 Formal Methods**

In the battle against exploding design complexity, the hardware industry is increasingly supplementing established *ad hoc* design practices with more rigorous mathematical techniques. As we have seen, functional verification at the system level and register transfer level is currently a flawed process; testing and code review allow design errors to pass through the design process unchecked. Formal methods are less affected by the inherent flaws that blight testing and code review, but there are significant unsolved technical challenges which prevent them from being used pervasively at these levels, as they are at the gate and transistor levels. Instead they are applied piecemeal, to raise the quality of functional verification incrementally. There is a focused effort across industry and academia to overcome these problems and thus increase the impact of formal methods in the earlier stages of the design flow.

The term *formal methods* covers a broad range of approaches which apply mathematical techniques to the design of computational systems. These include verification by mathematical proof, design with semantically elegant languages and a host of so-called *semi-formal* approaches that use formal techniques to enhance existing informal design and verification practices. Our discussion of formal methods begins with the notion of verification by mathematical proof, which is a primary motivation of the field and also leads to an intuitive understanding of other concepts, including semantically elegant languages.

#### **1.3.1** Verification by Mathematical Proof

Proof can be applied to programs written in any language for which a semantics can be precisely defined; for such languages, the behaviour of programs can be inferred before they are actually run, using mathematical reasoning. Intended properties of a given program can be expressed as theorems, and proof techniques can be used to establish their validity under all conceivable external environments. This presents a new approach to the functional verification of IC designs, which is potentially more rigorous than design review and more exhaustive than testing. Proof can offer a more systematic inspection of design functionality than *ad hoc* design review and, in contrast to testing, can verify properties for all possible inputs to a system.

The format of theorems and proofs can vary. Theorems can be written in natural language and proven with written prose, in the style which is common in text books and academic papers. This kind of specification and proof can be viewed as a refinement of the informal design review process. Instead of specifying a system with natural language prose or pseudo code, the system's requirements are partitioned into a set of concise natural language theorems which can be proven with structured, rigorous reasoning, in place of the unstructured *ad hoc* reasoning which is used in design reviews. However, theorems and proofs which are formulated in natural language inherit the intrinsic problems that were associated with design review in §1.2.2; natural language is ambiguous, allowing imprecision and misinterpretation, and proofs written in prose typically appeal to human reason, which can draw false conclusions and make oversights. Moreover, proofs require human effort to construct, and owing to the complex nature of IC designs, this can become extremely time consuming.

Alternatively, natural language can be abandoned in favour of a *formal logic*, which is a mathematical system for performing precise and unambiguous reasoning. It will typically include:

- 1. A *specification language* for describing systems and asserting theorems about them: for example, *higher-order logic* provides a simple functional programming language, together with universal and existential quantifiers (∀ and ∃) which allow theorems to be expressed about the properties of functions and variables.

- 2. A set of *inference rules* which are used to prove theorems written in the specification language.

Formal logic reduces mathematical proof to a process of *calculation*. Whereas natural language proofs appeal to human reason, their formal counterparts are composed purely from the repetitive application of inference rules, which for many logics are proven to be *sound*, meaning that they cannot possibly be used to establish the truth of a theorem which is actually false or *vice versa*.

Formal logic has a long history in the literature. For example, the epic *Principia Mathematica* of Whitehead and Russell (completed in 1913) was an attempt to

derive all mathematical truths within formal logic<sup>3</sup>. However, formal proof was impractical for most purposes until the advent of computers, which allowed proofs to be *mechanised*, giving rise to the field of *automated reasoning*<sup>4</sup>.

#### **1.3.2** Clean Abstractions and Semantic Elegance

In principle, proof can be applied to programs written in any language, as long as the semantics of the language can be formally specified. However, languages vary in terms of the ease with which formal semantics can be expressed, and the tractability of proofs which use these semantics. Unfortunately, as we shall see in later chapters, *ad hoc* languages such as VHDL, Verilog and SystemC perform poorly in both respects: they have convoluted semantics [Klo95, Gor95, BGG<sup>+</sup>92, MRH<sup>+</sup>01] which often necessitate contrived proof techniques. Spurred on by these challenges, the formal methods community has developed an innovative class of languages which are comparable to the popular *ad hoc* languages in terms of their utility for system design, but also have elegant semantics for the purpose of simplifying proof. The subtle attribute of semantic elegance has been achieved with a technique which is familiar from our discussion of the evolution of hardware languages – abstraction.

Abstraction is the art of describing systems in a way which hides unwanted detail whilst retaining the properties of interest. Hardware description languages use abstraction to express hardware designs without describing the nitty-gritty details of the gate and transistor levels. In a similar way, semantically elegant languages use abstraction to express computational systems without describing implementation details such as pointers, garbage collection and memory resources. This simplifies the semantics without reducing the class of computations that can be described. In the extreme, there are *calculi* such as the  $\lambda$ -calculus<sup>5</sup> [Chu40], a minuscule language which has just two primitive computational mechanisms (function parameterisation and function application) but is Turing complete. The semantics of the  $\lambda$ -calculus can be described with three simple rules; with these rules, one can evaluate any program written in the language. In order to prove a property about the evaluation of a  $\lambda$ -calculus program, one must only consider these three evaluation rules; in contrast, in order to prove properties of a C program, one would need to consider the behaviour of

<sup>&</sup>lt;sup>3</sup>In the event, it actually covered a fragment of set theory, cardinal numbers, ordinal numbers and the reals.

<sup>&</sup>lt;sup>4</sup>Excellent introductions to automated reasoning are provided in [Har09] (for automated deduction) and [CGP00] (for model checking).

<sup>&</sup>lt;sup>5</sup>For a comprehensive introduction, see [Pie02].

pointers, garbage collection and so-on.

Alongside the minimalist calculi, fully-featured programming languages have emerged which adhere to the spirit of abstraction and semantic elegance, but are usable for everyday programming tasks. For example, functional programming [Bir98, OGS08, Pie02] is a paradigm that closely resembles the  $\lambda$ -calculus. It is arguably the most well known programming formalism and is used extensively throughout this thesis.

#### Are Semantically Elegant Languages Usable?

The promise of semantically elegant languages would by diminished if they were not competitive with *ad hoc* languages in terms of utility for everyday design; fortunately, there is a growing body of evidence to show that they are. Functional languages, for example, are well-suited to formal proof, but are gaining popularity in the programming community for other reasons:

- Their abstract nature makes functional programs *concise*, which increases design efficiency by making programs less time-consuming to construct;

- Powerful type systems (which are another form of abstraction) make programs inherently less error prone compared to the popular imperative languages such as C [FSNB09, OGS08]. It is a truism that functional programs "tend to just work" once they compile.

In the hardware domain too, semantically elegant languages are having an impact on design productivity. For example, the language Bluespec SystemVerilog [Nik04], which is considered at length in this dissertation, uses novel abstractions from computer science to describe hardware in a way that is substantially more concise than RTL, thus reducing line count and design time, whilst producing hardware that is competitive with hand-written RTL in terms of time and area for many applications [WNRD04, Nik04].

### 1.4 Synopsis

This thesis investigates the application of proof-based verification to hardware designs expressed in two semantically elegant languages, namely Concurrent Haskell and Bluespec SystemVerilog.

#### 1.4. Synopsis

Chapter 2 employs Concurrent Haskell for the task of specifying and formally verifying a novel network-on-chip architecture. A behavioural specification is constructed for the SpiNNaker NoC, which can be executed and verified by hand-proof. A novel routing mechanism is verified by mathematical induction.

Chapter 3 reviews Bluespec SystemVerilog, and introduces BSV implementations of Peterson's algorithm and the control circuitry of a round-robin arbiter, which serve as running examples for the application of automated reasoning in the chapters that follow.

Chapter 4 introduces the concept of automated reasoning and surveys the literature for automated reasoning strategies of potential application to Bluespec SystemVerilog. It is found that several automated theorem provers support experimentation with a broad range of proof strategies, including model checking, automatic abstraction and the full spectrum of deductive reasoning. These strategies can be applied to BSV designs, if BSV can be embedded in the theorem prover's logic.

Chapter 5 embeds a non-trivial subset of BSV in the higher order logic of the PVS theorem prover. BSV is found to be naturally suited to expression in formal logic. Its use of guarded actions as an underlying model of concurrency makes it similar to a host of languages used for model checking, and its functionally-inspired language constructs can be translated into logic almost verbatim, with a novel application of monadic techniques. To demonstrate the proposed embedding strategy, the two BSV examples from chapter 3 are translated by hand into the PVS logic.

Chapter 6 applies automated reasoning to PVS specifications produced with the monadic embedding strategy of chapter 5. It is found that temporal logic theorems concerning these specifications can be verified with a combination of model checking and deductive reasoning. Proof strategies are written in the PVS strategy language to automate this process.

Chapter 7 investigates the verification of BSV designs with a stand-alone model checker. The monadic embedding strategy is used to translate BSV designs into the specification language of the SAL model checker. It is found that SAL permits monadic specifications, but fails to model check them efficiently, owing of their heavy use of higher order functions. However, an equivalent but more verbose *primitive* embedding strategy is found to be compatible with the SAL model checker, and a verification strategy is presented which combines SAL model checking over primitive specifications with deductive reasoning in PVS to establish the equivalence of primitive and monadic BSV embeddings.

Chapter 8 presents a review of the literature which is related to the embeddings of Bluespec SystemVerilog presented in earlier chapters. It is found that BSV presents unique challenges in the application of automated reasoning, being more complex than other guarded action languages, and exceptional amongst hardware languages in its choice of guarded actions as the underlying model of concurrency.

Chapter 9 draws conclusions, and presents topics for further work. For BSV in particular, a number of natural extensions to the present work are discussed, including the application of automatic abstraction and compositional reasoning to monadic PVS specifications. Furthermore, the overall direction of the present work is placed into the context of an expansive – and mostly unexplored – research space concerning automated reasoning for BSV.

### **1.5 Publications and Source Code**

The research contributions of this dissertation have also been published in the following papers:

- 1. DOMINIC RICHARDS AND DAVID LESTER. A monadic approach to automated reasoning for Bluespec SystemVerilog. In *Innovations in Systems and Software Engineering: a NASA Journal*, 7(2):85-95, 2011.

- 2. DOMINIC RICHARDS AND DAVID LESTER. A prototype embedding of Bluespec SystemVerilog in the PVS theorem prover. In *Proceedings of the 2<sup>nd</sup>* NASA Formal Methods Symposium (NFM), 2010.

- 3. DOMINIC RICHARDS AND DAVID LESTER. A prototype embedding of Bluespec SystemVerilog in the SAL model checker. In *Proceedings of the* 8<sup>th</sup> *International Workshop on Designing Correct Circuits (DCC)*, 2010.

- 4. DOMINIC RICHARDS AND DAVID LESTER. Concurrent functions: a system for the verification of networks-on-chip. In *Proceedings of the 3<sup>rd</sup> International Workshop on Hardware Design and Functional Languages (HFL)*, 2009.

- 5. DAVID LESTER AND DOMINIC RICHARDS. Specification of a network-on-chip. In *Proceedings of the 20<sup>th</sup> UK Asynchronous Forum (UK-ASYNC)*, 2008.

Accompanying source code can be found online [RL11].

## **Chapter 2**

## Verifying a Network-on-Chip

A network-on-chip architecture is specified and verified with a lightweight application of formal methods. The NoC features in the SpiNNaker many-core processor, which is being developed for efficient simulation of large scale neural networks. It supports a complex and unbounded toroidal network, which disregards established design conventions intended to ensure freedom from deadlock and livelock. A behavioural specification is produced in Concurrent Haskell, and a proof is presented which verifies a novel routing mechanism with mathematical induction.

### 2.1 Networks-on-Chip

As silicon feature sizes continue to shrink, it is becoming possible to fit entire systems onto a single chip, giving rise to the System-on-Chip (SoC) design paradigm. Such systems are typically composed of individually-designed intellectual property (IP) blocks such as processor cores, memory elements, graphics processing units, hardware accelerators and field-programmable gate arrays. Systems-on-Chip have complex communications requirements which can be provided by networks-on-chip [KJS<sup>+</sup>02] – scaled-down computer networks which allow IP blocks to communicate by routing data through a system of data links and connecting nodes. NoCs can transmit data either by creating direct communication links between IP blocks (an approach known as *circuit switching*) or by routing data packets (referred to as *packet switching*). It is with the latter that we are concerned.

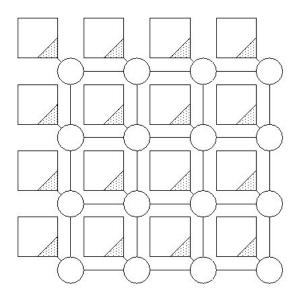

Circuit switched NoCs can have various topologies depending on the specific structure and purpose of the SoC; a popular topology, for example, is the mesh structure shown in figure 2.1. A node in a packet-switched NoC typically consists of:

Figure 2.1: A Mesh NoC Topology

- An arbiter which merges the streams of packets received from a node's incoming data links into a single stream.

- A router which reads packets from the arbiter's output stream and forwards them along one or more of the node's outgoing data links.

NoC architectures can be highly complex and error prone, making them an attractive target for the application of formal methods. They have large state spaces and are often nondeterministic, which limits the effectiveness of traditional test-based verification techniques. Furthermore, being highly concurrent they are also prone to deadlock – a phenomenon that can stay hidden until late stage simulation or even post-fabrication testing.

### 2.2 SpiNNaker: A Spiking Neural Network Architecture

The SpiNNaker chip [FTB06b, FTB06a] is a novel many-core processor being developed at the University of Manchester in collaboration with the University of Southampton and ARM Ltd. It will support efficient real-time simulation of large-scale spiking neural networks. At the time of writing, the first batch of SpiNNaker chips is being fabricated.

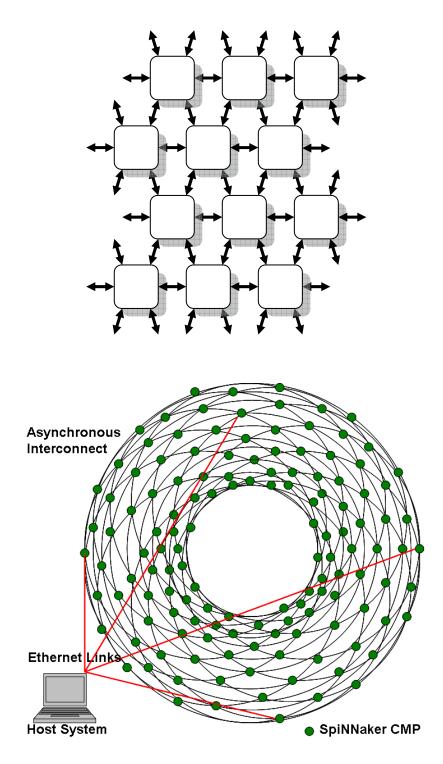

Figure 2.2: SpiNNaker system architecture. Top: each SpiNNaker chip is connected to its six nearest neighbours with bi-directional links. Bottom: the left and right sides of the mesh are connected, as are the top and bottom edges, to form a toroid. From [FT08].

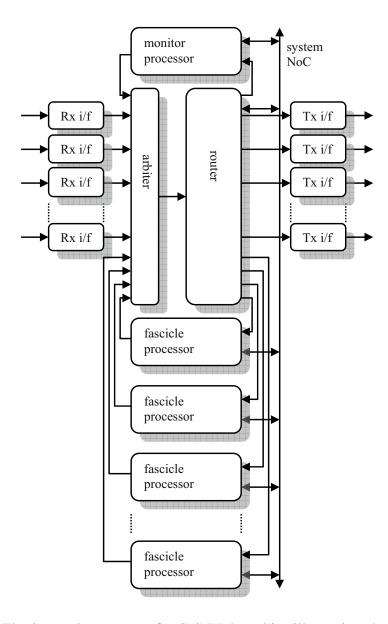

The SpiNNaker chip (along with associated SDRAM chip) forms a node in a scalable parallel system, as shown in figure 2.2. On-chip processing power is provided by 18 ARM968 cores; together, these provide the integer processing power of a typical PC, but at much lower electrical power and in a compact physical form. The ARM cores are connected with a packet-switched network-on-chip, which is also connected to the NoCs of six neighbouring chips through inter-chip links, as shown in figure 2.3. Of the 18 ARM cores, 17 are designated to be *fascicle* processors which each model around 1,000 neurons in real time. The remaining core is designated as a *monitor* processor, which carries out operating system functions and provides the user with information concerning on-chip activity. A system-wide packet-switched communications network is formed by the concurrent operation of the individual networks-on-chip.

SpiNNaker systems will support neural simulations, in which neurons communicate by firing 'spikes' which are transmitted to other neurons. This is supported in the physical system by allowing neurons to launch source addressed packets into the system-wide communications fabric. When this happens, the NoCs distribute the packets across the system with *multicast, source addressed* routing. Each NoC has a content addressed memory unit (CAM), for which the packet's source address is used as a lookup key. The CAM of each NoC maintains a list of NoC outputs to which the packet should be forwarded. In this way, packets representing 'neural spikes' can be propagated throughout the system.

SpiNNaker chips adhere to the *Globally Asynchronous*, *Locally Synchronous* (GALS) design paradigm, in which each ARM core is individually clocked and connected to the rest of the chip by an asynchronous NoC [BF02]. Each chip, in turn, is connected to its six nearest neighbours by asynchronous inter-chip links.

Work is currently underway to produce systems with 500 and 50,000 nodes; the latter will provide approximately 200 teraIPS, which could simulate approximately 10<sup>9</sup> neurons, or 10% of the human cerebral cortex, using the initial target neural model.

### 2.2.1 Fault Tolerance and Emergency Routing

Owing to the vast size of planned SpiNNaker systems, component failure is a significant issue. Consequently, SpiNNaker incorporates two novel fault-tolerance mechanisms:

1. If a processor fails, its workload is migrated to other processors in real-time.

Figure 2.3: The internal structure of a SpiNNaker chip, illustrating the network-onchip which is used to transmit 'spike' packets across the broader SpiNNaker system. Each fascicle processor models a cluster of neurons. Packets from neighbouring SpiNNaker chips arrive through the receiver interfaces (Rx i/f) and are merged with packets issued by the fascicle processors into a sequential stream by the arbiter. Each packet is then routed to one or more destinations, which may include neighbouring SpiNNaker chips (via the transmit interfaces Tx i/f) and/or local fascicle processors. The monitor processor carries out operating system functions and provides visibility to the user of on-chip activity. Processors are also connected to a separate 'system' NoC, which provides access to local memory, but is not discussed further in this thesis. From [FT08].

Figure 2.4: Emergency Routing.

2. If an inter-chip link fails (whether permanent or transient) traffic is handled in the first instance at the hardware level, by redirecting packets automatically via adjacent links, before invoking performance management software to carry out a more permanent solution.

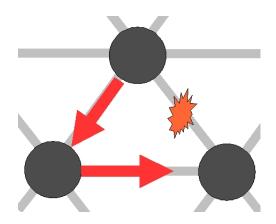

The automatic re-directing of traffic around unresponsive inter-chip links is achieved by the concurrent operation of the surrounding chips' NoCs, as shown in figure 2.4. If an inter-chip link fails, packets are re-routed via a neighbouring chip. This mechanism is called emergency routing and proceeds in the following way.

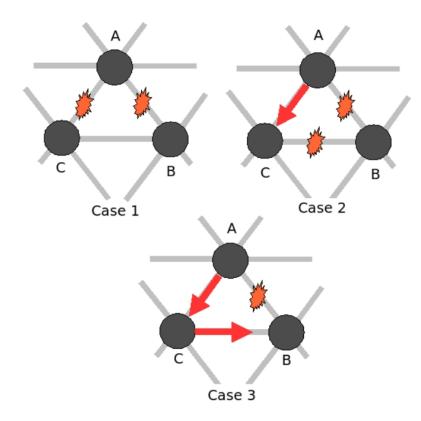

Observe the fragment of a SpiNNaker system shown in figure 2.5. Imagine that chip A wants to send a packet down link AB to chip B, but link AB is broken. There are three possible cases:

- 1. The NoC router of chip A attaches a label "E1" (emergency routing, stage 1) to the packet and attempts to send it along the clockwise neighbour of the unresponsive link, which in this case is link AC. If link AC is broken, the packet is dropped; this unusual choice of behaviour is acceptable because of the fault tolerant nature of neural systems.

- 2. If link AC is functioning and chip C receives a packet with the label "E1" attached, it automatically changes the label to "E2" and attempts to send it along the clockwise neighbour of the link through which it entered the chip, which in this case is link CB. If link CB is broken, the packet is dropped.

- 3. If the packet reaches chip B, its NoC router removes the "E2" label and treats the packet as normal.

Figure 2.5: Emergency Routing Scenarios

If a packet is to be passed down an inter-chip link with the E1 label, it is possible that the same packet should be passed down this link anyway, with the N (normal) label. If this is the case, the router sends a single packet with type N\_E1. When a packet of this type is received, it is split into an N packet and an E1 packet, which are then processed independently.

SpiNNaker NoCs also implement a 'default' routing mechanism, which allows packets to be routed through chips without entries being required in the chips' look-up tables. If a router receives a packet from an inter-chip link and the packet's sourceaddress is not in the router's look-up table, it forwards the packet to the diametrically opposite inter-chip link. Because of this, look-up table entries are required only when packets either originate on the chip, are destined for on-chip processors, or change their 'direction of travel' at the chip.

| Р | ::= | e                                    | Haskell expression of type <i>IO</i> ()         |

|---|-----|--------------------------------------|-------------------------------------------------|

|   |     | $(P_1 \mid P_2)$                     | parallel composition                            |

|   |     | $\langle \rangle_{\alpha}$           | empty memory element named $\alpha$             |

|   |     | $\langle x \rangle_{\alpha}$         | memory element named $\alpha$ holding value $x$ |

|   |     | $(\mathbf{v} \boldsymbol{\alpha}) P$ | restriction of the name ' $\alpha$ ' to P       |

|   |     | Ø                                    | the null process                                |

Figure 2.6: A Grammar of Process Types for Concurrent Haskell

## 2.3 Concurrent Haskell

Concurrent Haskell [PJGF96] extends the lazy functional programming language Haskell with channel-based concurrency. Its concurrency primitives are accompanied by an elegant operational semantics, meaning that programs can serve as a basis for formal reasoning. This section introduces a subset of Concurrent Haskell. A comprehensive introduction to Haskell can be found in [Bir98].

Peyton-Jones *et al.* [PJGF96] present an operational semantics for Concurrent Haskell, which is based on the "chemical abstract machine" presentation of  $\pi$ -calculus [Mil93, Mil99]. The grammar of process types is given in figure 2.6. It tells us that the following are valid Concurrent Haskell processes:

- 1. e, whenever e is a Haskell statement of type IO().

- 2.  $P_1 \mid P_2$  two processes executing concurrently.

- 3.  $\langle \rangle_{\alpha}$  an empty memory location with pointer  $\alpha$ . (Notice that memory locations are defined as concurrent processes.)

- 4.  $\langle x \rangle_{\alpha}$  a full memory location.

- 5.  $(v \alpha) P$ , where  $\alpha$  is a pointer for a memory location. This restricts the scope of  $\alpha$  to *P*. The symbol *v* is shorthand for 'new';  $\alpha$  is a *new* pointer for use in *P*.

Concurrent Haskell is implemented as a standard Haskell library which provides functions and types for creating concurrent processes and facilitating communication between them. We now discuss the following:

data MVar a forkIO :::  $IO() \rightarrow IO$  ThreadId newEmptyMVar :: IO (MVar a)putMVar ::  $MVar \ a \rightarrow a \rightarrow IO()$ takeMVar ::  $MVar \ a \rightarrow IO \ a$ – Haskell –

A value of type *MVar a* represents a pointer to a memory location that can hold one element of type  $\alpha$ . This memory location can be used as a channel for communication between Concurrent Haskell processes. The semantics of the above functions are formally defined with a reaction relation, which is shown in figure 2.7. The notation  $\mathcal{M}[f]$  can be read as "a monadic expression where the next function to be evaluated is f". For our purposes, this can be one of three things:

- 1. The monadic function *f* on its own; for example, *forkIO a* for some Haskell function *a*.

- 2. A **do** statement of the form:

do f < more statements >

3. A **do** statement of the form:

With this in mind, the above Concurrent Haskell functions are defined by figure 2.7 and their type declarations to have the following behaviour:

• The function *forkIO* takes a Haskell expression of type *IO*(), generates a new thread for this expression to execute in, and returns a thread ID. Its behaviour is described formally by the rule (*Fork*), which can be applied to any process of the form:

| (Fork) | $\mathcal{M}[forkIO a]$                                             | $\rightarrow$ | $a \mid \mathscr{M}[return id]$                                                |

|--------|---------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------|

|        |                                                                     |               | where <i>id</i> :: <i>ThreadId</i>                                             |

| (New)  | $\mathcal{M}[newEmptyMVar]$                                         | $\rightarrow$ | $(\mathbf{v}\alpha)(\langle\rangle_{\alpha} \mathscr{M}[return\alpha])$        |

|        |                                                                     |               | where $\alpha \notin free\_names(\mathcal{M})$                                 |

| (Put)  | $\langle \rangle_{\alpha} \mid \mathscr{M}[putMVar \; \alpha \; x]$ | $\rightarrow$ | $\langle \mathbf{x} \rangle_{\boldsymbol{\alpha}} \mid \mathscr{M}[return ()]$ |

| (Take) | $\langle x \rangle_{\alpha} \mid \mathscr{M}[takeMVar \alpha]$      | $\rightarrow$ | $\langle \rangle_{\alpha} \mid \mathscr{M}[return x]$                          |

| (Par)  | $P \mid Q$                                                          | $\rightarrow$ | $P' \mid Q  if \ P 	o P'$                                                      |

| (Res)  | $(\mathbf{v} \ \boldsymbol{\alpha})(P)$                             | $\rightarrow$ | $(\mathbf{v} \ \boldsymbol{\alpha})(P')  if \ P \to P'$                        |

|        |                                                                     |               |                                                                                |

Figure 2.7: A Reaction Relation for Concurrent Haskell

and it would transform this process into a new process of the form:

$$a \mid \mathcal{M}[return id]$$

Here, a new process is created with the function 'a' being evaluated inside it.

- *newEmptyMVar* creates a new empty memory location and returns a pointer to it, wrapped in the IO Monad: this is specified by the rule (*New*).

- *putMVar* takes a pointer to a memory location and a value. If the memory location is empty, the rule (*Put*) dictates that *putMVar* will place the value into it. Note that there is no rule for the process:

$$\langle y \rangle_{\alpha} \mid \mathscr{M}[putMVar \; \alpha \; x]$$

*putMVar* cannot write to a memory element which is already full. Hence, if it is called to write to a full location, it waits until the location becomes empty.

• *takeMVar* takes a pointer to a memory location. If the location is full its contents are removed, as specified by the rule (*Take*), and wrapped in the IO Monad. There is no rule to read from an empty memory location, meaning that *takeMVar* will not execute until the location in question becomes full.

# 2.4 Specifying a Network-on-Chip

This section introduces a novel framework for the behavioural specification of packet-switched networks-on-chip using Concurrent Haskell. Generic abstractions are presented for key NoC components, which can be modified to capture the behaviour and topology of specific NoC architectures.

#### 2.4.1 Packets and Physical Links

Packets are represented as instances of a Haskell datatype. The actual type is left undefined here, to be implemented for specific NoC architectures. In keeping with the behavioural (un-timed) level of abstraction, physical links are represented with unbounded 'first in, first out' (FIFO) buffers, which have the type *Chan* in Concurrent Haskell [Has11].

#### 2.4.2 IP Blocks

Because we are concerned with the verification of NoCs, rather than the specific IP blocks they serve, IP blocks are specified as simple non-terminating processes which receive and generate NoC traffic:

```

\begin{array}{rcl} mkIP & :: \ Int \ \rightarrow \ Chan \ Packet \ \rightarrow \ Chan \ Packet \ \rightarrow \ IO \ ThreadId \\ mkIP \ id \ input \ output \\ & = \ forkIO \ \$ \ loop \ \$ \ do \\ & p \ \leftarrow \ readChan \ input \\ writeChan \ output \ (new\_pack \ id \ p) \\ \hline & Haskell \\ \end{array}

```

This function ("make IP") initialises an IP block with a unique ID (*id*) and two *Chans* (*input* and *output*) which serve as its interface to the NoC. The IP block exists in its own concurrent process, and continually reads packets from the NoC, creates new packets with the *new\_pack* function, and launches them into the NoC to generate more network traffic. The *new\_pack* function can be tailored to suit the individual NoC architecture.

#### 2.4.3 Arbiters

Arbiters merge the incoming packet streams of a NoC node into a single stream which is input to the node's router. This behaviour can be expressed as a collection of concurrent processes, one for each input stream, which read packets from the relevant input and write them to a common output. The following function creates an arbiter which merges packets, having first paired them with integers to indicate the input that each packet came from:

The function *mkArbiter* takes a list of *Chans* representing the NoC node's inputs and another *Chan* representing the arbiter's output. It then calls the *listener* function for each of the NoC node's inputs: this is achieved using the standard Haskell function mapM which takes a function of type  $a \rightarrow mb$  (for some monad *m*) and a list of type [a] and applies the function to every element of the list, giving a new list of type [mb], which it then converts to a value of type m[b].

Arbiters must generally satisfy a *progress* requirement – any continuously available input value will always eventually be forwarded. The semantics of Concurrent Haskell ( $\S$ 2.3) makes no guarantees about this kind of progress. However, for the purposes of formal proof, we can show that certain theorems follow from an assumption of arbiter progress. This assumption would then need to be justified for the RTL implementation of the given arbiter.

#### 2.4.4 Routers

Routers are specified as follows:

$\begin{array}{rcl} mkRouter :: (Packet \rightarrow Maybe [Int]) \\ \rightarrow & Chan (Packet, Int) \rightarrow [Chan Packet] \rightarrow IO \ ThreadId \\ mkRouter \ lookup \ input \ outputs \\ &= \ forkIO \ bloop \ do \\ & (p, id) \leftarrow \ readChan \ input \\ route \ (lookup \ p) \ outputs \ id \ p \end{array}$

This function takes the following arguments:

- 1. A lookup table which maps packets to values of type *Maybe* [*Int*] which can be either *Nothing*, representing a lookup table miss, of *Just xs*, representing a lookup table hit which provides a list of integers to indicate the NoC nodes to which the packet in question should be forwarded.

- 2. A Chan representing the router's input (which is also the arbiter's output).

- 3. A list of *Chans* representing the inputs to the NoC nodes.

The functionality of *mkRouter* is to launch a new concurrent process which continually reads packets from the arbiter's output, consults the lookup table to obtain forwarding information and calls the auxiliary function *route* to execute the actual forwarding. The function *route* is left to be implemented for specific NoC architectures.

# 2.5 Specifying the SpiNNaker NoC

The toroidal structure of the system-wide communications network contains a myriad of cyclic paths, from small circuits between neighbouring nodes to Hamiltonian cycles along which the default routing mechanism will single-handedly carry packets through every node in the system. If any one of these paths is ever used, deadlock and/or livelock can ensue. Furthermore, two other novel features of SpiNNaker complicate the task of ensuring that they are not used:

- 1. Packets are routed through the system according to the contents of NoC CAMs, which are generated by third parties.

- 2. Emergency routing spontaneously alters the courses of packets.

Externally generated CAMs will be verified with software which checks for cyclic routing paths, and each packet also carries a time stamp, allowing it to be dropped if it remains in the system for too long. The emergency routing mechanism has been verified with testing, code review and the formal approach presented here.

#### 2.5.1 Packets and Inter-Chip Links

In the SpiNNaker system, packets are routed according to the unique 'address' of the neuron which initiated them. However, we abstract away from the concept of neurons and assign unique IDs to the ARM cores; this simplifies the specification of ARM core functionality, whilst still supporting the NoC's source-addressed routing functionality. Packets carry the ID of their originating core, and also a 'packet type' for emergency routing:

$$type \ Packet = (Int, \ PacketType)$$

$$data \ PacketType = N | E1 | N_E1 | E2$$

$$Haskell$$

On-chip and inter-chip links are represented as unbounded FIFO buffers, which can be specified as *Working* or *Broken*:

#### 2.5.2 ARM Cores

ARM cores are specified as IP blocks from  $\S2.4.2$ . The *new\_pack* function is defined as follows:

$$\begin{array}{cccc} new\_pack & :: & Int \rightarrow Packet \rightarrow Packet \\ new\_pack & id & (src, N) &= & (id, N) \end{array}$$

$$\begin{array}{ccccc} Haskell \end{array}$$

The behaviour of an ARM core is to receive packets form the NoC and issue new packets, carrying its own unique ID, back into the NoC.

#### 2.5.3 NoC Arbiters and Routers

Arbiters and routers are specified with the approaches presented in  $\S2.4.3$  and  $\S2.4.4$  respectively. The function *route*, which was left undefined in  $\S2.4.4$ , is given in figure 2.8 along with its auxiliary function *writeToICLs*; *route* takes slightly different arguments to its counterpart in  $\S2.4.4$ , as explained below.

The *route* function is responsible for copying packets to the appropriate inter-chip links and on-chip ARM cores, as well as initiating and handling emergency routing, and detecting erroneous packets. It takes the following arguments:

• *dests* :: *Maybe*[*Int*] – the information returned by the lookup table. *Nothing* represents a lookup table miss; *Just ds* indicates the on-chip and inter-chip links

route :: Maybe  $[Int] \rightarrow [Channel] \rightarrow [Channel] \rightarrow Int \rightarrow Packet \rightarrow IO()$ route dests procIns iclIns src (id, state)  $| state == N_{-}E1 = \mathbf{do}$ route dests procIns iclIns src (id, N)route dests procIns iclIns src (id, E1) | localMiss = local Miss Handler= forward iclIns src (id, state) forwardPacket = let Just ds = dests in otherwise do write ToICLs iclIns (filter (< 6) ds) (id, state) write ToProcs procIns (filter ( $\geq 6$ ) ds) (id, state) where localMiss  $= dests == Nothing \land src > 5$  $forwardPacket = state = E1 \lor dests = Nothing$ write ToICLs :: [Channel]  $\rightarrow$  [Int]  $\rightarrow$  Packet  $\rightarrow$  IO () write ToICLs iclIns dests pack =  $mapM_{-}$  (write ToICL pack) [0...5] where write ToICL(id, N) node normalPacket node = writeToChan(iclIns!!node)(id, N)node = writeToChan(iclIns!!node)(id, E1)emergencyPacket normAndEmerg  $node = writeToChan (iclIns!!node) (id, N_E1)$ dropped node = drop(id, N)otherwise = return () where normalPacketnode =(busy node)  $\land$   $(\neg (jammed (node + 1)))$ emergencyPacket node =(quiet  $node) \land ($ jammed (node + 1))normAndEmerg node = $node) \land ($ jammed (node + 1))(busy dropped node = $(jammed node) \land ($ broken (node - 1) $node = \neg(receiving \ node) \land \neg(broken$ quietnode) node =receiving node  $\land$ jammed broken node receiving node  $\land \neg$  (broken node =busy node) – Haskell –

Figure 2.8: A component of the SpiNNaker NoC specification.

that the packet should be forwarded to. The six inter-chip links are indexed [0..5] and the 18 ARM cores are indexed [6..23].

- *procIns* :: [*Channel*] a list of channels used for communication with ARM cores.

- *iclIns* :: [*Channel*] a list of channels used as inter-chip links.

- *src* :: *Int* an integer representing the NoC node (ARM core or inter-chip link) from which the packet entered the NoC.

- (*id*, *state*) :: *Packet* the packet.

Note that *route* takes separate *Channel* lists for on-chip and inter-chip links, whereas its counterpart in §2.4.4 took only one list containing all links; this small difference simplifies the definition of *route* and its auxiliary functions.

The function *route* evaluates as follows:

- If the packet has type *N*\_*E*1, it is split into two packets. Both are identical to the original except that one has packet type *N* and one *E*1: *route* is then called recursively on each of these.

- If the lookup table returns *Nothing* and the packet came from an on-chip processor, the predicate *localMiss* evaluates to true, indicating that an error has been detected. This situation should never happen, because the lookup table should only return *Nothing* for default routing when a packet enters the chip through an inter-chip link, and is forwarded to the diametrically opposite inter-chip link. The function *localMissHandler* is called.

- Whenever the state is not N or the lookup returns *Nothing*, *forwardPacket* evaluates to true and we have one of two scenarios:

- 1. If the state is not *N*, we have a packet which is being passed from an interchip link for emergency routing. (We know from the definition of *new\_pack* that only *N*-type packets originate from the on-chip ARM cores.)

- 2. If *dests* == *Nothing*, we know from the falsity of *localMiss* that the packet came from an inter-chip link, and so we have a valid case for default routing.

The cases for default and emergency routing have in common the fact that they can be handled without referring to the lookup table. For this reason, they are both passed to a function *forward* which deals with this scenario.

• *otherwise*: if none of the guards evaluate to true, we know that we have a packet with type *N*, for which the lookup returned *Just ds*. In this case, *writeToICLs* is called to write to the appropriate inter-chip links, and *writeToProcs* is called to write to the appropriate ARM cores.

The function *writeToProcs* is trivial and has been omitted here. However, *writeToICLs* performs an important role in emergency routing, and is shown in figure 2.8. When it is called to forward a packet, *writeToICLs* iterates through the inter-chip links (using the *mapM*<sub>-</sub> function<sup>1</sup>) looking for the following conditions on each link:

- If the link is working but should not receive the packet, it may still have to carry an emergency routing packet. The anti-clockwise neighbour is inspected; if it is broken and should receive the packet, the emergency-routing procedure dictates that the packet should be sent down the present link. This condition is recognised by the predicate *emergencyPacket*.

- If the link is working and the packet should be passed down it, the anti-clockwise neighbour is inspected;

- 1. If it is broken and should receive the packet, we have a case for emergency routing. An *N*\_*E*1 packet should be sent down the present link. This condition is recognised by the predicate *normAndEmerg*.

- 2. If it is working, or not due to receive a packet, an *N* packet is sent down the present link. This condition is recognised by the predicate *normalPacket*.

- If the link is broken, the anti-clockwise neighbour is inspected; if it is broken and should receive the packet, the emergency-routing procedure dictates that the packet should be dropped. This condition is recognised by the predicate *dropped*.

- If none of the above conditions have occurred, no action should be taken for the link in question.

$<sup>^{1}</sup>mapM_{-}$  is similar to mapM, except that it returns an instance of IO ().

# 2.6 Verifying the SpiNNaker NoC

It will now be shown that a packet passing through the SpiNNaker system-wide communications network will never enter a cyclic path as a result of emergency routing. When a packet is launched into the network, we define the *intended path* as the path which it will take in the absence of broken inter-chip links (henceforth *links*) and the *realised path* as the actual path it takes, which may deviate from the intended path because of broken links. To avoid livelock, intended routing paths are checked at compile time to ensure they are acyclic. Because SpiNNaker supports multicast routing, (acyclic) intended routing paths are trees. We define a *hop* as the traversal of a single link. Breaks are assumed to be constant: links which are broken at the creation of the system will remain so, and links which are functioning at the creation of the system will not break.

#### Lemma 1: No realised path will deviate from its intended path for more than one hop.

**Proof:** A realised path will only deviate from its intended path if a link on the intended path is broken. In this case, the packet will diverge for one hop with the type E1. When a SpiNNaker NoC receives an E1 packet, it will either return it to its intended path or drop it. (These scenarios are shown graphically in figure 2.5.)

#### **Theorem 1:** For an acyclic intended path, every realised path will also be acyclic.

**Proof:** We proceed by mathematical induction on the number of broken links in the system.

**Base Case:** No broken links. The realised path will be identical to the intended path, which is acyclic.

**Induction hypothesis:** If the realised path is acyclic in a given system with *n* broken links (henceforth the (n)-system) then it will also be acyclic in a system which is identical, except that it contains one extra broken link (henceforth the (n+1)-system).