## Low Overhead Dynamic Binary Translation for ARM

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science and Engineering.

2016

Bernard Amanieu d'Antras

School of Computer Science

# Contents

| Ab | strac  | t                       | 11 |

|----|--------|-------------------------|----|

| De | eclara | tion                    | 12 |

| Co | pyri   | ;ht                     | 13 |

| Ac | knov   | vledgments              | 14 |

| 1  | Intr   | oduction                | 15 |

|    | 1.1    | Binary translation      | 16 |

|    | 1.2    | Contributions           | 19 |

| 2  | Dyn    | amic Binary Translation | 23 |

|    | 2.1    | Code caches             | 24 |

|    | 2.2    | Multi-threading         | 27 |

|    | 2.3    | Environment             | 28 |

|    | 2.4    | Transparency            | 30 |

|    | 2.5    | MAMBO-X64               | 32 |

|    |        | 2.5.1 Binary translator | 34 |

|    |        | 2.5.2 System emulator   | 36 |

|    | 2.6    | Summary                 | 39 |

| 3 | Opti | imizing | indirect branches in dynamic binary translators | 40 |

|---|------|---------|-------------------------------------------------|----|

|   | 3.1  | Hardw   | vare-assisted function returns                  | 43 |

|   |      | 3.1.1   | Software return address stack                   | 44 |

|   |      | 3.1.2   | Hardware return address prediction              | 45 |

|   |      | 3.1.3   | Return address stack elision                    | 46 |

|   |      | 3.1.4   | Overflow and underflow handling                 | 50 |

|   |      | 3.1.5   | Misprediction handling                          | 51 |

|   |      | 3.1.6   | Unlinking                                       | 54 |

|   | 3.2  | Brancl  | h table inference                               | 55 |

|   |      | 3.2.1   | Detecting branch tables                         | 56 |

|   |      | 3.2.2   | Translating branch tables                       | 58 |

|   | 3.3  | Fast at | comic hash tables                               | 60 |

|   |      | 3.3.1   | Hash table operations                           | 60 |

|   |      | 3.3.2   | SPC and TPC packing                             | 64 |

|   | 3.4  | Evalua  | ntion                                           | 65 |

|   |      | 3.4.1   | Experimental setup                              | 65 |

|   |      | 3.4.2   | MAMBO-X64                                       | 67 |

|   |      | 3.4.3   | Hardware-assisted function returns              | 68 |

|   |      | 3.4.4   | Branch table inference                          | 72 |

|   |      | 3.4.5   | Fast atomic hash tables                         | 72 |

|   | 3.5  | Relate  | d work                                          | 76 |

|   |      | 3.5.1   | Indirect branch handling                        | 76 |

|   |      | 3.5.2   | Function return handling                        | 79 |

|   | 3.6  | Summ    | ary                                             | 81 |

| 4 | MAN  | MBO-X6  | 54: Advanced optimizations and general design   | 84 |

|   | 4.1  | Transl  | ation process                                   | 85 |

|   |      | 4.1.1   | Conditional execution                           | 87 |

|   |      | 4.1.2    | Register allocation                                     |

|---|------|----------|---------------------------------------------------------|

|   |      | 4.1.3    | Dynamic register bindings 93                            |

|   |      | 4.1.4    | Speculative address generation                          |

|   | 4.2  | Return   | n-aware trace generation                                |

|   |      | 4.2.1    | Interactions with hardware-assisted function returns 99 |

|   |      | 4.2.2    | Taking advantage of hardware return prediction 100      |

|   |      | 4.2.3    | Avoiding memory leaks                                   |

|   | 4.3  | Precise  | e OS signal handling 104                                |

|   |      | 4.3.1    | State reconstruction                                    |

|   |      | 4.3.2    | Fragment unlinking 106                                  |

|   |      | 4.3.3    | Race-free signal delivery 107                           |

|   | 4.4  | Evalua   | ntion                                                   |

|   |      | 4.4.1    | Experimental setup 110                                  |

|   |      | 4.4.2    | Overall performance                                     |

|   |      | 4.4.3    | Multi-threaded performance                              |

|   |      | 4.4.4    | ReTrace                                                 |

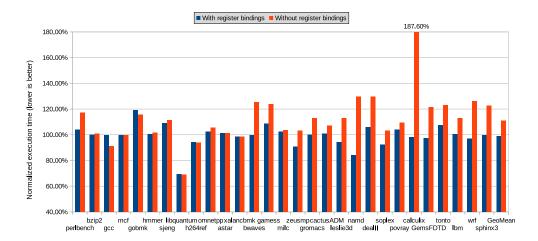

|   |      | 4.4.5    | Register bindings                                       |

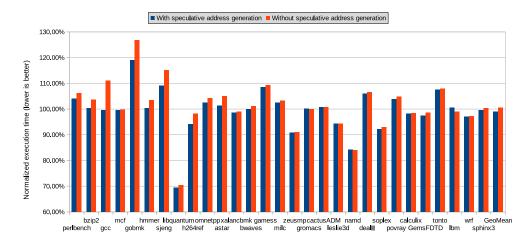

|   |      | 4.4.6    | Speculative address generation                          |

|   | 4.5  | Relate   | d work                                                  |

|   |      | 4.5.1    | Dynamic binary translation                              |

|   |      | 4.5.2    | Signal handling                                         |

|   | 4.6  | Summ     | ary                                                     |

| 5 | Usin | ıg hard  | ware virtualization to support high-performance trans-  |

|   | pare | ent bina | ary translation 127                                     |

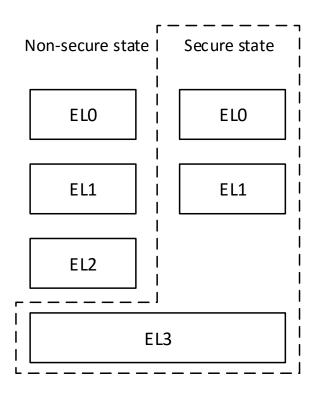

|   | 5.1  | ARMv     | 8 virtualization extensions                             |

|   | 5.2  | Hyper    | МАМВО-Х64                                               |

|   |      | 5.2.1    | Proposed approach                                       |

|   |      |          |                                                         |

|    |                 | 5.2.2                    | Architecture                                           | 38 |

|----|-----------------|--------------------------|--------------------------------------------------------|----|

|    |                 | 5.2.3                    | Memory management                                      | 40 |

|    |                 | 5.2.4                    | Code cache consistency                                 | 43 |

|    |                 | 5.2.5                    | Implementation                                         | 47 |

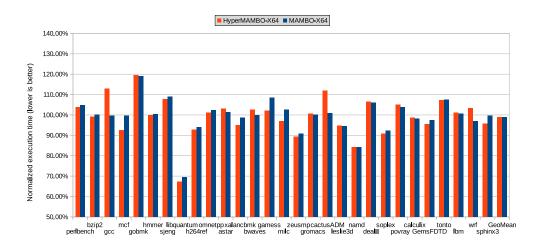

|    | 5.3             | Evalua                   | ation                                                  | 48 |

|    |                 | 5.3.1                    | Microbenchmarks 1                                      | 49 |

|    |                 | 5.3.2                    | SPEC CPU2006                                           | 52 |

|    | 5.4             | Relate                   | d work                                                 | 52 |

|    | 5.5             | Summ                     | ary                                                    | 54 |

| 6  | Con             | nclusions 15             |                                                        |    |

|    | 6.1             | Summary of contributions |                                                        |    |

|    | 6.2             | Future research          |                                                        |    |

|    |                 | 6.2.1                    | Improved startup times through pre-translation 1       | 59 |

|    |                 | 6.2.2                    | Automatic vectorization                                | 60 |

|    |                 | 6.2.3                    | Improving the handling of dynamically generated code   |    |

|    |                 |                          | in HyperMAMBO-X64                                      | 61 |

|    |                 | 6.2.4                    | Persistent code caching for system-level translators 1 | 62 |

|    | 6.3             | Closin                   | g remarks                                              | 63 |

| Bi | Bibliography 16 |                          |                                                        | 64 |

This thesis contains 35122 words.

# List of Figures

| 2.1  | Direct and indirect branch handling in a DBT                    | 26 |

|------|-----------------------------------------------------------------|----|

| 2.2  | Overview of application-level and system-level translators      | 29 |

| 2.3  | Overview of the architecture of MAMBO-X64                       | 35 |

| 2.4  | Address space layout of an application running under MAMBO-     |    |

|      | X64                                                             | 38 |

| 3.1  | Indirect branch types generated by GCC when compiling for       |    |

|      | AArch32                                                         | 41 |

| 3.2  | Return address stack contents while executing nested function   |    |

|      | calls                                                           | 45 |

| 3.3  | Translated function call and return in MAMBO-X64                | 47 |

| 3.4  | Example code showing RAS elision in MAMBO-X64                   | 49 |

| 3.5  | Overflow and underflow handling for the return address stack    | 52 |

| 3.6  | AArch32 branch table generated by Clang/LLVM for a switch       |    |

|      | statement, and an AArch64 translation of that branch table      | 56 |

| 3.7  | AArch32 branch tables generated by GCC                          | 59 |

| 3.8  | Indirect branch lookup algorithm with fast atomic hash tables   | 62 |

| 3.9  | AArch64 implementation of the indirect branch lookup algorithm. | 62 |

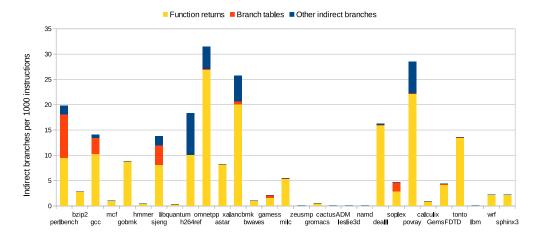

| 3.10 | Dynamic distribution of indirect branch types in SPEC CPU2006.  | 66 |

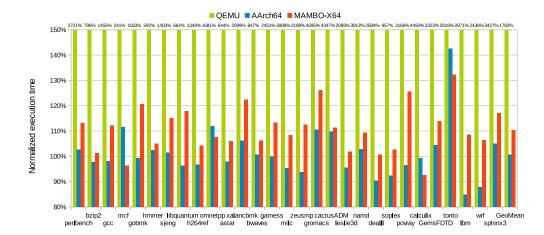

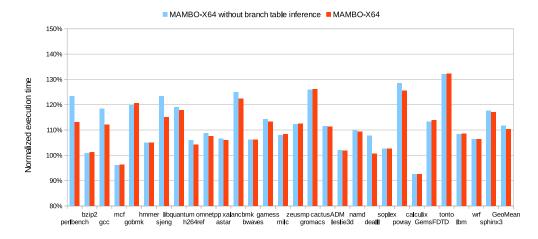

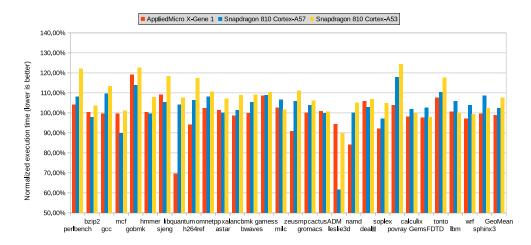

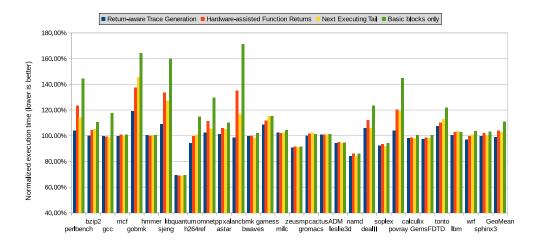

| 3.11 | Performance of various systems on SPEC CPU2006                  | 68 |

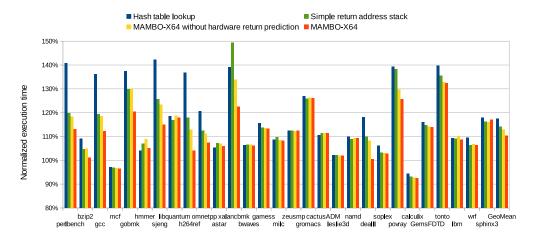

| 3.12 | MAMBO-X64 performance on SPEC CPU2006 with different ways     |

|------|---------------------------------------------------------------|

|      | of handling function returns                                  |

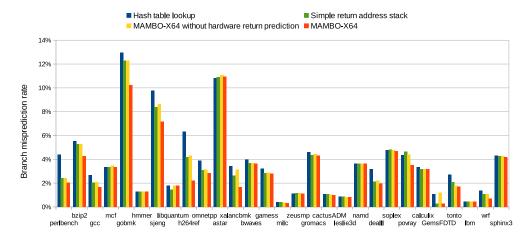

| 3.13 | Hardware branch misprediction rate of MAMBO-X64 on SPEC       |

|      | CPU2006 with different ways of handling function returns 71   |

| 3.14 | MAMBO-X64 performance on SPEC CPU2006 with and without        |

|      | branch table inference                                        |

| 3.15 | MAMBO-X64 performance on SPEC CPU2006 with various in-        |

|      | direct branch handling techniques                             |

| 4.1  | Floating-point register aliasing in AArch32 and AArch64 91    |

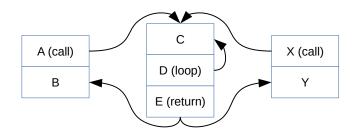

| 4.2  | Example traces showing the differences between NET and the    |

|      | ReTrace algorithm used by MAMBO-X64                           |

| 4.3  | Code to atomically execute a system call only if there are no |

|      | pending signals                                               |

| 4.4  | Performance of SPEC CPU2006 on MAMBO-X64 on different         |

|      | processors                                                    |

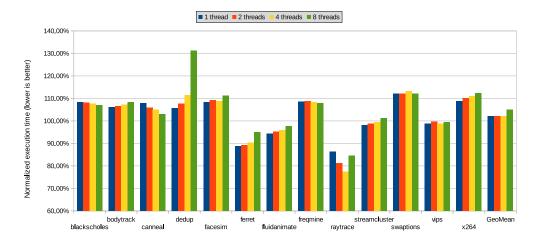

| 4.5  | Performance of the PARSEC benchmarks running on MAMBO-        |

|      | X64 with different numbers of threads                         |

| 4.6  | Performance of SPEC CPU2006 running on MAMBO-X64 with         |

|      | different trace generation techniques                         |

| 4.7  | Performance of SPEC CPU2006 on MAMBO-X64 with and with-       |

|      | out register bindings                                         |

| 4.8  | Performance of SPEC CPU2006 on MAMBO-X64 with and with-       |

|      | out speculative address generation                            |

| 5.1  | ARMv8 exception levels                                        |

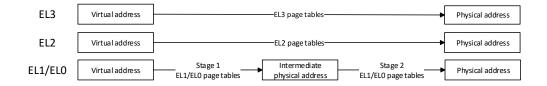

| 5.2  | ARMv8 virtual memory address translation for different excep- |

|      | tion levels                                                   |

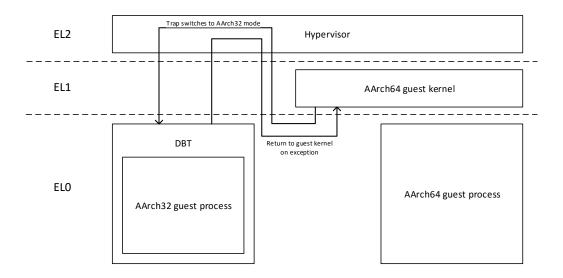

| 5.3 | Overall architecture of HyperMAMBO-X64                        |

|-----|---------------------------------------------------------------|

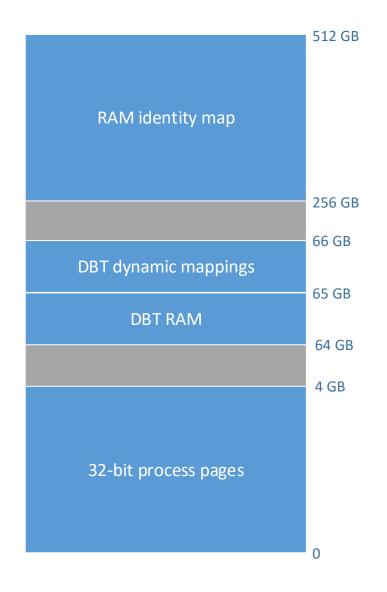

| 5.4 | Virtual memory map of a process running under the HyperMAMBO- |

|     | X64 DBT                                                       |

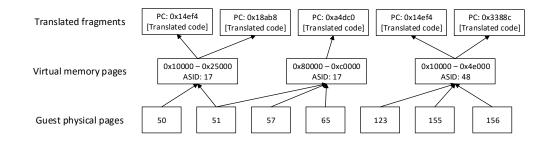

| 5.5 | HyperMAMBO-X64's data structures for tracking code cache in-  |

|     | validation                                                    |

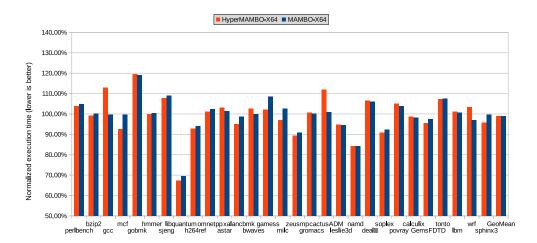

| 5.6 | Performance of SPEC CPU2006 under HyperMAMBO-X64 and          |

|     | MAMBO-X64                                                     |

# List of Tables

| 3.1 | Memory usage of megatables compare to fast atomic hash tables  |     |

|-----|----------------------------------------------------------------|-----|

|     | on SPEC CPU2006                                                | 75  |

| 4.1 | Examples of AArch32 instruction sequences translated by MAMBO- |     |

|     | X64                                                            | 88  |

| 4.2 | Comparison of AArch32 and AArch64 registers and how MAMBO-     |     |

|     | X64 uses them                                                  | 92  |

| 4.3 | Examples of memory addressing modes in AArch32 and AArch64.    | 95  |

| 5.1 | Microbenchmark results under HyperMAMBO-X64 in three tested    |     |

|     | configurations                                                 | 149 |

| 6.1 | Summary of the performance of SPEC CPU2006 on MAMBO-           |     |

|     | X64 on different processors                                    | 158 |

### Abstract

#### LOW OVERHEAD DYNAMIC BINARY TRANSLATION FOR ARM

#### Bernard Amanieu d'Antras

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy, 2016

Driven by Moore's Law, many computer architectures — ARM, x86, MIPS, PowerPC, SPARC — have evolved from 32-bit to 64-bit. To support existing applications, these have all kept support for a 32-bit compatibility mode. However, this comes at a cost in hardware complexity, power consumption and development time.

Dynamic binary translation — recompiling binaries into the new instruction set at runtime — can be used instead of specific hardware for this purpose. While this approach has previously been used to assist architecture transition, these translators have all traded-off performance and *transparency*, a measure of how accurately they emulate the 32-bit environment.

This thesis addresses ARM's transition from AArch32 to AArch64 through MAMBO-X64, a dynamic binary translator developed to support this transition. A range of novel optimizations were devised to improve translation performance while maintaining strict transparency. This follows a common theme of exploiting existing hardware features such as hardware return prediction, virtual memory and virtualization extensions to offset translation overheads. HyperMAMBO-X64 — a variant of MAMBO-X64 integrated in a hypervisor — was also developed to support system-level translation while remaining transparent to guest operating systems.

Results demonstrate that the cost of binary translation is reduced, delivering performance competitive with the manufacturer's hardware. Performance in several benchmarks even *exceeds* that from the integrated compatibility mode. Thus MAMBO-X64 not only provides a means for architectural upgrade, but also an *alternative* to the expense of the legacy support currently employed.

# Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester. ac.uk/DocuInfo.aspx?DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/ aboutus/regulations) and in The University's policy on presentation of Theses

## Acknowledgments

I am immensely grateful towards Prof. Mikel Luján, my supervisor, for his extensive support and guidance during my years as a PhD student. It was Mikel who first guided me towards binary translation as a research topic, and in hindsight it is obvious that he could not have made a better decision. I am similarly thankful to Dr. Jim Garside, my co-supervisor, who has always kept his door open for impromptu discussions, both technical and mundane, as well as his uncanny (but tremendously useful!) ability to always find something to improve in any paper that crosses his path.

Both of my supervisors have provided me with excellent and detailed feedback throughout the process of writing my thesis, for which I thank them, as well as Jonathan Heathcote and Dr. Andy Nisbet for providing helpful reviews of my thesis and papers.

I would like to extend special thanks to Cosmin Gorgovan and Guillermo Callaghan for the lively discussions on the finer points of dynamic binary translation. Though we may not have always agreed, these discussions were always mutually beneficial to our respective projects. And, of course, I thank the many members of the Advanced Processor Technologies group for filling the past few years of my life with fun, which more than compensated for the evanescent Manchester sunshine. I am also grateful to the School of Computer Science for the funding that it has provided for my research.

After nearly fifteen years, I extend a grateful thought to Nicolas Ténart, my secondary school mathematics teacher, who first taught me the joys of programming and started me down the path to this thesis.

Last but not least, I would like to thank my family for their patience, support and carefully orchestrated nodding as they endured a lifetime's quota of my rants on race conditions and obscure ARM instructions.

## Chapter 1

# Introduction

Computer architectures have always evolved following hardware and software technology trends over time, driven by Moore's Law [Moo65]. This evolution generally takes the form of adding new instructions to accelerate certain algorithms or implementing architectural features such as virtual memory. However, much like biological evolution, this process results in many features which "seemed like a good idea at the time" but turned out to be poorly adapted to a later software ecosystem.

For example, in early microprocessors (c. 1970) it was common to support Binary Coded Decimal (BCD) operations, something which is rarely wanted directly now. Such operations could be abandoned, but this renders old code potentially inoperable and is generally unacceptable. Thus they must be supported in some way.

Two major 'mainstream' processor architectures — Intel x86 and ARM — illustrate two contrasting approaches to this: Intel maintains full backwards compatibility with all instructions since the 8086 by emulating legacy instructions using low-level microcode programmes embedded in the processor. ARM has, instead, opted to support legacy instructions directly in hardware, while

simultaneously deprecating and removing old features (such as 26-bit addressing, Jazelle and ThumbEE) from newer versions of the ARM architecture. While removing features was acceptable when ARM processors were primarily used in embedded systems with tightly bound hardware and software, this is no longer the case now that ARM is a widespread, general-purpose architecture.

These considerations extend to architecture transitions: current computer architectures — ARM, MIPS, PowerPC, SPARC, x86 — have all evolved from a 32-bit architecture to a 64-bit one. Again, x86 and ARM take two contrasting approaches to this: on one hand x86-64 provides a mostly straightforward extension of the 32-bit instruction set to 64 bits, carrying over most of the legacy 8086 instructions to the new execution mode. On the other hand ARM exploited this opportunity to discard much of the 'baggage' it had accumulated over seven versions and many variants of the architecture, thus producing a 'clean' instruction set which, in turn, potentially allows for simpler and more efficient processor designs.

### **1.1** Binary translation

The desire to simplify and clean up the hardware architecture and the requirement to support software making use of legacy features can be bridged through the use of *binary translation*.

Binary translation is a technology which allows a program to be translated and modified transparently at the machine code level. It has numerous applications, such as dynamic instrumentation [MCGP07, SN05], program analysis [SIN11, ZKR<sup>+</sup>11], virtualization [AA06, Wat08] and instruction set translation [Bel05, DGB<sup>+</sup>03]. A binary translator does not need access to the source code of a program, which makes it particularly useful in cases where source code is not available or is not portable enough to be simply recompiled.

Binary translation has previously been used successfully to assist architecture transitions: the best known example is Rosetta [App06], which was used by Apple to transit their platform from PowerPC to x86, based on technology originally developed at the University of Manchester [Tra08]. IA-32 EL [BDE<sup>+</sup>03] and HP Aries [ZT00] both supported the transition to the IA-64 architecture from x86 and PA-RISC respectively. FX!32 [HH97, CHH<sup>+</sup>98] was similarly used to help migrate x86 applications to the Alpha architecture. Binary translation has also been used to allow execution of code from existing instruction sets on a Very Large Instruction Word (VLIW) architecture, such as Nvidia Denver (ARM on VLIW) [BBTV15] and Transmeta Crusoe (x86 on VLIW) [DGB<sup>+</sup>03].

While translation may be attempted statically (i.e. off-line by generating a new, translated binary) there has been a trend back to self-modifying code — particularly the use of Just-In-Time (JIT) compilers — which renders this process inefficacious. Instead, *dynamic binary translation* — at runtime — must be used for complete compatibility.

Binary translation typically suffers from some performance overhead compared to recompiling an application from its source code. The sources of overhead can be broadly categorized as follows:

Architectural mismatch While, fundamentally, the binary translation process is quite straightforward — an ADD instruction in the source architecture can be translated into an equivalent ADD instruction in the host architecture — complications can arise when the exact semantics of these instructions differ, such as the exact set of condition flags modified by such an ADD instruction (e.g. carry flag, overflow flag). While a source compiler only needs to translate the semantics of the source code and is thus free to discard most of these flags, e.g. only using one of them for a conditional branch, a binary translator works at a lower level and must emulate all aspects of the host architecture accurately. This type of overhead generally comes in the form of additional instructions required to simulate all the effects of the source instruction, such as calculating the correct values of all the condition flags.

- **Environment overhead** In addition to the above, generating code to work within the constraints of a binary translation environment brings its own challenges. For example, processor registers from the source architecture need to be mapped to those of the host architecture and, if the latter resource is insufficient, source register values should be spilled to memory. Additionally, any operations involving the program counter, such as branches, require special handling since the translated code may be located at a different address from the source instructions.

- **Translation overhead** Finally, for dynamic translators, the process of translation itself occupies a portion of the execution time. Unlike the previous two sources of overhead, which are evenly distributed over the runtime of an application, translation overhead mainly occurs during application startup when no code has been translated yet. This overhead becomes insignificant for long-running applications as it is amortized over the entire runtime of the application, providing the translated code can be retained.

#### **1.2 Contributions**

There has been incremental development of binary translation over the past few decades, however the overheads outlined above still imply that the translated code runs slower than it could with hardware support.

In particular, while existing research has developed optimizations to deal with the overheads of binary translation, many of these trade off *transparency* in favor of performance. In other words, such optimizations make assumptions about the behavior of a program (e.g. "the program never accesses invalid memory addresses" or "condition flags do not need to be preserved across function calls"), and cause the translated program to behave incorrectly if these assumptions are violated.

This thesis enables the elimination of hardware support for a legacy instruction set in new processors by describing how to create dynamic binary translators which rival the performance of direct hardware support. This is achieved through a series of novel optimizations which address various sources of performance overhead involved in binary translation, all while maintaining the transparency of the translation.

The focus of this thesis is on the ARM's transition to a 64-bit architecture. The ARMv8 architecture introduced AArch64, a 64-bit execution mode with a new instruction set, in addition to the existing AArch32 32-bit instruction set. Due to the need to support the large number of existing AArch32 applications, current hardware implementations of ARMv8 processors support *both* AArch32 and AArch64. However, this situation is problematic since such support comes at a cost in hardware complexity, power usage and development time.

MAMBO-X64, a dynamic binary translator which executes 32-bit ARM binaries using only the AArch64 instruction set, was developed as a solution to this problem. It opens a path for future processors to drop hardware support for the legacy 32-bit instruction set while retaining the ability to run AArch32 applications at realistic speeds. MAMBO-X64 is a mature piece of technology which is able to run complex Linux and Android applications and has already been licensed to at least one company.

The performance of MAMBO-X64 is competitive with that of the hardware support in current ARMv8 processors: 32-bit builds of many benchmarks — from suites such as SPEC CPU2006 and PARSEC — run faster under MAMBO-X64 than natively on the processor. This is attributable to a number of new techniques which have been developed to address the worst remaining inefficiencies of pre-existing translators.

It was reported some time ago that **indirect branch handling** was the biggest source of performance overhead in a binary translator [KS03, HWH<sup>+</sup>07], a problem which still had remained largely unsolved. An indirect branch is a branch instruction with a target which is only known at execution time and which can vary from one execution to the next, a common example being a subroutine return. Unlike direct branches, which have a known target at translation time, an indirect branch requires translating a source program counter address to a translated program counter address every time the branch is executed. This translation can impose a serious runtime penalty if it is not handled efficiently.

Chapter 3 describes three novel techniques for translating such branches. The first, *hardware-assisted function returns*, uses a software return address stack to predict the targets of function returns, making use of several novel optimizations while also exploiting hardware return address prediction. The second, *branch table inference*, is an algorithm for detecting and translating branch tables into equivalent structures for the host architecture. The remaining indirect branches are handled using a *fast atomic hash table*. This translates indirect branches using a single shared hash table which avoids expensive synchronization in performance-critical lookup code. This chapter is based on the paper *Optimizing Indirect Branches in Dynamic Binary Translators* [dGGL16] which was published in *Transactions on Architecture and Code Optimization*.

Chapter 4 describes the other new optimization principles used by MAMBO-X64 to achieve high performance without sacrificing accuracy. The most significant one, after indirect branch optimizations, is *ReTrace*, the trace generation algorithm used by MAMBO-X64 which improves the layout of translated code by further exploiting hardware return address prediction. MAMBO-X64 also supports a wide range of optimizations, including an efficient system for mapping AArch32 floating-point registers to AArch64 registers dynamically and a speculative optimization to improve the performance of certain ARM addressing modes.

Supporting legacy code through binary translation requires more than just translating one instruction set to another: software is designed to work within an **environment**, and the software-visible interfaces of this environment must be translated as well. In the case of a user-level binary translator like MAMBO-X64, this consists primarily of OS interfaces such as *system calls* and *signals*. While system call translation is fairly straightforward, signals pose particular challenges since some can occur at arbitrary points in the execution of a program. Section 4.3 describes how MAMBO-X64 supports accurate delivery of synchronous and asynchronous OS signals without sacrificing performance.

Dynamic binary translation generally comes in one of two forms: applicationlevel translators, which translate a single user mode process on top of a native operating system, and system-level translators which translate an entire operating system and all its processes. Application-level translators can have good performance but are not totally transparent; system-level translators may be 100% compatible but performance typically suffers.

Chapter 5 presents HyperMAMBO-X64, which uses a new approach that gets the best of both worlds, being able to run the translator as an application under the hypervisor but still react to the behavior of guest operating systems. It works with complete transparency with regards to the virtualized system whilst delivering performance close to that provided by hardware execution.

A key factor in the low overhead of HyperMAMBO-X64 is its deep integration with the virtualization and memory management features of ARMv8. These are exploited to support the caching of translations across multiple address spaces while ensuring that translated code remains consistent with the source instructions it is based on. These attributes are achieved without sacrificing either performance or accuracy.

Together this set of contributions has accelerated MAMBO-X64 such that it delivers execution performance rivaling that of a hardware implementation. This includes the translation time, which means that binary translation is not only feasible but also becomes an attractive option for future backward compatibility and will allow silicon companies such as ARM to reduce their development and verification overheads in future silicon implementations.

## Chapter 2

## **Dynamic Binary Translation**

A static binary translator translates the entirety of the program object code ahead of time. This is convenient because it may take time for optimization without impacting runtime. However such translators are not always practical in the general case due to the *code-discovery problem* [HM80]: since it is not always possible to determine which memory locations contain instructions as opposed to inline or pre-loaded data, all addresses need to be treated as potential branch targets to ensure full transparency. In modern systems this problem is worse in that not all the code that will be executed is present ahead of time, such as when a program imports shared libraries or generates new instructions using a Just-In-Time compiler. A Dynamic Binary Translator (DBT) translates code only as it is about to be executed, which avoids these issues but comes at a cost in overall runtime because code discovery and translation time is included.

A significant disadvantage of dynamic binary translators is that, while they are able to achieve good performance when executing translated code, they suffer from poor startup times because of the need to translate new code when an application begins. This has led to new types of DBTs which integrate some aspects of static translation to accelerate application startup times. This comes either in the form of ahead-of-time translation which generates translated code by pre-processing an application binary, or in the form of persistent code caches [BK08, RCCS07] which retain translated code across multiple invocations of an application. Both of these methods provide a pre-existing base of translated code which is available immediately on application startup, while dynamic translation is still available to handle any remaining untranslated code.

### 2.1 Code caches

Translating a block of code is more efficient than translating single instructions in many ways, hence DBTs usually translate sequences of instructions as blocks, called *code fragments*. Fragments can have many forms, depending on the design of the DBT, the most common of which is the *basic block*. A basic block corresponds to a linear sequence of source instructions with a single entry point and a single exit point. While this approach has the advantage of simplicity, it can suffer from poor performance due to the need for branches between basic blocks. Many DBTs therefore also use of some form of *superblocks* which still have a single entry point but can have multiple exits. Larger fragments also allow a DBT more opportunities for optimizations such as dead code elimination and constant propagation.

Since some code, such as loop and function bodies, is likely to be executed many times, it is advantageous to preserve translated fragments so that they can be used again, instead of re-translating each time they are encountered. Rather than modifying the program code, translated fragments are stored in a *code cache*, separate from the original instructions. A naïve DBT would schedule the execution of each fragment as it is needed by jumping to the start of the fragment and having the fragment return control to the DBT once it has finished running. A fragment typically ends when the translation has encountered a branch instruction, at which point the DBT must select the next fragment to execute. This approach is impractical because of the high overhead of context switching between fragments and the DBT, and the frequent changing of fragments in typical programs<sup>1</sup>.

Instead, a branch in one fragment can be *linked* to a different fragment by having the translated branch transfer control to the target fragment directly. Because source and translated fragments are not, necessarily, identical in size, the address from the source cannot be used directly: some address translation is necessary.

For *direct branches*, where the branch target is a constant encoded in the instruction itself, this translation can be performed statically at translation time, resulting in a single branch instruction in the translated code that points to the fragment for the target address. If a fragment has not yet been translated for the branch target, the translated branch can point to an *exit stub*, which returns control to the DBT while passing the current program counter value so that the DBT knows what to execute next. When the target fragment is translated, any branch instructions in other fragments that pointed to the exit stub are patched and redirected to point to the newly translated fragment.

*Indirect branches* need to be handled differently because their target is only known at execution time and can vary from one execution to the next. This requires its own dynamic translation and imposes a serious runtime penalty. Translation is typically implemented by using a hashed translation table to find the translated fragment for a given target address at runtime. While this

<sup>&</sup>lt;sup>1</sup>A typical basic block fragment has fewer than a dozen instructions.

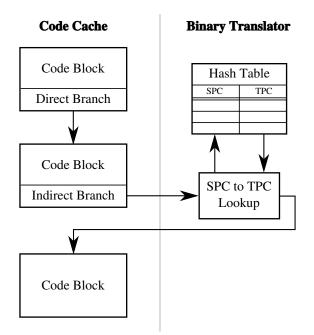

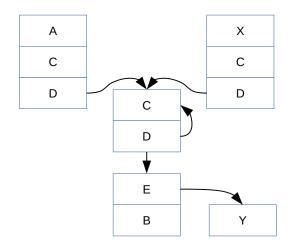

Figure 2.1: Direct and indirect branch handling in a DBT.

approach solves the translation problem, it is still many times slower than a native indirect branch, which only consists of a single instruction. It also interacts poorly with hardware branch prediction mechanisms that are optimized for native code, often resulting in unnecessary branch mispredictions.

Figure 2.1 shows how fragment in a code cache are linked through direct and indirect branches. While direct branches can be linked directly, every time an indirect branch is executed in a DBT, a Source Program Counter (SPC) value must be mapped to a Translated Program Counter (TPC) value, which is then branched to. This figure illustrates how the translation of an indirect branch can be much more costly than that of a direct branch.

### 2.2 Multi-threading

Multi-threaded applications pose additional challenges to a DBT. In particular, threads may share the source object code and different threads could 'collide' in deciding to perform translations. These concerns are particularly relevant for the design of the code cache, for which there exist two major models: *thread-private* code caches and *thread-shared* code caches.

Thread-private code caches This model is the simplest to implement since it involves each thread having a separate code cache. It also enables several optimizations that exploit the fact that a code cache is only used by a single thread, such as self-modifying code or embedding pointers to thread-local data directly in the translated code. The main disadvantage of thread-private code caches is that multi-threaded applications suffer from increased memory usage and high overhead on thread creation to fill the code cache, particularly for server applications which may create hundreds of threads. Additionally, the need for synchronization is not completely eliminated since it is still necessary to handle cases where one thread needs to invalidate a fragment in the code cache of another thread.

Thread-shared code caches While this model is more complicated to implement, researchers have demonstrated [BKGB06, HLC09] that it scales significantly better than thread-private code caches on multi-threaded applications. In this model, all threads share the same code cache, which means that translated code cannot 'hard-code' pointers to thread-local data and must use some form of indirection instead. Executing code in such a code cache does not require any synchronization and code translation can be performed concurrently in multiple threads. Synchronization is only required when adding or removing a fragment from the code cache, which is a rare operation compared to the execution of translated code.

A key issue with thread-shared code caches is the handling of fragment deletion: a fragment cannot be deleted from the code cache immediately since there may be other threads concurrently executing that fragment. Instead, the fragment must first be *unlinked*, which removes all branch instructions pointing to the fragment and ensures that it cannot be re-entered. The fragment can then be fully deleted once all other threads are known to have exited the code cache at least once since the fragment was unlinked, as this indicates that other threads can no longer be executing the deleted fragment.

### 2.3 Environment

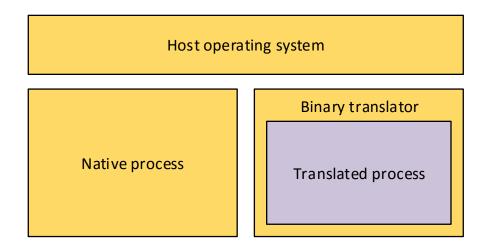

DBTs can generally be split into two categories, shown in Figure 2.2, depending on the type of environment that they inhabit:

**Application-level translators** These translators work at the level of a single user-mode process, running an application compiled for a guest ISA on top of an operating system for the host ISA. In addition to translating all the instructions executed by the user-mode process, such a DBT also needs to translate the operating system Application Binary Interface (ABI), which can have significant variations from one ISA to another. This is usually done by intercepting all interactions between the translated application and the host OS, such as system calls and signals, and translating them from the format of the guest ABI to that of the host ABI. Examples of DBTs in this category are QEMU [Bel05], Aries [ZT00], IA-32 EL [BDE<sup>+</sup>03], FX!32 [HH97, CHH<sup>+</sup>98], Rosetta [App06] and StarDBT [WHK<sup>+</sup>07].

(a) Application-level translator

(b) System-level translator

Figure 2.2: Overview of application-level and system-level translators.

**System-level translators** These translators work at the level of a complete system and, effectively, simulate a virtual machine running on a foreign architecture. These systems tend to be more complex than application-level translators because they need to be able to translate a larger portion of the guest instruction set. Whereas an application-level translator only needs to support user-mode, unprivileged instructions, a system-level translator must support the full guest ISA including all privileged instructions and related operations. An important part of this is efficiently simulating the guest ISA's virtual memory architecture, which involves translating page tables from one format to another and correctly handling page table modifications. Examples of DBTs in this category are MagiXen [CMR07], Transitive QuickTransit [Tra08], QEMU [Bel05], Transmeta's Code Morphing Software (CMS) [DGB<sup>+</sup>03] and Nvidia's Project Denver [BBTV15].

While the first part of this thesis focuses on application-level translators, the topic of system-level translators will be revisited in Chapter 5.

#### 2.4 Transparency

*Transparency* is a measure of how accurately a DBT emulates a target environment. As a general rule, the more transparent a DBT is, the more details of the target environment it emulates which, in turn, allows a wider range of applications to function under the DBT successfully. Conversely, increased transparency also comes at a cost in performance, since additional time needs to be spent emulating these details.

A perfectly transparent DBT is functionally indistinguishable from the target environment in every way from the point of view of the translated application, down to simulating details such as instruction timings. Such a level of transparency comes at a large performance cost, typically at least an order of magnitude slower than the simpler behavioral transparency, which is an unacceptably high cost in most situations.

A lesser form of transparency which is more commonly used by DBTs is *behavioral transparency*, which involves only supporting features defined by the ABI of the target environment. A DBT can exploit this by assuming that applications never perform any operations which the ABI considers to have undefined behavior. Examples of undefined behaviors in ABIs include using undefined instruction encodings, writing data below the stack pointer and not flushing the instruction cache after modifying instructions.

Despite this relative freedom, transparency requirements still have subtle implications for the code generated by a DBT, for example:

- An application's memory, including its code, should not be modified by a DBT. This is necessary to ensure that applications which inspect their own code memory see the original instructions, hence the use of a code cache by DBTs instead of modifying application memory. This restriction is further emphasized by the need to support applications that perform self-modification of their own code.

- Faulting memory accesses must be precisely emulated since they can be caught by an application fault handler which has the ability to inspect the full processor register state at the fault point. Some applications make use of this information to handle faults themselves, after which they resume execution with a modified register state. Supporting this means that a DBT must be able to recover the original values of all registers every time a potentially faulting instruction is executed.

• Even if memory accesses do not cause a fault, they may have side effects if their addresses refer to memory-mapped I/O regions. This means that a DBT cannot consider loads and stores to be free of side effects, which limits its ability to reorder, merge or elide such instructions.

#### 2.5 MAMBO-X64

ARM [Sea01] is a general purpose architecture widely used in both embedded systems and consumer devices such as phones, tablets and TVs. While ARM has traditionally been a 32-bit architecture, the ARMv8 version of the architecture [Gri11] introduced a new 64-bit execution mode and instruction set, called *AArch64*. This 64-bit ISA has double the number of general-purpose registers as the previous architecture and extends them to 64 bits, while also increasing the size of the floating-point/SIMD register bank.

One of the key factors driving the design of AArch64 is the desire to return to the RISC philosophy by cleaning up all the "clutter" that has accumulated in the 32-bit ARM architecture through its various revisions, which have led, among other things, to a convoluted and variable-width instruction encoding. The new instruction set is therefore a better fit for ARM's overall strategy by enabling smaller and lower-power core implementations.

While AArch64 has many benefits, there is a large ecosystem of existing 32bit applications which need to be able to run on ARMv8 systems. The current generation of ARMv8 processors is capable of running legacy 32-bit ARM code directly in *AArch32* mode, but maintaining this support comes at a cost:

• The AArch32 execution mode supports two instruction sets: a fixedwidth 32-bit instruction set (ARM) and a variable-length 16/32-bit instruction set (Thumb-2). This increases the complexity and power usage of the instruction decode unit compared to supporting just a single, fixedwidth instruction set. AArch64 instructions are always 32 bits long and of regular format, which allows a simpler decoder design. On typical ARM processors, the instruction decode unit alone can account for over 10% of the overall CPU power consumption [NVI13].

- AArch32 contains legacy instructions that have not been carried forward to AArch64. Many of these instructions are intended for specialized DSP workloads and rarely appear in compiler-generated code. Supporting these instructions requires additional complexity in the ALUs.

- Having to support two instruction sets in hardware can more than double the cost of hardware verification due to the possible interactions between instruction sets. This, in turn, increases the development time of a processor; it also increases the chance of a defect making its way into released hardware, fixing which may require the creation of a new processor revision.

MAMBO-X64 is a DBT developed by the author at the University of Manchester which translates AArch32 Linux programs into AArch64 code. It is implemented as a process-level virtual machine: a separate binary translator instance is started for each 32-bit process, while the operating system kernel and 64-bit processes run natively on the processor. The objective is to support the running of legacy AArch32 code without the need for specific hardware support, preferably at speeds competitive with hardware execution. No contemporary DBT which achieves a similar goal has been described.

When tested on existing ARMv8 systems which support both AArch32 and AArch64 in hardware, a 32-bit build of SPEC CPU2006 [Cor] ran on average 1% *faster* under MAMBO-X64 compared to running the same 32-bit binary na-

tively on the processor. Particular benchmarks were also measured to run up to 38% faster under MAMBO-X64 than natively, although a few other benchmarks suffer from a performance degradation of up to 19%.

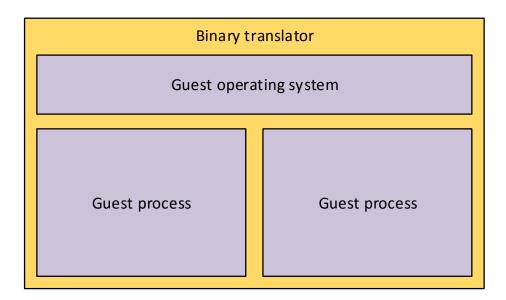

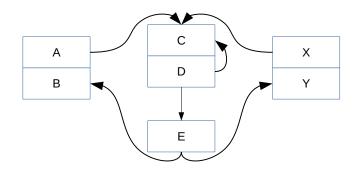

MAMBO-X64 is structured as three components, shown in Figure 2.3:

- **Binary translator** The binary translator is an operating system-independent module which performs the translation of AArch32 instructions into AArch64 code.

- **System emulator** The system emulator handles all interactions with the operating system, such as system calls and signals, and translates them between the 32-bit and 64-bit Linux ABIs.

- **Support library** The support library provides OS-specific utilities such as memory management and synchronization primitives to the binary translator and system emulator.

This arrangement isolates OS-specific code from the binary translator, which makes it easier to port MAMBO-X64 to other operating systems.

#### 2.5.1 Binary translator

The binary translator component has the same basic structure as a typical DBT: it works by scanning sequences of AArch32 instructions on demand and converting them into AArch64 code fragments, stored in a thread-shared code cache. Each fragment is either a single-entry, single-exit *basic block* or a single-entry, multiple-exit *trace* formed by combining multiple basic blocks.

A key focus in the design of MAMBO-X64 was efficient handling of indirect branches in translated code. For this purpose, three new techniques for translating indirect branches, each applying to a different class of indirect branch, have been developed. These techniques are discussed in detail in Chapter 3.

Figure 2.3: Overview of the different components in MAMBO-X64. The binary translator translates sequences of instructions from the guest address space into fragments in the code cache. The system emulator handles system interactions such as system calls and signals, and manages the guest address space. The code cache also contains various metadata associated with the translated fragments.

MAMBO-X64 also leverages a wide range of optimizations to improve the performance of the translated code. Specific techniques developed during the author's research are described in detail in Chapter 4. These optimizations include:

- An efficient scheme for mapping AArch32 floating-point registers to AArch64 registers dynamically.

- A method for efficiently translating AArch32 load/store addressing modes into AArch64 by speculatively assuming that address calculations do not overflow.

- A novel trace compilation algorithm that leverages hardware return address prediction to improve performance.

MAMBO-X64 is able to precisely emulate the full AArch32 instruction set, which includes both the traditional ARM instruction set as well as the newer Thumb instruction set. The binary translator was extensively tested through both manually written test suites and randomly generated instruction sequences, each time ensuring that the tests run identically whether translated or run natively.

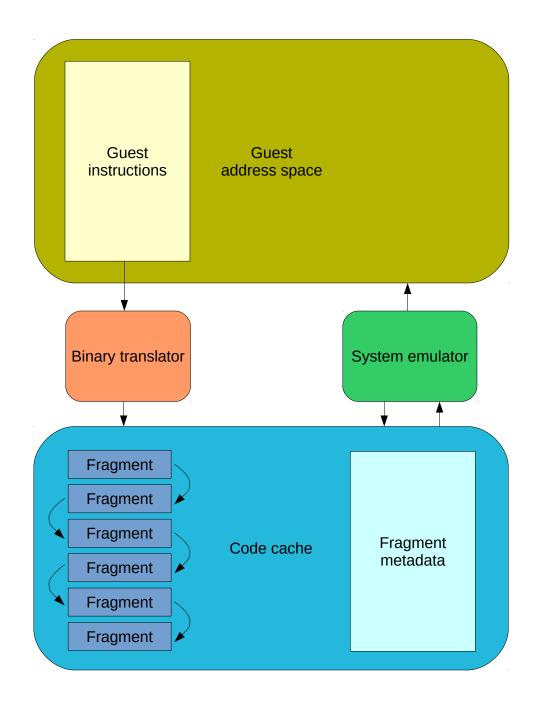

#### 2.5.2 System emulator

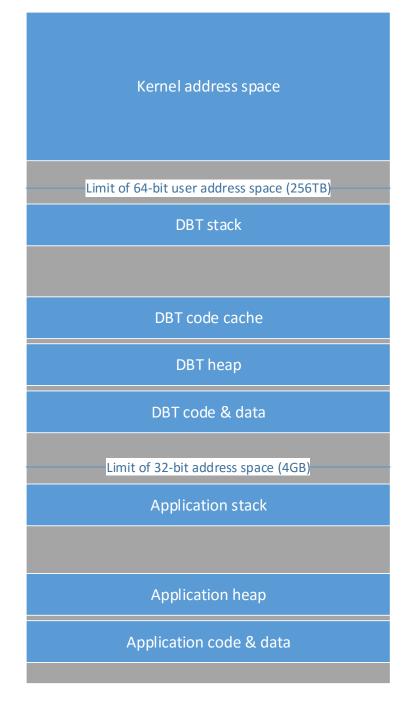

The system emulator has three main functions: managing the address space of the translated program, translating system call parameters and handling signals. MAMBO-X64 takes advantage of the 64-bit address space by allocating a 4 GB 'private' address space for the translated application. The program image is loaded into this address space on startup and all memory accesses performed by the application are restricted to this address space since the original code uses 32-bit memory addresses. This layout, shown in Figure 2.4, isolates the application from the DBT and ensures that it is impossible for faulty applications to affect the operation of the DBT.

The Linux system ABI for AArch64 differs from that for AArch32 in several ways, such as the size and layout of data types used in system calls and the layout of the stack frame when a signal handler is called. MAMBO-X64 therefore needs to emulate the AArch32 Linux ABI by translating the AArch32 system calls generated by the translated program into a format that can be handled by the host kernel. However, Linux exposes a large number of system calls and is constantly evolving<sup>2</sup>, which makes it impractical to create and maintain ABI translation wrappers for each of them. Such wrappers are even more impractical for multiplexed system calls, such as ioct1, which exposes thousands of device-specific sub-functions.

This complexity can be avoided by reusing the built-in compatibility layer in the AArch64 kernel. This layer is used to support running native AArch32 applications and provides system call wrappers which translate 32-bit system calls into their 64-bit equivalent. MAMBO-X64 intercepts some system calls and handles them internally, such as those used for virtual memory management and signal handling, and forwards the remaining ones to the compatibility layer in the host kernel.

MAMBO-X64 also intercepts all *signals* delivered to the translated program using a master signal handler, which then handles the delivery of the signal to the application. Signal handling in DBTs is complicated because they can occur at any point while executing translated code and require a view of the untranslated register state at the interrupted point to be given to the application signal handler. MAMBO-X64 uses a scheme involving fragment unlinking and signal

<sup>&</sup>lt;sup>2</sup>At the time of writing, Linux (version 4.5) has 387 different system calls.

Figure 2.4: Address space layout of an application running under MAMBO-X64.

masking to achieve race-free and efficient signal delivery to the application, which is described in Section 4.3.

# 2.6 Summary

This chapter has presented an overview of the various concepts underpinning binary translation, such as code caches and transparency. It has also presented MAMBO-X64, the DBT developed by the author, which translates code from AArch32 to AArch64 with the aim of eliminating the need for AArch32 hardware support in new processors. This is made possible through the various optimization techniques implemented by MAMBO-X64, which are presented in the following chapters.

# **Chapter 3**

# Optimizing indirect branches in dynamic binary translators

In a typical program, indirect branches mainly come from three sources, as shown in Figure 3.1:

- **Branch tables** Branch tables are an efficient way to branch to many targets by using an array of code addresses in memory.

- **Function returns** Because a function may be called from many places, functions must use an indirect branch to return to their caller.

- **Function pointers** Function pointers and virtual functions are used to dispatch execution to different functions dynamically.

When generated by a compiler, each of these classes has distinctive assembly code signatures which a DBT can detect. This allows the DBT to perform specialized optimizations depending on the branch type. This chapter presents three novel techniques for translating indirect branches which handle each type of indirect branch efficiently.

```

caller:

...

BL callee ; Branch to callee and set link register

; to the address of the next instruction

...

callee:

...

BX LR ; Branch to address in link register (return)

```

#### (a) Function call and return

```

CMP R0, #3

BHI default

ADR R1, table

LDR PC, [R1, R0, LSL #2]; Compare against limit

Branch to default case if higher

Cet base address of the table

Cet

```

.word case0 .word case1 .word case2 .word case3

#### (b) Branch table

```

caller:

...

LDR RO, [R1] ; Load a pointer from [R1]

BLX RO ; Branch to address in RO and set link register

; to the address of the next instruction

...

callee:

...

BX LR ; Branch to address in link register (return)

```

#### (c) Function pointer call

Figure 3.1: Indirect branch types generated by GCC when compiling for AArch32.

The first, *hardware-assisted function returns* (Section 3.1), uses a stack of translated return addresses to predict the target of function returns, thus avoiding the need for a hash table lookup. While return address stacks have previously been used in some DBTs [HK06] to predict function returns, they have not always resulted in performance improvements due to the increased number of memory operations and poor interactions with indirect branch prediction hardware. Hardware-assisted function returns are designed to work with the return address predictor of the host processor, while also including optimizations to eliminate many return address stack operations and handle return address mispredictions efficiently.

The second, *branch table inference* (Section 3.2), is a pattern-matching algorithm to detect branch tables during translation and generate a corresponding table in the code cache. Although ad-hoc branch table detection has been explored in DBTs [PG10], the proposed inference provides a systematic way of detecting many variants of branch tables and extracting the bounds of the table directly from the source instructions instead of guessing it.

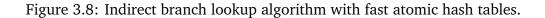

A hash table is still necessary to handle the remaining indirect branches that are not covered by the previously mentioned techniques. However, most existing hash tables used for indirect branch translation are not designed to work with multiple threads, and require either duplicating the hash table for each thread or introducing expensive synchronization mechanisms. This chapter presents *fast atomic hash tables* (Section 3.3) which take advantage of cheap 64-bit atomic loads and stores to provide a thread-shared hash table that matches the performance of single-threaded hash tables.

These techniques were implemented in MAMBO-X64 early in its development, which allowed it to reach an average performance overhead of only 10%. This overhead is measured by running a 32-bit build of SPEC CPU2006 on an ARMv8 system both natively and under MAMBO-X64, and measuring their relative performance.

In Section 3.4, these techniques are evaluated on an ARM Cortex-A57 system using the SPEC CPU2006 benchmark suite. The results show that the hardware-assisted function return optimization has the highest impact on performance, with an average overhead reduction of 40% and up to 90% on some benchmarks compared to hash table lookups. Branch table inference has a significant effect on benchmarks which make frequent use of branch tables, reducing DBT overhead by up to 40% in those benchmarks. Finally, fast atomic hash tables are shown to reduce DBT overhead by 40% compared to existing thread-shared hash table designs, also matching the performance of other indirect branch handling techniques while consuming significantly less memory.

# 3.1 Hardware-assisted function returns

Research has shown that function returns are by far the most common type of indirect branch [SKC<sup>+</sup>04]. Function returns are different from other indirect branches in that they usually target the instruction following a previously executed call instruction<sup>1</sup>. In some cases, a function may not return to the address it was called from, but this is atypical, only occurring in exceptional cases such as during stack unwinding after an exception is thrown or if the return address of a function has been modified.

Hardware-assisted function returns take advantage of this property in two ways, first by tracking the addresses of executed call instructions in a software return address stack and secondly by laying out the translated code in a way

<sup>&</sup>lt;sup>1</sup>Exceptions to this include functions which perform stack unwinding, such as with C++ exception or the C setjmp and longjmp functions.

that can take advantage of hardware return address prediction logic built into modern processors. While software return address stacks have been used previously in DBTs to optimize function returns [HK06, HH97], this technique extends them by efficiently handling stack overflows and underflows using memory protection hardware and by avoiding the return address stack entirely in certain cases (e.g. 'leaf' functions).

#### 3.1.1 Software return address stack

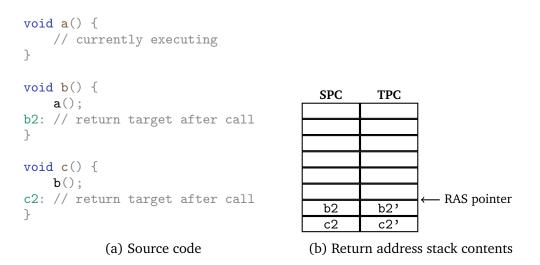

Hardware-assisted function returns work by maintaining a software *Return Address Stack* (RAS) in memory which tracks previously executed call instructions. Each thread is allocated its own RAS, and the current position in the stack is tracked by dedicated RAS pointer register. To account for the possibility of mispredicting returns, each RAS entry comprises a pair of values: the Source Program Counter (SPC) of the expected return address and its corresponding Translated Program Counter (TPC). An entry is pushed onto the RAS by a translated call instruction and an entry is popped from the RAS by a translated return instruction. The resulting RAS entries therefore mirror the call stack of the program, as shown in Figure 3.2.

Translating a call instruction is simple since all it needs to do is push the SPC and TPC of the assumed call return target, which is the instruction immediately following the call instruction. Translating a return instruction is more complicated due to the need to handle potential mispredictions, and requires four operations:

1. An entry containing a SPC and TPC pair is popped from the return address stack.

Figure 3.2: Return address stack contents while executing nested function calls.

- 2. The SPC is compared with the program-visible return address used by the return instruction.

- 3. If the values match then control branches to the TPC in the entry.

- 4. If the values do not match then control is returned to the DBT so that it can determine the target of the return by translating the SPC.

#### 3.1.2 Hardware return address prediction

Most modern processors include a return address prediction mechanism in hardware to predict the targets of function returns. This specifically detects 'call' and 'return' instructions and passes them to the branch prediction system. Unfortunately this is not used in most DBTs because code before and after the call is treated separately for translation purposes, so they might not place the target of a return immediately after the matching call instruction in the code cache, which is required to exploit the hardware predictor. Hardware-assisted function returns exploit hardware return prediction by including the return target in the same block as the call instruction. This is done by not regarding a call as the end of a basic block, thus ensuring that the return target is located immediately after the translated call instruction. Translated code can then use native call and return instructions, which take advantage of any return address predictor.

Figure 3.3 shows how a function call and return are translated in MAMBO-X64. The source BL instruction is translated into a constant move to set the source link register and a BL (call) instruction to branch to the translated function. The code takes advantage of the BL instruction to generate the TPC address in the link register. In the translated function, the source link register and translated link register are both saved to the return address stack. The BX LR (return) instruction is translated into a return address stack pop and compare. If the comparison succeeds then a RET instruction is used to branch to the translated address from the stack. The RET instruction allows the processor to use its return address predictor for this branch. Because the return address stack contains the link register value generated by the BL instruction, the processor will predict the target of the return correctly, thus avoiding any penalty from pipeline flushing in the hardware.

#### 3.1.3 Return address stack elision

Rather than pushing an entry to the RAS at the translated call instruction in the caller block, the SPC and TPC of the return target are passed to the callee block in registers. The SPC is passed in the application-visible link register for the source architecture (R14 on AArch32), while the TPC is passed in the link register for the host architecture (X30 on AArch64). This TPC value is hidden

```

orig_caller:

BL function ; branch and set LR

orig_ret_target:

... ; rest of code

orig_function:

... ; contents of function

BX LR ; return using LR (R14)

```

#### (a) Original AArch32 code

| translated_caller:            |   |                      |

|-------------------------------|---|----------------------|

| MOV W14, #orig_ret_target     | ; | calculate return SPC |

| BL translated_function        | ; | branch and set TPC   |

| translated_ret_target:        |   |                      |

|                               | ; | rest of code         |

|                               |   |                      |

| translated_function:          |   |                      |

| STP X14, LR, [ras_ptr], #16   | , | push SPC and TPC     |

| • • •                         | ; | contents of function |

|                               | ; | possibly spread over |

|                               | ; | multiple blocks      |

| LDP X16, LR, [ras_ptr, #-16]! | ; | pop SPC and TPC      |

| SUB W16, W16, W14             | ; | compare SPC with LR  |

| CBNZ W16, return_mispredict   | ; | handle mispredicts   |

| RET LR                        | ; | return using TPC     |

|                               |   |                      |

#### (b) Translated AArch64 code

Figure 3.3: Translated function call and return in MAMBO-X64. ras\_ptr is a register that holds the return address stack pointer, X16 is a scratch register and W14 contains the AArch32 link register.

from the target application and remains valid as long as the application link register is not modified.

The relationship between these two values is broken when the application link register is modified, either by explicitly overwriting the link register with a different value or implicitly through a call instruction which overwrites this register. In this situation, the SPC and TPC pair needs to be pushed to the RAS just before the register holding the SPC is modified. When a function returns by performing an indirect branch to the address in the source link register, a RAS pop can be avoided if the link register is known to not have been modified since the last executed call instruction. In this situation the host link register already contains the correct TPC address to return to and can be branched to directly.

Consider, as an example, the code in Figure 3.4 which consists of a function with two execution paths. In the first path, the source link register is not modified, which means that a function return in this execution path can be translated to a single branch to the address contained in the host link register, effectively matching the performance of a native function return. This can be done blindly since the DBT statically knows that the host link register holds the TPC for the source link register SPC value. In the second path, the relationship between the source and host link registers is broken when the source link register is modified by a subroutine call, which means that these values need to be preserved in the RAS rather than in registers.

The relationship between the host and source link registers is maintained across block boundaries by creating two variants of every block: a *normal* variant and a *callee* variant. The latter variant has the property that, on entry, both registers will contain valid values. Each variant is generated on demand since in practice most blocks only ever use a single variant: for the SPEC2006 bench-

```

function1-callee:

CBZ WO, ret-callee

(*)

STR W14, [X13, #-4]!

(*)

STP X14, LR, [ras_ptr], #16

(*)

MOV W14, #return_target

BL function2-callee

function1:

LDR W14, [X13], #4

LDP X16, LR, [ras_ptr, #-16]!

CMP R0, #0

; if RO == 0

BEQ RO, ret ; skip the call

SUB W16, W16, W14

CBNZ W16, return_mispredict

PUSH {LR}

; save link reg

B ret-normal

BL function2 ; call function2

POP {LR} ; restore link reg

ret-normal:

B ret

; branch to end

RET LR

ret:

ret-callee:

BX LR

; return to caller

RET LR

(*)

function2:

function2-callee:

BX LR

(*)

; return to caller

RET LR

```

(a) Original AArch32 code

(b) Translated AArch64 code

Figure 3.4: Example code showing RAS elision in MAMBO-X64. For instructions marked with (\*), W14 contains the return target SPC and LR contains the return target TPC. This property is preserved across branches by making them target callee blocks instead of normal blocks, but is lost when the AArch32 link register (W14) is modified, such as by the BL instruction, at which point the SPC and TPC values must be saved to the RAS.

marks, on average only 1.5 % of all blocks needed to have both a normal and callee variant generated.

Three rules determine which variant of a block is targeted when a branch instruction is translated:

- 1. If the instruction is a call then it will always target a callee variant.

- 2. If the instruction is a non-call branch, the block containing the branch is a callee variant and the source link register has not been modified since the start of the block then the branch will target a callee variant.

- 3. In all other cases, the branch will target a normal variant.

For indirect branches, two separate hash tables are used, one for normal variants and one for callee variants. Although the target address of an indirect branch can't be determined at translation time, the target variant can be determined because indirect calls (BLX on AArch32) can be distinguished from other indirect branch types. The indirect branch is then translated to use one of the two hash tables depending on the variant which needs to be targeted.

# 3.1.4 Overflow and underflow handling

Because the RAS is allocated as a block of memory of fixed size, it can *overflow* it if a function call is executed when the stack is full. Similarly, it is possible to *underflow* the RAS by attempting to return from a function when the RAS is empty. The former usually occurs when searching through a deep tree structure recursively, while the latter usually occurs when returning from such recursion. A DBT must handle both of these situations to maintain transparency since they could otherwise potentially result in incorrect code execution.

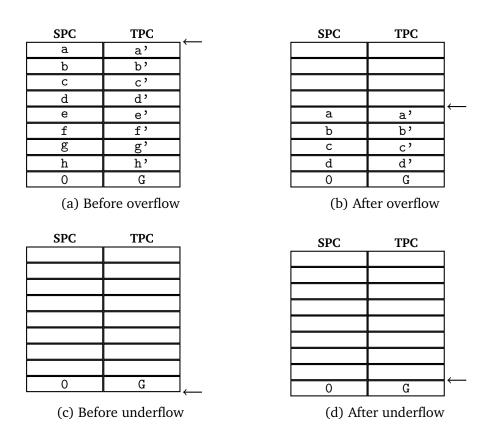

Many RAS implementations handle overflows and underflows by adding bound-checking instructions to the RAS push and pop operations, but this comes at a significant cost due to the additional instructions required multiplied by the high frequency of calls and returns in many programs. A better approach is to use memory protection hardware to trap overflows by allocating a *guard page* at the end of the RAS. Underflows are caught using a *guard entry* that is reserved at the bottom of the stack. Figure 3.5 shows an example of how RAS overflows and underflow are handled.

When the RAS is full and a push is attempted, the write to the guard page will trigger a page fault. The fault handler will shift the RAS contents down: the top half of the stack is copied to the bottom half and the RAS pointer register is adjusted to point to the new top of the stack. Although this discards the bottom half of the RAS entries, which are the least recently used, correct execution is not affected because the RAS is only used as a prediction mechanism. After the stack contents are moved, the push instruction is restarted with the adjusted RAS pointer, which will cause it to push a value into the newly freed space successfully.

To catch underflows, a guard entry is reserved at the bottom of the RAS. This entry contains an SPC address of 0 and a TPC address pointing to a stub that returns to the DBT, so that control returns to the DBT to handle the unlikely event of a return instruction jumping to address zero due to a software error correctly. Once control is returned to the DBT, the current RAS pointer is checked and adjusted to ensure that it always points above the guard entry. A misprediction is unavoidable at this point because there is no prediction information available in the RAS.

#### 3.1.5 Misprediction handling

There are two reasons that can cause a function return to be mispredicted: either the function did not return to its matching call instruction or the pre-

Figure 3.5: Overflow and underflow handling for the return address stack. On overflow, the contents of the RAS are shifted down, the RAS pointer is adjusted and the push instruction is restarted. On underflow the RAS pointer is moved above the guard entry so that the guard is not overwritten by a later push, and the misprediction is handled by the DBT.

dicted return address was lost due to a RAS overflow and subsequent underflow. These situations can be discerned by checking whether the entry that was just popped from the RAS is the guard entry. Since these situations have different causes, they are best handled separately.

**Return misprediction** A genuine return misprediction can occur for a variety of reasons, such as stack unwinding when an exception is thrown, calling the C longjmp function, switching stacks when invoking a coroutine or simply having a function modify its return address. In many of these cases, program execution will continue normally at an earlier point in the call stack, so it is beneficial to avoid further mispredictions by *unwinding* the RAS to an earlier point. Unwinding is done by scanning the RAS from the top down until an entry matching the current SPC return target is found, and adjusting the RAS pointer to remove that entry and all others above it from the RAS. If a matching entry could not be found then the RAS is left unmodified so that its contents are still available for a later attempt at unwinding.

**RAS underflow** A misprediction due to a RAS underflow can occur when the call depth of a program exceeds the size of the RAS, causing the RAS to overflow and lose some entries. This is more common than genuine mispredictions and can happen in algorithms which make heavy use of recursion, such as when searching through a very deep tree structure. In this situation it is possible to take advantage of the fact that these algorithms tend to only call a limited set of functions recursively: a small hash table is used to predict these function returns, which contains SPC and TPC addresses of returns that were previously mispredicted due to a RAS underflow. The hash table allows function returns to be predicted even when the relevant return address stack entry has been lost due to an overflow. This fallback avoids the need to perform an expensive context switch back to the DBT, which can cost hundreds of cycles.

Note that while a return address misprediction can affect program performance, it will never lead to incorrect code execution. This is guaranteed by always tracking the SPC address for each predicted TPC return address and checking that it matches the intended return target.

#### 3.1.6 Unlinking

Hardware-assisted function returns have been designed to work in a *thread-shared code cache* model [BKGB06, HLC09] where the same translated code is shared among multiple threads because this model has been shown to scale significantly better than thread-private code caches. One complication with this model is that block invalidation is more complicated: a block which needs to be deleted because its source assembly instructions have been modified may still have other threads concurrently executing it. This is solved by using *lazy deletion*: all incoming links to the block are removed so that is becomes unreachable and it is freed once all live threads have returned to the DBT at least once since the block was unlinked since this indicates that other threads can no longer be executing the deleted fragment.