# EXPLOITING CONCURRENCY IN A GENERAL-PURPOSE ONE-INSTRUCTION COMPUTER ARCHITECTURE

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Engineering and Physical Sciences

2010

By Christopher Daniel Emmons School of Computer Science

# Contents

| A            | Abstract |                       |                                        |    |  |  |

|--------------|----------|-----------------------|----------------------------------------|----|--|--|

| D            | eclar    | ation                 |                                        | 15 |  |  |

| C            | opyri    | $\operatorname{ight}$ |                                        | 16 |  |  |

| A            | ckno     | wledge                | ements                                 | 17 |  |  |

| $\mathbf{T}$ | he aı    | ıthor                 |                                        | 18 |  |  |

| Ι            | In       | trodu                 | ction and background                   | 19 |  |  |

| 1            | Inti     | coduct                | ion                                    | 20 |  |  |

|              | 1.1      | Motiv                 | ation                                  | 20 |  |  |

|              | 1.2      | Resea                 | rch objectives                         | 21 |  |  |

|              | 1.3      | Resea                 | rch contributions                      | 23 |  |  |

|              | 1.4      | Thesis                | s structure                            | 24 |  |  |

| <b>2</b>     | Ger      | ieral-p               | ourpose computer architecture          | 25 |  |  |

|              | 2.1      | Gener                 | al-purpose computer requirements       | 25 |  |  |

|              | 2.2      | Challe                | enges in computer architecture         | 26 |  |  |

|              |          | 2.2.1                 | Design complexity and productivity gap | 26 |  |  |

|              |          | 2.2.2                 | Power consumption                      | 27 |  |  |

|              |          | 2.2.3                 | Processor and memory performance gap   | 28 |  |  |

|              |          | 2.2.4                 | Cost of communication                  | 29 |  |  |

|              | 2.3      | Resea                 | rch directions                         | 30 |  |  |

|              |          | 2.3.1                 | Exploiting parallelism                 | 30 |  |  |

|              |          | 2.3.2                 | Increasing cache sizes                 | 35 |  |  |

|   |     | 2.3.3  | Designing at higher levels of abstraction | 35 |

|---|-----|--------|-------------------------------------------|----|

|   |     | 2.3.4  | Communication-centric architectures       | 36 |

|   | 2.4 | Conclu | usion                                     | 37 |

| 3 | The | Fleet  | architecture                              | 38 |

|   | 3.1 | Archit | tecture overview                          | 38 |

|   | 3.2 | Instru | ction set architecture                    | 39 |

|   |     | 3.2.1  | Native hardware data types                | 39 |

|   |     | 3.2.2  | One instruction                           | 40 |

|   |     | 3.2.3  | Code bags                                 | 43 |

|   |     | 3.2.4  | A simple Fleet program                    | 44 |

|   | 3.3 | Concu  | Irrency                                   | 45 |

|   | 3.4 | Hardw  | vare organization                         | 45 |

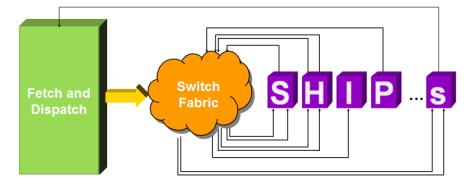

|   |     | 3.4.1  | Instruction fetch and dispatch            | 45 |

|   |     | 3.4.2  | Switch fabric                             | 46 |

|   |     | 3.4.3  | Ships                                     | 46 |

|   | 3.5 | Early  | findings                                  | 46 |

|   | 3.6 | Limita | ations                                    | 47 |

|   | 3.7 | Conclu | usion                                     | 47 |

|   |     |        |                                           |    |

## II The Armada architecture

| 4 | The | Arma    | ada architecture             | 50 |

|---|-----|---------|------------------------------|----|

|   | 4.1 | Differe | ences from Fleet             | 50 |

|   | 4.2 | Archit  | tecture enhancements         | 53 |

|   |     | 4.2.1   | Independent code bags        | 53 |

|   |     | 4.2.2   | Enhanced local register file | 54 |

|   |     | 4.2.3   | Context synchronizers        | 55 |

|   |     | 4.2.4   | Flow caching                 | 55 |

|   | 4.3 | Instru  | ction set architecture       | 56 |

|   |     | 4.3.1   | Memory model                 | 56 |

|   |     | 4.3.2   | One instruction              | 56 |

|   |     | 4.3.3   | Choosing the code bag type   | 58 |

|   |     | 4.3.4   | Fetching code bags           | 60 |

|   |     | 4.3.5   | Freeing Fleet cores          | 66 |

**49**

|          |     | 4.3.6   | Virtual pipelines                                                                                             | 3 |

|----------|-----|---------|---------------------------------------------------------------------------------------------------------------|---|

|          |     | 4.3.7   | Handling state in Ships                                                                                       | 3 |

|          |     | 4.3.8   | Context synchronizers                                                                                         | 9 |

|          |     | 4.3.9   | Flow caching                                                                                                  | ) |

|          |     | 4.3.10  | Hardware reset behavior                                                                                       | 2 |

|          |     | 4.3.11  | Event handling                                                                                                | 3 |

|          |     | 4.3.12  | Fleet prototype core ISA                                                                                      | 3 |

|          | 4.4 | Relate  | d work $\ldots \ldots 74$ | 4 |

|          |     | 4.4.1   | Transport-triggered architectures                                                                             | 1 |

|          |     | 4.4.2   | Dataflow machines                                                                                             | 4 |

|          |     | 4.4.3   | WaveScalar architecture                                                                                       | 5 |

|          |     | 4.4.4   | Independence architectures                                                                                    | 5 |

|          |     | 4.4.5   | SCALP and Vortex asynchronous processors                                                                      | 3 |

|          |     | 4.4.6   | TRIPS architecture                                                                                            | 3 |

|          |     | 4.4.7   | Fleet at Sun Microsystems and U.C. Berkeley                                                                   | 7 |

|          | 4.5 | Conclu  | 1sion                                                                                                         | 7 |

| <b>5</b> | The | Arma    | da-1 microarchitecture 78                                                                                     | 3 |

|          | 5.1 |         | ew                                                                                                            |   |

|          | 5.2 |         | ry subsystem                                                                                                  | 3 |

|          | 5.3 |         | rores                                                                                                         |   |

|          |     | 5.3.1   | Simultaneous multithreading                                                                                   | 9 |

|          |     | 5.3.2   | Data size                                                                                                     | ) |

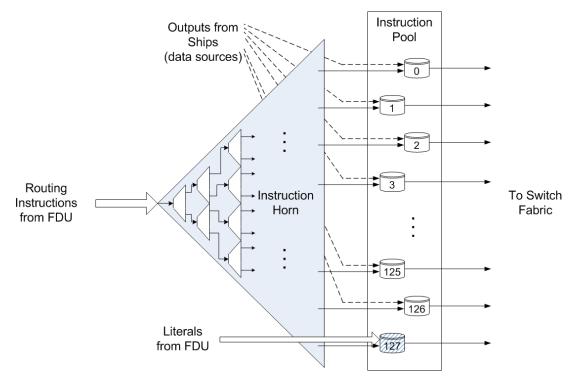

|          |     | 5.3.3   | Instruction horn                                                                                              | 1 |

|          |     | 5.3.4   | Instruction pool and reservation stations                                                                     | 1 |

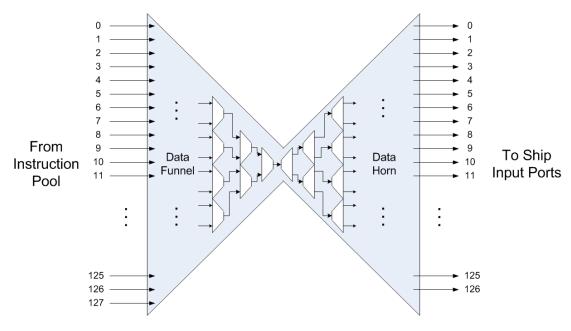

|          |     | 5.3.5   | Switch fabric                                                                                                 | 2 |

|          |     | 5.3.6   | Ships                                                                                                         | 3 |

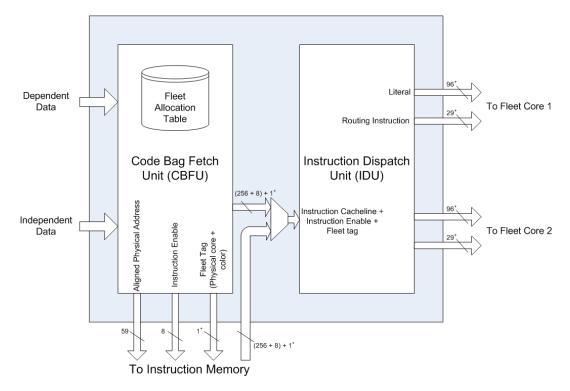

|          | 5.4 | Fetch a | and dispatch unit                                                                                             | 4 |

|          |     | 5.4.1   | Code bag fetch unit                                                                                           | 4 |

|          |     | 5.4.2   | Instruction dispatch unit                                                                                     | 7 |

|          | 5.5 | Contex  | ct synchronizers                                                                                              | 3 |

|          | 5.6 |         | unication                                                                                                     | 3 |

|          | 5.7 | Conclu  | nsion                                                                                                         | 3 |

| 6        | Eva | luation | n of Armada-1 90                                                                                              | ) |

|          | 6.1 |         | laSim                                                                                                         |   |

|          |     |         |                                                                                                               |   |

|      | 6.1.1 Structural configuration                                                                                                                | <br>• | 90          |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|

|      | 6.1.2 Timing model $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                    |       | 91          |

|      | 6.1.3 Statistics gathering                                                                                                                    |       | 91          |

|      | 6.1.4 Fleet state checker $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                  |       | 91          |

|      | 6.1.5 Value-change dump output                                                                                                                |       | 92          |

|      | $6.1.6  \text{Verification}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                 |       | 92          |

|      | 6.1.7 Design complexity $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                    |       | 93          |

|      | 6.1.8 Limitations                                                                                                                             |       | 94          |

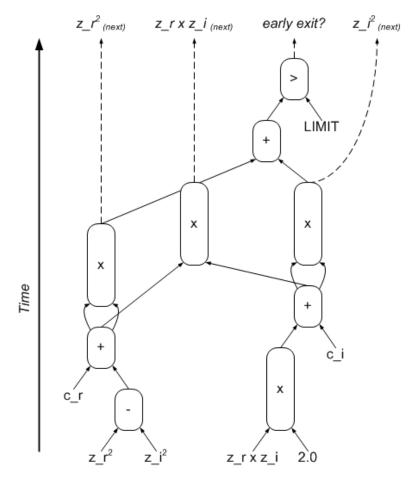

| 6.2  | Mandelbrot                                                                                                                                    |       | 94          |

|      | $6.2.1  \text{Computation}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                  |       | 94          |

|      | $6.2.2  \text{Parallelism} \dots \dots$ |       | 95          |

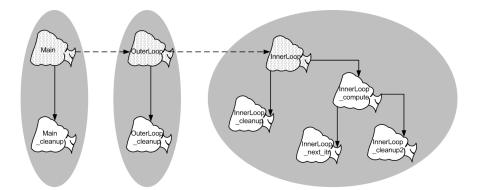

|      | 6.2.3 Mapping to Armada                                                                                                                       |       | 98          |

| 6.3  | Conclusion                                                                                                                                    |       | 101         |

| 7 Mi | croarchitecture results and discussion                                                                                                        |       | 102         |

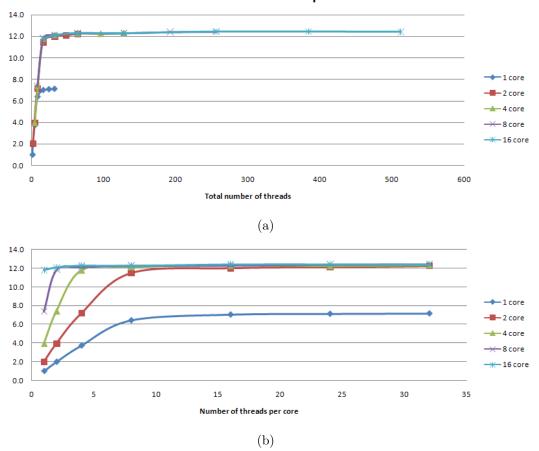

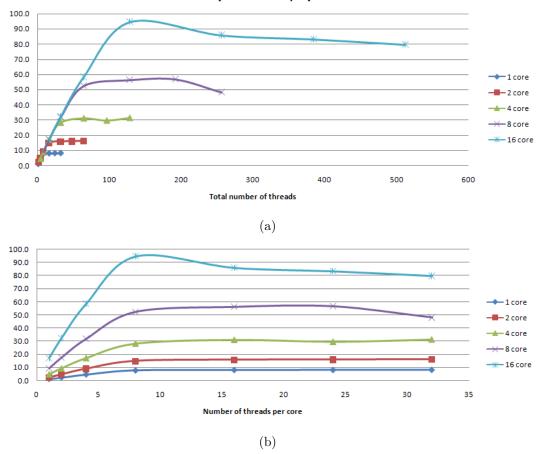

| 7.1  | Performance overview                                                                                                                          |       | 102         |

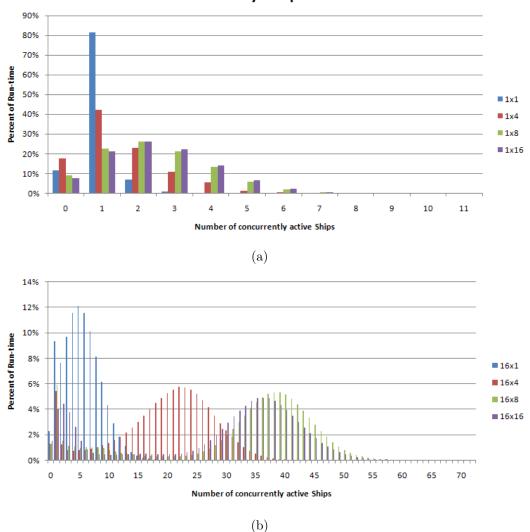

| 7.2  | Exploiting concurrency                                                                                                                        |       | 106         |

|      | 7.2.1 Instruction-level concurrency                                                                                                           |       | 106         |

|      | 7.2.2 Thread-level concurrency                                                                                                                |       | 108         |

| 7.3  | Code density                                                                                                                                  |       | 108         |

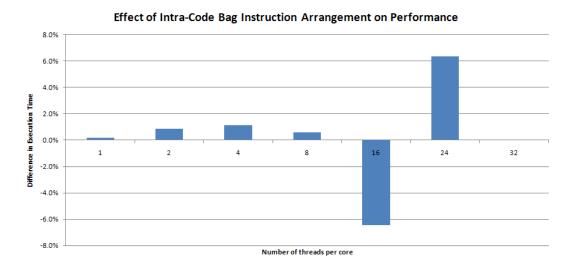

| 7.4  | Code bag organization                                                                                                                         |       | 109         |

| 7.5  | Asynchronous system performance                                                                                                               |       | 110         |

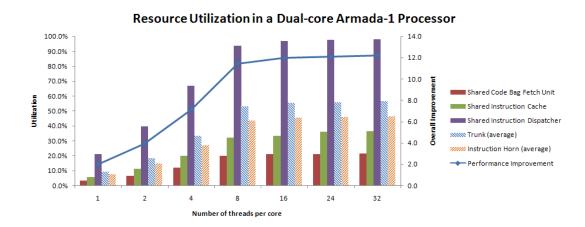

| 7.6  | Resource multiplexing                                                                                                                         |       | 111         |

| 7.7  | Conclusion                                                                                                                                    |       | 111         |

|      |                                                                                                                                               |       |             |

| III  | An Armada compiler                                                                                                                            |       | 113         |

| 8 Ar | mada Procedure Call Standard                                                                                                                  |       | <b>11</b> 4 |

| 8.1  | Overview                                                                                                                                      |       | 114         |

| 8.2  | Register file                                                                                                                                 |       | 115         |

|      | 8.2.1 Behavior                                                                                                                                |       | 115         |

|      | 8.2.2 Listing                                                                                                                                 |       | 115         |

|     | 8.2.1 | Behavior                       |

|-----|-------|--------------------------------|

|     | 8.2.2 | Listing                        |

| 8.3 | Stack |                                |

|     | 8.3.1 | Allocation policy 116          |

|     | 8.3.2 | Choosing the allocation policy |

|    | 8.4  | Data p  | placement                                                                                                                                        | 118 |

|----|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    |      | 8.4.1   | Argument passing                                                                                                                                 | 118 |

|    |      | 8.4.2   | Automatic variables                                                                                                                              | 120 |

|    |      | 8.4.3   | Return values                                                                                                                                    | 121 |

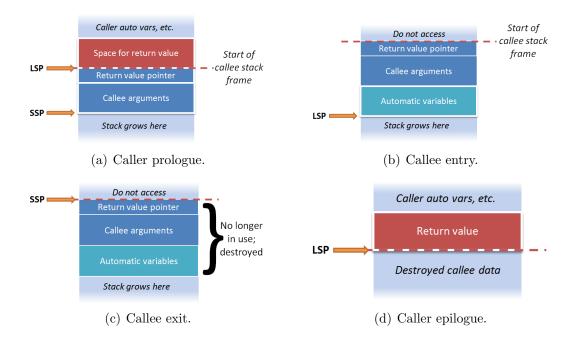

|    | 8.5  | Proced  | lure calls                                                                                                                                       | 121 |

|    |      | 8.5.1   | Serial procedure calls $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                   | 121 |

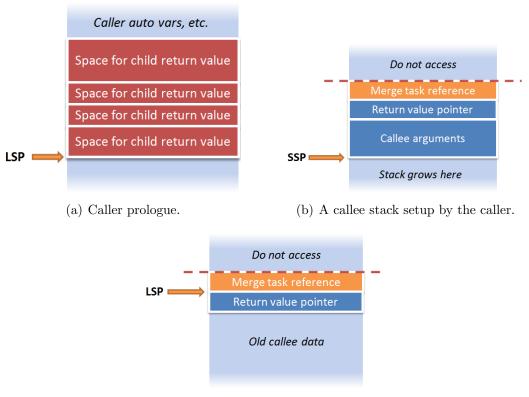

|    |      | 8.5.2   | Concurrent procedure calls                                                                                                                       | 122 |

|    | 8.6  | Conclu  | $sion \ldots \ldots$      | 126 |

| 9  | Con  | npiling | for Armada                                                                                                                                       | 127 |

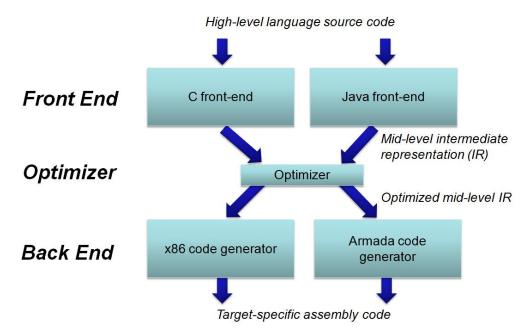

|    | 9.1  | Moder   | n optimizing compilers                                                                                                                           | 127 |

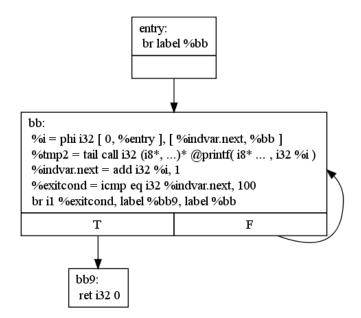

|    | 9.2  | LLVM    | IR                                                                                                                                               | 128 |

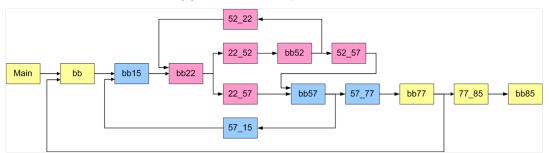

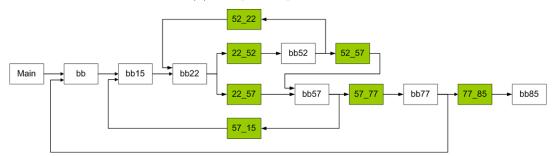

|    |      | 9.2.1   | Basic blocks                                                                                                                                     | 129 |

|    |      | 9.2.2   | Instructions                                                                                                                                     | 129 |

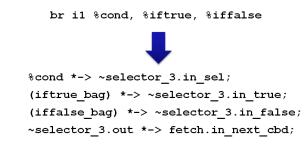

|    | 9.3  | Armad   | la code generator                                                                                                                                | 132 |

|    |      | 9.3.1   | Data types                                                                                                                                       | 132 |

|    |      | 9.3.2   | Pre-processing                                                                                                                                   | 133 |

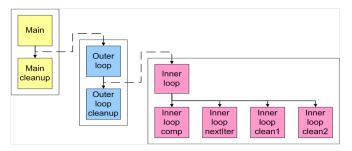

|    |      | 9.3.3   | Code bag formation                                                                                                                               | 135 |

|    |      | 9.3.4   | Ship type and instruction selection                                                                                                              | 137 |

|    |      | 9.3.5   | Instruction merging                                                                                                                              | 137 |

|    |      | 9.3.6   | Instruction splitting                                                                                                                            | 138 |

|    |      | 9.3.7   | Stray token cleanup                                                                                                                              | 138 |

|    |      | 9.3.8   | Ship allocation                                                                                                                                  | 140 |

|    | 9.4  | Assem   | bler                                                                                                                                             | 141 |

|    | 9.5  | Limita  | tions                                                                                                                                            | 141 |

|    | 9.6  | Conclu  | $sion \ldots \ldots$      | 142 |

| 10 | Arm  | nadaSir | m debugger                                                                                                                                       | 143 |

|    | 10.1 | Trace 1 | replay                                                                                                                                           | 143 |

|    | 10.2 | Messag  | ge view                                                                                                                                          | 143 |

|    | 10.3 | Source  | $code view \ldots \ldots$ | 144 |

|    | 10.4 | State t | racking view                                                                                                                                     | 145 |

|    | 10.5 | Limita  | tions $\ldots$                                                  | 147 |

|    | 10.6 | Conclu  | $sion \ldots \ldots$      | 148 |

| 11 Testing the Armada  | compiler                                   | 149   |

|------------------------|--------------------------------------------|-------|

| 11.1 Objectives        |                                            | . 149 |

| 11.2 Method and metric | cs                                         | . 149 |

| 11.2.1 Code struct     | ture                                       | . 150 |

| 11.2.2 Code densit     | ty                                         | . 150 |

| 11.2.3 Instructions    | s fetched                                  | . 150 |

| 11.2.4 Instructions    | s executed                                 | . 151 |

| 11.2.5 Instruction     | traffic                                    | . 151 |

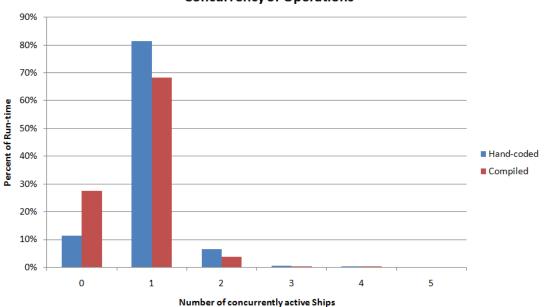

| 11.2.6 Concurrenc      | 29                                         | . 151 |

| 11.3 Results           |                                            | . 152 |

| 11.3.1 Performanc      | ce                                         | . 152 |

| 11.3.2 Code struct     | ture                                       | . 153 |

| 11.3.3 Code densit     | ty                                         | . 153 |

| 11.3.4 Instructions    | s fetched and instruction traffic          | . 155 |

| 11.3.5 Instructions    | s executed                                 | . 155 |

| 11.3.6 Concurrenc      | xy                                         | . 156 |

|                        | ·<br>· · · · · · · · · · · · · · · · · · · |       |

### IV Discussion and conclusion

| 12 Discussion and conclusion                                                                                 | 159 |

|--------------------------------------------------------------------------------------------------------------|-----|

| 12.1 Fleet changes $\ldots$ | 160 |

| 12.2 Architecture enhancements                                                                               | 160 |

| 12.2.1 Proposed extensions and motivating factors $\ldots \ldots \ldots$                                     | 160 |

| 12.2.2 Conclusions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                   | 161 |

| 12.3 Compiler and tools $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$              | 162 |

| 12.4 Limitations of described work                                                                           | 163 |

| 12.4.1 Few benchmarks $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                         | 163 |

| 12.4.2 Performance comparison to modern architectures $\ldots$ $\ldots$                                      | 163 |

| 12.4.3 Compiler maturity $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                    | 163 |

| 12.5 Areas for future work                                                                                   | 163 |

| 12.5.1 Memory subsystem $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$              | 164 |

| 12.5.2 Higher granularity Ship functionality                                                                 | 164 |

| 12.5.3~ Armada as an application-specific processor architecture $~$ .                                       | 164 |

| 12.5.4 Flow-control fabric                                                                                   | 164 |

158

|              |       | 12.5.5 Flow caching          | 165 |

|--------------|-------|------------------------------|-----|

|              |       | 12.5.6 Compiler enhancements | 165 |

|              | 12.6  | Final remarks                | 165 |

| Bi           | bliog | raphy 1                      | .66 |

| $\mathbf{A}$ | Ship  | os in Armada-1 1             | .73 |

|              | A.1   | Register                     | 173 |

|              | A.2   | IntAdd64                     | 173 |

|              | A.3   | IntDiv64                     | 174 |

|              | A.4   | IntMul64                     | 174 |

|              | A.5   | FPAdd64                      | 174 |

|              | A.6   | FPDiv64                      | 175 |

|              | A.7   | FPMul64                      | 175 |

|              | A.8   | BitShift                     | 175 |

|              | A.9   | BitOp                        | 176 |

|              | A.10  | IntToFP                      | 176 |

|              | A.11  | SExt                         | 177 |

|              | A.12  | Counter                      | 177 |

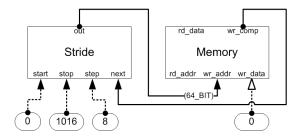

|              | A.13  | Stride                       | 177 |

|              | A.14  | Cmp                          | 178 |

|              | A.15  | Join                         | 179 |

|              | A.16  | Selector                     | 179 |

|              | A.17  | Toggle                       | 179 |

|              | A.18  | Fetch                        | 180 |

|              | A.19  | Memory                       | 180 |

|              | A.20  | ContextSynchronizer          | 181 |

|              | A.21  | Stack                        | 181 |

| Б            | TT    | 1 / 1 11 / 1                 | 0.0 |

| В            |       |                              | .83 |

|              | B.1   |                              | 183 |

|              | B.2   | 8 8                          | 184 |

|              | B.3   |                              | 185 |

|              | B.4   |                              | 185 |

|              | B.5   | Testing                      | 185 |

| $\mathbf{C}$ | Cod | le listings                     | 186 |

|--------------|-----|---------------------------------|-----|

|              | C.1 | Mandelbrot, hand-coded          | 186 |

|              | C.2 | Mandelbrot, LLVM-generated      | 189 |

| D            | LLV | M instruction mapping to Armada | 196 |

|              |     |                                 | 196 |

|              |     | D.1.1 ret                       | 196 |

|              |     | D.1.2 br                        | 196 |

|              |     | D.1.3 switch                    | 197 |

|              |     | D.1.4 invoke                    | 197 |

|              |     | D.1.5 unwind                    | 197 |

|              |     | D.1.6 unreachable               | 197 |

|              | D.2 | Binary class                    | 197 |

|              |     | D.2.1 add                       | 197 |

|              |     | D.2.2 sub                       | 197 |

|              |     | D.2.3 mul                       | 198 |

|              |     | D.2.4 udiv                      | 198 |

|              |     | D.2.5 sdiv                      | 198 |

|              |     | D.2.6 fdiv                      | 198 |

|              |     | D.2.7 urem                      | 199 |

|              |     | D.2.8 srem                      | 199 |

|              |     | D.2.9 frem                      | 199 |

|              | D.3 | Bitwise binary class            | 199 |

|              |     | D.3.1 shl                       | 199 |

|              |     | D.3.2 lshr                      | 200 |

|              |     | D.3.3 ashr                      | 200 |

|              |     | D.3.4 and                       | 200 |

|              |     | D.3.5 or                        | 200 |

|              |     | D.3.6 xor                       | 201 |

|              | D.4 | Vector class                    | 201 |

|              |     | D.4.1 extractelement            | 201 |

|              |     | D.4.2 insertelement             | 201 |

|              |     | D.4.3 shufflevector             | 201 |

|              | D.5 | Memory class                    | 201 |

|              |     | D.5.1 malloc                    | 201 |

|              |     | D.5.2 free                      | 201 |

|     | D.5.3  | alloca                                                                                                | 202 |

|-----|--------|-------------------------------------------------------------------------------------------------------|-----|

|     | D.5.4  | load                                                                                                  | 202 |

|     | D.5.5  | store                                                                                                 | 202 |

|     | D.5.6  | getelementptr                                                                                         | 202 |

| D.6 | Conve  | rsion class $\ldots$ | 203 |

|     | D.6.1  | trunc to                                                                                              | 203 |

|     | D.6.2  | sext to                                                                                               | 203 |

|     | D.6.3  | zext to                                                                                               | 203 |

|     | D.6.4  | fptrunc to                                                                                            | 203 |

|     | D.6.5  | fpext to                                                                                              | 203 |

|     | D.6.6  | fptoui to                                                                                             | 203 |

|     | D.6.7  | fptosi to                                                                                             | 203 |

|     | D.6.8  | uitofp to                                                                                             | 204 |

|     | D.6.9  | sitofp to                                                                                             | 204 |

|     | D.6.10 | ptrtoint to                                                                                           | 204 |

|     | D.6.11 | inttoptr to                                                                                           | 204 |

|     | D.6.12 | bitcast to                                                                                            | 204 |

| D.7 | Miscel | laneous class                                                                                         | 204 |

|     | D.7.1  | icmp                                                                                                  | 204 |

|     | D.7.2  | fcmp                                                                                                  | 205 |

|     | D.7.3  | phi                                                                                                   | 205 |

|     | D.7.4  | select                                                                                                | 205 |

|     | D.7.5  | call                                                                                                  | 205 |

|     | D.7.6  | $va_arg$                                                                                              | 205 |

|     | D.7.7  | getresult                                                                                             | 205 |

# List of Tables

| 3.1  | Fleet native data types                                 |

|------|---------------------------------------------------------|

| 3.2  | Comparison of Fleet and RISC instructions               |

| 3.3  | Move instruction syntax and graphical representation 41 |

| 4.1  | Code bag comparison                                     |

| 4.2  | Code bag descriptor syntax and representation 61        |

| 7.1  | Code size and instruction fetch traffic comparison 109  |

| 8.1  | Armada-1 register file listing                          |

| 9.1  | LLVM instruction classes                                |

| 11.1 | Hand-coded versus compiled Mandelbrot                   |

| 11.2 | Mandelbrot comparison on various ISA's                  |

| A.1  | Cmp Ship in_op input port values                        |

# List of Figures

| 2.1 | Design complexity and productivity gap                 |

|-----|--------------------------------------------------------|

| 2.2 | Memory and CPU performance gap                         |

| 2.3 | Cache size versus performance in Itanium2              |

| 3.1 | Sum of squares Fleet code snippet                      |

| 3.2 | Fleet architecture organization                        |

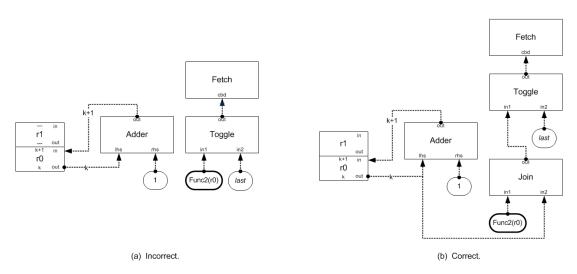

| 4.1 | Gating fetch of a successor code bag on token cleanup  |

| 4.2 | Move instruction encoding overview                     |

| 4.3 | Code bag descriptor format                             |

| 4.4 | Register forwarding example                            |

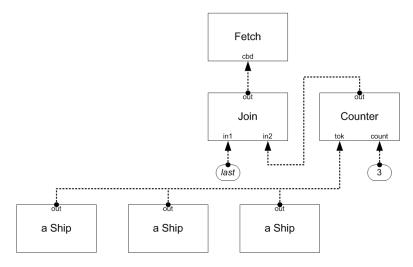

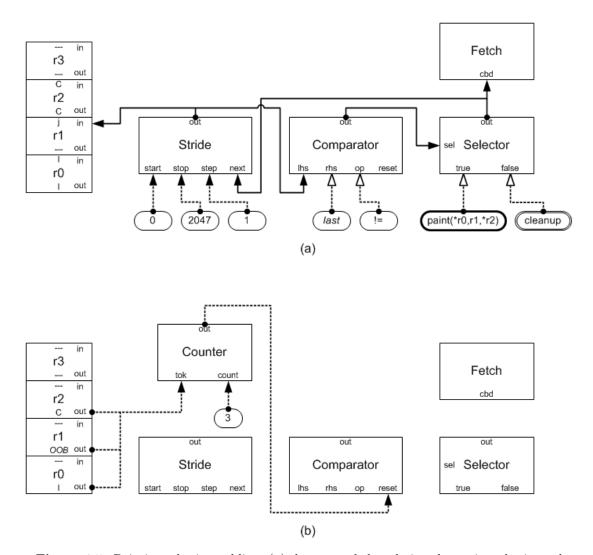

| 4.5 | Painting a horizontal line example                     |

| 4.6 | Virtual pipeline example                               |

| 4.7 | Color conversion cacheable flow                        |

| 4.8 | Color conversion cleanup code                          |

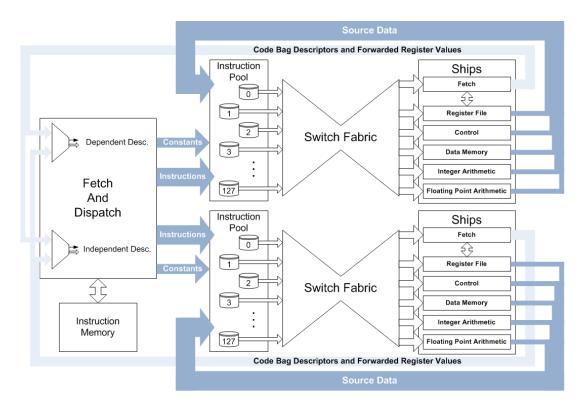

| 5.1 | Block diagram of a dual-core Armada-1 processor        |

| 5.2 | Instruction horn and pool                              |

| 5.3 | Switch fabric                                          |

| 5.4 | Fetch and dispatch unit                                |

| 6.1 | Mandelbrot benchmark inner loops in Java               |

| 6.2 | Mandelbrot inner loop operations                       |

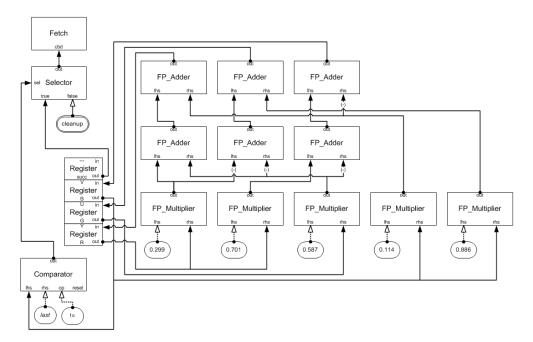

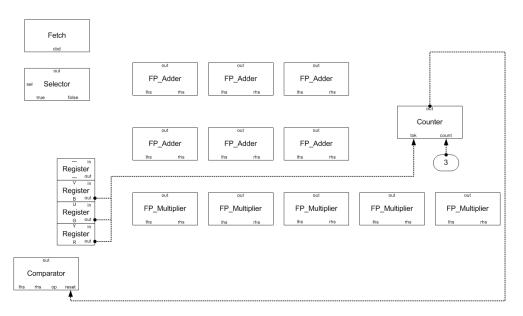

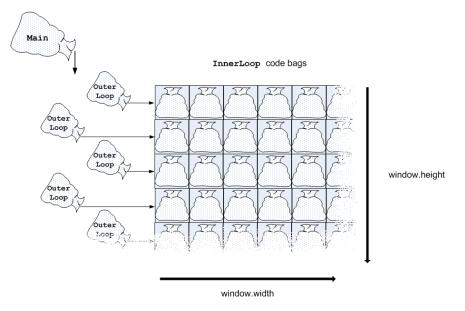

| 6.3 | Mandelbrot code bags 98                                |

| 6.4 | Mandelbrot code bag fetch scheme                       |

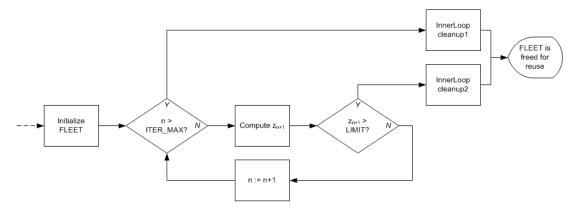

| 6.5 | InnerLoop control flow                                 |

| 7.1 | Overview of Mandelbrot performance on Armada-1 103     |

| 7.2 | Resource utilization of performance-limiting units 104 |

| 7.3  | Mandelbrot performance on optimized Armada-1                                      | 105 |

|------|-----------------------------------------------------------------------------------|-----|

| 7.4  | Concurrently active Ships in Armada-1, Mandelbrot                                 | 107 |

| 7.5  | Effect of code bag instruction arrangement on performance                         | 110 |

| 8.1  | Argument passing example with native and aggregate types                          | 119 |

| 8.2  | Stack layout for a serial procedure call $\ldots \ldots \ldots \ldots \ldots$     | 123 |

| 8.3  | Stack layout for a concurrent procedure call                                      | 125 |

| 9.1  | Modern optimizing compiler architecture                                           | 128 |

| 9.2  | Control flow graph of a simple LLVM loop                                          | 131 |

| 9.3  | LLVM add and store instructions                                                   | 131 |

| 9.4  | Translation of an LLVM branch to Armada move instructions                         | 137 |

| 10.1 | ArmadaSim Debugger messages view                                                  | 144 |

| 10.2 | Debugging multiple threads                                                        | 145 |

| 10.3 | Stepping through a program                                                        | 146 |

| 10.4 | Tracking Fleet state                                                              | 147 |

| 11.1 | Hand-coded and compiled Mandelbrot                                                | 154 |

| 11.2 | ILC comparison between hand-coded and compiled Mandelbrot $% \mathcal{A}^{(n)}$ . | 156 |

| B.1  | Hardware stack allocation scheme                                                  | 184 |

## Abstract

The University of Manchester Christopher Daniel Emmons Doctor of Philosophy Exploiting Concurrency in a General-Purpose One-Instruction Computer Architecture December 2009

Computer performance is suffering greatly from diminishing returns as the increasing cost of implementing complex hardware optimizations and of increasing clock frequency no longer yields the gains in computational ability and power efficiency consumers demand. Notable products including a generation of Intel Pentium 4 processors have been cancelled as a result. This sudden hiccup in an historically predictable performance road map has inspired research and industrial communities to investigate architectures, some rather unorthodox, that complete work more quickly and more efficiently.

One such computer architecture under development, Fleet, exposes fine-grain instruction level concurrency, addresses the growing costs of on-chip communications, and promotes simplicity in the underlying hardware design. This one-instruction computer transports data using simple *move* operations. The globally-asynchronous architecture promotes high modularity allowing specialized configurations of the architecture to be generated quickly with low hardware and software complexity.

The Armada architecture presented in this thesis expands on Fleet by introducing constructs that exploit thread-level concurrency. The proposals herein aim to increase the performance efficiency of Fleet and other communicationcentric architectures. Trade-offs between software and hardware complexity and between the static and dynamic division of labor are investigated through the implementation and study of an Armada microarchitecture and an Armada compiler created for this research. This thesis explores the merits and pitfalls of this unique architecture as the basis for general-purpose computers for the future.

# Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the "Copyright") and s/he has given The University of Manchester the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

- ii. Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the John Rylands University Library of Manchester. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

- iii. The ownership of any patents, designs, trade marks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and exploitation of this thesis, the Copyright and any Intellectual Property Rights and/or Reproductions described in it may take place is available from the Head of School of Computer Science (or the Vice-President).

## Acknowledgements

I would like to thank my supervisor Prof. Steve Furber for providing me with an opportunity to study in Manchester, for being an ever-insightful sounding board, and for imparting expert direction and advice throughout the course of my research. Ivan Sutherland clearly motivated this work with his wacky Fleet architecture. I would like to thank him, Igor Benko, Wesley Clark, and Sun Microsystems for supporting my efforts with an internship in California and with good discourse that helped me find focus and refine my ideas. Thank you family and friends who have provided the best of support and encouragement while being a steady reminder that there is a world outside of the Ph.D. – which can be quite easy to forget. Finally, this work would have certainly been left uncompleted without the surprise reemergence of an old friend. Thank you, Erin, for knowing exactly what I needed when I needed it and for pushing me through the final months.

## The author

Christopher Emmons obtained a Bachelor of Science degree in Computer Sciences from the University of Texas at Austin in 2003. While studying at Texas, he worked for Intel Corporation's Cellular and Handheld Group on XScale processors as an Applications Engineer intern. After graduating, he assumed Performance Validation Engineer and, subsequently, System-on-Chip Microarchitect roles at Intel. Leaving Intel in September 2005, Christopher began this Ph.D. work at the University of Manchester. He held two internship positions during the course of his research at ARM Holdings in Austin, Texas, and at Sun Labs in Menlo Park, California. He is currently working for ARM in Austin, Texas, in the Research and Development Group.

# Part I

# Introduction and background

## Chapter 1

## Introduction

In 2004, the means for increasing computer processor performance for over a decade reached an inflection point. Facing power inefficiency, difficulties designing increasingly complex hardware, growing costs of on-chip communication, and other barriers, the computer industry shifted focus to new ways of achieving more computing power more efficiently. This thesis presents one such computer architecture that attempts to overcome the contemporary performance, power, and design constraints that are inhibiting the progress of more typical computer processor designs. This architecture, called Armada, aims to create a power-efficient and reconfigurable computer useful for general purpose computing.

### 1.1 Motivation

For the past two decades, we have enjoyed large and predictable increases in computer performance. This improvement has largely been sustained by increasing utilization of hardware components as the processor operating frequency is increased. Intel unintentionally affirmed this trend is at an end by its highly publicized cancellation of a line of 4+ gigahertz processors in 2004 due to difficulty controlling the heat generated as an unwelcomed byproduct of such fast clock rates.

Designers are also having an increasingly difficult time putting additional transistors on a chip, made available each year by improvements in fabrication technology, to work. The density of transistors on a single chip roughly doubles every two years. This trend has proven very consistent over time and is commonly referred to as Moore's Law<sup>1</sup> [Moo65]. However, a more recent observation indicates that these additional resources are being used less and less efficiently; growth in performance of new processors is roughly the square root of their growth in density on any given chip process technology [Gel01]. The International Technology Roadmap for Semiconductors (ITRS) views this productivity gap as a great challenge for processor development over the coming years [ITR05].

Additionally, logic is becoming less expensive in terms of area and power consumption while communication is increasingly costly. The majority of processors have been designed to reuse once expensive logic as efficiently as possible. This reuse often requires moving large amounts of data through a minimal set of computation units. Although these computational units reside within close proximity to each other, controls spanning across the chip are greatly affected by the increasing wire delays that result from shrinking processor feature sizes [HMH01, AHKB00].

### **1.2** Research objectives

The overall goal of the research undertaken is to demonstrate a novel computer architecture with high power efficiency that addresses the modern challenges in processor design and manufacture. Computer architectures provide the framework on which processors are built and programmed. Architectures describe the programmer's view of the hardware – the *instruction set architecture* (ISA). They also describe the *microarchitecture* or *hardware organization* of the processor: what high-level blocks the hardware is composed of, what purposes they serve, and how they are interfaced together. Finally, computer architecture also encompasses the low-level implementation of the microarchitecture aptly referred to as the *hardware implementation*. Two or more implementations of the same microarchitecture may differ in characteristics such as size, performance, and clock frequency though they will share the same overall structure. This thesis will primarily focus on the ISA and microarchitectural aspects of computer architecture.

The soundness or goodness of a computer is largely judged on three factors:

<sup>&</sup>lt;sup>1</sup>Gordon Moore's original observation was that the number of transistors on a die doubled every 24 months, and he projected that the trend would continue for at least the next ten years. That prediction was made nearly 45 years ago.

performance, power consumption, and cost. The computer must minimally provide enough functionality and performance to meet the demands of the target application and, preferably, leave room to spare for increasingly demanding tasks of the future. The performance provided must not come at the expense of unreasonable power consumption. Mobile devices often have the most strict power requirements while consumers of high performance computer servers increasingly consider the cost of ownership of the machine before making their purchases. This cost of ownership includes the energy requirements of the server and the external cooling required to keep it functioning reliably. Finally, the cost of the finished computer must fit within the budget of the target products' requirements and be price-competitive with alternative designs for the computer to be successful.

The Armada architecture presented in this thesis is based on a one-instruction computer architecture called Fleet currently under development by Sun Labs and a handful of students from the University of California, Berkeley. Fleet addresses new challenges in processor design and fabrication and also provides a unique instruction set architecture that frees programmers and the hardware from common sequential programming paradigms. Specifically, it supports the concurrent execution of many instructions and supplies software with a clean method of representing this concurrency. The power of this architecture appears to stem from its unique representation of programs and the implications this has on the partitioning of complexity both between hardware and software and between static compile-time and dynamic run-time responsibilities. One goal of this research is to understand how this new representation affects hardware and software synergy compared to other prominent architecture designs.

The Armada architecture extends Fleet by supporting a coarser granularity of concurrency. Whereas Fleet provides the software representation of instruction level concurrency and capability required to execute many instructions at one time, Armada additionally provides the representation of task or thread level concurrency and capability required to execute many contexts at the same time. The proposed microarchitecture contains multiple Fleet cores on a single chip. Furthermore, each Fleet core is given new capabilities to run multiple tasks at the same time. These hardware enhancements are supported by a small but significant addition to the ISA that enables the spawning and management of these tasks.

To explore the benefits and disadvantages of this representation, a model of an

Armada microarchitecture implementation and an Armada imperative language compiler were created enabling insight into both hardware and software aspects of the architecture. The hope is to use the simple concurrency constructs in the ISA and the modular, decentralized microarchitecture to cheaply exploit concurrency and to create a scalable general purpose architecture for the future.

### **1.3** Research contributions

The following contributions were produced from this research:

- Method of representing and spawning threads in Fleet-based architectures

- Method of graphically representing Fleet and Armada architecture assembly language programs

- Method of hardware virtualization for one-instruction, asynchronous transport architectures that:

- enables simultaneous multithreading

- enables software performance to scale with the increasing number of functional units that may be placed on a chip each year

- enables increased resource utilization of processing elements in implementations with large numbers of such elements to decrease impact of rising static leakage power costs and to improve throughput

- An Armada microarchitecture: a multicore, globally asynchronous, simultaneous multithreading Fleet-based microarchitecture with thread level concurrency extensions

- Timing approximate simulation model of an Armada microarchitecture

- An assembler for Armada programs

- A trace-replay debugger for debugging highly concurrent Armada assembly language programs

- An Armada code generator for the Low Level Virtual Machine compiler infrastructure supporting high level imperative languages

### 1.4 Thesis structure

The thesis is divided into four parts. The remainder of part one describes the current challenges in computer architecture introduced here in more detail. Various types of general purpose computer architectures explored in the past and current research directions are discussed. Finally, an overview of the Fleet architecture upon which Armada is largely derived is given.

Part two discusses proposed enhancements to the Fleet architecture that form the Armada architecture. A microarchitecture implementation of Armada is presented, and a low-level simulator for the design is described. A discussion of how a benchmark was mapped to the architecture and some analysis of the microarchitecture's performance running this benchmark is provided.

Part three describes a procedure call standard that defines how software blocks are written for Armada so that they are interoperable with other software. A compiler code generator is described that transforms programs written in highlevel imperative languages such as C++ and Java into instructions for the Armada architecture. Code generated for Armada is compared to code generated for other more typical architectures. Additionally, a tool for debugging the highlyconcurrent architecture is described.

The final part of the report discusses the results, considers further work, and provides concluding remarks on this research.

## Chapter 2

# General-purpose computer architecture

This chapter provides an introduction to the area of general purpose computer architecture with a focus on major challenges of today and tomorrow. Some methods and research directions taken to confront these challenges are discussed. Exploiting concurrency is given special focus.

### 2.1 General-purpose computer requirements

Computer processors have widely varying applications from controlling kitchen appliances and children's toys to handling millions of secure transactions per minute in online store servers. Due to the enormous number of applications processors have, the design space for architectures is also large. This research focuses on the development and analysis of a new architecture to design general purpose computer processors.

General purpose processors may be found in powerful computer servers, home desktop and notebook computers, and in hand-held devices. Typical applications include gaming, media playback and editing, web browsing, data serving, and scientific workload processing. Successful processors will balance price-performance carefully; thus, semiconductor companies produce different flavors of general purpose processors to better meet the needs of the various target segments. For example, although one ISA may be used for all segments, a differentiation in microarchitecture for processors used in high-end desktop PC's and servers may be made from those processors used in mobile, power-constrained devices. Implementation differences such as clock frequency, chip fabrication technology, or cache sizes may be used to target more specific demands of applications and to satisfy a variety of customers with varying budgets while maximizing profits for the processor manufacturer.

General purpose architectures generally have long lifetimes because they serve as the rough blueprints for multiple generations of processors. Pre-compiled programs are expected to retain binary compatibility with these different processors. Therefore, programs should ideally benefit from any performance improvements made between each generation without having to recompile them.

An increasing number of applications in the traditionally general purpose computing design space have common and demanding tasks that they are expected to perform efficiently. For example, high-resolution video capture and compression on a desktop PC requires fast video encoding of a large amount of raw image data. Cryptography algorithms are used to securely transfer data and to enable digital rights management of protected media. The specialization of microprocessors for target applications such as these is enabled by reconfigurable architectures and by the addition of hardware accelerators for common and demanding tasks. As transistor budgets grow, processor manufacturers are able to integrate such reconfigurable logic and specialized accelerators into traditionally general purpose processors.

### 2.2 Challenges in computer architecture

Optimizing processors for performance, power, and cost requires a carefully balanced architecture which addresses numerous challenges. The following sections describe some of the contemporary challenges architects face.

### 2.2.1 Design complexity and productivity gap

Improving chip process technologies allow more transistors to be crammed onto processors with each generation. As foretold by Moore's Law, billion transistor chips have arrived; Intel's Itanium 2 processor in production in 2006, codenamed "Montecito," encompasses 1.72 billion transistors. Sun Microsystems' "Niagara" processor, shipping since late 2005, combines eight processing cores to tackle challenging applications. Managing such large numbers of resources effectively has become a formidable challenge.

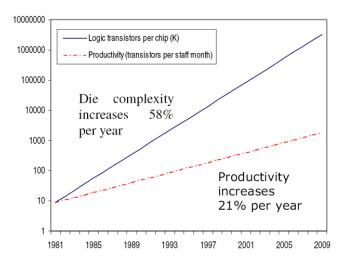

Design complexity is a metric that refers to the number of devices a chip contains or to the amount of behavior that a design exhibits. As design complexity has steadily risen at a rate of approximately 58% per year, design productivity, the rate at which design engineers and their tools can build new processors, has only risen at a rate of 21% per year as shown in figure 2.1 [ITR05]. Therefore, more than a twofold increase in productivity in the coming years is required to make efficient use of increasing transistor density.

Figure 2.1: Design complexity and productivity gap. (from Sematech)

#### 2.2.2 Power consumption

In recent years, maximizing processor performance has taken a back seat to limiting processor power consumption and increasing processing efficiency. High processor power consumption increases the cost of ownership of computers, limits the run time of mobile devices between charges, and stunts the growth potential of computer processors as the chips reach thermal package limits.

Power consumption in computer processors consists of a static component, called leakage power, and a dynamic component, called switching power (equation 2.1). Static power loss occurs when the circuit is in a steady-state. The switching power component captures the power loss due to the charging and discharging of the circuits as well as short-circuit power.<sup>1</sup> Short-circuit power is

<sup>&</sup>lt;sup>1</sup>In complementary metal oxide semiconductor technology, or CMOS, short-circuit power

generally a small portion of dynamic power in well-designed circuits and is not discussed here.

$$Power_{total} = Power_{static} + Power_{dynamic} = (I_{leakage} * V_{dd}) + [\alpha * C * V_{dd}^2 * f_{clk}]$$

(2.1)

Although static leakage power has historically been small compared to dynamic switching power, the situation is changing as feature sizes decrease. The smallest *feature size* of a chip process technology refers to the smallest size of transistors, wires, or gaps between them that can be created onto the chip die with that technology. As these sizes decrease, the capacitance of the system of transistors, C, is lowered. This reduced capacitance decreases the switching time of those transistors, or gate delay, resulting in faster logic performance accommodating faster processor clock frequencies  $(f_{clk})$ . The activity factor,  $\alpha | 0 \leq \alpha \leq 1$ , approximates the average switching activity of the circuit for each clock edge.<sup>2</sup> The supply voltage,  $V_{dd}$ , is lowered to reduce interference with the ever-closer neighboring components and to meet thermal requirements. Lowering  $V_{dd}$  greatly reduces dynamic power consumption since the dynamic power is proportional to the square of this supply voltage. However, lowering the supply voltage in turn often requires a lowering of the threshold voltage, the voltage level at which transistors switch, to maintain fast clock rates. Lowering the threshold voltage and moving the threshold closer to ground causes a disproportionate increase in the static leakage current,  $I_{leakage}$ , and thus an increase in static power consumption  $[KAB^+03].$

### 2.2.3 Processor and memory performance gap

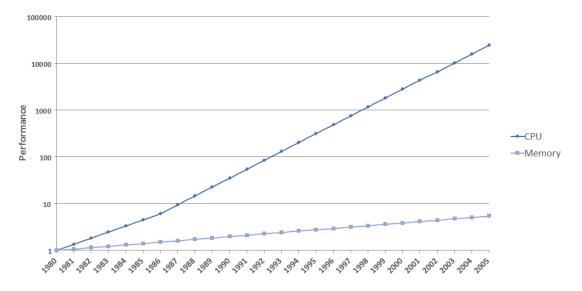

The computer processor is only one of the factors in computer system performance. Access to memory for instructions and data is often the bottleneck in today's systems. Computer processor performance has increased at a rate of roughly 55% per year while memory performance has increased at a rate of less than 10% per year as shown in figure 2.2 [HP03].

loss occurs when both n and p transistors are simultaneously enabled during a transition. The power lost is dependent on the slope of the rising and falling transition edges.

<sup>&</sup>lt;sup>2</sup>The activity factor for a clocked flip-flop, for example, is  $\frac{1}{2}$  since it toggles at most once per clock cycle and, thus, toggles once for every two clock edges. Techniques like clock-gating which decrease the number of logic transitions aim to keep this activity factor low.

Figure 2.2: Memory and CPU performance gap. (Hennessy and Patterson)

Memory caches are used to store frequently accessed data closer to the processor core for faster lookup to help alleviate this problem. Small, local, simple caches can be accessed with very low latency and the data used very quickly by the processing core. As cache sizes grow, the access latency increases, and the benefits of a larger cache may not compensate for this increased lookup time. For this reason, architectures often have a hierarchy of caches with small, fast, level one (L1) caches close to the processor supported by one or more increasingly slower, larger caches (L2, L3, and so on). Though slower than an L1 cache, these larger caches still provide much faster access to data than off-chip memory with less power consumption. Much research has been conducted on the trade-offs of different cache hierarchy schemes [Jou90, FPT94].

### 2.2.4 Cost of communication

In early computers, state-holding logic took the form of large and expensive vacuum tubes. Communication was handled by small and relatively cheap wires. Today's trends show that logic in the modern form of transistors is cheap and continually getting cheaper; communication costs, however, are growing in significance.

As mentioned in section 2.2.2, wires and transistors on-chip are becoming smaller. Although smaller feature sizes result in decreases in gate delay, the same is not necessarily true for wire delay. Thinner wires with some material resistivity,  $\rho$ , have increased resistance per unit length,  $\frac{R_w}{l}$ , due to lower cross-sectional area, A (equation 2.2). Wire delay,  $\tau$ , is a product of both this resistance and of wire capacitance (equation 2.3). The capacitance is not decreasing proportionally to the resistance; even reducing the length, width, and height of a wire by some common factor will not necessarily change the wire delay significantly since one component of the wire capacitance, fringing capacitance, does not scale with feature size. Therefore, decreasing feature sizes are resulting in an increase in the ratio of wire delay to gate delay and ultimately in communication-bound performance.

$$\frac{R_w}{l} = \frac{\rho}{A} \tag{2.2}$$

$$\tau = R_w C_w \tag{2.3}$$

### 2.3 Research directions

Computer architects and engineers have responded to the challenges of designing general purpose computer processors in many different ways. Some of the most successful and interesting approaches are described here.

#### 2.3.1 Exploiting parallelism

Parallelism in computer architectures is the ability for multiple actions to occur simultaneously. Parallelism is often categorized into the three types discussed here.

#### Data level parallelism (DLP)

General purpose architectures often support data-level parallelism (DLP), the parallelism found in the application of identical operations across many different data elements [HGLS86]. Some scientific applications and many multimedia applications exhibit large levels of DLP. Vector processors such as Cray Research's Cray-1 and Cray-2 use single instructions to operate on vectors of data elements at a time. Vector machines continue to be applied to scientific applications with high DLP, and research projects such as VIRAM show promise in applying vector processing to embedded markets [KP02, BG04]. Other common approaches for exploiting DLP are single-instruction multiple-data (SIMD) architecture extensions. SIMD instructions allow programmers to specify a single operation to apply to multiple, distinct data elements. Unlike vector processors, generally only a small number of elements that can fit in a single register at one time are operated on simultaneously. SIMD is fairly ubiquitous and has been supported by many commercial general-purpose processors since the mid-1990's in architecture extensions such as the Apple-IBM-Motorola alliance's AltiVec<sup>3</sup>; Digital's MAX; Intel's MMX, SSE, and WMMX; Sun's VIS; AMD's 3DNOW; MIPS's MDMX; and ARM's NEON.

#### Instruction level parallelism (ILP)

Many processors today also support instruction-level parallelism (ILP) by taking advantage of resource and data independence between instructions and executing multiple operations at one time. Superscalar processors (or *superscalars*) are capable of fetching and executing more than one instruction simultaneously and thus exploit some level of ILP. Statically-scheduled superscalars may execute several instructions in program order if there are no hazards between the instructions. These superscalars stop executing later instructions when any hazard is first encountered which limits ILP. Another class of architectures, very long instruction word architectures (VLIW), contain multiple operations in a single instruction. The compiler attempts to resolve dependencies and places independent instructions into slots of the instruction word for parallel execution by the hardware. This approach reduces hardware complexity versus superscalars since the independencies are discovered at compile-time and are explicitly specified to the hardware. More comparisons between superscalars and VLIW processors will be given later in this section.

Dynamic scheduling allows processors to find independences that cannot be found at compile time or through static run-time methods. Out-of-order superscalars are capable of examining many instructions at once, determining independences among those instructions, and executing multiple operations simultaneously and potentially out of order. Out-of-order superscalars can look past

$<sup>^3\</sup>mathrm{Also}$  known as Velocity Engine and VMX depending on which company is referring to the extensions

instructions that cause hazards and execute one or more of the later instructions immediately. However, the hardware resources involved in finding ILP dynamically are large. Structures such as reorder buffers, rename register files, and instruction windows must grow in size and complexity with instruction issue width and the number of supported instructions in flight. Furthermore, dependency tracking logic grows quadratically in the number of instructions [HP03].

The limits of attainable ILP have been explored many times over with researchers drawing different conclusions [Wal91, Wal95, GG98]. The general consensus is that dynamic scheduling and employing speculative techniques of control and data value prediction are necessary to create large opportunities for exploiting ILP, but hardware overhead must be controlled. The latter proves difficult.

#### Thread level parallelism (TLP)

Some programming languages allow programmers to explicitly define threads of control in a program that may be executed concurrently. Additionally, multiprocessing operating systems may have several programs to execute each having its own set of threads that may also be executed concurrently. The parallelism made available by executing multiple threads at a time is called thread-level parallelism (TLP). Hardware support for TLP typically comes in two forms, multiprocessing and multithreading. Multiprocessing involves two or more processing cores either on a single chip or connected with an external interconnect. The most common type of single chip multiprocessor, or CMP, is called a *symmetric multiprocessor*, or SMP, which contains two or more identical cores connected to shared memory. SMP's are commercially available today on entry-level systems with the introduction of Intel Pentium D and AMD Athlon X2 processors. Commercial systems have widely been available for years that interconnect multiple single core processors to create a multiprocessing system.

Multithreading refers to hardware-supported execution of multiple program threads. Multithreaded processors hold the state of two or more threads at a time. These processors appear as multiple single processor cores to most operating systems though the execution resources in the hardware are actually shared among the threads. Sharing these resources versus duplicating them such as in CMP designs saves die area which helps to contain static, leakage power and chip fabrication costs. Early approaches to multithreading executed a single thread at a time, switching between contexts on long latency operations like memory accesses or at regular, statically-defined intervals. These techniques helped to eliminate wasted cycles but did not improve utilization of idle hardware resources. Simultaneous multithreading (SMT) enables multiple threads to dynamically allocate and use available hardware resources concurrently providing opportunities for higher levels of resource utilization than CMP designs. Under high load, wide instruction issue SMT processors show similar performance to CMP's with several processing cores and smaller supported instruction widths [TEL98]; SMT's with more modest complexity and thus smaller issue widths and numbers of supported threads like those in commercially available processors to date see less improvement. Intel's SMT technology is marketed as Hyper-Threading or HT. SMT die area overhead in Pentium 4 HT processors supporting two threads is 5-6%, and performance gains are from 15-25% for a variety of common desktop applications [KM03]. Despite low die area overhead, design cost for the implementation was considerable due to supporting two logical contexts, changing micro-op prioritization schemes, and validating the permutations of the x86 architecture's operating modes possible among the contexts [KM03].

#### Finding ILP in programs

The previous sections identified several types of parallelism, and many different approaches have been made to exploit it. Special attention is given to ILP here as the relationship between the hardware and software for making use of it is complex and requires many trade-offs. Architectures can be classified into three types based on hardware and software partitioning to find ILP: sequential, dependence, and independence [RF93].

As discussed, superscalar processors are given programs in the form of streams of instructions that are expected to execute one after another. ILP extraction from the stream must be performed in the hardware without any guarantees from software. However, a compiler may attempt to help hardware exploit ILP by applying any knowledge it has of the hardware implementation to schedule independent instructions next to one another in the code it generates. Such architectures are called sequential architectures. Of the three classes, hardware complexity for exploiting ILP is the greatest, hardware-software coupling is the loosest, and software's responsibility in finding ILP is the lowest.

In another class of architectures called dependence architectures, software

communicates dependencies to the hardware directly. To execute instructions simultaneously, the hardware must still find independent operations, but the task is made easier than in sequential architectures due to the additional information the software provides. Data flow architectures are primary examples of dependence architectures. In data flow machines, an instruction typically contains a pointer to its successor instruction, the place to send the result of the current operation; this information expresses the dependence between the instructions. Dependence architectures have an easier task of finding parallelism than do sequential architectures, have loose hardware-software coupling, and rely on software to provide some information for exploiting ILP.

Finally, independence architectures may rely entirely on software to discover exploitable concurrency. VLIW architectures, for example, require software to fill slots in long instruction words with independent operations that may be executed in parallel. Generally, the compiler does most if not all of the scheduling work, and hardware in independence architectures can therefore be relatively simple and still exploit ILP. However, a hardware implementation may choose to search for additional independent operations at run time transparent to software like a superscalar processor does; this would of course result in an increase in hardware complexity. In independence architectures, hardware-software coupling is high as the compiler must often be aware of the hardware microarchitecture in order to determine instruction independences. Software and compilers for independence architectures are the most complex out of the three architecture classes presented here.

Independence architectures are becoming increasingly popular as a means to curb hardware complexity. VLIW independence architectures have been embraced in embedded markets as application-specific processors. TriMedia CPU64 VLIW processors can be found in set-top boxes and other embedded multimedia systems [vESV+99]. Explicitly parallel instruction computing architectures, or EPIC architectures, are a variant of VLIW developed by Hewlett Packard Labs that combine instruction independence discovery in software with traditionally superscalar approaches to dynamic exploitation of ILP [SR00]. The family of Itanium processors use this architecture.

#### 2.3.2 Increasing cache sizes

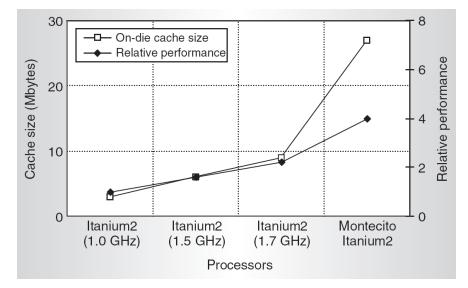

Today's high-performance processors are employing larger caches to help close the CPU and memory performance gap as shown in figure 2.3 [FH05]. Intel's "Montecito" Itanium 2 processor released in 2006 contains nearly 27MB of total cache memory on-die [MB05]. In addition to performance improving characteristics, caches have been optimized in ways to limit both dynamic and static power requirements thus providing power-efficient use of die area [FKM<sup>+</sup>02].

Figure 2.3: Cache size versus performance in Itanium2. (from Flynn)

### 2.3.3 Designing at higher levels of abstraction

A primary method of attacking the design complexity problem is to design architectures at higher levels of abstraction. Tools such as SystemC allow architects to develop high level models of architecture components and to explore the design space more quickly. SystemC-to-Verilog translators are becoming available to bridge the gap from the object oriented simulation environment to register transfer level (RTL) modeling and realization in hardware.

Another method of designing at a higher level of abstraction is the reuse of hardware and software blocks. SMP's, for example, copy multiple instances of identical cores into processors to exploit thread-level parallelism; the core is designed and validated once and reused many times. Tiled architectures are more extreme examples of this type of hardware reuse. Tiled architectures provide a framework for designing processors by copying a large number of logic and memory blocks in a regular fashion across the die. Raw architectures, for example, are built using multiple tiles containing a MIPS-style pipeline, a pipelined floating-point unit, several caches, and routers for communication with other tiles [TLM<sup>+</sup>02]. Despite exhibiting lower performance on sequential applications than traditional superscalar processors, some evaluations show a 2–9x improvement with Raw for applications with high ILP and a 10–100x improvement when highly parallel algorithms are carefully optimized for the architecture [TLM<sup>+</sup>04]. Unlike Raw architectures, Smart Memories have a heterogeneous mix of tiles that may be chosen for targeting specific applications and thus are also a type of reconfigurable architecture [MPJ<sup>+</sup>00]. The TRIPs architecture is a grid architecture composed of homogeneous but polymorphic resources [SNL<sup>+</sup>03]. Thus, unlike the Smart Memories approach, TRIPs uses identical processing elements and memories, but the behavior of these components can be dynamically reconfigured to enhance the performance of applications executing at the time by favoring ILP, TLP, or DLP at the software's discretion. These designs all reuse hardware blocks to minimize hardware complexity and development time.

#### 2.3.4 Communication-centric architectures

In addition to tackling the problem of how to make use of growing transistor budgets, tiled architectures are also directly addressing the problem of increasing wire delays as a first order design constraint. This thesis refers to such architectures as communication-centric. The Raw and Smart Memories architectures both limit maximum tile sizes such that intra-tile communications require no more than one clock cycle [TLM<sup>+</sup>02, MPJ<sup>+</sup>00]. This requirement helps ensure that the tiled processors will scale with smaller feature sizes.

Some architectures place data movements directly in the hands of the compiler and programmer. MOVE architectures explicitly describe transports among functional units rather than the operations to perform [CM91]. The operations occur as side-effects of the transport. For example, if two data elements get sent to the two input ports of a dyadic multiplication functional unit, the values will be multiplied together. The result can then be moved directly from the multiplier to another functional unit; register files may be completely bypassed in favor of the shortest route to the successor operation. Forsell shows that MOVE architectures do well in reducing hardware complexity but do not compete with the performance of traditional general-purpose architectures [For03].

### 2.4 Conclusion

This chapter discussed some of the contemporary challenges in computer architecture and also some of the current approaches to address these issues. The next chapter describes the Fleet architecture designed to target these challenges. It is the foundation for the Armada architecture discussed in the remainder of the thesis.

## Chapter 3

# The Fleet architecture

The previous chapter discussed some of the problems today's computer architectures will face in the foreseeable future. This chapter introduces the Fleet architecture and discusses how it proposes to address those concerns. A description of the instruction set architecture is given followed by an overview of the hardware organization. Finally, some initial observations on working with Fleet and some of the architecture's constraints are discussed.