# Energy Efficient Functional Unit for a Parallel Asynchronous DSP

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Engineering and Physical Sciences

July 2005

Wannarat Suntiamorntut

School of Computer Science

## **Contents**

| Contents                                                               | 2  |

|------------------------------------------------------------------------|----|

| List of Figures                                                        | 5  |

| List of Tables                                                         | 8  |

| Abstract                                                               | 9  |

| Declaration                                                            | 10 |

| Copyright                                                              | 10 |

| The Author                                                             | 11 |

| Acknowledgements                                                       | 12 |

| Chapter 1: Introduction                                                | 13 |

| 1.1 Motivation                                                         |    |

| 1.2 Research Contributions                                             | 19 |

| 1.3 Organization                                                       | 20 |

| Chapter 2: Background                                                  | 23 |

| 2.1 Digital Signal Processor                                           |    |

| 2.1.1 How a DSP is different from a general purpose processor?         |    |

| 2.1.2 Digital Signal Processor Architecture                            |    |

| 2.2 A Modern Digital Signal Processor Architecture                     |    |

| 2.2.1 Important features of DSP processor                              |    |

| 2.2.2 DSP for next generation mobiles and wireless communication       |    |

| 2.2.3 DSP for multimedia signal processing                             |    |

| 2.3 General Functional Unit for DSPs                                   |    |

| 2.4 Energy Efficient Design                                            | 33 |

| 2.4.1 Energy Sources                                                   | 33 |

| 2.4.2 Fundamental of low-power design                                  | 35 |

| 2.5 Low Power Systems                                                  |    |

| 2.5.1 Low power design at a technological-level                        |    |

| 2.5.2 Low-Power design at a circuit-level                              |    |

| 2.5.3 Low-Power design at a logic-level                                |    |

| 2.5.4 Timing Approach                                                  |    |

| 2.5.5 Low-Power Design at an architecture level                        |    |

| 2.5.6 Low-Power Design at an Algorithmic Level                         |    |

| 2.6 Concluding Remarks                                                 | 58 |

| Chapter 3: Asynchronous Parallel DSP                                   | 59 |

| 3.1 Background                                                         | 60 |

| 3.2 CADRE-s Top-Level Architecture                                     | 61 |

| 3.2.1 MIMD with VLIW encoding                                          | 64 |

| 3.2.2 Five Stage Asynchronous Pipeline Organization                    | 64 |

| 3.3 FU Interconnection                                                 | 67 |

| 3.4 Testability                                                        |    |

| 3.5 The example of Four-way Parallelism                                | 71 |

| Chapter 4: Energy Efficient Functional Unit - The Adder and Multiplier | 74 |

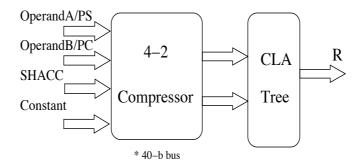

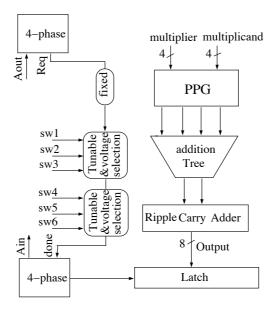

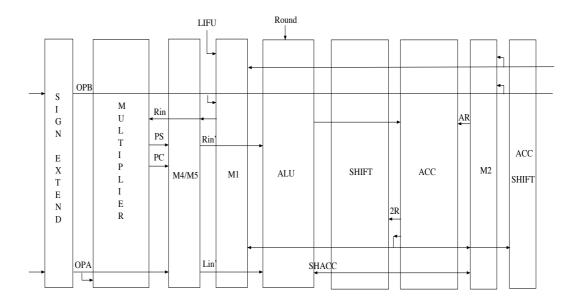

| 4.1 Functional Unit Architecture                                       |    |

|            | 4.1.1 Instruction Set                                       | 77             |

|------------|-------------------------------------------------------------|----------------|

|            | 4.1.2 FU datapath                                           | 77             |

|            | 4.1.3 A Data Flow                                           |                |

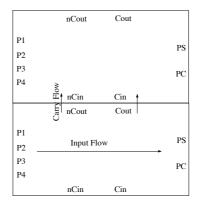

| 4.2        | Addition                                                    | 80             |

|            | 4.2.1 Carry-Look-ahead Tree Background                      |                |

|            | 4.2.2 Carry-Look-Ahead Tree Implementation                  |                |

|            | 4.2.3 Adder Implementation                                  |                |

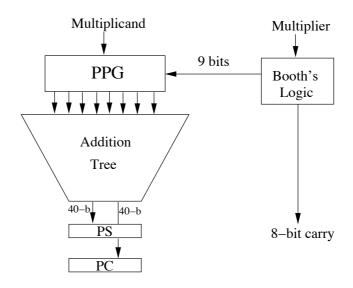

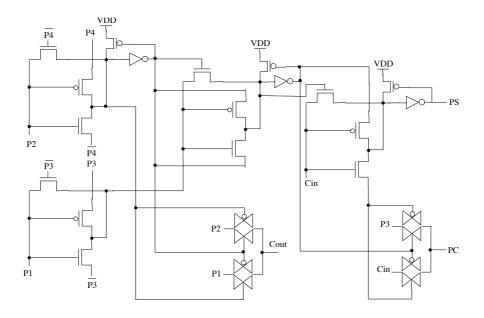

| 43         | Multiplication                                              |                |

| 7.5        | 4.3.1 Background                                            |                |

|            | 4.3.2 Multiplier Implementation                             |                |

|            |                                                             |                |

|            | 4.3.3 Input Swapping                                        |                |

| 4.4        | 4.3.4 Sign Extension                                        |                |

| 4.4        | Multiply Accumulate (MAC) Operation                         | 103            |

| Chapter    | : 5: Energy Efficient Functional Unit - Hamming Distance, N | Normalization, |

|            | and Control                                                 |                |

| _          | Hamming Distance and Normalization                          |                |

|            | 5.1.1 Hamming Distance and Normalization Specification      |                |

|            | 5.1.2 Hamming Distance and Normalization Design             |                |

|            | 5.1.3 HD and NORM Results                                   |                |

| 5.2        | Others Functions                                            |                |

|            | PTG Shifter                                                 |                |

|            | Accumulator                                                 |                |

|            | Configurable Memory                                         |                |

|            | Control Unit                                                |                |

| 5.0        |                                                             |                |

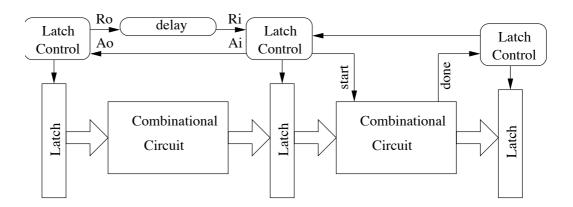

| <i>-</i> 7 | 5.6.1 Asynchronous Control Circuit                          |                |

| 5.7        | Delay Model and Tunable Timing Mechanism                    |                |

|            | 5.7.1 Data Encoding                                         |                |

|            | 5.7.2 Data Dependency                                       |                |

|            | 5.7.3 Delay Model                                           |                |

|            | 5.7.4 A Tunable Timing Mechanism                            |                |

|            | 5.7.5 Experimental Results                                  |                |

|            | 5.7.6 Extending the Concept                                 |                |

| 5.8        | Voltage Scaling Versus Energy Consumption                   | 131            |

| Chanter    | 6: Energy Efficient Circuit Design Methodology              | 134            |

| _          | Logic Style                                                 |                |

|            | Pass Transistor                                             |                |

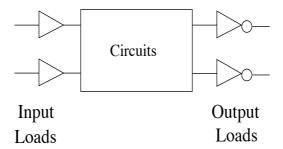

| 0.2        | 6.2.1 Fan-in and Fan-out of PTG                             |                |

|            |                                                             |                |

| 6.2        | 6.2.2 Transistor sizing                                     |                |

|            | Voltage Scaling in Pass Transistor Circuit                  |                |

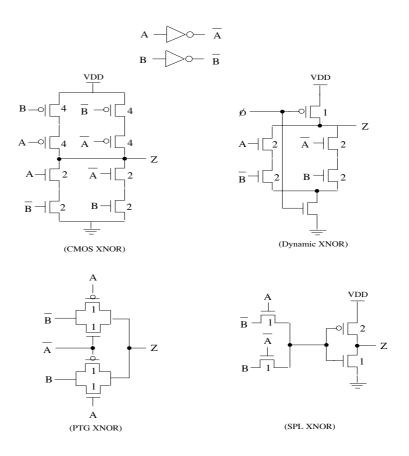

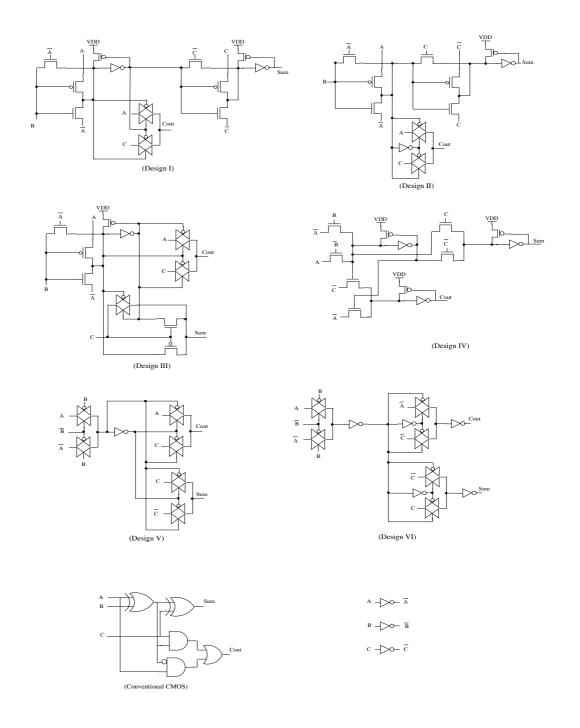

| 6.4        | XOR/XNOR Design For the Full Adder                          |                |

|            | 6.4.1 New full adder using Novel XOR-XNOR Gates             |                |

|            | 6.4.2 Efficiency Evaluation                                 |                |

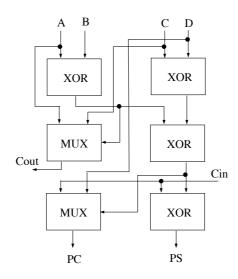

| 6.5        | Energy Efficient 4-2 compressor                             |                |

|            | 6.5.1 4-2 Compressor Designs                                |                |

|            | 6.5.2 4-2 Compressor Circuitry                              |                |

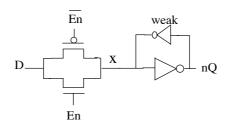

| 6.6        | Energy Efficient Latch                                      | 156            |

| 6.7        | Layout Consideration                                        | 157            |

|            | 6.7.1 Datapath Layout                                       | 157            |

| 6.7.2 Standard cell layout                    | 160 |

|-----------------------------------------------|-----|

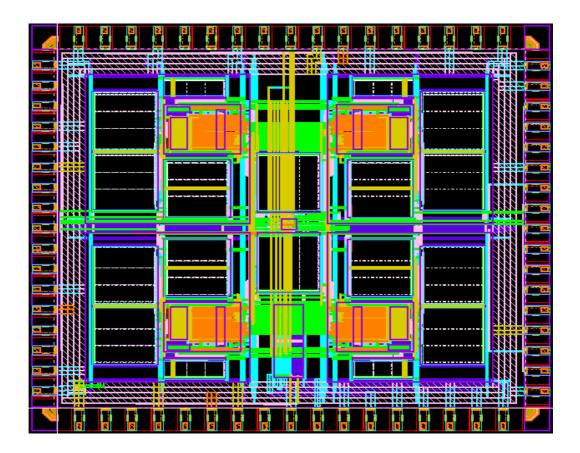

| Chapter 7: Evaluation                         | 163 |

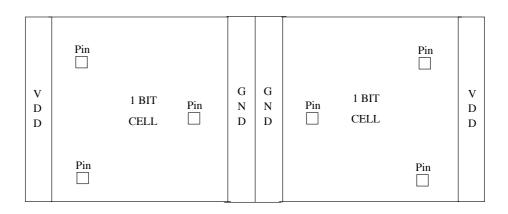

| 7.1 Chip Connections                          | 163 |

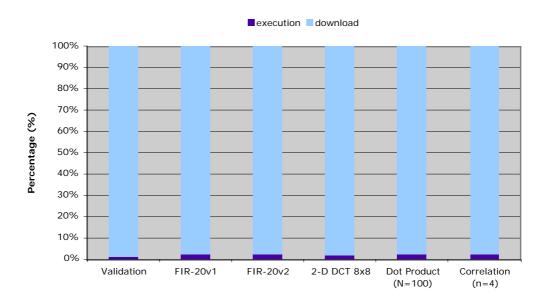

| 7.2 Kernel Benchmarks                         | 164 |

| 7.2.1 Digital filters                         | 164 |

| 7.2.2 Vector Dot Product                      | 165 |

| 7.2.3 Correlation                             | 165 |

| 7.2.4 Discrete Cosine Transform (DCT)         | 166 |

| 7.3 Speech / Voice Data                       | 167 |

| 7.4 Results                                   | 169 |

| 7.4.1 Operation Rate                          | 169 |

| 7.4.2 Run Time                                | 170 |

| 7.4.3 Execution Energy of FIR Filter          | 171 |

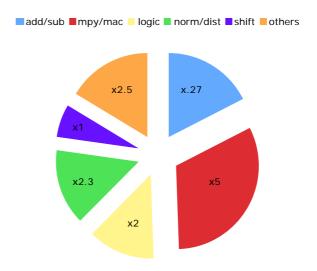

| 7.4.4 Instruction Mix and Execution Time      | 173 |

| 7.4.5 Scaling Down the Supply                 | 175 |

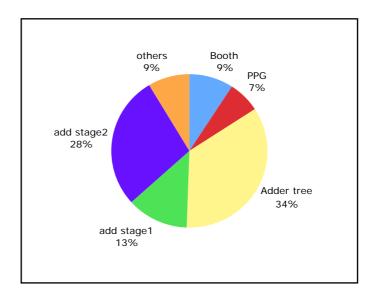

| 7.4.6 Power Breakdown in the Functional Units | 175 |

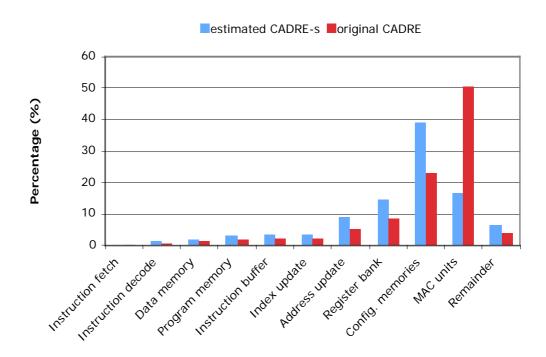

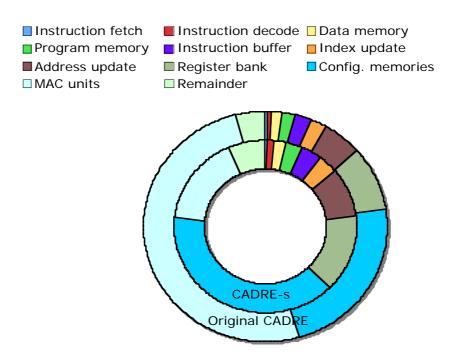

| 7.4.7 Projected CADRE-s                       | 177 |

| 7.5 Comparison with other DSPs                | 179 |

| Chapter 8: Conclusions                        | 184 |

| 8.1 Current Directions                        | 186 |

| 8.2 Future Research Directions                | 187 |

| 8.3 Conclusions                               | 187 |

| References                                    | 189 |

| Appendix A: Instruction set                   | 198 |

| Appendix B: Glossary                          |     |

| Appendix C: Simulation Details                |     |

# **List of Figures**

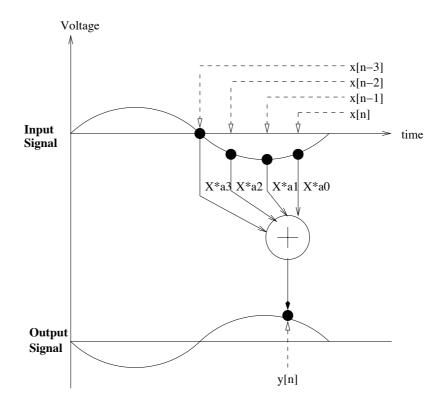

| 2.1 An example of FIR operation in a DSP                                    | 25  |

|-----------------------------------------------------------------------------|-----|

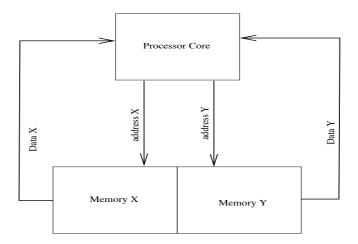

| 2.2 Typical DSP architecture                                                | 26  |

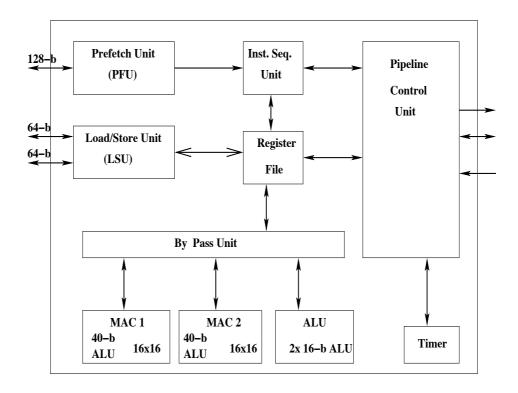

| 2.3 Block Diagram of ZSP600 DSP                                             | 30  |

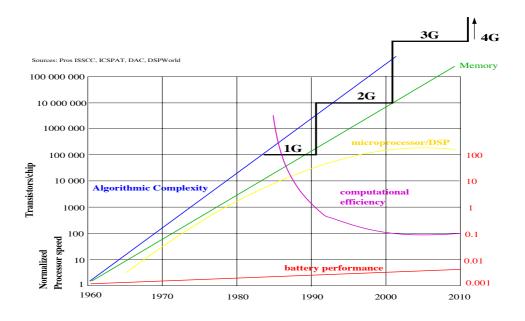

| 2.4 Improvement in technology[30]                                           | 34  |

| 2.5 Energy versus voltage scaling                                           | 35  |

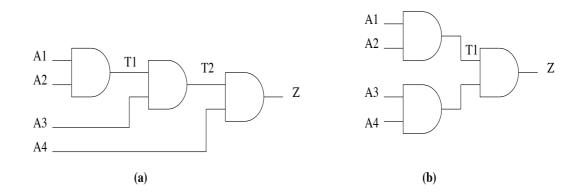

| 2.6 Circuit topology (a) chain structure (b) tree structure                 | 38  |

| 2.7 (a) Dynamic logic (b) Dynamic DCVSL (c) Static DCVSL                    | 47  |

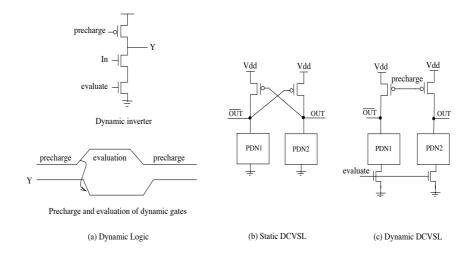

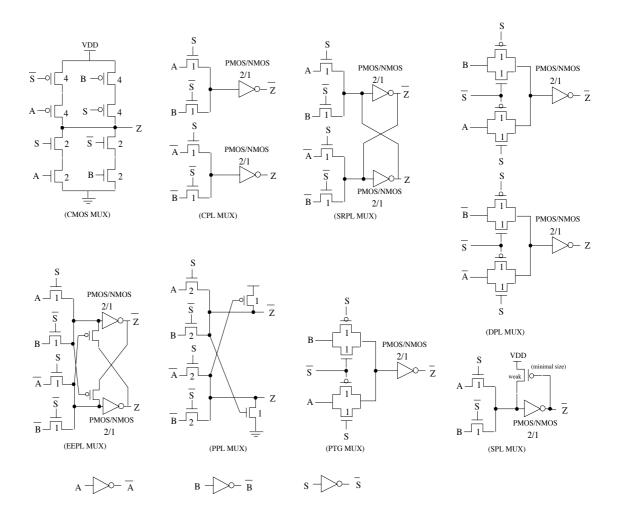

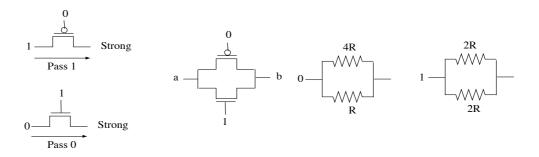

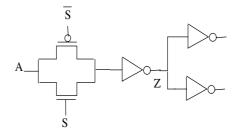

| 2.8 Pass gates or Pass Transmission Gate (PTG)                              | 49  |

| 2.9 Complementary Pass Transistor Logic (CPL)                               | 49  |

| 2.10 Energy Economized Pass Transistor Logic (EEPL)                         | 50  |

| 2.11 Single-ended Pass Transistor Logic (SPL)                               | 50  |

| 2.12 Principle of micro-pipeline                                            | 53  |

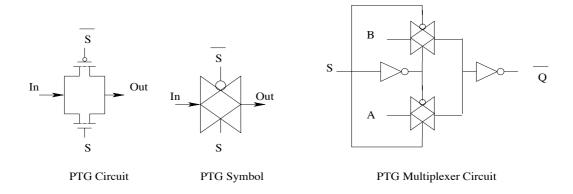

| 2.13 Two possible structures of execution unit-sharing                      | 57  |

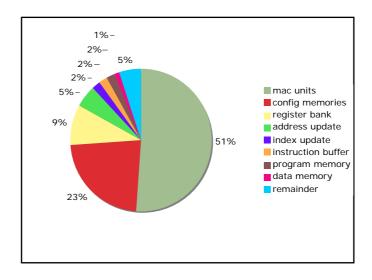

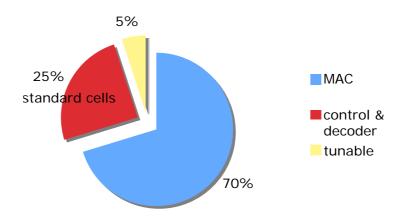

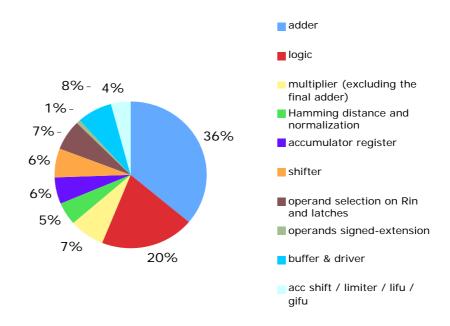

| 3.1 Average distribution of energy per block in CADRE                       | 62  |

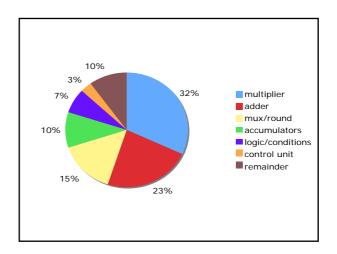

| 3.2 Breakdown of power consumption within the FU in CADRE                   | 62  |

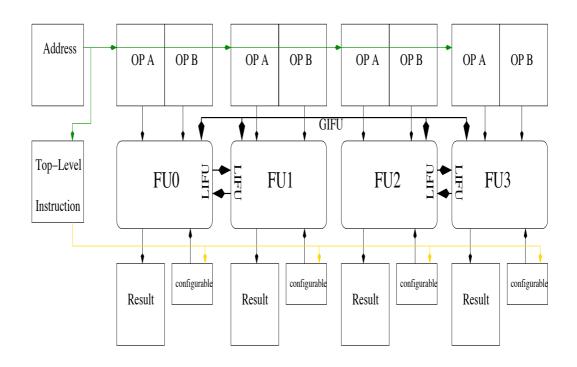

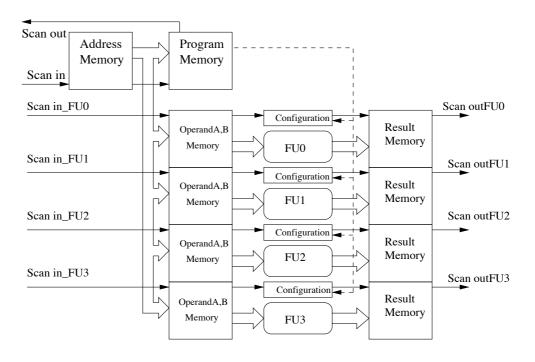

| 3.3 Top-level architecture for CADRE-s                                      | 63  |

| 3.4 CADRE-s Data Organization                                               | 63  |

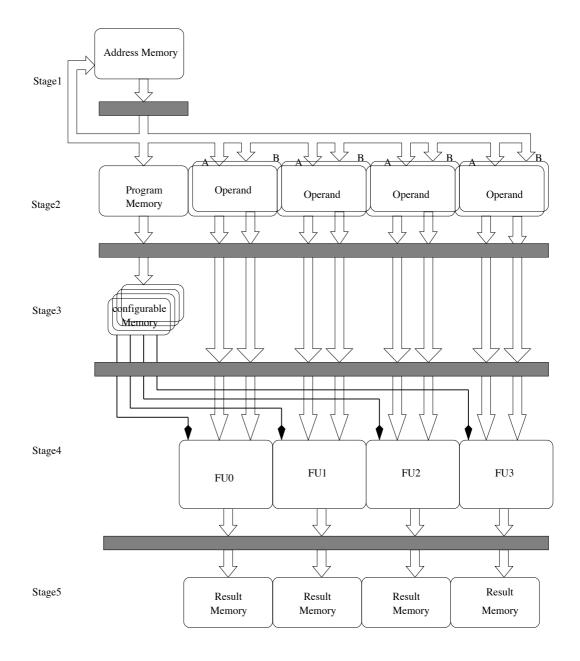

| 3.5 5-Stage pipeline CADRE-s Organization                                   | 65  |

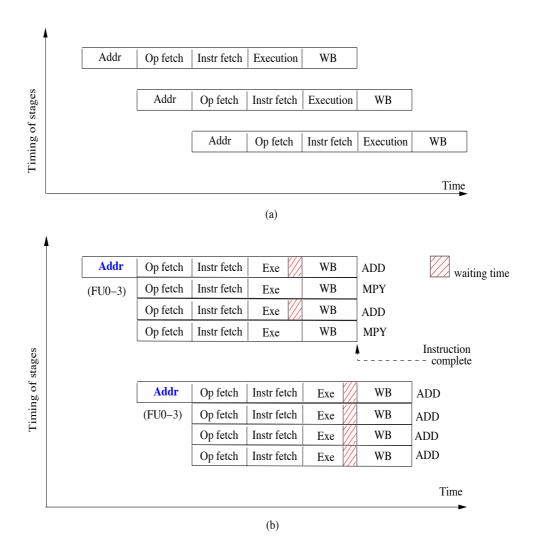

| 3.6 (a) CADRE-s 5-stage pipeline operation for a FU. (b) CADRE-s multi-time | ;   |

| slot instruction of 5-stage pipeline operation of 4FUs.                     | 67  |

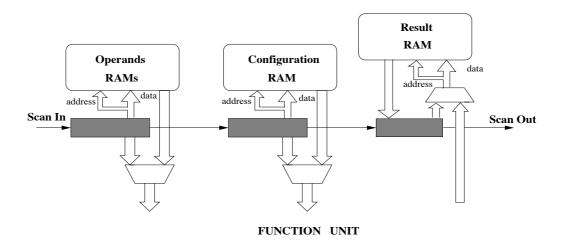

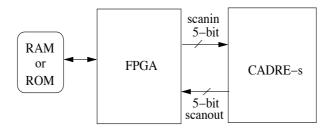

| 3.7 Scan-path in a FU of CADRE-s                                            | 70  |

| 3.8 Test board configuration                                                | 71  |

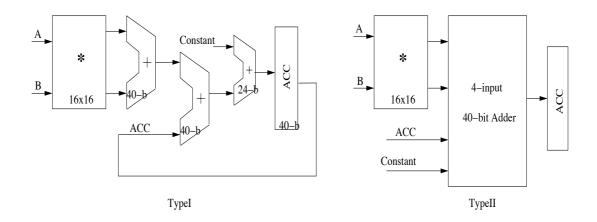

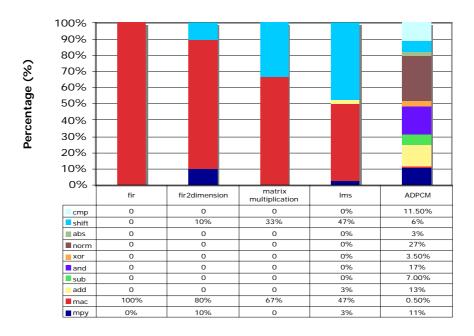

| 4.1 Analyse arithmetic instructions in DSP kernels                          | 75  |

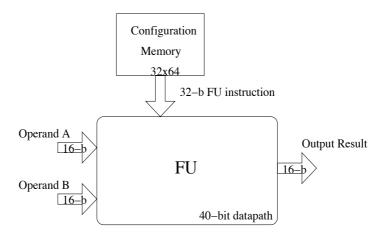

| 4.2 Top-level functional unit architecture                                  | 76  |

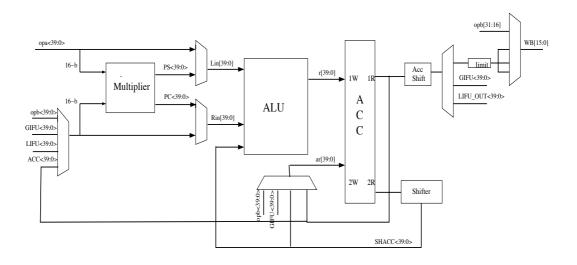

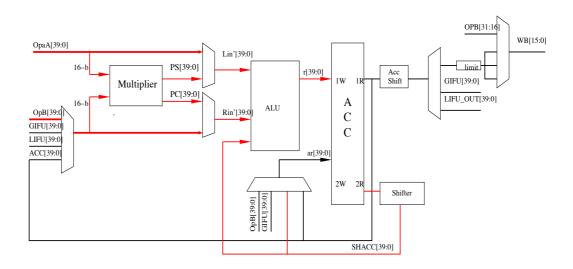

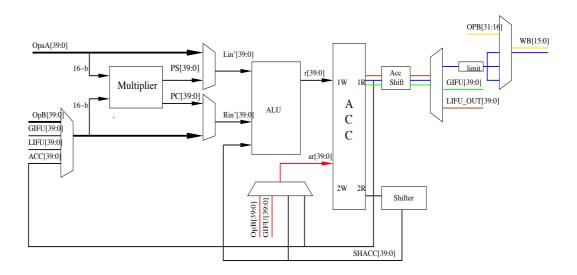

| 4.3 Functional Unit datapath                                                | 77  |

| 4.4 MAC instruction flow in FU datapath                                     | 79  |

| 4.5 Data movement flow in FU datapath                                       | 80  |

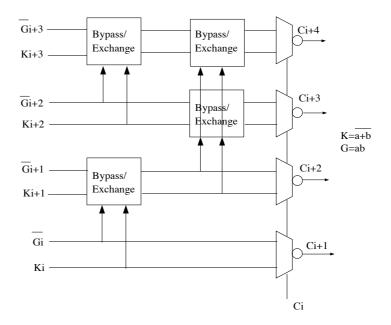

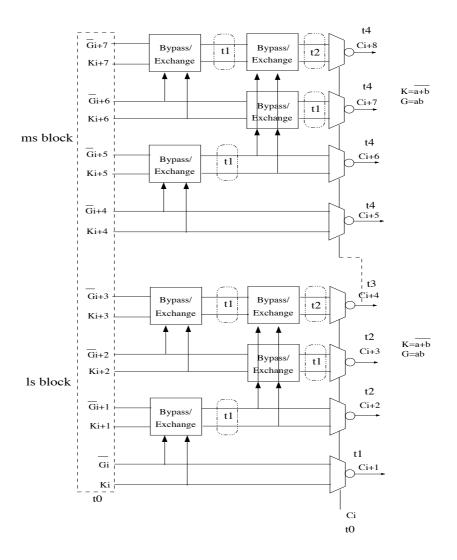

| 4.6 The structure of 4-bit carry-look-ahead tree block                      | 86  |

| 4.7 An example of the delay characteristic in an 8-bit CLA multiplexer tree | 87  |

| 4.8 The adder structure of this FU                                          | 87  |

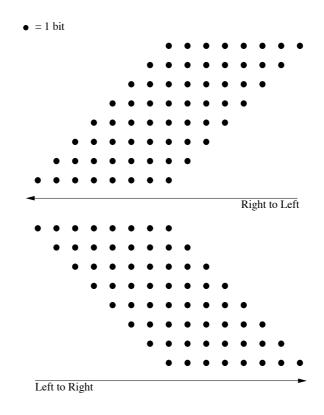

| 4.9 An example of the LR and RL in 8-bit parallel multiplier                | 90  |

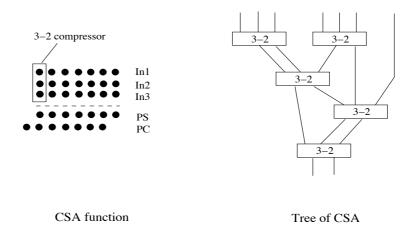

| 4.10 Carry save adder (CSA) and tree of CSA adder reducing 7 numbers to 2   | 90  |

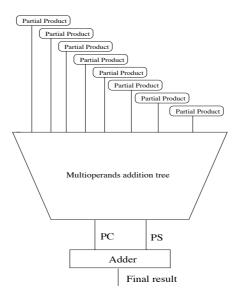

| 4.11 A general structure of 8-bit parallel or tree multiplier               | 92  |

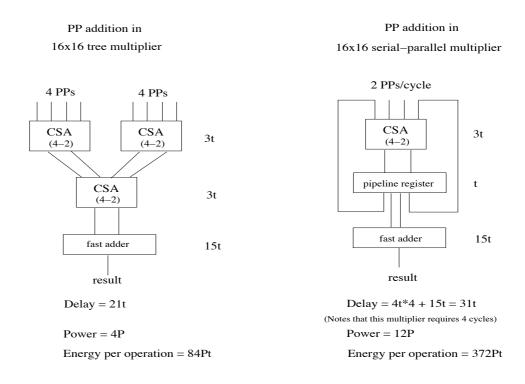

| 4.12 Energy estimation of serial-parallel and tree multipliers              | 93  |

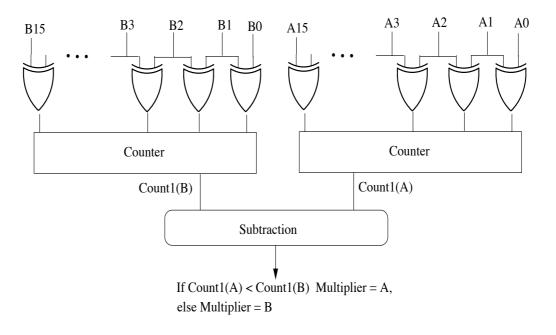

| 4.13 Determination block                                                    | 97  |

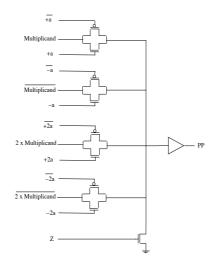

| 4.14 Partial product generator circuit                                      | 99  |

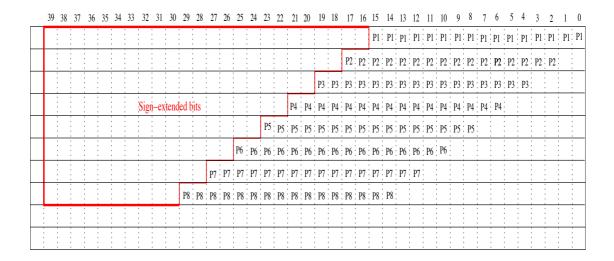

| 4.15 Eight PPs presented in excel worksheet                                 | 99  |

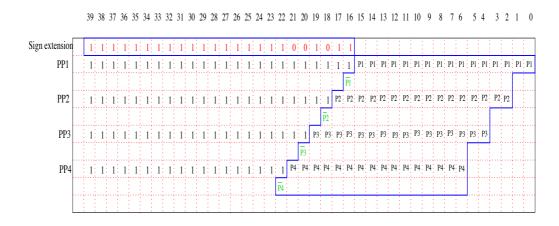

| 4.16 Pre-calculated sign extension                                          | 100 |

| 1                                                                           | 101 |

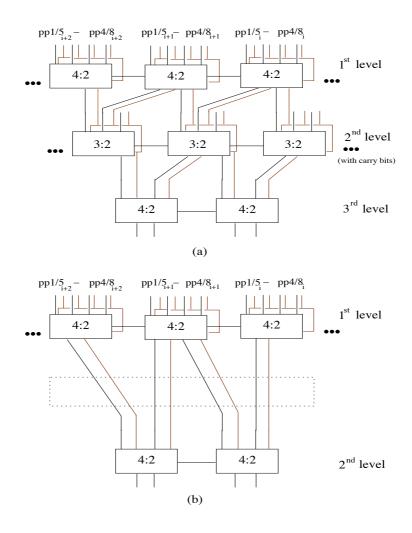

| 4.18 The conventional Wallce tree and this addition tree                    | 102 |

|                                                                             | 103 |

| 1 1                                                                         | 106 |

|                                                                             | 106 |

|                                                                             | 107 |

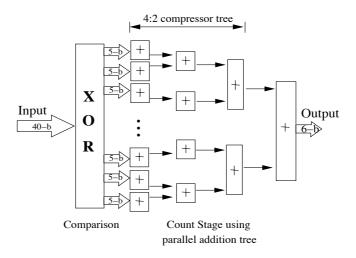

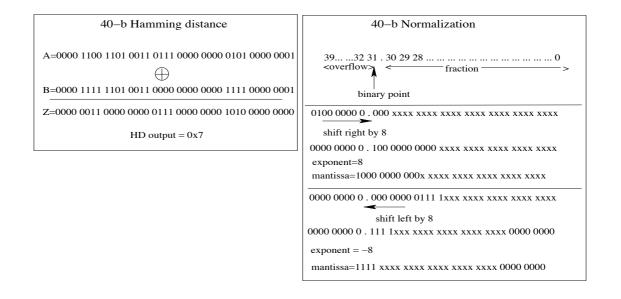

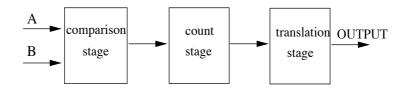

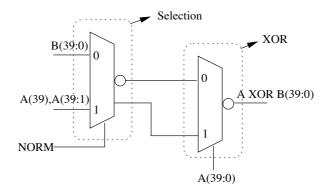

| 5.4 The first stage of HD and NORM operations.                              | 109 |

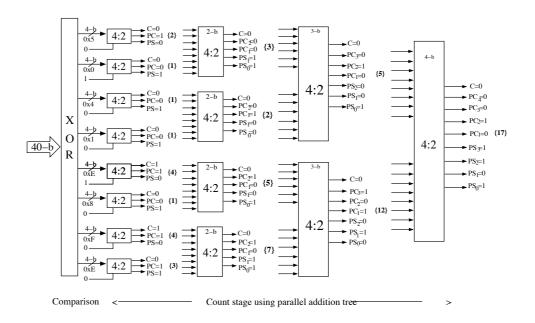

| 5.5 The parallel addition using 4-2 compressor                                 | 110 |

|--------------------------------------------------------------------------------|-----|

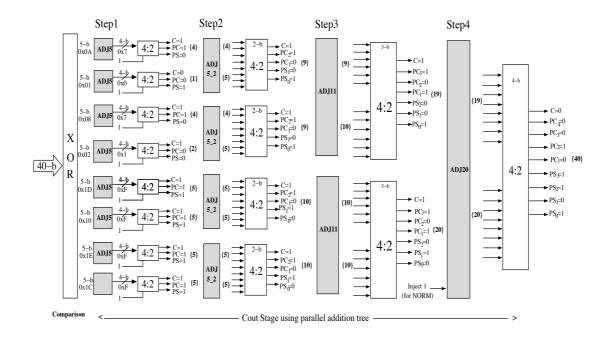

| 5.6 The population in each step of the NORM operation                          | 111 |

| 5.7 The example of the first adjusted component (ADJ5)                         | 112 |

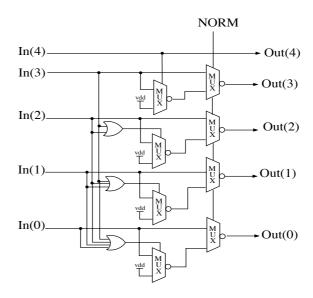

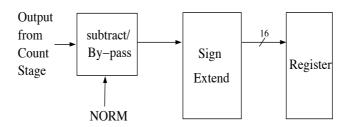

| 5.8 The translation stage diagram                                              | 113 |

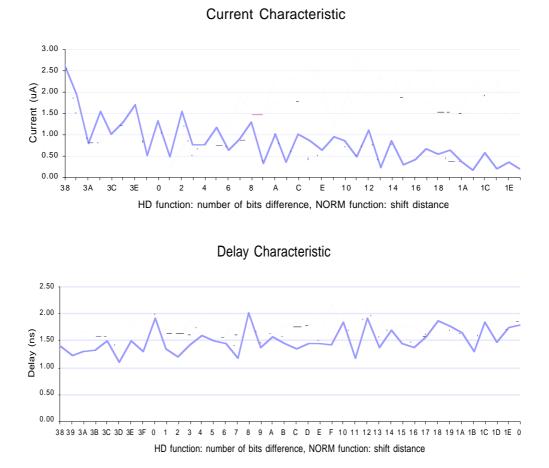

| 5.9 The delay and current characteristics of the HD and NORM circuits.         | 114 |

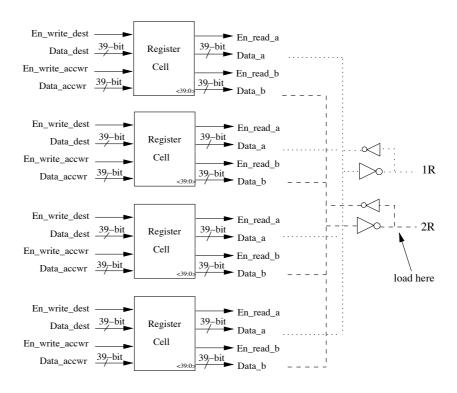

| 5.10 Accumulator register structure                                            | 116 |

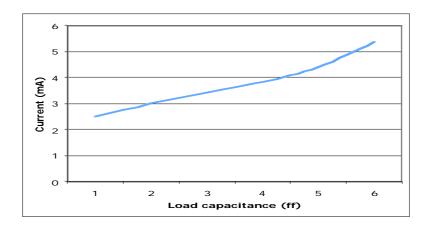

| 5.11 The relation between current and the amount of load in ACC                | 117 |

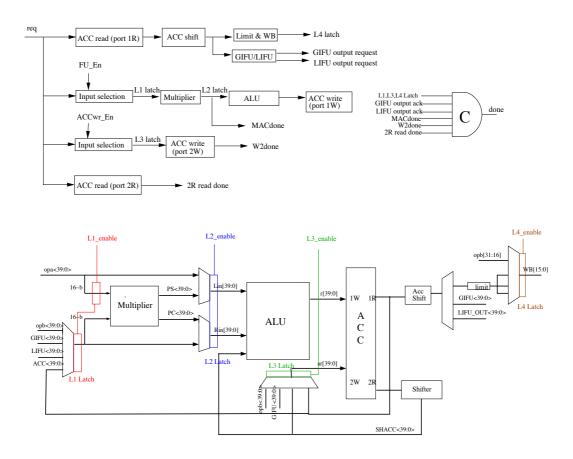

| 5.12 The control circuit diagram                                               | 119 |

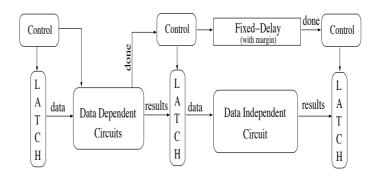

| 5.13 Bundled Data Asynchronous Structure                                       | 122 |

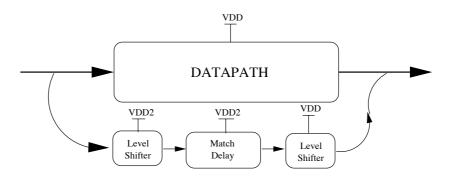

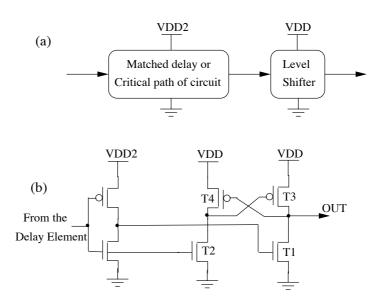

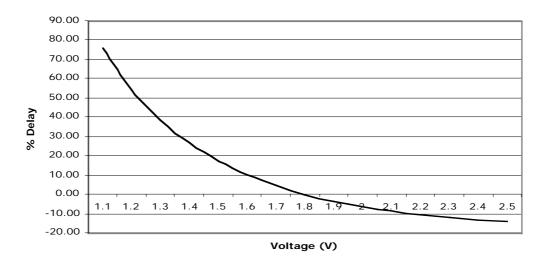

| 5.14 Tunable delay principle                                                   | 124 |

| · ·                                                                            | 125 |

|                                                                                | 126 |

|                                                                                | 127 |

| <del>-</del>                                                                   | 127 |

| •                                                                              | 128 |

| ·                                                                              | 129 |

| · · · · · · · · · · · · · · · · · · ·                                          | 129 |

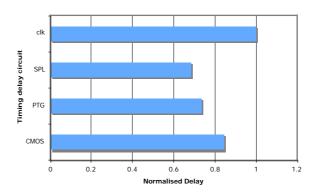

| 5.22 Relation between the normalised speeds of timing delay circuits for       |     |

|                                                                                | 132 |

| 1                                                                              | 135 |

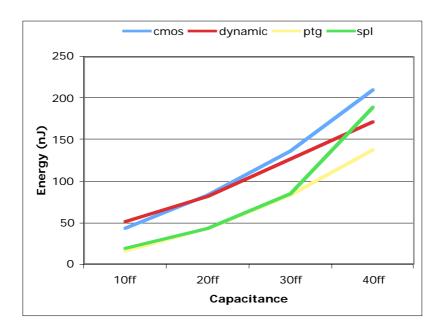

|                                                                                | 136 |

| $\mathcal{E}$                                                                  | 137 |

| <u>.</u>                                                                       | 139 |

| 1 1                                                                            | 140 |

|                                                                                | 141 |

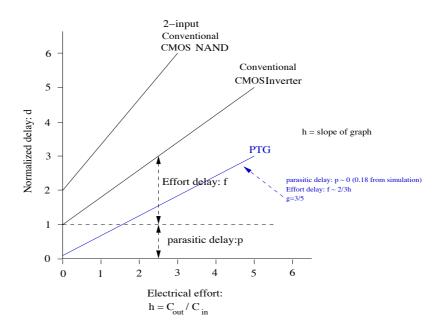

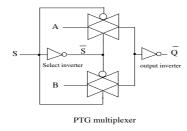

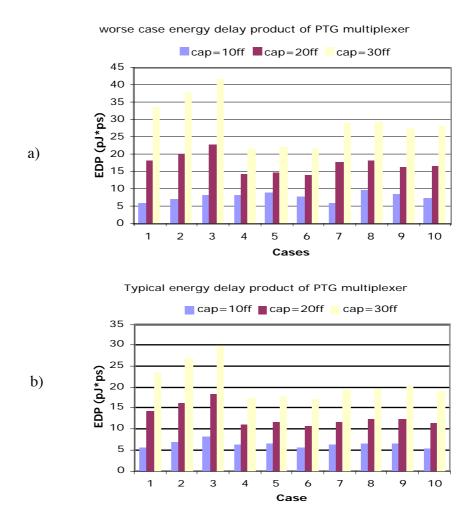

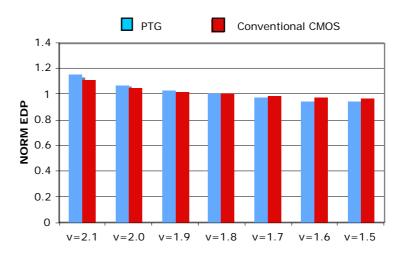

| 6.7 The relationship between normalized delay and electrical effort (h) of PTG |     |

|                                                                                | 143 |

| <u>.</u>                                                                       | 144 |

| 6.10 Effect of supply voltage on energy delay product in an 8-bit ripple       |     |

|                                                                                | 145 |

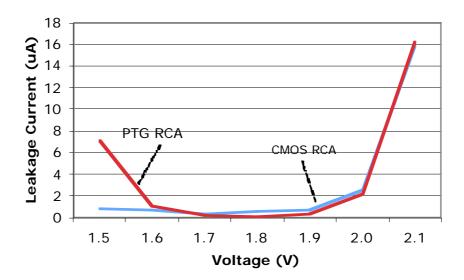

| 6.11 The relation between leakage current and scaling voltage of the CMOS      |     |

| <u> </u>                                                                       | 146 |

|                                                                                | 148 |

|                                                                                | 149 |

|                                                                                | 150 |

|                                                                                | 155 |

| 1                                                                              | 156 |

| 1 1 1                                                                          | 157 |

|                                                                                | 159 |

| 1 1                                                                            | 159 |

|                                                                                | 160 |

|                                                                                | 161 |

| <b>5</b>                                                                       | 164 |

|                                                                                | 167 |

|                                                                                | 173 |

|                                                                                | 174 |

|                                                                                | 177 |

| · ·                                                                            | 177 |

| 7.7 Comparison of distribution of energy throughout the original CADRE         |     |

| and the projected CADRE-s                                                  | 179 |

|----------------------------------------------------------------------------|-----|

| 7.8 Distribution of percentage energy throughout the Original CADRE versus |     |

| the projected CADRE-s                                                      | 180 |

## **List of Tables**

| 3.1 Mapping a arrangement FIR 20-tap filter ( $n = 0, 1, 2, 3$ ) onto four FUs         | 72    |

|----------------------------------------------------------------------------------------|-------|

| 3.2 A different data arrangement for the FIR 20-tap filter ( $n = 0, 1, 2, 3$ ) mapped | ed    |

| onto four FUs                                                                          | 73    |

| 4.1 The comparison of 40-b adders                                                      | 82    |

| 4.2 Modified Booth's recording                                                         | 91    |

| 4.3 Truth table of 4-2 compressor                                                      | 94    |

| 4.4 Partial Product Generator                                                          | 96    |

| 4.5 Power dissipation the different dynamic range inputs (multiplicand is              |       |

| constant)                                                                              | 97    |

| 4.6 Comparison of energy delay product of multiplier                                   | 103   |

| 6.1 Power and performance of 2-input multiplexers based on different type of           |       |

| pass transistor                                                                        | 138   |

| 6.2 Size of transistor of 2-1 PTG multiplexer                                          | 142   |

| 6.3 Six different input patterns                                                       | 150   |

| 6.4 Simulation results for the full adders at 1.8 V without output load                | 150   |

| 6.5 Simulation results for the full adders at 1.8 V with output load                   | 151   |

| 6.6 Simulation results for full adder sub-set with 8 inverters as the output           |       |

| load at different supply voltages.                                                     | 152   |

| 6.7 Simulation results for full adder sub-set with output load (8 inverters)           |       |

| with the 6 patterns of the sequence inputs                                             | 153   |

| 6.8 Energy saving of PTG XOR: standard cell versus full custom                         | 158   |

| 6.9 Metal usage summation for full custom datapath                                     | 160   |

| 7.1 Parallel instruction rates and operations per second                               | 170   |

| 7.2 Power and energy consumption of CADRE-s operated at 1.8V                           | 170   |

| 7.3 Break down average power, download and execution time of the CADRE-                | s 172 |

| 7.4 Instruction breakdown for the benchmark programs                                   | 174   |

| 7.5 Energy consumption during the execution time of CADRE-s a 1.6V                     |       |

| power supply                                                                           | 175   |

| 7.6 The average power consumption during the execution of the FU in                    |       |

| CADRE-s                                                                                | 176   |

| 7.7 Estimated energy consumption of using the FU in the original CADRE                 |       |

| architecture                                                                           | 178   |

| 7.8 Performance and power factor when process technology scaling to                    |       |

| 0.18mm@1.8V                                                                            | 181   |

| 7.9 Power per million instruction (mW/MHz2) of the commercial fixed-point              |       |

| DSPs                                                                                   | 181   |

| A.1 Top-level instruction specification                                                | 198   |

| A.2 Opcodes                                                                            | 198   |

| A.3 Configuration instruction specification                                            | 199   |

| A.4 CADRE-s chip pad pin (68-pin PGA package)                                          | 200   |

#### **Abstract**

In the last few years, the mobile market has grown extensively. The next generation of these 3G or 4G devices require much higher performance to operate the more complex algorithms required from increased functionality such as multimedia, voice recognition and internet access. As a consequence, the number of transistors required increases dramatically. Meanwhile, the energy density of existing battery technologies is not increasing at the same rate. Thus in order to have a longer battery operating time, energy efficient computing in a DSP assumes greater emphasis.

CADRE was designed and expected to be a minimum power consumption asynchronous DSP whilst meeting the performance requirements of next generation cellular phones. In the original CADRE, most of the research was focused on the algorithmic and architectural level design and resulted in a good energy economical design at these levels. However, the power dissipation of the original CADRE showed that approximately 50% of the overall power consumption was found to be dissipated in the functional units (FUs). Thus, reducing the power consumption of the FU was the primary motivation for the work described in this thesis.

The FU has been re-designed focusing on improving the energy efficiency at the logic, circuit and layout levels. Coherent design techniques have been applied. These include the use of pass gate logic, the sharing of the adder between the multiplier and adder, a combined logic block for performing the Hamming distance and normalization function and a new timing mechanism for better tuning the asynchronous control to the datapath. These functions reduce the amount of logic and possible failure of the system.

CADRE-s has been implemented as a full custom design and simulations are presented to successfully demonstrate the energy-efficiency of the FU. The results show that the FU designed can achieve an energy improvement by a factor of 5 in the multiply accumulator units and a factor of nearly 2 for the overall system compared with the original CADRE system. This demonstrates the importance that energy efficient logic, circuit and layout techniques contribute to a design.

#### **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification at this or any other university or other institute of learning.

### Copyright

- (1). Copyright in the text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) or copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

- (2). The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of the School of Computer Science.

#### The Author

After being born in the south of Phuket island, Thailand, Wannarat grew up and was educated by many wonderful teachers at many schools around Phuket city. She learnt about microelectronic design at King Mongkut Institute Technology of Ladkrabang (KMITL), one of the top three Thai universities in engineering. After joining the embedded system laboratory of KMITL for 2 years, she decided that the most interesting career would be as a researcher doing a fantastic microelectronic inventory for the country. However, being a researcher in Thailand was limited by funding sources. Thus she became a private research assistant for the laboratory at the Institute. Later, she was encouraged to do a master course in computer engineering at Chulalongkorn University which is the top Thai university in engineering. She spent 18 months in the microprocessor verification field, obtaining a master degree. She became a lecturer at Prince of Songkla University, returning to do research on microelectronics and also to be a member of the national IC design group.

Her main responsibility was teaching and developing the microelectronic laboratory for the 3rd year of the undergraduate computer engineering course. After spending a year setting up the machines and EDA tools, a Microcontroller and FPGA hardware laboratory were established for the third year course. A project of a talking chip using a FPGA, implemented by a senior student under her supervision received a third place award in the national microelectronic contest. In addition other projects such as a non-coding robot implemented on Complex Programmable Logic Device (CPLD), design and implementation of an ARM7 core, and a network protocol soft-core using VHDL, were developed during her time at the Prince of Songkla University. She joined the APT group at The University of Manchester in 2002.

## **Acknowledgements**

I would like to thank my supervisor Dr. Linda Brackenbury to give me a great opportunity and wonderful support both in term of technical questions and English. I also would like to thank my advisor Dr. Jim Garside for the circuit design inspiration and answers to many of my technical questions.

Special thanks go to Mr. Dave Clark for being a wonderful help with many technical problems, especially his brilliant support on the layout and Mr. Jeff Pepper who maintained and solved the Cadence and other CAD tools problems through adversity and gave help whenever difficulties were encountered.

Many thanks to everybody who has helped by proof-reading my thesis, especially Mrs Wendy Warburton who spent her time to correct my English. Thanks also to Dr. Andrew Bardsley and Dr. John Bainbridge for their useful comments on the thesis.

Thank you to the whole APT group who have somehow managed to put up with my silly ways and also badminton players who shared great fun with me.

Thanks to my parent who know nothing about microelectronic but are wonderful advisors of all kinds.

Thanks to Apinetr Unakul for his wonderful advice and inspiring me to do research work in this field when I was in Thailand.

The work presented in this thesis was funded by the EPSRC, grant number GR/N39159/01 and GR/561270/01. The author is grateful for this support.

# Chapter 1: Introduction

In the last few years, the number of applications of portable, battery powered electronic equipment has grown considerably. Pocket PCs, handheld PCs, hearing aids, portable military equipment and mobile phones are good examples. Nowadays, the third generation (3G) handsets serve as not only voice communication equipment, but also include data, image, multimedia and other complex functions. Furthermore, the next generations of mobile equipment will require even higher performance to operate more complex systems and to support the growing trend towards portable computing and wireless communication.

The enormous improvements in technology allows many functions to be integrated onto a chip. Thus, one chip can support an expanding range of functions, and multiple devices can be placed into a single unit [1]. The improvement in technology has opened up many possibilities for current and future mobile systems to expand functions. Future mobile systems will comprise a small personal portable computer and wireless communication device. An important feature will be the interface to and interaction with the user. Thus speech and pattern recognition will be key functions. Real-time multimedia data such as video, speech, and music will improve the productivity, usability, quality and enjoyment of future mobile systems. These require not only a high speed computation, but also a significant amount of computing power. Therefore, one of the most compelling issues in portable computing is to keep the energy consumption of the devices low in order to have a longer battery operating time.

High power consumption means a short battery life-time of the mobile application. In addition, high consumption causes a heat problem affecting the reliability and life-time of circuits as these depend on the power consumption. So high power consumption will become more critical in future because of the future mobile system requirements. In

addition, battery weight and life time are becoming more important than processing speed due to various microprocessors now running well in excess of 10 GHz. Thus in portable systems, energy consumption is the limiting factor in the amount of functionality that can be operated. For example, speech or hand writing recognition functions on an embedded system board needs about 20W to realize 20,000 words[2]. Unfortunately, the nickel-cadmium battery technology can provide only 35-57 Wh/Kg (Watt-hour per Kg.)[3]. Thus systems have to be designed to be more efficient in the way they use the energy. Consequently, energy efficiency can be informally defined as doing more work with the same amount of energy resource or doing the same work with less energy. This is the approach needed for portable systems having a limited energy budget.

Most portable systems have a Digital Signal Processor (DSP) operating as the main processing core. DSP programs are typically tight loops of arithmetic operations with fewer branches than general purpose code. Furthermore, DSP algorithms are used in real-time applications with different sampling rates. These require processing speeds from 20 MHz to over 500 MHz depending on their applications. Therefore, a significant challenge in the implementation of a DSP for portable systems is how to use the limited power source efficiently.

Using voltage scaling, low power circuit design and architectural modifications, such as parallelism and pipelining, can reduce the power dissipation by more than 100 fold as demonstrated in custom DSP ASICs[4]. With some low power processors widely used in portable devices[5], this has been at the expense of accepting a lower performance. Therefore, those processors achieve low power operation by running slowly. However, it is not suitable for a DSP application which requires both a high performance and power efficiency.

Another good example of a low power processor, which may not be the highest energy efficient processor for mobile systems, is the StrongARM[6]. [7] compares StrongARM with other contemporary processors because ARM designed StrongARM with energy consumption in mind from the start. However, StrongARM cannot achieve an energy efficient processing core in mobile systems because of the many additional features it includes. For this reason, the ARM7[6] was introduced and widely used in mobile systems thereafter. ARM7 also has many features such as branch prediction, a 16-bit thumb

decoder and so on, which are not required for signal processing systems. This is a large power overhead for a signal processor. Nevertheless, a DSP could take advantage of the superscalar and/or pipelined micro-architecture feature from the StrongARM or ARM7 processor to achieve an energy-efficient improvement. The ARM9E[6] was introduced to DSP systems with enhanced DSP functionality in response to the growing demand for greater signal processing capabilities. The need for a separate DSP can potentially be eliminated by adding DSP functionality into an embedded general-purpose processor such as the ARM9E. However, its ability for keeping its execution units supplied with operands, is limited by the lack of parallel move support.

Contemporary DSPs exploit parallelism by being organised as single-instruction multiple-data (SIMD), multiple-instruction multiple data (MIMD) or very long instruction word (VLIW) architectures. This achieves higher performance irrespective of the clock. These architectures were introduced to exploit the regularity of DSP algorithms. The motivation for these designs was to avoid high clock frequencies. This was because increasing the clock frequency is limited by technology and an increased frequency raises the power consumption in a circuit as power is proportional to frequency. Also, high frequencies usually require more complex logic to meet the clock speed. Therefore, parallel architectures have advantages for future mobile applications, especially in terms of energy efficiency.

VLIW processor chips have been used in non-portable commercial applications; for example, the TI TMS320C6000 DSP[8] is used in 3G base stations, in the Digital Subscriber Line (DSL) access multiplexers and in network concentration units. An alternative, attractive architectural approach employs a parallel 2D array of hundreds of small processors and used in (non-portable) applications such as image and video processing. This has been implemented by the PACT (Processor Array Computing Technology) Company who have been developing an eXtreme processor platform called XPP [9]. The power consumption and performance are set to rise exponentially in the future. Therefore even those architectures which are currently energy efficient will become high dissipation devices in the future. Hence energy efficient architectures are required and even more is the subject of this and other research.

The emerging trend for wireless based stations and voice channels in telecommunications systems are reconfigurable architectures and there is a small group of companies such as Elixent Ltd., Morpho Technologies and Quick Silver Technologies, who are all working on reconfigurable FPGA (Field Programmable Gate Array) Architectures. A reconfigurable DSP was introduced in some research work[10],[11] to achieve the system-on-chip (SOC) concept; this is rapidly becoming a reality, with the time-to-market and product complexity promoting the reuse of complex macromodules. As an alternative, an application domain specific architecture for digital signal processing, the Field Programmable Function Array (FPFA) has been employed[12]. Unfortunately, the draw back of this reconfigurable architecture over ASIC designs is their energy efficiency even though they are more flexible than ASICs.

#### 1.1 Motivation

Even those architectures which claim to be energy efficient digital signal processing components will not meet future needs as the power consumption is set to rise exponentially as will the performance required for portable applications. Therefore, these processors will have high power dissipation when future computing is considered. There is much research[13],[14] in this area resulting in architectural structures which are energy efficient. For examples, a novel asynchronous parallel architecture, named CADRE[14] has been designed in the School of Computer Science, University of Manchester. CADRE has expanded instructions to give a flexible VLIW capability including a large register file, instruction buffer and four functional units. It has been designed based on the sign and magnitude number representation and asynchronous circuit design. The compressed instruction was exploited to reduce long instructions. Even though CADRE has been designed to be an efficient CPU architecture for DSP processors, it requires a large amount of power as demonstrated in the original CADRE power results[14], [72].

Similarly, reducing the number of multiplications for general DSP algorithms such as finite impulse response (FIR) filters, infinite impulse response (IIR) filters, or fast Fourier transforms (FFT), has been developed to improve the energy efficiency[15]. Results for these show that whilst algorithm organization can make some contribution to power efficiency, the power consumption is still large. Moreover, developed or modified

algorithms cannot save the power dissipation if the DSP is implemented on power-hungry circuits, especially in the multiplier and adder, which contribute to a big part of the power consumption in a DSP. Therefore, another research angle to reduce and minimize the power budget is logic and circuit optimization with full-custom layout also contributing to a large part of the energy efficiency.

As is well-known, arithmetic operations, such as multiply or multiply-accumulate are frequently performed and are power hungry in the functional unit (FU) of a DSP. Therefore, this thesis looks at the functionality that a FU needs to perform and makes a low power version. This will then be compared to the (scaled) original design of the CADRE FU to demonstrate the significant power saving realised by low power logic and circuits. Whilst this is a study of a FU for a DSP, the techniques used are generally applicable to all digital logic gate design, yielding similar improvements elsewhere.

The CADRE FU has been re-designed based on two's complement number representation; the circuits for sign-magnitude computation were found to be more complex and larger than those used to compute in two's complement format because an extra circuit was required to produce a precise sign bit result. CADRE performed reasonably in the overall comparison to other DSP's as shown in [72]. CADRE's greatest benefit stems from the fact the complex algorithms can be executed efficiently by the parallel architecture through the use of compressed instructions and the register file. According to the requirement of the third generation of wireless communication, the digital signal processing circuit needs high computational performance, low-power dissipation and a high degree of flexibility. Embedded configurable memory within a FU offers the advantage of combining flexibility and low-energy by providing control signals mapping directly from algorithm to hardware. The encoding instructions are stored in a configuration memory which can be reconfigured by storing the instructions in advance at the start of each algorithm. This reduces the control overhead associated with instruction-set processors. Philips REAL DSP[16] and the Infineon CARMEL DSP[17] have embedded this feature as a single global configurable memory which is only used for special instructions. As a result, the flexibility and performance of the FU is limited. Therefore, an embedded configuration memory in each FU gains the user increased flexibility and performance.

The challenge in the work described here is to meet the requirements of future portable applications, such as multimedia mobile phones. These devices need a very small power budget, higher performance with an increased complexity approaching that of a desktop computer. This can be achieved by adopting a parallel architecture. However, parallelism without dropping the supply voltage leads to increased area and power. This can be reduced by trading any excess performance for power by reducing the voltage. The next challenge is therefore to increase the performance if the voltage is scaled downwards. Parallel FUs give increased overall speed and are relatively easy to exploit in DSP applications. Throughput is roughly proportional to supply voltage, so four-way parallelism allows a voltage reduction of up to four times. This translates to a 16 times power reduction per FU (corresponding to CV<sup>2</sup>) or 4 times overall compared with a single FU. Thus, reducing the power dissipation in a FU is the most effective way of power saving in a parallel DSP.

An energy efficient configurable DSP architecture framework with four power efficient FUs has been designed and implemented to demonstrate a high energy-efficiency DSP. Algorithms such as FIR filters and the FFT, have been transformed to parallel assembly codes and then mapped onto the framework. The binary codes are generated by assembler and then stored in each configuration memory at the start of algorithm. Self-time completion detection circuits in FUs are employed because of using a globally asynchronous framework. Additional advantages of this framework that arise from asynchronous timing are power saving, higher performance and low electromagnetic interference.

To support a power efficient design of FU, the major components such as the multiplier, adder, shifter, Hamming distance and normalization need to be optimized. In addition to logic optimization for these component, the logic is implemented with energy efficient circuits using the smallest number of transistors. Thus the FU is aimed at the next generation of wireless and portable applications, and should achieve the ultimate in power efficiency.

#### 1.2 Research Contributions

The goal of this research is to significantly improve the power efficiency of a FU for DSPs and to demonstrate this by combining four FUs running in parallel with configurable memories as well as a demonstrator framework. Several key research contributions are:

- Demonstration of the energy-efficient architectural framework comprising four asynchronous FUs and data memories for executing digital signal processing algorithms.

- Developing a flexible FU for the user and system programmer. This has led to

additional cost, particularly in the implementation of the configuration memory.

This cost can be justified by the flexibility and performance gained by users. In

particular, the use of configurable memory embedded in the FU is unique compared

with other DSPs such as REAL and CARMEL. This feature also allows each FU to

operate independently on different instruction streams.

- Showing that lowering power at the logic, circuit and layout makes a large contribution to overall power levels. The architectural framework will be fabricated on 0.18 um operating at 1.8V to evaluate the parallel DSP approach.

- Developing a large power improvement on an unusual low power FU datapath

particularly suitable for use in DSP's aimed at portable applications. This datapath

is an extended knowledge component combining many good low power circuit

design techniques in each component. This leads to high performance and keeps the

power dissipation of the FU low.

- Developing the FUs ability to keep the execution units supplied with operands by supporting parallel movement.

- Developing a technique to reduce the switching activities and the number of stages

of addition in the multiplier by using a parallel wallace tree structure and sharing

the final addition circuitry between the adder and multiplier. The use of a shared

adder has not previously been described.

Chapter 1: Introduction

- Considering addition and multiplication schemes for an energy-efficient DSP component.

- Developing a combined novel circuit for performing the Hamming distance and normalization functions.

- Designing a novel tunable timing mechanism to better tune the control logic to the data path.

- Developing the power-efficient and novel circuits necessary for a FU. In addition, the comparison of circuit families at 0.18 um geometry operates at 1.8 V. is presented.

- Investigating the power and energy efficiency when voltage scaling is applied.

- Identifying the contribution the design can make to future designs. The

implementation can be used on future Super-scalar Asynchronous DSP

architectures. This contribution is aimed at next generation designs requiring a high

performance and low power.

#### 1.3 Organization

Chapter 2 presents the principles of the hardware and algorithms for digital signal processing, and describes current and future general-purpose DSPs. The advantages and disadvantages of parallel general-purpose DSPs in terms of energy efficiency are discussed here. The features of DSPs for next generation mobile, wireless communication and multimedia applications are presented. This chapter also presents the sources of power dissipation and an overview of low power design techniques for CMOS circuits. How to minimize the power consumption in CMOS circuits is discussed here. The comparison of various logic families such as conventional CMOS, different pass transistor circuits and dynamic logic will also be given in this chapter. Finally, the chapter briefly looks at low power design at the different levels in the design hierarchy.

System design is presented in Chapter 3. The original CADRE architectural features and power results from simulation are discussed here. This chapter shows that despite good

design at the top levels, power efficiency is disappointing and the reason for this is that logic and circuits need optimizing; power consumption at circuit and logic level can be a large contributory factor to power. This chapter also presents an overview of the FU proposed in this research. The FU comprises a sophisticated arithmetic unit. The basic top level operation of the FU is demonstrated by the multiply-accumulate shifting with rounding instruction to show concurrence of many execution paths within each FU. The significant power consumption of the original CADRE multiplication and addition operations are given.

Chapter 4 presents the design of a low power high performance multiplier and adder. Different multiplier architectures are described. The strengths and weakness of these architectures for digital signal processing are discussed and concludes with the choices made for the new FU. The multiplier employs logic optimization. Techniques used in the multiplier such as input selection, pre-sign extension calculations, balanced inputs, completion detection, compressor circuits, partial product generator, Wallace tree reduction and forwarding of the carry signal scheme are explained. The implementation techniques for mapping both in 2-1 multiplexers and XOR/XNOR circuits efficiently onto Pass Transmission Gates are described. This chapter also presents the structure of the 4-input adder design which makes multiplication simpler but adds complexity to the adder which now has a 4-2 compressor at its front end. The comparison with 2-input adder structures are discussed. The carry look-ahead tree adder architecture is explained along with the timing analysis through the tree structure.

Chapter 5 presents the other necessary operations of the function unit such as the Hamming distance and normalization. The other components of the FU such as the shifter, accumulators, accumulate-shifter, limit circuits and control circuits including the timing tunable mechanism are described.

Chapter 6 presents an investigation into the most energy efficient logic family and low power circuit; as a result, Single-ended Pass transistor Logic (SPL) and Pass Transmission Gate (PTG) are identified as the most promising for energy efficient circuits. Chapter 6 also describes the investigation results from energy efficient circuits such as a novel XOR and pass-gate latch which are employed in the functional unit. The logical effort,

transistor sizing, dual supply voltage and layout design techniques are also presented for the design.

Chapter 7 presents the tests performed and the evaluation of the design. The floorplan of the whole chip and its area is given. Algorithms such as FIR, DCT (Discrete Cosine Transform) and simple vector dot product programs run on the FUs for testing are discussed as well as how to map algorithms to the FUs in an optimized way. Performance and power results of the FUs from running these algorithms are given and compared with the (scaled) original CADRE. Multiplier and adder results are discussed together with other research work.

Finally, Chapter 8 summarizes the contributions of the presented work and proposes directions for future research.

# Chapter 2: Background

The demand for portable computing and communication devices is growing exponentially. Increasingly such devices contribute to the improvement to the quality of life and are used to increase business productivity. Laptop computers, personal digital assistants and mobile phones are well-known examples of those portable and communication devices which provide the ability to process multimedia information and the ability to communicate information over a wireless communication channel. Digital Signal Processing is the key element underpinning the processing of multimedia information e.g. speed, audio and video.

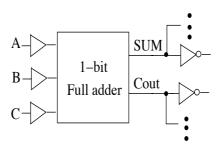

As is well-known, a general purpose processor is not well-suited to signal processing, control system applications and vice versa. Thus, the Digital Signal Processor (DSP) has been specifically developed for signal processing applications[18]. A DSP is targeted for use in arithmetic computation and contains many power hungry units such as a multiplier, adder, shifter and accumulator registers. These circuits are usually implemented and embedded in a block called a Functional Unit (FU). Therefore, reducing energy in a FU used in battery powered application would enable a DSP to operate within its limited energy resource.

This chapter describes the basic structure of a DSP, distinguishing between the characteristics of a general purpose processor and a signal processor. A modern DSP architecture and design techniques are then discussed in terms of energy efficiency. Then energy efficient design techniques ranging from the circuits and transistor level up to the architecture and algorithm level are explained in this chapter.

#### 2.1 Digital Signal Processor

Nowadays, Digital Signal Processing is widely used in a variety of applications such as IP telephony, radar, audio, digital TV, multimedia and handsets. This processing analyses information which comes from the real world as signals and converts these into digital numbers. DSPs are microprocessors specifically designed to handle digital signal processing tasks. Therefore, the characteristics of a DSP are different from a general purpose processor. In a DSP, one or more outputs,  $Y_i[n]$ , can be produced for n = ..., -1, 0, 1,... and i = 1...N corresponding to one or more discrete-time inputs,  $X_i[n]$ . The samples of input signals are quantized to a finite number of bits which is either fixed-point or floating-point. Generally, a DSP has to perform many millions of operations per second[19] and hence requires a large memory bandwidth.

Generally, a DSP can be classified into two types; the first type is for a specific application DSP, such as FFT-type (Butterfly operation), and the second type is a general purpose DSP. Both types of DSPs can be implemented as a programmable DSP by using a FPGA or implemented as a hardwired ASIC DSP. However, an ASIC DSP can offer a faster operation time and less power dissipation than a programmable DSP.

#### 2.1.1 How a DSP is different from a general purpose processor?

Since the 1960s, many processors have been developed for use in artificial intelligence equipment. However, the capabilities of those processors can be categorized into two areas; data manipulation and mathematical calculation. The data manipulation concerns storing information or organizing information such as word processing, database management or operating systems. The processor running this kind of task is occasionally used in mathematic calculation. In comparison, digital signal processing is concerned directly with mathematical calculations especially multiplication and addition. A common DSP algorithm is a FIR digital filter as shown in Figure 2.1, where 'x' is the input signal and the output signal is 'y'. The input signal is multiplied by a group of coefficients, a0,a1,... and then the products are summed. A group of coefficients is a filter kernel on the input signal. The coefficients will depend on each application.

Figure 2.1: An example of FIR operation in a DSP

In addition, DSPs require continuous processing and the timing depends on the sample rate to maintain a sustained throughput. In contrast, the operation of a general purpose processor to perform a word processing job may take two milliseconds or half of a second. This is because users will wait until the job is finished and then assign the next tasks. The most important aim is therefore to make DSPs run faster. Unfortunately, increasing the speed consumes more power and the design becomes more difficult and complex. Particularly, portable applications require a high performance and low power consumption.

#### 2.1.2 Digital Signal Processor Architecture

A traditional microprocessor architecture called *Von Neuman[17]*, contains a single memory and single bus for transferring data in and out of the processing unit. Obviously, a multiplication needs at least three clock cycles to get the instruction and two operands. The *Harvard Architecture* is therefore employed to improve the performance of the processor. With a Harvard Architecture, the memories are separated for each data operand

and program instructions, each memory has its own buses. Nowaday, most DSPs use this architecture to improve the speed. However, modern applications require a higher performance from a DSP. Analog Devices therefore invented the *Super Harvard Architecture*[21] by adding features such as an instruction cache and I/O controller to improve the throughput in their SHARC DSPs.

Figure 2.2 illustrates a Central Processing Unit (CPU). Within the CPU, a block such as a Data Address Generator (DAG) controls the address sent to the data memories. In a DSP, it is designed to be performed with circular buffers to avoid the overhead of keeping track of how the data is stored. In addition, bit-reversed address mode can be selected by the DAG to efficiently carry out the FFT algorithm. Another block in the CPU is for mathematical processing and this mainly consists of a multiplier, arithmetic logic unit and shifter. Instruction execution can operate with fixed-point or floating-point numbers. With the fixed-point format, the programmer needs to understand the amplitude of the numbers, the accumulation of quantization errors and what scaling needs to take place. There is no need to worry about these factors in a floating-point format. However, there is benefit to using fixed-point hardware rather than floating-point hardware for DSP development because many DSP applications require low-power and cost-effective circuitry, which makes fixed-point hardware a natural choice.

Figure 2.2: Typical DSP architecture

In a DSP processor, the programmer explicity controls which data and instructions are stored in the on-chip memory bank. The programmers have to write programs so that the processor can efficiently use its data and its instruction memory. In contrast, general purpose processors (GPPs) use control logic to determine which data and instruction words reside in the on-chip cache, a process that is typically invisible to the programmer. From the GPPs programmer's perspective, there is generally only one memory space for both data and instruction rather than two memory spaces of the Harvard architecture. Most DSP processors do not have any cache, they use multiple banks of on-chip memory and multiple bus sets to enable several memory accesses per instruction cycle.

DSP processors often support specialized addressing modes that are useful for common signal processing algorithms. Examples include circular addressing (which is useful for implementing digital-filter delay lines) and bit-reversed addressing (which is useful for performing a commonly used DSP algorithm, the fast Fourier transform). These specialized addressing modes are not often found on GPPs, which have to instead rely on software to implement the same functionality.

## 2.2 A Modern Digital Signal Processor Architecture

It becomes obvious that exploiting parallelism to speed up the processing is necessary in high data rate applications. The parallelism can be achieved by implementing different algorithms onto the different hardware components. However, different designs are required if the applications are changed. Another parallel approach is to employ a processor with a parallel datapath. By using this approach, different algorithms can be performed on a common architecture.

#### 2.2.1 Important features of DSP processor

The important features of DSP processors are repetitive numerical intensive tasks and special instruction sets to exploit hardware efficiency. Two of the most important features of modern DSP processor architecture aimed at low power are the datapath containing an energy efficient multiply-accumulate unit(s) and an energy efficient multiple-access memory architecture.

#### Datapath

From the reason for using fixed-point given in section 2.1.1, only a fixed-point DSP processor is discussed in depth in this thesis. The datapath typically incorporates a multiplier, adder, shifter, logical unit and other specialized functions such as Hamming distance and normalization. Multiplication is an essential operation and frequently used in DSP applications. In many DSP algorithms, multiplication is followed by summing the product with the sum of previous products. Therefore, most DSP processors integrate the multiplier with an adder so that the multiply-accumulate operation can be performed with one instruction. However, multiplication itself is based on an addition generally implemented using XOR and multiplexer circuits.

A shifter is usually required in a DSP processor for two purposes. One is to shift by any number of bits and is used to scale the result of the multiplier and adder which tends to grow in bit width. The shifter for this purpose can be implemented by multiplexers.

The other shift unit (a single bit shifter) involves dealing with overflow and saturation. When the magnitude of the sum exceeds the maximum or minimum value that can be represented in an accumulator register, the quantity overflows. Scaling down the result or saturation is required to handle the overflow situation and so yield a correct value.

#### **Memory Architecture**

The memory architecture including its interconnection with the DSP processor's datapath is important for the datapath itself. Consider the N-tap FIR filter. N multiply-accumulate operations are required to produced the new output every N instruction cycles. To achieve this performance, the memory needs to be accessed several times within one instruction cycle.

Typically, three memory banks, comprising one program bank and two data memory banks, are common in current DSP processors. With this feature, it is possible to perform a 1-tap FIR filter operation per instruction cycle. However, using a dual-ported memory which provides two simultaneous read operands only requires one operand memory bank. Therefore, some DSP processors use one single-ported program memory with one dual-

ported data memory. Finally, register-indirect addressing modes are used. Most DSP processors have an address generation unit (AGU) dedicated to address calculations. An AGU is used to calculate complex addressing in parallel with arithmetic operations.

A modern DSP processor has multiple functional units and multiple-access memory banks. Therefore special instructions are needed to specify the several simultaneous operations performed by the different functional units in one instruction cycle. Encoding instructions so that operations are packed into one instruction can also reduce the program memory size.

# 2.2.2 DSP for next generation mobiles and wireless communication

Currently, multiple time slots and processing in parallel are employed to speed up the throughput. Additional features such as MP3 and speech processing in handsets requires a high performance DSP whilst the power consumption needs to be low. A highly parallel architecture with Very Long Instruction Word (VLIW) architecture can increase the performance. Adelante Technologies produced a DSP called Saturn[23] with these properties. It has a highly parallel 96-bit VLIW architecture that is accessed using encoded 16-bit instruction words. Saturn was demonstrated using Viterbi butterfly operations. Normally, it takes about 11 clock cycles to complete in regular assembly code but in Saturn it takes only 2 clock cycles with two application specific instructions. This is a factor of 5.5 performance improvement. Unfortunately, gains in the power consumption have not been realised yet in this design.

LSI logic[24] presented the second-generation (G2) superscalar ZSP DSP architecture which is able to enhance the instructions per cycle (IPC) performance by nearly three times that of current architectures running various benchmarks. The ZSP600, as shown in Figure 2.3, uses a Prefetch unit (PFU) that can prefetch eight 16-bit words per cycle. The instruction cache inside the PFU needs to have the data required by the instruction sequencing unit (ISU) for any given fetch cycle. The ISU has the responsibility for the instruction fetch and decode, instruction grouping, and instruction issue. The ZSP600 has the capability of issuing up to six instructions per cycle to each of the six primary datapaths each comprising: two Address Generation Units (AGUs), two ALUs and two

multiplication/arithmetic units (MAUs). The core of the multiplication and arithmetic unit is multiply accumulate (MAC) logic. This MAC operation is fundamental to most DSP algorithms where successive products are computed and summed. Each of the primary datapaths are controlled by the pipeline control unit (PCU). The interrupt controller, the co-processor and debug interface and timer are also controlled by the PCU.

Figure 2.3: Block Diagram of ZSP600 DSP

The ZSP600 has a quad-MAC implementation. A dual-MAC datapath in a MAU allows two 16-bit MAC operations or one 32-bit operation to execute per cycle. Therefore, each MAU can accumulate the two 16-bit multiplications into a single accumulator or into separate accumulators.

In terms of power improvement, the ZSP600 has many levels of power saving. The first level is to control the power consumption by an instruction to idle the core, so the core is effectively shut down if it is not being used. An interrupt is used to wake the core when needed. The second level of power saving is to shut down any part of the primary unit by using the clock control unit; this can prevent unnecessary dynamic power dissipation. The

last level of power reduction is at the register level, allowing control logic within the ALU to determine the operations. So only the appropriate logic is active in the datapath. This prevents switching activity in the unused parts of the datapath. The design can achieve 300 MHz operation on a 0.13µm geometry. However, the ZSP600 core is available to customers as a licensable RTL design, no custom logic is used in any part of the design. Unfortunately, there is no detailed report of the power reduction achieved, only the performance improvement is provided. It should be noted that in an asynchronous DSP, the power dissipation equals zero when the core is not being used. Furthermore there is no power overhead in switching to full performance and so asynchronous operation should be considered for next generation DSPs.

Yuan-Hao Huang et. al[25], proposed a communication digital signal processor (DSP) suitable for massively parallel signal processing operations in orthogonal frequency division multiplexing (OFDM) and code-division multiple-access (CDMA) communication systems. This proposed architecture supports basic butterfly operations, single/double-precision error computation, and the add-compare-select (ACS) operation. The processor chip is fabricated using a 0.35µm CMOS technology. The fabricated DSP chip reaches a speed of 1.1 G MACs/s when operating in high-speed mode, and it achieves 4 M MACs/s/mW in the low-power mode.

The latest series of processors provided by Motorola are called DragonBall[26]. It has been proposed for use in smartphone applications. The DragonBall performs the applications processor processing and provides seamless integration with the Bluetooth wireless chipset and with the Innovative Convergence cellular platform. This new feature leads to a change and enhancement of the functionality in the applications' processor without the need to re-certify the cellular functionality of the Smartphone with carriers. Moreover, it is claimed that DragonBall can provide extremely low power consumption for extended battery life.

#### 2.2.3 DSP for multimedia signal processing

Another approach for performing DSP applications is centred around multimedia processing. Li-Hsun Chen et.al[29], proposed a reconfigurable DSP architecture which has 5 ALUs, 1 multiplier and 2 load/store units. This allows the special purpose DSP

architecture to have a better parallel processing capability for the MPEG-4 Video encoder. In a comparison of the block coding of the MPEG-4 Video, their DSP is nearly 25% more efficient than the TI TMS320C64X architecture. Moreover, it is 80% more efficient in the MPEG-4 video encoding process.

Hyunjune Yoo et. al[13], proposed a multimedia DSP (MDSP) chip for portable applications. Parallel processing techniques such as SIMD, vector processing and DSP schemes were used and four MAC operations ran in parallel. Therefore, the MDSP is able to handle a 2-D video signal and 1-D signal processing. Their DSP speed capability is 30 MHz. The design was implemented using Verilog-HDL and the synthesized core simulation results have shown a performance improvement on various algorithms such as FFT, IIR, FIR, BMA (Block Matching Algorithm) and convolution encoding.

#### 2.3 General Functional Unit for DSPs

The arithmetic unit is the main core of a DSP and operates on almost every cycle. The operands required can be stored in a data register file or be an immediate value. Multiplication, addition, multiply-accumulate and other necessary functions of digital signal processing are performed here. The 40-bit accumulators are also in this unit. As is well-known, the number of processing elements has been increased in a modern DSP. This leads to much research work proposing various low power or high performance arithmetic components such as multipliers and adders to try and achieve the optimal energy requirements of DSPs. However, more complex designs may require extra power and a delay in the overall system.

As already stated, the multiplier is based on adder circuits. The adder can be implemented based on XOR and multiplexer circuits. Therefore, optimal energy of basic cells such as XOR and multiplexer can contribute to the energy saving of the multiplier. However, this can only be applied in some particular multiply and add algorithms which are suitable for implementation with XOR and multiplexer cells.

#### 2.4 Energy Efficient Design

In this section, an overview of low-power design and the techniques to employ them from the structural level down to the logic and circuit level in the FU are described. Design techniques such as avoiding unnecessary activity, reducing the supply voltage, the logical effort for energy efficient circuits, the logic family selection, transistor sizing and layout considerations, are focused on in order to achieve an energy efficient design for a portable computer having a wireless communication system.

The capabilities of computation in portable applications have been rising exponentially but battery technology has improved only slowly. Therefore, the intensive and continuous computing of hand-held computers and other portable devices is becoming restricted by the sources of power and energy management. Consequently, a variety of energy reduction techniques at various levels are required.

#### 2.4.1 Energy Sources

Since 1990, the speed-power efficiency has increased tenfold every 2.5 years for general purpose processors and DSPs. The most difficult task for future mobile system designers is to attempt to pack more capabilities, such as multimedia processing, into a battery operated portable miniature package. The main problem is that there is no equivalent of Moore's Law in the case of battery technology. In particular, only a 20% improvement in capacity is expected over the next 10 years[30]. Figure 2.4 shows these trends[30] and it is clear that the energy density of existing battery technologies is far from what is needed.

The Nickel Metal Hydride (NiMH) battery was introduced in the late eighties. Its best qualities were that it was compact in size, had light weight and had a long battery operating time. In the early nineties, more energy was available in a Lithium Ion (Li-ion) cell compared to the Nickel Cadmium (NiCd) battery. [31] examined the batteries not only in terms of energy density but also service life, load characteristics, maintenance requirements, self-discharge and costs. Alternative chemistries were also evaluated against the Nickel Cadmium battery type. However, Ni-Cd is still used in low cost applications like portable CD/tape players. Although Nickel-MH batteries have roughly twice the energy density of Ni-Cd batteries, they have a shorter cycle life and are more

Figure 2.4: Improvement in technology[30]

expensive. So the most popular battery choice for Laptop, PDAs and cellular phones is the Li-ion batteries. However, Li-ion batteries can be unsafe when they are used improperly.

Fuel cells may offer a promising alternative technique. It is an electrochemical device that converts the chemical energy of a fuel directly to usable energy. A fuel cell running on methanol could provide power for more than 20 times longer than traditional Nickel Cadmium batteries in a comparably sized package[32]. Lithium Polymer is one kind of fuel cell. It has been established recently to make ultra thin batteries with less than 1 mm thickness[33]. It is expected to suit the needs of light-weight next-generation portable computing and communication devices. However, these batteries are still expensive to manufacture.

According to the slight improvement of the battery technology, it is clear that the energy density of existing battery technologies is far from what is needed. Hence, an energy efficient DSP becomes vital.

#### 2.4.2 Fundamental of low-power design

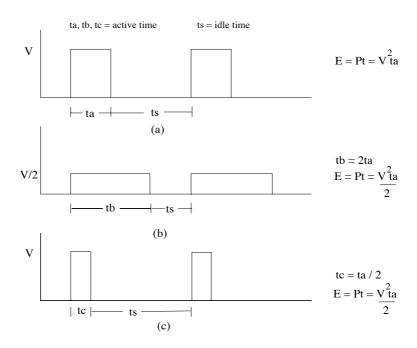

Most research work in low power design for battery driven applications is concerned with lowering energy consumption because of the finite energy source. Figure 2.5a shows a computation taking time ta when operated from a voltage V. This is followed by an idle time ts. Thus the energy consumed is proportional to  $V^2$ ta. When the supply voltage is scaled down by a factor of 2, Figure 2.5b, the execution time extends to tb = 2ta and the energy is  $\alpha V^2$ ta/2; the power reduces quadratically whilst the performance is reduced linearly. With lowering the supply voltage and running the task slowly so that the idling time is reduced, the implementor needs to be aware of leakage current in a small process geometry and aware of the timing overhead involved in changing the supply voltage. However, there is another approach to gain an energy saving as shown in Figure 2.5c. Here high speed logic operating from a supply of V is used to reduce the computation time to tc. Assuming tc = ta/2, the energy consumed is the same as that from scaling the voltage down as shown in Figure 2.5b. This approach depicted in Figure 2.5c is the one adopted in this work.

Figure 2.5: Energy versus voltage scaling

The power dissipation in a CMOS circuit needs to be explained before understanding energy and how to minimize it. Following this, an explanation of the several measurement metrics of energy efficiency are then described and the most suitable metric will be chosen to evaluate the FU of a DSP.

#### 2.4.2.1 CMOS Power Consumption

In digital CMOS circuit, there are three major sources of power dissipation as shown in the following equation[4]:

$$\begin{split} P_{avg} &= P_{switching} + P_{shortcircuit} + P_{leakage} \\ &= \alpha_{0 \rightarrow 1} \cdot C_L \cdot V_{DD}^2 \cdot f_{clk} + I_{sc} \cdot V_{DD} + I_{leakage} \cdot V_{DD} \end{split} \quad \text{... Eq. 2.1}$$

The switching or dynamic component of power consumption is the product of the load capacitance ( $C_L$ ), clock frequency ( $f_{clk}$ ), an activity factor,  $\alpha_{0\rightarrow 1}$ , is used to denote the average fraction of clock cycles in which a low-to-high transition occurs and the power supply  $V_{DD}^2$ . The second term is the power dissipated due to the direct-path short circuit current,  $I_{sc}$ , which occurs during switching when both NMOS and PMOS transistor are active. The last term is the power caused by the leakage current,  $I_{leakage}$ , which arises from substrate injection and sub-threshold effects. The leakage current becomes a significant problem when the fabrication technology is scaled down or when there are significant periods of idle time. In general, in an active circuit, the first term (the switching component) is by far the most dominant term with the short circuit current being generally 10% to 20%.

#### 2.4.2.2 Dynamic Power Consumption

Since each switching event in CMOS circuit expends energy  $\alpha_{0\rightarrow 1}C_LV_{DD}^2$   $f_{clk}$ , it is extremely important to reduce this source of power dissipation. Firstly,  $\alpha_{0\rightarrow 1}C_L$  needs to be minimized through the choice of logic function, logic style, circuit topology, data statistics and sequencing of operations. Looking at each of these in turn:

<u>Logic function</u>: Generally, each gate will have different static transition probabilities. For example, a 2-input static NOR gate is assumed to have only one possible input transition during a clock cycle and a uniform input distribution of high and low levels. So  $\alpha_{0->1}$  of this NOR gate will be  $3/16 \ (=p(0)(1-p(0))=3/4(1-3/4))$ . For a 2-input static XOR, the 0->1 transition probability equals  $1/4 \ (=1/2(1-1/2))$ .

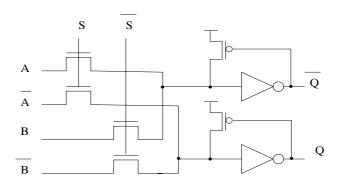

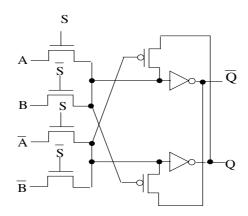

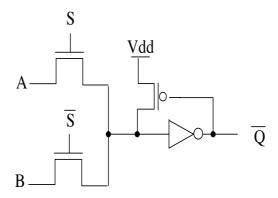

<u>Logic Style</u>: The logic style can give a different transition probability. Basically, the activity for the dynamic CMOS depends only on the signal probability, whilst the transition probability in the static CMOS depends on its previous state. So the static CMOS gate cannot be switched, if the inputs do not change. However, the amount of capacitance on the switching node and the sensitivity to supply voltage reduction are other factors for choosing a particular logic style.