# OPTIMISING DYNAMIC BINARY MODIFICATION ACROSS ARM MICROARCHITECTURES

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science and Engineering

2017

By Cosmin Gorgovan School of Computer Science

## Contents

| A        | bstra | let                                               | 11        |

|----------|-------|---------------------------------------------------|-----------|

| D        | eclar | ation                                             | 12        |

| C        | opyri | $\mathbf{ght}$                                    | 13        |

| A        | cknov | wledgements                                       | <b>14</b> |

| 1        | Intr  | oduction                                          | 16        |

|          | 1.1   | Dynamic binary modification                       | 16        |

|          |       | 1.1.1 General principles                          | 16        |

|          |       | 1.1.2 Uses                                        | 17        |

|          |       | 1.1.3 Overhead                                    | 17        |

|          |       | 1.1.4 DBM for ARM                                 | 18        |

|          | 1.2   | The ARM architecture                              | 19        |

|          |       | 1.2.1 Emergence                                   | 19        |

|          |       | 1.2.2 The ARM hardware ecosystem                  | 19        |

|          | 1.3   | Motivation                                        | 20        |

|          | 1.4   | Contributions                                     | 21        |

|          | 1.5   | Publications                                      | 22        |

|          | 1.6   | Thesis structure                                  | 23        |

| <b>2</b> | Bac   | kground and related work                          | <b>25</b> |

|          | 2.1   | Binary modification                               | 25        |

|          |       | 2.1.1 Static and dynamic binary modification      | 26        |

|          | 2.2   | Transparency                                      | 26        |

|          | 2.3   | The implementation of dynamic binary modification | 27        |

|          |       | 2.3.1 Tool injection / application loading        | 28        |

|          |       |                                                   |           |

|   |      | 2.3.2   | Code scanners                                                                                                                          | 29 |

|---|------|---------|----------------------------------------------------------------------------------------------------------------------------------------|----|

|   |      | 2.3.3   | Code caches                                                                                                                            | 30 |

|   | 2.4  | Branch  | linking                                                                                                                                | 33 |

|   |      | 2.4.1   | Direct branches                                                                                                                        | 33 |

|   |      | 2.4.2   | Indirect branches                                                                                                                      | 34 |

|   | 2.5  | Perform | nance overhead                                                                                                                         | 41 |

| 3 | Ove  | rview o | of MAMBO 4                                                                                                                             | 13 |

|   | 3.1  | Introdu | $action \dots \dots$             | 43 |

|   | 3.2  | Aims a  | nd current state                                                                                                                       | 44 |

|   | 3.3  | The Al  | RM architecture                                                                                                                        | 44 |

|   | 3.4  | Scratch | n space                                                                                                                                | 46 |

|   | 3.5  | Execut  | able loader $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                             | 47 |

|   |      | 3.5.1   | The userspace ELF Loader                                                                                                               | 48 |

|   | 3.6  | Code c  | ache                                                                                                                                   | 49 |

|   | 3.7  | Code s  | $\operatorname{canner}$                                                                                                                | 50 |

|   | 3.8  | System  | $\alpha$ call interception $\ldots \ldots $ | 51 |

|   | 3.9  | Test ar | nd development methodology $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                            | 51 |

|   | 3.10 | Plugins | 5                                                                                                                                      | 53 |

|   | 3.11 | Transp  | arency                                                                                                                                 | 53 |

|   | 3.12 | Summa   | ary                                                                                                                                    | 54 |

| 4 | Bra  | nch lin | king 5                                                                                                                                 | 56 |

|   | 4.1  | Introdu | $\operatorname{action}$                                                                                                                | 56 |

|   | 4.2  | Indirec | t branches $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                       | 56 |

|   |      | 4.2.1   | Function returns: low overhead return address prediction . 5                                                                           | 57 |

|   |      | 4.2.2   | Table branches: space-efficient linking $\theta$                                                                                       | 60 |

|   |      | 4.2.3   | Inline hash lookup for indirect branches $\theta$                                                                                      | 63 |

|   |      | 4.2.4   | Fallthrough branch linking                                                                                                             | 65 |

|   |      | 4.2.5   | Indirect branch target prediction $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                              | 66 |

|   | 4.3  | Direct  | branches $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                         | 67 |

|   |      | 4.3.1   | Direct branch linking                                                                                                                  | 67 |

|   |      | 4.3.2   | Eliding unconditional direct branches $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                               | 68 |

|   | 4.4  | Evalua  | $	ext{tion}$                                                                                                                           | 70 |

|   |      | 4.4.1   | Experimental setup                                                                                                                     | 70 |

|   |      | 4.4.2   | Contribution of different optimisations                                                                                                | 73 |

|          |       | 4.4.3   | Comparison of the space-efficient and fastBT table branch |     |

|----------|-------|---------|-----------------------------------------------------------|-----|

|          |       |         | linking schemes                                           | 74  |

|          |       | 4.4.4   | Overall performance                                       | 76  |

|          |       | 4.4.5   | Code cache size                                           | 79  |

|          | 4.5   | Summ    | nary                                                      | 81  |

| <b>5</b> | Mic   | roarch  | nitectural optimisations                                  | 82  |

|          | 5.1   | Introd  | luction                                                   | 82  |

|          | 5.2   | Traces  | 5                                                         | 83  |

|          |       | 5.2.1   | Trace heads                                               | 85  |

|          |       | 5.2.2   | Trace building                                            | 87  |

|          |       | 5.2.3   | Trace size limits                                         | 88  |

|          |       | 5.2.4   | Summary                                                   | 88  |

|          | 5.3   | Indire  | ct branches                                               | 89  |

|          |       | 5.3.1   | Hardware-assisted return address prediction               | 90  |

|          |       | 5.3.2   | Low footprint inline hash table lookup dispatch           | 93  |

|          |       | 5.3.3   | Adaptive indirect branch inlining                         | 96  |

|          |       | 5.3.4   | Huge pages                                                | 100 |

|          | 5.4   | Evalua  | ation                                                     | 101 |

|          |       | 5.4.1   | Experimental setup                                        | 101 |

|          |       | 5.4.2   | Trace creation threshold                                  | 103 |

|          |       | 5.4.3   | Overall performance                                       | 104 |

|          |       | 5.4.4   | Performance counter analysis                              | 105 |

|          | 5.5   | Summ    | nary                                                      | 122 |

| 6        | Cor   | nclusio | ns and future work                                        | 124 |

|          | 6.1   | Summ    | nary and conclusions                                      | 124 |

|          | 6.2   | Optim   | nisation selection guidelines                             | 127 |

|          | 6.3   | Portal  | bility to AArch64                                         | 127 |

|          | 6.4   | Future  | e work                                                    | 130 |

|          |       | 6.4.1   | Asynchronous multithreaded trace generation               | 130 |

|          |       | 6.4.2   | Automatic optimisation of DBM plugins                     | 131 |

|          |       | 6.4.3   | Dynamic microarchitectural optimisations                  | 132 |

|          |       | 6.4.4   | Trace layout optimisations                                | 132 |

| Bi       | bliog | graphy  |                                                           | 133 |

| A | Example plugin                 | 140 |

|---|--------------------------------|-----|

| В | The full evaluation results    | 142 |

| С | Raw performance counter values | 148 |

Word Count: 36686

## List of Tables

| 1.1  | Structure of the thesis                                                                                |

|------|--------------------------------------------------------------------------------------------------------|

| 3.1  | Linux system calls discarded, emulated or otherwise modified by<br>MAMBO                               |

| 4.1  | Number of branch mispredictions on Jetson TK1 with different implementations of shadow branches tables |

| 4.2  | Summary of geometric mean overheads for MAMBO, Valgrind and QEMU running SPEC CPU2006                  |

| 4.3  | Code cache size for SPEC CPU2006, in KiB and number of basic                                           |

|      | blocks                                                                                                 |

| 5.1  | Overview of the NET algorithm                                                                          |

| 5.2  | Comparison of MAMBO traces and NET                                                                     |

| 5.3  | Overview of the systems used for evaluation                                                            |

| 5.4  | The MAMBO baseline, $+traces$ and the configuration with the                                           |

|      | lowest overhead for SPEC CPU2006 on each system 104                                                    |

| 5.5  | Overhead under the baseline MAMBO configuration, on ODROID-                                            |

|      | XU3 (LITTLE cluster)                                                                                   |

| 5.6  | Overhead under the baseline MAMBO configuration, on ODROID-                                            |

|      | X2                                                                                                     |

| 5.7  | Overhead under the baseline MAMBO configuration, on Trons-                                             |

|      | mart R28                                                                                               |

| 5.8  | Overhead under the baseline MAMBO configuration, on Jetson TK1.110                                     |

| 5.9  | Overhead under the baseline MAMBO configuration, on APM X-C1.110                                       |

| 5.10 | Overhead of the <i>traces</i> optimisation (relative to baseline), on ODROID-                          |

|      | XU3                                                                                                    |

| 5.11 | Overhead of the <i>traces</i> optimisation (relative to baseline), on ODROID-                          |

|      | X2                                                                                                     |

| 5.12 | Overhead of the <i>traces</i> optimisation (relative to baseline), on Tronsmart R28                                                        | 113 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.13 | Overhead of the <i>traces</i> optimisation (relative to baseline), on Jet-                                                                 |     |

|      |                                                                                                                                            | 113 |

| 5.14 | Overhead of the <i>traces</i> optimisation (relative to baseline), on APM                                                                  |     |

|      | X-C1                                                                                                                                       | 114 |

| 5.15 | Overhead of the $hw_ras$ optimisation (relative to $+traces$ ), on ODROI                                                                   | D-  |

|      | XU3                                                                                                                                        | 115 |

| 5.16 | Overhead of the $hw_ras$ optimisation (relative to $+traces$ ), on ODROI                                                                   | D-  |

|      | X2                                                                                                                                         | 115 |

| 5.17 | Overhead of the $hw_ras$ optimisation (relative to $+traces$ ), on Tron-                                                                   |     |

|      | smart R28                                                                                                                                  | 115 |

| 5.18 | Overhead of the $hw\_ras$ optimisation (relative to $+traces$ ), on Jet-                                                                   |     |

|      | son TK1                                                                                                                                    | 116 |

| 5.19 | Overhead of the $hw_ras$ optimisation (relative to $+traces$ ), on APM                                                                     |     |

|      | X-C1                                                                                                                                       | 116 |

| 5.20 | Overhead of the <i>hugetlb</i> optimisation (relative to $+hw_ras + traces$ ),                                                             |     |

|      | on Jetson TK1.                                                                                                                             | 117 |

| 5.21 | Overhead of the <i>hugetlb</i> optimisation (relative to $+hw_ras + traces$ ),                                                             |     |

|      | on APM X-C1.                                                                                                                               | 117 |

| 5.22 | Overhead of the $ldm_pc_sr$ optimisation (relative to $+traces$ ), on                                                                      |     |

|      | ODROID-XU3.                                                                                                                                | 118 |

| 5.23 | Overhead of the $ldm_pc_sr$ optimisation (relative to $+traces$ ), on                                                                      | 110 |

| 5.04 |                                                                                                                                            | 118 |

| 5.24 | Overhead of the $ldm_pc\_sr$ optimisation (relative to $+traces$ ), on                                                                     | 110 |

| 5 95 | Tronsmart R28                                                                                                                              | 119 |

| 0.20 | Overhead of the $ldm_pc_sr$ optimisation (relative to $+traces$ ), on Jetson TK1.                                                          | 110 |

| 5 26 | Overhead of the $ldm_pc_sr$ optimisation (relative to $+traces$ ), on                                                                      | 119 |

| 5.20 | APM X-C1. $\dots$                                                  | 120 |

| 5.27 | Overhead of the <i>aibi</i> optimisation (relative to + <i>traces</i> ), on ODROID-                                                        |     |

| 0.21 | XU3                                                                                                                                        |     |

| 5.28 | Overhead of the <i>aibi</i> optimisation (relative to $+traces$ ), on ODROID-                                                              |     |

| 0.20 | $X2. \ldots \ldots$ |     |

|      | · · · · · · · · · · · · · · · · · · ·                                                                                                      |     |

| 5.29 | Overhead of the $aibi$ optimisation (relative to $+traces$ ), on Trons- |     |

|------|-------------------------------------------------------------------------|-----|

|      | mart R28                                                                | 121 |

| 5.30 | Overhead of the $aibi$ optimisation (relative to $+traces$ ), on Jetson |     |

|      | TK1                                                                     | 121 |

| 5.31 | Overhead of the $aibi$ optimisation (relative to $+traces$ ), on APM    |     |

|      | X-C1                                                                    | 122 |

| 6.1  | Optimisation selection guidelines                                       | 128 |

| 6.2  | Portability of the optimisations to AArch64                             | 129 |

| C.1  | The raw performance counter values for the native execution of          |     |

|      | SPEC CPU2006 on ODROID-XU3 (thousands)                                  | 149 |

| C.2  | The raw performance counter values for the native execution of          |     |

|      | SPEC CPU2006 on ODROID-X2 (thousands)                                   | 149 |

| C.3  | The raw performance counter values for the native execution of          |     |

|      | SPEC CPU2006 on Tronsmart R28 (thousands)                               | 150 |

| C.4  | The raw performance counter values for the native execution of          |     |

|      | SPEC CPU2006 on Jetson TK1 (thousands)                                  | 150 |

| C.5  | The raw performance counter values for the native execution of          |     |

|      | SPEC CPU2006 on APM X-C1 (thousands)                                    | 151 |

|      |                                                                         |     |

# List of Figures

| 2.1  | The components of a DBM system and the control flow between            |    |

|------|------------------------------------------------------------------------|----|

|      | them                                                                   | 27 |

| 3.1  | The ARM registers                                                      | 44 |

| 3.2  | Translation using scratch registers for an instruction which accesses  |    |

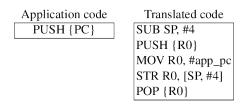

|      | the stack                                                              | 48 |

| 3.3  | Structure of an ELF file                                               | 48 |

| 3.4  | MAMBO data structures for an example basic block.                      | 49 |

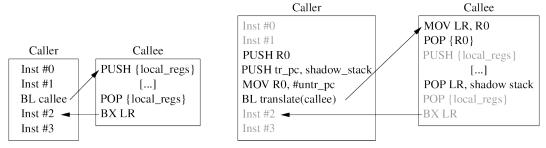

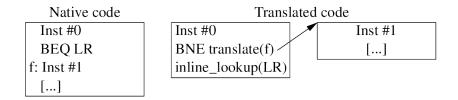

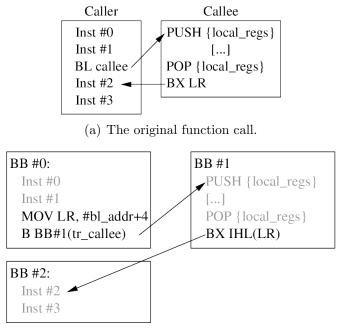

| 4.1  | Example of a typical function call and the translation generated       |    |

|      | by MAMBO                                                               | 57 |

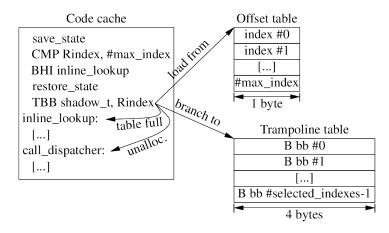

| 4.2  | Space-efficient shadow branch table                                    | 61 |

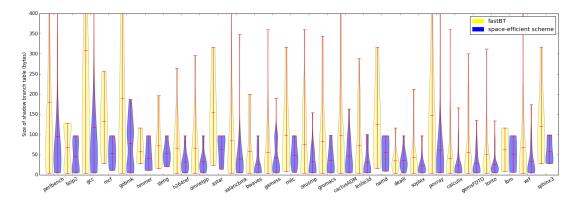

| 4.3  | Comparison of shadow branch table size for SPEC CPU2006                | 61 |

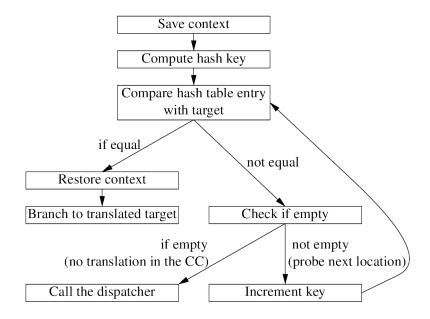

| 4.4  | Inline hash lookup routine                                             | 64 |

| 4.5  | Linking of fallthrough branches                                        | 66 |

| 4.6  | Comparison between translations with and without unconditional         |    |

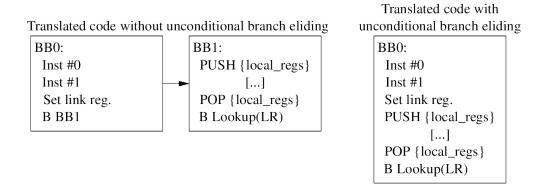

|      | direct branch eliding                                                  | 68 |

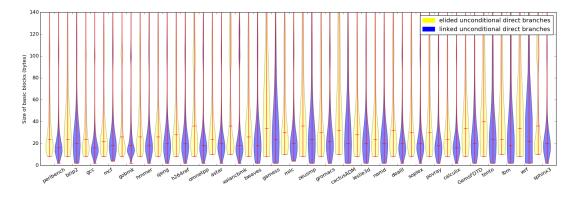

| 4.7  | Comparison of basic block sizes                                        | 69 |

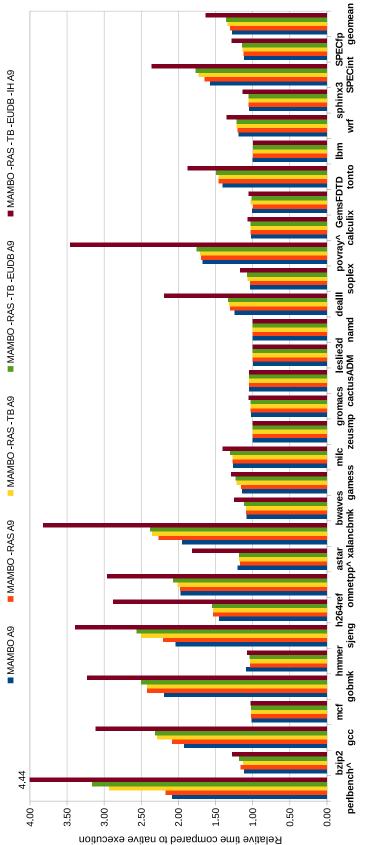

| 4.8  | Relative execution time for SPEC CPU2006 with the $ref$ dataset        |    |

|      | on ODROID-X2.                                                          | 71 |

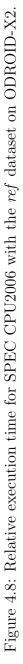

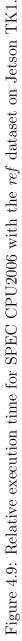

| 4.9  | Relative execution time for SPEC CPU2006 with the $ref$ dataset        |    |

|      | on Jetson TK1.                                                         | 72 |

| 4.10 | Relative slowdown for selected SPEC CPU2006 benchmarks with            |    |

|      | the fastBT table branch linking scheme.                                | 75 |

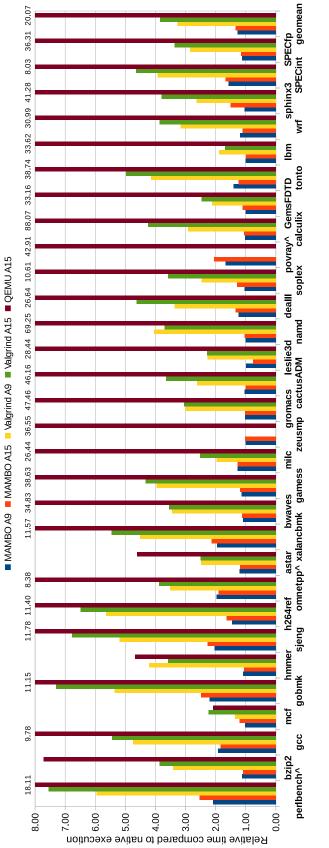

| 4.11 | Relative execution time for SPEC CPU2006 under MAMBO, Val-             |    |

|      | grind and QEMU ( <i>ref</i> dataset).                                  | 77 |

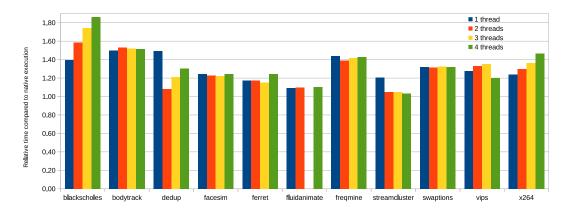

| 4.12 | Relative execution time for PARSEC 3.0 with the <i>native</i> dataset. | 79 |

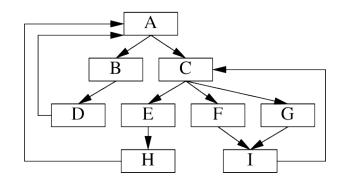

| 5.1 | Example control flow graph. Each box represents a basic block.     |     |

|-----|--------------------------------------------------------------------|-----|

|     | Block A, the entry point, contains a conditional direct branch,    |     |

|     | block C contains an unconditional indirect branch and all other    |     |

|     | blocks contain unconditional direct branches                       | 85  |

| 5.2 | Inline hash table lookup                                           | 89  |

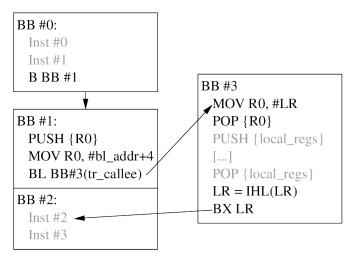

| 5.3 | Example of a typical function call                                 | 91  |

| 5.4 | Comparison of hit rates on a selection of SPEC CPU2006 bench-      |     |

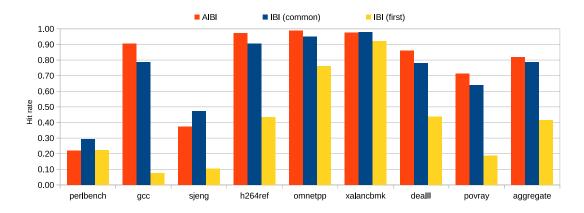

|     | marks for indirect branch predictors                               | 96  |

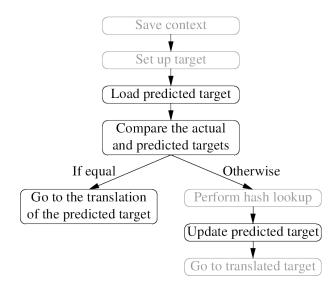

| 5.5 | Adaptive indirect branch inlining                                  | 98  |

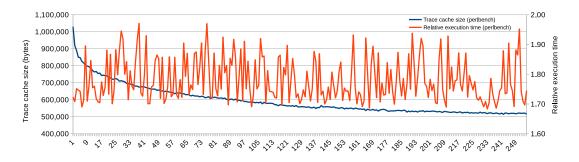

| 5.6 | Trace creation threshold vs relative execution time and trace code |     |

|     | size                                                               | 104 |

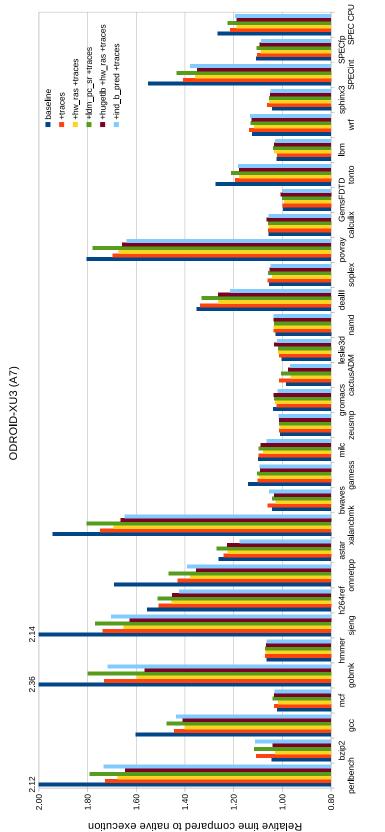

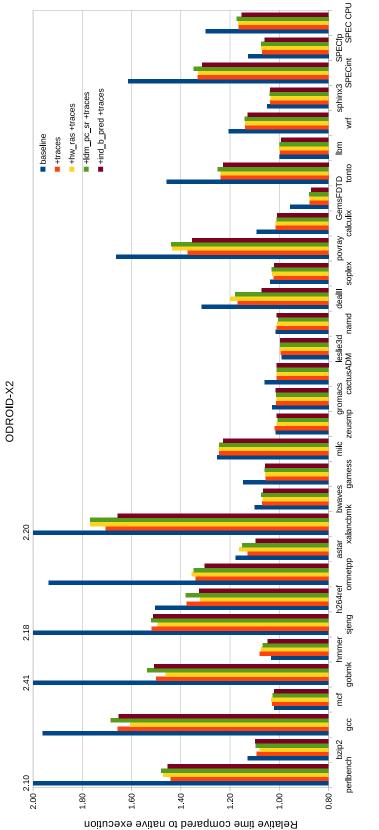

| B.1 | Relative execution time for SPEC CPU2006 with the $ref$ dataset    |     |

|     | on ODROID-XU3 - with microarchitectural optimisations              | 143 |

| B.2 | Relative execution time for SPEC CPU2006 with the $ref$ dataset    |     |

|     | on ODROID-X2 - with microarchitectural optimisations               | 144 |

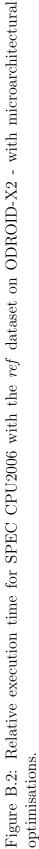

| B.3 | Relative execution time for SPEC CPU2006 with the $ref$ dataset    |     |

|     | on Tronsmart R28 - with microarchitectural optimisations           | 145 |

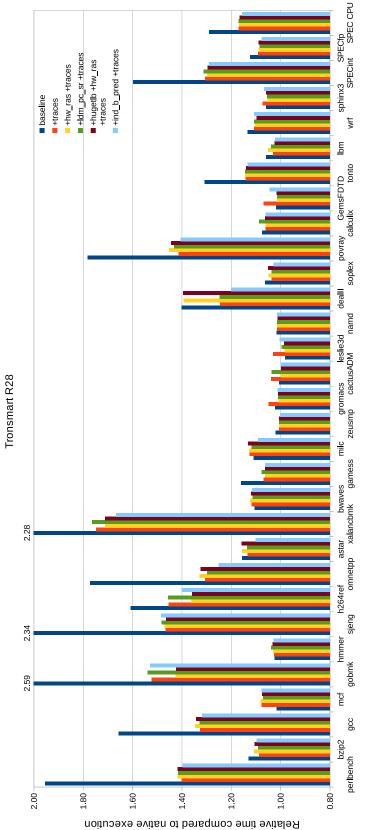

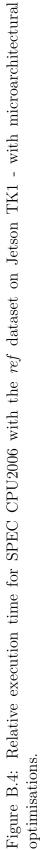

| B.4 | Relative execution time for SPEC CPU2006 with the $ref$ dataset    |     |

|     | on Jetson TK1 - with microarchitectural optimisations              | 146 |

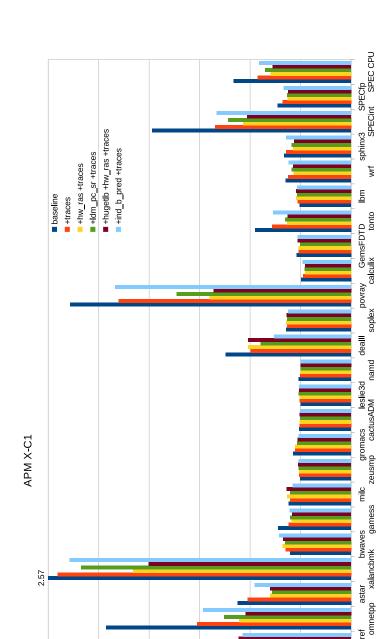

| B.5 | Relative execution time for SPEC CPU2006 with the $ref$ dataset    |     |

|     | on APM X-C1 - with microarchitectural optimisations                | 147 |

|     |                                                                    |     |

## Abstract

## OPTIMISING DYNAMIC BINARY MODIFICATION ACROSS ARM MICROARCHITECTURES Cosmin Gorgovan A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy, 2017

Dynamic Binary Modification (DBM) is a technique for modifying applications at runtime, working at the level of native code. It has numerous applications, including instrumentation, translation and optimisation. However, DBM introduces a performance overhead, which in some cases can dominate execution time, making many uses impractical.

While avenues for reducing this overhead have been widely explored on x86, ARM, an architecture gaining widespread adoption, has received little attention. Consequently, the overhead of DBM on ARM, as reported in the literature and measured using the available DBM systems, has fallen behind the state-of-the-art by one or two orders of magnitude. The research questions addressed in this thesis are: 1) how to develop low overhead DBM systems for the ARM architecture, and 2) whether new optimisations are plausible and needed.

Towards that end, a number of novel optimisations were developed and evaluated specifically to address the sources of overhead for DBM on various ARM microarchitectures. Furthermore, many of the optimisations in the literature were ported to ARM and evaluated. This work was enabled by a new DBM system, named *MAMBO*, created specifically for this purpose. MAMBO, using the optimisations presented in this thesis, is able to achieve an overhead an order of magnitude smaller than that of the most efficient DBM system for ARM available at the start of this PhD.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/ DocuInfo.aspx?DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses

## Acknowledgements

First of all, I would like to thank my supervisor, Mikel Luján, for his support, guidance and contributions during these past four years. His broad experience has been most helpful in guiding my research. In particular, Mikel has always encouraged me to consider the broader context, rather than getting caught up in the details of dynamic binary modification systems, for which I am thankful.

I would also like to thank Alasdair Rawsthorne for encouraging me to start a PhD and also for introducing me to the fields of dynamic binary modification and virtualisation. Had I not done the undergraduate final year project on system virtualisation for ARM, proposed and supervised by Alasdair, chances are that I would have never started this PhD.

I would also like to thank Oscar Palomar Perez, who has reviewed this thesis and has provided very useful and thorough feedback despite the tight timeline caused by my abysmal time management skills. Thanos Stratikopoulos has also provided feedback on this thesis, for which he has my gratitude.

I would like to thank Amanieu d'Antras and Guillermo Callaghan, the two other PhD students with whom I have worked on a regular basis. Amanieu was working on dynamic binary translation during the time I was working on dynamic binary modification. While we often do not agree on the finer points of mangling binaries, we have debated these points and occasionally joined efforts throughout most of our PhDs; MAMBO is all the better for it. Guillermo has been working hard on porting MAMBO to AArch64. He has made great progress and I am looking forward to putting the finishing touches together. Guillermo has also provided feedback on this thesis.

John Mawer has my gratitude for being the first user of MAMBO and providing valuable feedback and bug reports.

Last but not least, I will thank Amanieu, Mireya Paredes and Yaman Cakmakci for their support while we were writing up our theses at the same time. This brings us to the other residents of IT301, who deserve our gratitude for putting up with four of their colleagues being stressed and keeping strange hours over the past few months.

## Chapter 1

## Introduction

## 1.1 Dynamic binary modification

### **1.1.1** General principles

Dynamic Binary Modification (DBM) is a technique for modifying applications transparently while they are executed, working at the level of machine code. A system implementing DBM is called a *DBM tool* or simply a *DBM system*. To be able to modify the code at runtime, a DBM system must maintain control of execution by scanning and, where required, translating all code before execution. To perform a given task (e.g. to optimise or to instrument the code), additional (*optional*) modifications are performed. A *DBM framework* is a DBM system which exposes its functionality through an external API, enabling an external tool to apply optional code modifications. For example, DynamoRIO [Bru04], Pin [LCM+05] and Valgrind [NS07b] are DBM frameworks, while Dynamo [BDB00] and QEMU [Bel05] are DBM systems which are not DBM frameworks.

It shall be noted that since a DBM system deals with machine code, a large part of the implementation of such a system is architecture-specific. Therefore, an optimised DBM implementation is not easily portable to a different architecture.

DBM can be used both at the system level and at the userspace level. The main differences between the two consist of isolation and security challenges in the case of a system level DBM (while for userspace DBM systems these are mostly handled by the operating system) and handling of irregular changes to the execution flow: for userspace DBM these consist of signals (on Linux), while system level DBM has to handle hardware interrupts, exceptions and faults. This thesis explicitly deals with a userspace level DBM system. However, the proposed optimisations for branch handling are generally suitable for use in a system level DBM as well.

#### 1.1.2 Uses

DBM is a general purpose technique with numerous applications. Most uses of DBM can be classified in one of three categories: Dynamic Binary Instrumentation (DBI), Dynamic Binary Translation (DBT) and Dynamic Binary Optimisation (DBO).

*DBI* is a technique for dynamically adding instrumentation code. DBI is often used for fine-grained analysis of applications, since it allows data to be collected up to the level of individual instructions and data bits. One example of DBI is Memcheck [NS07a], a tool which allows sources of memory errors to be tracked at the level of individual bits and which was implemented using Valgrind [NS07b], a DBM framework.

DBT is a technique for efficiently translating software at runtime from one Instruction Set Architecture (ISA) to another one. At the system level, DBT has been used by Transmeta to run x86 software on their processors, which implemented a proprietary VLIW architecture [DGB+03]. DBT is also commonly used by Virtual Machine Monitors, for example QEMU [Bel05] and those developed by VMware [AA06].

*DBO* is a technique which uses runtime information to optimise machine code. For example, DynamoRIO has been used to show that even programs compiled with a high level of static optimisation can benefit from dynamic application of traditional optimisations [Bru04]. Additionally, microarchitectural optimisations have been demonstrated [Bru04]. Furthermore, the NVIDIA Denver processor is employing both DBT to execute ARM applications on a proprietary VLIW architecture and also DBO to optimise the translated code for the VLIW processor [BBTV15].

#### 1.1.3 Overhead

A general limitation of DBM is that it introduces various overheads compared to native execution, even if no optional transformations are performed. Such overheads include increasing the memory usage due to the data used by the DBM system and increasing the start-up time by having to inspect and patch the code before executing it. However, the most important overhead is the one affecting execution speed, even after the start-up phase. This overhead varies significantly between DBM systems, workloads and hardware architectures. The average overhead on the SPEC CPU benchmark suite can be as low as 10% for performance-optimised state-of-the-art DBM systems on the x86 architecture and as high as 1900% for less optimised systems.

Depending on the magnitude of the execution speed overhead, many of the uses described in Section 1.1.2 can become limited or even impractical. For example, if the performance of a DBT system is noticeably poor to its users, then the technology is unlikely to be deployed at all. Similarly, if a profiling or debugging tool using DBI has high overhead, it might become impossible to employ it in some cases (e.g. if the intention is to analyse a real-time video game which ends up running at a very low frame rate under the tool). Finally, it only makes sense to create a DBO tool when the overhead of the underlying DBM framework is low enough to be easily amortised.

The execution speed overhead is caused by multiple factors, however it is essential to note that the main source of overhead is the lower execution speed of the code after being patched by the DBM system and not the patching process itself. The reasons for the lower execution speed include: the additional instructions inserted for handling branches, in particular indirect branches, and those used to hide the DBM system from the application; also microarchitectural causes such as lower cache hit rates due to the increased code and data sizes and poor branch prediction rates in the modified code. Section 2.5 further discusses the causes of performance overhead identified in the literature.

### 1.1.4 DBM for ARM

The recent popularity of the ARM architecture, especially in the mobile and embedded markets, has created a demand for compatible DBM systems. However, both the literature and the existing DBM systems have almost exclusively focused on support for other architectures, especially x86. Consequently, ARM is supported by only two DBM / DBT systems (Valgrind [NS07b] and QEMU [Bel05]), neither of which is designed to achieve low overhead. Previously, an ARM port of Intel Pin has also been available [HK06], however 1) it has since been discontinued and 2) its overhead was around one order of magnitude higher compared to state of the art DBM systems for x86. The lack of publications and expertise on optimising DBM for the ARM architecture, together with the demand for such tools, both from academia and from industry, presented an interesting opportunity.

## **1.2** The ARM architecture

#### 1.2.1 Emergence

Development of fast, low power systems led to the wide adoption of powerful mobile devices in the form of smartphones starting from the late 2000s. This created the current situation of the consumer mobile device market dwarfing the traditional computer market and the tentative adoption of low power architectures for less traditional applications such as datacentres. These platforms have reached similar complexity with that of more performance-oriented architectures. Most recent developments aim to further improve power efficiency and performance using same-ISA heterogeneous multicore chips, such as ARM big.LITTLE, which combines a cluster of ISA-compatible low power processors and a cluster of high performance processors on the same chip [ARM13b].

### 1.2.2 The ARM hardware ecosystem

Multiple vendors are developing and commercialising ARM-based SoCs for different markets, such as smartphones and tablets, network appliances, embedded applications and network servers. Since these markets have different requirements, a wide range of ARM implementations are commercially available at the same time. There are two paths through which commercial ARM implementations are developed. First, an implementation can be licensed from ARM, which allows the vendor to tweak some microarchitectural parameters such as the size of caches and TLBs, but does not allow for fundamental changes to the microarchitecture. Alternatively, the vendor can develop their own implementation, which has to correctly support the ARM instruction set, however this allows complete freedom in designing the microarchitecture. Several vendors have chosen the second approach, further increasing hardware fragmentation.

Currently available implementations vary from single issue, in-order systems (e.g. ARM Cortex-A5) to high performance 6-issue out-of-order cores (e.g. Apple Twister) or cores designed for large multicore systems (e.g. APM X-Gene2, a 4issue out-of-order microarchitecture which can be used in clusters of 8 to 16 cores [SFY14]). Additionally, same-ISA heterogeneous multicores have been widely adopted.

The work presented in this thesis is applicable to the Application profile of the ARM architecture, i.e. ARMv7-A and ARMv8-A, which is used for general purpose computing. The ARM architecture also has a Microcontroller profile and a Realtime profile, which are used for microcontrollers and for hard real-time applications respectively. The latter two profiles are not within the scope of this document. Furthermore, ARMv8-A has introduced a 64-bit execution state called AArch64, while also providing a 32-bit state called AArch32, which is backwardscompatible with ARMv7-A. The techniques presented in the following chapters have been implemented for the 32-bit state only, due to the late availability of ARMv8 hardware and time limitations. Therefore, in the context of this document, the generic term ARM will be used to refer to the 32-bit execution state of ARM. Nevertheless, many of the optimisations presented in this thesis are expected to also apply to AArch64, with little or no modification. The compatibility of the optimisations with AArch64 is summarised in Section 6.3. The ARM ISA and the specific challenges it poses to DBM are discussed in Section 3.3.

### 1.3 Motivation

The ARM architecture, once almost exclusively found in embedded systems, is growing in adoption for general purpose computing, however most DBM systems and research have focused on the x86 architecture. This has resulted in the performance of DBM systems for ARM lagging behind; cf. Pin [LCM<sup>+</sup>05] or DynamoRIO [Bru04] on x86/x86-64. For example, Valgrind serialises multithreaded execution on ARM and x86/x86-64, while performance optimised DBM systems such as Pin and DynamoRIO do not. This raises two of the questions that this thesis addresses: (i) how to develop such DBM systems for the ARM architecture and (ii) whether new optimisations are plausible and needed.

Additionally, the ARM ecosystem poses unique challenges for high performance DBM systems because of the large number and wide range of capabilities of the commercially available implementations: from single issue, in order cores (Cortex-A5), up to 6-issue out-of-order cores (Apple Twister) and including less traditional implementations such as NVIDIA Denver (a 7-way VLIW processor using a combination of hardware and software DBT to run ARM code). These challenges are exacerbated by the wide adoption of single-ISA heterogeneous multicores (such as *big.LITTLE* [ARM13b]), which use different microarchitectures on the same System on Chip (SoC) and allow the migration of active applications from one type of core to another. This raises the question of whether it is possible to develop DBM optimisations which either improve or, at the very least, do not affect performance on all available systems and microarchitectures. Furthermore, are the results obtained by evaluating a DBM system on one or a small selection of systems relevant across the available platforms?

## **1.4 Contributions**

The contributions of this thesis are:

- developing a research DBM system, to enable optimising the key code manipulation algorithms for ARM 32-bit platforms; this system has been named MAMBO and is presented in Chapter 3;

- proposing the principle of *behavioural transparency* to relax the transparency requirements for DBM systems in order to minimise implementation complexity and improve performance (Section 3.11);

- comparing the performance of MAMBO against two other DBM systems, Valgrind and QEMU (Section 4.4.4);

- showing that due to the wide range of ARM microarchitectures commercially available, runtime selection of optimisations is desirable to achieve optimum performance (Section 5.4);

- microarchitectural optimisations for DBM, which take advantage of certain features of the hardware implementations:

- introducing a hot code profiling technique for the creation of *traces* while avoiding branch target prediction for poorly predictable branches or expensive modification of existing translated code (Section 5.2);

- introducing a novel technique to enable hardware return address prediction in a code cache without a software return address stack (Section 5.3.1);

- introducing a software indirect branch prediction scheme which allows effective prediction for polymorphic indirect branches (Section 5.3.3);

- introducing a technique aimed at reducing the data cache and TLB footprint of the inline hash table lookup routine used in the translation of indirect branches on ARM (Section 5.3.2);

- introducing the use of huge pages to reduce the TLB pressure created by running modified code from a software code cache (Section 5.3.4);

- architectural optimisations for DBM, which mainly aim to reduce the dynamic instruction count:

- introducing a novel return address prediction scheme which trades off guaranteed transparency for improved performance (Section 4.2.1);

- introducing an improvement of the fastBT [PG10] table branch linking scheme, which is implemented more efficiently on ARM and reduces the memory space requirements on all architectures (Section 4.2.2);

- describing how to implement and configure several other established DBM optimisations for ARM (Sections 4.2.3, 4.2.4 and 4.3); and

- evaluating and providing a detailed analysis of the effectiveness of these optimisations when running on a wide range of microarchitectures (Sections 4.4 and 5.4).

## 1.5 Publications

The material from Chapters 3 and 4 appears in the following journal publication:

MAMBO: A LOW-OVERHEAD DYNAMIC BINARY MODIFICATION TOOL FOR ARM. Cosmin Gorgovan, Amanieu d'Antras and Mikel Luján. In ACM Transactions on Architecture and Code Optimization (TACO), 13 (1), 14, April 2016.

The material from Chapter 5 is based on the following submission-pending paper:

• OPTIMISING DYNAMIC BINARY MODIFICATION ACROSS ARM MICROAR-CHITECTURES. Cosmin Gorgovan, Amanieu d'Antras and Mikel Luján. Other related publications:

OPTIMIZING INDIRECT BRANCHES IN DYNAMIC BINARY TRANSLATORS. Amanieu d'Antras, Cosmin Gorgovan, Jim Garside and Mikel Luján. In ACM Transactions on Architecture and Code Optimization (TACO), 13 (1), 7, April 2016.

### **1.6** Thesis structure

Chapter 2 presents the organisation and components of a DBM system and the interactions between them. The chapter then continues with a literature review of the existing optimisations for these components, in particular for the *code cache* and for *branch linking*. The final section of the *Background* chapter discusses the performance overhead of state-of-the-art DBM systems. Chapter 3 then presents an overview of the MAMBO system. This chapter defines the aims of the system and then presents the design decisions which were taken towards those aims, in the context of the larger design space presented in Chapter 2.

Chapter 4 starts presenting the novel contributions of this thesis related to branch linking, which is one of the major sources of overhead for DBM systems. Existing linking techniques are also discussed in the context of efficiently implementing them for the ARM architecture. The chapter includes an evaluation, conducted on two commercial ARM systems, using two different microarchitectures. The evaluation is done both for each individual optimisation separately and also for the overall system performance, in comparison to the Valgrind and QEMU systems. At this point, the overhead of MAMBO is significantly lower than the overhead of the other two systems. This is considered the *baseline* version of MAMBO, which achieves lower overhead than the other DBM systems available for ARM, but slightly higher than the state-of-the-art DBM systems. Chapter 5 then continues presenting novel optimisations for reducing this overhead, however the focus is shifted from optimising at the architectural level (i.e. implementing operations using a low number of instructions) to optimising for the underlying microarchitectures. For example, the techniques presented in this chapter prioritise efficient use of the memory subsystem and good branch prediction over a low dynamic instruction count. Due to the nature of these optimisations, their evaluation is done on five different microarchitectures with a wide range of capabilities. In addition to the execution time, the hardware performance counters

are used to measure the effect of each optimisation on the microarchitecture, by counting events such as cache, branch prediction and TLB misses.

Chapter 6 summarises the contents of this thesis and the conclusions which have been drawn. Based on these conclusions and the various behaviours observed in the evaluation of the existing system, a number of avenues for future optimisation are suggested. Furthermore, a possible approach towards automatic optimisation of instrumentation code inserted via the plugin API of MAMBO is proposed.

Table 1.1 summarises the structure of this thesis.

| Chapter 1 | Introduction, motivation, contributions and publications. |

|-----------|-----------------------------------------------------------|

| Chapter 2 | Background and related work.                              |

| Chapter 3 | Overview of MAMBO, the DBM platform.                      |

| Chapter 4 | Linking techniques for indirect and direct branches.      |

| Chapter 5 | Microarchitectural optimisations, including traces.       |

| Chapter 6 | Conclusions and future work.                              |

Table 1.1: Structure of the thesis.

## Chapter 2

## Background and related work

## 2.1 Binary modification

Binary modification is a technique for modifying computer programs at the level of machine code. It is used either when 1) the source code or toolchain required to re-build the code are not available, or 2) when it is desired to preserve parts of the machine code intact. The first case is fairly clear: without the ability to access and modify the source code and then to rebuild the program from the updated source code, the only alternative is to modify the native code. However, the second case deserves further explanation. Let us take the example of instrumentation being used to obtain code execution traces, for the purpose of architectural simulation. This could be implemented by modifying the source code by adding an instrumentation procedure and a number of calls to it. However, the additional instrumentation code would change the original layout of the executable and therefore affect the addresses recorded in the execution trace. Furthermore, the compiler and linker will observe and optimise the instrumented code, possibly changing the generated machine code even more in terms of control flow, generated instructions and their scheduling. In practice, an application instrumented by modifying its source code will provide an insight into its own behaviour rather than into the behaviour of the original, uninstrumented application. This is often undesirable, including in this example. On the other hand, at the level of native code, it is practical to observe the original code, and then insert instrumentation with minimal disturbance.

### 2.1.1 Static and dynamic binary modification

There are two approaches to binary modification: static binary modification and dynamic binary modification. Static binary modification is altering the program ahead of its execution. Its main advantage is that it can have minimal or no overhead compared to the original executable. However, it is not universally applicable because of the *code discovery problem* [HM80]: for non-trivial programs, it is impossible to accurately determine which locations contain code and which locations contain data ahead of time, therefore it will suffer from incomplete coverage, when code is misidentified as data and incorrect modification, when data is misidentified as code. Additionally, static binary modification cannot be used for Just-In-Time-compiled code and self-modifying code.

Dynamic binary modification avoids the code discovery problem by identifying the code just before it executes: instead of statically scanning and modifying the whole executable, this is done in single-entry and single-exit units called *basic blocks*. The first basic block is scanned at the entry point of the program, stopping when the first control flow instruction is encountered. Once the basic block has finished executing, the target address of the control flow instruction is used to scan the second basic block, and so forth. This approach may not have complete coverage of all static code regions, however it will capture all code that is executed and will not misidentify code and data. Furthermore, it is compatible with Just-In-Time (JIT) compilation and self-modifying code. Therefore, DBM is a universal solution to the binary modification problem. However, this process introduces a number of overheads, which can have a high impact on performance. Avoiding and amortising these overheads is the aim of DBM performance research.

### 2.2 Transparency

A key concept related to DBM is *transparency*, which refers to preventing the code being modified from observing any changes compared to native execution. There are multiple *types* of transparency (i.e. what kind of changes can be observed) and also various *degrees* of transparency (i.e. how can the changes be observed and how likely are they to interfere with correct execution).

Bruening [Bru04] classifies the types of transparency in three categories, depending on how they are handled by DynamoRIO. The first category includes the resource usage conflicts (e.g. library transparency, I/O transparency), which are handled by avoiding to share resources between the application and DynamoRIO. The second category includes the types of transparency which can be provided by *leaving the application unchanged* (e.g. thread transparency, data transparency). The third category includes the types of transparency which require specific handling by DynamoRIO (e.g. application address transparency, debugging transparency).

Some types of transparency can be fully supported with minimal implementation complexity and overhead. For example, library transparency can be implemented by statically linking any libraries used by the DBM tool and ensuring that no data is shared between the copy used by the DBM tool and any copies which might be used by the application. Other types of transparency are impractical to fully support or would have a high overhead, e.g. timing transparency.

Many DBM tools are designed to support the best degree of transparency for as many types of transparency as possible. However, this goal can directly conflict with the goal of minimising execution overhead. At the same time, implementing some types of transparency can have a major impact on the design of a DBM system and require significant development effort, while only being required to correctly execute very few applications.

## 2.3 The implementation of dynamic binary modification

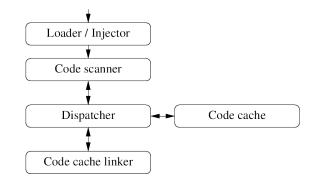

Figure 2.1: The components of a DBM system and the control flow between them.

Figure 2.1 shows the major components of a DBM system. The entry point is the mechanism which allows the DBM system to take control over the execution of an application (the *Loader / Injector*). There are two major approaches to doing so: either launching the DBM system first and then *loading* the application or, alternatively, *injecting* a DBM system into an already running process. These are further explored in Section 2.3.1.

Once the DBM system has control of a process, it must inspect and modify the code of the application. This is done by the *code scanner*, which is further discussed in Section 2.3.2. The modified code produced by the code scanner is then typically stored in a software *code cache* (Section 2.3.3), from where it can execute multiple times to amortise the overhead of the code scanner. To efficiently transfer control between different basic blocks, they are linked together by the *code cache linker* (Section 2.4). Because code is dynamically discovered and then scanned at runtime, execution of the modified code, of the code scanner and of the linker is interleaved. Control transfers between the code cache and the other system components is managed by a *dispatcher*, which preserves the context of the application on exit from the code cache and then restores it back when returning.

### 2.3.1 Tool injection / application loading

DBM systems generally run in the same thread and memory space as the application to be modified. It follows that before the DBM system can start executing the application, both executables (the DBM system itself and the application) have to be loaded in the memory space of the process. This can be achieved using one of two approaches: **Injection**, when the application is launched in the regular way, using the system loader and dynamic linker. After loading has completed, the DBM system injects itself into the same memory space. Injection has been implemented mainly using two mechanisms: LD\_PRELOAD, which is a feature of the dynamic loader on GNU/Linux systems which forces the loading of specific shared object files in a process. A DBM system can inject itself by using this feature, and then it can take control of execution by declaring a *con*structor function, which the dynamic linker calls before the main function of the application. This approach is simple to implement because it delegates loading to the system software. However, this method is fundamentally incompatible with statically compiled applications. It can also allow some application code to run unmanaged (e.g. constructors from other loaded libraries) and it is not portable to other platforms. This is the default approach taken by DynamoRIO [Bru04].

A second mechanism which can be used for injection is *ptrace*. Ptrace is a Unix API which allows one process to control a second process. A DBM tool can use ptrace to pause the execution of the application, inject code which loads the DBM system in the same process, and then resume execution. After a successful injection, the DBM tool has to restore the memory contents of the application and start managed execution. This approach is difficult to implement reliably because the tracing process has limited control over the context of the traced application, requiring the DBM tool to overwrite existing machine code in the application, only with limited information being available to it. Additionally, ptrace functionality is incomplete on many combinations of hardware platforms and operating systems, reducing portability. The advantage of this approach is that it can be used to inject a DBM system into a running process. This is an alternative injection implementation used by DynamoRIO [Bru04].

The alternative to injection is **Loading**, when the DBM system is started first, using the standard launching mechanism of the platform. The DBM system then loads the application itself. Because the executable loader used on GNU/Linux is implemented in the kernel, a different loader, running in the userspace, has to be included with the DBM system. This approach allows the DBM tool to maintain control of the execution at all times. In addition, it is more easily portable to different platforms. The current implementation of Valgrind uses this loading strategy, which has been found to be more reliable than injection [NS07b].

#### 2.3.2 Code scanners

DBM systems work by scanning and, if required, modifying code before it executes. This is done by code scanners, which disassemble the native machine code, inspect it and then assemble any needed modifications. Multiple approaches have been used to build code scanners. The main differentiating criteria is instruction representation: *Copy-and-Annotate* (C&A) code scanners essentially copy most code unmodified, while only translating a relatively small number of instructions, such as sensitive and control flow instructions. This approach is well suited for DBI and DBO applications, which tend to only modify a small subset of the input code. C&A is generally used by performance-oriented DBM systems, such as DynamoRIO [Bru04], Pin [LCM<sup>+</sup>05] and FastBT [PG10].

*Disassemble-and-Resynthesise* (D&R) code scanners, on the other hand, translate all input code into an Intermediate Representation (IR), then perform any required modifications at the IR level and finally translate the IR back to native code. This approach is well suited for portable DBM systems because it allows the modification logic and any architecture-independent optimisations to be implemented once and reused across multiple architectures. Similarly, this approach is also well suited for DBT applications, which have to translate all instructions to a different ISA. D&R can also be useful for performing complex analysis by using a simplified IR to reduce the challenge of writing instrumentation code. D&R enables the JIT compiler to optimise across the original and the modified code, which can also reduce the challenge of developing complex instrumentation [NS07b]. However, it is difficult to maintain the performance of the original input code across the native-to-IR and IR-to-native translations. In particular, it is difficult to represent all properties of the input native code in a simple IR, which typically results in the IR representation using significantly more instructions than the input. To control this overhead, an architecture-specific optimisation pass is usually required when the IR is translated back to native code. Furthermore, the scanning process itself generally has higher overhead compared to C&A because of the additional operations involved. D&R is used by DBM systems such as Valgrind [NS07b] and QEMU [Bel05].

Apart from instruction representation, another design decision is whether and how much of the code scanner to craft manually and how much to automate. FastBT, for example, uses a high level representation of the instruction set to automatically generate translation tables [PG10]. The logic for modifying specific instructions is then implemented using the C++ language. This allows FastBT to automate the error prone aspects of the code scanner, while also allowing low level control for modifying and translating instructions. On the other hand, DynamoRIO mostly uses hand-crafted C-language implementations for instruction decoding, instruction encoding and modification / translation logic. This allows experienced implementers the maximum degree of flexibility and opportunities for optimisation.

#### 2.3.3 Code caches

Scanning and translating any given basic block takes significantly longer than executing the translated code in the basic block once, therefore it is essential for a DBM system to be able to reuse its translations, especially those of the *hot code* (the regions in which most of the execution time is spent). This can

be achieved in two ways: the first one is to modify the original code in-place. For example, to insert instrumentation code at a specific location, the original instruction at that location would be replaced by a trampoline. This trampoline would branch to a different memory region, where the instrumentation code, the original instruction and a branch back to the instruction following the trampoline have been injected. This approach is taken by Dyninst [BH00]. It has the advantage that a performance penalty is only paid when the original code is modified. However, it has a number of shortcomings related to code discovery and transparency [HMC94, BM11]. Additionally, the overhead of the modified code is relatively high since it cannot be inlined, or alternatively, it involves additional complexity in relocating large blocks of code to allow inlining [BM11].

The other approach, used by most DBM systems [Bru04, LCM<sup>+</sup>05, PG10, Bel05, SN05, BDB00], is to relocate all code to a software code cache and to link the code cache *fragments* directly, a technique introduced by Shade (under the name *chaining*), an instruction set simulator [CK94]. The mapping from the original application addresses (the Source Program Counters - SPCs) to their translations in the code cache (the Translated Program Counters - TPCs) is maintained using a hash table indexed by the SPCs. This approach has a number of advantages, namely: it avoids the code discovery problem by identifying the reachable code at runtime; it avoids transparency issues by preserving both the original code and data unmodified at their original locations; and it simplifies inline modification of code by combining the relocation and modification in one step [Bru04]. The disadvantage of this approach is that an overhead is introduced for all code due to its relocation to the code cache, even if it is not otherwise modified. However, various code cache linking optimisations have been used to minimise this overhead, while retaining the advantages of the code cache. The overhead of a number of DBM systems is further discussed in Section 2.5.

#### **Basic blocks**

A DBM software code cache is organised in *basic blocks*, which are single-entry and single-exit fragments, meaning they are created from linear code regions, with the first instruction being the only allowed entry point. Consequently, different entry points to the same linear code region in the application will create multiple basic blocks in the code cache, with tail duplication. The source of each block can only contain up to one control flow instruction, which must be the last instruction. Other conditions such as reaching a size limit or encountering a sensitive instruction can be used to terminate a basic block, in which case they are equivalent to a basic block which unconditionally branches to the following instruction in memory.

#### Traces

Traces (also known as superblocks or extended basic blocks) are single-entry, multiple-exit fragments, usually a result of merging together multiple basic blocks which are reachable from a specific entry point. Traces eliminate branching on a preferred execution path and improve cache locality, thereby reducing the overhead of modified code.

Traces are usually built using hot path profiling, however they can also be created using static heuristics, in which case they are known as pseudo-traces. To be effective, online hot path profiling requires low overhead and must produce a result after a very limited number of executions, therefore offline profiling techniques are not generally considered suitable [DB00]. Next Executing Tail (NET) [DB00], a lightweight profiling scheme originally developed for the Dynamo dynamic optimiser [BDB00] has been widely adopted. NET works by inserting an execution counter into the basic blocks which are a target of backward branches, known as path heads, based on the insight that hot code regions consist of loops and the targets of backward branches are the start of loops. Once this counter has reached a certain threshold, a new trace is created with the path head as the entry point. The taken target at the end of each fragment in the trace is then appended to the trace, until another backward branch or the entry point to an existing trace is executed. When conditional branches are encountered, the selected target is added to the trace and the alternate target is conditionally linked, creating trace exits. NET is described in more detail in Section 5.2.

Last-Executed Iteration (LEI) has been proposed as an alternative to NET [HHS05]. It improves on NET by placing interprocedural cycles inside a single trace and by reducing duplication in the case of nested loops and unbiased conditional branches. However, its implementation introduced high profiling overhead, which overshadowed the expected performance benefits [DH11a].

*NETPlus* [DH11a] is another alternative to NET. It identifies the hot code regions in the same manner as NET, by inserting a dynamic execution counter in the targets of backward branches. Its improvement over NET is in the trace termination condition: when NETPlus encounters a backward branch, it first performs a forward search for loops back to the trace head and then only terminates the trace if a loop is not found. This allows NETPlus to create fewer, longer traces compared to NET, further improving code locality. NETPlus was shown to reduce the number of transfers of control directly from one trace to another compared to NET on the SPEC CINT2006 benchmarks [DH11a].

## 2.4 Branch linking

Optimising the translation of branches in the code cache is essential to achieve low overhead. This is done by linking the code cache fragments directly, instead of going through the dispatcher to transfer control. Branches can be classified in *direct branches*, which have a static target, and *indirect branches*, which have a dynamic target. Due to this difference, the two types of branches are handled separately.

### 2.4.1 Direct branches

Because the target of direct branches is known at the time they are scanned, their handling is relatively straightforward: if a translation of the target is available in the code cache, then it can be *linked* directly by placing a branch at the end of the code cache fragment. The design space of direct branch linking is relatively small. One decision is whether to *proactively* link direct branches when the fragment is created or to *lazily* link them when and if they are taken. Bruening [Bru04] has found that for DynamoRIO on x86, proactive linking is generally more efficient and improves the overall performance for *mesa*, a SPEC CPU2000 benchmark, by 5% compared to lazy linking. The performance of some benchmarks is slightly reduced by proactive linking, but only by up to around 1.5% for *swim* and under 1% for other benchmarks. The overall effect is relatively small, with a harmonic mean improvement of under 1% across the SPEC CPU2000 benchmarks and a selection of desktop applications. Hazelwood and Klauser [HK06] also found proactive linking to be more efficient for the ARM implementation of Pin.

A second design choice is whether to terminate basic blocks on unconditional direct branches or to elide the branch and inline the target of the branch in the same basic block. Terminating minimises tail duplication, while inlining eliminates a control transfer and can increase code cache locality. Nethercote and Seward [NS07b] argue that inlining, together with an efficient dispatcher implementation, enables Valgrind to achieve relatively low overhead despite not linking branches. DynamoRIO also elides unconditional direct branches, although the main benefit is in reducing the memory usage rather than directly reducing overhead [Bru04]. HDTrans elides unconditional branches, but only for targets which do not already have a translation in the code cache, to reduce code duplication [SSNB06].

### 2.4.2 Indirect branches

Because indirect branches have a dynamic target, they cannot be directly linked like direct branches. Instead, the original target address used by the application (the SPC) must be matched to the address of its translation in the code cache (the TPC) every time the indirect branch executes. The translation of indirect branches is the main source of overhead for DBM systems and an efficient implementation is critical for achieving good performance [KS03b]. Various solutions have been proposed, which can be broadly classified in two categories. The first category, hardware and hardware/software co-designed solutions, modify the architecture or microarchitecture of processors. The second category are the software-only solutions, which are compatible with unmodified general purpose architectures.

Before exploring the indirect branch linking techniques in the literature, it is necessary to further classify indirect branches into several types with distinct properties. The first category of indirect branches is *returns*, which execute at the end of a procedure (the callee) to return control back to the caller. More specifically, returns branch to the instruction immediately following the call instruction in the caller. This enables very accurate target address prediction, simply by recording the address of the instruction following each executed call in a Last In, First Out (LIFO) structure and then removing one entry, the predicted address, for each executed return. However, prediction is not always correct, for example due to exceptions and therefore must always be checked for correctness. A second category of indirect branches is *table branches*, which load their target address from an indexed table in memory. The third category of indirect branches is *generic indirect branches*, which simply branch to a dynamic target address from a register or from memory.

#### Returns

Returns make up the majority of executed indirect branches [SKC<sup>+</sup>04]. Most microarchitectures incorporate a Return Address Stack (RAS) which is automatically maintained by the hardware across calls and returns, and which is used for return address prediction when code is executing natively. However, the naive translation of calls and returns in the code cache uses generic branch instructions, which do not take advantage of this hardware branch prediction mechanism. Kim and Smith have found this to be a limiting factor in the performance of DBM systems [KS03a].

One optimisation which can be considered is to use code cache addresses (i.e. TPCs) instead of the original addresses (SPCs) as return addresses, by copying call and return instructions unmodified to the code cache. This would enable hardware return address prediction in the code cache, at the cost of application transparency. However, as reported by Bruening [Bru04], many applications are affected by breaking transparency in this way, therefore making this optimisation impractical. To avoid the transparency issues, another possible optimisation is to maintain a software RAS together with the hardware RAS. The software RAS consists of pairs of SPCs and their matching TPCs. An entry is pushed by the translation of call instructions, while translated return instructions pop the first entry from the software RAS, compare the actual target SPC of the application to the SPC of the RAS entry and if the two match, then execution can branch directly to the TPC in the RAS entry. This optimisation was used for return address prediction in FX!32 [HH97] and Pin for ARM [HK06]. However, an experimental implementation in DynamoRIO was found to be slower than the baseline indirect branch translation using an optimised hash table lookup and indirect branch [Bru04].

A different approach, in the form of *function cloning* [CHK93], is taken by Pin [LCM<sup>+</sup>05]. Pin creates multiple copies of procedures in the code cache, one for each call site. This allows each copy to statically predict a single return address, which is expected to be correct in the common case. However, this can result in large amounts of code duplication and increases the pressure on the instruction memory subsystem.

HDTrans introduced a technique called the *return cache* [SSB07], which is also used by FastBT [PG10]. Similarly to the software RAS technique, it is exploiting the relationship between calls and returns to predict the target address of returns. The return cache is a thread-private hash table storing TPCs indexed by their SPC. The translated calls add an entry to the return cache for the instruction following the call. The translated returns then *blindly* load the hash table entry indexed by the SPC of the return target. Collisions are handled in the translated return fragment, which compares the return target SPC with its own source SPC and falls back to the generic SPC-to-TPC lookup if a mismatch is detected. This technique can reuse the return cache entries in case of deep recursion, as opposed to the software RAS predictor which stores a SPC-TPC pair for every call. It also requires use of fewer registers compared to the software RAS. However, the performance of the return cache is severely affected by collisions, which are reported to happen at a rate of 15% to 22% [SSNB06].

#### Table branches

FastBT introduced an optimisation for the translation of table branches called the *shadow jump table*. This optimisation detects table branches on the x86 architecture by pattern matching specific encodings of the *jmp* instruction, which load the target address from a table using an absolute or PC-relative base address and an offset. When a table branch is detected, FastBT creates a shadow jump table, which is populated on demand with the TPCs of the SPCs in the original table. The performance overhead of the DBM system is reduced by translating a table branch in the application to a table branch in the code cache, as opposed to one of the less efficient lookup implementations for generic indirect branches. However, the size of the jump table is not statically determined, therefore runtime bounds checking is used for the shadow branch table, introducing a performance overhead. Furthermore, a memory overhead is introduced by the shadow jump table.

#### Generic indirect branches