# A CHIP MULTI-CLUSTER ARCHITECTURE WITH LOCALITY AWARE TASK DISTRIBUTION

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2007

Matthew James Horsnell School of Computer Science

# Contents

| L                         | ist of | Table                | S                                       | 7  |

|---------------------------|--------|----------------------|-----------------------------------------|----|

| $\mathbf{L}_{\mathbf{i}}$ | ist of | Figur                | es                                      | 8  |

| $\mathbf{L}_{\mathbf{i}}$ | ist of | Algor                | rithms                                  | 12 |

| A                         | bstra  | $\operatorname{act}$ |                                         | 13 |

| D                         | eclar  | ation                |                                         | 14 |

| $\mathbf{C}$              | opyri  | ight                 |                                         | 15 |

| $\mathbf{A}$              | ckno   | wledge               | ements                                  | 16 |

| 1                         | Intr   | oduct                | ion                                     | 17 |

|                           | 1.1    | Motiv                | ration                                  | 17 |

|                           | 1.2    | Micro                | processor Design Challenges             | 19 |

|                           |        | 1.2.1                | Wire Delay                              | 20 |

|                           |        | 1.2.2                | Memory Gap                              | 21 |

|                           |        | 1.2.3                | Limits of Instruction Level Parallelism | 22 |

|                           |        | 1.2.4                | Power Limits                            | 23 |

|                           |        | 1.2.5                | Design Complexity                       | 24 |

|                           | 1.3    | Design               | n Solutions                             | 26 |

|                           |        | 1.3.1                | Exploiting Parallelism                  | 26 |

|          |     | 1.3.2    | Partitioned Designs                | 29       |

|----------|-----|----------|------------------------------------|----------|

|          |     | 1.3.3    | Bridging the Memory Gap            | 80       |

|          |     | 1.3.4    | Design Abstraction and Replication | 31       |

|          | 1.4 | Summ     | ary                                | 3        |

|          | 1.5 | Resear   | rch Aims                           | 3        |

|          | 1.6 | Contri   | ibutions                           | 3        |

|          | 1.7 | Thesis   | Structure                          | 34       |

|          | 1.8 | Public   | eations                            | 85       |

| <b>2</b> | Par | allelisr | m 3                                | 6        |

|          | 2.1 | Applie   | cation Parallelism                 | 6        |

|          |     | 2.1.1    | Amdahl's Law                       | 37       |

|          |     | 2.1.2    | Implicit and Explicit Parallelism  | 37       |

|          |     | 2.1.3    | Granularity of Parallelism         | 89       |

|          | 2.2 | Archit   | sectural Parallelism               | 2        |

|          |     | 2.2.1    | Bit Level Parallelism              | 2        |

|          |     | 2.2.2    | Data Level Parallelism             | 13       |

|          |     | 2.2.3    | Instruction Level Parallelism      | 4        |

|          |     | 2.2.4    | Multithreading                     | 17       |

|          |     | 2.2.5    | Simultaneous Multithreading        | 0        |

|          |     | 2.2.6    | Chip Multiprocessors               | 0        |

|          | 2.3 | Summ     | ary                                | 51       |

| 3        | Jan | naica C  | CMP and Software Environment 5     | <b>2</b> |

|          | 3.1 | The J    | amaica Chip Multiprocessor         | 2        |

|          |     | 3.1.1    | Multithreading                     | 3        |

|          |     | 3.1.2    | Register Windows                   | 5        |

|          |     | 3.1.3    | Lightweight Task Distribution      | 8        |

|          |     | 3.1.4    | Branch Prediction                  | 9        |

|          |     | 3.1.5    | Coherent Shared Memory Hierarchy 6 | 60       |

|          |     | 3.1.6    | Hard and Soft Interrupts           | 64       |

|          |     | 3.1.7    | Devices                            | 5        |

|          | 3.2 | Jamai    | ca Core Revisions                  | 5        |

|          |     | 3.2.1    | Interleaved Multithreading         | 5        |

|          |     | 3.2.2    | Working Set and Register Windows   | 66       |

|          | 3 3 | Inmai    | ca Softwaro Environment            | :7       |

|   |     | 3.3.1    | Jamaica Assembler and C Compiler 6                | 7 |

|---|-----|----------|---------------------------------------------------|---|

|   |     | 3.3.2    | Jamaica Boot Procedure                            | 8 |

|   |     | 3.3.3    | The Jamaica Virtual Machine 6                     | 8 |

|   | 3.4 | Jamai    | ca Simulation Environment                         | ( |

|   |     | 3.4.1    | Simulation Accuracy                               | ( |

|   |     | 3.4.2    | Simulation Configuration                          | 1 |

|   |     | 3.4.3    | System Simulation                                 | 2 |

|   | 3.5 | Summ     | ary                                               | 4 |

| 4 | Mu  | lti-leve | el Cache Coherence 7                              | 5 |

|   | 4.1 | Multip   | processor Organisation                            | - |

|   |     | 4.1.1    | Memory Access                                     | 6 |

|   |     | 4.1.2    | Inter-Processor Communication                     | 7 |

|   | 4.2 | Scalin   | g the Jamaica Architecture                        | 8 |

|   |     | 4.2.1    | Limitations to Bus Scaling                        | 8 |

|   |     | 4.2.2    | Multi-Level Cache Hierarchy                       | ( |

|   |     | 4.2.3    | Cache Inclusion                                   | 1 |

|   |     | 4.2.4    | Locality and Affinity                             | 4 |

|   | 4.3 | PIMM     | IS - a Multi-Level Coherence Protocol             | 4 |

|   |     | 4.3.1    | Cache States                                      | - |

|   |     | 4.3.2    | Network Transactions                              | ( |

|   |     | 4.3.3    | State Transitions                                 | 6 |

|   |     | 4.3.4    | Four Phase Transactions                           | 6 |

|   | 4.4 | Summ     | ary 9                                             | 2 |

| 5 | Mu  | lti-leve | el Cache Hardware 9                               | 3 |

|   | 5.1 | Cache    | Organisation                                      | ٠ |

|   |     | 5.1.1    | Level 1 Private Caches                            | 4 |

|   |     | 5.1.2    | Shared Level Caches                               | 5 |

|   | 5.2 | Coher    | ence Messages and Transactions                    | 6 |

|   | 5.3 | Flow (   | Control                                           | 6 |

|   |     | 5.3.1    | Blocking and Negative Acknowledgments 9           | 7 |

|   | 5.4 | Deadle   | ock Avoidance                                     | 8 |

|   |     | 5.4.1    | Sinkable Messages                                 | 8 |

|   |     | 5.4.2    | Non-Sinkable Messages                             | ć |

|   |     | 5.4.3    | Sinkable and Non-Sinkable Queues and Priorities 9 | Ć |

|   |     | 5.4.4    | Passive and Active Non-Sinkable Messages 10 | 0 |

|---|-----|----------|---------------------------------------------|---|

|   | 5.5 | Addre    | ss Blocking                                 | 3 |

|   |     | 5.5.1    | Local Transactions                          | 3 |

|   |     | 5.5.2    | Deadlock Avoidance                          | 4 |

|   | 5.6 | Multi-   | Level Synchronisation                       | 5 |

|   | 5.7 | Lazy     | Cache-Line Allocation                       | 6 |

|   | 5.8 | Summ     | ary                                         | 7 |

| 6 | Mu  | lti-leve | el Task Locality 10                         | 8 |

|   | 6.1 | Cluste   | ers and Cache Locality                      | 8 |

|   | 6.2 | Task l   | Distribution                                | 9 |

|   |     | 6.2.1    | Locality Aware Task Distribution            | 0 |

|   |     | 6.2.2    | Token Requests                              | 0 |

|   |     | 6.2.3    | Locality Aware Token Request Extensions     | 2 |

|   |     | 6.2.4    | Cache-Distance Identifiers                  | 2 |

|   |     | 6.2.5    | Hardware Support for Locality               | 4 |

|   |     | 6.2.6    | Software Support for Locality               | 6 |

|   | 6.3 | Summ     | ary                                         | 0 |

| 7 | Res | ults aı  | nd Analysis 12                              | 1 |

|   | 7.1 | Exper    | imental Method                              | 1 |

|   |     | 7.1.1    | Simulation Environment                      | 2 |

|   | 7.2 | Bench    | mark Descriptions                           | 3 |

|   |     | 7.2.1    | Fork/Join Benchmarks                        | 3 |

|   |     | 7.2.2    | Multithreaded JavaGrande Benchmarks         | 5 |

|   |     | 7.2.3    | Benchmark Parameters                        | 7 |

|   | 7.3 | PIMM     | [S Coherence Protocol                       | 7 |

|   |     | 7.3.1    | Coherence Transactions                      | 7 |

|   |     | 7.3.2    | Four-phase Transactions                     | 9 |

|   |     | 7.3.3    | Interconnect Latency                        | 1 |

|   |     | 7.3.4    | Negative Acknowledgment                     | 1 |

|   |     | 7.3.5    | Non-Sinkable Queue Rotation                 | 4 |

|   |     | 7.3.6    | Effect of Inclusion                         | 5 |

|   |     | 7.3.7    | Protocol Robustness                         | 7 |

|   | 7.4 | Single   | Bus Chip Multiprocessor Architecture        | 8 |

|   |     | 7 / 1    | Spood up                                    | Q |

|    |                            | 7.4.2                                                                                        | Wire Delay                                                                                                                                                                                                                                                                                                                     |

|----|----------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                            | 7.4.3                                                                                        | Bus Contention                                                                                                                                                                                                                                                                                                                 |

|    |                            | 7.4.4                                                                                        | Memory Saturation                                                                                                                                                                                                                                                                                                              |

|    | 7.5                        | Cluste                                                                                       | er Architectures                                                                                                                                                                                                                                                                                                               |

|    |                            | 7.5.1                                                                                        | Speed-up                                                                                                                                                                                                                                                                                                                       |

|    |                            | 7.5.2                                                                                        | Bus-Tree Cluster                                                                                                                                                                                                                                                                                                               |

|    |                            | 7.5.3                                                                                        | Crossbar Cluster                                                                                                                                                                                                                                                                                                               |

|    |                            | 7.5.4                                                                                        | Hybrid Bus-Crossbar Cluster                                                                                                                                                                                                                                                                                                    |

|    | 7.6                        | Locali                                                                                       | ty Aware Task Distribution                                                                                                                                                                                                                                                                                                     |

|    |                            | 7.6.1                                                                                        | Synchronisation Locality                                                                                                                                                                                                                                                                                                       |

|    |                            | 7.6.2                                                                                        | Application Isolation                                                                                                                                                                                                                                                                                                          |

|    |                            | 7.6.3                                                                                        | Application Restructuring                                                                                                                                                                                                                                                                                                      |

|    | 7.7                        | Chip I                                                                                       | Multi-Cluster Design Considerations                                                                                                                                                                                                                                                                                            |

|    | 7.8                        | Summ                                                                                         | ary                                                                                                                                                                                                                                                                                                                            |

| 8  | Con                        | clusio                                                                                       | ns 168                                                                                                                                                                                                                                                                                                                         |

|    |                            |                                                                                              |                                                                                                                                                                                                                                                                                                                                |

|    | 8.1                        | Contri                                                                                       | ibutions                                                                                                                                                                                                                                                                                                                       |

|    | 8.1<br>8.2                 |                                                                                              | ibutions                                                                                                                                                                                                                                                                                                                       |

| Bi | 8.2                        | Future                                                                                       | e Work                                                                                                                                                                                                                                                                                                                         |

| Bi | 8.2                        |                                                                                              | e Work                                                                                                                                                                                                                                                                                                                         |

|    | 8.2<br>bliog               | Future<br>graphy<br>naica -                                                                  | Work       171         173       185         Instruction Set Architecture       185                                                                                                                                                                                                                                            |

|    | 8.2<br>bliog               | Future<br>graphy<br>naica -                                                                  | e Work                                                                                                                                                                                                                                                                                                                         |

|    | 8.2<br>bliog<br>Jam        | Future<br>graphy<br>naica -                                                                  | Work       171         173       185         Instruction Set Architecture       185                                                                                                                                                                                                                                            |

|    | 8.2<br>bliog<br>Jam        | Future<br>graphy<br>naica -<br>Instru                                                        | Work                                                                                                                                                                                                                                                                                                                           |

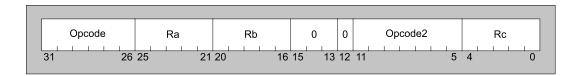

|    | 8.2<br>bliog<br>Jam        | Future<br>graphy<br>naica -<br>Instru<br>A.1.1                                               | Instruction Set Architecture 185 ction Formats 185 Register Form 186                                                                                                                                                                                                                                                           |

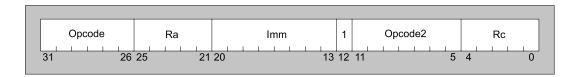

|    | 8.2<br>bliog<br>Jam        | Future<br>graphy<br>naica -<br>Instru<br>A.1.1<br>A.1.2<br>A.1.3                             | Instruction Set Architecture 185 ction Formats 185 Register Form 186 Immediate Form 186                                                                                                                                                                                                                                        |

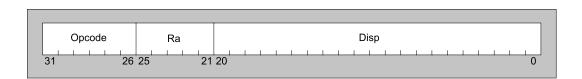

|    | 8.2<br>bliog<br>Jam<br>A.1 | Future<br>graphy<br>naica -<br>Instru<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4                    | Work       171         173       173         Instruction Set Architecture       185         ction Formats       185         Register Form       186         Immediate Form       186         Branch Form       186                                                                                                             |

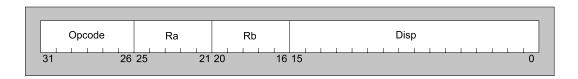

|    | 8.2<br>bliog<br>Jam<br>A.1 | Future<br>graphy<br>naica -<br>Instru<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4                    | Work       171         173       173         Instruction Set Architecture       185         ction Formats       185         Register Form       186         Immediate Form       186         Branch Form       186         Memory Form       186                                                                               |

|    | 8.2<br>bliog<br>Jam<br>A.1 | Future<br>graphy<br>naica -<br>Instru<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4<br>Instru          | Work       171         173       173         Instruction Set Architecture       185         ction Formats       185         Register Form       186         Immediate Form       186         Branch Form       186         Memory Form       186         ction Set       187                                                   |

|    | 8.2<br>bliog<br>Jam<br>A.1 | Future<br>graphy<br>naica -<br>Instru<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4<br>Instru<br>A.2.1 | Work       171         173       173         Instruction Set Architecture       185         ction Formats       185         Register Form       186         Immediate Form       186         Branch Form       186         Memory Form       186         ction Set       187         Arithmetic/Logical Instructions       187 |

# List of Tables

| 1.1 | Growth in area between successive generations of Intel architectures. | 24  |

|-----|-----------------------------------------------------------------------|-----|

| 4.1 | Configuration of a 1 billion transistor CMP                           | 79  |

| 4.2 | PIMMS protocol: cache states                                          | 85  |

| 4.3 | PIMMS protocol: network transactions, mnemonic codes and de-          |     |

|     | scriptions                                                            | 86  |

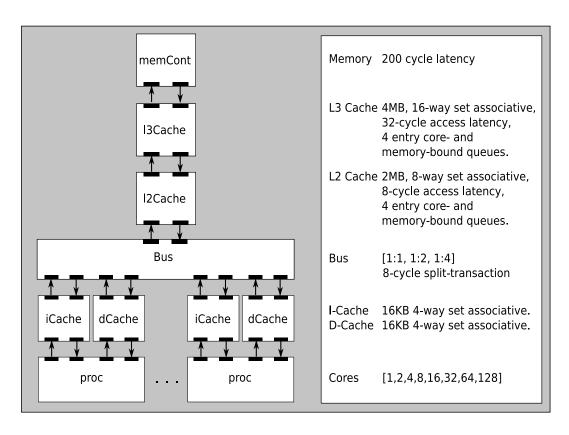

| 7.1 | Configuration of the simulated cache hierarchy                        | 122 |

| 7.2 | Benchmark parameters used during experimentation                      | 127 |

| 7.3 | Locality-aware task distribution                                      | 163 |

| 7.4 | Performance comparison CMC vs. single bus CMP                         | 165 |

| A.1 | Jamaica instruction set: arithmetic/logical instructions              | 187 |

| A.2 | Jamaica instruction set: branch form control instructions             | 188 |

| A.3 | Jamaica instruction set: memory form control instructions             | 188 |

| A.4 | Jamaica instruction set: memory instructions                          | 189 |

| A.5 | Jamaica instruction set: builtin instructions                         | 190 |

# List of Figures

| 1.1 | Predicted percent of die reachable by each generation [104]              | 21 |

|-----|--------------------------------------------------------------------------|----|

| 1.2 | A growing gap between memory speed and processor speed leads             |    |

|     | to bottlenecks during data intensive workloads [62]                      | 22 |

| 1.3 | A growing gap between increases in the complexity of a chip and          |    |

|     | productivity of design engineers and tools                               | 25 |

| 1.4 | Exploiting thread-level parallelism: a) software scheduling, b) multi-   |    |

|     | threaded hardware, c) multi-processor hardware                           | 29 |

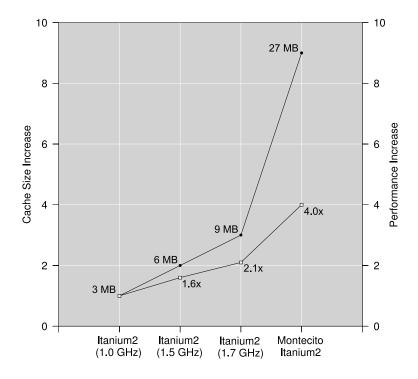

| 1.5 | The effect of increased cache size (MB) on performance $(\times)$ of the |    |

|     | Itanium 2 processor [107]                                                | 31 |

| 1.6 | Comparison of hardware scouting and increasing cache size $[27]$         | 32 |

| 2.1 | Amdahl's Law: Parallel speedup $(S)$ vs. parallel fraction $(P)$         | 38 |

| 2.2 | A simple code sequence amenable to ILP execution                         | 40 |

| 2.3 | A simple code sequence containing no ILP                                 | 40 |

| 2.4 | Inner loop of the motion detection algorithm used in MPEG en-            |    |

|     | coding, calculation of the sum of absolute differences                   | 41 |

| 2.5 | Inner loop after scalar expansion and loop fission. The first loop       |    |

|     | is now amenable to data level parallelism optimisations                  | 41 |

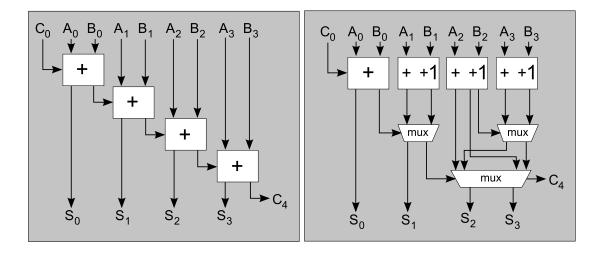

| 2.6 | 4-bit ripple-carry adder                                                 | 43 |

| 2.7 | 4-bit carry-select adder                                                 | 43 |

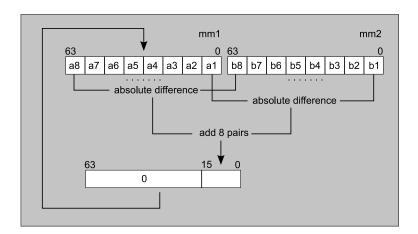

| 2.8 | Data Level Parallelism: the datapath inside the execution of the         |    |

|     | psadbw SSE2 instruction                                                  | 44 |

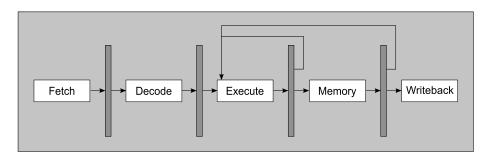

| 2.9  | A simple pipelined architecture                                      | 45 |

|------|----------------------------------------------------------------------|----|

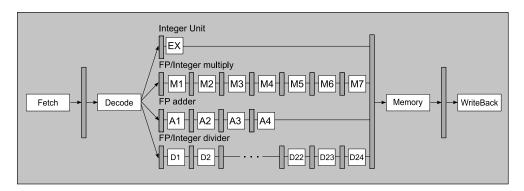

| 2.10 | Superscalar pipelined architecture                                   | 46 |

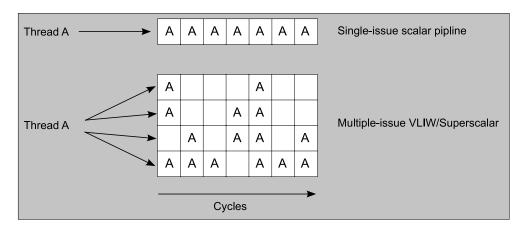

| 2.11 | Single issue and superscalar scheduling                              | 46 |

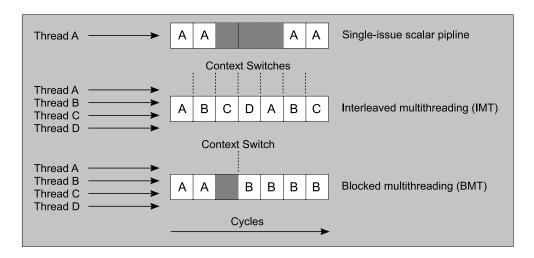

| 2.12 | Multithreading scheduling                                            | 49 |

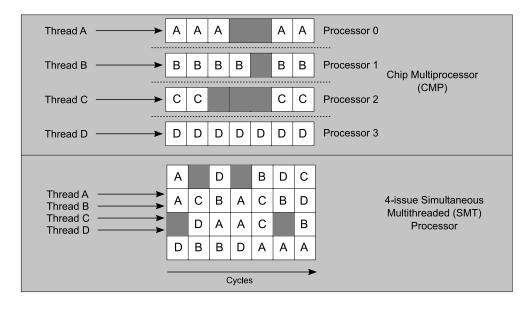

| 2.13 | SMT and CMP scheduling                                               | 50 |

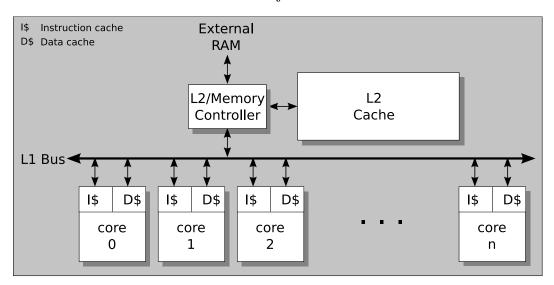

| 3.1  | The Jamaica single chip multiprocessor                               | 53 |

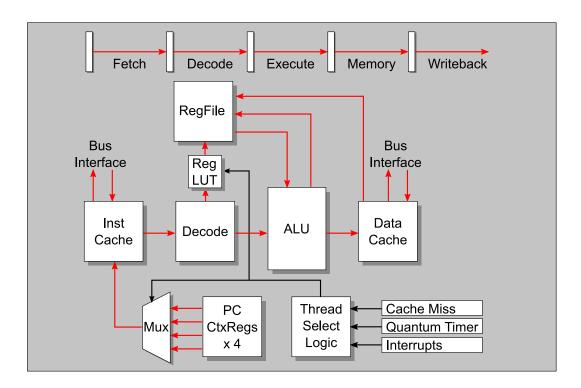

| 3.2  | Jamaica core: Multithreaded pipeline and support structures          | 54 |

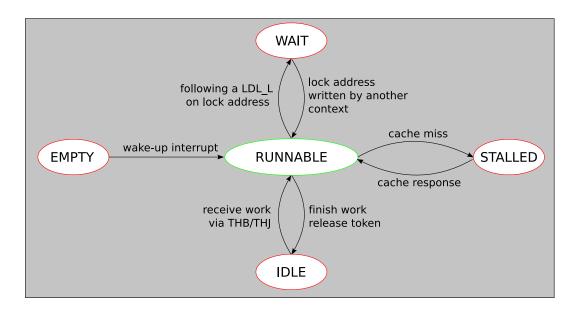

| 3.3  | Jamaica core: Context running states                                 | 54 |

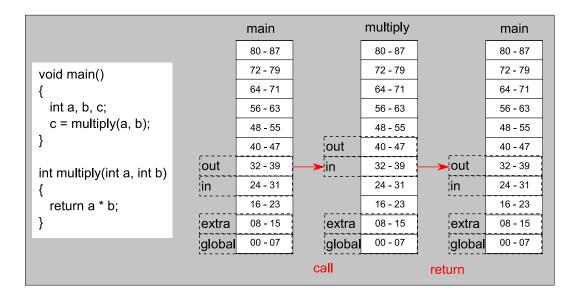

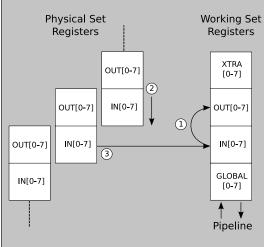

| 3.4  | Jamaica core: Register windows, call and return overlaps             | 57 |

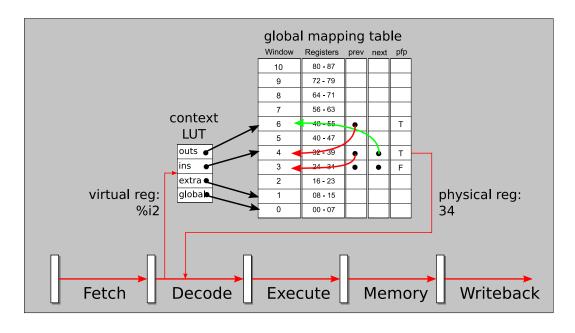

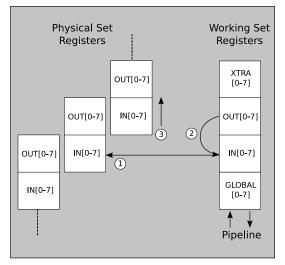

| 3.5  | Jamaica core: Register windows; virtual to physical register lookup. | 57 |

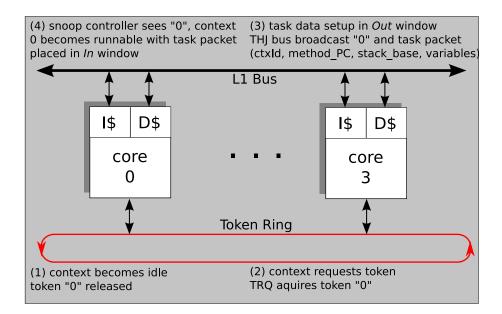

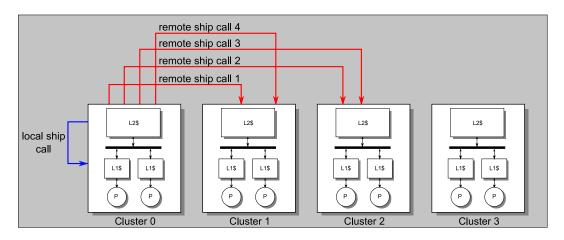

| 3.6  | Jamaica core: Lightweight task distribution                          | 59 |

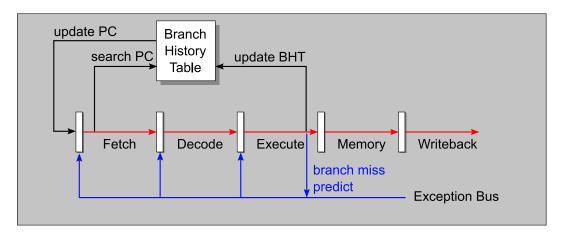

| 3.7  | Jamaica core: branch prediction                                      | 60 |

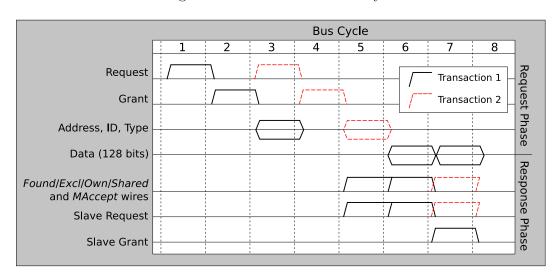

| 3.8  | Jamaica: Split transaction bus protocol                              | 61 |

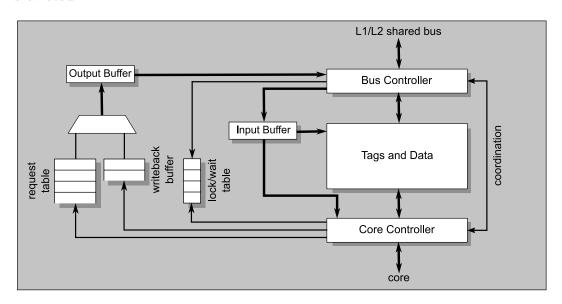

| 3.9  | Jamaica: Level 1 private cache                                       | 62 |

| 3.10 | Jamaica: Lock acquisition code                                       | 63 |

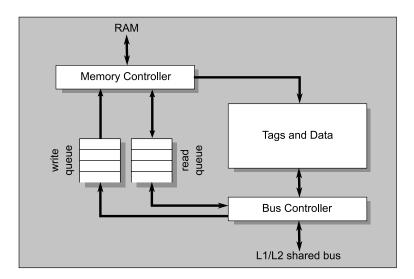

| 3.11 | Jamaica: Shared level 2 cache and memory interface                   | 64 |

| 3.12 | Jamaica core revisions: Register window call                         | 67 |

| 3.13 | Jamaica core revisions: Register window return                       | 67 |

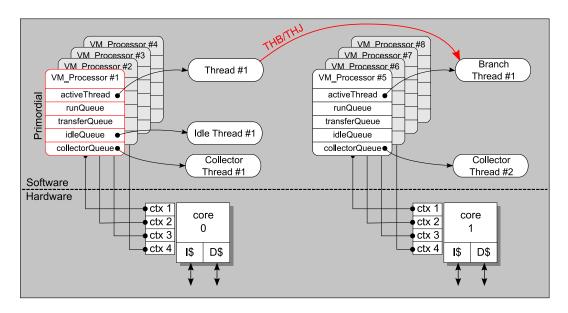

| 3.14 | JikesRVM software to Jamaica hardware mapping                        | 69 |

| 3.15 | Configuration code for jamsim                                        | 72 |

| 3.16 | Connected simulation components for jamsim                           | 73 |

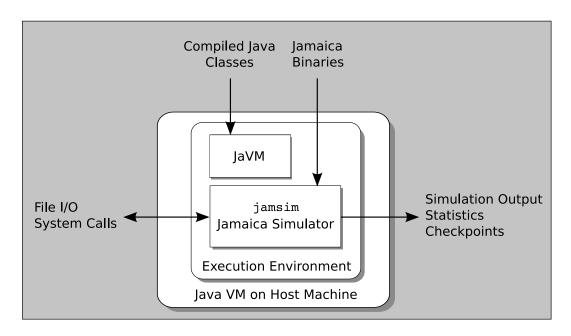

| 3.17 | Jamaica Simulation: Java bytecode is executed through the JaVM       |    |

|      | by jamsim within a Java virtual machine on top of the host system.   | 73 |

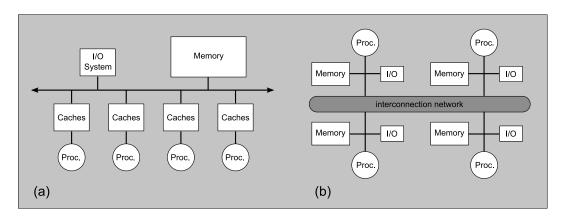

| 4.1  | Multiprocessor memory access                                         | 76 |

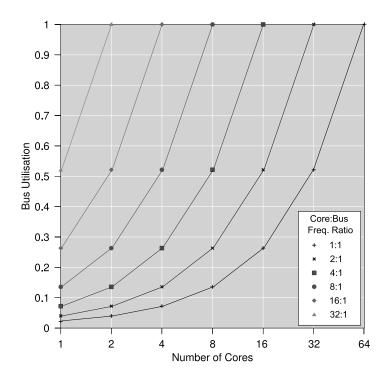

| 4.2  | Theoretical bus access limitations                                   | 79 |

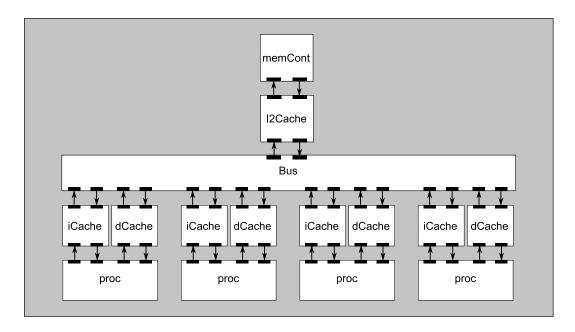

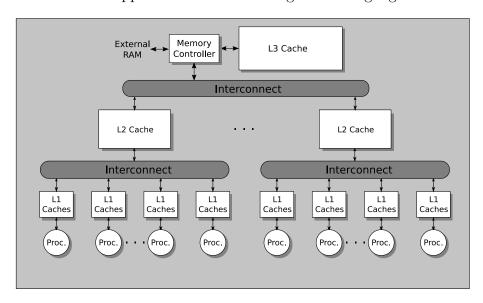

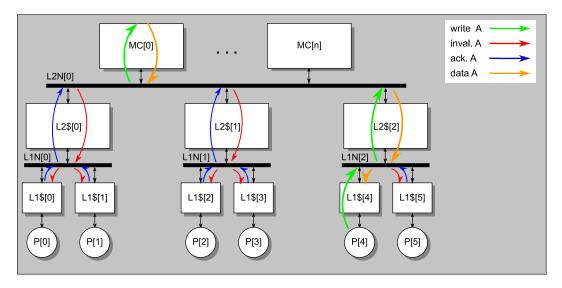

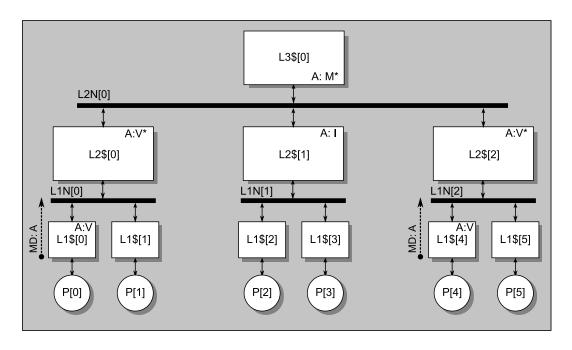

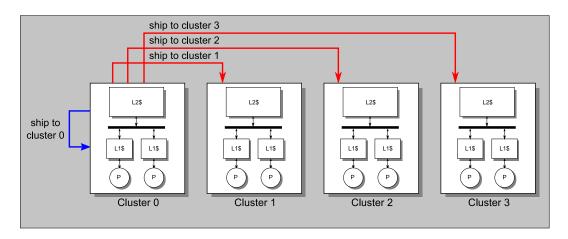

| 4.3  | Jamaica multi-level cache hierarchy                                  | 80 |

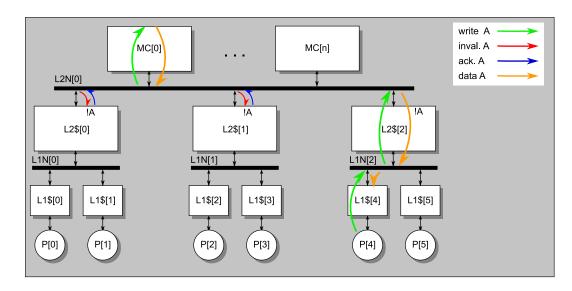

| 4.4  | Multi-level hierarchy without inclusion                              | 82 |

| 4.5  | Multi-level hierarchy with inclusion                                 | 83 |

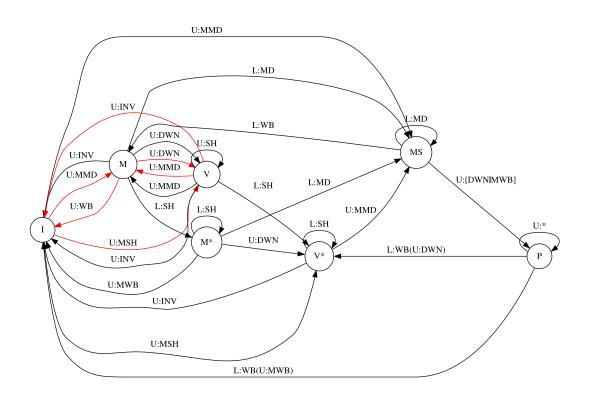

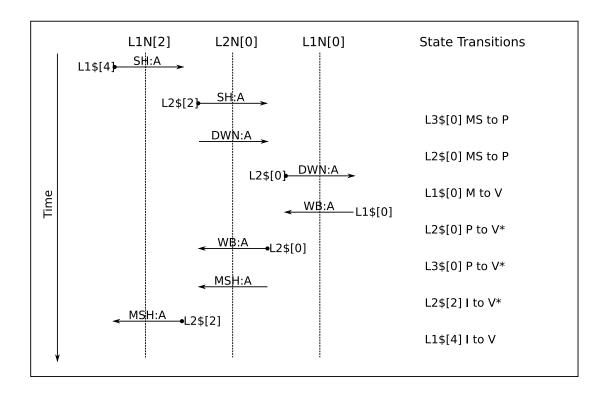

| 4.6  | Multi-level cache state transitions                                  | 87 |

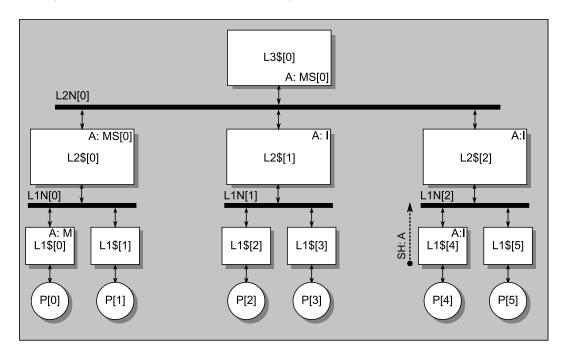

| 4.7  | Four phase read transaction                                          | 88 |

| 4.8  | Four phase read transaction, timeline                                | 89 |

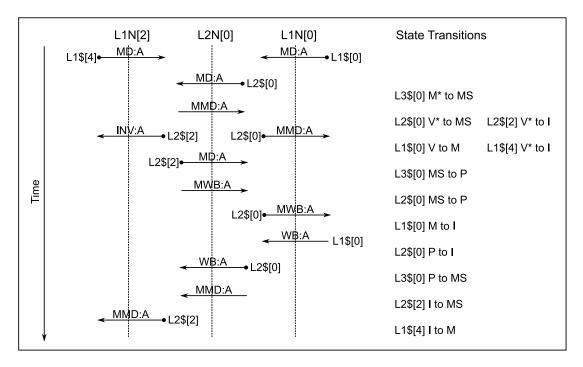

| 4.9  | Four phase concurrent write transactions                             | 90 |

| 4.10 | Four phase concurrent write transaction, timeline                    | 91 |

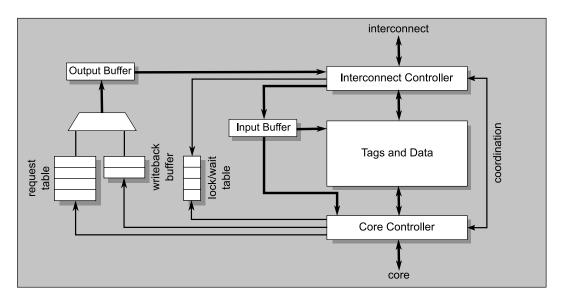

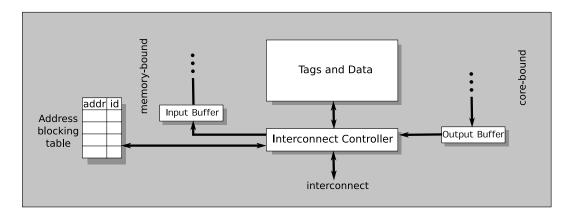

| 5.1  | Level 1 cache                                                        | 94 |

| 5.2  | Shared level cache                                                               | 95  |

|------|----------------------------------------------------------------------------------|-----|

| 5.3  | Circular queue dependence                                                        | 98  |

| 5.4  | Shared cache request queues divided into sinkable and non-sinkable               |     |

|      | entities. Non-sinkable queue divided further into passive and active             |     |

|      | queues allowing reordering                                                       | 99  |

| 5.5  | Passive/Active queue reordering                                                  | 102 |

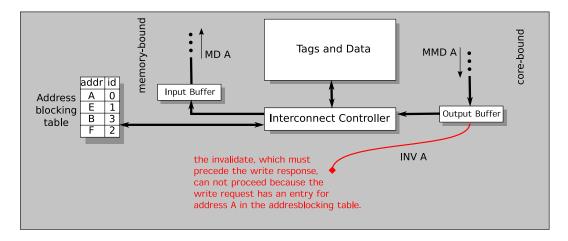

| 5.6  | Multi-level address blocking table                                               | 103 |

| 5.7  | Multi-level deadlock arising in the address blocking table                       | 104 |

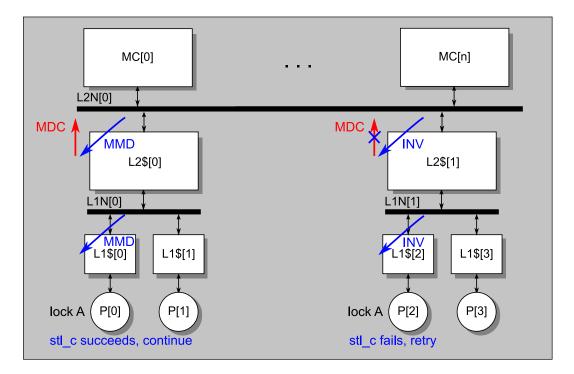

| 5.8  | Multi-cluster load-linked/store-conditional                                      | 105 |

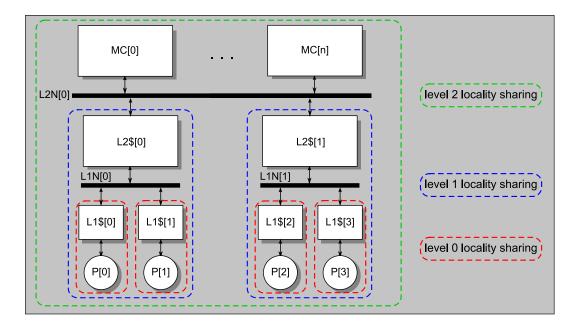

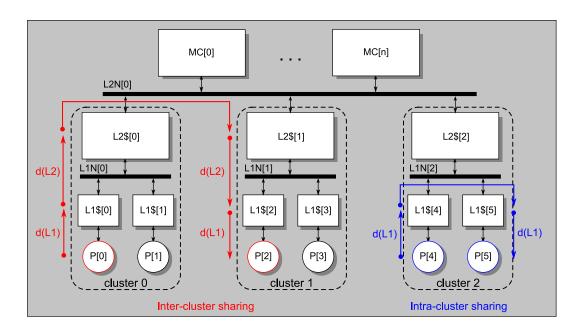

| 6.1  | Multi-cache locality of reference                                                | 109 |

| 6.2  | Multi-level data sharing                                                         | 111 |

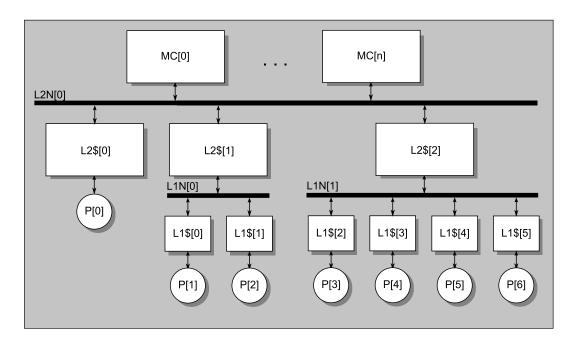

| 6.3  | Unbalanced multi-cluster configuration                                           | 113 |

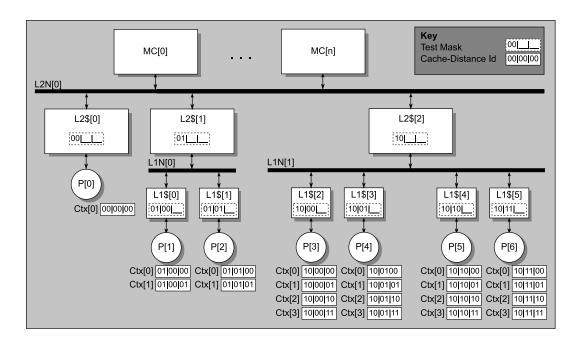

| 6.4  | Cache-distance identifiers                                                       | 114 |

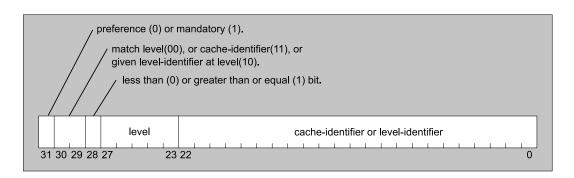

| 6.5  | TRQ semantics: the preference operand                                            | 117 |

| 6.6  | Remote-local distribution                                                        | 118 |

| 6.7  | Cluster affinity distribution                                                    | 119 |

| 7.1  | Bus utilisation during execution of the lu benchmark. The archi-                 |     |

|      | tecture is configured as a symmetric 2 cluster $\times$ 64 processors $\times$ 1 |     |

|      | context CMP                                                                      | 128 |

| 7.2  | Coherence traffic generated during the JavaGrande barrierBench                   |     |

|      | benchmark, on a symmetric 2 cluster $\times$ 8 processors CMP                    | 130 |

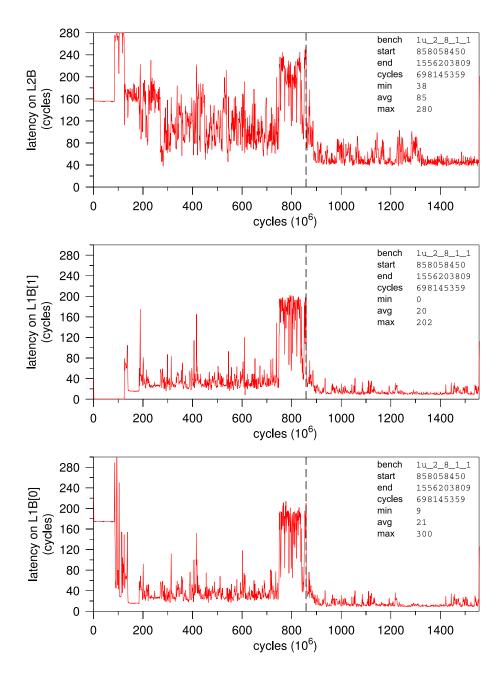

| 7.3  | Network latency (lu)                                                             | 132 |

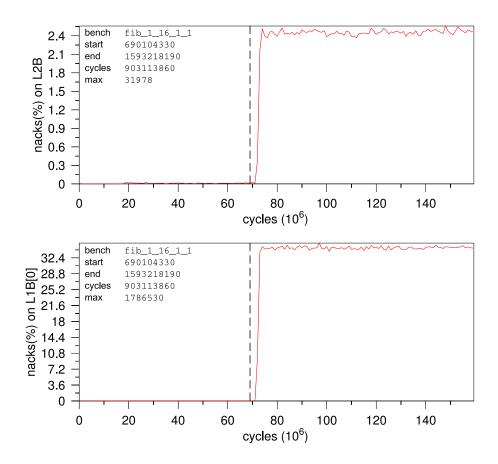

| 7.4  | Negative acknowledgments                                                         | 133 |

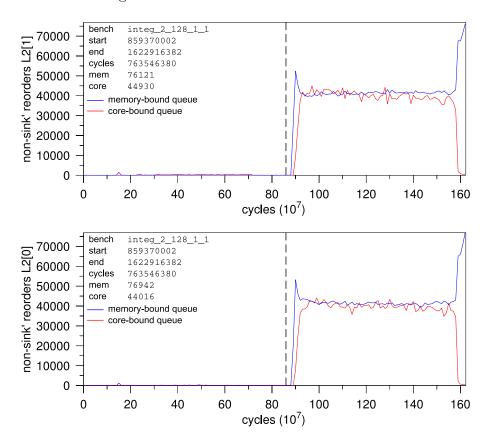

| 7.5  | Non-sinkable reordering                                                          | 134 |

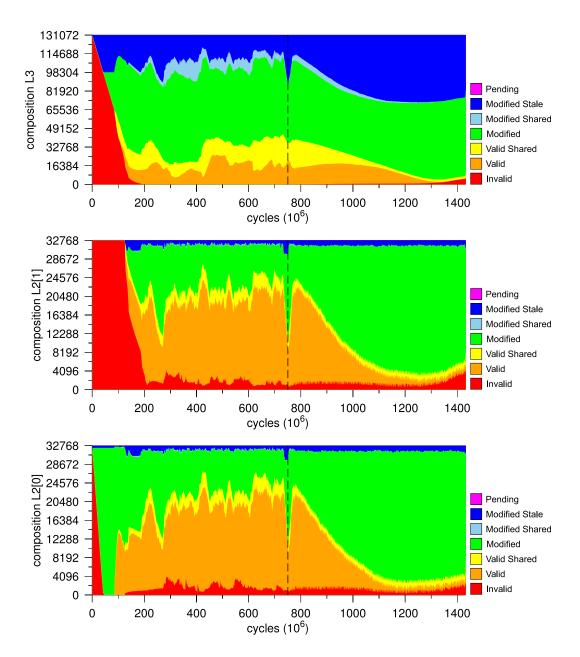

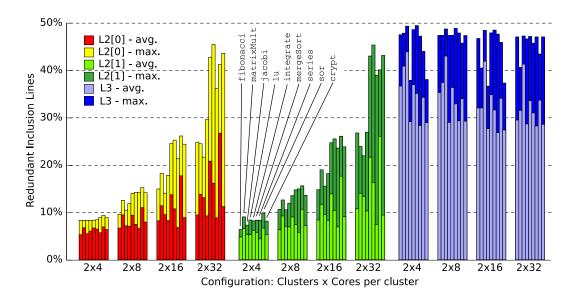

| 7.6  | Inclusive caches                                                                 | 136 |

| 7.7  | Cost of inclusion                                                                | 137 |

| 7.8  | Single bus CMP                                                                   | 139 |

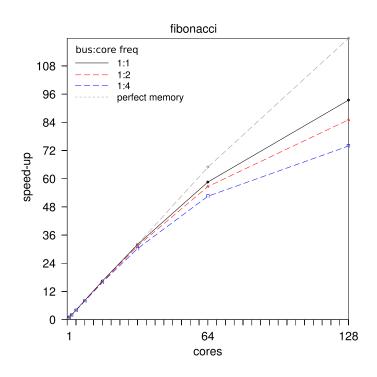

| 7.9  | CMP bus scaling - fibonacci                                                      | 141 |

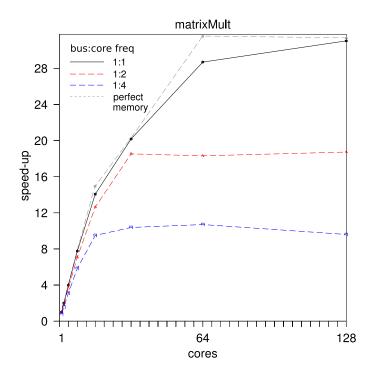

| 7.10 | CMP bus scaling - matrixMult                                                     | 141 |

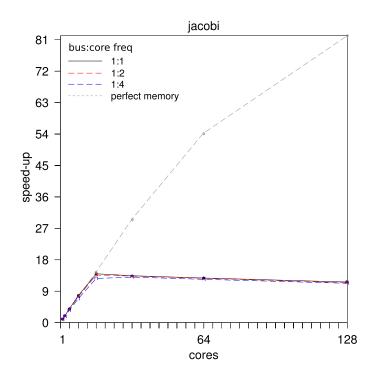

| 7.11 | CMP bus scaling - jacobi                                                         | 142 |

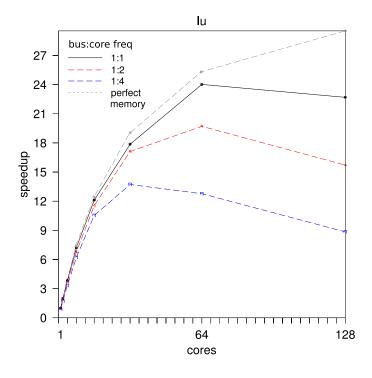

| 7.12 | CMP bus scaling - lu                                                             | 142 |

| 7.13 | CMP bus scaling - integrate                                                      | 143 |

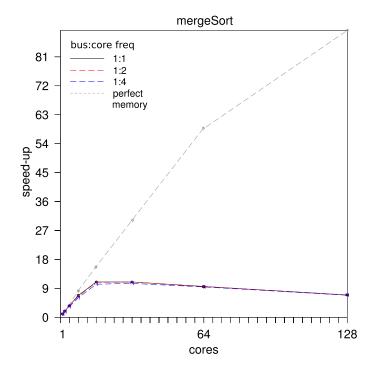

| 7.14 | CMP bus scaling - mergeSort                                                      | 143 |

|      |                                                                                  | 144 |

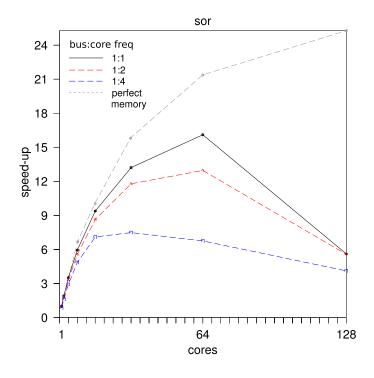

| 7.16                    | CMP bus scaling - sor                             | 4 |

|-------------------------|---------------------------------------------------|---|

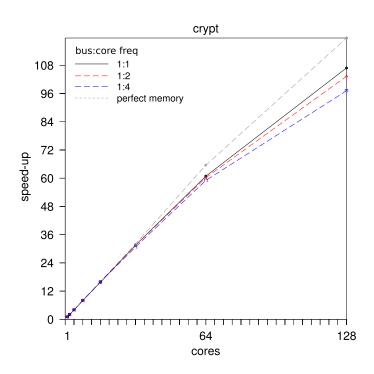

| 7.17                    | CMP bus scaling - crypt                           | 5 |

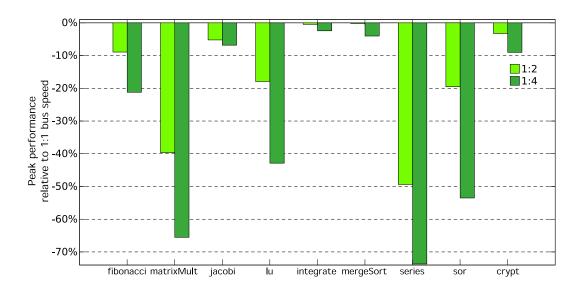

| 7.18                    | Bus speed relative performance                    | 6 |

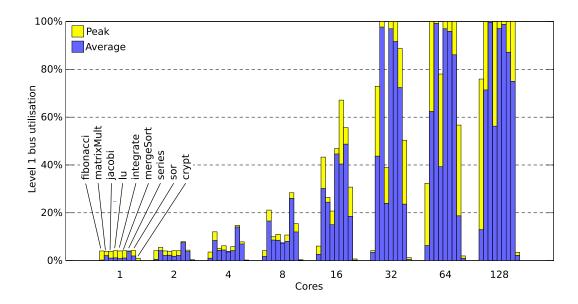

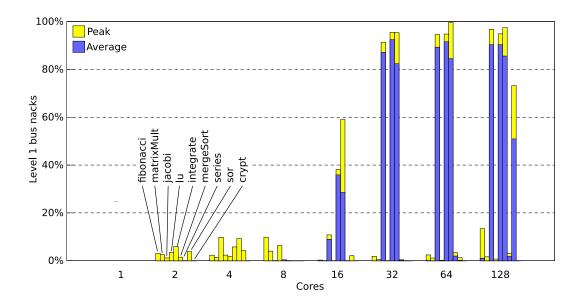

| 7.19                    | Level 1 bus utilisation                           | 7 |

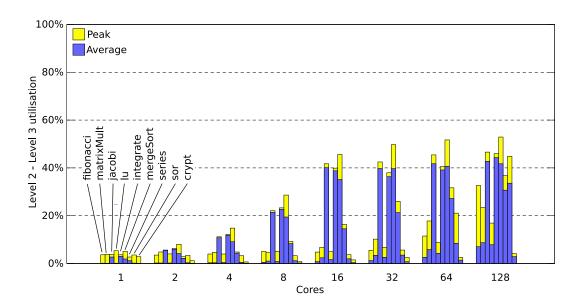

| 7.20                    | Level 2 - level 3 bus utilisation                 | 8 |

| 7.21                    | L1 bus negative acknowledgments                   | 8 |

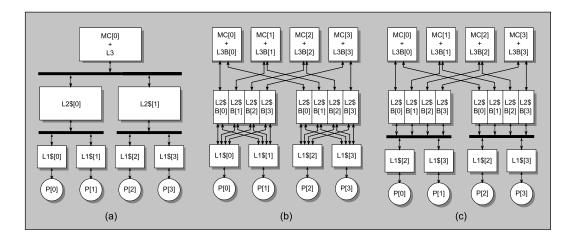

| 7.22                    | CMC architectures                                 | 9 |

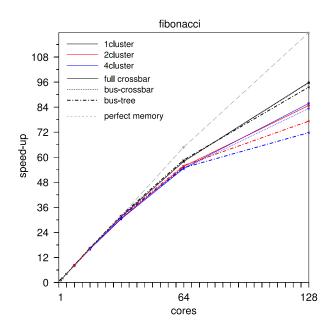

| 7.23                    | CMC scaling - fibonacci                           | 0 |

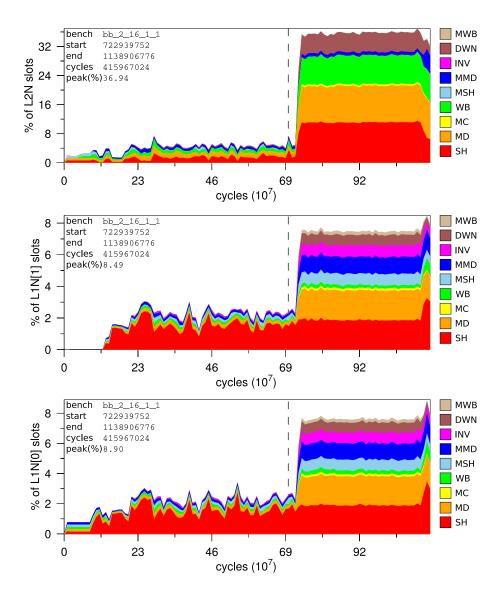

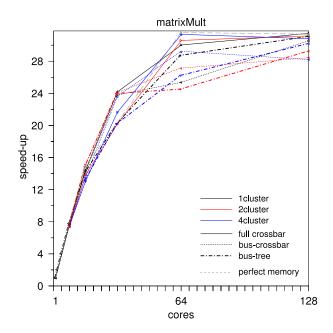

| 7.24                    | CMC scaling - matrixMult                          | 1 |

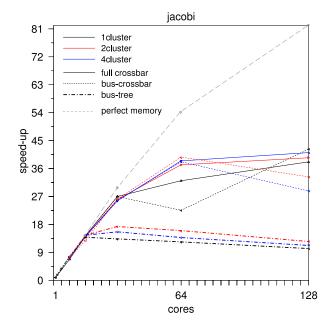

| 7.25                    | CMC scaling -jacobi                               | 1 |

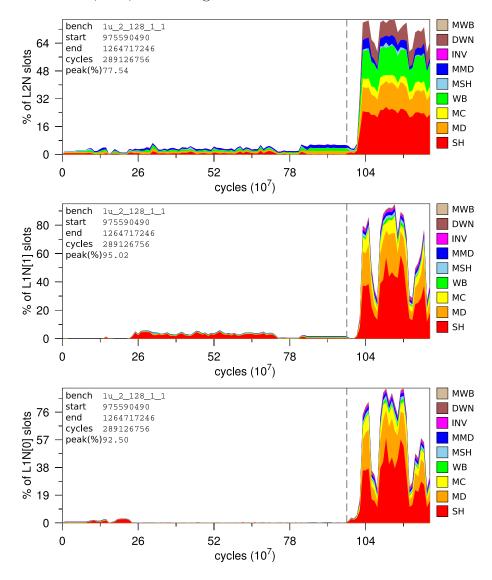

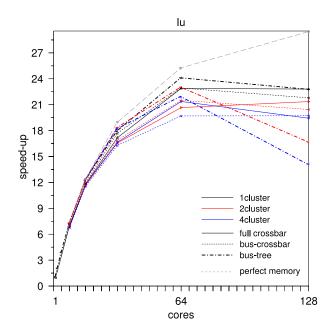

| 7.26                    | CMC scaling - 1u                                  | 2 |

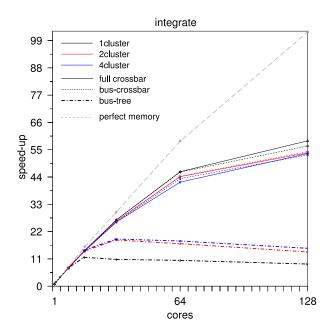

| 7.27                    | CMC scaling - integrate                           | 2 |

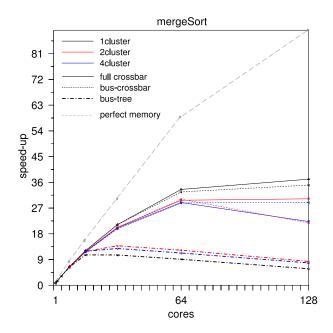

| 7.28                    | CMC scaling - mergeSort                           | 3 |

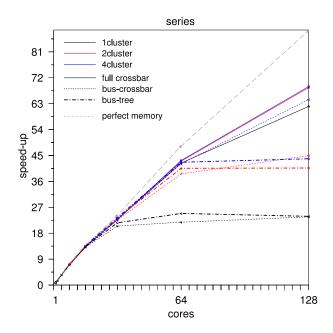

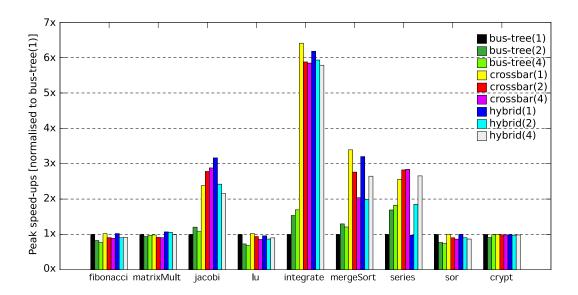

| 7.29                    | CMC scaling - series                              | 3 |

| 7.30                    | CMC scaling - sor                                 | 4 |

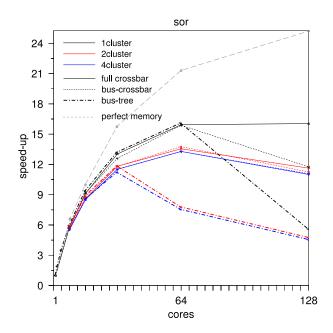

| 7.31                    | CMC scaling - crypt                               | 4 |

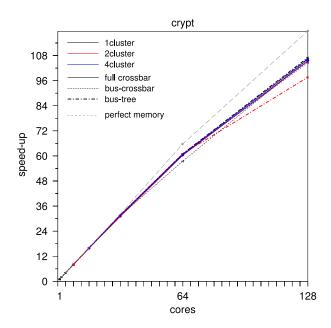

| 7.32                    | CMC scaling speed-ups                             | 6 |

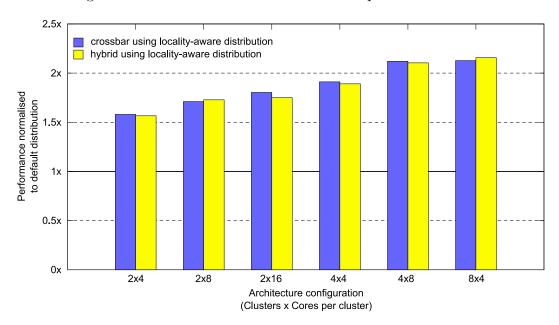

| 7.33                    | Locality-aware: setClusterAffinity                | 9 |

| 7.34                    | Locality-aware synchronisation                    | 9 |

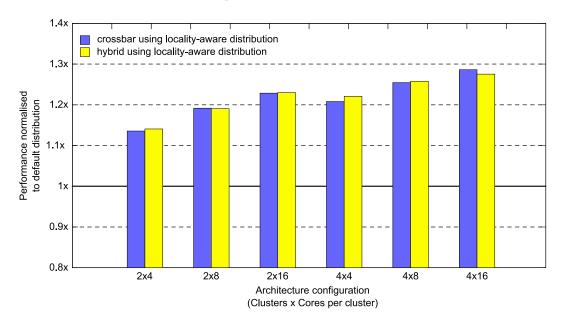

| 7.35                    | Locality-aware isolation                          | 0 |

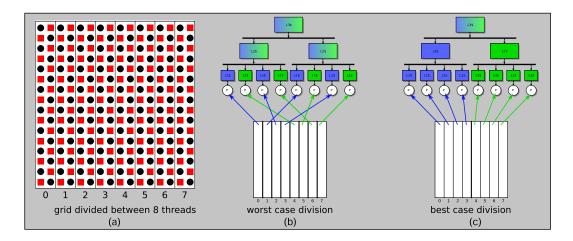

| 7.36                    | Locality-aware restructuring of the sor benchmark | 2 |

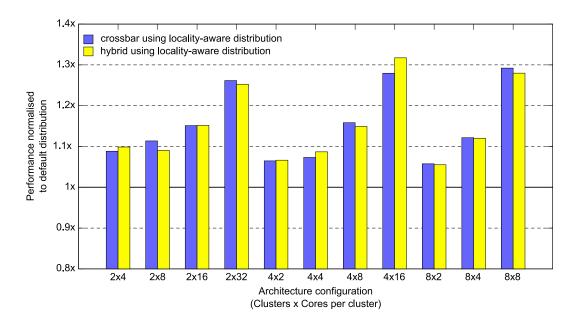

| 7.37                    | Locality-aware isolation                          | 4 |

| A.1                     | Register form $R_c \leftarrow R_a$ op $R_b$       | c |

| A.1<br>A.2              |                                                   |   |

| A.2<br>A.3              |                                                   |   |

|                         | Branch form                                       |   |

| $\mathbf{A} \mathbf{A}$ | MAMORY TORM                                       | n |

| List | of | Α   | løori | ith | ms   |

|------|----|-----|-------|-----|------|

| LIJU | Οı | / \ | IZULI | LII | 1113 |

| L'acho digtanco ancoding  |     |   |

|---------------------------|-----|---|

| 1 Cache-distance encoding | -11 | 2 |

### Abstract

Chip MultiProcessor (CMP) architectures are fast becoming ubiquitous. Their widespread adoption has been motivated by three dominant factors; power and thermal limits have constrained higher clock frequencies, the memory wall has expedited concurrency as a means of maintaining performance, and technology advances have increased transistor budgets enabling the integration of multiple cores on a single chip. It is anticipated that a trend of increasing the number of cores with increasing transistor budgets will emerge, and that within the next decade it will be feasible to integrate up to 128 cores within a single chip architecture.

This thesis investigates the scaling limitations of current single bus CMP architectures and proposes a Chip Multi-Cluster (CMC) architecture as a feasible approach for future many-core designs. A novel cache coherence protocol and hardware support for maintaining coherence across multiple clusters is presented. Additionally, support at the hardware/software interface is provided to allow locality-aware thread creation and distribution in order to best utilise the architecture. Several possible implementations of the CMC architecture are studied through cycle accurate simulation using multithreaded benchmarks.

# Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institution of learning.

# Copyright

Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of the School of Computer Science.

## Acknowledgements

I would like to thank my supervisor Professor Ian Watson for all of the help, encouragement, support and constructive feedback he has given me over the last four years. I would also like to thank Ian Rogers, Ahmed El-Mahdy and Andrew Dinn for proof reading this thesis and for the many discussions that have continued to motivate me.

I would like to thank all of the members of the Jamaica project and the APT group. Those with whom I have been able to discuss research ideas and those who have provided lively conversations over a few pints. I would also like to thank my friends outside of computer science for keeping me sane by taking me away from computers and remaining in contact with me throughout.

Special thanks to my parents for their continued support and encouragement, and to my brother Jonathan and sister Katherine for their enduring friendship.

Finally, and certainly not least, a debt of gratitude is owed to Laura for her unfaltering patience, understanding and love.

# CHAPTER 1

## Introduction

A chip multi-cluster architecture based on a novel multi-level cache coherence protocol is presented in this thesis. This architecture supports interleaved multi-threading and provides facilities for lightweight locality aware thread distribution. The architecture is simulated using a novel cycle-level simulation platform and is used to evaluate the concepts associated with increasing the number of cores, bus contention and wire delay, scaling the memory hierarchy, and locality aware task distribution.

## 1.1 Motivation

Over 40 years ago Gordon Moore observed that the total number of devices integrated on a chip doubled every 12 months [111]. Based on this observation he boldly predicted that this trend would continue throughout the 1970s and would subsequently slow down to a doubling every 24 months in the 1980s. This prediction, commonly referred to as Moore's Law, triggered a revolution in microarchitecture innovation and design that has delivered enormous increases in computing power.

During the last decade alone, the number of transistors integrated on a single die has doubled every 24 months and the relative performance of microprocessors when executing SPECint benchmarks has grown by over 75 times [63]. In the same period the type of applications processed by microprocessors has diversified enormously. With further expansion of broadband internet, multimedia, gaming and mobile communication the complexity of such application areas continue to push a demand for yet more performance increases.

Sustaining this performance growth has, to date, largely been achieved through technology scaling. In the last 10 years mainstream semiconductor technology has scaled feature sizes down from 350nm to 65nm, enabling operating frequencies to increase from 200MHz to 3.2GHz, on the Intel Pentium Pro and Pentium 4 respectively. This frequency increase, of 16 times, has provided the majority of the 75 times performance increase, with the remaining increase due to microarchitecture innovation and exploiting higher transistor budgets. Both frequency increases and exploiting higher transistor budgets are becoming increasingly difficult in single processor designs.

Until recently increasing transistor budgets have been exploited by increasing the pipeline depth, issue width and reorder buffers of single processor superscalar architectures. Unfortunately, the performance gained in this manner has been diminishing [20] and further small performance gains require discouragingly complex additional hardware. A recent study [53] showed that there is a growing discrepancy between the increase in area employed by a new microarchitecture and the increase in performance, with the increase in performance growing at the square root of the increase in area. A productivity gap is also emerging, as designers and design tools are not able to keep pace with the increase in complexity of modern designs. This was highlighted by the International Technology Roadmap for Semiconductors as a grand challenge [139].

As mentioned previously, the rapid increase in clock frequency, 40 percent per year for the past 15 years, has been the dominant factor in microprocessor performance increases. This speed increase has come from two sources: smaller, faster transistors and deeper pipelines with shorter critical paths. For two reasons this increase has diminished in the past few years. Firstly, the rapid increases in speed have hastened the emergence of a *power wall*. Simply put, the power consumed by modern microprocessors is becoming too costly for the end user, and more

importantly perhaps, the heat dissipated is becoming too expensive to cool [38]. Secondly, as feature size decreases transistor switching speed increases, however wires are not scaling as quickly [17]. This is leading to wire delay limited circuits, where the percentage of the chip accessible in one clock cycle is decreasing per generation.

With the main techniques responsible for increases in microprocessor performance rapidly expiring, a shift towards different design strategies capable of maintaining performance increases is currently underway. Although many alternatives were initially proposed in a special issue of IEEE Computer [19], parallel architectures, in the form of Chip Multiprocessors (CMP) have become the focus of most major microprocessors roadmaps [81, 127, 78, 108]. These architectures are able to overcome or avoid design challenges of modern microprocessors and at the same time continue increasing performance, largely by exploiting parallelism.

The remainder of this chapter introduces and expands on some of the key issues facing modern microarchitecture design. This is followed by a discussion of how computer architects are innovating in order to overcome these challenges.

# 1.2 Microprocessor Design Challenges

As mentioned previously, the application space for general purpose microprocessors is vast and is growing as new technologies and application areas are discovered. Applications, whether multimedia, gaming, communications or scientific, require microprocessors that are capable of processing a variety of tasks, many within imposed timing constraints. At the same time computer systems are used to run multiple applications concurrently, adding additional complexity to the workload of a general purpose microprocessor.

For these purposes it is desirable that each successive generation of microprocessor is able to face a changing and growing application space, and is able to remain capable of processing workloads into the future. At the same time the end user of a computer system does not want the cost of ownership to become overly expensive, so power consumption is a key concern. The design of processors optimised for performance, power and cost requires a carefully balanced architecture which

addresses numerous challenges. This section describes the major challenges that architects face in designing modern architectures.

#### 1.2.1 Wire Delay

As semiconductor technology advances, transistors are becoming smaller and more transistors can be integrated onto a single silicon die. These transistors consume less power and the time taken by them to switch state, the gate delay, decreases. In real terms transistors, and hence logic, on a chip are becoming cheaper and faster.

In order to connect transistors as their feature sizes decrease, the width of wires writhin a given technology must also decrease. This reduces the cross-sectional area of the wires (A), which increases the resistance (R) per unit of length (L)because resistance is inversely proportional to area, Equation 1.1. In the equation  $\rho$  is the resistivity constant of the material.

$$R = \frac{\rho L}{A}$$

$$\tau = RC$$

$$(1.1)$$

$$(1.2)$$

$$\tau = RC \tag{1.2}$$

This means that the delay  $(\tau)$  through a wire, Equation 1.2, where C is wire capacitance, will only decrease linearly with its length, which depends on the underlying transistor technology [17]. As wire delay is only decreasing linearly and gate delay is decreasing more rapidly, circuits are increasingly becoming wire delay limited. This happens because the number of gates reachable in a single clock cycle is decreasing.

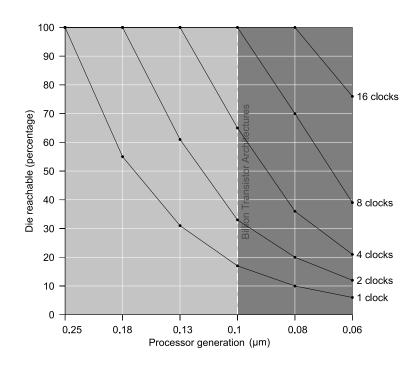

The overall impact that this has on a microarchitecture is that shrinking a wire delay limited circuit will not make it run any faster, as less of the silicon is available within one clock cycle [66]. In fact, it was estimated that when the semiconductor technology gets down to a  $0.1\mu m$  process, only 16% of the die will be reachable within a single clock cycle [104], Figure 1.1.

**Figure 1.1:** Predicted percent of die reachable by each generation [104].

## 1.2.2 Memory Gap

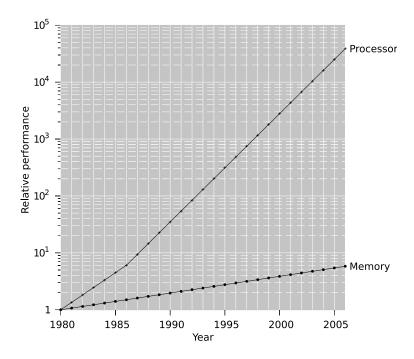

In order for a microprocessor to operate efficiently it needs to be fed with a steady stream of instructions to process and to have access to the data required by those instructions. In today's architectures access to main memory, to load or store instructions and data, is often a bottleneck. This bottleneck is caused by the discrepancy in memory and processor speeds. While processor clock speeds have increased by approximately 55% per year since 1980, memory performance has only been increasing at less than 10%, creating a widening memory gap [62], see Figure 1.2.

This increasing memory gap reduces the benefit of increased operating frequencies; whenever a processor requires access to a piece of data or instruction not currently in a local cache it has to wait. Access to memory, in modern microprocessors, takes hundreds of cycles during which time the processor remains idle. This gap is especially evident in commercial applications that are transaction intensive.

In order to alleviate this problem, smaller *cache* memories are used to keep frequently accessed data local to the processor and most modern architectures now

**Figure 1.2:** A growing gap between memory speed and processor speed leads to bottlenecks during data intensive workloads [62].

contain at least two levels of cache memory, of which many different configurations have been researched [75, 42]. Complimentary to storing frequently used data are schemes for fetching data in advance of requirement. These *prefetching* schemes have been attempted both in software [23, 113] and hardware [28, 162] to reduce the impact of the memory wall further.

#### 1.2.3 Limits of Instruction Level Parallelism

Many modern processors contain hardware support for exploiting instruction level parallelism (ILP). ILP exists where multiple instructions are independent from each other and can be executed simultaneously. Independent instructions found within an instruction stream can be issued to multiple functional units within the processor for execution, and modern superscalar architectures are capable of dispatching four or more instructions per clock cycle to separate functional units.

Whilst this approach has enabled performance increases, and fundamentally allows more than one instruction to be executed in each clock cycle, it does have limitations. In particular instructions within the same thread usually display a

high degree of dependence, and finding further independent instructions requires the ability to look further ahead in the instruction stream, which requires additional hardware.

A plethora of studies have looked at the limits of ILP [10, 22, 166, 129]. Many have shown that even in the presence of theoretical perfect caches<sup>1</sup>, and perfect branch prediction, the maximum attainable ILP is still only in the order of 10 to 100 instructions per cycle (IPC) [62]. In practice ILP very rarely attains greater than 4 IPC with relatively complex but manageable hardware. Beyond this, the complexity of large instruction fetch windows, broadcast networks which suffer from wire delays, multiple functional units and centralised control becomes impractical. Some of this hardware, for example register bypass logic, grows quadratically [123] when attempting to exploit further ILP and performance gains diminish.

## 1.2.4 Power Limits

Power consumption has gone from being a factor that needed to be considered when designing a new architecture, to becoming a first order constraint on the design of new architectures. The limit to acceptable power consumption is usually realised when the ability to dissipate the heat from a processor becomes difficult. With the recent rapid increases in clock frequency and the continual increase in chip transistor density, the heat dissipated by modern high end microprocessors is becoming unmanageable.

Power consumption in a processor comprises a static component, called leakage power, and a dynamic component, called switching power, Equation 1.3. Traditionally the static component has been a fraction of the dynamic component, however in modern semiconductor technologies this is changing.

$$Power_{total} = Power_{static} + Power_{dynamic}$$

$$= V \times I_{leakage} + \frac{CV^2 f_{clock}}{2}$$

(1.3)

<sup>&</sup>lt;sup>1</sup>A theoretical perfect cache would have the property that each access would result in a cache hit.

| Process              | Old Architecture     | Area mm <sup>2</sup> | New Architecture   | Area mm <sup>2</sup> | Area Increase |

|----------------------|----------------------|----------------------|--------------------|----------------------|---------------|

| $1.0 \mu \mathrm{m}$ | i386 (compaction)    | 42.25                | i486 (lead)        | 132.25               | 3.1           |

| $0.7 \mu \mathrm{m}$ | i486 (compaction)    | 90.25                | Pentium (lead)     | 289                  | 3.2           |

| $0.5 \mu \mathrm{m}$ | Pentium (compaction) | 148.84               | Pentium Pro (lead) | 299.29               | 2.0           |

Table 1.1: Growth in area between successive generations of Intel architectures.

As the feature size decreases with semiconductor technology, the size of the transistors and hence their capacitance (C) decreases. This reduced capacitance decreases the transistor switch time, or gate delay, leading to increased performance. However as the feature size decreases the voltage (V) must be lowered to reduce the interference between the closer components and in order to meet thermal requirements for the design.

In order to keep the chip functioning correctly at a reduced operating voltage the threshold voltage, the threshold at which the transistor switches state, must be decreased. A lower threshold voltage brings it closer to ground which increases the static leakage current,  $I_{leakage}$ , increasing the static power consumption. Recent research has focused on techniques to reduce static power consumption [115].

## 1.2.5 Design Complexity

Each semiconductor technology generation is allowing more transistors to be integrated onto a single silicon chip, and potentially these additional transistors can be incorporated into future microarchitecture designs. Recently Intel released the Montecito processor [107], a dual-core, dual-threaded Itanium architecture, which incorporated 1.72 billion transistors in the design, taking silicon chips into the era of billion transistor architectures.

Unfortunately, growth in performance in a new microarchitecture is declining in subsequent generations and is approximately proportional to the square root of the growth in area of the microarchitecture in any given technology generation. Taking the x86 family of architectures as an example, the growth in area of approximately 2-3 times, Table 1.1, was accompanied by only a 1.5 - 1.7 times increase in performance.

This discrepancy is due to the hardware that was added in subsequent generations of microarchitecture. As previously mentioned, hardware for exploiting ILP suffers from diminishing returns, as does adding larger cache memories. At some point quadratic increases in the size of the hardware only achieve linear increases in performance.

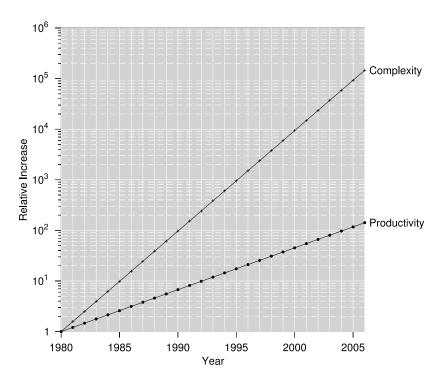

**Figure 1.3:** A growing gap between increases in the complexity of a chip and productivity of design engineers and tools.

Another important issue associated with design complexity is designer productivity. The International Technology Roadmap for the Semiconductor Industry (ITRS) 2005 [139] continued to highlight the gap between design complexity, measured as the total number of transistors on a chip, and designer productivity measured as transistors designed-in per staff member per month, Figure 1.3. The number of transistors on-chip is growing at a rate of 58% per year, but design productivity is only increasing at a rate of 21% per year. In order to close the productivity gap the ITRS stated that reuse, testing and verification must all improve by over 2 times.

# 1.3 Design Solutions

Computer architects have responded, with many novel solutions, to the current problems facing microprocessor design. In the following section some of these solutions are presented.

## 1.3.1 Exploiting Parallelism

As increases in the underlying circuit speed decline, due to issues such as power density and clock distribution, it appears that future performance will need to come from doing more work in parallel. As mentioned previously, Section 1.2.3, architectural techniques capable of extracting ILP are now reaching practical limits, motivating the need to look elsewhere for parallelism.

Just over 40 years ago, a taxonomy was proposed placing all computer architectures into four categories based on the parallelism in both the instruction and data streams [48]. This model is still useful for explaining where additional parallelism can be found in future microprocessors.

#### Single Instruction, Single Data Stream (SISD)

This category includes the uniprocessor, where a single instruction stream is processed against a single data stream. As discussed parallelism in SISD architectures can be extracted using ILP techniques, as is the case in superscalar architectures [123]. In addition to the ILP extracted through complex hardware, simpler hardware in combination with complex compiler techniques can be used to define explicitly parallelism in a single instruction stream, as is the case in Very Long Instruction Word (VLIW) architectures [45]. Both of these techniques have reached practical limits and further advances require discouraging expense in hardware with low utilisation.

#### Single Instruction, Multiple Data Stream (SIMD)

In SIMD architectures a single instruction is executed by multiple Processing Elements (PEs) on different data streams. SIMD architectures exploit data level

parallelism (DLP), by applying the same operation to multiple data items in parallel. Each PE has its own data memory, hence multiple data streams, however each PE is driven by the same instruction streams, usually from a single control processor responsible for fetching and dispatching each instruction.

For multimedia and scientific applications, which exhibit significant amounts of DLP, this approach is very efficient. As these applications have rapidly migrated into the desktop space, architectures have incorporated SIMD extensions into the instruction set [126, 39, 118] and provided special purpose hardware for executing these instructions. SIMD instructions are now ubiquitous in modern general purpose architectures, accelerating cryptographic, media encoding and decoding, and graphics processing.

The performance of SIMD architectures is limited only by the amount of DLP available in any given application, as the addition of further PEs is relatively cheap, in comparison to the structures associated with extending superscalar techniques.

## Multiple Instruction, Single Data Stream (MISD)

MISD architectures process a single data memory with multiple instruction streams. An implementation of a MISD architecture [58] has been shown to be useful for very specific tasks, such as fast pattern matching in large data streams for which there is no efficient index, and hence multiple different search tasks can be executed on the same data in parallel. It appears that MISD architectures have not shown significant benefits in any general purpose application areas, and as such no commercial architecture of this type has been developed.

#### Multiple Instruction, Multiple Data Stream (MIMD)

In MIMD architectures multiple processors execute independent instruction streams on independent data streams. Each processor in a MIMD architecture executes a separate thread of control. That is, they execute independent instruction streams on largely independent<sup>2</sup> data streams in parallel. This thread-level parallelism

<sup>&</sup>lt;sup>2</sup>In MIMD architectures shared memory coherence, in particular atomic primitives such as synchronisation, may prevent the streams from being fully independent.

(TLP) is far more flexible than DLP and it can be exploited by a larger set of the application space of general purpose microprocessors. For this reason TLP is perhaps the best candidate to achieve future performance gains in general purpose microprocessors.

#### Thread Level Parallelism

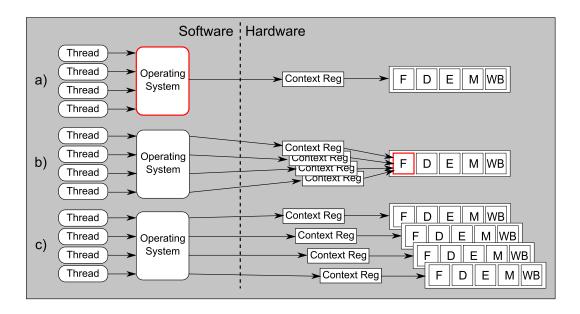

Many modern programming languages allow programmers to define, explicitly, independent threads of control within a program all of which can be executed in parallel. Additionally multi-processing operating systems allow multiple processes to be run concurrently. Each of these processes may be run in parallel, and in turn may contain threads that can also be run in parallel. Prior to MIMD architectures, SISD architectures relied on the operating system software to switch among concurrent processes and threads, ensuring that each was allowed sufficient execution time within the same processor to continue making forward progress, Figure 1.4 (a).

In order to accelerate TLP, many modern processors, especially in the server class, incorporate hardware that allows a single processor to maintain information for multiple threads, switching between each thread at a hardware level and filling empty slots in the processor's pipeline on long latency cache misses, Figure 1.4 (b). In highly threaded applications, of which the operating system is an example, multi-threaded hardware can help with hiding the long idle times associated with data and instruction accesses that miss local or intermediate caches. Due to the increasing memory gap, Section 1.2.2, these idle times can be several hundreds of clock cycles during which time, in the absence of multi-threading hardware, the processor would effectively remain idle. In some data intensive applications, such as database workloads, the idle time in modern microprocessors is as much as 75% [90]. A recent study [53], stated that adding multithreading hardware, in the study two threads, to an existing architecture adds approximately 10% additional logic to the CPU, increases the maximum power by less than 10% but can increase throughput by over 30%.

Another approach to exploiting TLP in hardware is to add additional processors to the architecture, via an off-chip interconnect at the board or multi-chip module (MCM) level, or, with billion transistor budgets, increasingly in the same

**Figure 1.4:** Exploiting thread-level parallelism: a) software scheduling, b) multi-threaded hardware, c) multi-processor hardware.

silicon die, Figure 1.4 (c). Additional processors can provide linear increases in performance with die size on transactional workloads such as TPC-C [34]. CMPs, where multiple processors are integrated on a single chip, can provide performance increases even on applications exhibiting fine-grained TLP.

## 1.3.2 Partitioned Designs

As mentioned in Section 1.2.1, wire delay is diminishing the area of a chip reachable in a single clock cycle with each generation of process technology. This motivates the need for designs where cross chip communication is minimised.

A new class of parallel architectures have been designed with wire delay treated as a first order design constraint. These communication-centric architectures such as RAW [165], Smart Memories [102] and TRIPS [137] keep the length of critical paths in the design to within 1 or 2 cycles. Whilst these architectures overcome limits due to wire delay they also impose a message-passing [165] or data-flow [141] paradigm of programming onto the compiler or software.

CMPs can also be designed to overcome wire delay limits. Each of the many small processing cores on CMPs take up a relatively small area on the total chip, minimising the size of critical paths within each core. Only infrequently used and therefore less latency critical wires, connecting processors and caches, need to be long.

## 1.3.3 Bridging the Memory Gap

The memory gap, as mentioned in Section 1.2.2, is constantly increasing the penalty, in cycles, of memory loads and stores. In modern processors, such as the Intel Pentium 4, the cost of accessing main memory can be as large as 200-300 cycles. For this reason today's high performance processors employ multiple levels of cache memory to help reduce the performance gap.

Increasing the size of on-chip caches decreases the chance of a memory operation in the processor having to go all the way to main memory. In today's semiconductor technologies it is possible to integrate extremely large caches on-chip. Indeed, Intel's Montecito [107] processor included nearly 27MB of on chip cache memory, improving the performance by almost a factor of 2 over previous generations of the same architecture, Figure 1.5.

Cache memories cannot totally close the memory gap, as untouched data, when first loaded must always come from main memory unless prefetched in advance using hardware [28] or software [23]. It is however possible to improve performance even during loads and stores to untouched areas of memory by exploiting memory-level parallelism (MLP) [30]. MLP can be exploited by overlapping multiple accesses to main memory during the period that the processor is idle waiting for the first access to resolve.

To illustrate the potential of MLP as a performance booster, consider a memory-bound application that spends two-thirds of its execution time in off-chip accesses, doubling the MLP can halve the time spent in these accesses and potentially improve performance by 25%. As long latency memory accesses are fairly dynamic, occurring when a cache has evicted previously held data or has not yet seen it, hardware schemes are needed to look for memory accesses that can be overlapped.

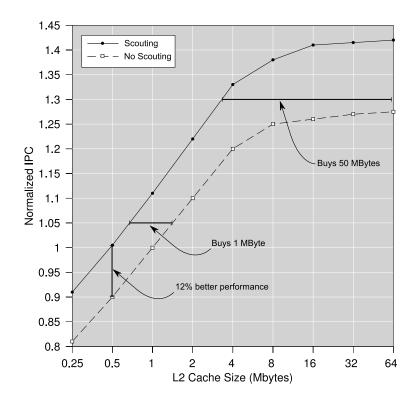

One such scheme is *hardware scouting* [27]. When a processor is forced to stall on a memory operation, a scout thread is invoked. The scout thread's sole purpose is to run ahead in the instruction stream and look for memory accesses, while the real

**Figure 1.5:** The effect of increased cache size (MB) on performance  $(\times)$  of the Itanium 2 processor [107].

thread is stalled waiting for the initial access to come back. The hardware scout can pass control flow operations such as branches and jumps taking whichever path is deemed most likely, and can continue scouting for memory accesses many hundreds of cycles in advance of the real thread. Obviously when the initial memory access is resolved the real thread is switched back in, and continues from the point at which it stalled. Any memory accesses that were overlapped will have been fetched into local caches and the cost for the following accesses is reduced. Hardware scouting can be more efficient, in terms of logic area consumed, than simply increasing the size of caches, as illustrated in Figure 1.6.

# 1.3.4 Design Abstraction and Replication

Two methods by which the design complexity problem can be addressed are abstraction and replication. The International Technology Roadmap for Semi-conductors [139], has continually outlined the need for both of these methods to be increased by at least a factor of two in order to bridge the productivity gap.

**Figure 1.6:** Comparison of hardware scouting and increasing cache size [27].

Abstraction can be addressed by designing systems at a higher level. Initially circuits were designed at the transistor level, then at the gate level using libraries, and more recently at the macro block level. With billion transistor budgets the abstraction level may have to be raised higher once more, possibly to the processor or multiple processor level. Next generation architectures can be composed of multiple copies of the previous generations in order to best utilise the increase in transistor space.

Replication within an architecture is also necessary. This can already be seen with current generation chip multiprocessors. Sun's Niagara processor [81] contains 8 identical Sparc in-order cores, IBM's Power 5 [78] and Intel's Core Duo [108] architectures both contain two identical superscalar processors, and STI's<sup>3</sup> Cell processor [127] contains one Power processor and eight synergistic processors. All of these architectures have reduced the design time normally associated with a new architecture through successful replication and reuse.

<sup>&</sup>lt;sup>3</sup>STI - a collaboration by Sony, Toshiba and IBM

# 1.4 Summary

In this introduction, the major challenges facing modern microprocessor design have been outlined. These challenges and the demand for continual performance gains, have motivated research within this area. Moreover some of the solutions to these challenges have been discussed, and many come from a shift to parallelism as a design paradigm. In this context CMP architectures have been shown to have significant potential for future general purpose high performance processors.

## 1.5 Research Aims

The research presented in this thesis focuses on CMP architectures. An architecture is presented that scales beyond the current generation of CMPs by incorporating a multi-level cache hierarchy on a chip, allowing the notion of Chip Multiple-Cluster (CMC) architectures. In order to facilitate this clustering, a novel multi-level cache hierarchy is presented as well as a novel cache coherence protocol to maintain shared memory coherency. A scheme allowing locality based task distribution is presented, showing that in such architectures task isolation and task affinity can be used to improve performance.

## 1.6 Contributions

The contributions made by the work presented in this thesis are summarised as follows:

- A multi-level shared memory cache coherence protocol.

- Cache hardware to support a multi-level shared memory cache coherence protocol.

- An instruction set extension and mapping mechanism for exploiting cache locality between threads.

- A simulation platform capable of evaluating, through cycle-level simulation, chip multiprocessor and chip multi-cluster architectures containing up to and including 128 cores.

- A fully cache coherent study, using real multithreaded applications, of the effects and performance of large scale chip multiprocessor and chip multicluster architectures.

## 1.7 Thesis Structure

The rest of the thesis is structured as follows:

Chapter 2 reviews the availability of parallelism within software and the exploitation of parallelism within software and architecture design.

Chapter 3 outlines the Jamaica CMP which is the base architecture subsequently extended in later chapters. The chapter also presents the simulation platform used to investigate and analyse the architecture, and describes the software toolchain supporting it.

Chapter 4 introduces a multi-level cache coherence protocol capable of maintaining shared memory coherence across multiple on-chip clusters.

Chapter 5 presents the hardware extensions necessary to implement the coherence protocol. In particular a deadlock free queueing mechanism is described.

Chapter 6 introduces an extension to the instruction set which allows software to exploit locality by controlling the affinity of distributed threads.

Chapter 7 evaluates the performance of the multi-level coherence protocol, the architecture supporting it, and the optimisations using locality aware task distribution.

Chapter 8 concludes the thesis by summarising the contributions made and suggesting future directions of research that could be conducted.

Finally, the Appendix includes details of the Jamaica instruction set for reference.

# 1.8 Publications

#### Accepted Papers

- M. J. Horsnell, J. Zhao, I. Rogers, A. Dinn, C. K. Kirkham, I. Watson, Optimizing Chip Multiprocessor Work Distribution using Dynamic Compilation, European Conference on Parallel and Distributed Computing, Rennes, France, August 28-31, 2007. Lecture Notes in Computer Science, Volume 4641/2007, pages 258–267.

- I. Rogers, <u>M. J. Horsnell</u>, I. Watson, *Virtualization and chip multiprocessor memory management: the JAMAICA architecture*, 5<sup>th</sup> UK Memory Management Network Workshop, University of Glasgow, UK, July 2005.

- M. J. Horsnell, I. Watson, Harnessing Java for Novel Chip-Multiprocessor Architecture Simulations, PREP2005 Conference, Lancaster, UK, March 2005.

#### Abstracts

- M. J. Horsnell, I. Watson, Simulating the Jamaica CMP Architecture, HiPEAC ACACES, L'Aquila, Italy, July 2005.

- M. J. Horsnell, I. Watson, Cycle-Accurate, Distributed Chip Multiprocessor Simulation, PREP2004 Conference, Hertfordshire, UK, March 2004.

# Application and Architectural Parallelism

With the gains available from conventional uniprocessor architecture techniques diminishing with each successive generation of processor technology, parallel computer architectures are being embraced by industry and researchers to provide scalable, consistent performance increases.

Parallel architectures consist of multiple processing elements that cooperate in order to solve problems, ideally in a shorter period of time than solving the problem using a single processing element alone. There exist three constraints on the performance attainable from a parallel architecture: the available parallelism in the application, the parallelism available in the hardware and the efficiency and nature of distributing and scheduling parallel work.

# 2.1 Application Parallelism

For a parallel computer architecture to realise any speed-up during the execution of a given workload, the workload must to some extent be amenable to parallelisation. The amount of an application that can be successfully parallelised and executed concurrently on a parallel architecture determines the extent to which the parallel architecture is capable of reducing the overall execution time.

### 2.1.1 Amdahl's Law

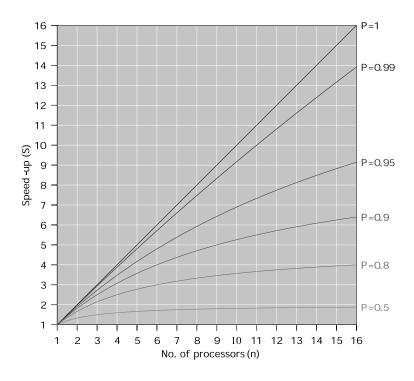

The correlation between the amount of parallelism in a given code and the maximum speedup from parallel execution is commonly referred to as Ahmdahl's Law [4], and is a demonstration of the law of diminishing returns. The maximum theoretical speedup S, attainable from running an application on N processors, is shown in Equation 2.1, where P is the percentage of the code that can be parallelised.

$$S = \frac{1}{(1-P) + \frac{P}{N}} \tag{2.1}$$

When Amdahl's law is applied, as shown in Figure 2.1, applications containing large percentages of parallel code sections do not guarantee large performance speedups. When P=0.9, that is 90% of the code in a target application is amenable to parallelisation, and assuming no overheads associated with the parallel execution of the code, a 16 processor machine realises a speedup of less than 7. This result may initially appear disappointing, however, for the reasons outlined in Section 1.2, it may be infeasible to design and build a processor that can run at 7 times the clock frequency, whilst remaining inside a given power budget, therefore it may be more cost and time effective to replicate multiple processing cores from an existing design, in order to achieve the additional performance.

# 2.1.2 Implicit and Explicit Parallelism

With the amount of parallelism available in an application determing the amount of speedup attainable on a parallel architecture, it becomes essential to locate or introduce parallelism into an application. Locating parallelism within existing code is referred to as exploiting *implicit* parallelism, introducing or programming-in parallel sections of code is referred to as exploiting *explicit* parallelism.

**Figure 2.1:** Amdahl's Law: Parallel speedup (S) vs. parallel fraction (P).

## Implicit Parallelism

Writing programs without concern for how they map onto a given parallel architecture has obvious benefits. However, without explicity marking sections in the code as being parallel, a good automated strategy needs to be employed in order to decide when to fork parallel computation. Much work has been done in this area, with static parallelising compilers [122, 56, 16, 59] and also dynamic run-time recompilation techniques [136, 41, 172], ranging from conservative approaches [37, 121, 120] where all dependencies must be guaranteed before applying a given parallelisation technique to liberal speculative techniques [57, 135, 148] that speculate on dependencies, predict values and roll-back on dependency violations or value misspredictions.

### Explicit Parallelism

Implicit parallelism, whilst being an attractive approach to locating parallelism, often under performs as it either extracts parallelism conservatively, missing potential performance gains, or it extracts parallelism too liberally and then wastes

time cleaning up speculative state changes. Additionally the performance of implicit techniques are often hard to reason without a solid understanding of the underlying compiler or runtime execution environment.

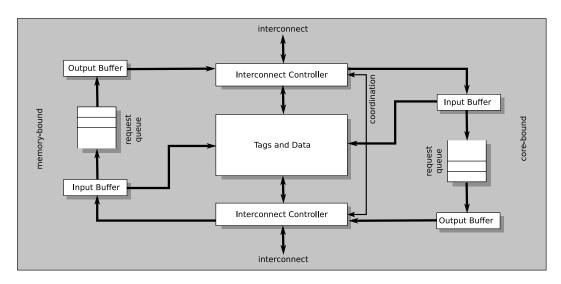

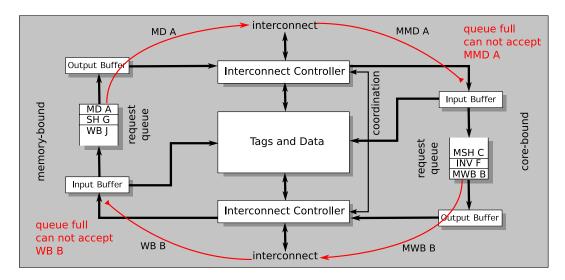

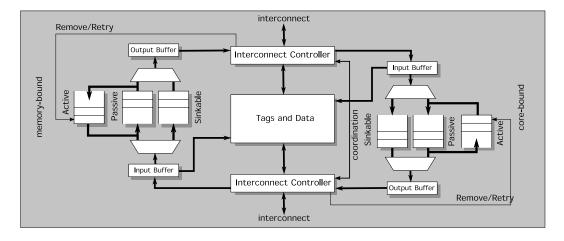

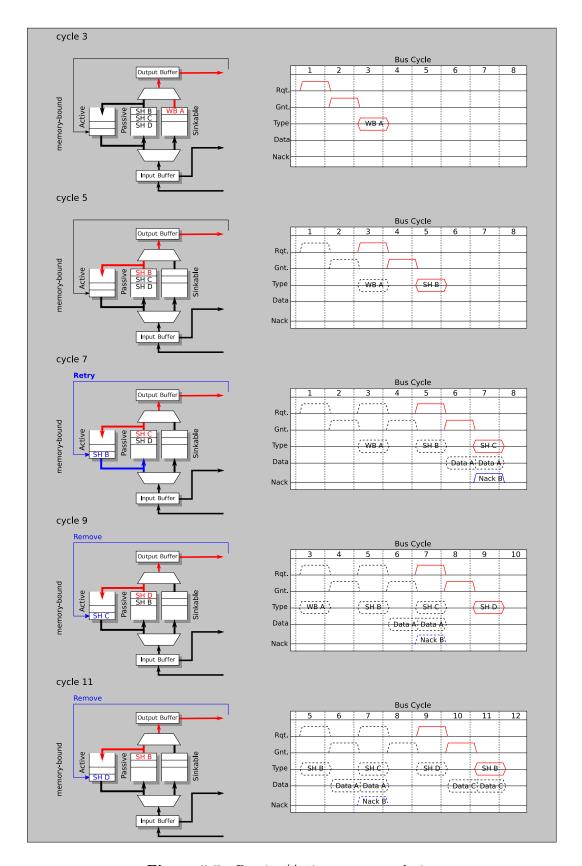

An alternative approach is for the programmer to annotate a program in order to indicate to the compiler and runtime execution environment that parallel computation might be beneficial. Most high-level programming languages support abstractions for implementing concurrency such as the concurrency package [94] in Java, and the POSIX thread library [21] in C and C++. Using such libraries it is possible for the programmer to abstract away much of the detail of the underlying implementation and concentrate on writing parallel applications.