# CONFIGURING A MASSIVELY PARALLEL CMP SYSTEM FOR REAL-TIME NEURAL APPLICATIONS

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Engineering and Physical Sciences

2009

By M. Mukaram Khan School of Computer Science

## Contents

| A            | bstra  | $\mathbf{ct}$                | 12 |

|--------------|--------|------------------------------|----|

| D            | eclara | ation                        | 13 |

| $\mathbf{C}$ | opyri  | $_{ m ght}$                  | 14 |

| A            | cknov  | wledgements                  | 15 |

| 1            | Intr   | oduction                     | 16 |

|              | 1.1    | Background                   | 16 |

|              | 1.2    | Motivation                   | 18 |

|              | 1.3    | Aim and Objectives           | 19 |

|              | 1.4    | Contributions                | 20 |

|              | 1.5    | Thesis structure             | 21 |

|              | 1.6    | Publications                 | 23 |

| <b>2</b>     | The    | Brain – Nature's Masterpiece | 25 |

|              | 2.1    | Introduction                 | 25 |

|              | 2.2    | Basic Neural Structure       | 26 |

|              |        | 2.2.1 Membrane               | 27 |

|              |        | 2.2.2 Axon                   | 28 |

|              |        | 2.2.3 Dendrite               | 29 |

|              |        | 2.2.4 Synapse                | 30 |

|              | 2.3    | Membrane Potential           | 30 |

|              | 2.4    | Action Potential             | 32 |

|              | 2.5    | Synaptic Transmission        | 34 |

|              | 2.6    | Neural Networks              | 35 |

|              | 2.7    | Neural Computation           | 36 |

|              |        |                              |    |

|   | 2.8  | Temporal Dynamics    40                                                                                                                                             |

|---|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 2.9  | Adaptability and Learning                                                                                                                                           |

|   | 2.10 | Summary 44                                                                                                                                                          |

| 3 | The  | Brainbox – Learning From Nature 45                                                                                                                                  |

|   | 3.1  | Computer Simulations                                                                                                                                                |

|   | 3.2  | Neural Network Simulation                                                                                                                                           |

|   | 3.3  | Expected Features                                                                                                                                                   |

|   |      | 3.3.1 Biological Realism                                                                                                                                            |

|   |      | 3.3.2 Scale of Simulation $\ldots \ldots 52$                                                  |

|   |      | 3.3.3 Simulation Time $\ldots \ldots 52$                                                             |

|   |      | $3.3.4  \text{Abstraction Level}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  53$                                                                              |

|   |      | 3.3.5 Interactive Control                                                                                                                                           |

|   | 3.4  | Software Neural Simulations                                                                                                                                         |

|   |      | 3.4.1 Example Software Simulations                                                                                                                                  |

|   |      | 3.4.2 Limitations of Software Simulation                                                                                                                            |

|   | 3.5  | Hardware Neural Simulations                                                                                                                                         |

|   |      | 3.5.1 Remaining Challenges                                                                                                                                          |

|   | 3.6  | Summary 58                                                                                                                                                          |

| 4 | The  | SpiNNaker Computing System 60                                                                                                                                       |

|   | 4.1  | Introduction                                                                                                                                                        |

|   | 4.2  | SpiNNaker Objectives 60                                                                                                                                             |

|   | 4.3  | Architectural Overview                                                                                                                                              |

|   |      | 4.3.1 SpiNNaker Processing Node                                                                                                                                     |

|   |      | 4.3.2 SpiNNaker CMP                                                                                                                                                 |

|   |      | 4.3.3 Inter-Neuron Communication                                                                                                                                    |

|   |      | 4.3.4 System-level Behaviour $\ldots \ldots \ldots$ |

|   | 4.4  | Main Features                                                                                                                                                       |

|   | 4.5  | The SpiNNaker Application Model                                                                                                                                     |

|   | 4.6  | Hardware Support                                                                                                                                                    |

|   | 4.7  | Development constraints                                                                                                                                             |

|   | 4.8  | User Expectations                                                                                                                                                   |

|   | 4.9  | Summary                                                                                                                                                             |

|   |      |                                                                                                                                                                     |

| <b>5</b> | Syst | cem-Level Simulation 8                                                                                                                              | 85         |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|          | 5.1  | Introduction                                                                                                                                        | 85         |

|          | 5.2  | Simulating a Complete Computing System                                                                                                              | 86         |

|          |      | 5.2.1 Related Work $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                   | 87         |

|          |      | 5.2.2 SpiNNaker Complete System Model                                                                                                               | 88         |

|          | 5.3  | System-level Simulation Options                                                                                                                     | 89         |

|          | 5.4  | SystemC Transaction-Level Modelling                                                                                                                 | 90         |

|          | 5.5  | Advantages of SystemC TLM                                                                                                                           | 90         |

|          |      | 5.5.1 Levels of Abstraction $\ldots \ldots $                                  | 91         |

|          |      | 5.5.2 Early Software Development                                                                                                                    | 92         |

|          |      | 5.5.3 Architecture Analysis                                                                                                                         | 92         |

|          |      | 5.5.4 Functional Verification                                                                                                                       | 92         |

|          |      | 5.5.5 Open Source Industry Standard                                                                                                                 | 93         |

|          |      | 5.5.6 Real-time Debug Support                                                                                                                       | 93         |

|          | 5.6  | SpiNNaker System-Level Simulation                                                                                                                   | 93         |

|          |      | 5.6.1 SpiNNaker UTF-PV Model                                                                                                                        | 94         |

|          |      | 5.6.2 SpiNNaker UTF-AV Model                                                                                                                        | 95         |

|          |      | 5.6.3 SpiNNaker TF-AV(CX) Model                                                                                                                     | 96         |

|          |      | 5.6.4 SpiNNaker TF-AV(CA) Model                                                                                                                     | 98         |

|          | 5.7  | Functional Validation                                                                                                                               | 99         |

|          |      | 5.7.1 Case Study I $\ldots \ldots $ | 00         |

|          | 5.8  | Case Study II                                                                                                                                       | 04         |

|          |      | 5.8.1 Case Study III $\ldots \ldots $      | 07         |

|          | 5.9  | Hardware Functional Verification                                                                                                                    | 09         |

|          | 5.10 | Summary                                                                                                                                             | 10         |

| 6        | Mul  | ti-CMP Systems Configuration 11                                                                                                                     | 11         |

| U        | 6.1  |                                                                                                                                                     | 11         |

|          | 6.2  |                                                                                                                                                     | 12         |

|          | 6.3  |                                                                                                                                                     | 16         |

|          | 0.0  |                                                                                                                                                     | $16 \\ 16$ |

|          |      |                                                                                                                                                     | $10 \\ 19$ |

|          | 6.4  |                                                                                                                                                     | 22         |

|          | 6.5  | -                                                                                                                                                   | 23         |

|          | 6.6  |                                                                                                                                                     | 25         |

|          | 0.0  | ~                                                                                                                                                   | -0         |

| <b>7</b> | $\mathbf{Spi}$ | NNake   | er Configuration Process               | 127   |

|----------|----------------|---------|----------------------------------------|-------|

|          | 7.1            | Introd  | luction                                | . 127 |

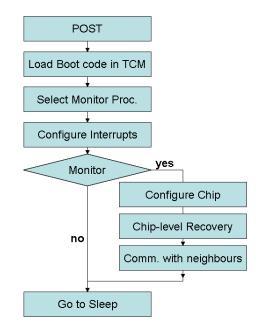

|          | 7.2            | SpiNN   | Naker Boot-up Process                  | . 129 |

|          | 7.3            | The A   | Application Loading Process            | . 135 |

|          | 7.4            | Config  | guration Issues                        | . 138 |

|          | 7.5            | Evalua  | ation Work                             | . 142 |

|          |                | 7.5.1   | CMP Boot-up                            | . 142 |

|          |                | 7.5.2   | Application Loading                    | . 143 |

|          |                | 7.5.3   | Impact of Ethernet Connections         | . 147 |

|          | 7.6            | Summ    | nary                                   | . 148 |

| 8        | Fau            | lt-Tole | erance                                 | 149   |

|          | 8.1            | Introd  | luction                                | . 149 |

|          | 8.2            | Fault-  | tolerance In Computing Systems         | . 150 |

|          | 8.3            | SpiNN   | Naker Fault-tolerance Support          | . 152 |

|          | 8.4            | Fault-  | Tolerance in the Configuration Process | . 156 |

|          |                | 8.4.1   | Monitor Processor Selection            | . 156 |

|          |                | 8.4.2   | Boot ROM Failure                       | . 156 |

|          |                | 8.4.3   | Chip-level Recovery                    | . 157 |

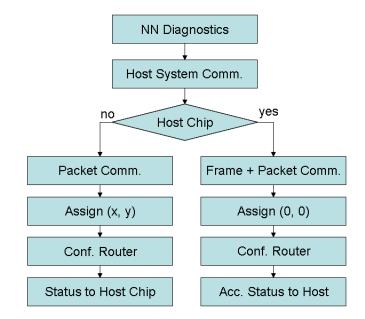

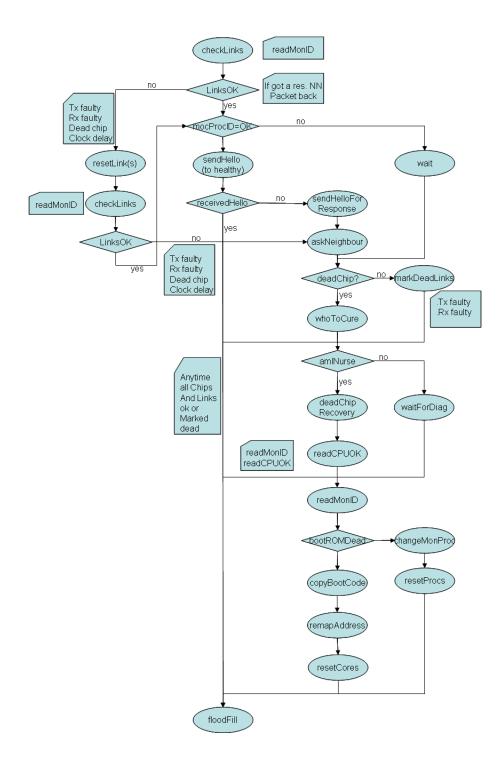

|          |                | 8.4.4   | NN Diagnostics and Recovery            | . 158 |

|          |                | 8.4.5   | Connection to the Host PC              | . 162 |

|          | 8.5            | Fault-  | Tolerance in Application Loading       | . 162 |

|          | 8.6            | Evalua  | ation Work                             | . 163 |

|          |                | 8.6.1   | Chip-level Recovery                    | . 163 |

|          |                | 8.6.2   | NN Diagnostics and Recovery            | . 164 |

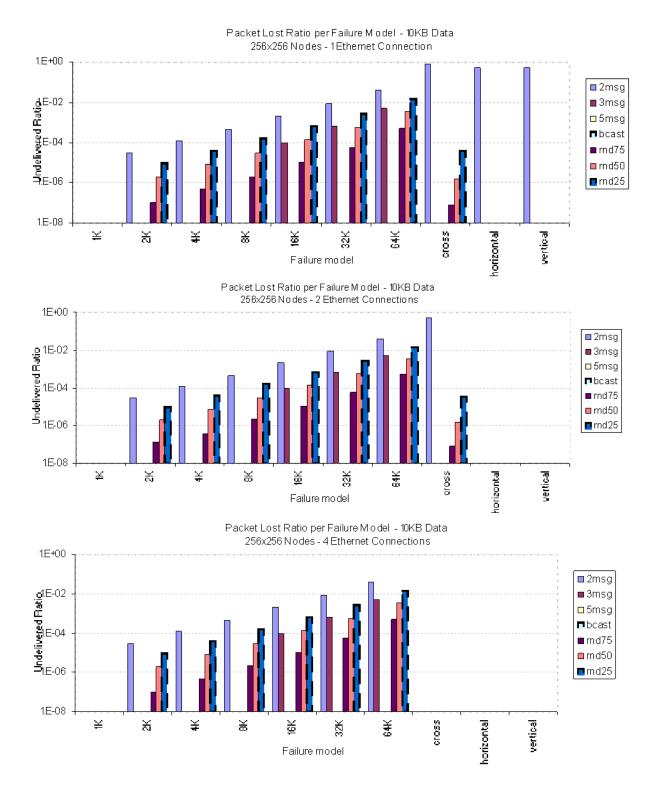

|          |                | 8.6.3   | Application Loading                    | . 166 |

|          | 8.7            | Summ    | nary                                   | . 168 |

| 9        | Spi            | NNake   | er Hardware Abstraction Layer          | 169   |

|          | 9.1            | Introd  | luction                                | . 169 |

|          | 9.2            | Hardw   | vare Abstraction Layer                 | . 170 |

|          | 9.3            | Abstra  | acting SpiNNaker                       | . 172 |

|          |                | 9.3.1   | Boot-up Instructions                   | . 172 |

|          |                | 9.3.2   | Neural Support Functions               | . 173 |

|          |                | 9.3.3   | Interrupt Service Routines             | . 173 |

|          |                | 9.3.4   | Optimal and Safe Device Interface      | . 174 |

|              |                | 9.3.5   | Device Exception Handling                                                                        | 175 |

|--------------|----------------|---------|--------------------------------------------------------------------------------------------------|-----|

|              |                | 9.3.6   | Fault-Recovery Procedures                                                                        | 175 |

|              |                | 9.3.7   | Shared Memory Message-passing                                                                    | 175 |

|              |                | 9.3.8   | SpiNNaker-Host Communication $\ldots \ldots \ldots \ldots \ldots$                                | 179 |

|              | 9.4            | Host F  | PC User Interface                                                                                | 180 |

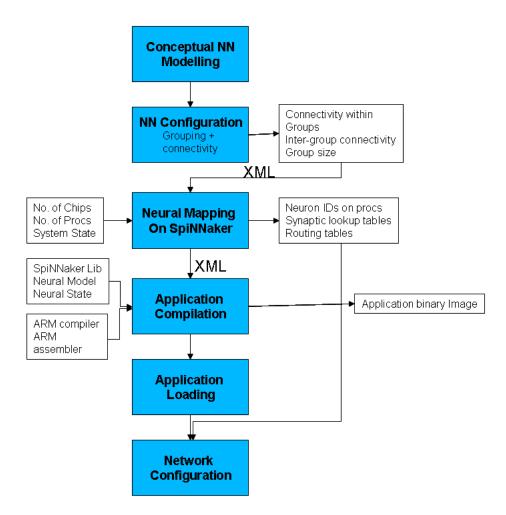

|              | 9.5            | Applic  | ation Development Process                                                                        | 182 |

|              | 9.6            | Summ    | ary                                                                                              | 182 |

| 10           | Con            | clusior | 18                                                                                               | 184 |

|              | 10.1           | Dissert | tation Summary                                                                                   | 184 |

|              | 10.2           | Resear  | ch Analysis                                                                                      | 186 |

|              |                | 10.2.1  | Response to Research Objectives                                                                  | 186 |

|              |                | 10.2.2  | Strengths of the Configuration Process                                                           | 188 |

|              |                | 10.2.3  | Limitations                                                                                      | 191 |

|              | 10.3           | Sugges  | sted Future Directions                                                                           | 192 |

|              | 10.4           | Resear  | ch Implications                                                                                  | 193 |

| Bi           | bliog          | raphy   |                                                                                                  | 194 |

| $\mathbf{A}$ | $\mathbf{Spi}$ | Nake    | r Inter-CMP NN Communication Protocol                                                            | 204 |

|              | A.1            | Introd  | uction                                                                                           | 204 |

|              | A.2            | System  | n-level Configuration Process                                                                    | 205 |

|              | A.3            | NN Di   | agnostic Process                                                                                 | 205 |

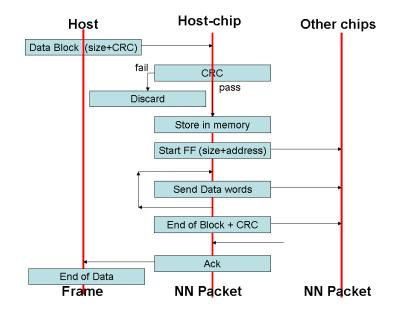

|              | A.4            | Applic  | ation Loading Flood-fill Process                                                                 | 207 |

| в            | Spil           | Nake    | r-Host PC Communication Protocol                                                                 | 208 |

|              | B.1            | Introd  | uction $\ldots$ | 208 |

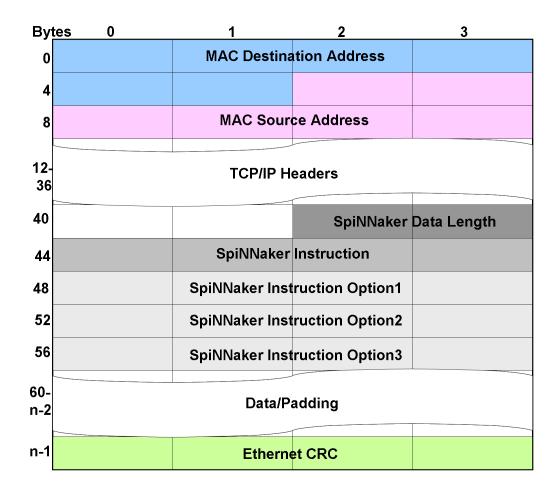

|              | B.2            | Ethern  | et Frame Instructions                                                                            | 210 |

|              | B.3            | P2P C   | Communication Instructions                                                                       | 212 |

## List of Tables

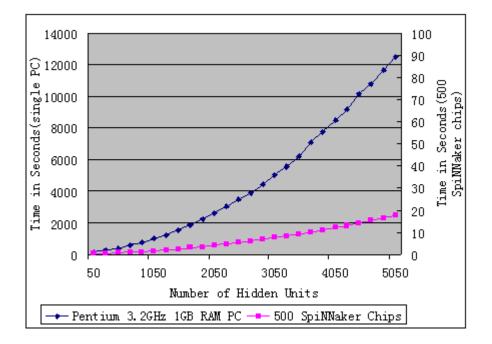

| 5.1 | Performance of PDP on PC vs. on SpiNNaker [KJFP07] 107                        |

|-----|-------------------------------------------------------------------------------|

|     | Configuration Issues Handling Approaches.138CMP-level Boot-up Process Time143 |

| 8.1 | NN Diagnostic and Recovery Process-Time Taken                                 |

| A.1 | System-level Configuration Instructions                                       |

| A.2 | NN Diagnostic and Recovery Instructions                                       |

| A.3 | Application Loading Floodfill Instructions                                    |

| B.1 | Host-System Communication Instructions                                        |

| B.2 | Inter-CMP P2P Communication Instructions                                      |

# List of Figures

| 2.1  | Neural Structure (from [Izh07], fig 1.1 page 2)                                    | 26      |

|------|------------------------------------------------------------------------------------|---------|

| 2.2  | A Typical Neuron (from [Wik09a])                                                   | 27      |

| 2.3  | Ionic Channels in Neural Membrane (from [DA01], fig. 5.8 page                      |         |

|      | $169)).  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 28      |

| 2.4  | Inter-neuron Synapse (from [DA01], fig 1.2 page 6)                                 | 29      |

| 2.5  | Ionic Channel Interplay to Develop Membrane Potential (from [Wik09                 | d]). 31 |

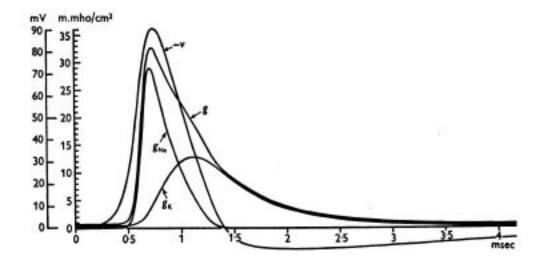

| 2.6  | Membrane equivalent conductance $(g)$ and voltage $(v)$ as a result                |         |

|      | of interplay between $Na^+$ conductance $(g_{Na})$ and $K^+$ conductance           |         |

|      | $(g_K)$ as measured by Hodgkin and Huxley [HH52] (they used a                      |         |

|      | resting potential of 0 mV instead of -65 mV for computational                      |         |

|      | simplicity).                                                                       | 33      |

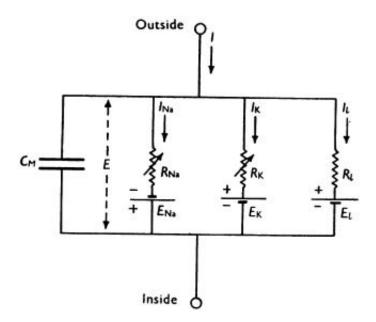

| 2.7  | Equivalent Electric Circuit for Ionic Channels used by Hodgkin                     |         |

|      | and Huxley (from Hodgkin and Huxley [HH52])                                        | 38      |

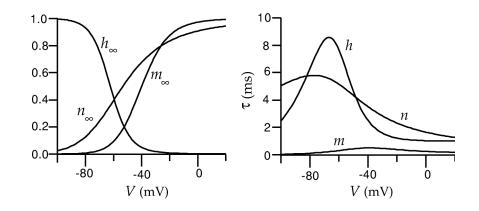

| 2.8  | Empirical Variables used by Hodgkin and Huxley (from Hodgkin                       |         |

|      | and Huxley $[HH52]$ ).                                                             | 39      |

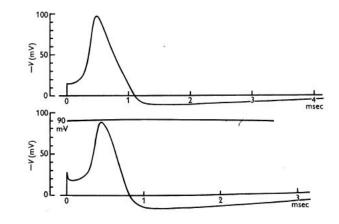

| 2.9  | Threshold potential as noted by Hodgkin and Huxley [HH52] at $18^{\circ}$          |         |

|      | C (bottom graph) and $20^{\circ}$ C (upper graph) (they used a resting             |         |

|      | potential of 0mV instead of -65mV for computational simplicity).                   | 40      |

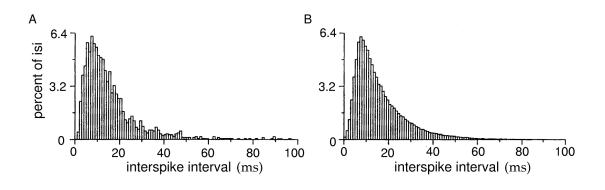

| 2.10 | Inter-spike Interval (isi) (from [DA01], fig 1.15 page 33).                        | 41      |

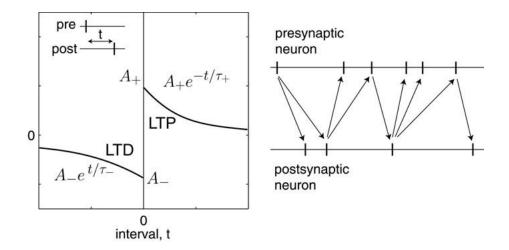

| 2.11 | Spike Timing Dependent Plasticity (STDP) (from [EMIE04], fig. 3).                  | 42      |

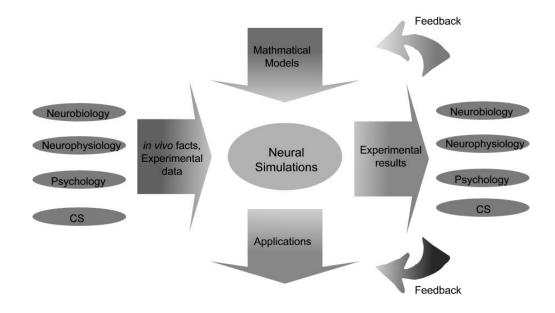

| 3.1  | Multi-disciplinary Interest in Neural Simulation (adapted from [Tra02]             |         |

|      | fig 1.2 page 6.)                                                                   | 47      |

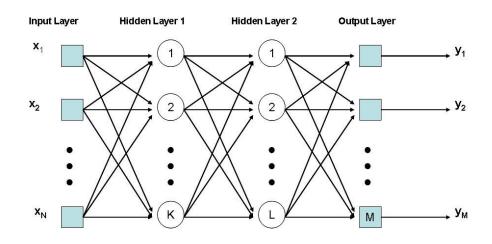

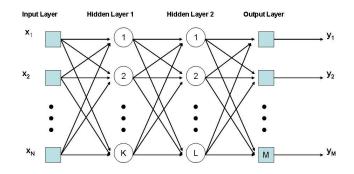

| 3.2  | Traditional Multilayer Neural Network.                                             | 49      |

|      |                                                                                    |         |

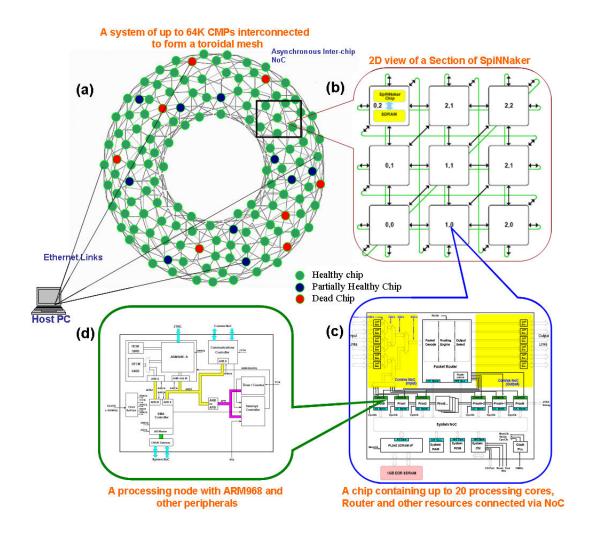

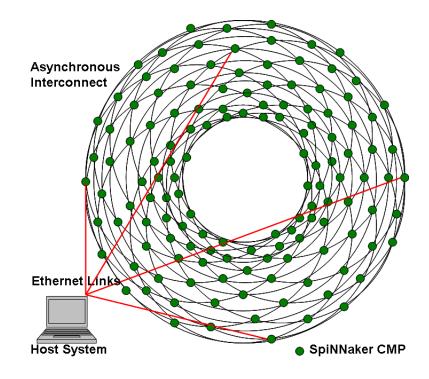

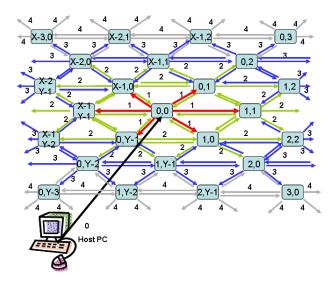

| 4.1  | SpiNNaker Computing System [Pro07]                                                 | 62      |

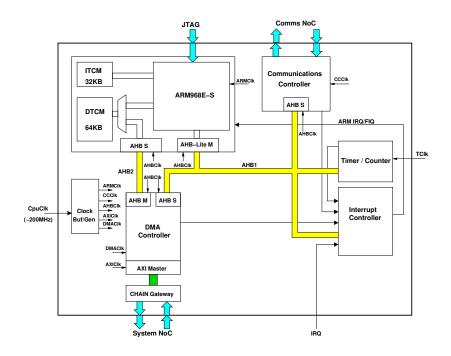

| 4.2  | SpiNNaker Processing Node [Pro07]                                                  | 64      |

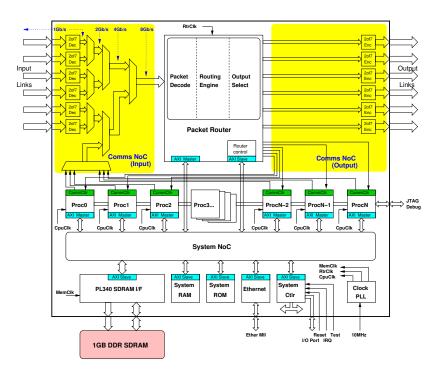

| 4.3  | SpiNNaker CMP [Pro07]                                                              | 66      |

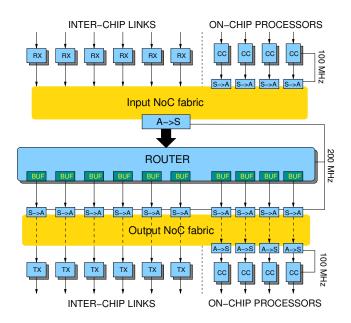

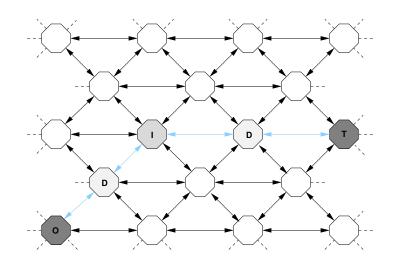

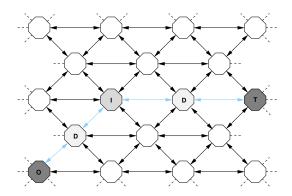

| 4.4        | Spike Communication Network [PBF <sup>+</sup> 08]                  | 67  |

|------------|--------------------------------------------------------------------|-----|

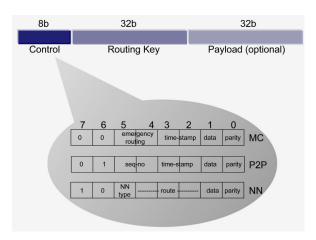

| 4.5        | Packet Format [Pro07]                                              | 68  |

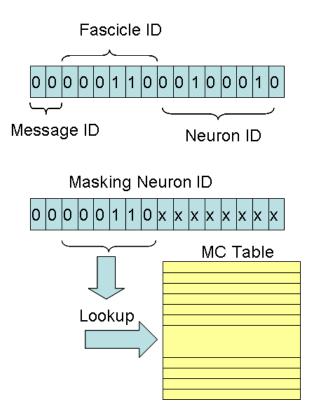

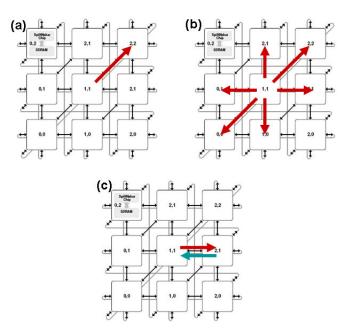

| 4.6        | Multicast Routing – Default Routing                                | 69  |

| 4.7        | Multicast Routing – Masking the Bits                               | 69  |

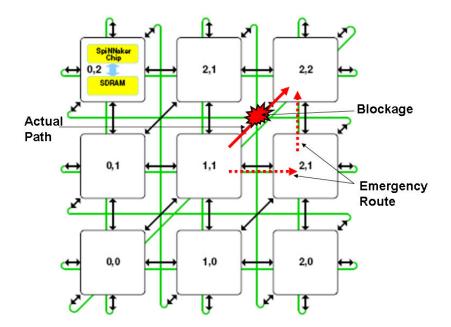

| 4.8        | Multicast Routing – Emergency Routing                              | 70  |

| 4.9        | NN Packet Routing (a) To a particular neighbour (b) Broadcast      |     |

|            | to all six neighbours (c) Peak and poke                            | 71  |

| 4.10       | SpiNNaker System - a conceptual view                               | 72  |

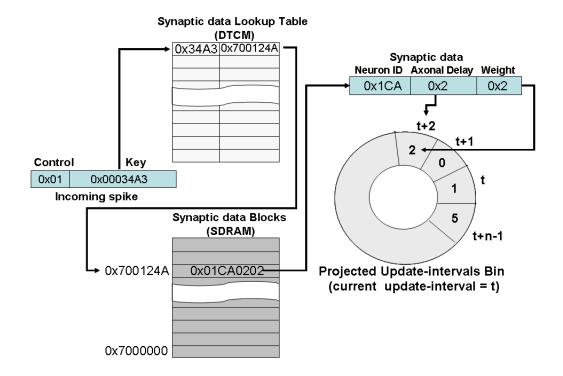

| 4.11       | SpiNNaker Standard Application Model - Stimulus Update Process     |     |

|            | on Receipt of a Spike                                              | 77  |

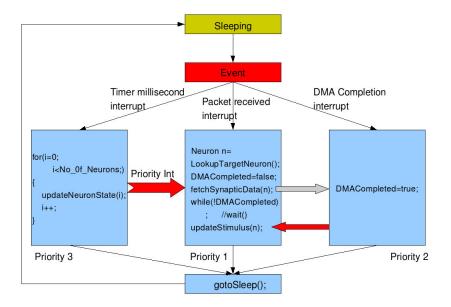

| 4.12       | SpiNNaker Evnet-driven Application Model with the Help of ISRs.    | 79  |

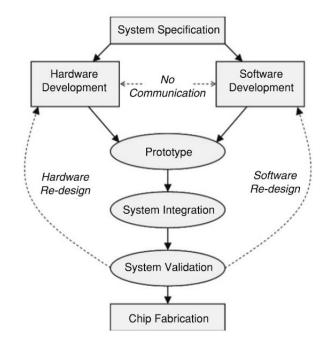

| 5.1        | Classic Hardware Design Flow [Ghe05]                               | 89  |

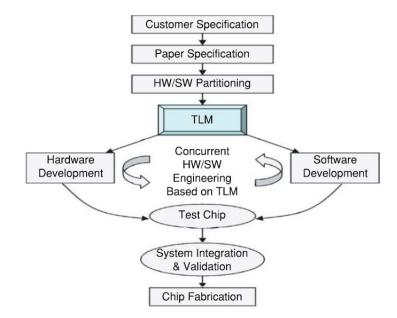

| 5.2        | TLM Design Flow [Ghe05]                                            | 91  |

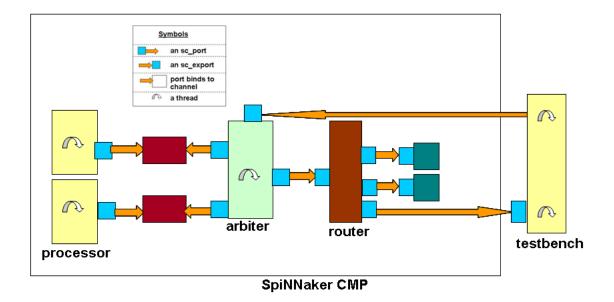

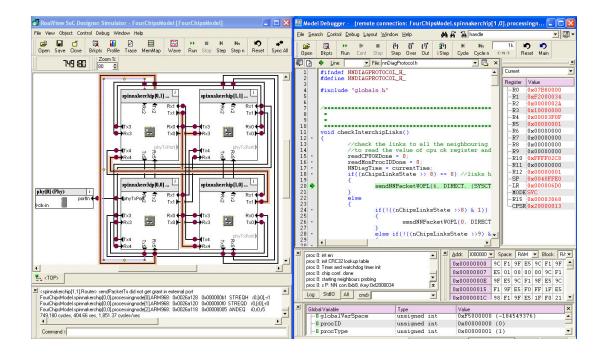

| 5.3        | SpiNNaker CMP Model - UTF-PV                                       | 94  |

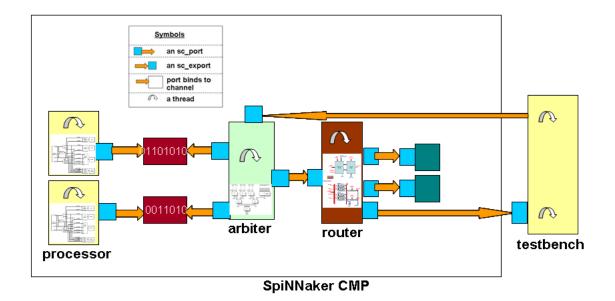

| 5.4        | SpiNNaker CMP Model with Component-level Architectural De-         |     |

|            | tails - UTF-AV.                                                    | 95  |

| 5.5        | SpiNNaker System-level Model (TF-AV(CA)) with Real-time Code       |     |

|            | and System Debugging                                               | 98  |

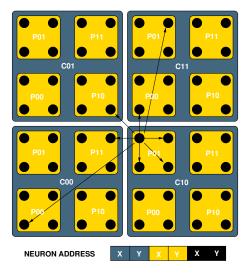

| 5.6        |                                                                    | 100 |

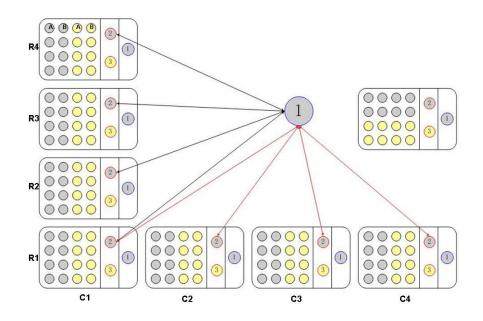

| 5.7        | Neuron mapping to the processors in a 4-CMP (C00-C11) SpiN-        |     |

|            | Naker system, each CMP containing 4-application (fascicle) pro-    |     |

|            | cessors (P00-P11). A 32-bit neuron's address (shown in the bot-    |     |

|            | tom) is formed by placing the CMP ID ( $X=0$ , $Y=0$ for chip C00) |     |

|            | in the 16 most significant bits, processor ID (X=0, Y=0 for pro-   |     |

|            | cessor P00) in the next 6 bits, while the neuron ID $(X=n, Y=m)$   | 101 |

| <b>F</b> 0 |                                                                    | 101 |

| 5.8        |                                                                    | 102 |

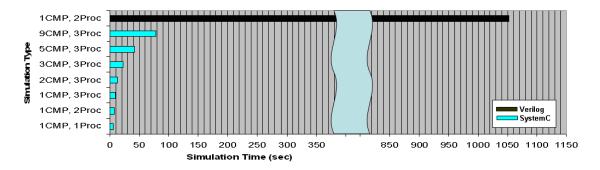

| 5.9        |                                                                    | 104 |

|            |                                                                    | 105 |

|            | Simulation of the PDP Model on the SpiNNaker System [KLP+08].      |     |

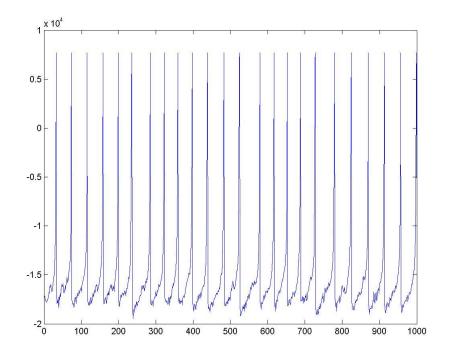

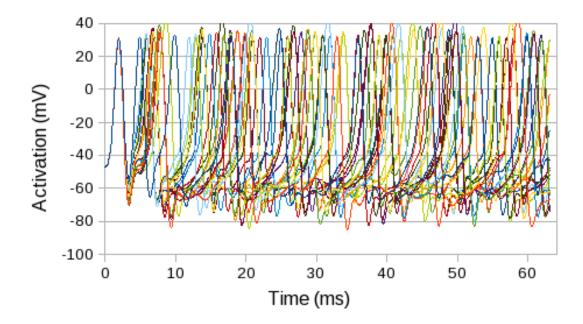

|            | Spike Train from Izhikevich Neurons [JFW08]                        | 108 |

| 0.10       |                                                                    | 108 |

|            |                                                                    | 100 |

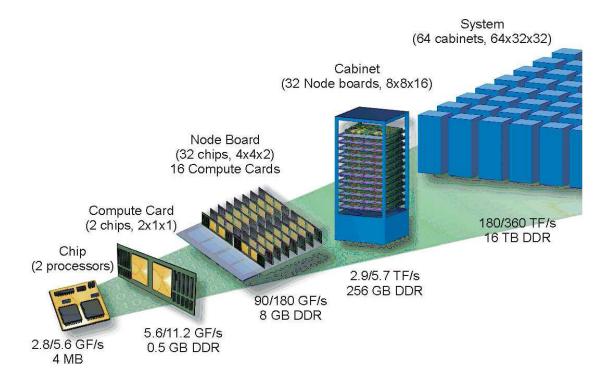

| 6.1        | Blue Gene/L - System Overview [ea03]                               | 116 |

|            |                                                                    |     |

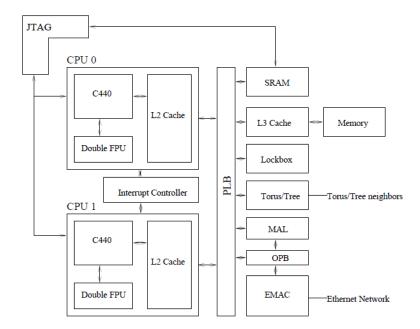

| 6.2  | Blue Gene/L - Compute Node's Block Diagram [ea03]                                       | 117 |

|------|-----------------------------------------------------------------------------------------|-----|

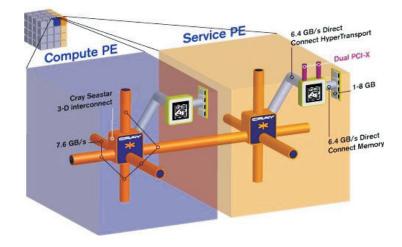

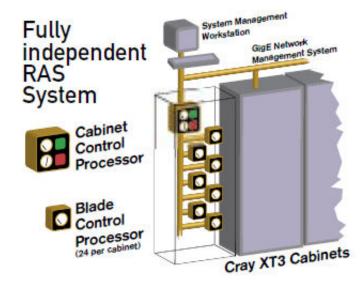

| 6.3  | Cray XT3 Massively Parallel Computing System [ea08]                                     | 120 |

| 6.4  | Cray XT3 - System Overview [Inc05b]                                                     | 120 |

| 7.1  | The SpiNNaker Boot-up Process - Phase I                                                 | 130 |

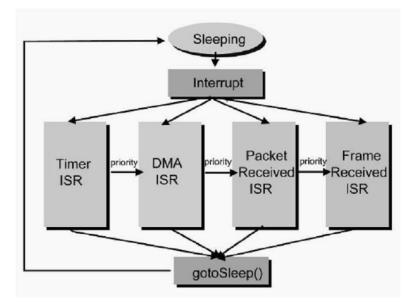

| 7.2  | Event-Driven System-level Configuration                                                 | 133 |

| 7.3  | The SpiNNaker Boot-up Process - Phase II                                                | 134 |

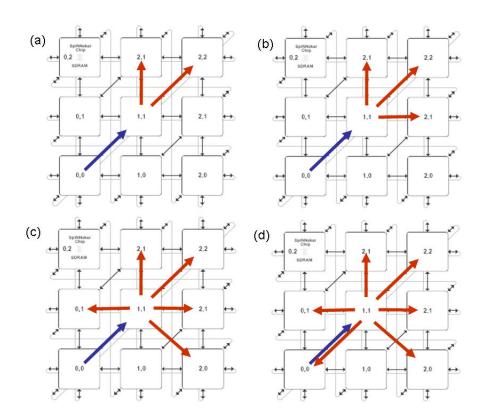

| 7.4  | Selective Forward Flood-fill                                                            | 136 |

| 7.5  | Flood-fill Process - Sequence Diagram.                                                  | 137 |

| 7.6  | Application Loading Process - Flood-fill Approaches [KNJ+08b,                           |     |

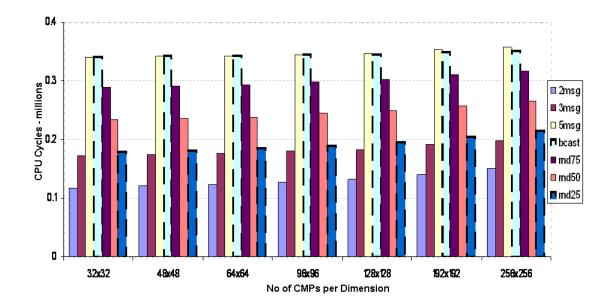

|      | $KNJ^+08a, KNR^+09]$ .                                                                  | 144 |

| 7.7  | Application Loading Process - Impact of System Size (10-Kbyte                           |     |

|      | Date with 1 Ethernet Connection to the Host PC) [KNJ $^+08b$ ,                          |     |

|      | $KNJ^+08a, KNR^+09]$ .                                                                  | 145 |

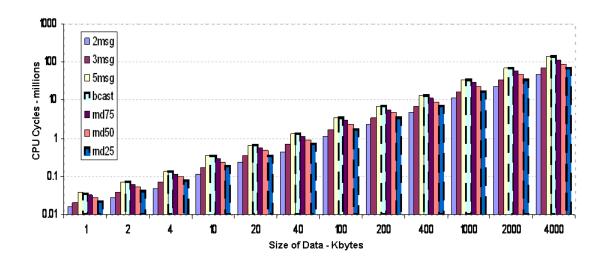

| 7.8  | Application Loading Process - Impact of Data Size (32x32 Nodes                          |     |

|      | System with 1 Ethernet Connection to the Host PC) [KNJ $^+08b$ ,                        |     |

|      | $KNJ^+08a, KNR^+09]$ .                                                                  | 146 |

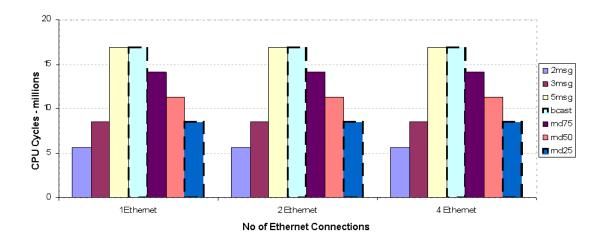

| 7.9  | Application Loading Process - Impact of Ethernet Connections                            |     |

|      | (10-K<br>byte Date on a 256x256 Node System) [KNJ+08b, KNJ+08a,                         |     |

|      | $KNR^+09$ ]                                                                             | 147 |

| 8.1  | NN Diagnostic and Recovery Process.                                                     | 159 |

| 8.2  | Fault-tolerance in Application Loading Process with Varying Num-                        |     |

|      | bers of Ethernet Connections [KNR <sup>+</sup> 09] $\ldots \ldots \ldots \ldots \ldots$ | 167 |

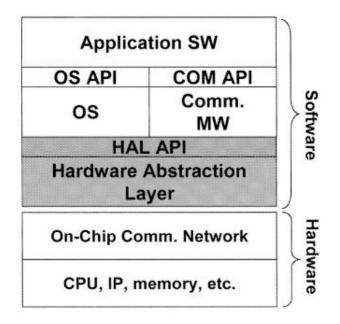

| 9.1  | Hardware Abstraction Layer [SY03].                                                      | 170 |

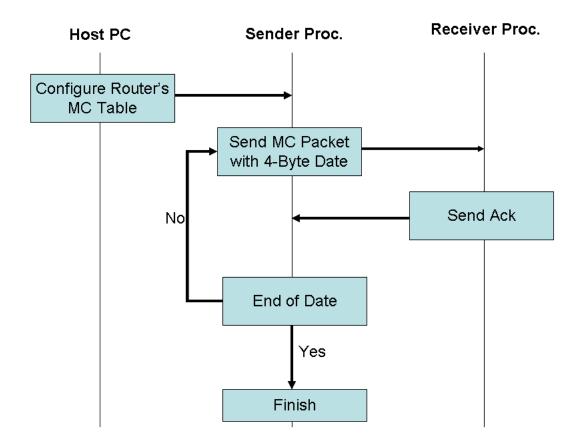

| 9.2  |                                                                                         |     |

|      | Passing using MC packets.                                                               | 176 |

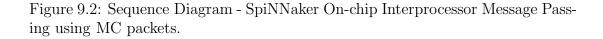

| 9.3  | Interprocessor Message Passing in a SpiNNaker CMP using Shared                          |     |

|      | Memory, (a) Send side, (b) Receive side.                                                | 177 |

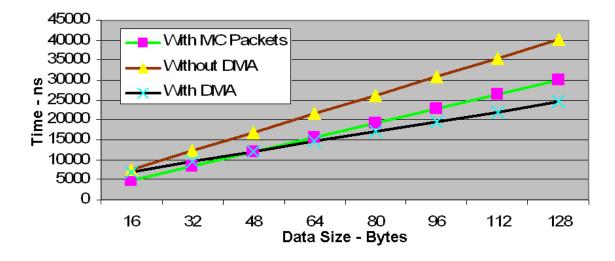

| 9.4  | Analysis of Interprocessor Message Passing Techniques. [SY03]                           | 178 |

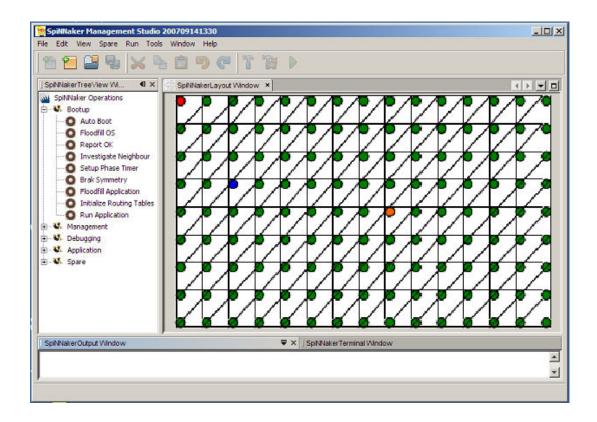

| 9.5  | Host PC Graphical User Interface                                                        | 180 |

| 9.6  | SpiNNaker Application Development Process                                               | 181 |

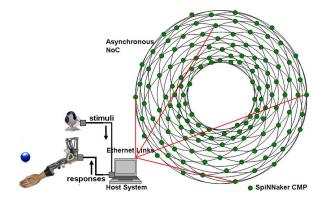

| 10.1 | Example Real-time Interactive Neural Application on SpiNNaker                           |     |

|      | Controlling a Robotic Arm.                                                              | 193 |

| B.1 | The Ethernet | Frame | Format | used for | : SpiNNaker-Host | Communi- |     |

|-----|--------------|-------|--------|----------|------------------|----------|-----|

|     | cation       |       |        |          |                  |          | 209 |

### Abstract

Configuring a million-core parallel system at boot time is a difficult process when the system has neither specialised boot-up hardware support nor a preconfigured default state that puts it in operating condition. The SpiNNaker massivelyparallel computing system has been designed to support large-scale simulations of biologically-inspired neural networks in real-time. The system building block is a Chip Multiprocessor (CMP) using low-power embedded processors, with an asynchronous network-on-chip to support high-performance, scalable, and faulttolerant parallel distributed processing. Where most large CMP systems feature a sideband network to complete the boot process, SpiNNaker has a single homogeneous network interconnect for both application inter-processor communication and system control functions such as boot load and run-time user-system interaction. This network improves fault tolerance and makes it easier to support dynamic run-time reconfiguration. However, it requires a boot process that is transaction-level compatible with the application's communications model.

Since SpiNNaker uses event-driven asynchronous communication throughout, the loader operates with purely local control: there is no global synchronisation, state information, or transition sequence. A novel two-stage unfolding boot-up process efficiently configures a multi-CMP SpiNNaker into an integrated computing system and loads the application using a high-speed flood-fill technique with support for run-time reconfiguration. SystemC simulation of a multi-CMP SpiNNaker system indicates an error-free CMP configuration time of  $\approx 1.3$  ms, while a high-level simulation of a full-scale system (with 64,000 CMPs) indicates a mean application-loading time of  $\approx 20$  ms for a 100-Kbyte application that is virtually independent of the size of the system.

The configuration process also supports application development through a hardware abstraction layer (HAL) that provides architectural visibility appropriate to the developer's purpose.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the "Copyright") and s/he has given The University of Manchester the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

- ii Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the John Rylands University Library of Manchester. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

- iii The ownership of any patents, designs, trade marks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

- iv Further information on the conditions under which disclosure, publication and exploitation of this thesis, the Copyright and any Intellectual Property Rights and/or Reproductions described in it may take place is available from the Head of School of School of Computer Science (or the Vice-President).

### Acknowledgements

I would like to thank my colleagues in the APT group, especially from the SpiN-Naker project, for providing a wonderful company without which IT302 would have been a boring place. I want to thank them all for their support that saved me a lot of effort and time. My special thanks to Viv Woods for refining my writings which let me concentrate on my work. Luis has always been available for help when ever required. The list of my publication would have not been that long if Alex was not on our side, and my implementation would have been behind schedule if Xin Jin was not there to help me. Steve Temple, Jim Garside and Mikel have been very patient in helping me refine my protocols and their verification. Eustice, Jian, Shufan, Yebin, Dom, Cameron, Frencesco, and Zenyu have been a great help on many occasions in enabling me to understand part of my work related to their research areas. Javier's helpful and timely response from Spain made a long-distance collaboration possible during my research. I wish to thank them all for their time and help. I also want to thank our partners in the University of Southampton for their hospitality and nice company during this project.

My special thanks to Steve Furber for being so helpful to me. He has always been an inspiration for me during this research, and I look forward to having a continued research collaboration with him during my academic career.

I dedicate my thesis to my wife Sabeen and children Muazam, Maham and Mahad, who deserved much more time and attention than I could manage to give them during my PhD.

My thanks to E. Izhikevich and P. Dayan for permitting me to use diagrams from their publications. Last but not the least, I am grateful to NUST Pakistan, HEC Pakistan, and EPSRC UK who supported me in paying my utility bills.

# Chapter 1

### Introduction

"As our understanding grows about how the brain perceives, thinks and remembers, so does our ability to devise machine intelligence ...... When it was realized that the brain is not a serial processor of information but rather an extraordinarily complex parallel system, the field of computer science turned to a new kind of computer - massively parallel processors - .... The long-term possibilities have the flavour of science fiction and raise the most basic questions of philosophy and ethics. Can we someday create machine minds as capable as, or even more capable than, the human mind in all its ramifications, including the ability to create and evaluate new concepts? ... Can we someday develop instrumentation to "read" the mind? Can thoughts and knowledge someday be implanted in the mind or transferred from one mind to another? Can our intellectual capabilities someday be substantially enhanced by "symbiosis" with machine intelligence? ..... The pace of developments in neuroscience and in computer science is so rapid and accelerating that many of these science-fiction-like possibilities may become realities in your lifetime." Richard F. Thompson [Tho00]

### 1.1 Background

By most qualified definitions, a computer is taken to be "a machine that manipulates data according to a list of instructions" [Wik09b]. In more general terms, "a computer is an electronic machine that can receive, process and present information [based on a set of instructions]" [Wik09c]. Originally the term referred to a person who did mathematical calculations using a mechanical device [Wik09b]. From their inception, it was commonplace to compare computers with brains and to find similarities between the two. However, the two "devices" outweigh each other in their respective strengths: computers are fast, accurate and have a large capacity to store data, while brains are flexible, fault-tolerant and highly concurrent in their operations [FT07]. There have been many endeavours to design a computing device with a union of the two differing domains, though the two contribute to the same end. Over the last half a century or more of the evolution of programmable computers, we (computer scientists) have been trying to bridge this gap and are learning from neurobiology to build "brain like computers": computing devices characterised by their ability to adapt to the environment, having an interactive and error-prone behaviour, employing highly-parallel distributed processing, and still being fast and accurate. However, this requires a detailed understanding of the brain which we are still lacking.

The brain is probably the most complex structure in the universe and is the last mystery to be revealed by humans [Tra02]. Our brain consists of 10<sup>11</sup> neurons having more than  $10^{15}$  connections each of which can transmit an information signal a few times a second. Each neuron, with its connections, contributes to a very complex biological system which has not yet been fully understood. The least understood aspect is the emergent behaviour exhibited by a population of neurons (a neural network), which collectively display a holistic behaviour quite different from individual neurons. Many discoveries over the last few decades have improved our understanding of the nervous system. New techniques, such as Functional Magnetic Resonance Imaging (fMRI) etc, are adding considerably to this knowledge-base. Mathematical models based on these discoveries and computer simulations based on hypothesised mathematical models are helping us to understand phenomenological observations of neurons and their interactions. A few detailed mathematical models can simulate biological neurons realistically, however, they are too complex to simulate a large population of neurons on a general-purpose computer [FT07].

The SpiNNaker project at the University of Manchester aims to realise largescale neural simulations using biologically realistic mathematical models. Our aim is two-fold: firstly adopting known biological engineering principles from the brain to develop a fault-tolerant massively-parallel computing system using a low-power architecture. Secondly, using this large-scale neural network simulation engine in collaboration with multi-disciplinary researchers to discover more about the brain's functionality. It is intended to use the resulting discoveries to improve the hardware system, making it operate in a manner more akin to the human brain [FT07]. This iterative process to "explore and synthesize", in order to bridge the gap between the man-made and natural computing systems, should help us learn how to build a more flexible, interactive and robust computing device.

SpiNNaker is based upon an Application Specific Integrated Circuit (ASIC) design using state-of-the-art technologies such as the Chip Multiprocessor (CMP) and asynchronous inter-processor communication. To simulate a large-population of neurons, it uses an event-driven application model akin to real-time embedded applications. The architecture and application model are quite different from those used in conventional computing systems. For an application to make optimal use of the designed features, it is important to configure the SpiNNaker system properly and manage its resources at run-time to support real-time simulations of large-scale neural networks.

#### 1.2 Motivation

The main motivation for this research has spun out from the objectives of designing the SpiNNaker massively-parallel computing system, i.e. to support understanding the brain by providing a high-performance simulation engine to support large-scale neural modelling to the scale of a part of the nervous system. This requires researchers from multiple disciplines to use SpiNNaker for a variety of applications using various kinds of mathematical models (spiking neurons vs. multi-layer perceptrons, biologically realistic neurons vs. simple spiking neurons etc). It implies that developers would wish to develop their applications for SpiN-Naker without delving into its architectural complexities, or to port their existing applications to the SpiNNaker computing system without much difficulty. This requires configuration of the hardware for specific application requirements, providing support to the developers in the form of ready-made functions to hide the architectural details at higher levels of implementation, providing middlelayer support functions to help transform an application into the SpiNNakerapplication-model, and mapping the neural network to the available resources to make optimal use of them.

In this research we aim to provide application support for real-time large-scale neural simulations on the SpiNNaker multi-CMP system. We intend to provide a personal-computer (PC) like environment to application developers, application users and system administrators interacting with SpiNNaker. We want to motivate developers to develop or to port existing applications to SpiNNaker with minimal effort. We also wish to support an interactive system administration for resource management and run-time fault handling.

#### **1.3** Aim and Objectives

The aim of this research is to "devise a configuration process for a multi-CMP system to configure the system at run-time as required by the application, and then to load the tailored application at run-time using the SpiNNaker interchip communication interconnect". The research is directed toward achieving the following objectives:

- Performance: To make the system available to the application by efficiently testing and initializing the SpiNNaker-CMPs at configuration time, and interactively configuring the system, as a whole, at run-time as required by the application. This also implies that the system be configured to make optimal use of its resources, and support the application execution to make full use of its designed features.

- Scalability: SpiNNaker is a scalable computing system i.e. a system of almost any desired scale can be assembled by linking the SpiNNaker CMPs together. The configuration process should be independent of the scale of the system with regards to initialization and loading applications.

- Fault-tolerance: SpiNNaker has been designed as a reconfigurable and faulttolerant computing system. However, the system depends on the software to make full use of these features. The configuration process should use these features to support autonomous fault recovery at run-time. At the same time, the configuration process itself should be robust enough to be able to bring the system to an operational state despite some chip- or system-level malfunctions.

- Interactive Support: The process should provide run-time support to enable users to interact with the application and a visualization of the state of the application or the system at any point in time. This is important, for

example, to provide stimuli to the neural application at run time and to get responses as a result of these stimuli. It is also important for system diagnostic and debugging support.

#### **1.4** Contributions

The research has contributed in providing:

- A high-level instruction- and cycle-accurate simulation model of a multi-CMP system, developed much before the hardware design of the systems to support the conceptual validation of the application model, detailed design verification and architectural exploration, and application development for the SpiNNaker multi-CMP system (Chapter 5).

- A novel process to configure a multi-CMP system at run-time using a realtime event-driven application model, with characteristics of efficiency, scalability, and fault-tolerance (Chapter 7).

- A novel event-driven application loading process to load a tailored application efficiently, from outside the system, onto a multi-CMP system at run-time in a scalable way (Chapter 7).

- A novel real-time chip- and system-level fault-tolerance mechanism to improve system availability by timely fault-detection and run-time recovery to attempt to recover a faulty chip-component or a faulty chip (Chapter 8).

- A novel protocol to provide interactive communication between the user and the system/application by bridging between the Ethernet network, which connects the system with the user interface on a Host PC, and the SpiN-Naker packet-switching Communication Network, which interconnects the SpiNNaker CMPs (Chapeter 9).

- A Hardware Abstraction Layer (HAL) library of useful functions and device drivers to support application development for the SpiNNaker computing system without the need for a developer to have detailed knowledge of the underlying hardware architecture (Chapter 9).

#### 1.5 Thesis structure

The thesis comprises 10 chapters as follows:

- Chapter 2 is a review of the literature on neural computation which forms the main motivation for the SpiNNaker project to deliver a massivelyparallel multi-CMP neural network simulation engine to support large-scale simulation of biologically-realistic neural populations. This chapter explains the neural dynamics which result in information processing in a neuron, its communication to other neurons, and the resultant learned behaviour of the nervous system. It is important to understand these phenomena to understand potential applications for the SpiNNaker computing system. A reasonable explanation of neural structures and their functionality in generating an overall spatio-temporal neural information processing system would fill a complete book. However, we focus on only those concepts related to the understanding of the real-time application model for the SpiNNaker computing system.

- Chapter 3 focuses on the need to create computer simulations to explore neural information processing in neural populations (neural networks). A few software-based approaches to the simulation of large-scale neural networks are reviewed with their limitations necessitating purpose-built hardware engines for high performance. The chapter concludes with motivation for designing SpiNNaker as an Application Specific Integrated Circuit (ASIC) to support large-scale neural simulations.

- Chapter 4 highlights the objectives of the SpiNNaker computing system, its architecture, and certain important features from the programmer's point of view. The envisaged standard application model to support large-scale neural simulations with the SpiNNaker computing system is explained. Finally, a few important guidelines for software developers writing neural applications for SpiNNaker are given, along with some users' expectations acquired from our interaction with potential users.

- Chapter 5 covers our motivation for creating a system-level model for the SpiNNaker computing system. The available choices for simulating a Systemon-Chip (SoC) i.e. high-level simulation vs. typical Register-Transfer-Level (RTL) modelling are described. This chapter also gives an overview of the

SystemC Transaction Level Modelling (TLM) technique as a choice for highlevel simulation. Our experiences while creating a novel complete-system model for a multi-CMP system to an instruction- and cycle-accurate level are covered in this chapter. The chapter then presents some case studies performed to validate the accurate behaviour of the model at chip- and system-level, and a few experiments performed with the help of this simulation to verify the design objectives of the SpiNNaker computing system. The chapter also presents the test chip verification process with the help of the SystemC system-level and Verilog top-level behavioural models.

- Chapter 6 highlights some multi-CMP configuration challenges. Some work from the literature is presented to examine a few approaches to deal with these challenges. We describe some peculiarities of the SpiNNaker system, a truly multi-CMP system, to justify why the configuration processes used in the past are not suitable for SpiNNaker. We also identify the required features from the SpiNNaker configuration process.

- Chapter 7 explores the configuration challenges specific to the SpiNNaker architecture in the light of those already described in Chapter 6. The proposed configuration and application loading protocols for a multi-CMP system are presented in the context of the SpiNNaker system. Some experimental results are given to justify our claim that we meet our objectives.

- Chapter 8 introduces the fault-tolerance features of the SpiNNaker configuration process proposed in this thesis. Some fault-tolerance concepts are reviewed in the context of real-time computing systems and the hardware support in the SpiNNaker computing system to facilitate fault-resilience is explained. Finally, the chapter explains how the configuration process uses the SpiNNaker fault-tolerance features to make it a reliable computing system.

- Chapter 9 gives some details of the Hardware Abstraction Layer (HAL) developed to help the programmers by hiding the architectural details and to ease application development for the SpiNNaker computing system. The purpose is to make optimal use of the designed features in the SpiNNaker hardware, of which the programmer may not be aware. The chapter also describes a few features of a proposed user interface to interact with the

system.

• In the last chapter of this dissertation we conclude and summarise our research work. A few important aspects related to this research have been highlighted which could not be addressed due to paucity of time or being out of scope, and which provide a good starting point for future research.

### 1.6 Publications

The following publications include aspects of the work described in this dissertation:

- M.M. Khan, D.R. Lester, L.A. Plana, A. Rast, X. Jin, E. Painkras, and S.B. Furber. "SpiNNaker: Mapping Neural Networks onto a Massively-parallel Chip-multiprocessor". In Proc. Intl. Joint Conf. on Neural Networks (IJCNN2008), 2008 June 1-6 Hong Kong. (included in Chapters 4 & 5).

- M.M. Khan, J. Navaridas, X. Jin, L.A. Plana, J.V. Woods, and S.B. Furber. "Real-time Application Support for a Novel SoC Architecture". In Proc. 4th UK Embedded Forum, Southampton, UK, September 2008. (Chapters 4, 7 & 9).

- M. Khan, X. Jin, S. Furber, and L.A. Plana. "System-level Model for a GALS Massively Parallel Multiprocessor". In Proc. 19th UK Asynchronous Forum, page 19-22, September 2007. (Chapters 4 & 5).

- M.M. Khan, J. Navaridas, X. Jin, L.A. Plana, J.V. Woods, and S.B. Furber. "Configuring a GALS CMP System for Real-time Applications". In Proc. 20th UK Asynchronous Forum, September 2008. (Chapters 4 & 7).

- M.M. Khan, L.A. Plana, J.V Woods, and S.B. Furber. "System-level Model for SpiNNaker CMP System", 1st International Workshop on Rapid Simulation and Performance Evaluation: Methods and Tools (RAPIDO'09) held in conjunction with the 4th International Conference on High-Performance and Embedded Architectures and Compilers (HiPEAC2009) Paphos, Cyprus, January 25-28, 2009. (Chapters 4 & 5).

- M.M. Khan, J. Navaridas, A.D. Rast, X. Jin, L.A. Plana, M. Luján, J.V. Woods, J. Miguel-Alonso and S.B. Furber. "Event-Driven Configuration

of a Neural Network CMP System over a Homogeneous Interconnect Fabric", to appear in Proc. of Intl. Symposium on Parallel and Distributed Computing (ISPDC2009) 1-3 July 2009 Lisbon Portugal. (Chapters 4, 7 & 9).

- Luis A. Plana, Steve B. Furber, Steve Temple, Mukaram Khan, Yebin Shi, Jian Wu, and Shufan Yang. "A GALS Infrastructure for a Massively Parallel Multiprocessor". IEEE Design & Test of Computers, 24(5):454463, Sept-Oct. 2007. (Contributions in the validation process using the systemlevel model; Chapter 5).

- Alexander Rast, Xin Jin, Mukaram Khan, Steve Furber, "The Deferred Event Model for Hardware Oriented Spiking Neural Networks", 15th Intl. Conf. on Neural Information Processing (ICONIP2008), 2008 Nov. 25-28, Auckland, New Zealand. (Contributions in defining the SpiNNaker architecture specific to the spike communication infrastructure and deriving the results with the help of the system-level model (Chapters 4 & 5)).

- A.D. Rast, S. Yang, M. Khan, and S.B. Furber. "Virtual Synaptic Interconnect using an Asynchronous Network-on-Chip". In Proc. Intl. Joint Conf. on Neural Networks (IJCNN2008), 2008 June 1-6 Hong Kong. (Contributions in defining the SpiNNaker architecture and hardware abstraction layer functions at application level to make use of DMA operations (Chapter 4 & Chapter 7)).

- A.D. Rast, M.M. Khan, X. Jin, L.A. Plana and S.B. Furber, "A Universal Abstract-Time Platform for Real-Time Neural Networks" to appear in proc. of Intl. Joint Conf. on Neural Networks (IJCNN2009), 2009 June 14-19 Atlanta Georgia (USA). (Contributed in defining the SpiNNaker architecture specific to the axonal conductance delays in the spike communication infrastructure, setting up experiments with large population of neurons, and deriving the results with the help of a multi-CMP system-level model (Chapter 4 & 5)).

- A. Rast, S. Furber, D. Lester, S. Temple, L. Plana, E. Painkras, M. Khan, J. Wu, Y. Shi, S. Yang and X. Jin, "Abstracting both Architecture and Time: The SpiNNaker Neuromimetic Modelling Platform", ESSDERC2008, 15-19 Sep, Edinburgh.

### Chapter 2

# The Brain – Nature's Masterpiece

"The human brain is by far the most complex structure in the known universe. The extraordinary properties of this three or so pounds of soft tissue have made it possible for Homosapiens to dominate the earth, change the course of evolution through genetic engineering, walk on the moon, and create art and music of surpassing beauty. We do not yet know the limits of the human mind and what it can accomplish" Richard F. Thompson [Tho00]

### 2.1 Introduction

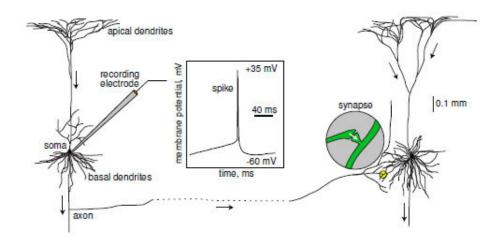

SpiNNaker's target application is the simulation of biologically-realistic neural networks. Neural networks are characterised by parallel distributed processing employing a massive number of small independently functional processing units (neurons) with a tremendous amount of connectivity. Several key properties of "real" neural networks drive the design of SpiNNaker's application-specific architecture. It is, therefore, important to understand a neuron's functional behaviour in order to comprehend the intended applications for the SpiNNaker massively-parallel computing system. Neurons communicate through spikes: short-duration impulses [DA01] (Figure 2.1<sup>1</sup>). It is usual to abstract the spike to an instantaneous pulse, or event, triggered when the neuron reaches a certain threshold value [Me98]. The neuron's spike is characterised by a temporal delay on a millisecond scale during its development and firing due to its biochemical properties.

<sup>&</sup>lt;sup>1</sup>The diagrams from publications are included with the authors' permission.

Figure 2.1: Neural Structure (from [Izh07], fig 1.1 page 2).

The spiking behaviour of neurons with the associated temporal characteristics is called the neural dynamics of the nervous system and controls its functional behaviour including stimulus-response and learning.

This chapter will first explore briefly some neural structures to make the later discussion accessible to readers who may have a limited knowledge of the nervous system. This is important to introduce these concepts from a neural computation point of view as these will be referred a number of times in the later chapters. The chapter then focuses on a few neural dynamics phenomena which contribute together to the information processing mechanism in neurons and then to a collective intelligent behaviour from the nervous system. We culminate this discussion by describing a valuable effort to capture neural dynamics using a mathematical model to help reproduce this behaviour within the computer simulations. The chapter will end with an introduction to learning dynamics in neural networks. We shall not go into the details of these concepts to avoid unnecessary digressions as this research is not directly based on neural dynamics.

### 2.2 Basic Neural Structure

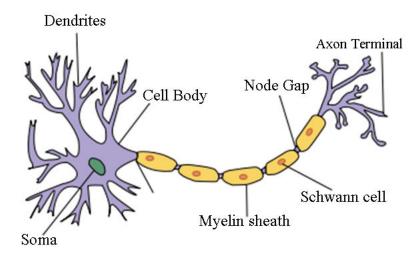

The neurons (Figure 2.2) are the basic functional unit of the nervous system [Tho00]. Neurons are like other body cells in most respects. However, they are specialized in their behaviour in order to process and transmit information to other neurons

Figure 2.2: A Typical Neuron (from [Wik09a]).

or muscles. The brain's behaviour, as a whole, depends on the way its neurons are organized, so to understand the brain it is important to understand neurons and their information processing mechanisms. A neuron's functionality is defined by its microstructure and connectivity to other neurons. One major characteristic of neurons that differentiates them from the other body cells is the structure of their cell membrane, which is made specifically to transmit and receive information. Neurons are specialized in information processing, utilizing special electrophysical and chemical processes [Tra02]. There are many different types of neuron based on their size, shape, and physiological properties. However, many features of neurons can be generalized to almost all types of neuron.

The following sections describe some important parts of a neuron which contribute to its functional behaviour.

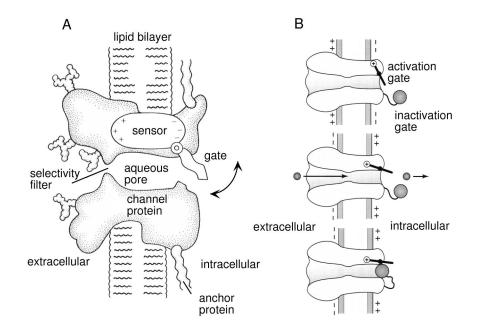

#### 2.2.1 Membrane

The neural membrane is made of organic fluid (phosphoric acid and fatty acid), about 3-4 nm in thickness [DA01], that keeps a neuron intact in the ionic water solution inside and around it. The ionic solution contains ions which are mostly sodium  $(Na^+)$ , potassium  $(K^+)$ , calcium  $(Ca^{+2})$ , and chloride  $(Cl^-)$ . The membrane is impermeable to most charged molecules, which causes it to behave like a capacitor separating charges along its interior and exterior surfaces. The cell membrane contains some protein molecules scattered throughout it.

Figure 2.3: Ionic Channels in Neural Membrane (from [DA01], fig. 5.8 page 169)).

molecules are the chemical receptors of charged ions and are called *ion channels* as shown in Figure 2.3. Charged ions attach to the appropriate protein molecules on the cell membrane and may cause various changes in both the membrane and the inner process of the neuron [Tho00]. There can be more than a dozen types of ion channel in a cell membrane, with a total number of channels in a neuron's membrane ranging from hundreds to thousands [Tho00]. Most of these channels form valves to allow specific ions to enter or leave the cell body and are named after the ions they allow to pass, i.e. a  $Na^+$  ion channel will let only  $Na^+$  ions to pass through it. Some channels are always open and are called *leakage channels* while the other channels are normally closed and are activated by certain changes in the membrane.

#### 2.2.2 Axon

Each neuron has only one axon as an output terminal to other neurons, gland cells or muscles. The axon may branch and send multiple fibres to attach to the other neurons through its *axon terminals* (Figure 2.2). The axons are filled with tiny tubes running the length of the axons from the cell body to the synaptic terminals called *microtubules*. Chemical substances called *neurotransmitters*, which are

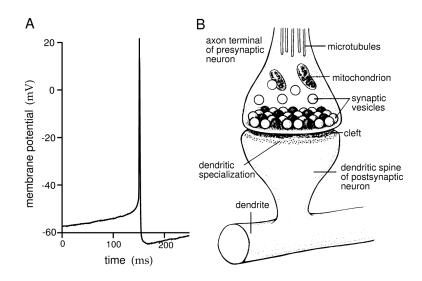

Figure 2.4: Inter-neuron Synapse (from [DA01], fig 1.2 page 6).

produced in the cell body, are transported to the axon terminals with the help of these microtubules. The chemicals move in both directions with the help of a fast and a slow process with a transportation speed of 10-20 millimetres per day and 1 millimetre per day respectively. The larger axons are covered with a sheath of fatty insulation called *myelin* (Figure 2.2). Myelin considerably increases the speed of conduction in an axon [Tho00]. Once an axon is fully developed, it is covered by many layers of myelin.

#### 2.2.3 Dendrite

Dendrites are thought to be an extension of the cell body's receptive surface. These are the fibres around neuron (Figure 2.2) which give a neuron its typical tree-like shape. They may range from a few short fibres to a huge mass of entangled bushes. A typical neuron can have 10,000-100,000 dendrites. The axons from one neuron can attach to the cell body of another neuron directly or through these dendrites to form *synapses* (Figure 2.1). The dendrites of many neurons are covered with thousands of little extensions called *dendritic spines*. The spine is the *postsynaptic* part of the synapse made with the *presynaptic* axon-terminal from some other neuron [Tho00].

#### 2.2.4 Synapse

One way that neurons are different from other body cells is that they make synapses with other neural tissues with the help of their axons. Synapses (Figure 2.4) are the point of functional contact formed by axons to the other neurons at their dendrites or cell bodies. Synapses can be divided into two basic types: electrical and chemical synapses [Tho00]. The mammalian brain predominantly contains chemical synapses. The neuron contributing its axon to a synapse is termed as a *presynaptic* neuron while the neuron on whose dendrite or cell body the axon is attached is called the *postsynaptic* neuron. Axon terminals contain a large number of chemical pockets called *vesicles* which are filled with *neuro*transmitters. The attachment point on the postsynaptic neuron forms a dense staining band that defines the extent of the the synapse. In between the preand postsynaptic contact points, there is a space of about 20 nm called *synaptic cleft.* When a synapse is active, the vesicles open and release neurotransmitters into the synaptic cleft. These are received by chemical receptor molecules on the surface of postsynaptic neurons. A synapse can either be *excitatory* or *inhibitory* depending on the type of neurotransmitter being released by the presynaptic neuron. The excitatory synapses increase the activation of target neurons while the inhibitory synapse reduce their activation.

Various types of neurotransmitter with specific properties are found in the nervous system. These neurotransmitters regulate neurotransmitter-gated ion channels which, in turn, regulate the ionic conductances of the membrane through the binding of particular neurotransmitters. On receipt of a specific neurotransmitter, these channels allow ions of specific size and shape to pass through them. Each neurotransmitter affects the receiving neuron in a different way.

#### 2.3 Membrane Potential

The concentration of ions is not the same within and outside a neuron as shown in Figure 2.5. This difference between the ion concentration causes a concentration gradient across the neuron's membrane. The concentration of  $K^+$  is much higher inside the neuron than in the the fluid outside the cell. The leakage-channels allow the  $K^+$  from the ionic solution inside the neuron to move outside to balance its concentration under a *diffusion force* caused by the concentration gradient. The solution inside the neuron contains negatively charged protein ions  $P_{2-}$  which

Figure 2.5: Ionic Channel Interplay to Develop Membrane Potential (from [Wik09d]).

always remain inside the cell because of their large size [Tho00]. The diffusion process leaves an excess of negative charge inside the neuron and an excess of positive charge outside the cell body which causes a strong *electric potential* across the cell membrane. The electric force is in the opposite direction to the diffusion force and tries to stop  $K^+$  flow. The two forces, i.e. the ion concentration gradient and the electric potential, will eventually balance each other to stop further transportation of  $K^+$  ions from inside to outside the cell membrane. The neuron settles at an equilibrium state with a concentration of  $K^+$  ions of 400 and 20 millimoles per litre inside and outside the cell respectively. The resting membrane potential due to  $K^+$  can be found using the Nernst equation [Tho00] as:

$$V = \frac{RT}{kF} \log \frac{[I^+]_{in}}{[I^+]_{out}}$$

(2.1)

where k, R and F are constants, T is the absolute temperature and  $[I^+]$  is the concentration of positive ions. At a normal temperature of  $18^0$  Celsius  $\frac{RT}{kF} = 58$  and the Nernst equation gives a resting potential of  $K^+$  [Tho00] as:

$$V = 58\log[\frac{20}{400}] = -75.46mV \approx -75mV \tag{2.2}$$

Similarly, the other ion concentrations, such as those of  $Na^+$ ,  $Cl^-$  and  $Ca^{+2}$ , are greater on the outside of the cell membrane, however, these do not contribute substantially to the resting potential as the  $Na^+$ ,  $Cl^-$  and  $Ca^{+2}$  ion channels are not affected too much by the concentration diffusion force. These are mostly voltage-gated or neurotransmitter-gated channels as compared to the  $K^+$  channel which are mostly diffusion-gated leakage channels. The Nernst equation can be extended to take into account the effect of these channels as well [Izh07], eventually leading to the resting potential of a neuron, which is typically about  $V_{rest} = -65mV$  [Tra02].

#### 2.4 Action Potential

As discussed earlier, the membrane at rest is slightly permeable to  $Na^+$   $(\frac{1}{20}th)$ the permeability of  $K^+$ ) due to leakage channels. When a large quantity of neurotransmitter is released by the presynaptic neuron or a small quantity of it released by a few presynaptic neurons in a short span of time, this can trigger a stronger response in the postsynaptic neuron's membrane potential. If the neurotransmitter is excitatory, it will move the potential difference in a positive direction (from -65mV to -30mV - threashold potential) and activate the cell membrane, developing an action potential across the membrane. This opens all Na+ channels suddenly, making the membrane permeable to  $Na^+$ . The diffusion force due to the strong concentration of  $Na^+$  outside the cell body pushes  $Na^+$ inside the cell (Figure 2.5). As there are more negatively charged ions (protein ions) inside the cell, the positive  $Na^+$  ions rush inside due to electrical force as well. Both forces, i.e. the diffusion force and the electrical force, act in the same direction to bring the  $Na^+$  inside the cell body with 500 times more permeability for  $Na^+$  than the one it has in the resting state. In a short period, the membrane potential reaches a  $Na^+$  equilibrium value of +50 mV (an increase of  $\approx 100 mV$ in the membrane potential from its resting potential), which closes the  $Na^+$ channels. At the same time a few voltage-gated  $K^+$  channels which are normally closed at the resting potential are opened, letting  $K^+$  move outside more freely than at rest. This removes  $K^+$  from the cell bringing the membrane potential towards its resting potential. As the opening and closing of the  $K^+$  channels is slower than the  $Na^+$  gates, the  $K^+$  gates remain open while the Na+ gates are closed, as a result of which the membrane potential goes toward -75mV (more

Figure 2.6: Membrane equivalent conductance (g) and voltage (v) as a result of interplay between  $Na^+$  conductance  $(g_{Na})$  and  $K^+$  conductance  $(g_K)$  as measured by Hodgkin and Huxley [HH52] (they used a resting potential of 0 mV instead of -65 mV for computational simplicity).

negative than the resting potential), i.e. towards the  $K^+$  equilibrium potential. This state of more negative voltage than the resting potential remains for a few milliseconds and is called the *afterpotential* state or *hyperpolarization*.

The few voltage-gated  $K^+$  channels close eventually and the potential returns back to the normal resting (-65mV) voltage. The period when the  $Na^+$  channels are open, and the spike of action potential develops and decays, is called the *absolute refractory period*. During this period the neuron can not be electrically stimulated to generate another action potential [Tho00]. After the spike, i.e. in the afterpotential period, the neuron can be electrically activated, however, it requires a very strong electrical stimulus. Normally neurons do not spike during this period. This is called the *relative refractory* period. The hyperpolarization of the neuron relative to its resting voltage causes the voltage-dependent  $K^+$ channels to close and the voltage-dependent sodium channels to deactivate, eventually reinstating the normal resting potential of the neuron. Figure 2.6 shows the interplay of the ionic conductances due to the opening and closing of the ionic channels during the process of action potential. The graph labelled V shows the resultant membrane potential as an accumulated voltage across the membrane.

With the repeated generation of action potentials, resulting in repeated outflow of K+ and inward flow of  $Na^+$ , the K+ concentration will decrease and Na+ concentration will increase within the cell. This will ultimately reduce the probability of generating an action potential. At this stage, the action potential can be generated with the help of yet another type of ion channel called an *ion* pump, which can transfer ions against their concentration gradient. The process is expensive as a neuron requires energy for this process [Tra02].

#### 2.5 Synaptic Transmission

Information processing in the brain is dependent on the transmission of signals between the neurons. Chemical synapses are the main source of information transfer in the nervous system [Tra02]. The cell membrane has a relatively high resistance and accumulates charge on both sides creating a capacitor effect. The action potential is generated at the stem of the axon where it starts from the neuron's body. As the  $Na^+$  moves into the axon at the site of the action potential, the region closer to the site begins to become relatively less negatively charged from its resting potential due to  $N^+$  ions, a process called *depolarization*. The rate of depolarization depends on the membrane capacitance. The patch of membrane immediately next to the place where the  $Na^+$  gates open will then reach the Na+gate opening threshold voltage. In this way the action potential continuously moves down the axon until it reaches the axon terminal which contains normally closed  $Ca^+$  channels. The arrival of the action potential opens these channels briefly, causing an influx of  $Ca^+$  ions due to the diffusion gradient as  $Ca^+$  ions are more in number outside the cell membrane than inside it. The  $Ca^+$  ions then trigger the release of neurotransmitters. The released neurotransmitter at the synapse enters the cleft and attaches the postsynaptic membrane.

As a result of excitatory neurotransmitters the neurotransmitter-gated  $Na^+$  channels open in the postsynaptic neuron. The postsynaptic neuron becomes depolarized and if reaches a threshold potential, the voltage-gated  $Na^+$  channels will open, generating an action potential and so on. This process is time consuming as it takes a few milliseconds from the time the action potential reaches the presynaptic axon terminal to the point where the postsynaptic neuron is depolarised. It is believed that the sodium channels are situated closer to the axon stem and along the axon, as the rest of the cell body and the dendrites are covered with axons from other neurons and thus act as if myelinated. Because of this reason, the action potential is generated closer to the point the axon emerges

from the cell body and travels along the axon towards its terminal rather than moving in the opposite direction [Tra02]. Normally, the activation of a single excitatory synapse on a neuron will not cause it to develop an action potential. It may require a number of synapses to be activated together in a short span of time and influence the postsynaptic neuron together - a phenomenon called *spatial summation*. If the synapses are far apart, they may not generate an action potential on being activated together. However, if they are activated repeatedly at a fast enough rate, they will sum over time and generate an excitatory postsynaptic potential (EPSP) to cause an action potential in the postsynaptic neuron. This phenomenon is called *temporal summation* [Tra02].

#### 2.6 Neural Networks

Each neuron connects with on the order of 1000 other neurons (some may receive even more than 100,000 input connections). A small number of interconnected neurons can exhibit complex behaviour and information processing capabilities not present in a single neuron [DA01, Tra02]. There is still little understanding of such non-linear interacting systems which are characterised by additional information processing capabilities beyond that of single neurons, such as presenting information in a distributed manner. A combination of such networks in a specific area of the nervous system is able to perform even more complex information processing tasks. It is the neural interaction in large population of neurons that enables their processing abilities different from a single neuron. This forms a system of interacting processing units with emergent properties. Emergence is probably the most defining property of neural networks which distinguishes these from parallel computing in classical computer science [Tra02]. Interacting real-time systems have unique properties beyond combined properties of single processors and the outcome may not be deterministic, while in a typical parallel computing system we distribute a large and complex job across independent algorithmic threads to speed up the processing but to get the same result. Emergent systems, however, are rule-based systems. Neural networks are also governed by a finite set of rules or fundamental laws [Tra02]. These rules are not fully understood in case of the nervous system and some people are convinced that a simple set of rules explaining brain functions might never be discovered, or even after discovering some of these rules we might not have sufficient understanding of this most complex emergent system in the universe. However, there is enormous progress to this end, and today we know much more than we knew a decade ago.

#### 2.7 Neural Computation