# WORKLOAD-ADAPTATION IN MEMORY CONTROLLERS

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2015

By Mohsen Ghasempour School of Computer Science

# Contents

| Ał | ostrac | t       |                                     | 13 |

|----|--------|---------|-------------------------------------|----|

| De | eclara | tion    |                                     | 15 |

| Co | opyrig | ght     |                                     | 16 |

| Ac | know   | ledgem  | ients                               | 17 |

| 1  | Intr   | oductio | n                                   | 18 |

|    | 1.1    | Memo    | ry Challenges                       | 19 |

|    | 1.2    | Contri  | butions                             | 21 |

|    | 1.3    | Thesis  | Organisation                        | 23 |

| 2  | Bacl   | kgroun  | d and Motivation                    | 25 |

|    | 2.1    | Overv   | iew of DRAMs                        | 25 |

|    | 2.2    | DRAN    | As: Basic Circuits and Architecture | 27 |

|    |        | 2.2.1   | DRAM Cell                           | 27 |

|    |        | 2.2.2   | DRAM Array                          | 28 |

|    |        | 2.2.3   | DRAM Bank                           | 28 |

|    |        | 2.2.4   | DRAM Device                         | 29 |

|    | 2.3    | DRAN    | As: Memory Access Protocol          | 29 |

|    |        | 2.3.1   | Basic DRAM Commands                 | 31 |

|    |        | 2.3.2   | Row-Buffer Access Classification    | 34 |

|    | 2.4    | DRAN    | I vs SDRAM                          | 36 |

|    | 2.5    | DRAN    | As: Memory System Organisation      | 36 |

|    |        | 2.5.1   | DRAM Rank                           | 36 |

|    |        | 2.5.2   | DRAM Channel                        | 36 |

|    | 2.6    | DRAN    | A Memory Controller                 | 37 |

|   |     | 2.6.1   | Address Mapping                                  | 38 |

|---|-----|---------|--------------------------------------------------|----|

|   |     | 2.6.2   | Command Scheduling                               | 39 |

|   |     | 2.6.3   | Row-Buffer Management                            | 40 |

|   |     | 2.6.4   | Reliability Monitor                              | 41 |

|   | 2.7 | Perfor  | mance, Power and Reliability                     | 41 |

|   |     | 2.7.1   | Memory Access Pattern                            | 41 |

|   |     | 2.7.2   | Susceptibility to Address Translation            | 42 |

|   |     | 2.7.3   | Susceptibility to Page Closure Policy Prediction | 43 |

|   |     | 2.7.4   | Susceptibility to Error Detection                | 43 |

|   | 2.8 | Future  | Memory Technology and Scalability Challenges     | 44 |

|   |     | 2.8.1   | DDR4 DRAM                                        | 44 |

|   |     | 2.8.2   | Hybrid Memory Cube (HMC)                         | 45 |

|   |     | 2.8.3   | Non-Volatile Memory                              | 45 |

|   | 2.9 | Workle  | oad Adaptation                                   | 45 |

| 3 | Exp | eriment | tal Methodology                                  | 47 |

|   | 3.1 | Tools l | Development                                      | 47 |

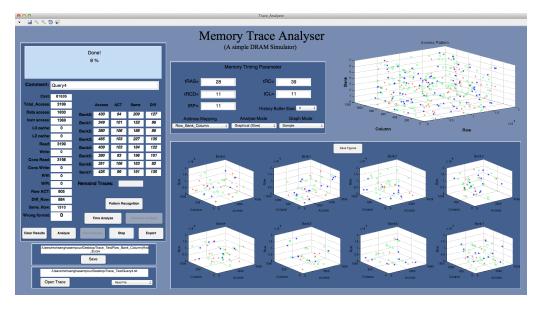

|   |     | 3.1.1   | A Simple DRAM Simulator                          | 47 |

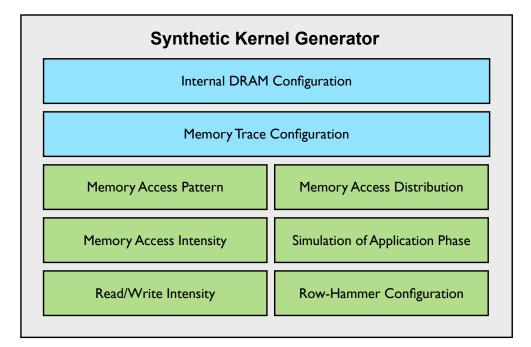

|   |     | 3.1.2   | A Synthetic Kernel Generator (SKG)               | 48 |

|   | 3.2 | Evalua  | tion Platform                                    | 50 |

|   |     | 3.2.1   | USIMM: The Utah Simulated Memory Module          | 50 |

|   | 3.3 | Evalua  | ted Benchmark Suites                             | 51 |

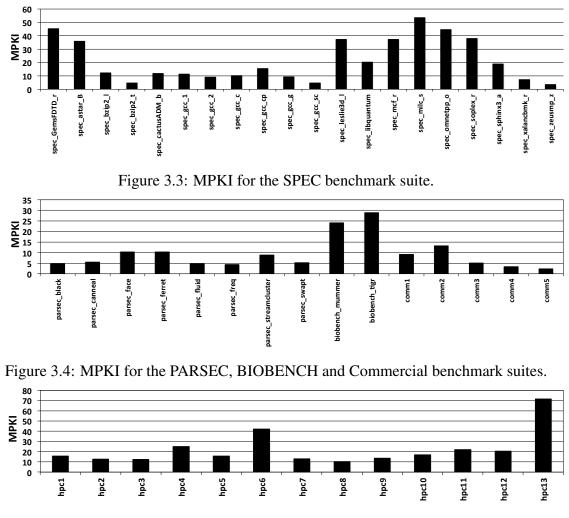

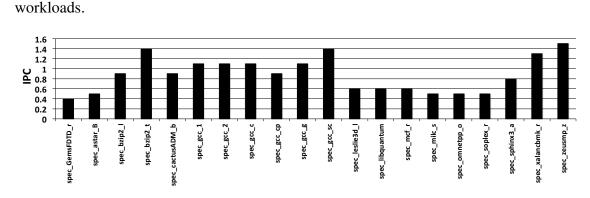

|   |     | 3.3.1   | Workload Characterisation                        | 52 |

| 4 | HAI | PPY: Hy | ybrid Address-based Page PolicY                  | 55 |

|   | 4.1 | Introdu | uction                                           | 55 |

|   | 4.2 | Backg   | round on DRAM Page Closure Policy                | 57 |

|   | 4.3 | HAPP    | Y:Hybrid Address-based Page PolicY               | 59 |

|   |     | 4.3.1   | HAPPY: Basic Principles                          | 59 |

|   |     | 4.3.2   | HAPPY: Access-based Prediction                   | 59 |

|   |     | 4.3.3   | HAPPY: Time-based Prediction                     | 62 |

|   |     | 4.3.4   | HAPPY: Further Possible improvements             | 64 |

|   |     | 4.3.5   | HAPPY: Intuition                                 | 64 |

|   | 4.4 | Evalua  | tion Methodology                                 | 65 |

|   | 4.5 | Result  | s and Discussions                                | 68 |

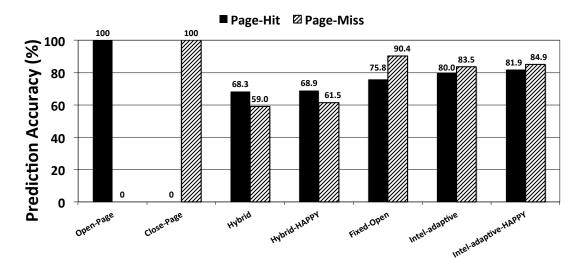

|   |     | 4.5.1   | Prediction Accuracy                              | 69 |

|   |     |         |                                                  |    |

|   |     | 4.5.2   | Performance Analysis                                | 70  |

|---|-----|---------|-----------------------------------------------------|-----|

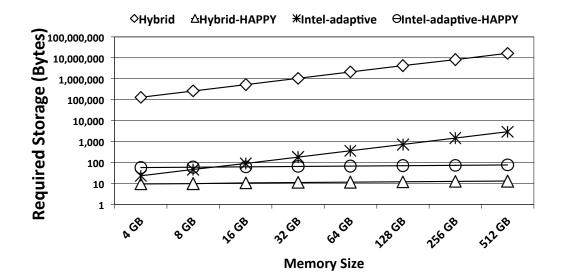

|   |     | 4.5.3   | Sensitivity to Memory Size                          | 72  |

|   |     | 4.5.4   | Scalability with Memory Size                        | 73  |

|   |     | 4.5.5   | Prediction Algorithms - Weakness and Strength       | 74  |

|   |     | 4.5.6   | Flexibility                                         | 75  |

|   | 4.6 | Relate  | d Work                                              | 76  |

|   | 4.7 | Summ    | ary                                                 | 77  |

| 5 | DRe | AM: D   | ynamic Re-arrangement of Address Mapping            | 79  |

|   | 5.1 | Introdu | uction                                              | 79  |

|   | 5.2 | Backg   | round on DRAM Address Mapping                       | 80  |

|   |     | 5.2.1   | Motivation - Address Mapping Analysis               | 82  |

|   | 5.3 | DReA    | M: Dynamic Re-arrangement of Address Mapping        | 84  |

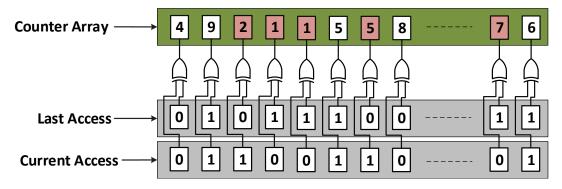

|   |     | 5.3.1   | DReAM - Online Prediction of Address Mapping        | 84  |

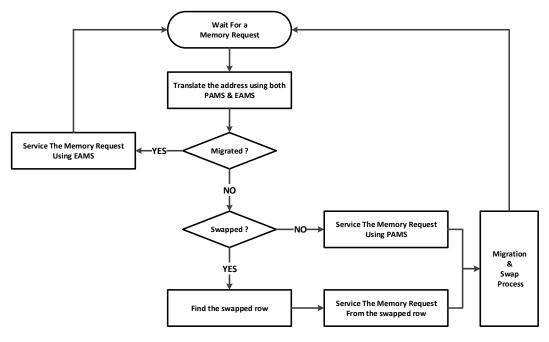

|   |     | 5.3.2   | DReAM - Data Migration Solutions                    | 91  |

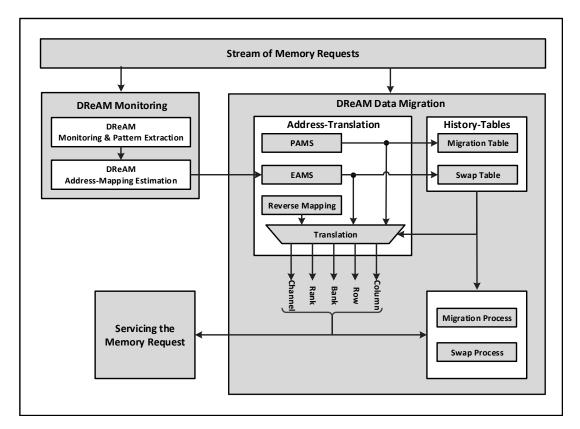

|   |     | 5.3.3   | DReAM - Overview of Architecture                    | 99  |

|   | 5.4 | Evalua  | tion Methodology                                    | 104 |

|   | 5.5 | Result  | s and Discussions                                   | 107 |

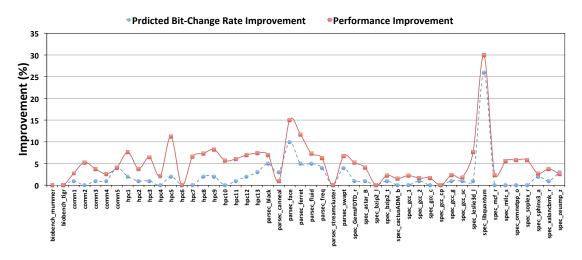

|   |     | 5.5.1   | Bit-Change Rate vs Performance Improvement          | 107 |

|   |     | 5.5.2   | Performance Analysis                                | 107 |

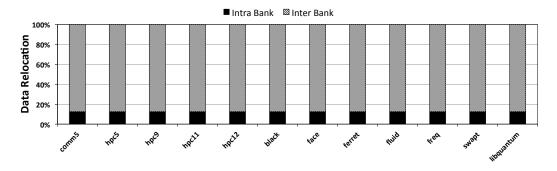

|   |     | 5.5.3   | Data Relocation Analysis                            | 111 |

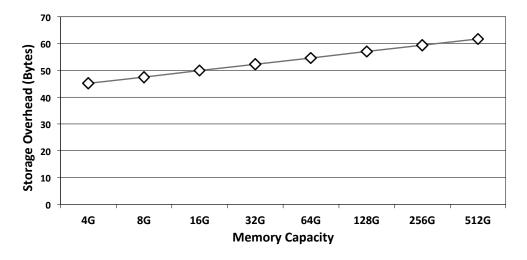

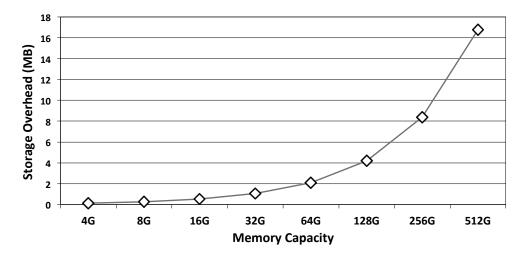

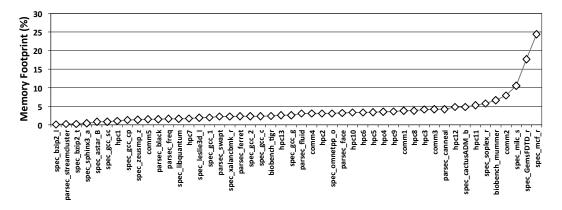

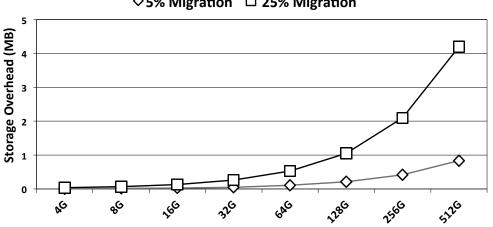

|   |     | 5.5.4   | Storage Overhead and Scalability                    | 112 |

|   | 5.6 | Relate  | d Work                                              | 114 |

|   | 5.7 | Summ    | ary                                                 | 115 |

| 6 | ARN | MOR: A  | A Run-time Memory hot-row detectOR                  | 117 |

|   | 6.1 | Introdu | uction                                              | 117 |

|   | 6.2 | Backg   | round on Row Hammer Error                           | 120 |

|   |     | 6.2.1   | DRAM Refresh                                        | 120 |

|   |     | 6.2.2   | Row Hammer Effect - Corrupting Data without Writing | 121 |

|   | 6.3 | Row H   | Iammer: Analytical Analysis                         | 122 |

|   | 6.4 | ARMO    | DR: A Run-time Memory hot-row detectOR              | 124 |

|   |     | 6.4.1   | ARMOR - Basic Principles                            | 124 |

|   |     | 6.4.2   | ARMOR - Overview of Architecture                    | 125 |

|   | 6.5 | ARMO    | OR Applications                                     | 129 |

|   |     | 6.5.1   | Target Row Refresh                                  | 130 |

|    |        | 6.5.2    | ARMOR Cache Solution                    | 130 |

|----|--------|----------|-----------------------------------------|-----|

|    | 6.6    | Evalua   | tion Methodology                        | 131 |

|    | 6.7    | Result   | s and Discussions                       | 134 |

|    |        | 6.7.1    | Benchmark Profiling                     | 135 |

|    |        | 6.7.2    | Performance Analysis                    | 139 |

|    |        | 6.7.3    | Hot-Row Table Size vs Accuracy          | 143 |

|    |        | 6.7.4    | Scalability                             | 145 |

|    |        | 6.7.5    | ARMOR Cache Performance                 | 145 |

|    | 6.8    | Relate   | d Work                                  | 147 |

|    | 6.9    | Summ     | ary                                     | 148 |

| 7  | A 33   | orklood  | d Adaptive Memory Controller            | 150 |

| /  | 7.1    |          | · ·                                     | 150 |

|    |        |          | uction                                  |     |

|    | 7.2    | Evalua   | tion Methodology                        |     |

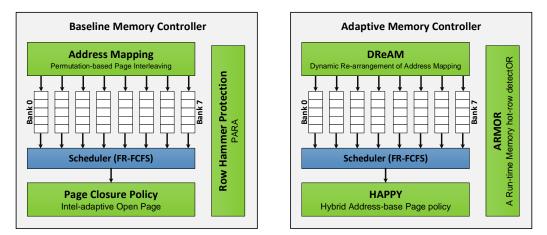

|    |        | 7.2.1    | Baseline vs. Adaptive Memory Controller | 151 |

|    | 7.3    | Result   | s and Discussions                       | 152 |

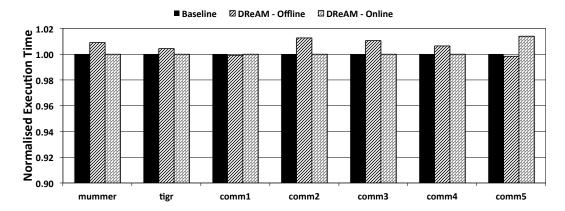

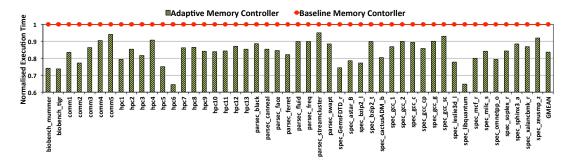

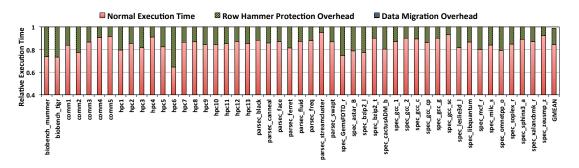

|    |        | 7.3.1    | Performance Analysis                    | 152 |

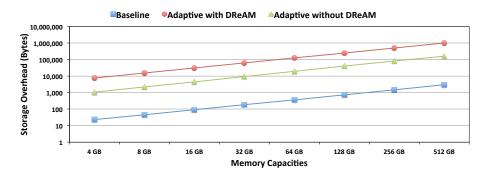

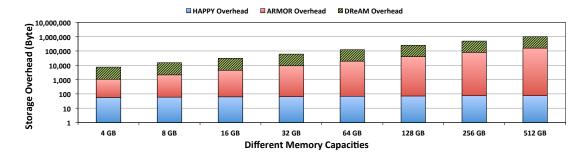

|    |        | 7.3.2    | Implementation Cost Analysis            | 155 |

|    | 7.4    | Summ     | ary                                     | 157 |

| 8  | Con    | clusions | s and Future Work                       | 159 |

|    | 8.1    | Conclu   | isions                                  | 159 |

|    | 8.2    |          | Work                                    | 163 |

| 9  | Pub    | lication | s, Patent and Commercialisation         | 164 |

| Bi | bliogi | aphy     |                                         | 166 |

|    | 0      |          |                                         |     |

# **List of Tables**

| 2.1 | Summary timing constraints of DRAM                                  | 30  |

|-----|---------------------------------------------------------------------|-----|

| 3.1 | Standard workloads and benchmark suites                             | 51  |

| 4.1 | Cost of page-hits and page-misses when using different page closure |     |

|     | policies                                                            | 57  |

| 4.2 | USIMM configuration parameters                                      | 66  |

| 4.3 | Evaluated workloads and benchmark suites                            | 66  |

| 4.4 | Randomly generated multithread workloads.                           | 68  |

| 4.5 | Required performance counters for different page closure policies   | 74  |

| 5.1 | USIMM configuration parameters                                      | 105 |

| 5.2 | Evaluated workloads and benchmark suites                            | 106 |

| 5.3 | Randomly generated multithread workloads.                           | 107 |

| 6.1 | ACT <sub>th</sub> for different evaluated DRAM modules.             | 123 |

| 6.2 | USIMM configuration parameters used in the experiments              | 132 |

| 6.3 | Evaluated workloads and benchmark suites                            | 133 |

| 6.4 | Synthetic kernel generator configuration parameters used to produce |     |

|     | the synthetic kernels                                               | 134 |

| 6.5 | Synthetic workloads.                                                | 134 |

| 6.6 | Randomly generated Multithread workloads.                           | 135 |

| 7.1 | Implementation options for standard and adaptive memory controller. | 152 |

# **List of Figures**

| 1.1  | Memory hierarchy.                                              | 19 |

|------|----------------------------------------------------------------|----|

| 1.2  | Internal structure of a DRAM device.                           | 20 |

| 1.3  | An abstract view of the developed adaptive memory controller   | 23 |

| 2.1  | A Memory Module                                                | 25 |

| 2.2  | A typical computer system memory hierarchy                     | 26 |

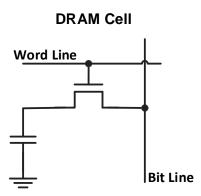

| 2.3  | A basic DRAM cell structure                                    | 27 |

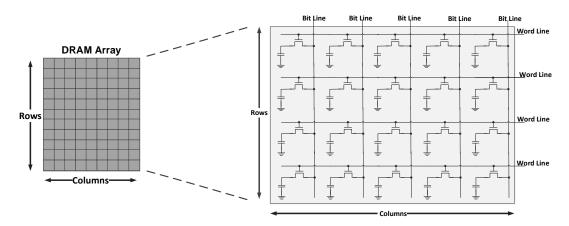

| 2.4  | A basic DRAM array structure                                   | 28 |

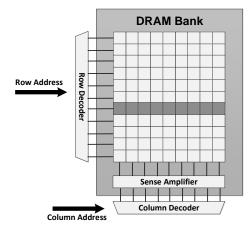

| 2.5  | A DRAM bank structure                                          | 29 |

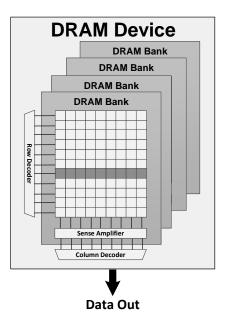

| 2.6  | A DRAM device structure                                        | 31 |

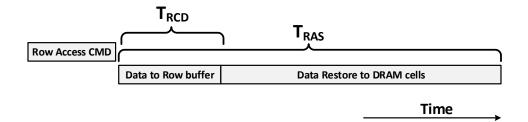

| 2.7  | Row access command timing.                                     | 32 |

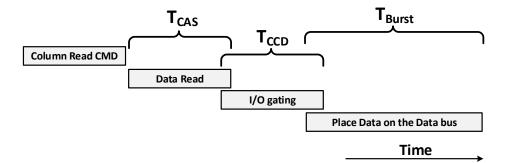

| 2.8  | Column read command timing                                     | 32 |

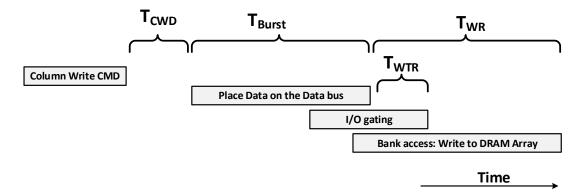

| 2.9  | Column write command timing.                                   | 33 |

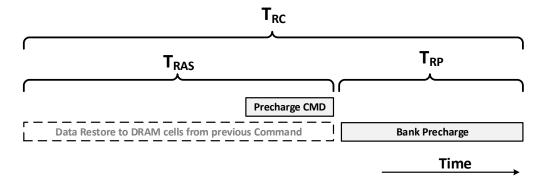

| 2.10 | Precharge command timing.                                      | 34 |

| 2.11 | Refresh command timing                                         | 35 |

| 2.12 | A DRAM rank structure.                                         | 37 |

| 2.13 | Different industrial memory organisations                      | 38 |

| 2.14 | An abstract view of a DRAM controller                          | 38 |

| 2.15 | Examples of address mapping using different schemes            | 39 |

| 3.1  | A simple DRAM simulator                                        | 48 |

| 3.2  | Block diagram of the synthetic kernel generator                | 49 |

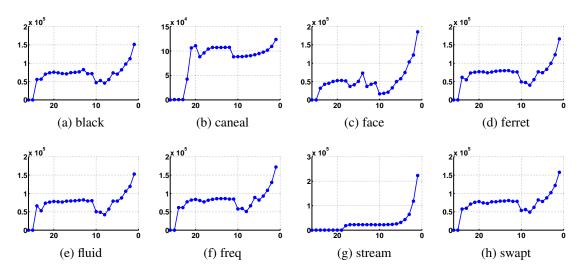

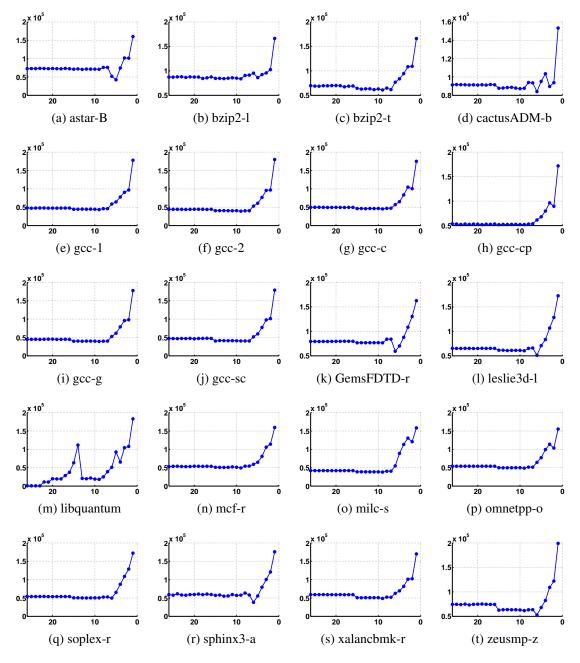

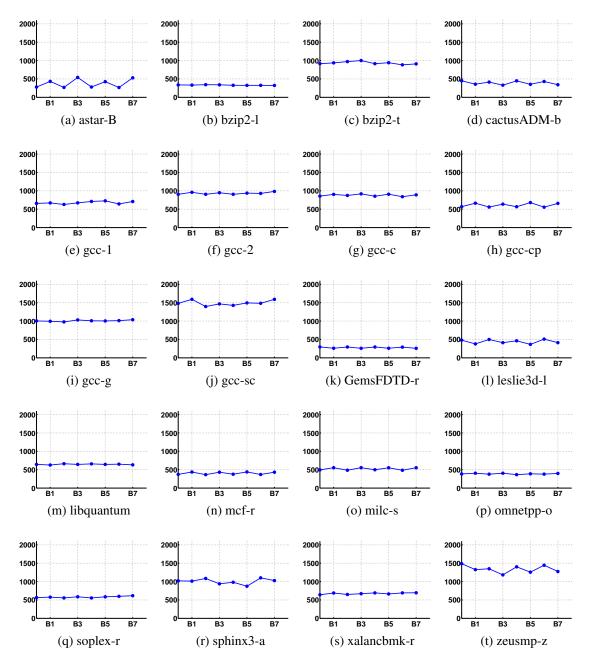

| 3.3  | MPKI for the SPEC benchmark suite.                             | 52 |

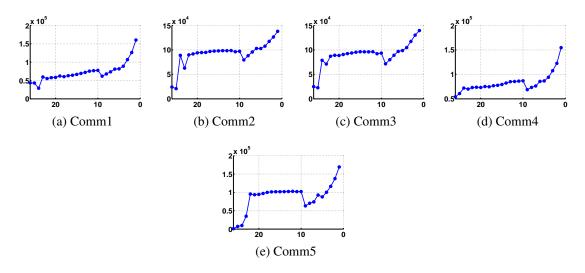

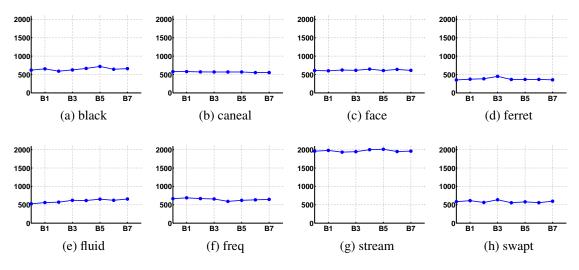

| 3.4  | MPKI for the PARSEC, BIOBENCH and Commercial benchmark suites. | 52 |

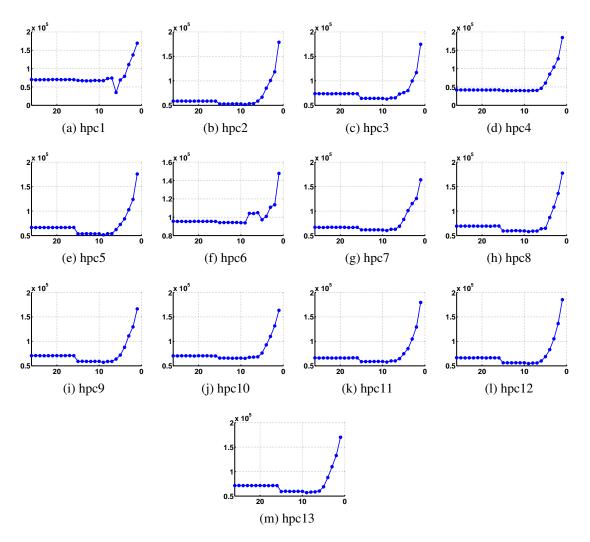

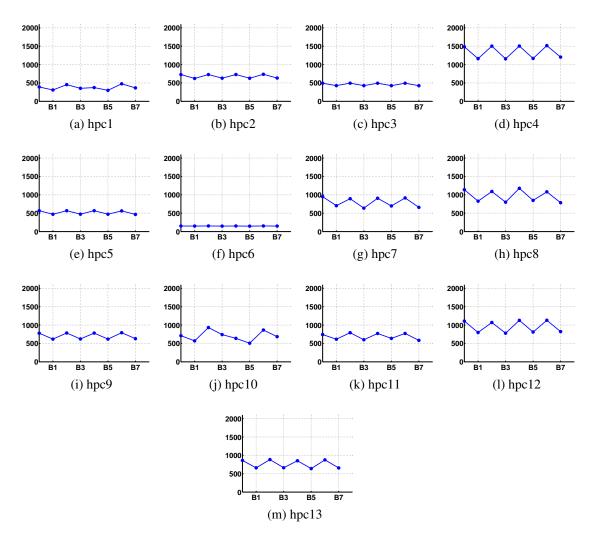

| 3.5  | MPKI for the HPC benchmarks.                                   | 52 |

| 3.6  | IPC for the SPEC benchmark suite                               | 53 |

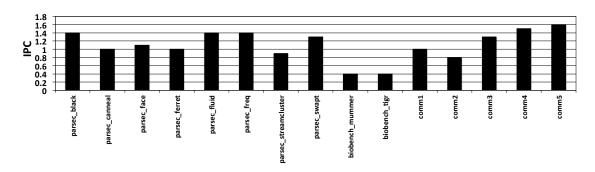

| 3.7  | IPC for the PARSEC, BIOBENCH and Commercial benchmark suites.  | 53 |

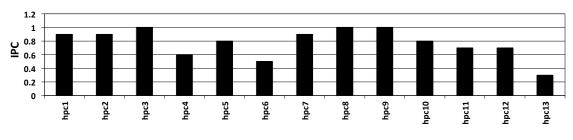

| 3.8  | IPC for the HPC benchmarks.                                    | 53 |

|      |                                                                |    |

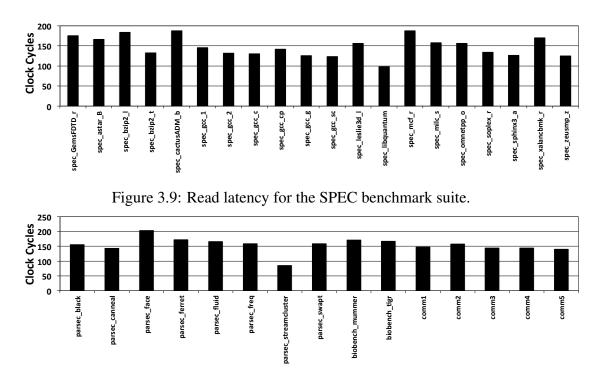

| 3.9  | Read latency for the SPEC benchmark suite                                | 54 |

|------|--------------------------------------------------------------------------|----|

| 3.10 | Read latency for the PARSEC, BIOBENCH and Commercial bench-              |    |

|      | mark suites.                                                             | 54 |

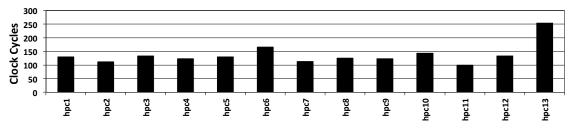

| 3.11 | Read latency for the HPC benchmarks.                                     | 54 |

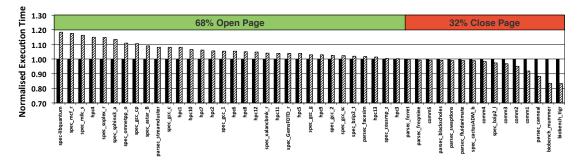

| 4.1  | Performance of static page policies for all workloads                    | 58 |

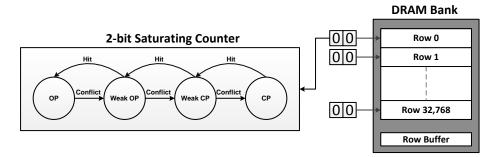

| 4.2  | Basic structure of hybrid page policy.                                   | 60 |

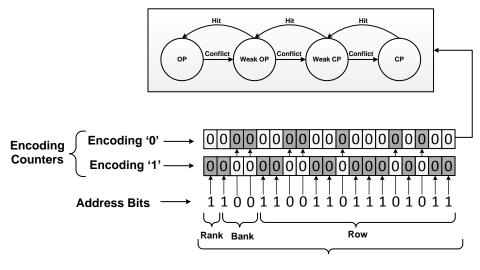

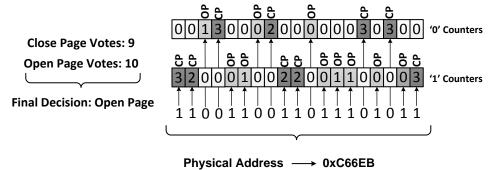

| 4.3  | HAPPY implementation of hybrid page policy.                              | 61 |

| 4.4  | Example of HAPPY majority vote decision                                  | 61 |

| 4.5  | Basic structure of the Intel-adaptive page policy predictor              | 62 |

| 4.6  | HAPPY implementation of Intel-adaptive page policy predictor             | 63 |

| 4.7  | Different address mappingg schemes.                                      | 67 |

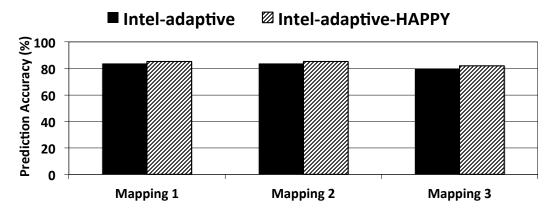

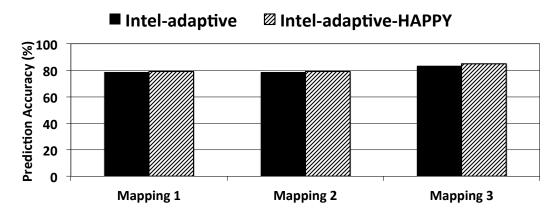

| 4.8  | Prediction accuracy for different predictors.                            | 70 |

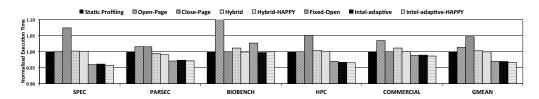

| 4.9  | Average execution time normalised to static profiling for the single-    |    |

|      | thread workloads.                                                        | 71 |

| 4.10 | Execution time normalised to static profiling for HPC workloads          | 71 |

| 4.11 | Execution time normalised to static profiling for SPEC workloads         | 71 |

| 4.12 | Execution time normalised to static profiling for PARSEC, BIOBENCH       |    |

|      | and Commercial workloads.                                                | 71 |

| 4.13 | Execution time normalised to static profiling for multithread workloads. | 71 |

| 4.14 | Page-hit prediction accuracy with different address mappings             | 73 |

| 4.15 | Page-miss prediction accuracy with different address mappings            | 73 |

| 4.16 | Scalability of different page closure prediction algorithms              | 74 |

| 5.1  | DRAM device organisation.                                                | 81 |

| 5.2  | Two different address mapping schemes                                    | 82 |

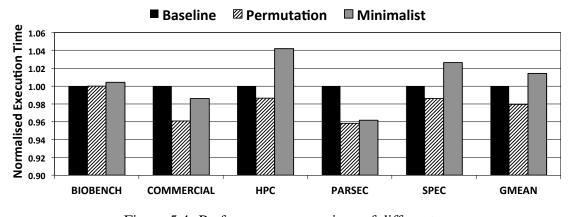

| 5.3  | Different address mapping schemes                                        | 83 |

| 5.4  | Performance comparison of different address-mapping schemes              | 84 |

| 5.5  | Address mapping profiling for BIOBENCH and COMMERCIAL bench-             |    |

|      | mark suites                                                              | 85 |

| 5.6  | Address mapping profiling for HPC benchmarks                             | 85 |

| 5.7  | Address mapping profiling for PARSEC benchmark suite                     | 85 |

| 5.8  | Address mapping profiling for SPEC benchmark suite                       | 85 |

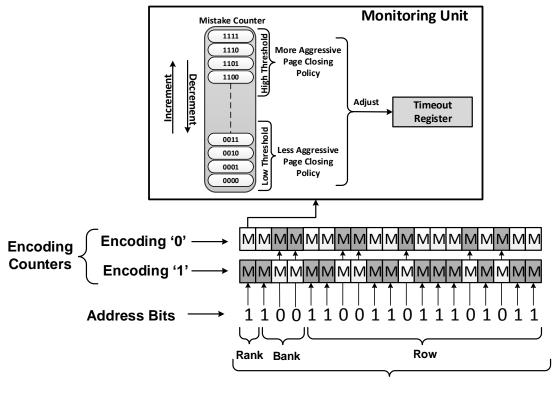

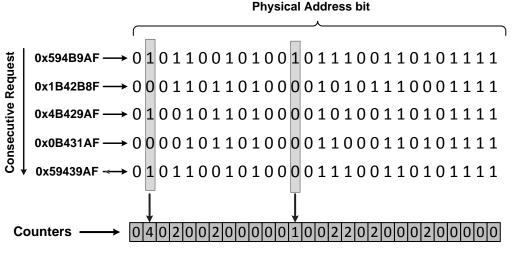

| 5.9  | Bit-counters mechanism                                                   | 86 |

| 5.10 | Extracted bit-change pattern for the COMMERCIAL benchmark suite.         | 87 |

| 5.11 | Extracted bit-change pattern for HPC benchmarks.                         | 88 |

| 5.12 | Extracted bit-change pattern for PARSEC benchmark suite                | 88  |

|------|------------------------------------------------------------------------|-----|

| 5.13 | Extracted bit-change pattern for SPEC benchmark suite                  | 89  |

| 5.14 | Extracted bit-change pattern for BIOBENCH benchmark suite              | 89  |

| 5.15 | DReAM flowchart.                                                       | 95  |

| 5.16 | DReAM architecture                                                     | 99  |

| 5.17 | DReAM monitoring counter structure.                                    | 100 |

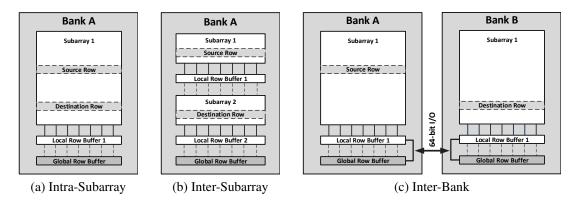

| 5.18 | Different data migration scenarios                                     | 101 |

| 5.19 | Basic structure of the USIMM scheduler                                 | 106 |

| 5.20 | Comparison between the bit-change rate improvement predicted by        |     |

|      | DReAM and the overall performance improvement                          | 108 |

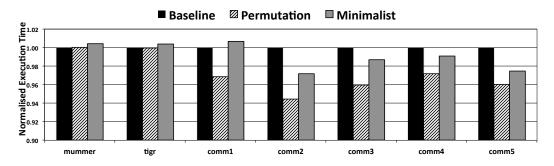

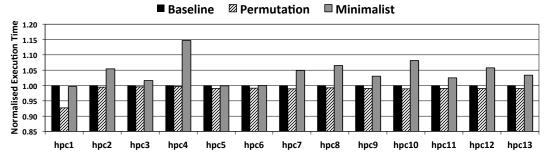

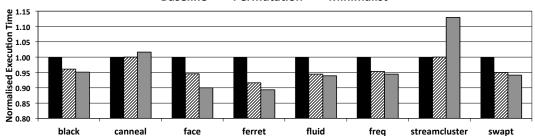

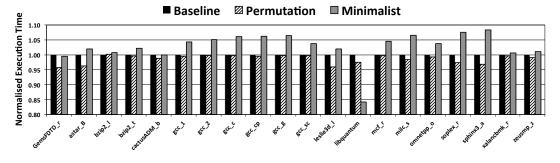

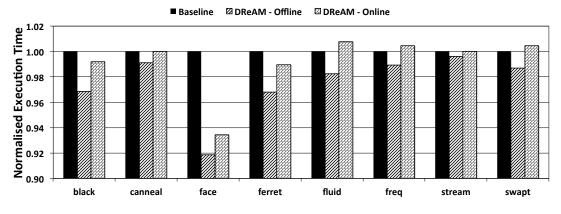

| 5.21 | Execution time (normalised to baseline) achieved for BIOBENCH and      |     |

|      | COMMERCIAL benchmark suites.                                           | 109 |

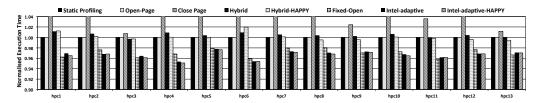

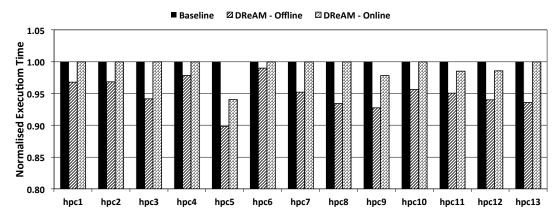

| 5.22 | Execution time (normalised to baseline) achieved for HPC benchmarks.   | 110 |

| 5.23 | Execution time (normalised to baseline) achieved for PARSEC bench-     |     |

|      | mark suite                                                             | 110 |

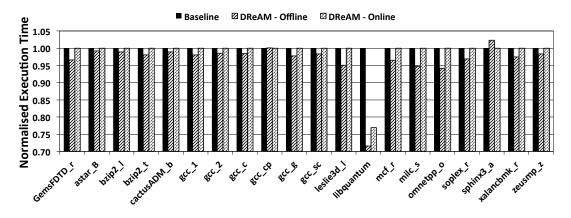

| 5.24 | Execution time (normalised to baseline) achieved for SPEC benchmark    |     |

|      | suite                                                                  | 110 |

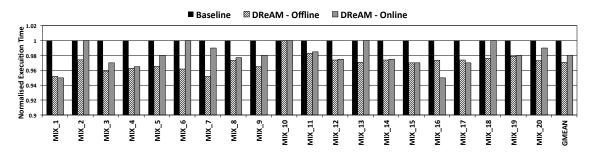

| 5.25 | Final execution time (normalised to baseline) achieved for multithread |     |

|      | benchmarks                                                             | 111 |

| 5.26 | The analysis of inter and intra bank data relocation required by DReAM |     |

|      | online                                                                 | 112 |

| 5.27 | DReAM address-mapping prediction phase implementation cost             | 113 |

| 5.28 | DReAM data migration phase implementation cost                         | 113 |

| 5.29 | Memory footprint for all the evaluated workloads                       | 114 |

| 5.30 | Associated cost of partial data migration for DReAM                    | 114 |

| 6.1  | DRAM Cell                                                              | 120 |

| 6.2  | Row Hammer phenomenon                                                  | 121 |

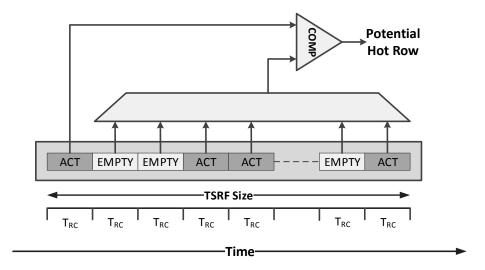

| 6.3  | Hot time windows.                                                      | 125 |

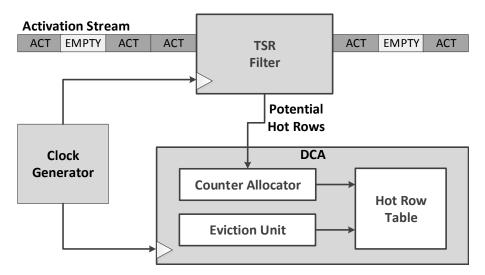

| 6.4  | ARMOR overview.                                                        | 126 |

| 6.5  | Time-based Shift Register.                                             | 127 |

| 6.6  | Dynamic Counter Allocator.                                             | 128 |

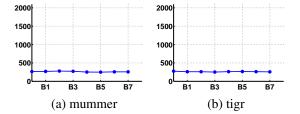

| 6.7  | Average activation intervals to each bank for BIOBENCH benchmark       |     |

|      | suite                                                                  | 136 |

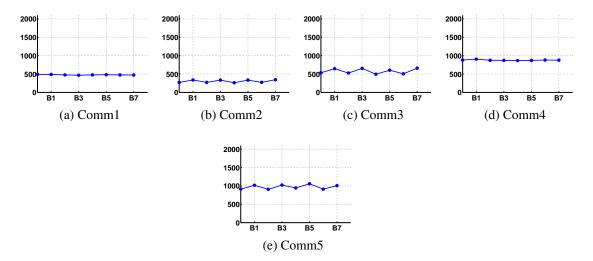

| 6.8  | Average activation intervals to each bank for COMMERCIAL bench-        |     |

|      | mark suite                                                             | 136 |

| 6.9  | Average activation intervals to each bank for HPC benchmarks           | 137 |

|------|------------------------------------------------------------------------|-----|

| 6.10 | Average activation intervals to each bank for PARSEC benchmark suite.  | 137 |

| 6.11 | Average activation intervals to each bank for SPEC benchmark suite     | 138 |

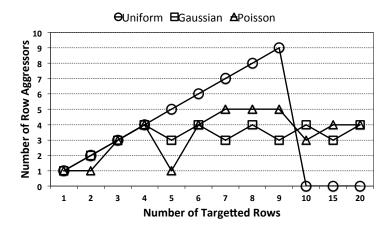

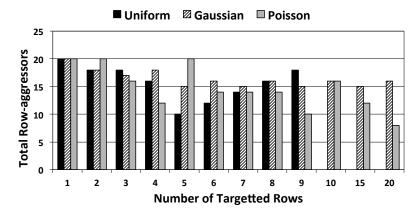

| 6.12 | Induced unique number of row-aggressors                                | 139 |

| 6.13 | Total row aggressors during execution time.                            | 139 |

| 6.14 | Average activation intervals to each bank for HPC benchmarks           | 140 |

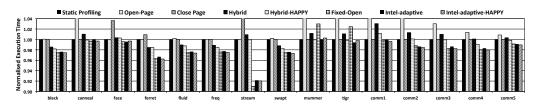

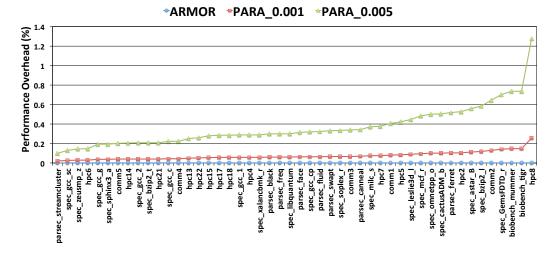

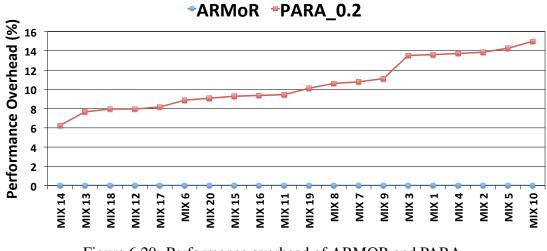

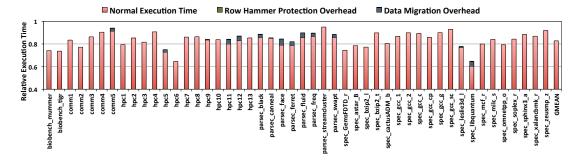

| 6.15 | Performance overhead of ARMOR and PARA for standard workloads.         | 141 |

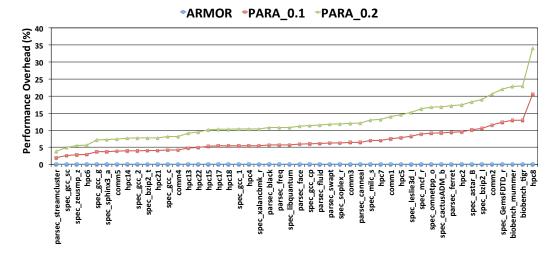

| 6.16 | Performance overhead of ARMOR and PARA (with the higher Proba-         |     |

|      | bility Values) for standard workloads.                                 | 141 |

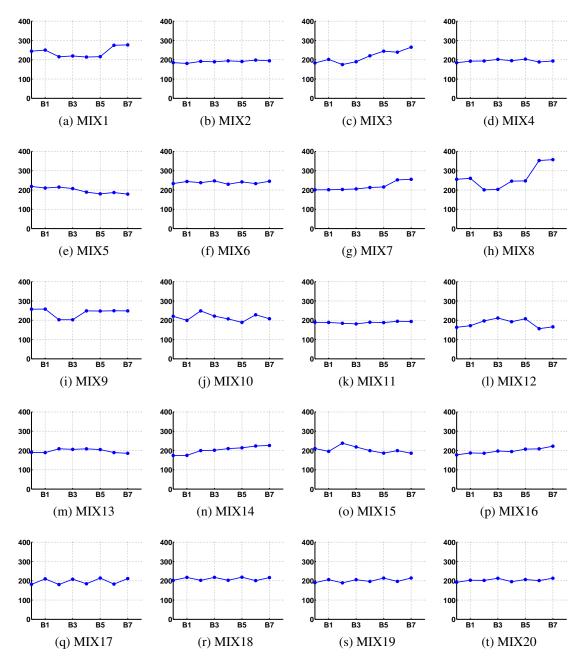

| 6.17 | ARMOR overhead for synthetic kernels with various access distribution. | 142 |

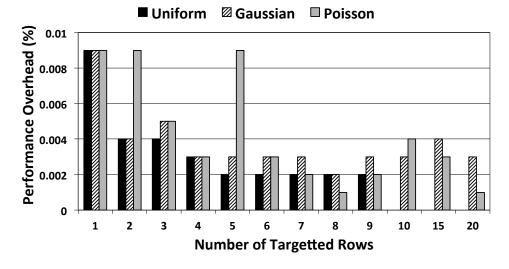

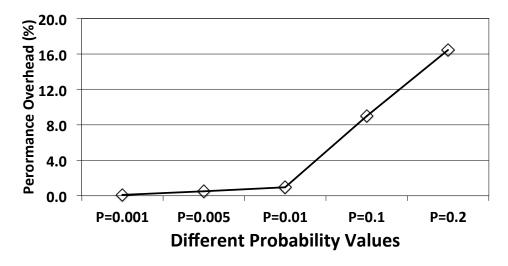

| 6.18 | PARA overhead for synthetic kernels.                                   | 143 |

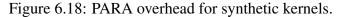

| 6.19 | PARA miss-rate for synthetic kernels.                                  | 143 |

| 6.20 | Performance overhead of ARMOR and PARA for multithreaded work-         |     |

|      | load mixes.                                                            | 144 |

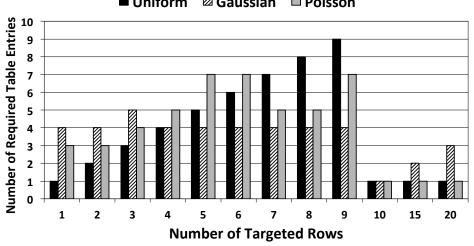

| 6.21 | The required number of table entries to detect the possible row-hammer |     |

|      | errors                                                                 | 144 |

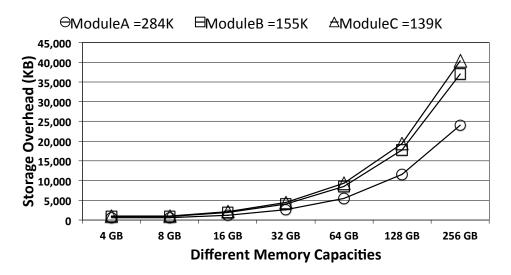

| 6.22 | Storage overhead for different memory capacities                       | 145 |

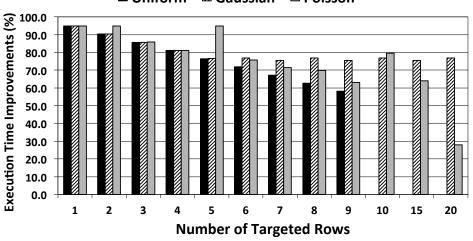

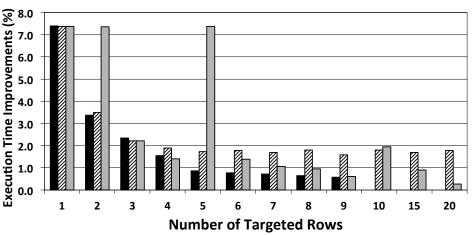

| 6.23 | Execution time improvements considering buffering entire row           | 146 |

| 6.24 | Execution time improvements considering buffering cache lines          | 146 |

| 7.1  | An overview of the adaptive and baseline memory controllers            | 151 |

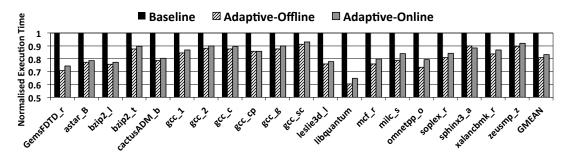

| 7.2  | Execution time comparison between the adaptive and the baseline mem-   |     |

|      | ory controller (normalised to the baseline execution time)             | 152 |

| 7.3  | The profiled execution time for the baseline memory controller         | 153 |

| 7.4  | The profiled execution time for the adaptive memory controller         | 154 |

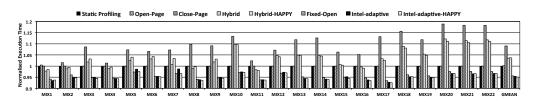

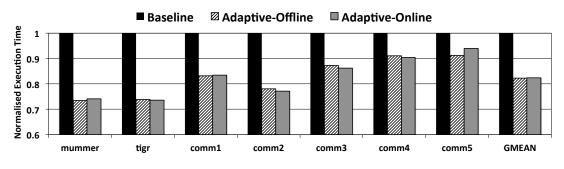

| 7.5  | Final performance improvement achieved for BIOBENCH and COM-           |     |

|      | MERCIAL benchmark suites.                                              | 154 |

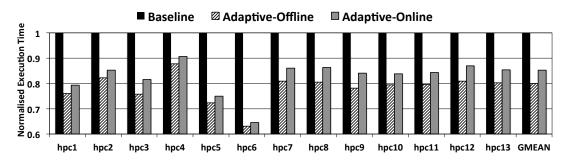

| 7.6  | Final performance improvement achieved for HPC benchmarks              | 155 |

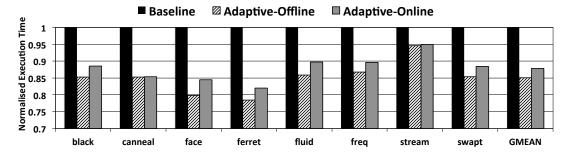

| 7.7  | Final performance improvement achieved for PARSEC benchmark suite.     | 155 |

| 7.8  | Final performance improvement achieved for SPEC benchmark suite.       | 155 |

| 7.9  | Implementation cost comparison between the baseline and the adaptive   |     |

|      | memory controller                                                      | 156 |

| 7.10 | The implementation cost of the adaptive memory controller profiled     |     |

|      | base on the cost of HAPPY, DReAM and ARMOR                             | 157 |

| 9.1  | ARMOR logo                                                             | 165 |

## Acronyms

- AAI Average Activation Intervals. 136

- ARMOR A Run-time Memory hot-row detectOR. 15

- DCA Dynamic Counter Allocator. 126

- **DIMM** Dual In-line Memory Module. 26

- **DRAM** Dynamic Random Access Memory. 14

- DReAM Dynamic Re-arrangement of Address Mapping. 15

- EAMS Estimated Address-Mapping Scheme. 95

- ECC Error Correcting Codes. 42

- FCFS First Come First Served. 41

- FPGAs Field-Programmable Gate Arrays. 14

- FR-FCFS First Ready First Come First Served. 41

- **GMEAN** Geometric Mean. 70

- GPUs Graphics Processing Units. 14

- HAPPY Hybrid Address-based Page PolicY. 14

- HMC Hybrid-Memory Cubes. 22

- HTW Hot Time Window. 125

- **IPC** Instruction Per Clock cycle. 53

JEDEC Joint Electron Device Engineering Council. 20

LLC Last-Level Cache. 26

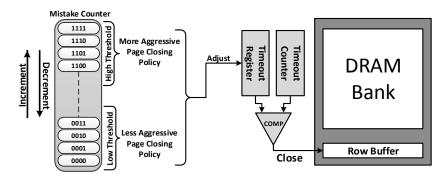

MC Mistake Counter. 63

MF Memory Footprint. 68

MPKI LLC Misses Per Kilo Instructions. 50

MSC Memory Channel Storage. 94

MT Migration Table. 96

NaCl Native Client. 119

PAMS Pre-defined Address-Mapping Scheme. 95

PARA Probabilistic Adjacent Row Activation. 123

PCM Phase-Changed Memory. 46

**RI** Refresh Interval. 124

ROI Region Of Interest. 93

SDRAM Synchronous Dynamic Random Access Memory. 37

SKG Synthetic Kernel Generator. 49

**ST** Swap Table. 96

TC Timeout Counter. 63

TR Timeout Register. 63

TRR Target Row Refresh. 46

TSRF Time-based Shift Register Filter. 126

TSV Through-Silicon Via. 46

USIMM Utah Simulated Memory Module. 51

## Abstract

## WORKLOAD-ADAPTATION IN MEMORY CONTROLLERS Mohsen Ghasempour A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy, 2015

Advanced development in processor design, increasing the heterogeneity of computer system, by involving Graphics Processing Units (GPUs), Field-Programmable Gate Arrays (FPGAs) and custom accelerators, and increasing the number of cores and threads in such systems puts extra pressure on the main memory, demanding a higher performance. Current computing trends are putting ever more pressure on main memory. In modern computer systems, this is generally Dynamic Random Access Memory (DRAM) which consists of a multi-level access hierarchy (e.g. Rank, Bank, Row etc.). This heterogeneity of structure implies different access latencies (and power consumption), resulting in performance differences according to memory access patterns. DRAM controllers manage access and satisfy the timing constraints and now employ complex scheduling and prediction algorithms to mitigate the effect on performance. This complexity can limit the scalability of a controller with the size of memory, while maintaining performance. The focus of this PhD thesis is to improve performance, reliability and scalability (with respect to memory size) of DRAM controllers. To this end, it covers three significant contributors to the performance and reliability of a memory controller: 'Address Mapping', 'Page Closure Policies' and 'Reliability Monitoring'. A detailed DRAM simulator is used as an evaluation platform throughout this work. The following contributions are presented in this thesis.

**Hybrid Address-based Page PolicY (HAPPY)**: Memory controllers have used static page-closure policies to decide whether a row should be left open (*open-page policy*) or closed immediately (*close-page policy*) after use. The appropriate choice can reduce the average memory latency. Since access patterns are dynamic, static page policies cannot guarantee to deliver optimum execution time. *Hybrid* page policies can cover dynamic scenarios and are now implemented in state-of-the-art processors. These switch between open-page and close-page policies by monitoring the access

pattern of row hits/conflicts and predicting future behaviour. Unfortunately, as the size of DRAM memory increases, fine-grain tracking and analysis of accesses does not remain practical. HAPPY proposes a compact, memory address-based encoding technique which can maintain or improve page closure predictor performance while reducing the hardware overhead. As a case study, HAPPY is integrated, with a state-of-the-art monitor – the Intel-adaptive open-page policy predictor employed by the Intel Xeon X5650 – and a traditional Hybrid page policy. The experimental results show that using the HAPPY encoding applied to the Intel-adaptive page closure policy can reduce the hardware overhead by  $5 \times$  for the evaluated 64 GB memory (up to  $40 \times$  for a 512 GB memory) while maintaining the prediction accuracy.

**Dynamic Re-arrangement of Address Mapping (DReAM)**: The initial location of data in DRAMs is determined and controlled by the 'address-mapping' and even modern memory controllers use a fixed and runtime-agnostic address-mapping. On the other hand, the memory access pattern seen at the memory interface level will be dynamically changed at run-time. This dynamic nature of memory access pattern and the fixed behaviour of address mapping process in DRAM controllers, implied by using a fixed address-mapping scheme, means that DRAM performance cannot be exploited efficiently. DReAM is a novel hardware technique that can detect a workload-specific address mapping at run-time based on the application access pattern. The experimental results show that DReAM outperforms the best evaluated baseline address mapping by 5%, on average, and up to 28% across all the workloads.

A Run-time Memory hot-row detectOR (ARMOR): DRAM needs refreshing to avoid data loss. Data can also be corrupted within a refresh interval by crosstalk caused by repeated accesses to neighbouring rows; this is the *row hammer* effect and is perceived as a potentially serious reliability and security threat. ARMOR is a novel technique which improves memory reliability by detecting which rows are potentially being "hammered" within the memory controller, which can then insert extra refresh operations. It can detect (and thus prevent) row hammer errors with minimal execution time overhead and hardware requirements. Alternatively by adding buffers inside the memory controller to cache such hammered rows, execution times are reduced with small hardware costs. The ARMOR technique is now the basis of a patent applicant and under process for commercial exploitation.

As a final step of this PhD thesis, an adaptive memory controller was developed integrating HAPPY, DReAM and ARMOR into a standard memory controller. The performance and the implementation cost of such an adaptive memory controller were compared against a state-of-the-art memory controller, as a baseline. The experimental results show that the adaptive memory controller outperforms the baseline, on average by 18%, and up to 35% for some workloads, while requiring around 6 KB-900 KB more storage than the baseline to support a wide range of memory sizes (from 4 GB up to 512 GB).

# Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?DocID= 487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses

## Acknowledgements

First and foremost, I would like to thank my supervisors, Dr. Mikel Luján and Dr. Jim Garside, for their mentorship, dedication, and support throughout my PhD study. Mikel has not only been a constant source of excellent, technically sound advice, but also a joy to work with. He has always been a great source of motivation and my PhD study would not be possible without his financial and educational support. Jim has always been patient and a supportive supervisor spending a significant amount of time and effort supervising me. His technical advice improved my research quality and his excellent comments and feedback helped me improving my writing significantly.

I have learned a lot from my fellow graduate students, friends and colleagues at Advanced Processor Technologies (APT) group in the school of computer science at The University of Manchester. Specially, I would like to thank John Mawer for his excellent technical comments and feedback on my ideas. Also, I would like to thank him for accepting to be one of my thesis readers and appreciate his feedback to improve the content of this PhD thesis. I want to thank my collaborator Dr. Aamer Jaleel, principal research scientist at Nvidia, whose advice had an important role to develop the evaluation methodology of this PhD thesis. I would like to thank Professor Stephen Furber and Professor George Constantinides for taking the time to be my thesis examiners.

On a more personal note, I would like to thank my family in IRAN for their unwavering support and encouragement. I would like to thank my parents for their support, both emotionally and financially, and encouraging me to pursue a PhD. Finally, I want to thank my wife, Farideh, for her love, support, patience and faith. Finishing this PhD thesis was not possible without her unwavering support and encouragement.

# Chapter 1

# Introduction

At least as early as in 1995 researchers have postulated that the performance improvement of computers will cease 'soon' [WM95]. They reasoned that, at some point, processors would become much faster than memory and thus the program execution time would depend on the memory performance and how fast main memory can feed the data required by a processor. They referred to this situation as "hitting the memory wall" [WM95].

For decades, continuous advancement in device technology has improved processors' performance by increasing the clock frequency. However, as Moore's law is coming to an end, the scaling of transistors is no longer a reliable solution for further improvements of future processors. Therefore, the processor industry shifted to multicore systems in the past decade to take advantage of thread-level parallelism to keep the efficiency of modern processors up.

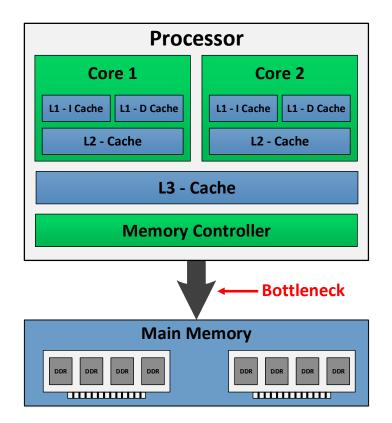

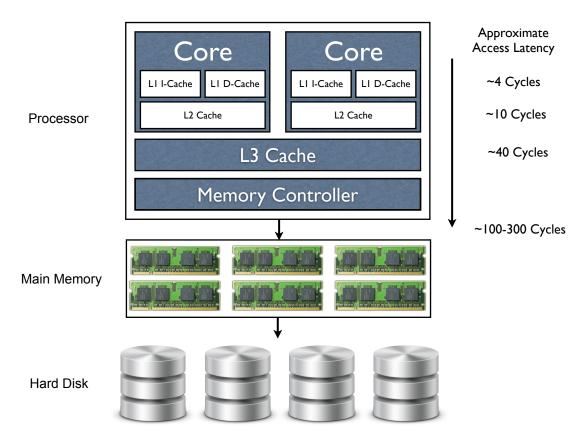

Nowadays, as was postulated, system performance is not normally processor-bound. In this situation, the main bottleneck is shifted toward the memory hierarchy and especially the main memory. Figure 1.1 presents a typical memory hierarchy. Typically, the main memory is populated with DRAM modules that, in general, operate at a lower frequency than the processor. In this situation, it is crucial to utilise the maximum bandwidth offered by DRAMs to minimise the degradation of overall system performance.

DRAM stands for Dynamic RAM (Random Accessed Memory). RAM refers to a memory device that allows a data block to be read or written in almost the same amount of time regardless of the address of the block. Despite this, a DRAM is not truly randomly accessible. Depending on the order of different memory accesses to the data blocks, the access latency might vary significantly. Due to the internal structure

Figure 1.1: Memory hierarchy.

of DRAMs, described in Chapter 2, the performance of DRAMs is dependent on the application behaviour and memory access patterns. Moreover, the high level of parallelism in multicore systems increases the level of randomness of the memory access patterns that makes the DRAMs' performance even more unpredictable.

The sensitivity of DRAMs to memory access patterns at run-time affects all the efficiency aspects of the memory system from *Performance* to *Power* including *Reliability*. In the next section, memory challenges are discussed in more detail.

### **1.1 Memory Challenges**

At a high level, a DRAM device is organised in a 3D structure consisting of multiple Banks, Rows and Columns (Figure 1.2). To access a DRAM module specific timing constraints complying with Joint Electron Device Engineering Council (JEDEC) standard [SPE09] have to be respected. For instance, two consecutive accesses to different rows within the same bank (i.e. *Page Miss*) must be delayed allowing DRAMs to close the previous opened row and activate a new row. On the other hand, consecutive accesses to the same row within the bank delivers lower access latency than the previous example since the target row is prepared to be accessed by the first memory access (i.e. *Page Hit*).

Figure 1.2: Internal structure of a DRAM device.

DRAM controllers are devised to take care of these timing constraints while issuing desired commands (e.g. read/write commands) to a DRAM module. However, the sensitivity of DRAM modules to the memory access pattern has demanded a memory controller with more capabilities than traditional memory controllers. Thus, memory controllers have started to employ algorithms to predict memory access patterns and re-order memory requests to minimise the memory access latency.

Performance, power and reliability of DRAMs depend upon the application runtime behaviour (order of memory requests, timing interval between each request etc.). For instance, as will be discussed in chapter 2, *Page Misses* are one of the most harmful phenomena that affect the efficiency aspects of a DRAM. The most obvious drawback of a Page-Miss is increasing the memory latency, and consequently, degrading the performance. Also, a Page-Miss increases the power consumption as it imposes extra DRAM operations, precharging the previously opened row and activating a new row. Moreover, depending on the occurrence pattern of Page-Misses, they might affect the reliability of DRAMs by corrupting the data in the specific DRAM cells (i.e. *the RowHammer* phenomenon [KDK<sup>+</sup>14]). Considering this phenomenon in DRAMs and its dependence on the memory access behaviour, the focus of designing modern memory controllers is to detect and reduce the possibility of page-miss occurrence at run time. Although it is not possible to know the future access pattern, it is possible to make a prediction based on past behaviour. In principle, gathering more (statistical) information may enable better prediction. A complete access trace over the size of DRAM is infeasible as it would require storage of the same order as the memory itself. The problem is to discern what can be collected at a sensible cost – in energy and processor die area – to give 'adequate' prediction accuracy.

Probably the most challenging issue while designing a memory controller is considering that the memory controller is a part of the processor die area. This means that increasing the complexity of memory controllers will increase the overall processor area which may not be economical. This constrains the accuracy and scalability of scheduling and prediction algorithm implemented. On the other hand, the scalability of emerging modern memory technologies such as DDR4 [Mic14b, Mic14a, LCC<sup>+</sup>07, SNS<sup>+</sup>13] or Hybrid-Memory Cubes (HMC) [Mic14d, Mic14e, Paw11] demands new designs of future memory controllers. For instance, HMC, introduced by Micron, is a 3D stacked multibank DRAM that provides  $15\times$  more bandwidth than conventional DDR3 modules and requires 70% less energy and 90% less space than existing modern memory technologies [Mic14d]. Moreover, the 3D structure of this memory system makes it extremely scalable in comparison with normal DRAM systems.

Overall, considering the demands for a more scalable and efficient memory controller on future computer architectures motivated this PhD thesis to improve the performance of key components of a traditional memory controller.

### **1.2** Contributions

The focus of this PhD thesis is to improve the workload adaptivity of DRAM controllers to improve the *Performance* and *Reliability* of memory systems. To this end, a set of contributions is presented to redesign key components of a traditional DRAM controller. DRAM controllers leverage various page closure policy predictors (to leave a page open or close a page in advance) to mitigate the performance and power degradation imposed by *Page-Misses*. However, designing an efficient page closure policy predictor requires extra cost of implementation (i.e. area and power) and increases the complexity of DRAM controllers. This thesis proposes an efficient and *scalable* encoding-based technique which can improve the performance of DRAMs' page closure predictors with a lower cost of implementation in comparison with state-of-the-art techniques. As a case study, HAPPY was integrated with a state-of-the-art monitor – the Intel-adaptive open-page policy predictor employed by the Intel Xeon X5650 CPU [Int] – and a traditional Hybrid page policy. These are evaluated intensively across wide range of workload mixes consisting of single-thread and multi-thread applications. The experimental results show that using the HAPPY encoding applied to the Intel-adaptive page policy can reduce the hardware cost by  $5\times$  for the evaluated 64 GB memory (up to  $40\times$  for a 512 GB memory) while maintaining the prediction accuracy. Effectively, HAPPY can achieve a similar (or slightly better) performance to existing high performance industry and academic predictors at much smaller hardware overhead.

Data placement in DRAMs, determined by how the physical addresses are mapped across the 3D space of channel, bank and row, has a significant effect on the performance. Memory controllers use fixed and runtime-agnostic address mappings to translate the physical address requested by a processor to the internal structure of DRAMs. However, a fixed address mapping scheme cannot guarantee to deliver optimum data placement for a range of workloads. This thesis presents DReAM (Dynamic Rearrangement of Address Mapping), a novel hardware technique based on approximating the entropy of each memory address bit for a set of memory requests, to generate a workload specific address mapping at run-time. To re-arrange the address mapping dynamically at run-time DReAM needs to support the online-data migration imposed by changing the address-mapping scheme. DReAM investigates different hardware-based solutions for data-migration with different levels of complication. The proposed solutions were evaluated over a wide range of mapping-sensitive and mapping-insensitive workload mixes. The experimental results show that the on-the-fly detected workload specific address mapping scheme produced by DReAM improves the performance of the memory system in comparison with the best static baseline address mapping evaluated in this PhD thesis. Overall, DReAM outperforms the permutation-based addressmapping scheme (the best evaluated baseline) by 5%, on average, and up to 28% across all the workloads. DReAM is complementary to existing schedulers in memory controllers and is the first on-the-fly mechanism capable of generating workload specific address-mappings without requiring the running applications to stop.

Due to the volatile nature of DRAM memory controllers need to issue refresh commands at specific time intervals to avoid losing stored data. Another not so well known means of losing or corrupting stored data within a refresh interval is to have a sequence of memory requests requiring a DRAM row to be activated very frequently. This can corrupt the data in the rows that are physically adjacent to the accessed row; the *Row*

#### 1.3. THESIS ORGANISATION

*Hammer effect.* The data corruption is due to electrical disturbance and segmented memory or page protection cannot guarantee isolation of two or more programs when they are using memory mapped to adjacent physical rows. Moreover, ECC modules are not very efficient in this situation since they cannot detect multi-bit errors. This thesis proposes ARMOR which is a novel hardware technique that improves memory controllers by detecting which specific rows are at risk of being "hammered" without interfering with the processors. In addition, ARMOR can detect and prevent row hammer errors with minimal performance overhead and hardware requirements. The experimental results over a wide range of memory intensive workloads show that AR-MOR incurs virtually no execution time overhead for the workloads. When buffers are added to the memory controller to capture such hammered rows, the execution times can also be improved with small hardware costs.

Finally, this thesis integrates *HAPPY*, *DReAM* and *ARMOR* as a part of a uniform system to develop an 'adaptive' memory controller. Figure 1.3 presents a high level overview of such a memory controller. The performance of this adaptive memory controller is compared against a state-of-the-art memory controller configured with the best parameters achieved in each Chapter.

Figure 1.3: An abstract view of the developed adaptive memory controller.

### **1.3** Thesis Organisation

The rest of this thesis is organised as follows. Chapter 2 provides general background and motivation of this PhD thesis. Chapter 3 presents the experimental methodology. The three techniques outlined in Section 1.2 each have a chapter dedicated to them; these are largely intended to be standalone studies of each technique. Chapter 4 presents HAPPY, a hybrid address-based page closure policy to mitigate the effect of *Page-Misses* in DRAMs. Chapter 5 proposes DReAM, a highly efficient technique that dynamically changes the address-mapping scheme of DRAMs at run-time. Chapter 6 describes ARMOR, an accurate hot-row detector scheme to improve the reliability in DRAMs. Chapter 7 integrates HAPPY, DReAM and ARMOR to develop an adaptive memory controller and investigates the overall performance improvement of the memory system taking advantage of all three techniques proposed. Finally, Chapter 8, concludes this PhD thesis and discusses future work.

# **Chapter 2**

# **Background and Motivation**

### 2.1 Overview of DRAMs

DRAMs play a significant role as the main memory of modern computer architectures. Performance, power and reliability of computer systems are highly affected by DRAM architectures. A typical DRAM module, as can be found in a general purpose computer, is pictured in figure 2.1. More specifically, this figure depicts a Dual In-line Memory Module (DIMM) that consists of multiple DRAM devices (i.e. black rectangles) plus corresponding circuitry. In general, due to the internal structure of DRAM devices, the performance of these memory systems depends on the application behaviour. This means that, depending on the internal state of DRAMs and the memory access pattern, the response time of the overall memory system can vary significantly. This phenomenon makes the overall performance of computer systems unpredictable.

Figure 2.1: A memory module [eTe14].

Figure 2.2 presents a high level overview of a typical computer systems' memory hierarchy. Typically, modern processors consist of multiple cores. Each core has its own private caches (in figure 2.2 L1 and L2 are private) and shares the Last-Level

Cache (LLC) with other cores in the system. The next level of memory hierarchy is the main memory consisting of DRAM modules which are connected to the processor through a *Memory Controller*.

This figure provides some insight into the memory latency expected for different levels of memory hierarchy. Typically, accessing off-chip memory (DRAMs) is a very expensive process due to the high latency of IOs. In this situation, the dynamic behaviour of the DRAM modules can impose an extra latency on the off-chip memory accesses which degrades the overall system performance.

Figure 2.2: A typical computer system memory hierarchy.

To get a better insight into the main reason behind this dynamic behaviour of DRAM systems, the internal organisation of DRAMs will be discussed in more detail in the following sections.

## 2.2 DRAMs: Basic Circuits and Architecture

In this section, basic DRAM architecture and organisation will be discussed in detail.

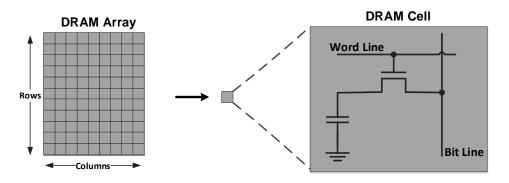

#### 2.2.1 DRAM Cell

A DRAM cell is the smallest storage unit of a DRAM device. A schematic representation is shown in figure 2.3. It consists of a capacitor connected to a bit-line via a transistor, which is controlled by a word-line. When the word-line is asserted the capacitor is connected to the bit-line. If the bit-line is driven when word-line is asserted then the value will be stored on the capacitor, a write operation.

To read the cell the bit-line is first precharged, by changing the line to a known driver voltage and then disconnecting the driver. When the word line is asserted if both the bit-line and the capacitor are at the same voltage then the bit-line potential will remain unchanged; if, however, they are different charge sharing will occur resulting in a detectable change of voltage on the bit-line. The presence or absence of this change indicates the state of the bit. It should be noted that the charge sharing will also cause the capacitor's voltage to change, so after reading, the voltage has to be restored by driving the cell back to its original value. Furthermore, over time the charge on the capacitor will leak away, so it needs to be refreshed regularly hence the name dynamic memory.

Figure 2.3: A basic DRAM cell structure.

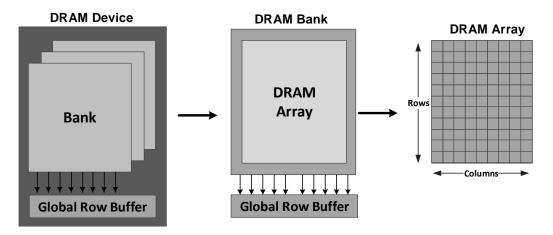

#### 2.2.2 DRAM Array

A DRAM array consists of DRAM cells populated in 'Rows' and 'Columns'. Figure 2.4 presents an abstract structure of a DRAM array. As this figure depicts, wordlines are connected to all the transistors located in a horizontal line (a DRAM Row). This means that raising the word-line will activate all the transistors in one row. Similarly, bit-lines are connected to all the DRAM cells located in a vertical line (a DRAM Column). This implies that, at any given time, only one row can be activated to avoid collision of capacitors' charges. Rows and Columns are separately addressable and some physical address bits are used to address a specific row – and others a column – within a DRAM device. In the literature a DRAM's row may also be referred to as a *DRAM Page*.

Figure 2.4: A basic DRAM array structure.

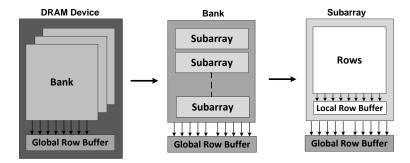

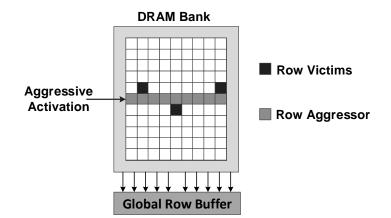

#### 2.2.3 DRAM Bank

A DRAM Bank comprises a DRAM array plus a Sense Amplifier (or Row Buffer). During normal DRAM's operation, a row and column decoder are used to decode the accessed row and column addresses to internal row and column IDs. In the first step, a DRAM device will bring the entire accessed row to the sense amplifier which amplifies the signals and holds the row's state in a latch. Then the desired data can be accessed by decoding the column address and a read or write operation can be carried out. Figure 2.5 depicts an overview of a DRAM bank organisation. Typically, DRAM banks have a relatively narrow data bus (e.g. 4-16 bit) which means for each read/write request only part of the requested data can be provided by each bank. This is because of implementation limitations and challenges such as maximum current limitation etc.

Moreover, since accesses from the sense amplifier are faster than from the DRAM array, it is usual to burst data serially from the sense amplifier for a specific size such as a cache-line size. This improves the bandwidth but mandates that adjacent addresses are in the same row.

Figure 2.5: A DRAM bank structure.

#### 2.2.4 DRAM Device

A DRAM Device (black rectangle in figure 2.1) comprises multiple DRAM banks which can be accessed in parallel. However, since the existing banks within a DRAM device share resources such as the communication bus, address decoders etc. only one bank at a time can transfer data to the output world. This means that the transfer rate of each device is limited to the transfer rate of a DRAM bank which, as discussed, is about 4-16 bit wide (depending on DRAM model).

### 2.3 DRAMs: Memory Access Protocol

To access a DRAM a set of processes, manifested by particular commands, must be used. Each of these has its own timing constraints. Table 2.1 presents some of these timing parameters [JNW10]. In general, a combination of a specific set of commands along with the timing constraints depicted in Table 2.1 construct the DRAM access protocol which will be discussed in this section.

| Timing Parameters  | Description                                                              |

|--------------------|--------------------------------------------------------------------------|

| T <sub>Burst</sub> | Data burst duration. The time period that a data burst occu-             |

|                    | pies on the data bus. Typically 4 or 8 beats of data. In DDR             |

|                    | SDRAM, 4 beats occupy 2 full clock cycles.                               |

| T <sub>CAS</sub>   | Column Access Strobe latency. The time interval between                  |

|                    | column access command and the start of data return by the                |

|                    | DRAM device(s). Also known as T <sub>CL</sub> .                          |

| T <sub>CCD</sub>   | Column-to-Column Delay. The minimum column com-                          |

|                    | mand timing, determined by internal burst (prefetch) length.             |

| T <sub>CMD</sub>   | Command transport duration. The time period that a com-                  |

|                    | mand occupies on the command bus as it is transported from               |

|                    | the DRAM controller to the DRAM devices.                                 |

| T <sub>CWD</sub>   | Column Write Delay. The time interval between issuance of                |

|                    | the column-write command and placement of the first data                 |

|                    | on the data bus by the DRAM controller.                                  |

| T <sub>FAW</sub>   | Four (row) bank Activation Window. A rolling time-frame                  |

|                    | in which a maximum of four-bank activation can be en-                    |

|                    | gaged. Limits peak current profile in DDR2 and DDR3 de-                  |

|                    | vices with more than 4 banks.                                            |

| T <sub>RAS</sub>   | Row Access Strobe. The time interval between row access                  |

|                    | command and data restoration in a DRAM array. A DRAM                     |

|                    | bank cannot be precharged until at least T <sub>RAS</sub> time after the |

|                    | previous bank activation.                                                |

| T <sub>RC</sub>    | Row Cycle. The minimum time interval between accesses                    |

|                    | to different rows in a bank.                                             |

| T <sub>RCD</sub>   | Row to Column command Delay. The time interval between                   |

|                    | row access and data being ready at sense amplifiers.                     |

| T <sub>RFC</sub>   | Refresh Cycle time. The minimum time interval between                    |

|                    | Refresh and Activation commands.                                         |

| T <sub>RP</sub>    | Row Precharge. The time interval that it takes for a DRAM                |

|                    | array to be precharged for another row access.                           |

| T <sub>RRD</sub>   | Row activation to Row activation Delay. The minimum time                 |

|                    | interval between two row activation commands to the same                 |

|                    | DRAM device. Limits peak current profile.                                |

| T <sub>RTP</sub>   | Read to Precharge. The time interval between a read and a                |

|                    | precharge command.                                                       |

| T <sub>WR</sub>    | Write Recovery time. The minimum time interval between                   |

|                    | the end of a write data burst and the start of a precharge               |

|                    | command. Allows sense amplifiers to restore data to cells.               |

| T <sub>WTR</sub>   | Write To Read delay time. The minimum time interval be-                  |

|                    | tween the end of a write data burst and the start of a column-           |

|                    | read command. Allows I/O gating to overdrive sense ampli-                |

|                    | fiers before the read command starts.                                    |

Table 2.1: Summary timing constraints of DRAM [JNW10].

Figure 2.6: A DRAM device structure.

#### 2.3.1 Basic DRAM Commands

In this section, five basic and crucial DRAM commands will be discussed; *Row Access*, *Column-Read*, *Column-Write*, *Precharge* and *Refresh*.

#### **Row Access Command**

This is an initialisation command that needs to be issued to move data from the DRAM's cells in the DRAM array to the sense amplifiers (Row-Buffer) and to restore data back to the DRAM array (as part of the same command). It is also known as an *Activa-tion Command*, which is accompanied by a subset of the address bits to select the row. Considering the main operation of this command, there are two main timing parameters associated with it: *Row Column Delay* ( $T_{RCD}$ ) and *Row Access Strobe latency* ( $T_{RAS}$ ).  $T_{RCD}$  is the time it takes to move data from DRAM cells to the sense amplifier. After  $T_{RCD}$  the data is ready for read and write operations. In this situation, although data is ready to access in the Row-Buffer it is not fully restored back to the DRAM cells.  $T_{RAS}$  specifies the delay required to restore data to the DRAM array from the row access command. The sense amplifiers cannot be precharged until  $T_{RAS}$  has passed. Figure 2.7 presents the associated timing parameters to the row access command.

Figure 2.7: Row access command timing.

#### **Column-Read Command**

This command transfers selected data from the sense amplifiers over the data bus to the memory controller. There are three timing parameters associated with this command; *Column Access Strobe latency* ( $T_{CAS}$ ), *Column-to-Column Delay* ( $T_{CCD}$ ) and *Data burst duration* ( $T_{Burst}$ ).  $T_{CAS}$ , also known as  $T_{CL}$ , is the time it takes after a column read command is issued for the DRAM device to place data on the data bus. Internally, DRAM devices move data in a short and continuous burst. The duration of these bursts is called  $T_{CCD}$ . Similarly, the data will be placed on the data bus in bursts but with a longer burst period which is called  $T_{Burst}$ . Figure 2.8 depicts the associated timing parameters to the column read command.

Figure 2.8: Column read command timing.

#### **Column-Write Command**

The column-write command is fairly similar to the column-read command with the difference that the direction of data movement is reversed. This command moves data from the memory controller to the sense amplifier. One specific timing parameter associated with this command is *Column Write Delay* ( $T_{CWD}$ ). This specifies the time between issuance of a column-write command and placing of the data on the data bus

by the memory controller. Moreover, there are two other timing parameters that correspond to the column write command in specific situations; *Write Recovery* ( $T_{WR}$ ) and *Write-To-Read* turnaround ( $T_{WTR}$ ). The  $T_{WR}$  is the time it takes to transfer the written data to the DRAM array. This timing must be respected in the case of a precharge command that follows the column write command. In addition, since both read and write operation use a common data bus there is a timing constraint that must be taken into consideration when changing the direction of the I/Os.  $T_{WTR}$  is the time that it takes to release the I/O resources by the write command. This timing must be respected in the case of a read command that follows the write command. Figure 2.9 shows the corresponding timing parameters to the column write command.

Figure 2.9: Column write command timing.

#### **Precharge Command**

It has been discussed that each bank within a DRAM device has only one Row-Buffer and it has been explained that the first step to access a row is the activation process that moves data from DRAM array to the row-buffer. Thus, the located data in the rowbuffer is ready to perform a read/write operation. In this situation, accessing a different row within the same bank is not possible since the row-buffer is already occupied. The *Precharge Command* solves this problem by resetting the row-buffer and corresponding bit-lines. This prepares them for another row-access command within the same bank. The associated timing parameter for this command is called *Row Precharge* (T<sub>RP</sub>). T<sub>RP</sub> is the time it takes to precharge the row-buffer and corresponding bit-lines properly after the assertion of the precharge command. Considering the T<sub>RP</sub> described here and the *Row Access Strobe latency* (T<sub>RAS</sub>) described before, a new timing parameter can be defined as *Row Cycle* ( $T_{RC} = T_{RAS} + T_{RP}$ ) which is the timing constraint of accessing two different rows within the same bank. Figure 2.10 presents the timing parameters associated to the precharged command.

Figure 2.10: Precharge command timing.

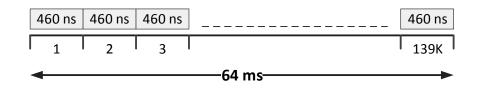

#### **Refresh Command**

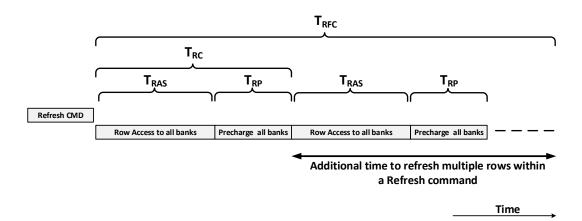

Due to the dynamic nature of DRAMs and considering the basic structure of a DRAM cell presented in figure 2.3, the electrical storage in DRAM cells is not persistent. It means that a DRAM cell will lose its charge, and as a result its stored value, gradually over time. Therefore, to maintain data integrity, the data values must be read and restored to their original value periodically. The purpose of the *Refresh Command* in DRAMs is to perform this periodic read out and restoration of data. In theory, the Refresh process can guarantee data integrity in DRAMs if the time interval of refresh command issuance is shorter than the minimum retention time of the DRAM cell's retention time is around *64 ms*. Thus, the memory controller must issue a refresh command to every row at least every *64 ms*. The associated timing parameter to the refresh command and the next activation to the same row. An overview of the timing parameters associated with the refresh command is presented in figure 2.11.

#### 2.3.2 Row-Buffer Access Classification

Row-Buffer access classifications affect many aspects of a memory system including Performance, Power and Reliability. Considering the basic operation of DRAMs and the associated access protocol discussed in the previous section, a memory access to a DRAM device can be classified in three different categories; *Page-Hit*, *Page-Miss* and

Figure 2.11: Refresh command timing.

*Page-Empty*. The memory latency of a specific memory access can be significantly different depending on the category that the memory request falls into. In the following, each category and its associated timing parameters will be discussed.

#### **Page-Empty**

To perform a read or write operation in a DRAM device the target row must be activated (moved to the Row-Buffer) first. In this scenario if the Row-Buffer is empty the accessed row will be activated and ready for a read/write operation after  $T_{RCD}$ . This is called "Page-Empty".

#### Page-Hit

Considering two memory requests to the same row within the same bank, after the first memory request the target row is open in the Row-Buffer. Thus, the second memory request does not need to wait for  $T_{RCD}$  and the read/write operation can be done immediately. This is called a "Page-Hit" which delivers the lowest access latency across the Row-Buffer access classifications.

#### **Page-Miss**

Considering two consecutive memory requests to different rows within the same bank, since after the first access the Row-Buffer holds the previously target row then to access a new row the row buffer must first be precharged before the second row can be activated. This imposes an extra  $T_{RP}$  to the overall memory access latency. Moreover, the Row-Buffer cannot be precharged until the data is fully restored to the DRAM cells

(T<sub>RAS</sub>). Therefore,  $T_{\text{RC}} = T_{\text{RAS}} + T_{\text{RP}}$  is the memory latency of accessing different rows within the same bank. This is called a "Page-Miss" which imposes the highest access latency in a DRAM device.

### 2.4 DRAM vs SDRAM

Synchronous Dynamic Random Access Memory (SDRAM) is a version of DRAM. Traditional DRAM has an asynchronous interface which means that it responds to its control inputs as soon as they arrive. On the other hand, SDRAM has a synchronous interface with the processor clock cycle. SDRAM uses this clock to pipeline the incoming commands from processor. This means that the chip can accept new commands while processing the previous command. Therefore, this increases the throughput in comparison with an asynchronous DRAM.

## 2.5 DRAMs: Memory System Organisation

A basic overview of a DRAM device's internal structure was presented in the previous section. In this section, different organisations of a DRAM device that are currently used in memory systems will be discussed.

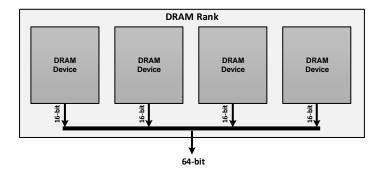

#### 2.5.1 DRAM Rank

It was mentioned that each DRAM device has a narrow data bus. Thus, to improve the performance of DRAM modules multiple DRAM devices work in parallel within a *Rank* to provide the bandwidth required by modern processors. Typically, a DRAM rank is designed to support 64-bit data for each read or write request. Furthermore, modern DRAM DDR3 memory systems are restricted to perform read or write operations in bursts (generally limited to a fixed burst size of 4 or 8 items). In this way for each read/write operation 64 bytes of data can be delivered by the DRAM module which is enough to fill a cache-line. Figure 2.12 presents an overview of a DRAM rank organisation with a 64-bit wide data bus.

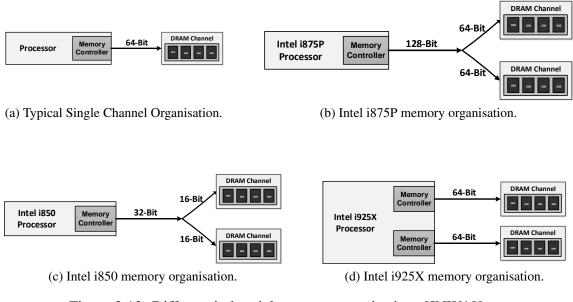

#### 2.5.2 DRAM Channel

A DRAM channel is the physical connection between a processor and the DRAM modules. Multiple DRAM modules, each of which can consist of 1 to 4 ranks, can

Figure 2.12: A DRAM rank structure.

be placed on a DRAM channel. A processor communicates with DRAM modules through a Memory Controller which will be discussed in detail in the next section. In general, each processor can support multiple memory controllers each of which can manage single or multiple memory channels. Figure 2.13 presents a few examples of existing memory organisations [JNW10]. Figure 2.13a shows a simple processor with one memory controller that manages only one channel. Figure 2.13b depicts the Intel i875P system controller that has one memory controller that manages two channels at the same time, each of which is 64-bit wide. Similarly, figure 2.13c presents the Intel i850 memory system where one memory controller handles two physical channels with narrower data width (i.e. 16-bit) than the Intel i875P. Figure 2.13d, shows the Intel i925X memory system that has two independent memory controllers each of which can manage different 64-bit wide channels. Having independent memory controllers increases the efficiency of the memory system since the memory pressure will be distributed.

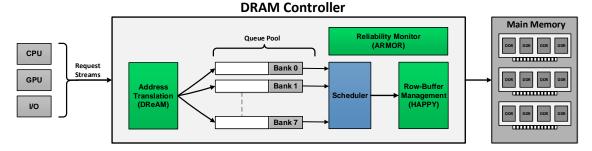

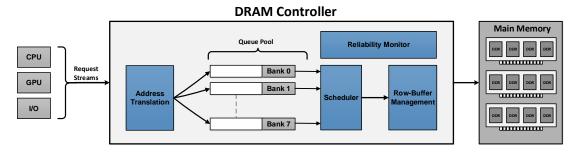

# 2.6 DRAM Memory Controller

The memory controller is the key component of a computer architecture that is in charge of handling communication between the processor and the main memory. In modern computer systems, the memory controller is implemented on the same silicon die as the processor to reduce the communication latency as much as possible. Since, in the multicore era, the main performance bottleneck has moved toward the memory system (rather than processors) the performance of DRAM controllers has become critical. In this section, a high level overview of a modern DRAM memory controller will be investigated and its key components will be analysed in detail. Figure 2.14 presents a abstract view of a DRAM memory controller. This figure is simplified to

Figure 2.13: Different industrial memory organisations [JNW10].

show only the main components of such a system.

Figure 2.14: An abstract view of a DRAM controller.

The main four components highlighted in figure 2.14 are described as follows.

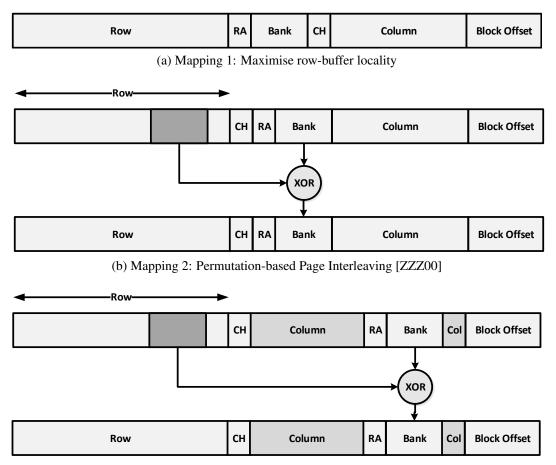

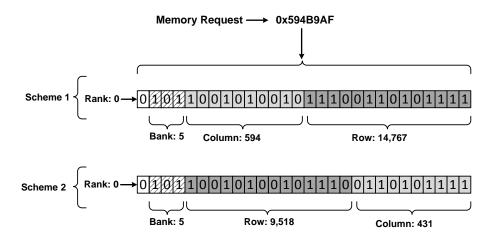

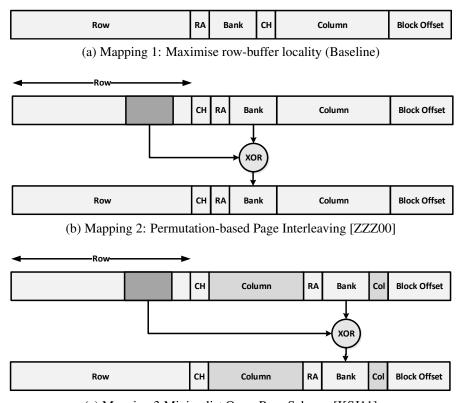

# 2.6.1 Address Mapping

The address mapping unit is one of the most important components of a DRAM controller and has a significant effect on the overall performance of the memory system. The first step to service a memory request is to decompose the physical address to the internal structure of the memory system. This process maps given physical address bits (e.g. 32 address bits) to their corresponding Channel, Rank, Bank, Row and Column indices of a given memory organisation. Typically, DRAMs use a *fixed* address-mapping scheme. Figure 2.15 presents an example of how a physical address

is divided to the corresponding DRAM internal structure using two different address mapping schemes.

Figure 2.15: Examples of address mapping using different schemes.

As presented in figure 2.15, an address-mapping scheme simply dictates which part of the physical address is used to address specific parts of DRAMs. Although, this process looks very simple, choosing different address mapping schemes can have a significant effect on the overall performance of a memory system. The rationale behind this is that the address translation process has a strong correlation with the data placement in the memory. Therefore, choosing one address-mapping scheme might distribute consecutive memory requests to different banks and choosing another address-mapping scheme might place consecutive memory requests to different rows within the same banks. In the first case, since the multiple banks can be accessed in parallel, the consecutive memory requests can be serviced in parallel but in the second scenario consecutive memory accesses to different rows within the same bank cause a large number of page-misses and, as a result, degrade the memory latency significantly. There are a few novel address-mapping schemes that have been proposed by other researchers in this area to mitigate page-misses [KSJ11, ZZZ00].

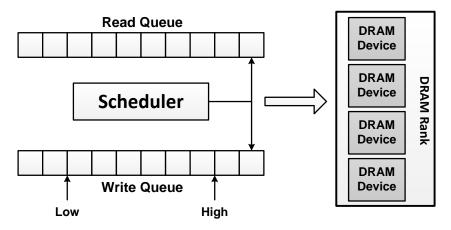

# 2.6.2 Command Scheduling

In the second phase, after the translation process, the translated memory requests will be placed in different request queues depending on their target bank. It has been discussed that to service a memory request multiple commands must be issued (e.g. *AC-TIVATION*, *READ/WRITE*, *PRECHARGE*, etc.). To take advantage of the maximum available parallelism in a memory system DRAM controllers employ a *Scheduler* to

re-order the issuable memory request from the request queues. The main aim of the scheduling process is to reduce the page-misses and to increase the page-hits in the system. Therefore, a scheduler can prioritise memory requests targetting the open row within a bank over those that target other rows within the same bank.

In general, there are two traditional scheduling algorithms called First Come First Served (FCFS) and First Ready First Come First Served (FR-FCFS). The FCFS algorithm schedules the memory requests according to their order of arrival. This delivers a poor level of parallelism. On the other hand, FR-FCFS scheduler scans the request queue and prioritises the memory request whose target destination is ready (i.e. memory request targetting an open row within a bank). In addition to the traditional scheduling algorithms, there has been a significant number of other novel algorithms developed to improve the performance of memory systems [EMF<sup>+</sup>11, KPMHB11, MM08, IFSK12, MKK<sup>+</sup>12, LWWX12].

#### 2.6.3 Row-Buffer Management

Considering the basic operation of DRAMs explained so far, accessing a row implies transferring the entire row to the row-buffer (sense amplifier). Thus, after performing the read or write operation a DRAM device can either keep data in the row-buffer or return the data to the original row. DRAM controllers employ techniques, collectively called the Row-Buffer Management Policy, to decide either to leave a row-buffer open or close it immediately after it has been accessed. This decision can have a significant effect on the access latency for the next memory request to the same bank. Typically, there are two traditional (static) Row-Buffer management policies that are used by DRAM controllers: Open-Page and Close-Page. A memory controller that employs an Open-Page policy leaves a page open after it has been accessed. This reduces the access latency of the next memory request to the same bank and the same row since the target row is open and there is no extra cost to opening it again (Page-Hit). This policy is desired for workloads with high-locality behaviour. On the other hand, a memory controller that employs the Close-Page policy closes a row immediately after it has been accessed. This reduces the access latency for the next memory request to a different row within the same bank since the row-buffer has been prepared (closed) in advanced for the new row to be activated. This page policy is desired for workloads with random memory access behaviour.

In addition to the static page closure policies, modern memory controllers also take advantage of Hybrid (Dynamic) page policies which are a combination of Open-Page and Close-Page policies. This type of policy, instead of using a fixed page closure policy, monitors the memory access pattern at run time and switches between static policies considering the locality and randomness of the memory accesses. Although, the idea of Hybrid page closure polices looks promising the main challenge is the compromising of the prediction accuracy and cost of implementation. There are a number of previously published works in this area [KSJ11, ANBD11, XAD09, SM05a, MC07].

# 2.6.4 Reliability Monitor

The performance of all the components described so far (i.e. Address-Mapping schemes, Schedulers and Row-Buffer management policies ) can all affect both the *Performance* and *Power* of the memory system. *Reliability* of memory systems is another crucial factor that must be taken into consideration when designing a computer architecture. Typically, DRAM controllers do not employ a standard standalone Reliability Monitor unit as is highlighted in figure 2.14. The highlighted block in this figure represents a combination of different fault tolerant techniques, such as Error Correcting Codes (ECC), that a DRAM controller implements to take care of reliability issues. Employing smaller memory technology makes DRAM cells more vulnerable to errors. Therefore, modern DRAM controllers employ more resources to implement different fault detection and correction techniques to overcome this issue.

# 2.7 Performance, Power and Reliability

In this section, considering the basic background on DRAM systems discussed so far, the potential performance and reliability improvement of DRAM-based memory systems will be investigated. Referring to Figure 2.14, it has been highlighted that there are a few critical component in a DRAM controller whose performance has a significant effect on the overall memory systems. In this section, the effect of these key component on the performance and reliability of the overall memory system will be discussed.

#### 2.7.1 Memory Access Pattern

DRAMs' performance, power and reliability are susceptible to the memory access pattern. Due to the heterogeneous nature of the internal structure of these memory systems, accessing different locations of a DRAM device imposes different latencies and energy consumptions on the overall memory system. In addition, following a specific access pattern while performing read/write operations to the DRAM arrays can affect the reliability of the memory system.

Data placement is one of the factors that affects the memory access pattern and, as a result, the overall performance of the memory system. The key components of a DRAM controller, highlighted in Figure 2.14, will affect the data placement and the memory access pattern in one way or another. In the following sections, the effect of each component on the memory access pattern will be investigated more closely to see how these components can affect the performance, power and reliability of a DRAM device.

#### 2.7.2 Susceptibility to Address Translation

The address translation process is one of the most significant factors in determining the final latency and power for each specific memory request. Considering a sequence of memory requests, each requested address will be mapped to its destination (i.e. channel, rank, bank, row and column) based on a pre-defined address-mapping scheme employed by the DRAM controller. In other words, the address translation process controls the data placement.