# Emulating the ARM Architecture Using a Java Dynamic Binary Translator

A dissertation submitted to the University of Manchester for the degree of Master of Science in the Faculty of Engineering and Physical Sciences

Author: Michael Baer

Submitted in: 2007

# **Contents**

| LIST ( | OF ABBREVIATIONS                                    | 4  |

|--------|-----------------------------------------------------|----|

| LIST ( | OF FIGURES                                          | 5  |

| ABST   | RACT                                                | 7  |

| DECL   | ARATION                                             | 8  |

| COPY   | RIGHT STATEMENT                                     | 9  |

| 1 IN   | TRODUCTION                                          | 10 |

| 1.1    | CLIENT                                              | 10 |

| 1.2    | Subject                                             |    |

| 1.3    | Mission                                             | 10 |

| 2 BA   | ACKGROUND                                           | 12 |

| 2.1    | EMULATION AND DYNAMIC BINARY TRANSLATION            | 12 |

| 2.1.1  | Interpretation                                      | 13 |

| 2.1.2  | Binary Translation                                  | 14 |

| 2.1.3  | Optimisations in Binary Translation                 | 16 |

| 2.2    | THE JIKES RESEARCH VIRTUAL MACHINE                  | 19 |

| 2.2.1  | The Java Virtual Machine Architecture               | 19 |

| 2.2.2  | The Jikes Research Virtual Machine                  | 21 |

| 2.3    | PROCESS VIRTUAL MACHINES                            | 26 |

| 2.4    | THE ARM ARCHITECTURE                                | 28 |

| 2.4.1  | Programmer's Model                                  | 32 |

| 2.4.2  | IO and Memory Model                                 | 37 |

| 2.4.3  | Architecture Versions                               | 38 |

| 3 PI   | EARCOLATOR ARCHITECTURE                             | 40 |

| 3.1    | INTEGRATION INTO THE JIKES RESEARCH VIRTUAL MACHINE | 40 |

| 3.2    | PEARCOLATOR CLASS ARCHITECTURE                      | 42 |

| 3.3    | INITIALIZATION                                      | 43 |

| 3.4    | Loader                                              | 44 |

| 3.5    | EXECUTION CONTROLLER                                | 49 |

| 3.6    | Decoder                                             | 51 |

| 3.7    | OS EMULATION                                        | 55 |

| 3.8    | Profiling                                           | 58 |

| 3.9    | Memory                                              | 59 |

| 3.10  | Faults                                 | 60 |

|-------|----------------------------------------|----|

| 3.11  | PROCESS SPACE                          | 61 |

| 4 T   | THE ARM EMULATOR                       | 62 |

| 4.1   | GENERAL ARCHITECTURE                   | 62 |

| 4.2   | THE ARM- AND THUMB-DECODER             | 64 |

| 4.3   | INSTRUCTION REPRESENTATION             | 67 |

| 4.4   | ARM Translator                         | 68 |

| 4.4.1 | Scheme Selection                       | 68 |

| 4.4.2 | Implementation                         | 70 |

| 4.4.3 | Conditional Instructions               | 71 |

| 4.4.4 | Condition code handling                | 72 |

| 4.5   | THE ARM INTERPRETER                    | 74 |

| 4.6   | THE ARM DISASSEMBLER                   | 75 |

| 4.7   | OPERATING SYSTEM EMULATION             | 76 |

| 4.7.1 | Linux Operating System Support         | 76 |

| 4.7.2 | Angel Debug Monitor Support            | 77 |

| 5 E   | VALUATION OF THE ARM BACKEND           | 78 |

| 5.1   | FUNCTIONALITY EVALUATION               | 78 |

| 5.2   | PERFORMANCE EVALUATION                 | 78 |

| 5.2.1 | Execution Controllers                  | 79 |

| 5.2.2 | Condition Code Evaluation              | 81 |

| 5.2.3 | Memory Model                           | 82 |

| 5.2.4 | Inlining Options                       | 83 |

| 5.2.5 | Profiling and Indirect Jump Prediction | 84 |

| 5.2.6 | Overall Emulator Performance           | 86 |

| 6 C   | CONCLUSION                             | 87 |

| 6.1   | Conclusion                             | 87 |

| 6.2   | FUTURE WORK                            |    |

| 7 R   | REFERENCES                             | 89 |

| 8 A   | .PPENDIX                               | 94 |

| 8.1   | APPENDIX A                             | 94 |

| 8.2   | Appendix B                             |    |

| 8.3   | APPENDIX C                             | 96 |

Word Count: 24875

# **List of Abbreviations**

| Abbreviation | Long Form                              |

|--------------|----------------------------------------|

| ABI          | Application Binary Interface           |

| ARFF         | Attribute Relation File Format         |

| APCS         | ARM Procedure Call Standard            |

| BURS         | Bottom Up Rewriting System             |

| CISC         | Complex Instruction Set Computer       |

| CMP          | Chip Multiprocessor                    |

| CPI          | Clocks per Instruction                 |

| CPSR         | Current Program Status Register        |

| EABI         | Embedded Application Binary Interface  |

| ELF          | Executable and Linkable Format         |

| GC           | Garbage Collector                      |

| gdb          | GNU Debugger                           |

| GOT          | Global Offset Table                    |

| HIR          | High-Level Intermediate Representation |

| ISA          | Instruction Set Architecture           |

| JNI          | Java Native Interface                  |

| JRVM         | Jikes Research Virtual Machine         |

| JVM          | Java Virtual Machine                   |

| LIR          | Low-Level Intermediate Representation  |

| MIR          | Machine Intermediate Representation    |

| MMU          | Memory Management Unit                 |

| OS           | Operating System                       |

| PIC          | Position Independent Code              |

| PLT          | Procedure Linkage Table                |

| RISC         | Reduced Instruction Set Computer       |

| SMP          | Symmetric Multiprocessing              |

| SPSR         | Saved Program Status Register          |

| SWI          | Software Interrupt                     |

| TIB          | Type Information Block                 |

| UML          | Unified Modelling Language             |

| XML          | Extended Markup Language               |

| VM           | Virtual Machine                        |

# **List of Figures**

| FIGURE 1 – OVERVIEW OF INTERPRETER COMPONENTS                               | 13   |

|-----------------------------------------------------------------------------|------|

| FIGURE 2 - JAVA VIRTUAL MACHINE RUNTIME DATA AREAS                          | 20   |

| FIGURE 3 – JRVM OPTIMISING COMPILER OVERVIEW                                | 24   |

| FIGURE 4 – THE JIKES ADAPTIVE OPTIMIZATION SYSTEM                           | 25   |

| FIGURE 5 – COMPONENTS OF A PROCESS VIRTUAL MACHINE                          | 27   |

| Figure 6 - ARM Register Layout                                              | 30   |

| FIGURE 7 – THE ARM 3-STAGE PIPELINE                                         | 32   |

| Figure $8-$ Relation of Pearcolator to the Jikes Research Virtual Machine   | 40   |

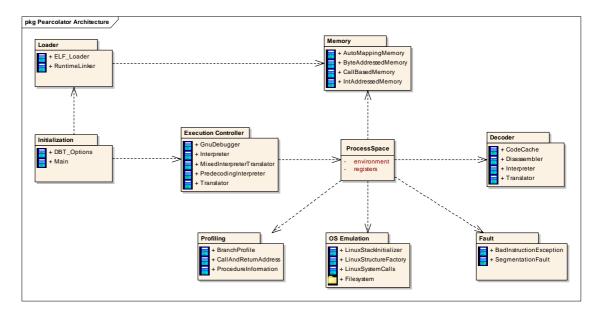

| Figure 9 – Pearcolator Overview as a UML Package Diagram                    | 43   |

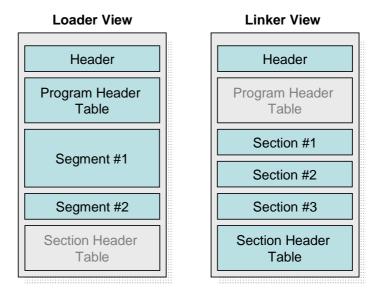

| Figure 10 – Perspectives on an ELF file                                     | 45   |

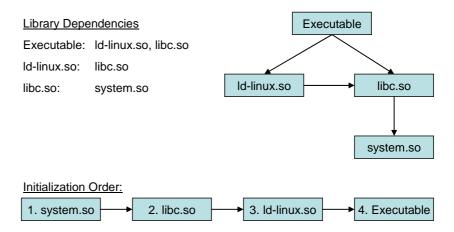

| FIGURE 11 – DEPENDENCIES BETWEEN ELF SHARED OBJECTS                         | 48   |

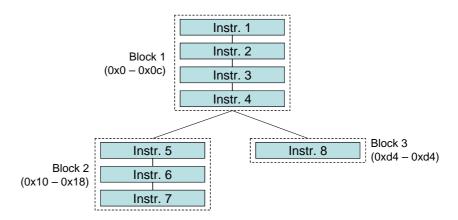

| Figure $12-Building$ dynamic basic blocks of interpreted instructions       | 52   |

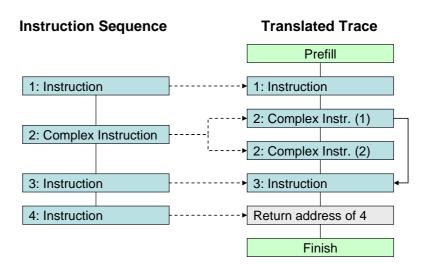

| Figure $13-$ Translation of a simple instruction sequence into a trace      | 53   |

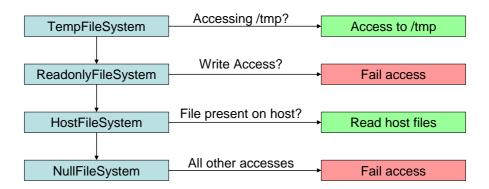

| FIGURE 14 – DEFAULT PEARCOLATOR FILESYSTEM CONFIGURATION                    | 57   |

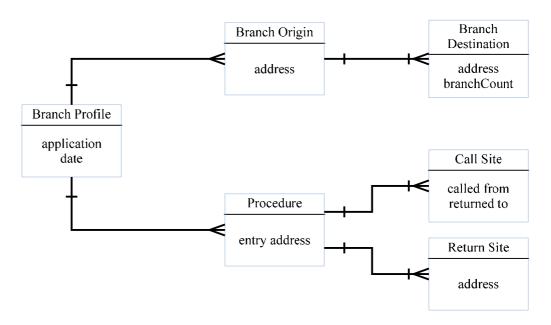

| Figure $15$ – Entity Relationship Diagram of the Pearcolator Profiling Data |      |

| Model                                                                       | 59   |

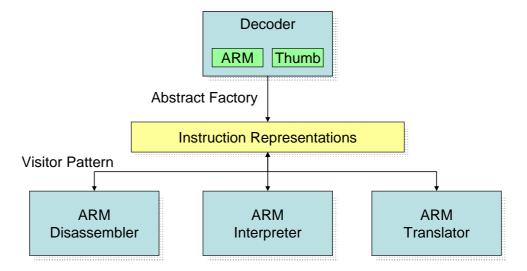

| FIGURE 16 - ARCHITECTURE OF THE PEARCOLATOR ARM BACKEND                     | 62   |

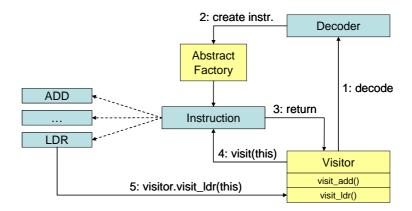

| FIGURE 17 – COMMUNICATION BETWEEN ARM BACKEND COMPONENTS.                   | 64   |

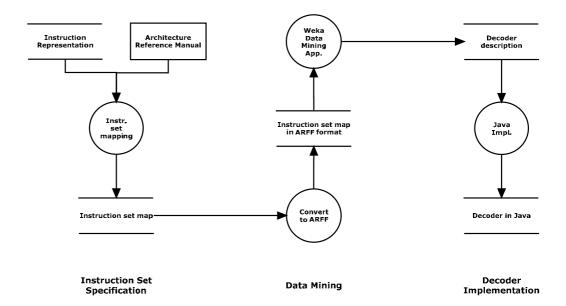

| FIGURE 18 – DATA FLOW DIAGRAM OF THE DECODER CONSTRUCTION PROCESS           | 66   |

| FIGURE 19 – SAMPLE INSTRUCTION DEFINITIONS                                  | 67   |

| Figure $20$ - Confluence between guest and host translation for the Pearcol | ATOR |

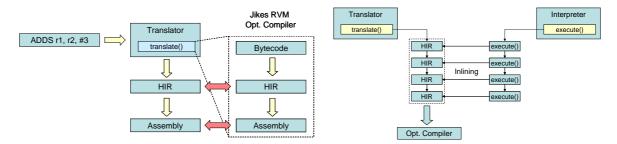

| BINARY TRANSLATOR                                                           | 69   |

| Figure 21 – Inlining an interpreter during translation                      | 69   |

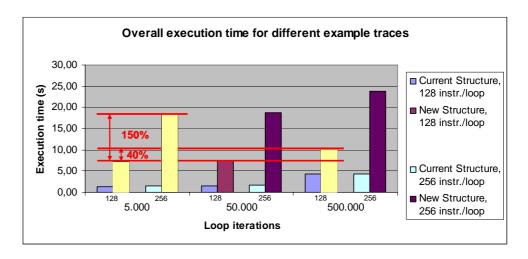

| FIGURE 22 – COMPARISON OF EXECUTION TIME FOR DIFFERENT BINARY TRANSLATION   |      |

| SCHEMES                                                                     | 70   |

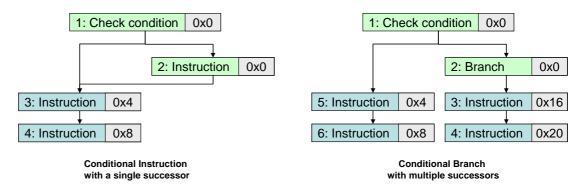

| Figure 23 – Translation of a conditional instructions                       | 72   |

| Figure 24 – Execution time of Dhrystone for different Execution Controlle   | RS   |

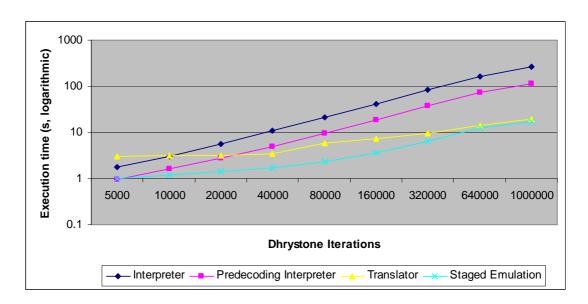

| AND DIFFERENT NUMBER OF DHRYSTONE LOOPS (ARM 32-BIT CODE)                   | 79   |

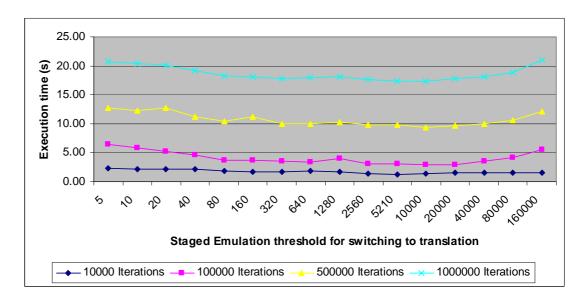

| FIGURE 25 – EXECUTION TIME FOR DIFFERENT NUMBER OF DHRYSTONE ITERATIONS AND | D    |

| VARIOUS STAGED EMULATION THRESHOLDS.                                        | 81   |

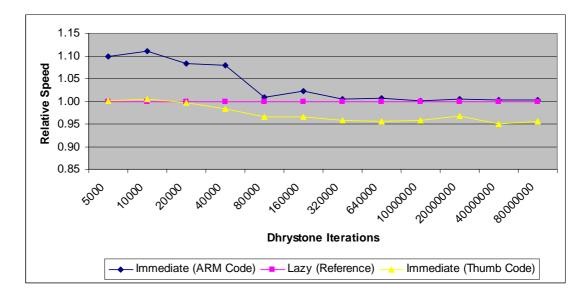

| FIGURE 26 – RELATIVE EXECUTION SPEED OF LAZY AND IMMEDIATE EVALUATION OF      |      |

|-------------------------------------------------------------------------------|------|

| CONDITION CODES FOR DIFFERENT NUMBERS OF DHRYSTONE ITERATIONS                 | 82   |

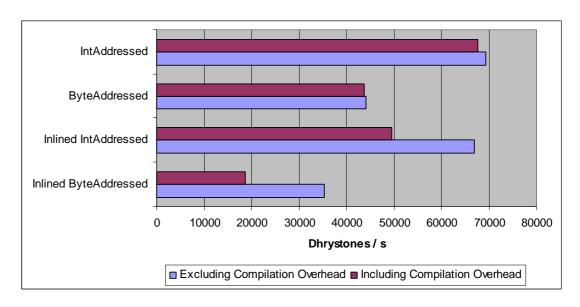

| FIGURE 27 – TRANSLATOR PERFORMANCE FOR DIFFERENT MEMORY MODELS                | 83   |

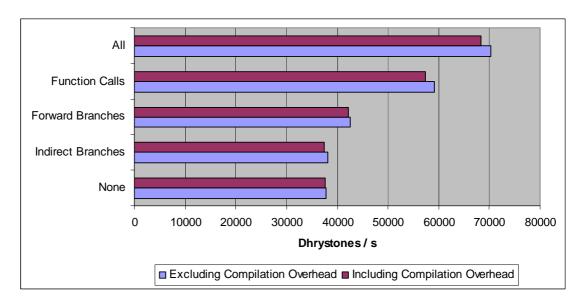

| Figure 28 – Influence of inlining different types of branches into a Pearcola | ATOR |

| TRACE                                                                         | 84   |

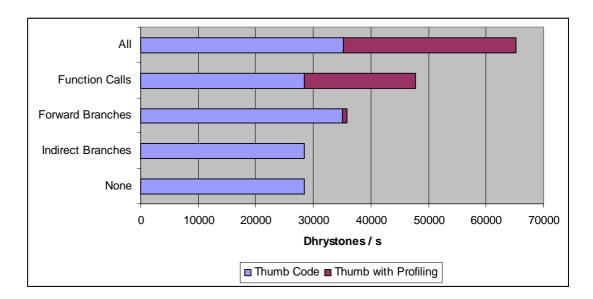

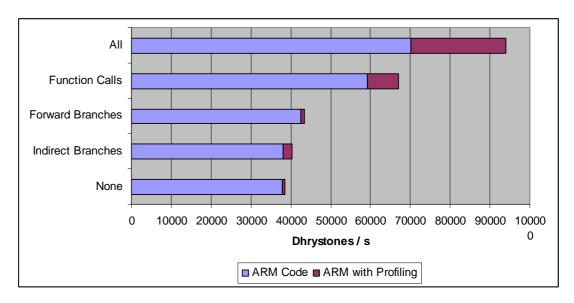

| FIGURE 29 – EFFECT OF PROFILING FOR DIFFERENT INLINING TECHNIQUES             | 85   |

| Figure 30 - Effect of profiling for different inlining techniques             | 85   |

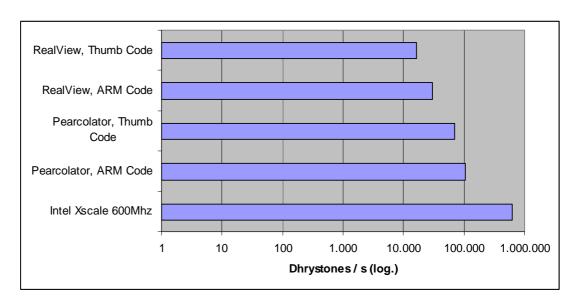

| FIGURE 31 – COMPARISION OF PEARCOLATOR PERFORMANCE WITH A COMMERCIAL          |      |

| EMULATOR AND NATIVE EXECUTION                                                 | 86   |

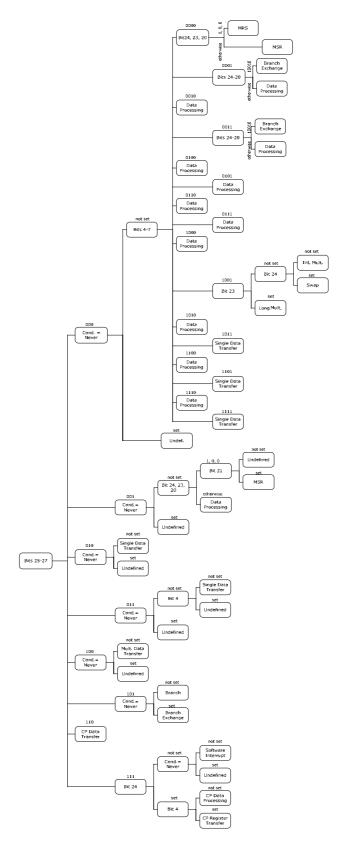

| Figure 32 – ARM Decoder Decision Tree                                         | 95   |

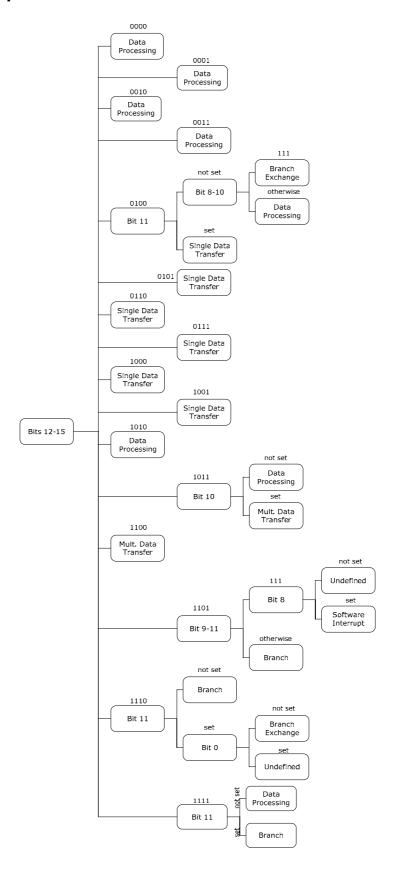

| FIGURE 33 – THUMB DECODER DECISION TREE                                       | 96   |

## **Abstract**

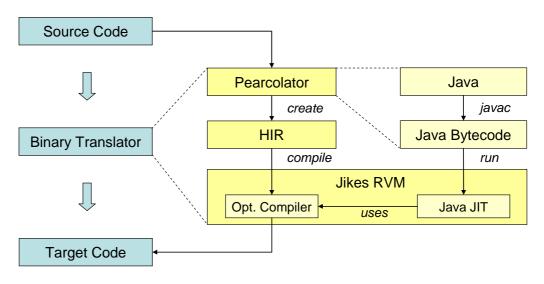

Binary translation enables the execution of binary code from one processor architecture on a different architecture by translating the respective machine code. Pearcolator is a dynamic binary translator written in Java, which runs on top of the Jikes Research Virtual Machine. It has been developed by the Advanced Processor Technologies group, which explores architectures for Chip Multiprocessors (CMP) as well as appropriate operating system designs and compiler technologies. Pearcolator allows running legacy applications on the group's Jamaica processor architecture.

In this thesis, Pearcolator is enhanced with a backend to run programs for the ARMv4T architecture. Furthermore, it is reengineered to support interpretation, profiling, dynamic linking and a generic software component model. The interpreter support is leveraged to implement staged emulation, i.e. the dynamic switching between interpretation and translation, within Pearcolator.

Using the new Pearcolator component model, the performance impact of different strategies for program execution, flag management, memory access, code inlining and profiling were investigated. It has been found that staged emulation yields a three times performance increase in the best case. Furthermore, it is shown that lazy flag evaluation is not always the best performing flag emulation strategy. The performance of these strategies is dependant on the instruction set. Choosing immediate flag evaluation for ARM code and lazy flag evaluation for Thumb code improves performance by up to 10%. Similarly, the right choices for the memory model and inlining of code during binary translation deliver a significant speedup. Profiling further increases the translator's speed by about 30%.

The thesis produced the first open source ARM emulator written in Java. The final emulator performance proved to be five times faster than a commercial emulator, but still several orders of magnitude slower than native execution.

# **Declaration**

No portion of the work referred to in the thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# **Copyright Statement**

- i. Copyright in text of this dissertation rests with the author. Copies (by any process) either in full, or of extracts, may be made only in accordance with instructions given by the author. Details may be obtained from the appropriate Graduate Office. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the author.

- ii. The ownership of any intellectual property rights which may be described in this dissertation is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

- iii. Further information on the conditions under which disclosures and exploitation may take place is available from the Head of the School of Computer Science.

## 1 Introduction

#### 1.1 Client

The Advanced Processor Technologies Group within the University of Manchester conducts research into the design of novel processing architectures. Its focus spans from software approaches, esp. compiler optimisations, to developing new hardware architectures.

The Jamaica Project Group is part of the Advanced Processor Technologies Group. It explores architectures for Chip Multiprocessors (CMP), appropriate operating system designs and compiler technologies that leverage parallelism within applications. The group has developed a CMP architecture that is able to run a customized version of the Jikes Research Virtual Machine.

This thesis has been written in the Jamaica Project Group under the supervision of Prof. Ian Watson and Dr. Ian Rogers.

## 1.2 Subject

The thesis focuses on the dynamic binary translator Pearcolator, which is a development of the Jamaica Project Group. Binary translation enables the execution of binary code from one processor architecture on a different architecture by translating the respective machine code. Pearcolator runs on top of the Jikes Research Virtual Machine, thus enabling the CMP architecture developed by the Jamaica Project Group to run legacy applications from different systems. This is an important strategic asset, as it increases the application base and therefore the acceptance of a novel architecture.

Pearcolator supports multiple source architectures through different backends. A PowerPC and an X86 backend have been developed previously [Burcham2004] [Matley2005]. However, though both backends used similar techniques, they were essentially developed as separate applications and made no efforts to unify Pearcolator into a single system.

#### 1.3 Mission

This thesis aims to improve the architecture of the dynamic binary translator Pearcolator, to enhance it with a new backend and to investigate possible performance gains that have not been analyzed by the previous authors. More specifically, the following tasks will be accomplished.

- The Pearcolator architecture will be revised to unify the previous PowerPC and X86 backends. A template architecture, which promotes the reusability of components and facilitates the implementation of new backends, will be developed and implemented.

- 2. Pearcolator will be enhanced with support for interpreters. This feature will be driven by a staged emulation framework, which dynamically switches between translation and interpretation to improve execution performance.

- A new backend for the ARM processor architecture will be implemented into Pearcolator. The backend shall support translation and interpretation of the ARM 32-bit and the Thumb 16-bit instruction set.

- 4. The new architecture and the ARM backend will be used to evaluate the performance of Pearcolator. Especially the influence of dynamic switching between translation and interpretation and the benefits of lazy evaluation of condition codes will be explored.

The thesis will first introduce the technologies that were used during its realization, continue by describing the new architecture as well as the ARM backend, which have been implemented into Pearcolator, and finally investigate the performance of the system.

# 2 Background

## 2.1 Emulation and Dynamic Binary Translation

Emulation is the *process of implementing the interface and functionality of one system or subsystem on a system or subsystem having a different interface and functionality* [Smith2005, p. 27]. The term was first used in 1962 in conjunction with IBM testing the compatibility of their new products with their predecessors. In 1965, IBM shipped the System/360– it contained the world's first emulator, which ran programs that were originally written for the IBM 7070 machine.

According to the above definition, emulation involves two systems<sup>1</sup>. Commonly, the system that is being emulated is called the emulation *source* while the system that the emulator is running on is called the emulation *target*. Some authors also use the terms *guest* to denote the source and *host* to denote the target system in conjunction with binary translation. Usually, source and target refer to two distinct computer architectures or instruction sets. However, some systems may apply the same techniques that are subsequently described in cases where source and target refer to the same entity. [Smith2005, p. 63] calls this same-ISA emulation. For instance, the dynamic binary optimizer Dynamo, developed by HP Labs, re-translates a binary for the HP PA-8000 or IA-32 processor while running on the same processor. Though not strictly an emulator, Dynamo applies optimisations known from emulation to the binary, thereby increasing execution speed by up to 20% [Bala1999, p.12].

Though various aspects of a system can be emulated, the following paragraphs focus on the emulation of conventional instruction sets<sup>2</sup>. Naturally, performance is one of the primary concerns during emulation. In emulation, execution performance is usually achieved by weighing off the amount of pre-processing applied to the program and

<sup>2</sup> Virtual instruction sets, such as Java Bytecode, may have special properties that can be exploited to apply more advanced emulation techniques [Smith2005, p. 28].

.

<sup>&</sup>lt;sup>1</sup> The term *subsystem* from the above definition is omitted in the remainder of this document and only the term system is used instead.

runtime performance on the host. In that regard, one usually distinguishes interpretation and translation.

#### 2.1.1 Interpretation

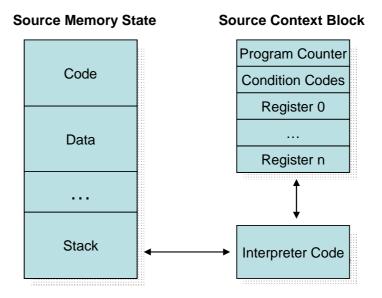

An interpreter is a computer program that analyzes and executes another computer program at runtime, without translating the interpreted program itself into machine language. Interpretation usually involves a cycle in which an instruction is retrieved from the source program, processed and executed before the next instruction is retrieved. Figure 1 shows an overview of a typical interpreter. The interpreter holds an image of the source program's code and data in memory, as well as code to perform the interpretation and a *source context block*, which stores the state of the guest that is usually held in hardware registers.

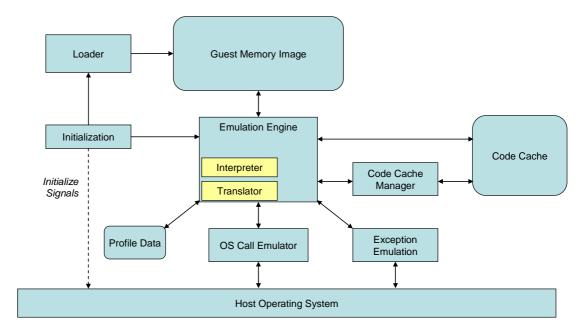

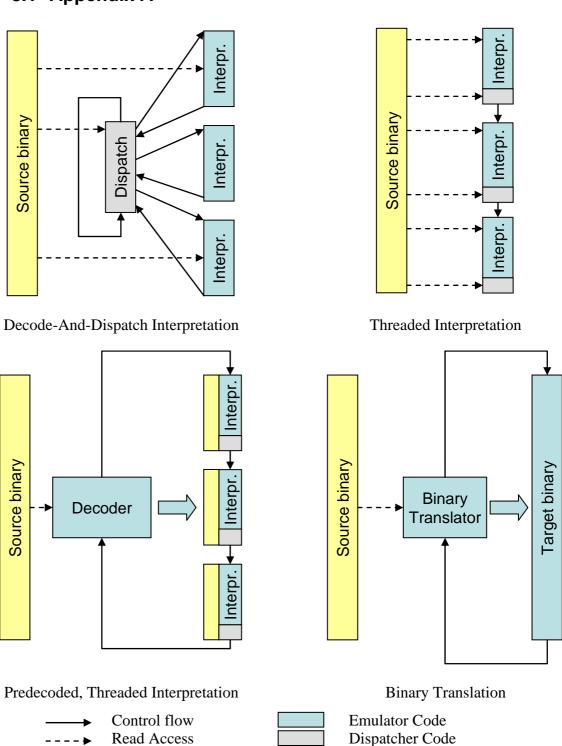

Figure 1 – Overview of interpreter components Inspired by [Smith2005, p. 30]

Appendix A gives a graphical representation of the most common interpreter types. A simple decode-and-dispatch interpreter *operates by stepping through the source program, instruction by instruction, reading and modifying the source state according to the instruction* [Smith2005, p. 30]. More specifically, the interpreter runs a *dispatch loop*, which uses a switch statement<sup>3</sup> to distinguish between different instruction types. The loop invokes an individual *interpreter routine* for each instruction type,

\_

<sup>&</sup>lt;sup>3</sup> Or an equivalent structure, depending on the language of implementation.

which retrieves further information from the instruction and performs the actual execution. Though such an interpreter is easy to understand and write, a number of advanced interpretation techniques have been developed, which lead to improved performance for certain applications. These techniques are described next.

A common approach to building a high performance interpreter is to append the branch to the next interpreter routine directly to the end of the each single interpreter routine. This is equivalent to inlining parts of the dispatch loop into the interpreter routines. This technique, called threaded interpretation, disposes of the dispatch loop and thereby also a number of jumps related to it<sup>4</sup>. Because there are usually patterns in the instruction stream (e.g. a compare instruction is often followed by a conditional branch), threaded interpretation also leads to regular execution patterns, which are often more amenable to branch predictors.

Nevertheless, threaded interpretation still requires some kind of dispatch code, which will associate a binary instruction with the address of the respective interpreter routine. Direct threaded interpretation replaces the instructions in the memory image of the source binary with the address of the respective interpreter routine. Though this requires some pre-processing, it minimizes the dispatch time upon repeated instruction execution. A similar, popular technique is *predecoding*, where pieces of information are extracted from the instruction and put into more accessible fields [Smith2005, p. 35]. Machine instructions are usually highly compressed and not necessarily memoryaligned in the manner preferred by the host machine. Predecoding extracts the necessary information to execute an instruction from its machine representation and stores this information within memory-aligned, easy accessible structures. The predecoded information is saved for later reuse and allows skipping the decoding phase on repeated execution.

# 2.1.2 Binary Translation

Predecoding translates source instructions into an easily accessible format, but still uses central interpreter routines to execute the instruction. Binary translation takes the

<sup>&</sup>lt;sup>4</sup> More specifically, the return from the interpreter routine and the return to the top of the dispatch loop.

approach further. Instead of translating from source instructions to an intermediate representation, binary translation describes the *process of converting the source binary program into a target binary program* [Smith2005, p. 49]. In essence, binary translation will create custom target code for each occurrence of a source instruction. However, this translation is not trivial and poses a number of problems for the translator, the most common of which will be introduced in the following sections.

A basic problem in binary translation is the *code discovery* problem. It describes a translator's inability to discover which sections of a binary actually contain executable code and to distinguish this code from data. Even though many binary formats designate regions containing program code, it is not uncommon for compilers to include additional (read-only) information within these regions. For instance, the MIPSPro C compiler inserts a mask before each procedure that denotes, which registers the procedure saves onto the stack and at which offset from the stack pointer those registers are saved [Huffman1997, p. 106]. Other compilers may include constant values in literal pools at the beginning of a function or introduce padding bytes in order to align code with word or cache line boundaries. Especially when instruction sets have variable sized instructions, it may be impossible to distinguish data from code by just performing a static, syntactical analysis of the instruction stream. Similar problems arise in the presence of indirect jumps, whose targets may be hard to determine.

Indirect jumps also give rise to a second problem, known as the *code location* problem. When translating a source binary to a target system, it is almost inevitable that the target code will reside at a different memory address than it would on the source system. Reasons for that include (but are not limited to) different memory architectures, operating system constraints, different instruction sets or simply optimisations performed by the binary translator that change the code structure. It is the translator's task to make sure that target addresses for indirect jumps within the source executable are fixed up to comply with the memory layout on the target system. A related problem is *self-referencing code* [Smith2005, p. 62], where a program reads values from its text segment. A translator also has to make sure that these reads, which are often used to access constants, return the expected value.

Depending on the amount of emulation desired, *self-modifying code* and *precise traps* may also cause a problem for binary translators [Smith2005, p. 62]. Self-modifying code is concerned with programs that write to code regions, thereby altering

their behaviour. Precise traps try to simulate a system's exact reaction to traps, such as memory faults and hardware or software interrupts. However, both problems are less prominent in environments where the source operating system shields the program from traps and prevents the use of self-modifying code.

A common solution to these problems is to use *dynamic translation*. The idea behind this technique is *to translate the binary while the program is operating on actual input data, i.e. dynamically and to* [..] *translate new sections of code incrementally, as the program reaches them.* In contrast, *static translation* aims *to translate a program in its entirety before beginning emulation* [Smith2005, p. 52, 55]. The advantage of dynamic translation is that it not only allows to lazily discover and translate code as the program tries to execute it, but also that self-modifying code can usually be handled by triggering a recompilation once a code region gets modified. However, dynamic translation comes with a substantial runtime overhead, as the program has to be translated on the target machine. This also means that code to perform this translation and manage previously translated code has to be present on the target machine.

## 2.1.3 Optimisations in Binary Translation

In contrast to interpretation, binary translation opens the opportunity for applying a whole new set of optimisations to the target code. These optimisations can provide a vast speed-up, making binary translators a popular option for high-speed emulation. A few general techniques are presented in this section. Note that most techniques used in compiler backends and Just-In-Time compilers can also be applied to binary translation. In fact, Just-In-Time compilation is actually a special case of binary translation [Altman2000, p. 40f].

One of the most obvious code optimisations during binary translation is to map parts of the source context block (see section 2.1.1) to target machine registers, thus providing faster access to the context block and allowing some operations to be executed without any memory accesses at all. With this technique, *the speed of execution of the translated code* [..] *starts becoming comparable to the original source code* [Smith2005, p. 52]. Some registers on the target machine are typically reserved for

usage by the translator<sup>5</sup>. If the number of registers available on the source machine is higher than the number of available registers on the target machine, the mapping of source to target registers must be carefully performed as to maximize performance. Previous solutions for register allocation in compilers can be applied to this problem. Depending on the amount of register pressure<sup>6</sup>, graph colouring or linear scan register allocation algorithms are commonly used.

During dynamic translation, instructions are commonly grouped into blocks that are translated and scheduled together. The number of instructions within a block is an important performance issue. When the translated blocks are too small, the overhead of scheduling these blocks increases. On the other hand, when the blocks are too large, the effort for translation and optimisation increases, while the resuse of translations might be limited. The natural unit of translation in dynamic binary translators is a dynamic basic block [Smith2005, p. 56]. A static basic block is a sequence of instructions that can be entered only at the first of them and exited only from the last of them [Muchnick1997, p. 173]. Dynamic basic blocks usually start after a branch and follow the line of execution until a branch is encountered. They do no stop at branch labels and therefore tend to be larger than static basic blocks. Translation chaining increases the size of the executed portions even further by chaining several dynamic basic blocks into a larger trace. A trace is usually not stopped by static but only by dynamic jumps, because their target address might be hard to determine until the jump is actually performed. The best size for a trace depends on the actual translator.

Indirect jumps often cause a large evaluation overhead during the execution of programs that have been binary translated. This is particularly an issue for object oriented programs, which tend to make heavy use of indirect jumps to implement polymorphism. Indirect jump prediction or inline caching [Smith2005, p. 66] can mitigate this problem. This technique uses profiling to gather information about previously seen target addresses for each indirect jump. The most common jump targets

<sup>&</sup>lt;sup>5</sup> This thesis uses the term "translator" as a short form for "binary translator". This is in accordance with contemporary writing on the subject, e.g. [Altman2000].

<sup>&</sup>lt;sup>6</sup> Register pressure describes the inverted ratio of free registers and variables that are to be allocated to these registers.

are included within a trace. At an indirect jump location, the translator inserts code that checks, if the dynamic jump target is included within the trace. In case it is, it can directly branch to that target. Otherwise, a default handler is invoked that will return control to the binary translator.

Finally, another well known source of performance problems are condition codes or flags, which characterize the result of a previous instruction. Common condition codes indicate whether an operation produced a carry, the result is zero or if an overflow occurred. They are frequently tested during the execution of conditional instructions. There are different approaches to updating the condition codes: some architectures feature special *compare* instructions that will explicitly update the conditions codes<sup>7</sup>, other architectures implicitly update the condition codes after each arithmetic operation<sup>8</sup> and some architecture do not have a distinct set of condition codes at all<sup>9</sup>. In general, computing all the condition codes for a given source instruction takes many target instructions, often more than emulating the rest of the instruction, and it can slow emulation considerably [Smith2005, p. 71]. The problem is prominent on architectures that set condition codes implicitly with every instruction. A common solution is *lazy* evaluation of condition codes. In that scheme, instead of updating the condition codes at the same rate as the source architecture, only the operands and the operation that will produce the condition codes are saved. Instruction that need the condition codes can then produce them from the saved information. This technique is based upon the observation that many architectures update the condition codes more frequently than they are actually read. The usefulness of lazy evaluation depends on the condition code update/usage ratio of the source architecture as well as on how well the source and target ISA match in their handling of condition codes. In some situations, it might be beneficial to always evaluate the condition codes or to use a subset of the condition codes created by the target architecture [Smith2005, p. 74].

\_

<sup>&</sup>lt;sup>7</sup> For example, the PowerPC ISA provides a special set of arithmetic operations that will also update the condition codes [Frey2003, p. 26].

<sup>&</sup>lt;sup>8</sup> The Zilog Z80 (which is binary compatible to the Intel 8080) updates condition codes with every arithmetical operation [Zilog2001, p. 75ff]

<sup>&</sup>lt;sup>9</sup> The MIPSPro architecture does not have a special condition code register, but instead uses compare instructions that write their results into a general purpose register [Huffman1997, p. 52ff].

#### 2.2 The Jikes Research Virtual Machine

#### 2.2.1 The Java Virtual Machine Architecture

The Jikes Research Virtual Machine (JRVM) is a virtual machine targeted at executing programs for the Java Virtual Machine (JVM) Architecture. Therefore it is beneficial to introduce this architecture first. *The Java virtual machine is the cornerstone of the Java and Java 2 platforms.* [... It] is an abstract computing machine. Like a real computing machine, it has an instruction set and manipulates various memory areas at run time [Sun1999, ch. 1.2]. The instruction set of the JVM is called Java bytecode. The JVM must not be confused with the Java Compiler. The Java Compiler translates the Java Programming Language into Java bytecodes, while the JVM executes those bytecodes.

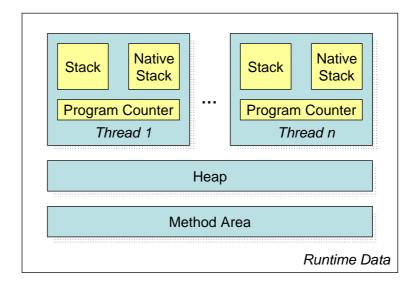

Figure 2 illustrates the general structure of the Java Virtual Machine. The JVM may execute multiple threads, which share a common memory area but also have separate per-thread data areas. The JVM is a stack machine and subsequently Java bytecodes are a zero-operand ISA. This unusual definition<sup>10</sup> of the JVM ensures that it does not favour a specific real architecture.

Each thread consists of a program counter, a stack and a native stack. The program counter identifies the currently executed bytecode. The stack holds all operands that are managed by the JVM, while the native stack is available to non-Java code, which can be called from Java using the Java Native Interface (JNI).

<sup>&</sup>lt;sup>10</sup> The definition is unusual in the sense that most real-world target architectures for the JVM do not support stack operations, but rather contain a varying number of registers. However, this kind of definition can also be found in other virtual instruction sets, such as P-Code.

Figure 2 - Java Virtual Machine Runtime Data Areas

Naturally, the stack layout is a crucial part of a stack machine's definition. The Java Virtual Machine Stack is organized into frames, one for each method in a program's call stack. A frame contains all parameters and local variables of that method, an operand stack and a reference to the constant pool, which is part of the read-only method area and maps identifiers to constants [Sun1999, ch. 3.5.4]. Data on the stack is typed. The JVM distinguishes between primitive and reference types. Primitives types are the boolean type, numeric types (byte, char, short, int, float, long, double) and the returnAddress<sup>11</sup> type. Reference types denote references to instances of classes, array types and interfaces on the heap as well as the null reference, which references no object. In contrast to languages such as C, the size of all types is well defined. The JVM's stacks are split into slots of 32 bits, which can contain most data types<sup>12</sup>. The operand stack is controlled by the application and contains the operands for bytecode instructions.

The JVM separates memory into a heap and a method area. The method area works similar to a UNIX process' TEXT segment [Sun1999, ch. 3.5.4]. It stores the constant pool, field and method data and the Java bytecodes, which form the executable part of a Java program. The heap is a memory area, *from which memory for all class instances*

<sup>&</sup>lt;sup>11</sup> In contrast to all other JVM data types, the returnAddress type does not correspond to any Java programming language type [Sun1999, ch. 3.3.3].

<sup>&</sup>lt;sup>12</sup> Except for the long and double types, which occupy two slots.

and arrays is allocated [Sun1999, ch. 3.5.3]. The Java bytecode instruction set only features instructions that allocate objects, but none that deallocate them. Therefore, the heap is managed by an automatic storage management system (known as garbage collector) [Sun1999, ch. 3.5.3]. The garbage collector manages object allocation, movement, deallocation of unused objects and heap compaction. [Sun1999] intentionally does not specify implementation details about the garbage collector. That allows different garbage collectors to be used in different environments, while retaining compatibility to the JVM specification.

Java bytecodes are a mixed stream of instruction bytes and operand data. The instruction byte identifies the operation that is to be executed. It implicitly defines the number of operands that are following in the bytecode stream and those that have to be retrieved from the operand stack. This specification makes for a very compact instruction set, with a maximum of 256 instructions. However, only slightly more than 200 instruction codes are used and as bytecode instructions are typed, the actual number of different instruction classes is even lower. In contrast to other ISAs, the Java bytecode is directly targeted at running an object oriented Java program. Therefore, it is not surprising to find instructions that access object members, allocate objects, do type checking or perform synchronization within the instruction set. Finally, the Java bytecode ISA only allows type-checked memory access. This feature makes Java bytecodes immune to many of the security problems faced by traditional ISAs.

Efforts to build hardware implementations of the JVM architecture include Sun Microsystem's picoJava microprocessor, the ARM926EJ-S processor, which uses the Jazelle Direct Bytecode Execution engine and other implementations. However, the emphasis of the JVM Architecture is still on execution on a wide variety of systems whose ISA is not Java bytecode. Consequently, the JVM Architecture has to be emulated on these systems.

#### 2.2.2 The Jikes Research Virtual Machine

The Jikes Research Virtual Machine is a Java bytecode Just-in-Time compiler. It originated in the Jalapeño research project, conducted in 1997 at IBM's Thomas J. Watson Research Center. IBM recognized that existing JVMs were not built to cope with requirements of high-performance servers, such as *SMP scalability, continuously running JVMs, [limited] GC pause times, thread limits* and optimisations concerning the

use of libraries [Alpern1999, p. 3]. The Jalapeño project was targeted specifically at server machines and meant to fulfil these requirements. After serving as a research environment at IBM for many years, the software was released as an open source project called the Jikes Research Virtual Machine in 2005.

Compared to other virtual machines, the JRVM has two distinguishing features [Alpern1999, p. 1]:

#### 1. Written in Java

The JRVM is mostly written in Java. Though there are previous references to JVMs being written in Java<sup>13</sup>, the JRVM is self-hosted and does not need another JVM to run.

#### 2. The widespread use of compilers and compiler technologies

Instead of providing both an interpreter and a JIT compiler as in other JVMs, bytecodes are always translated to machine code before they are executed [Alpern1999, p. 1]. As servers are the main target of the JRVM, it was anticipated that programs are long-running [Alpern1999, p. 3], which made forgoing an interpreter acceptable. Furthermore, the JRVM features two different compilers and an Adaptive Optimization System (AOS), making it possible to adapt compilation effort to execution requirements.

Writing a JVM in Java poses two additional challenges: Booting the VM and accessing the underlying hardware. The first problem is solved by building a bootstrap that can execute enough of the VM to enable it to compile itself. During the compilation process, a partially running version of the JRVM is created and an image of that process is stored into a file (Boot Image). On the target machine, the Boot Image Runner loads the Boot Image into a new process and branches into it to start execution of the JRVM.

In order to enable low-level hardware access for the JRVM, code replacement is used. If certain function calls, contained within the VM\_Magic class, are encountered during the compilation, they are replaced with fixed target machine code sequences.

\_

<sup>&</sup>lt;sup>13</sup> For example, see the *JavaInJava* Project at http://research.sun.com/kanban/JavaInJava.html

This pattern allows the JRVM to be written mostly in Java, only resorting to platform-dependent code, where necessary.

At the heart of the JRVM lie two compilers, the baseline and the optimizing compiler. As the overall optimization strategy is to compile only [Smith2005, p. 320], these compilers present different compilation-runtime speed tradeoffs. The baseline compiler does not use an intermediate language, but rather translates Java bytecodes directly into equivalent machine code. The resulting code will emulate the Java stack in memory, bypassing any opportunities for optimisation. This results in fast code production, but slow runtime performance.

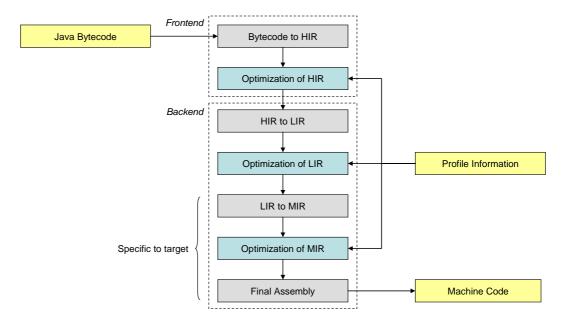

Alternatively, the sophisticated optimizing compiler puts much more emphasis on producing quality code, sacrificing compilation performance instead. Figure 3 gives an overview of the different optimisation stages within the optimizing compiler. Initially, Java bytecode is converted into HIR (High-level Intermediate Representation<sup>14</sup>), the first of three internal intermediate representations. Though the JVM architecture defines a stack machine, all intermediate representations are register-based. Not only do register-based intermediate representations allow a closer fit to the target instruction set, but they also facilitate code motion and transformation, leading to better code optimisations [Alpern2000, in ch. "A Dynamic Optimising Compiler"]. HIR groups instructions into extended basic blocks. In contrast to regular basic blocks, Jikes' extended basic blocks are not terminated by method calls or instructions that possibly throw exceptions. Upon them, *simple optimization algorithms with modest compile-time overheads are performed* [Brewer2003, slide 44], including dead-code elimination, common sub-expression elimination and copy propagation.

<sup>14</sup> The expression "high level" refers to the representation having instructions and semantics that are close

\_

to Java bytecode.

Figure 3 – JRVM Optimising Compiler Overview

Next, HIR is converted to a low-level intermediate representation (LIR). Though similar in principle, LIR is much more specific regarding JRVM internals. Most HIR instructions expand into several LIR instructions. For instance, the invokevirtual HIR instruction, which calls a virtual method, is translated into three LIR instructions: the first instruction retrieves the class' Type Information Block (TIB)<sup>15</sup> pointer, the second one locates the address of the appropriate method and the third instruction performs the actual branch.

It is obvious that the same code is much larger in LIR than it was in HIR. In fact, LIR can be two to three times larger than corresponding HIR [Alpern2000, in section "Low-level optimization"]. Due to its compactness and target-platform independency, HIR is the main optimisation target within the JRVM. However, the breakdown of HIR instructions into several LIR instructions offers new optimisation opportunities. Therefore, selected optimisations, such as common sub-expression elimination, are performed on LIR.

As a final step, the code in LIR is translated into machine intermediate representation (MIR). MIR is specific to the target machine's instruction set. For that conversion, a

<sup>&</sup>lt;sup>15</sup> The Type Information Block manages all type information that does not vary with regard to individual instances. This includes the object's memory layout, its virtual method table and interface information.

dependency tree is created for each basic block, modelling the relationships between the instructions within the basic block. This dependency tree is passed to a Bottom-Up-Rewriting-System (BURS) to select the most appropriate machine instruction for a set of LIR instructions. BURS is *based on term rewrite systems, to which costs are added* [Nymeyer1997, p. 1]. An external grammar specification, which details the capabilities of the target machine's instruction set, maps sets of LIR to MIR instructions. Similar to other parser generators, a tool is used that builds a BURS parser from that grammar. After running the parser on the input LIR, it outputs equivalent MIR for the target machine.

Finally, live variable analysis is applied to determine the lifetime of registers. This information is used to drive a simple linear-scan register allocator. The optimizing compiler adds prologue and epilogues to function calls and, as a last step, outputs machine instructions for the target machine.

The described process can be performed using three different optimisation levels. Higher levels use additional optimisations to generate more efficient code, but are also costly in terms of compilation time. Therefore, it is necessary to determine which optimisation level to apply to which section of code. The Adaptive Optimisation System (AOS) within the JRVM performs this task.

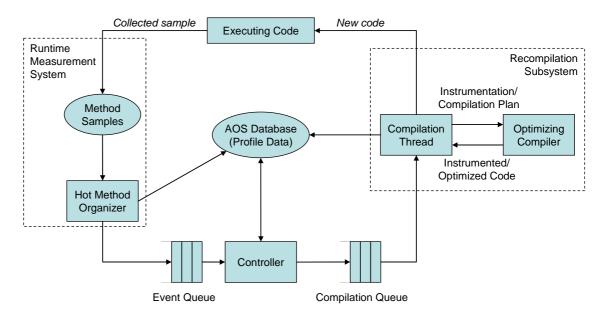

Figure 4 – The Jikes Adaptive Optimization system Inspired by [Smith2005, p. 321]

Figure 4 given an overview of the Jikes Adaptive Optimization system. Naturally, the central part of the system is a database of profiling data, which is continuously being updated during the execution of a program. As Jikes has a non-preemptive scheduling model that relies on yield points, it is easy for the AOS to add profiling code at these yield points. The profiling information is available to the AOS as well as to the optimizing compiler.

The AOS can increase a method's performance by recompiling it at a higher optimisation level. It is the task of the Runtime Measurement Subsystem to organize and analyze the samples retrieved from the profiling activities. Using that data, it can evaluate how much a method might benefit from recompilation.

The Controller steers the JRVM optimizations. *It instructs the measurement subsystem to initiate, continue or change profiling activities* [Smith2005, p. 322]. Furthermore, it chooses the methods which are to be recompiled and also determines the required optimization level. Those methods are finally forwarded to the Recompilation Subsystem, which controls the activity of the Optimizing Compiler. After the chosen methods are recompiled, On-Stack-Replacement<sup>16</sup> is used to switch to the optimized version.

#### 2.3 Process Virtual Machines

Most computer systems are designed to only run programs that have been compiled for a specific ISA and operating system. One use of emulation in conjunction with virtual machines is to overcome this restriction. A process virtual machine architecture is tailored for solving this problem. By using a process VM, a guest program developed for a computer other than the user's host system can be installed and used in the same way as all other programs on the host system [Smith2005, p. 83]. A process virtual machine runs as a process on top of an operating system and encapsulates a guest process with a runtime layer, which controls the guest process' execution and manages the communication with the host operating system.

.

<sup>&</sup>lt;sup>16</sup> On-Stack-Replacement is a compiler technique that allows code of a running method to be exchanged by a newly compiled version.

Pearcolator uses the features of the JRVM to build a process virtual machine with *extrinsic compatibility*. This means that application compatibility partially relies on properties of the guest software. More specifically, Pearcolator only provides limited Operating System emulation, which restricts its support for guest software.

Figure 5 – Components of a process virtual machine Inspired by [Smith2005, p. 86]

Figure 5 shows the typical components of a process virtual machine:

#### 1. Initialization

The initialization routine sets up the different components of the process virtual machine and establishes communication with the host operating system. It parses user arguments and invokes the loader.

#### 2. Loader

It is the loader's task to read the guest executable and initialize a memory area containing the guest program's code and data. This may involve loading and linking other modules, as required by the guest executable. Note that the guest executable's code is not loaded as an executable memory segment, but that it is rather considered as "input" data for the emulation engine.

#### 3. Emulation Engine

The emulation engine is what drives the guest program's execution. As the process virtual machine's central component, it arranges the collaboration of all other

components. It uses binary translation or interpretation to execute the instructions contained within the guest memory image.

#### 4. Profile data

A process virtual machine may use profile data to optimize the runtime behaviour of the guest program. Most commonly, profile data is used to switch between translation and interpretation. During binary translation, it may also be used to support various optimizations.

#### 5. OS Call Emulator

As the guest program executes an operating system call, the OS call emulator has to emulate the expected operating system behaviour. Depending on the emulated and the host operating system, this may involve translating the guest OS call into a host OS call and marshalling data between both environments. After the call has been executed, the call's result has to be translated into the format expected by the guest.

#### 6. Code Cache and Code Cache Manager

Especially when using binary translation, it is necessary to store translated blocks of code and retrieve them for later reuse. The code cache stores the appropriate target code while the code cache manager decides which code portions to replace in case the cache grows too large.

#### 7. Exception emulation

This component manages the emulation of exception conditions. Depending on the host operating system, this may involve intercepting signals or interrupts from the host and translating them into the format expected by the guest. Exception emulation may be tightly coupled to the emulation engine, which must emulate the *precise guest state (including program counter, register values and trap conditions)* when an exception occurs [Smith2005, p. 87].

#### 2.4 The ARM Architecture

The ARM Architecture is based upon a microprocessor developed by Acorn Computers Limited between 1983 and 1985. This microprocessor, called the ARMv2, was the world's first commercial Reduced Instruction Set Computer (RISC). To market the new processor architecture, ARM Ltd. was formed in 1990 as a joint venture with Apple Computer and VLSI Technology. Since then, ARM Ltd. has become *the*

industry's leading provider of 32-bit embedded RISC microprocessors with almost 75% of the market [Allison2002].

RISC is a microprocessor design philosophy that favours a simpler instruction set. While Complex Instruction Set Computer (CISC) architectures aim to provide powerful and varied instructions, RISC architectures focus on executing a small set of instructions. This makes them easier to implement and more amenable to optimization. RISC architectures often achieve competitive performance through higher clock rates, lower Clocks per Instruction (CPI) ratios and other advanced features.

RISC designs usually share three common features that are visible from a programmer's point of view [Furber2000, p. 24f]:

#### 1. Load-store architecture

Only load and store instructions access memory, while all other instructions work on register operands. This reduces the complexity of the instruction set.

#### 2. Fixed instruction sizes

In machine code, all instructions are represented by the same number of bits. Fixed instruction sizes allow a whole instruction to be retrieved by a single memory fetch, increasing the efficiency of the instruction decoder.

#### 3. Large amount of registers

The original RISC design featured 32 general purpose processor registers, far more than even modern CISC microprocessors, such as the Intel P4 Architecture, offer. The vast number of registers reduces the performance penalty that comes with separate instructions for memory operand fetches.

By constraining the architecture in the described way, RISC designs can be implemented on smaller die sizes and in shorter time, while still maintaining high performance due to the ability to hardwire the instruction decoder and pipeline the instruction execution [Furber2000, p. 25ff].

The ARM architecture is a RISC microprocessor design. It features a load-store architecture with fixed-length 32-bit instructions and a 3-address instruction format. However, it is not a pure RISC design. Some popular RISC features have not been implemented into the ARM architecture: delayed branches, register windows and the execution of instructions in a single-cycle. Instead, CISC instructions have been

included for a small number of commonly used operations, namely multi-register data transfers and compare-and-swap instructions.

|      | Privileged Modes |                                           |         |         |          |         |

|------|------------------|-------------------------------------------|---------|---------|----------|---------|

|      |                  | Exception Modes                           |         |         |          |         |

| User | System           | Supervisor Abort Undefined Interrupt Fast |         |         | Fast IRQ |         |

| R0   | R0               | R0                                        | R0      | R0      | R0       | R0      |

| R1   | R1               | R1                                        | R1      | R1      | R1       | R1      |

| R2   | R2               | R2                                        | R2      | R2      | R2       | R2      |

| R3   | R3               | R3                                        | R3      | R3      | R3       | R3      |

| R4   | R4               | R4                                        | R4      | R4      | R4       | R4      |

| R5   | R5               | R5                                        | R5      | R5      | R5       | R5      |

| R6   | R6               | R6                                        | R6      | R6      | R6       | R6      |

| R7   | R7               | R7                                        | R7      | R7      | R7       | R7      |

| R8   | R8               | R8                                        | R8      | R8      | R8       | R8_fiq  |

| R9   | R9               | R9                                        | R9      | R9      | R9       | R9_fiq  |

| R10  | R10              | R10                                       | R10     | R10     | R10      | R10_fiq |

| R11  | R11              | R11                                       | R11     | R11     | R11      | R11_fiq |

| R12  | R12              | R12                                       | R12     | R12     | R12      | R12_fiq |

| R13  | R13              | R13_svc                                   | R13_abt | R13_und | R13_irq  | R13_fiq |

| R14  | R14              | R14_svc                                   | R14_abt | R14_und | R14_irq  | R14_fiq |

| PC   | PC               | PC                                        | PC      | PC      | PC       | PC      |

| CPSR | CPSR             | CPSR                                      | CPSR    | CPSR    | CPSR     | CPSR    |

|      |                  | SPSR                                      | SPSR    | SPSR    | SPSR     | SPSR    |

Figure 6 - ARM Register Layout Inspired by [ARM2000, p. A2-4]

As illustrated in Figure 6, the ARM processor has 16 general purpose user-mode registers, each 32-bit in size. An additional register, the Current Program Status Register (CPSR) maintains a number of flags:

#### 1. Four arithmetical flags

The negative, zero, carry and overflow flag can be set by arithmetic operations. Many processors update the flags after each arithmetical operation. On ARM, most instructions come in two versions, which either do or do not update the arithmetical flags.

#### 2. Two Interrupt flags

The ARM architecture supports two types of hardware interrupts: normal interrupts (IRQs) and fast interrupts (FIQ), with the latter taking precedence over the former. Two bits within the CPSR can be used to mask both types of interrupts.

#### 3. One Thumb flag

Some ARM processors support two instruction sets: the "regular" ARM instruction set with 32-bit instructions and the Thumb instruction set, which provides compressed 16-bit instructions. The Thumb instruction set has been developed to provide better code density. Section 2.4.1 discusses it in more detail. This flag denotes which instruction set is currently executed.

#### 4. Five operating mode flags

The processor's operating mode determines the layout of the register map, availability of certain instructions and can influence memory access privileges, if the system is equipped with a Memory Management Unit (MMU). The ARM processor distinguishes seven operating modes, all of which are listed in Figure 6. The undefined instruction and memory abort modes are used when trapping undefined instructions or illegal memory accesses (prefetch or data aborts). The undefined instruction trap is also invoked when an instruction for a missing coprocessor is encountered. Therefore it is commonly used to perform software emulation in systems where no floating point coprocessor is installed. The *interrupt* and fast interrupt modes are entered to handle the respective hardware interrupts, while software interrupts or system calls are handled in *supervisor mode*. Interrupts are only raised between executions of two instructions [ARM2000, p. A1-4], while aborts can occur during instruction execution, as long as enough state is preserved to restart the current instruction. System mode is equivalent to supervisor mode, but permits access to all user mode registers. Finally, user mode offers the least privileges and is the mode that user processes are usually running in. When an exception is processed, the processor changes its operating mode accordingly and executes a branch instruction from the exception vector<sup>17</sup> to reach the exception handler. The exception type serves as an offset into the exception vector. In addition to the 16 general purpose registers, the ARM processor also contains 15 shadow registers for system-level programming and exception handling. Depending on the processor's operating mode, the shadow registers overlay some of the general-purpose registers. During normal operation, they are not visible to the programmer. Using shadow registers, the ARM processor saves enough state before processing an exception to allow execution to be resumed later as if the exception did not occur. In order to support context switching, ARM also provides special instructions that allow accessing the user mode registers from privileged modes [Furber2000, p. 310].

\_

<sup>&</sup>lt;sup>17</sup> The exception vector is commonly stored at the beginning of the memory map. It is expected to contain branch instructions, though it may, strictly speaking, contain any ARM instruction.

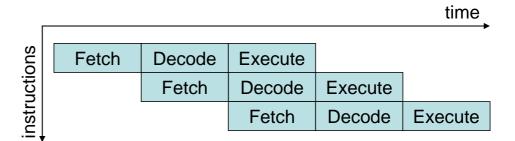

The ARM architecture features a three stage instruction pipeline<sup>18</sup>, which improves processor performance by overlapping the execution of adjacent instructions. The ARM pipeline is split into a fetch, decode and execute stage, omitting the *operand fetch* and *operand store* stages from the classical RISC pipeline [Clements1991, p. 279]. At each pipeline stage, an instruction uses either the memory, the data path or the processor's decode logic, as shown in Figure 7. Note that the before-mentioned CISC instructions may stall the pipeline, as they can occupy the decode and execute stages for more than one cycle. The ARM pipeline is partially visible to the programmer. An instruction reading the program counter (PC) register during the execute stage will actually retrieve the address of the next but one instruction.

Figure 7 – The ARM 3-stage pipeline

#### 2.4.1 Programmer's Model

Most ARM processors support two instruction sets: the regular 32-bit ARM and the optional 16-bit Thumb instruction set. This section describes the features of the regular ARM instruction set, unless stated otherwise.

The ARM instruction set is a fixed-length instruction set, with each instruction being 32-bits long. *The ARM instruction set can be divided into six broad instruction classes*:

- Branch instructions

- Data-processing instructions

<sup>18</sup> The ARM9 processor family improves upon the performance of previous ARM processors by using a five-stage pipeline and simulating a Harvard architecture (using a separate data and instruction cache). Nevertheless, for backwards compatibility the ARM9 still simulates the "program-visible" parts of the three-stage pipeline as described here.

- Status register transfer instructions

- Load and store instructions

- Coprocessor instructions and

- Exception-generating instructions [ARM2000, p. A1-5].

Almost<sup>19</sup> all ARM instructions can be executed conditionally, depending on the values of the arithmetical flags. The condition is determined by a 4-bit *condition field* within the binary instruction encoding and allows

- tests for equality and non-equality

- tests for <, <=, > and >= inequalities, in signed and unsigned arithmetic

- *each condition code flag to be tested individually* [ARM2000, p. A1-5].

Branches are expensive, because they flush the instruction pipeline. The ARM instruction set also offers conditional execution of instructions, which does not suffer from this drawback and is therefore commonly used as a alternative for conditional branches and to unroll loops. Code 1 illustrates this by comparing two assembly functions for copying memory regions. The left one relies on conditional branches, while the right one uses conditional execution to unroll the copy loop. Not only does the unrolled version execute 25% less instructions than the normal version, its longer instruction sequence also makes much better use of the ARM pipeline, leading to a better CPI ratio.

| MemMove_Normal MemMove_Unrolled |                     | Unrolled      |                  |

|---------------------------------|---------------------|---------------|------------------|

| LDR                             | r4, [r1], #1        | CMP           | r3, #2           |

| STR                             | r4, [r2], #1        | LDR           | r4, [r1], #1     |

| ADDS                            | r3, r3, # <b>-1</b> | STR           | r4, [r2], #1     |

| B <b>GT</b>                     | MemMove_Normal      | LDRGE         | r4, [r1], #1     |

|                                 |                     | STRGE         | r4, [r2], #1     |

|                                 |                     | LDR <b>GT</b> | r4, [r1], #1     |

|                                 |                     | STRGT         | r4, [r2], #1     |

|                                 |                     | ADDS          | r3, r3, #-3      |

|                                 |                     | B <b>GT</b>   | MemMove_Unrolled |

Code 1 - Normal and unrolled ARM Assembly code for a Memory Copy operation<sup>20</sup>. The usage of conditional execution is highlighted.

<sup>&</sup>lt;sup>19</sup> Architecture versions up to ARMv5 supported conditional execution for all instructions [ARM2000, p. A3-5]. Enhancements to the ISA have since then occupied the encodings of some conditional instructions.

Although the ARM architecture is built upon RISC principles, it provides a high number of addressing modes, for arithmetic as well as load and store instructions. Table 1 gives an overview of the available addressing modes. Most of this flexibility is provided by the barrel shifter, which sits on the processor's B-bus and can perform shift operations on one of the two ALU operands. Additionally, the barrel shifter can also provide a carry flag for logical operations that do not usually create a carry (e.g. AND, OR, etc.).

| <b>Instruction Class</b> | Addressing Modes                                                |

|--------------------------|-----------------------------------------------------------------|

| Data Processing          | Immediate                                                       |

|                          | Register                                                        |

|                          | Logical shift left by register / immediate                      |

|                          | Logical shift right by register / immediate                     |

|                          | Arithmetic shift right by register / immediate                  |

|                          | Rotate right by register / immediate                            |

|                          | Rotate right with extend                                        |

| Load / Store             | Immediate offset / pre-indexed / post-indexed                   |

|                          | Register offset / pre-indexed / post-indexed                    |

|                          | Scaled register offset / pre-indexed / post-indexed             |

| Load / Store             | Increment address before / after transfer (optional write back) |

| Multiple                 | Decrement address before / after transfer (optional write back) |

| Load / Store             | Immediate offset / pre-index / post-indexed                     |

| Coprocessor              | Consecutive memory reads                                        |

Table 1 – ARM Addressing Modes

Adhering to the RISC principles, ARM instructions commonly take three 32-bit operands. Additionally ARM can access other operand types using powerful load-and-store instructions. For instance, the single-register load-and-store instructions also accept other data types, such as signed and unsigned half-words (16 bits) and bytes. Other data transfer instructions can transfer an arbitrary number of registers (including the CPSR) in a single instruction.

The exceptional characteristic of ARM coprocessor instructions is that their exact meaning is not defined by the instruction set, but rather by the coprocessor itself. In the ARM architecture, coprocessors are supported using a flexible "plug-in" system. Each coprocessor within a system is assigned a unique id. Coprocessors listen to the instructions executed by the processor, ignoring all ARM instructions and instructions

<sup>&</sup>lt;sup>20</sup> Both code snippets assume that at least one word is to be copied. The ARM processor also provides multi-word data transfer operations. For the purpose of this example, these were omitted.

for other coprocessors. Once they encounter an instruction that they are supposed (and able) to execute, they will signal this to the CPU, stalling the instruction pipeline until the coprocessor instruction has been processed. The ARM ISA provides instructions that allow the *processor to initiate a coprocessor data processing operation, ARM registers to be transferred to and from coprocessor registers* and *addresses* [to be generated] for coprocessor load and store instructions [ARM2000, p. A3-25].

Most instructions accept any of the 16 general purpose registers as a target or operand. Though the registers can be used in such a versatile manner, there are two hardware restrictions and a couple of software conventions that apply to register usage. The hardware restrictions are:

#### 1. Register 15 serves as the program counter

Though register 15 (r15) contains the program counter, it can still be used as an operand, as long as the ARM pipeline behaviour is taken into account. When reading from r15, the address of the next instruction but one is returned<sup>21</sup>, while writing to r15 flushes the pipeline and branches to the written address. Furthermore, the Branch-And-Exchange instructions (BX and BLX) may also use the first bit of the new program counter value to determine the target instruction set.

#### 2. Register 14 serves as the link register

Like most instruction set architectures, the ARM architecture provides support for function calls with an instruction that will branch to a destination address and put the address of the instruction following the branching instruction into the link register. The ARM architecture features three different Branch-And-Link instructions<sup>22</sup>, all of which use register 14 as the link register. Nevertheless, the register may be used as a general purpose target and source operand register with all other instructions.

<sup>22</sup> Architecture version 5 provides the BL and BLX instruction, the latter of which is available in two addressing modes.

-

<sup>&</sup>lt;sup>21</sup> For instructions that occupy any of the pipeline stages for longer than one cycle, the result of reading from the program counter is implementation defined.

Additionally to these restrictions, there are a number of software conventions, which are commonly followed. They are captured within the ARM Procedure Call Standard<sup>23</sup> (APCS). The APCS defines register usage conventions, procedure call conventions and the stack layout [STD1998, p. 6-4ff].

The APCS register layout defines the first four registers as "scratch registers", i.e. registers that do not need to be preserved by functions. The following six registers (r4r9) serve as variable registers. They need to persist across function calls. The remaining six registers have special uses, though they can be treated as variable registers, if their special functionality is not required by the program. The stack limit register (r10) contains the maximum address that the stack can grow to. It can be used to perform software stack overflow checking. The frame pointer (r11) contains a pointer to the stack frame (or activation record) of the active function. The stack frame stores a function's local variables, return address and parameters passed into the function. Register 12 contains the Intra-Procedure-call scratch register. The linker is often required to insert a veneer between a calling and a called function. In dynamic linking, the veneer may be part of the Procedure Linkage Table (PLT); in static linking it may be a piece of code that compensates for the ARM BL instruction being unable to address the whole 32-bit address space [ARM2000, p. A4-10]. The Intra-Procedure-call register can be used as a scratch register by the linker. Furthermore, it can also be used within a routine to hold intermediate values between subroutine calls [Earnshaw2006, p. 14]. Finally, the stack pointer (r13) holds the address of the top of the stack. By default, the APCS uses a full descending stack.

Code density is a measure for *the amount of space that an executable program takes up in memory* [Computer Desktop Encyclopedia: Code Density]. In embedded systems, code density is important to enable low power consumption. Higher code density not only results in less memory being needed for a particular piece of software, but also allows significant power savings by reducing cache activity, which can amount to about 22% of the total energy expended by a system [Gupta2002]. RISC systems traditionally

<sup>23</sup> See [Earnshaw2006] for a complete definition of the APCS.

.

suffer from lower code density than CISC systems [Dandamudi2005]. The Thumb instruction set addresses this disadvantage on the ARM architecture.

Many ARM processors incorporate a second instruction set, the Thumb instruction set. Thumb offers a restricted functional subset of the ARM instruction set with each Thumb instruction being only 16 bits long. The goal is to provide higher code density, by limiting instructions to those that are frequently used by compilers.

The Thumb instruction set is not a complete ISA and relies on *recourse to the full ARM instruction set where necessary* [Furber2000, p.188]. Apart from certain subtleties, all Thumb instructions can be translated into equivalent ARM instructions [ARM2000, p. A6-2]. In contrast to the ARM instruction set, Thumb mostly contains 2-address instructions that are executed unconditionally. Thumb also hard codes the APCS assumption of register 13 being the stack pointer into the instruction set. Furthermore, the accessible register set is restricted to the eight registers for most instructions. While ARM instructions set the condition codes optionally, Thumb instruction always set the condition codes when executing data processing instructions.

Despite these restrictions, Thumb has an impressive track record. A typical Thumb program requires 70% of the space of ARM code, while needing 40% more instructions. Nevertheless, when being run from 16-bit memory Thumb code is about 45% faster than ARM code. Finally, using Thumb code needs about 30% less energy than equivalent ARM code [Furber2000, p. 203].

### 2.4.2 IO and Memory Model

The ARM architecture uses a linear address space of 2<sup>32</sup> bytes. The word size is 32 bits with the endianess being configurable by a processor input pin. ARM usually expects word addresses to be aligned at 4-byte boundaries. Some architecture versions are also able to access 16-bit half-words aligned at 2-byte boundaries. Accesses that are not aligned according to these rules are called *unaligned accesses*. The behaviour of an ARM processor for an unaligned access differs on the specific system and the instruction used. Generally, the results are either unpredictable or cause an alignment

exception<sup>24</sup>. However, some instructions specifically ignore the bottom address bits or use them to control a rotation of the loaded data<sup>25</sup>.

Similar to other RISC processors, ARM does not provide special instructions to communicate with I/O devices. Instead, it uses memory-mapped I/O, where regions of memory are overlapped with I/O device registers. To avoid the related caching issues, the ARM System Control Coprocessor supports marking regions of memory as uncacheable and unbufferable.

#### 2.4.3 Architecture Versions

Having been developed from 1985, the ARM architecture underwent several architectural revisions. The very first version (ARMv1) mostly served as an evaluation architecture for Acorn. It was only used as a second processor to the BBC microcomputer and manufactured in very small numbers [Furber2000, p. 147]. Nevertheless, it is today known as the first commercially exploited RISC architecture [Furber2000, p. 147]. The ARMv2 architecture was used in the Acorn Archimedes computer. As the ARMv1, it only had a 26-bit address bus, but did already feature a multiplication instruction. The ARM3 chip introduced the ARMv2a architecture version. It enhanced the previous design with two atomic compare-and-swap instructions and established a standard for the System Control Coprocessor, now widely integrated as coprocessor 15 in most ARM systems. Furthermore, it was the first ARM processor to include a 4kb cache. The following architecture version, ARMv3 was the first version to use a 32-bit address space. It also introduced new aborts (undefined instruction and memory aborts) as well as 64-bit multiplication for certain architecture revisions. The ARMv4 is the oldest version of the architecture supported today [ARM Website]. Its main innovation was the introduction of the Thumb instruction set in the ARMv4T architecture revision. As it was the first architecture version that was built upon a formal specification, certain instruction combinations were deprecated (specifically reading the program counter in instructions that spend more than one cycle in the execute pipeline phase). With the release of the ARMv5T architecture, new

-

<sup>&</sup>lt;sup>24</sup> This only applies to systems containing a MMU capable of checking access alignments.

<sup>&</sup>lt;sup>25</sup> This behaviour is exhibited by the LDR and SWP instructions.

instructions were added to the instruction set that were *greatly improving compiler* capabilities and the ability to mix and match ARM versus Thumb routines [ARM Website]. The most recent architecture versions, ARMv6 and ARMv7 are specifically targeted at advanced applications. They provide Single Instruction Multiple Data instructions for multimedia applications, the TrustZone security extensions and support for dynamic compilers.

### 3 Pearcolator Architecture