## Real time Spaun on SpiNNaker

Functional brain simulation on a massively-parallel computer architecture

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF SCIENCE AND ENGINEERING

2016

Andrew Mundy School of Computer Science

## **Contents**

| A | Abstract |                                                                | 13 |

|---|----------|----------------------------------------------------------------|----|

| 1 | Intr     | oduction                                                       | 21 |

| 2 | Neu      | irons, synapses and representation                             | 27 |

|   | 2.1      | Modelling the nervous system                                   | 27 |

|   |          | Leaky Integrate-and-Fire model                                 | 28 |

|   |          | Neural networks and synapses                                   | 29 |

|   | 2.2      | The Neural Engineering Framework                               | 30 |

|   |          | Representation                                                 | 32 |

|   |          | Transformation                                                 | 40 |

|   |          | Dynamics                                                       | 43 |

|   | 2.3      | The Semantic Pointer Architecture                              | 45 |

|   |          | Representing and operating on symbols                          | 45 |

|   | 2.4      | Cognitive architectures and Spaun                              | 50 |

|   |          | Action selection and execution                                 | 50 |

|   |          | Spaun: The Semantic Pointer Architecture Unified Network model | 53 |

|   | 2.5      | Summary                                                        | 53 |

| 3 | Mod      | delling and simulation                                         | 57 |

|   | 3.1      | Nengo: modelling with the Neural Engineering Framework         | 57 |

|   |          | The Nengo object model                                         | 58 |

|   |          | Nengo simulators                                               | 58 |

|   | 3.2      | Simulating neural networks                                     | 59 |

|   |          | General Purpose Graphics Processing Units (GP-GPUs)            | 60 |

|   |          | Neuromorphic hardware                                          | 61 |

|   |          | Field-Programmable Gate Arrays (FPGAs)                         | 62 |

|   | 3.3      | SpiNNaker                                                      | 63 |

|   |          | Hardware                                                       | 63 |

|   |          | Neural simulation                                              | 65 |

|   |          | Placement and routing                                          | 68 |

| 4 | The | Neural Engineering Framework and SpiNNaker                | 71  |

|---|-----|-----------------------------------------------------------|-----|

|   | 4.1 | Mapping the Neural Engineering Framework to SpiNNaker     | 71  |

|   | 4.2 | Communicating with values, not spikes                     | 74  |

|   |     | Simulating neurons                                        | 77  |

|   |     | Simulating synapses                                       | 77  |

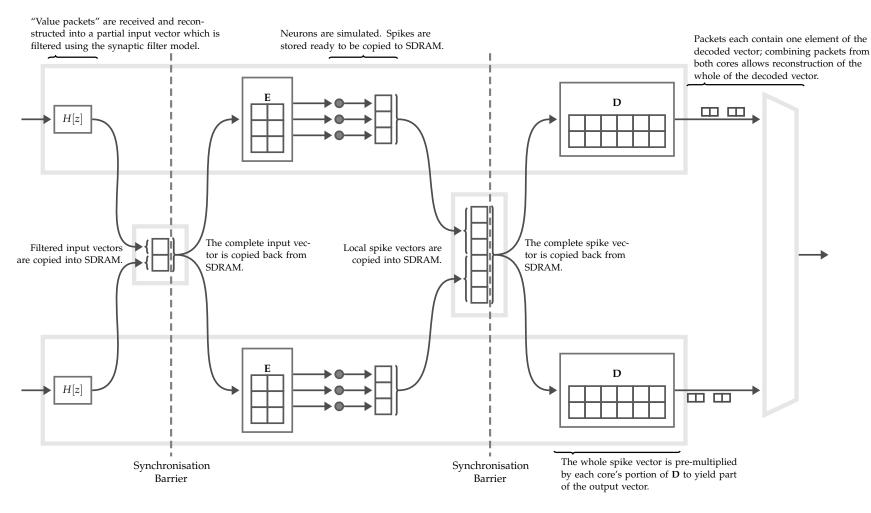

|   | 4.3 | Using shared-memory parallelism to reduce network traffic | 80  |

|   |     | Overview of the solution                                  | 81  |

|   |     | Parallel simulation of neurons                            | 83  |

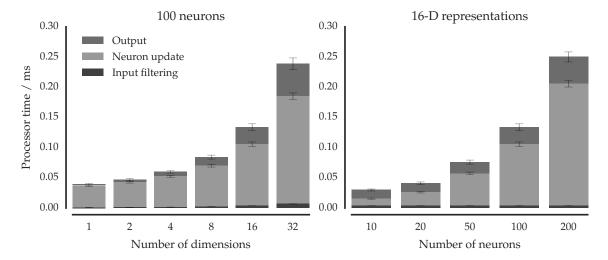

|   |     | Analysis                                                  | 83  |

|   | 4.4 | Performance                                               | 85  |

|   |     | Single-core processor utilisation                         | 85  |

|   |     | Multiple-core processor utilisation                       | 89  |

|   |     | Packet processing cost                                    | 89  |

|   |     | Network loading                                           | 90  |

|   | 4.5 | Correctness                                               | 90  |

|   |     | Neural tuning curves                                      | 92  |

|   |     | Representation                                            | 92  |

|   |     | Transformation                                            | 92  |

|   |     | Dynamics                                                  | 94  |

|   | 4.6 | Summary                                                   | 94  |

| 5 | The | Semantic Pointer Architecture and SpiNNaker               | 97  |

|   | 5.1 | Representing high-dimensional values                      | 97  |

|   |     | Large or small ensembles?                                 | 100 |

|   |     | Techniques for improving reliability                      | 101 |

|   | 5.2 | Interposer design                                         | 102 |

|   |     | Row partitioning                                          | 104 |

|   |     | Block partitioning                                        | 105 |

|   |     | Interposer costs                                          | 107 |

|   |     | Scheduling and timing                                     | 108 |

|   |     | Summary                                                   | 110 |

|   | 5.3 | Circular convolution                                      | 111 |

|   |     | Interposer parameter selection                            | 113 |

|   |     | Comparison to spiking implementation                      | 118 |

|   | 5.4 | Results                                                   | 119 |

|   | 5.5 | Summary                                                   | 123 |

| 6 | Rou | ting table minimisation                                   | 125 |

|   | 6.1 | Introduction                                              | 125 |

|   | 62  | Ranchmarks                                                | 126 |

|    | 6.3   | Routing table compaction        | 128  |

|----|-------|---------------------------------|------|

|    |       | "Order-exploiting" minimisation | 129  |

|    |       | On-chip logic minimisation      | 130  |

|    | 6.4   | Ordered-Covering                | 131  |

|    |       | Resolving the up-check          | 133  |

|    |       | Resolving the down-check        | 134  |

|    | 6.5   | Results                         | 136  |

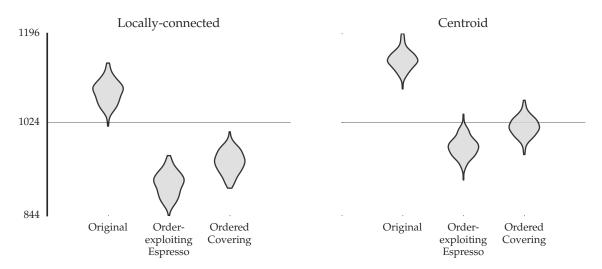

|    |       | Compression                     | 136  |

|    |       | Memory usage                    | 136  |

|    |       | Execution time                  | 138  |

|    | 6.6   | Summary                         | 139  |

| 7  | Con   | clusion – Spaun and SpiNNaker   | 141  |

|    | 7.1   | SpiNNaker                       | 143  |

|    | 7.2   | Spaun                           | 146  |

|    | 7.3   | Future work                     | 146  |

|    | 7.4   | Summary                         | 147  |

| D. | foror | acos                            | 1/10 |

This thesis contains 29 904 words.

## **List of Figures**

| 1.1  | Representation of the Spaun model                                      | 22 |

|------|------------------------------------------------------------------------|----|

| 2.1  | Simulation of a LIF neuron                                             | 29 |

| 2.2  | Varying parameters of a LIF neuron                                     | 31 |

| 2.3  | Postsynaptic currents from three weighted and shaped spikes            | 31 |

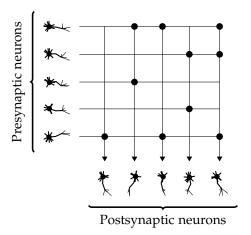

| 2.4  | Sample weight matrix between two populations of neurons                | 31 |

| 2.5  | Response of a pair of LIF neurons to a time-varying input signal       | 33 |

| 2.6  | Response of a population of LIF neurons to a time-varying input signal | 34 |

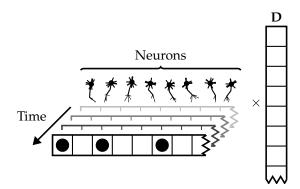

| 2.7  | Decoding the output of a population of neurons                         | 35 |

| 2.8  | Multiplying the tuning curves of a population by the decoders          | 35 |

| 2.9  | Representing a 2D value with four neurons                              | 37 |

| 2.10 | Decoding $x^2$ from a pair of neurons                                  | 41 |

| 2.11 | Decoding the square of the value represented by an ensemble            | 41 |

| 2.12 | Applying a linear transform to the decoding of an ensemble             | 42 |

| 2.13 | Using a recurrent connection to implement a dynamic system             | 44 |

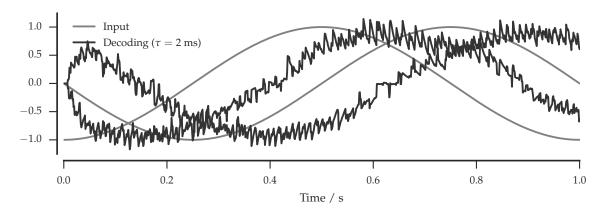

| 2.14 | Simulation of a neurally implemented integrator                        | 44 |

| 2.15 | High-level view of a symbol unbinding neural network                   | 48 |

| 2.16 | Simulation of a neural implementation of symbol unbinding              | 49 |

| 2.17 | Block diagram of Spaun                                                 | 52 |

| 2.18 | A neurally implemented state machine                                   | 52 |

| 2.19 | Spaun performing a fluid reasoning task                                | 54 |

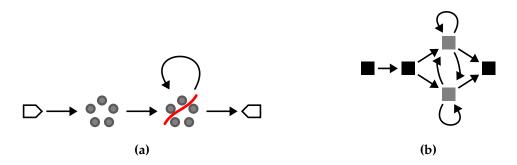

| 3.1  | Simple serial neural simulator                                         | 59 |

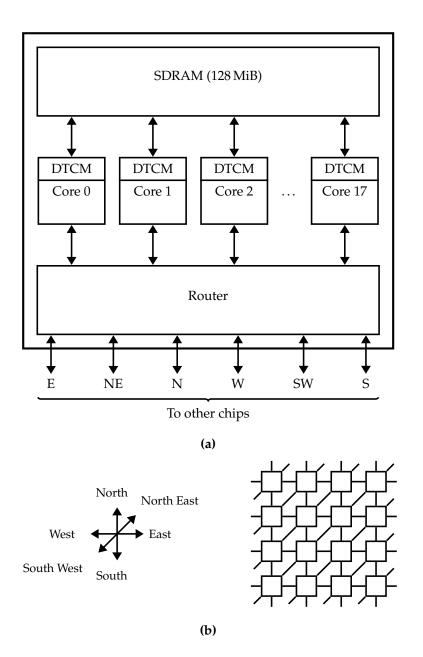

| 3.2  | SpiNNaker chip and network                                             | 64 |

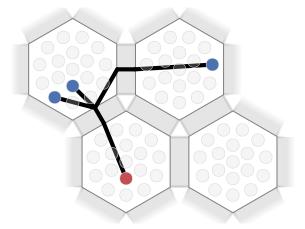

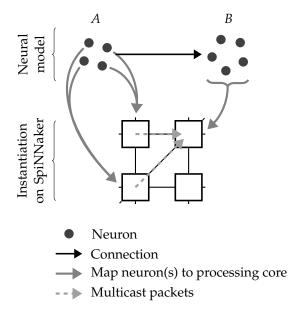

| 3.3  | Multicasting packets across the SpiNNaker architecture                 | 65 |

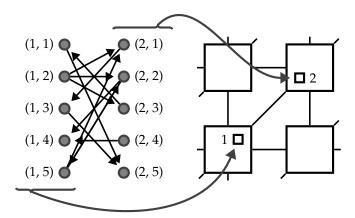

| 3.4  | Sample neural network mapped to a SpiNNaker machine                    | 66 |

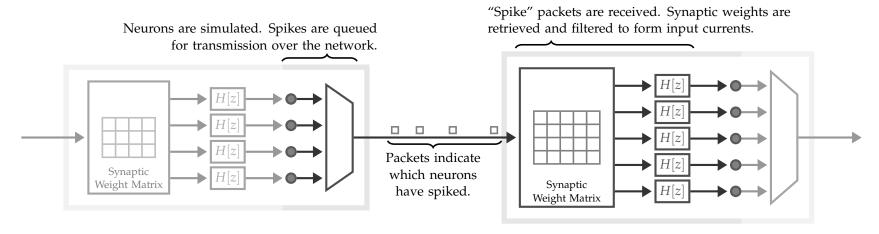

| 3.5  | Simulation of neural nets on SpiNNaker                                 | 67 |

| 3.6  | Neural network represented as a data flow graph                        | 69 |

| 3.7  | Partitioning a population of neurons                                   | 69 |

| 3.8  | Partitioning, place and routing a neural network                       | 70 |

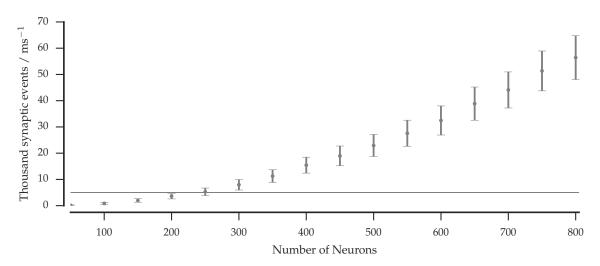

| 4.1  | Synaptic events in an $n$ -dimensional communication channel           | 73 |

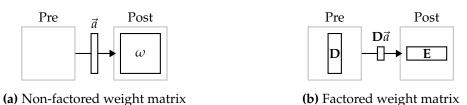

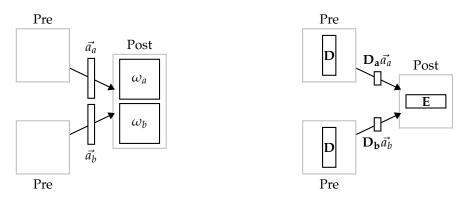

| 4.2  | Comparison between non-factored and factored weight matrices               | 74         |

|------|----------------------------------------------------------------------------|------------|

| 4.3  | Multiple fan-in for non-factored and factored weight matrices              | <b>7</b> 5 |

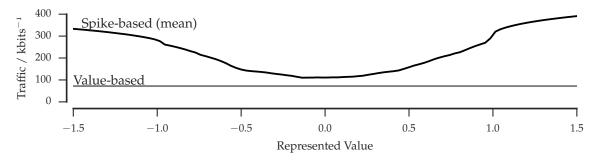

| 4.4  | Sample traffic rates for a simple neural network                           | 76         |

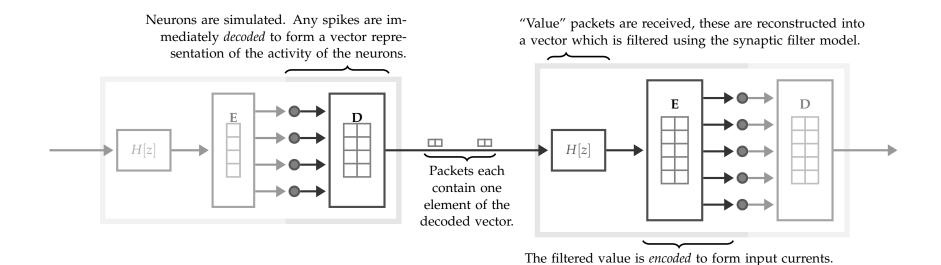

| 4.5  | "Value"-based method of simulating neural nets on SpiNNaker                | 78         |

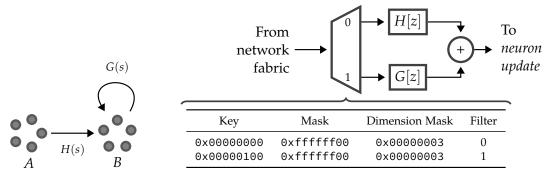

| 4.6  | Example of routing packets to synapse models                               | 79         |

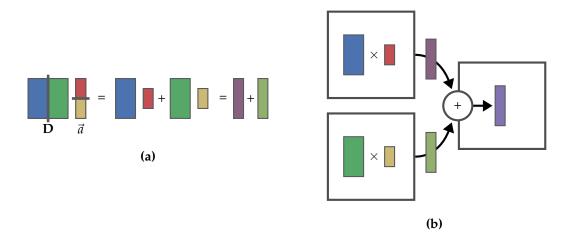

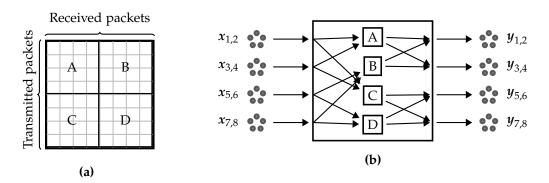

| 4.7  | Column-wise division of the decoding operation                             | 81         |

| 4.8  | Row-wise division of the decoding operation                                | 82         |

| 4.9  | Shared memory simulation of a population of ensembles                      | 84         |

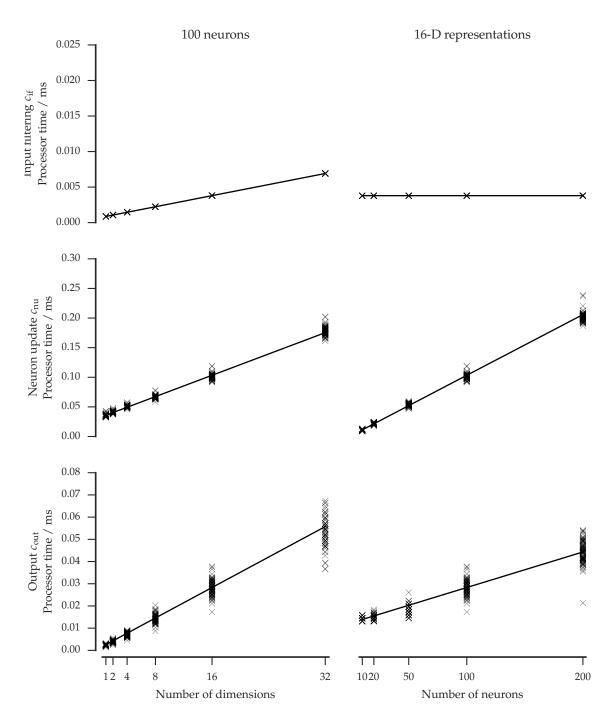

| 4.10 | Single-core performance of the ensemble implementation                     | 86         |

| 4.11 | Modelled and recorded ensemble performance                                 | 88         |

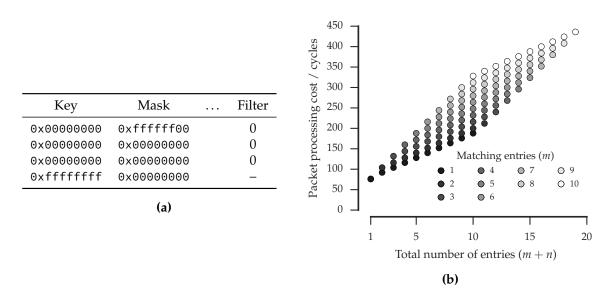

| 4.12 | Measuring the packet processing cost                                       | 91         |

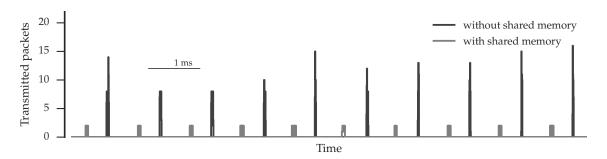

| 4.13 | Packets transmitted for a 16-D decoding of an 800-neuron ensemble          | 91         |

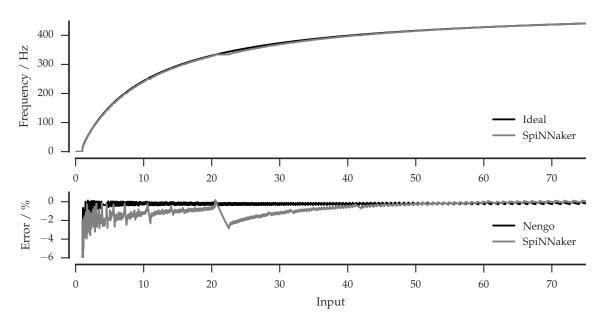

| 4.14 | Tuning curve of LIF implementation                                         | 93         |

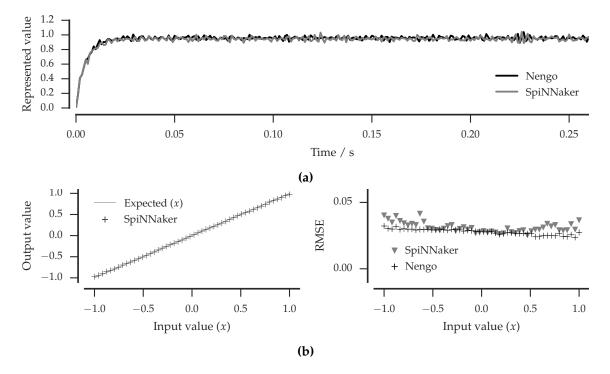

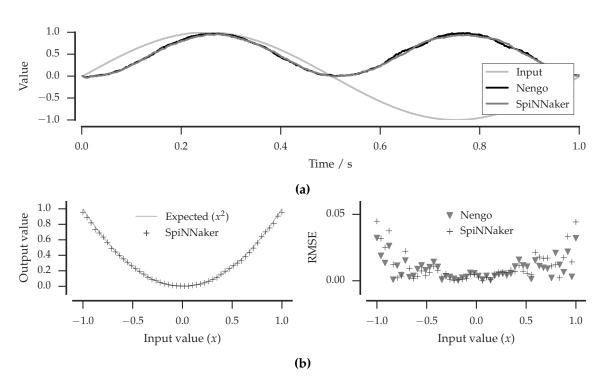

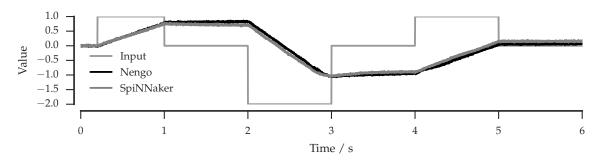

| 4.15 | Representing values with neurons on SpiNNaker                              | 93         |

| 4.16 | Transforming values with neurons on SpiNNaker                              | 95         |

| 4.17 | Sample output of a neural integrator implemented with the NEF              | 95         |

| 5.1  | Splitting large ensembles to reduce decoder compute time                   | 98         |

| 5.2  | Splitting large ensembles increases communication                          | 100        |

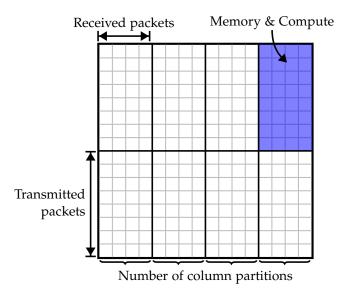

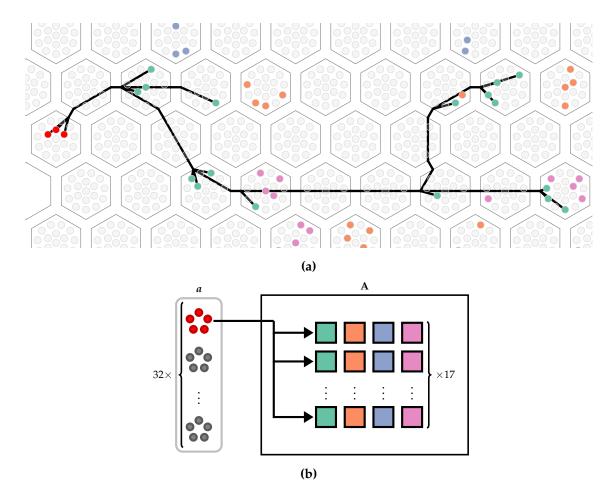

| 5.3  | Use of an interposer to decrease fan-out, fan-in and overall traffic       | 103        |

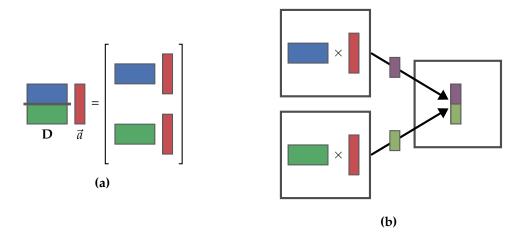

| 5.4  | Implementation of an interposer core                                       | 104        |

| 5.5  | Row-based decomposition of the interposer matrix                           | 104        |

| 5.6  | Block-based decomposition of the interposer matrix                         | 105        |

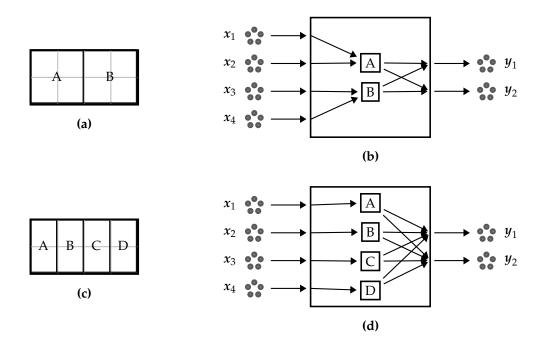

| 5.7  | Column-partitions affect the number of packets received downstream         | 107        |

| 5.8  | Interposer and partition costs                                             | 108        |

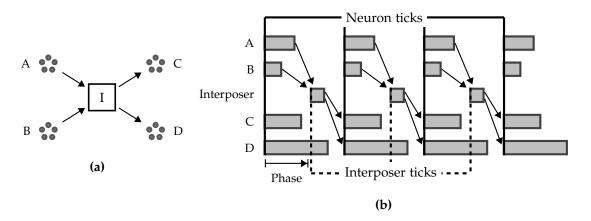

| 5.9  | Interposer timing                                                          | 109        |

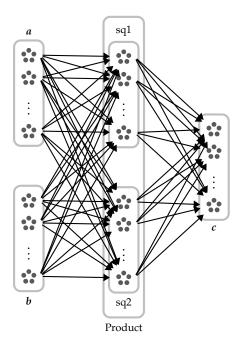

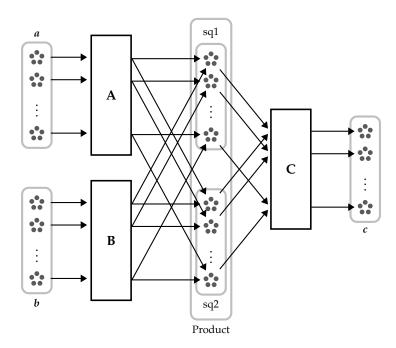

| 5.10 | Neural network implementation of circular convolution                      | 112        |

| 5.11 | Circular convolution network with interposers                              | 113        |

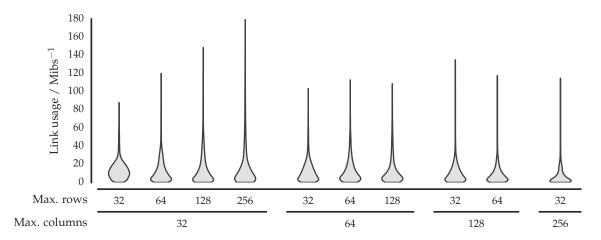

| 5.12 | SpiNNaker link loads for the circular convolution network                  | 114        |

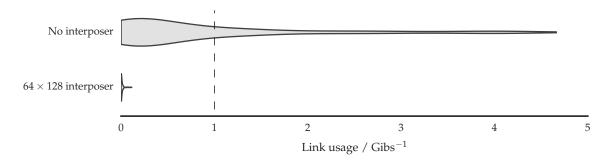

| 5.13 | Circular convolution link usage with and without interposers               | 115        |

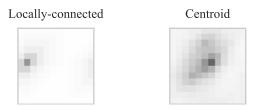

| 5.14 | Section of the place-and-route solution for circular convolution           | 117        |

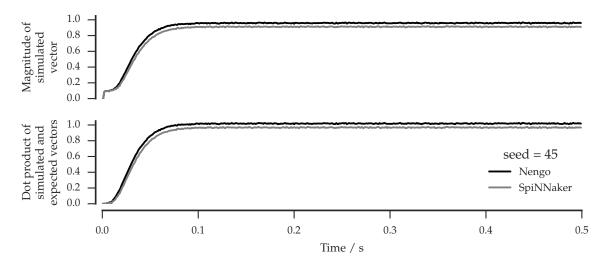

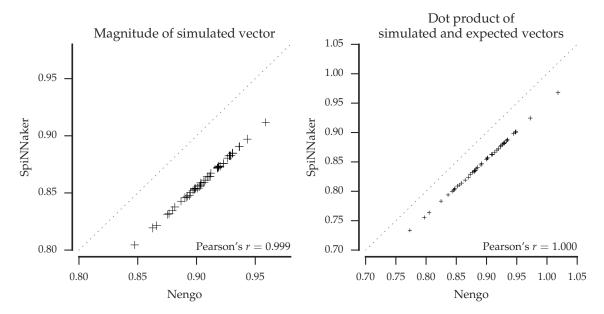

| 5.15 | Sample of 512-D circular convolution simulation results                    | 120        |

| 5.16 | Comparison of 512-D circular convolution simulation results                | 120        |

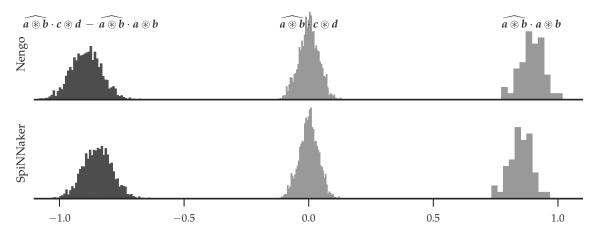

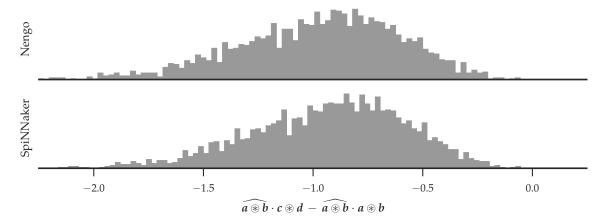

| 5.17 | Distributions over the dot products of convolved vectors                   | 121        |

| 5.18 | Distribution over the dot products of convolved 16-D vectors               | 122        |

| 6.1  | Benchmark network connectivity                                             | 127        |

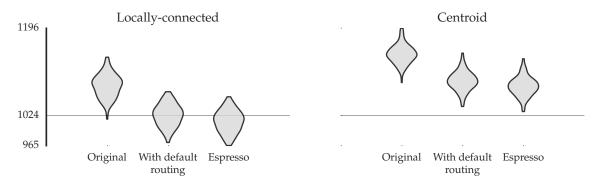

| 6.2  | Benchmark routing tables after removing default routes, and using Espresso | 128        |

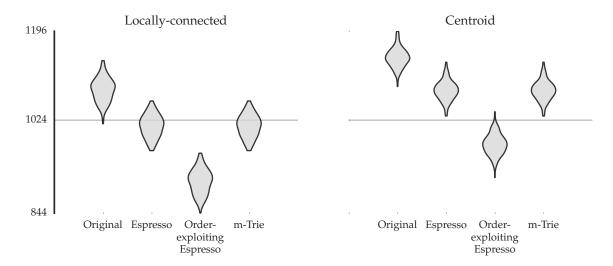

| 6.3  | Benchmark performance of order-exploiting Espresso and m-Trie              | 130        |

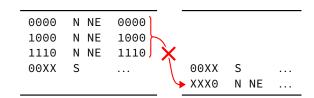

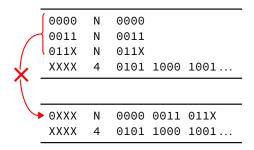

| 6.4  | Examples of invalid merges as defined by the Ordered-Covering rules        | 132        |

| 6.5 | Benchmark performance of Ordered-Covering | 137 |

|-----|-------------------------------------------|-----|

| 7.1 | SpiNNaker machines                        | 144 |

## **List of Tables**

| 2.1 | Similarity between compound symbols and their constituents          | 47  |

|-----|---------------------------------------------------------------------|-----|

| 2.2 | Similarity of unbound symbols to vectors in the original vocabulary | 47  |

| 5.1 | Network utilisation of circular convolution                         | 112 |

| 5.2 | Interposer partitions and the circular convolution network          | 114 |

| 5.3 | Cores required in SpiNNaker instantiation of circular convolution   | 115 |

| 5.4 | Interposers reduce the number of packets transmitted                | 115 |

| 5.5 | Costs of spike-transmission for the circular convolution network    | 118 |

| 5.6 | Comparison of simulation methods for Circular Convolution network   | 123 |

| 6.1 | SpiNNaker performance of Ordered-Covering                           | 138 |

| 6.2 | Desktop performance of order-exploiting Espresso                    | 138 |

| 7.1 | Comparison of simulation methods for a core Spaun component         | 143 |

### **Abstract**

#### Real time Spaun on SpiNNaker

Functional brain simulation on a massively-parallel computer architecture

Andrew Mundy

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY, 2016

Model building is a fundamental scientific tool. Increasingly there is interest in building neurally-implemented models of cognitive processes with the intention of modelling brains. However, simulation of such models can be prohibitively expensive in both the time and energy required. For example, Spaun – "the world's first functional brain model", comprising 2.5 million neurons – required 2.5 hours of computation for every second of simulation on a large compute cluster.

SpiNNaker is a massively parallel, low power architecture specifically designed for the simulation of large neural models in biological real time. Ideally, SpiNNaker could be used to facilitate rapid simulation of models such as Spaun. However the Neural Engineering Framework (NEF), with which Spaun is built, maps poorly to the architecture – to the extent that models such as Spaun would consume vast portions of SpiNNaker machines and still not run as fast as biology. This thesis investigates whether real time simulation of Spaun on SpiNNaker is at all possible.

Three techniques which facilitate such a simulation are presented. The first reduces the memory, compute and network loads consumed by the NEF. Consequently, it is demonstrated that only a twentieth of the cores are required to simulate a core component of the Spaun network than would otherwise have been needed. The second technique uses a small number of additional cores to significantly reduce the network traffic required to simulated this core component. As a result simulation in real time is shown to be feasible. The final technique is a novel logic minimisation algorithm which reduces the size of the routing tables which are used to direct information around the SpiNNaker machine. This last technique is necessary to allow the routing of models of the scale and complexity of Spaun. Together these provide the ability to simulate the Spaun model in biological real time – representing a speed-up of 9000 times over previously reported results – with room for much larger models on full-scale SpiNNaker machines.

## **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy, in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations and in The University's policy on presentation of Theses.

## Acknowledgements

I'm immensely grateful to all the friends, family and colleagues who have supported me over the past, very enjoyable, four years and, in particular, the last nine months while I've been located away from Manchester. I would have been utterly lost without the very generous open door policies, enthusiasm, guidance and oft needed criticism of my supervisors – Jim Garside, Simon Davidson and Steve Furber – and I owe much to the members of the APT group for their time and help – Steve Temple and Luis Plana especially.

Much of the work in this thesis is possible as a result of collaboration. Jonathan Heath-cote and Jamie Knight have been great friends, and wonderful collaborators, who I will miss sharing an office with. Terry Stewart, Chris Eliasmith and others at the University of Waterloo have been immensely kind and I look forward to joining them in due course. It's been a pleasure to work with Jörg Conradt and others.

This work would not have been possible if not for the Engineering and Physical Sciences Research Council, the School of Computer Science and various other bodies who funded my studies and travel.

Finally, I'd like to thank my parents for their proof-reading, support and love, and my wonderful wife Beccy for sharing the first four years of our marriage with this thesis.

## Chapter 1

## Introduction

Building and simulating models of the brain is a promising way to investigate the principles which underlie human cognition. Although this is not a recent observation (Turing 1950) developments in computing technology have made simulation of larger and more detailed models increasingly tractable. These technological advances have catalysed computational neuroscience and resulted in the formation of both the European Human Brain Project (Markram et al. 2011) and the US BRAIN Initiative (The White House 2013) – two 'mega projects' dedicated to significantly improving understanding of the brain through simulation of computer models. These models can be broadly classified as those which build "up" from a description of neural form (e.g., Izhikevich and Edelman 2008) and those which focus on function and build "down" to tie *behaviour* to a *neurally-inspired* implementation (e.g., Verschure and Voegtlin 1998; Sandamirskaya 2013).

The leading model in this latter field is, arguably, Spaun (Eliasmith, Stewart, et al. 2012; Eliasmith 2013), which, unlike many *cognitive* models, draws together ideas from classical Artificial Intelligence (e.g., Fodor and Pylyshyn 1988; Anderson et al. 2004), Artificial and Spiking Neural Networks (e.g., McCulloch and Pitts 1943; Rosenblatt 1958; Hopfield 1982; Maass 1997) and dynamic systems theory (Gelder 1998). Consisting of 2.5 million neurons and a virtual 'eye' and 'arm', Spaun is capable of performing eight tasks, in which it is apparent that it reproduces some characteristics of human performance. For example, humans have been shown to be more likely to forget the middle, rather than the beginning or the end, of lists they have remembered (Dosher 1999). Spaun shows a similar tendency, implying that it captures something about how the human brain memorises lists. To truly assess this requires many more trials than have been performed.

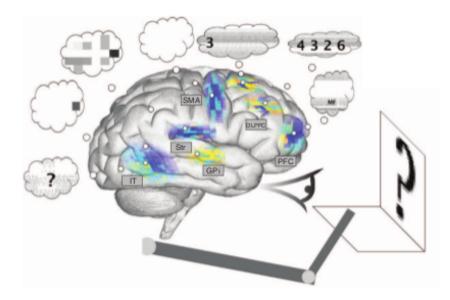

Alongside these developments in the fields of computing and cognitive modelling has been a growing recognition that *behaviour* is inextricably tied to *environment* (Braitenberg 1986; Brooks 1990; Webb 2001; Kaplan 2008). While the environments in which these neural models are *embodied* could be entirely virtual, the growing range of biologically-inspired (*biomimetic* and *neuromorphic*) sensors (e.g., Chan, Liu, and Schaik 2007; Lichtsteiner, Posch, and Delbruck 2008) suggests that the environment could be our environment and the neural models used to control robotic agents. For example, the virtual eye and arm to which Spaun is connected (Figure 1.1) could be replaced with a biomimetic retina and a robotic arm. For this to be realistic simulations of neural models that run as fast as biology will be required.

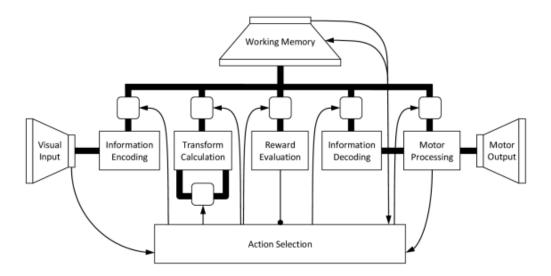

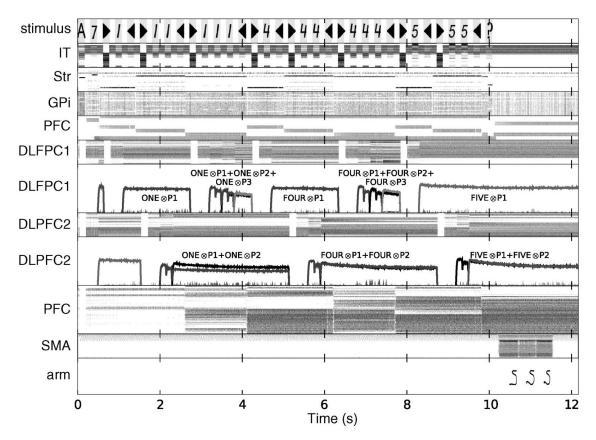

Figure 1.1 – The Spaun model, reproduced from Eliasmith, Stewart, et al. (2012).

Unfortunately, complex neural networks are rarely simulated in biological real time, meaning that the time taken to perform the computation associated with the simulation is often significantly greater than the 'time' that has passed in the model. For example, the Spaun model required 2.5 hours of compute for every 1 s of the simulation (in 2012, as reported by Stewart and Eliasmith 2014) – i.e., 9000 times slower than biology. Improvements are possible, indeed an improvement of an order of magnitude has been informally reported, but the technologies involved suffer from severe drawbacks. Supercomputers and General Purpose Graphics Processing Units (GPGPUs) consume much power and have limited scalability. In contrast, hardware implementations of neurons (Choudhary et al. 2012; Merolla et al. 2014; Meier 2015) consume little power but are too inflexible

to allow new types of neural model to be investigated. Since Spaun is less than 1% of the size of the human brain, the abilities of simulation technologies to scale and adapt is crucial if ever-larger and more complex models are to be constructed and simulated.

SpiNNaker (Furber, Galluppi, et al. 2014) – a low power, massively parallel computer designed for the real time simulation of large scale spiking neural networks – may prove to be a solution. A SpiNNaker machine consists of up to a million highly constrained processing cores connected to a customised network. This network is optimised, using a 'multicast' architecture, for the efficient simulation of the high degree of neural interconnectivity found in brains. While SpiNNaker has proven to be suitable for the simulation of a wide range of neural networks (Sharp, Petersen, and Furber 2014; Stromatias et al. 2015; Knight, Tully, et al. 2016) the architecture is not well suited to the simulation of networks like Spaun (Section 4.1).

Construction of Spaun was guided by two theories: the Neural Engineering Framework (Eliasmith and Anderson 2004) and the Semantic Pointer Architecture (Eliasmith 2013). The Neural Engineering Framework is a series of principles which describe how a functional description of a system may be implemented in a network of spiking neurons (Section 2.2) and the Semantic Pointer Architecture describes how high dimensional vectors can be used to represent and manipulate symbol-like values (Section 2.3). Unfortunately, networks constructed using these principles act to stress the SpiNNaker architecture. In particular, the dense neural interconnectivity and high firing rates they require consume much more memory, network bandwidth and compute time than would be needed for the types of neural networks for which SpiNNaker was designed (Sections 3.3 and 4.1). To manage these loads a choice must be made between simulating the network slower than biology, acquiring a larger SpiNNaker machine, limiting the scale of the neural models which can be investigated or ignoring neurons altogether and simulating merely the "computational" elements of Spaun. Unfortunately, each of these choices presents drawbacks: simulating the network slower than biology precludes interaction with biomimetic sensors and actuators; acquiring (or building) a larger computing system may be prohibitively expensive; limiting the scale of the neural network limits the scale and complexity of system which may be examined; replacing simulation of neurons with simulation of "computational" elements alone can change the behaviour of the system and reduce the explanatory strength of the model and results (Eliasmith, Stewart, et al. 2012, p. 219; Stewart 2012).

This thesis presents techniques which reduce the memory, compute and network loads required to simulate neural networks built with the Neural Engineering Framework and Semantic Pointer Architecture. Specifically, it demonstrates that a core component of the Spaun network can be simulated *in biological real time* (meaning that 1 s of simulation requires 1 s of computation) using one twentieth of the resources that would have been required had SpiNNaker been used as intended. As a consequence, SpiNNaker is shown to be an ideal platform for future research on Spaun and its successor models. In particular, since the scale of machine expected to be necessary to simulate Spaun is small enough, and consumes sufficiently little power, it may be situated in the same room as a robot, allowing Spaun (or similar) models to interact with an environment through a tight control loop. Alternatively, many instances of the Spaun model could be run in parallel, allowing more data to be gathered about its performance and enabling more meaningful comparisons with results from biology and psychology. Finally, there is scope to increase the scale or complexity of Spaun allowing it to perform more tasks and again increasing potential comparisons with the empirical sciences.

These reductions in the memory, compute and networks loads consumed by neural simulation are made by exploiting a characteristic of the Neural Engineering Framework to change the way in which simulation data is transferred amongst processing cores (Chapter 4). As a result, the architectural target of 1000 neurons per core is more than doubled and the memory required to represent a neural network significantly reduced (Mundy, Knight, et al. 2015). This increases how densely neural models may be packed into a SpiNNaker machine, allowing larger models to be simulated using fewer processors.

Unfortunately, the improvements made by changing the way in which processors communicate are still not enough to allow real time simulation of neural models like Spaun (Chapter 5). This is because the dense interconnectivity of models built with the Semantic Pointer Architecture requires much more network bandwidth and processing than are available. Managing these loads requires that the simulation run slower than biology. However, by replacing the dense network connectivity with an 'interposer' the traffic and compute loads can be reduced sufficiently to allow simulation in biological real time. The interposer proposed in this thesis exploits the changed values which are communicated by processors and the *multicast* capability of the SpiNNaker network to distribute simulation state over a wide area. This reduces both the overall traffic and the

fan-out and fan-in of individual processors, which in turn reduces local traffic and the processing required.

Despite these improvements, the interposer still requires some degree of traffic fanout and fan-in and this results in the *routing tables* which are used to direct traffic around the SpiNNaker network becoming too large to store on the chip (Chapter 6). Although logic minimisation can be used to reduce the size of these routing tables (Liu 2002) existing techniques result in insufficient minimisation of benchmark SpiNNaker routing tables. This thesis introduces a new technique which, by exploiting the ordered nature of the tables, achieves a greater degree of minimisation (Section 6.3). As serial application of this technique to all the tables in a million core machine would be prohibitively expensive, the massive parallelism of SpiNNaker can be exploited to perform this task. As the limited memory available to a SpiNNaker core precludes the use of any of the existing minimisers this thesis introduces a new algorithm. Parallel use of this algorithm on SpiNNaker is shown to minimise one of the benchmark sets of routing tables 64 times faster than a desktop PC (Mundy, Heathcote, and Garside 2016).

The work presented in this thesis builds towards biological real time simulation of "the world's first functional brain model" (Stewart and Eliasmith 2014), Spaun (Eliasmith, Stewart, et al. 2012), on SpiNNaker. This is a major milestone, not only for the SpiNNaker project, but also, since it paves the way for simulation of models *larger and more complex* than Spaun, in our quest to understand cognition.

#### **Contributions**

Mundy, Andrew, James Knight, Terrence C. Stewart, and Steve Furber (2015). "An efficient SpiNNaker implementation of the Neural Engineering Framework". In: *Neural Networks* (*IJCNN*), 2015 International Joint Conference on. DOI: 10.1109/IJCNN.2015.7280390. – Nominated for Best Paper Award

Mundy, Andrew, Jonathan Heathcote, and Jim D. Garside (2016). "On-Chip Order-Exploiting Routing Table Minimization for a Multicast Supercomputer Network". In: *High Performance Switching and Routing (HPSR)*, 17th International Conference on. – **Best Paper Award**

Stewart, Terrence C., Ashley Kleinhans, Andrew Mundy, and Jorg Conradt (2016). "Serendipitous Offline Learning in a Neuromorphic Robot". In: *Frontiers in Neurorobotics* 10 (1). ISSN: 1662-5218. DOI: 10.3389/fnbot.2016.00001.

Knight, James, Aaron R. Voelker, Andrew Mundy, and Chris Eliasmith (2016). "Efficient SpiN-Naker simulation of a heteroassociative memory using the Neural Engineering Framework". In: Neural Networks (IJCNN), 2016 International Joint Conference on.

Further publications based on the contents of this thesis are planned.

#### In addition:

- An implementation of the algorithm presented in Chapter 6 has already been used by other researchers in Manchester to minimise the routing tables arising from a detailed model of a part of the human brain (Potjans and Diesmann 2012).

- Various insights arising from this work are being fed into design of the next generation of the SpiNNaker hardware and support software built in collaboration with others for this project is used by others in the group (Knight and Furber 2016).

- The implementation of the Neural Engineering Framework described in Chapters 4 and 5 is in active use by a number of researchers across the globe.

## **Chapter 2**

# Neurons, synapses and representation

#### 2.1 Modelling the nervous system

The human brain is thought to contain of the order of 85 billion neurons (Herculano-Houzel 2009). Each neuron is a complex electrochemical system capable of altering the ratio of ions and hence the electric potential across its cellular membrane. From the main cell body of a neuron grows a tree-like structure of inputs, named *dendrites*, in addition to which each neuron possesses a single (often long) output structure, the *axon*. Varying electric potentials on the dendrites will modify the potential of the cell itself, eventually causing a *spike* or series of spikes of potential to be generated and pass down the axon, affecting further neurons via *synapses* – the connections between neurons.

In computational modelling of the nervous system it is common to use a system of coupled differential equations to describe a single neuron. One of the earliest models was proposed by Hodgkin and Huxley (1952). However, this model is computationally expensive and while simplifications exist there are wide variations in the types and characteristics of neurons found within different regions of the brain and accounting for this range of variation within a single model is challenging. Moreover, there is debate as to exactly which features of neurons are relevant for computational models (Izhikevich 2004). Since there is controversy about which features of the neural behaviour are relevant the *flexibility* resulting from software simulation of the nervous system may well outweigh the speed and power benefits of dedicated hardware – see Chapter 3.

#### Leaky Integrate-and-Fire model

The Leaky Integrate-and-Fire (LIF) model of the neuron (Lapicque 1907; Abbott 1999) is a simple neuron model which captures some of the key features of the behaviour of biological neurons and is a good illustration of how a typical neuron works. LIF neurons will be used in all models in this thesis since it was the only model used in Spaun (Eliasmith, Stewart, et al. 2012). The techniques described in this thesis are, however, amenable for use with other neural models. Likewise, it is possible to construct Spaun from alternative neuron models (Eliasmith, Gosmann, and Choo 2016).

The LIF neuron can be thought of as the combination of a first-order low-pass filter and a 'spike generator'. Input to the neuron is filtered using the low-pass filter. Should the output of the filter pass a given *threshold* value the neuron emits a *spike* and the output of the filter is reset to a lower value and held there for a time. We will focus on a *normalised* LIF model in which the output of the filter, representing the cell membrane voltage, is allowed to vary between zero and one. As a consequence of this the 'currents' and 'voltages' discussed below are analogues of the real quantities of the LIF neuron and are unitless.

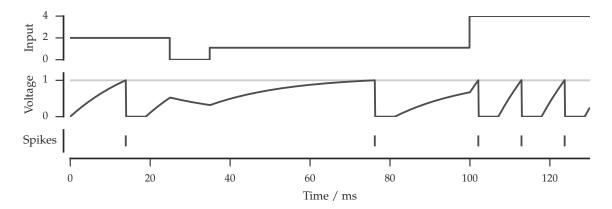

Figure 2.1 shows a simulation of a LIF neuron fed by a constant current, rather than by the spikes of other neurons. As can be seen, the input value (uppermost panel) is filtered to form the membrane 'voltage' (middle panel) and once the 'voltage' passes the threshold a *spike* is emitted (lowest panel) and the voltage is reset to zero for a period. The time constant of the low-pass filter is  $\tau_{rc}$  and the duration for which the voltage is held at zero after a spike is called the *refractory period*,  $\tau_{ref}$ .

While the neuron is neither firing nor in the refractory period the 'membrane voltage' (in this case a dimensionless quantity) is described by the equation:

$$\dot{v} = \frac{i_{\text{input}} - v}{\tau_{\text{rc}}} \tag{2.1}$$

where  $i_{input}$  is the input to the neuron (and is a dimensionless quantity analogous to the 'current' in the non-normalised LIF model). This input is a combination of a bias,  $i_{bias}$ , and the spiking-output of other neurons. However, for our purposes it is useful to express this as  $i_{input} = gx + i_{bias}$  where g is called the gain of the neuron and x is a value over which we have control.

**Figure 2.1** – Simulation of a Leaky Integrate and Fire (LIF) neuron. The top panel shows the input to the neuron which, for illustrative purposes, is a piecewise function rather than the accumulated spikes of other neurons. The middle panel shows the membrane 'voltage' – formed as a 'leaky' integral of the input with time constant  $\tau_{rc}$ . Once the voltage passes a threshold a *spike* is emitted (bottom panel) and the membrane voltage held low for a period of time called the *refractory period*,  $\tau_{ref}$ . (For this illustration  $\tau_{ref} = 5 \, \text{ms}$  and  $\tau_{rc} = 20 \, \text{ms}$ ).

#### **Tuning curves**

One of the characteristics of the LIF model is that when fed a constant input it produces spikes at a constant rate (see the final 30 ms of Figure 2.1). This allows us to draw a graph describing the relationship between constant input on the *x*-axis and firing rate (in Hz) on the *y*-axis. The line represented on this graph is called the *tuning curve* of the neuron.

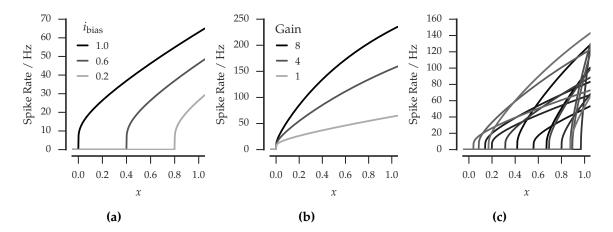

Figure 2.2 shows a number of tuning curves which illustrate the effect that varying  $i_{\text{bias}}$  and g has on the characteristic response of the neuron. Through modification of the bias current,  $i_{\text{bias}}$ , the value of x for which the neuron starts to fire can be selected (Figure 2.2(a)). By modifying the gain of the neuron, g, the slope of the tuning curve can be made steeper or shallower (Figure 2.2(b)). By varying both the gain and the bias a range of neural responses can be generated.

It is important to note that while the neuron response is characterised in terms of spike rates this is merely an analytic convenience and all simulations in this thesis are run using spiking models of neurons rather than "rate" neuron models.

#### Neural networks and synapses

When a biological neuron *fires* the pulse that is generated travels along the axon of the neuron. To make contact with the dendrites of other neurons the axon is branched, with each branch leading to junctions with other neurons. Each junction between the axon of

the *presynaptic* neuron and the dendrites of the *postsynaptic* neuron is called a *synapse*. At a synapse the spike generated by the neuron is chemically transmitted across a short gap and the transmission method is capable of varying both the strength and the shape of the impulse that is received by the postsynaptic neuron.

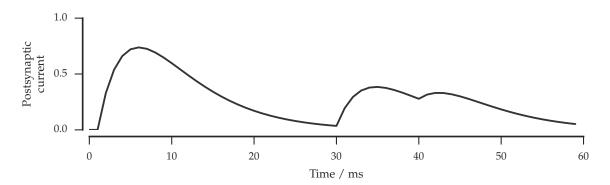

Instead of modelling synapses directly it is common to specify them in two ways: The change in strength of the impulse caused by a synapse is called the synaptic *weight*; the pulse-shaping is often referred to as *synaptic filtering* and can be modelled as a linear transfer function. Note that the transfer function used to model synaptic shaping is distinct from the transfer function used to model the changes in the membrane voltage of the LIF neuron. If multiple spikes travel across synapses to the same neuron (the *postsynaptic* neuron) their contributions to the input of the neuron are summed. Figure 2.3 shows the shaping, weighting and summing applied to three spikes arriving at the same postsynaptic neuron. In this example the synaptic shaping was performed with a second-order filter; the Spaun model, however, uses first-order filters and these are used throughout the remainder of this thesis.

Neurons rarely occur in isolation; it is common to think of them forming groups, or *populations*, which work together to fulfil some function. The synaptic weights between two populations of neurons can be described by a *synaptic weight matrix*, one of which is illustrated in Figure 2.4 in which a black dot indicates a synaptic connection between two neurons.

#### 2.2 The Neural Engineering Framework

The base components of the nervous system are, of course, only part of the story about behaviour and cognition. There is a wealth of studies which indicate the utility of even small nervous systems in behavioural responses (e.g., Kandel 1976), but tying more complex behaviours to their neural implementation has proven much more complex. The Neural Engineering Framework (NEF) (Eliasmith and Anderson 2004; Stewart and Eliasmith 2014) is one attempt.

The Neural Engineering Framework provides a toolkit that allows the conversion of a functional description of a *system* into a neural implementation or *model*. Such a model consists of populations of neurons (or *ensembles*) which act to represent the *variables* of the system. These ensembles produce spikes which are transmitted to other ensembles by

**Figure 2.2** – Varying parameters of a LIF neuron with  $\tau_{\rm ref} = 2\,\rm ms$  and  $\tau_{\rm rc} = 20\,\rm ms$ . In (a) the gain is held at 1 and the bias current,  $i_{\rm bias}$ , is varied. In (b) the bias is held at 1 and the gain is varied. Finally, (c) illustrates how a range of tuning curves can be achieved through varying both the bias current and the gain.

**Figure 2.3** – Postsynaptic currents from three weighted and shaped spikes. Spikes occurred at times t = 1 ms, 30 ms and 40 ms and had weights of 10, 5 and 2 units respectively.

Figure 2.4 – Sample weight matrix between two populations of neurons

synaptic connections whose weights are selected to compute functions of the values represented by the transmitting neurons and whose synaptic shaping is leveraged to both smooth the spikes and implement system dynamics. By constraining the number and types of neurons and synapses in the model it is possible to compare the neural implementation of a particular functional description with the brain region thought to fulfil the same functional role. Consequently, hypotheses regarding the nature of some neural system (e.g., the role of basal ganglia in action-selection (Gurney, Prescott, and Redgrave 2001; Stewart, Choo, and Eliasmith 2010)) can be tested by implementing a model of the system and comparing aspects of the implementation (e.g., timing response, failure modes, etc.) with known biological values.

At the heart of the NEF are three principles:

**Representation** Populations of neurons act to represent *values* of the kind that we would use to typify the behaviour of a system (e.g., velocity).

**Transformation** Connections between ensembles can be used to *compute* functions of the values represented by the neurons (e.g., speed).

**Dynamics** *Synaptic filtering* of the spikes transmitted between ensembles may be used to implement dynamical systems (e.g., a recurrent connection can be used to construct an integrator which may be used to compute displacement).

#### Representation

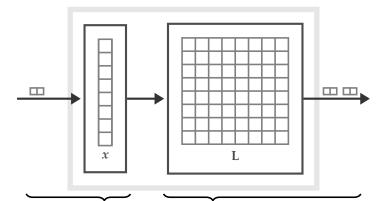

The NEF characterises neural representation using two processes. *Encoding* converts the value of interest (e.g., a displacement, temperature, or other physical characteristic) into a spike-train. *Decoding* the spike-train returns an estimation of the original value. Alternatively expressed, the *encoding* process takes a low-dimensional value and transforms it into a high-dimensional space and the *decoding* process is able to recreate an estimation of the original value given the value in the higher-dimensional space.

Eliasmith and Anderson (2004) use a analogue-to-digital converter (ADC) to explain the processes of encoding and decoding. At its input the ADC receives, from a transducer, an analogue signal which represents some physical quantity. The ADC converts this input signal, which is continuous in both time and value, into a series of digital samples. These digital samples – constructed by a highly non-linear encoding – represent,

with some quantisation noise, the original value of interest but in the 'language' that is used to communicate between components of a digital rather than an analogue circuit. We can recover a representation of the original value by multiplying the *i*th bit of the output of the ADC by  $2^i$  and summing, i.e.,  $\sum_{i=0}^{n-1} 2^i y[i]$  where y is the output of the ADC. This representation is a *decoding* of the value that is represented by the output and is an *approximation* of the input.

The same principles of encoding and decoding may be applied to a population of neurons. Each neuron acts as an encoder which converts its input into a series of spikes – the 'language' that is used to communicate between neurons. The timing characteristics of these spikes depends on the dynamics of the neuron and the selectivity of the neuron to the space it represents. This selectivity is achieved by adding an *encoder* term,  $e_i$ , to the expression for the input of a neuron:

$$i_{\text{input}} = ge_i x + i_{\text{bias}} \tag{2.2}$$

where g is the gain of the neuron and x is an input over which we have control (see p. 29).

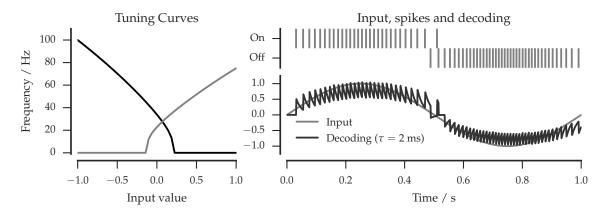

When representing scalar values the encoder may be either +1 or -1 resulting in positive and negative sloping tuning curves respectively. For example, Figure 2.5 shows the tuning curves of two LIF neurons configured to act as an on/off pair. Their response to a time-varying input signal and the decoding of their spiking output are also shown. As can be seen, as the input signal (a 1 Hz sine wave) becomes increasingly positive the "on" neuron fires increasingly frequently; as the signal becomes increasingly negative the

**Figure 2.5** – Response of a pair of LIF neurons to a time-varying input signal. The tuning curves of the neurons, their spiking response to the input and the low-pass filtered linear decoding of the spiking output are shown.

**Figure 2.6** – Response of a population of 15 LIF neurons to a time-varying input signal. Note that the decoded representation of the ensemble is cleaner than that of Figure 2.5.

"off" neuron fires more strongly. By using more neurons we can increase the accuracy of the representation and decrease the noise present in the decoding. Figure 2.6 shows the response of a *population* or *ensemble* of 15 neurons to the same input signal, as each spike has a proportionally less effect the decoding is a 'cleaner' recreation of the input.

To *decode* the spike train emanating from a neural population we use a technique similar to that used to decode the output of the ADC. Each neuron is associated with a decoder  $d_i$ , and the decoding of the entire population is simply the sum of the spikes of the population multiplied by the decoders. This can be thought of as a matrix-vector multiply, as shown in Figure 2.7. The decoding is usually filtered to emulate the effects of synaptic transmission. Consequently, in the two neuron case (Figure 2.5) we see that as the "on" neuron fires more strongly the decoded output increases in value and as the "off" neuron fires more strongly the decoded value decreases.

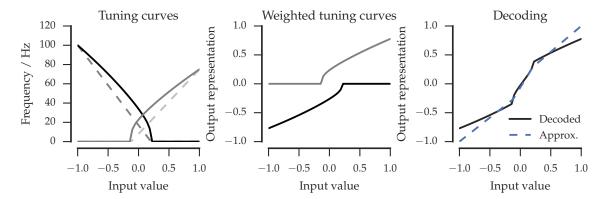

Correct choice of decoder values is important; Stewart and Eliasmith (2014) describe a method to select such values automatically but a simple approach is outlined below. The tuning curves for the example 'on' and 'off' neurons can be approximated by the linear piece-wise functions, shown in left-hand pane of Figure 2.8:

$$a_{\text{On}}(x) = \begin{cases} 67x + 8 & -0.12 < x \\ 0 & x \le -0.12 \end{cases} \qquad a_{\text{Off}}(x) = \begin{cases} 0 & 0.2 \le x \\ -83x + 17 & x < 0.2 \end{cases}$$

**Figure 2.7** – Decoding the output of a population of neurons. For each discrete simulation time step a vector can be constructed whose elements indicate whether each neuron fired or not (these are shown as the stacked row vectors on the left of the figure). Multiplying this vector by a decoder matrix (**D**) results in a single value which is an estimate of the value represented by the population of neurons.

Figure 2.8 – Multiplying the tuning curves of a population by the decoders. The tuning curves and decoders are those from Figure 2.5. Piece-wise approximations of the tuning curves and the decoding formed from these approximations are shown as dashed lines.

We now want to find the decoders  $d_{\rm On}$  and  $d_{\rm Off}$  such that  $\hat{x}=d_{\rm On}a_{\rm On}(x)+d_{\rm Off}a_{\rm Off}(x)\approx x$ . One way to do this is to pick values of  $d_{\rm On}$  and  $d_{\rm Off}$  such that  $\hat{x}=x$  for x=1 and x=-1. For x=1 we have  $\hat{x}=d_{\rm On}$  (67+8) = 1, therefore  $d_{\rm On}=\frac{1}{75}$ . At x=-1 we have  $\hat{x}=d_{\rm Off}$  (83+17) = -1, therefore  $d_{\rm Off}=-\frac{1}{100}$ .

Using these decoders gives:

$$d_{\text{On}}a_{\text{On}}(x) = \begin{cases} 0.9x + 0.1 & -0.12 < x \\ 0 & x \le -0.12 \end{cases} \qquad d_{\text{Off}}a_{\text{Off}}(x) = \begin{cases} 0 & 0.2 \le x \\ 0.8x - 0.2 & x < 0.2 \end{cases}$$

Resulting in the decoding:

$$d_{\text{On}}a_{\text{On}} + d_{\text{Off}}a_{\text{Off}} = \begin{cases} 0.9x + 0.1 & 0.2 \le x \\ 1.7x - 0.1 & -0.12 < x < 0.2 \\ 0.8x - 0.2 & x \le -0.12 \end{cases}$$

Note that this decoding curve does not exactly match the desired function f(x) = x but approximates it closely aside from a 'bump' in the range -0.12 < x < 0.2. This decoding and a similar 'bump' in the decoding formed from the tuning curves, rather than from the linear approximations, are shown in Figure 2.8. As will be seen in Section 2.2 decoders can be chosen such that the decoding is a transformation of the input value.

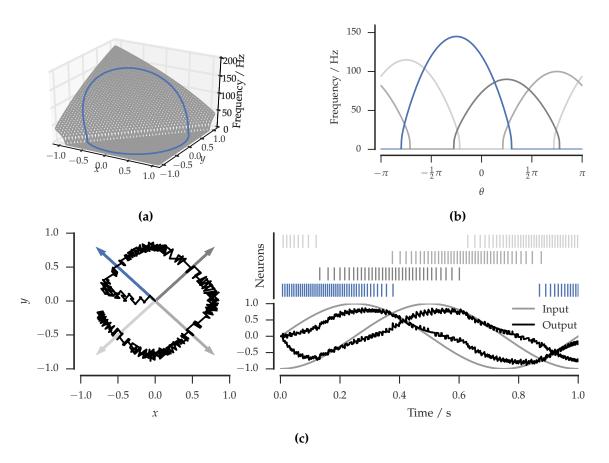

If the *encoders*,  $e_i$ , and *decoders* are selected to be vectors rather than scalars a population may be used to represent a multi-dimensional value, the vector x. The input current to a neuron is now derived as  $i_{\text{input}} = ge_i \cdot x + i_{\text{bias}}$ , such that neurons fire more strongly the more similar the represented value is to their encoding vector. An example of this is shown in Figure 2.9 where four neurons are used to represent a 2-dimensional value. Each neuron in the ensemble is receptive to a portion of the representational space.

Figure 2.9(a) shows how the firing rate of a neuron with the encoder  $e = \left(-\frac{1}{\sqrt{2}}, +\frac{1}{\sqrt{2}}\right)$  varies with the input representation. Described on the *tuning surface* of this neuron is a circle, with a radius of one, centred at the origin. In Figure 2.9(b) the firing rates on the perimeter of this circle are redrawn against their angular position, along with the tuning curves of a further three neurons. Finally, Figure 2.9(c) shows how, together, these four neurons can be used to represent a two dimensional value. As before, greater accuracy could be achieved through using more neurons both because each spike will have

**Figure 2.9** – Representing a 2D value with four neurons. The tuning *surface* of a single neuron in shown in (a) – described on this surface is a circle of radius one centred at the origin. In (b) the firing rates on the perimeter of this circle are plotted against their angular position and the responses of a further three neurons are shown. This population can be used to represent a 2D value, as shown in (c) – note that since at time t=0 the neurons are not firing there is a transient in the output.

proportionally less effect but also because the encoders will better 'cover' the space. All that is required to represent higher dimensional spaces, such as those used in Spaun, are higher dimensional encoders.

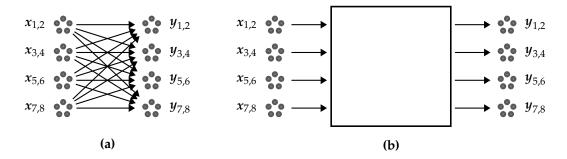

Thus far we have seen how to use a population of neurons to convert a scalar or vector value into a number of spike trains and how a linear decoding of these spikes can be used to form an approximation of the original scalar or vector. However, biological neural networks contain many interconnected populations of neurons, between which connections are described by synaptic weight matrices. Using the NEF we can construct a weight matrix,  $\omega$ , as the product between the encoders of the post-synaptic population,

**E**, and the decoders of the pre-synaptic population, **D**.

$$\omega = ED \tag{2.3}$$

Imagine we were to connect our two neuron population from before (Figure 2.5 and Figure 2.8) with the decoders  $\mathbf{D} = \begin{pmatrix} d_{\mathrm{On}} & d_{\mathrm{Off}} \end{pmatrix} = \begin{pmatrix} \frac{1}{75} & -\frac{1}{100} \end{pmatrix}$  to another pair of neurons. We let this other population consist of another pair of 'on' and 'off' neurons with the encoders:

$$\mathbf{E} = \begin{pmatrix} +1 \\ -1 \end{pmatrix}$$

To compute the synaptic weight matrix of the connection between these populations we multiply the encoders of the post-synaptic matrix, **E**, by the decoders of the presynaptic matrix, **D**.

$$\omega = \begin{pmatrix} +1 \\ -1 \end{pmatrix} \begin{pmatrix} \frac{1}{75} & -\frac{1}{100} \end{pmatrix} = \begin{pmatrix} \frac{1}{75} & -\frac{1}{100} \\ -\frac{1}{75} & \frac{1}{100} \end{pmatrix}$$

The matrix  $\omega$  is constructed such that the first column describes connections *from* the presynaptic-'on' neuron and the second describes connections *from* the presynaptic-'off' neuron. Additionally, the first and second rows describe connections *to* the postsynaptic-'on' and -off neurons respectively. Consequently we note that there are *excitatory* connections between the 'on' neurons and between the 'off' neurons:  $\omega_{\text{On,On}}$  and  $\omega_{\text{Off,Off}}$  are positive. In addition to which there are *inhibitory* connections from the presynaptic-'on' to the postsynaptic-'off' neuron and from the presynaptic-'off' neuron to the postsynaptic-'on' neuron:  $\omega_{\text{On,Off}}$  and  $\omega_{\text{Off,On}}$  are negative. As a result, when the presynaptic population represents a positive value (causing the presynaptic-'on' neuron to become active) the postsynaptic-'on' will be excited and the postsynaptic-'off' neuron will be inhibited. Likewise, when the presynaptic population represents a negative value (causing the presynaptic-'off' neuron to become active) the postsynaptic-'off' neuron to become active) the postsynaptic-'off' neuron will be excited and the postsynaptic-'off' neuron inhibited.

An example with vector (rather than scalar) encoders and decoders gives a better intuition of the meaning of the synaptic weight matrix. Consider an example consisting of two ensembles, consisting of three and four neurons respectively, representing a two

dimensional space. The encoders of the postsynaptic population,  $e_i$ , and the decoders of the presynaptic population,  $d_i$ , are:

$$e_1 = \begin{pmatrix} -0.6 & 0.8 \end{pmatrix}$$

$d_1 = \begin{pmatrix} -0.2 & 0.45 \end{pmatrix}^{\top}$   $e_2 = \begin{pmatrix} -0.9 & -0.4 \end{pmatrix}$   $d_2 = \begin{pmatrix} -2.3 & -0.6 \end{pmatrix}^{\top}$   $e_3 = \begin{pmatrix} -0.9 & -0.2 \end{pmatrix}$   $d_3 = \begin{pmatrix} 2.1 & 0.9 \end{pmatrix}^{\top}$   $e_4 = \begin{pmatrix} 0.3 & 0.9 \end{pmatrix}$

We intend to select the synaptic weight matrix such that the firing rate of a neuron in the second population is proportional to the value being represented by the output of the first population. A simple way to achieve this is to set the synaptic weight between every pair of pre- and postsynaptic neurons according to the similarity between their respective decoders and encoders. For example, the synaptic weight between the second neuron of the first population and the third neuron of the second will be given by:

$$\omega_{3,2} = e_3 d_2 = (-0.9 \cdot -2.3) + (-0.2 \cdot -0.6) = 2.19$$

Forming the encoders and decoders into matrices (**E** and **D**, respectively) and multiplying them together forms the complete weight matrix:

$$\omega = \mathbf{ED} = \begin{pmatrix} e_1 \\ e_2 \\ e_3 \\ e_4 \end{pmatrix} \begin{pmatrix} d_1 & d_2 & d_3 \end{pmatrix} = \begin{pmatrix} e_1 d_1 & e_1 d_2 & e_1 d_3 \\ e_2 d_1 & e_2 d_2 & e_2 d_3 \\ e_3 d_1 & e_3 d_2 & e_3 d_3 \\ e_4 d_1 & e_4 d_2 & e_4 d_3 \end{pmatrix} = \begin{pmatrix} 0.48 & 0.90 & -0.54 \\ 0 & 2.31 & -2.25 \\ 0.09 & 2.19 & -2.07 \\ 0.35 & -1.23 & 1.44 \end{pmatrix}$$

This procedure works for any pair of neural populations whose encoders and decoders can be formed into a matrices of shape  $N_{\text{post}} \times D$  and  $D \times N_{\text{pre}}$  and will always result in a synaptic weight matrix of form  $N_{\text{post}} \times N_{\text{pre}}$ .

It should be noted that, since a pair of neurons will only *not* be connected if their encoders and decoders are orthogonal (for example,  $\omega_{2,1}$  above), the synaptic weight matrices produced this way will be *dense*. This has important ramifications for the sim-

ulation of these networks. In addition, the weight matrices often violate the observation that, in biology, neurons only ever form either *excitatory* or *inhibitory* outgoing connections (Dale's Principle, see Strata and Harvey 1999). Eliasmith and Anderson (2004) and Tripp and Eliasmith (2016) describe methods to build networks such that they obey this principle.

#### **Transformation**

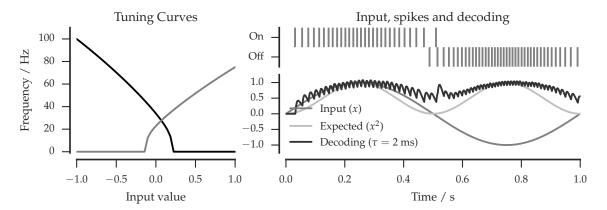

In the previous section we saw that the decoders for a population of neurons could be chosen to allow us to estimate the value represented by the ensemble. However, it is also possible to choose decoders to estimate *a function of* the value represented by a population of neurons. For example, we might select decoders such that we could estimate the *square* of the value represented by an ensemble.

We can approximate this process for the two neurons configured as an *on/off* pair. Using the same tuning curve approximations as before we know that we would like to find  $d_{\text{On}}^f$  and  $d_{\text{Off}}^f$  such that  $d_{\text{On}}^f a_{\text{On}} + d_{\text{Off}}^f a_{\text{Off}} \approx f(x)$ , where  $f(x) = x^2$ . Keeping  $d_{\text{On}}^f = \frac{1}{75}$  as before, but negating  $d_{\text{Off}}^f$  to be  $+\frac{1}{100}$  results in the decoding:

$$d_{\text{On}}^{f} a_{\text{On}} + d_{\text{Off}}^{f} a_{\text{Off}} = \begin{cases} 0.9x + 0.1 & 0.2 \le x \\ 0.1x + 0.3 & -0.12 < x < 0.2 \\ -0.8x + 0.2 & x \le -0.12 \end{cases}$$

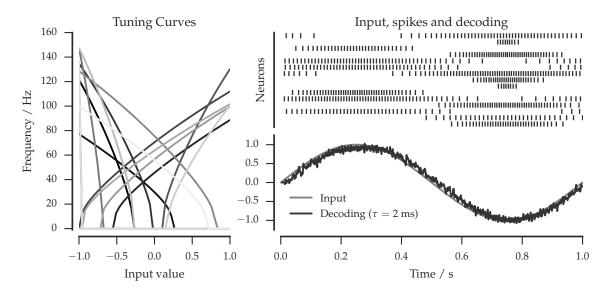

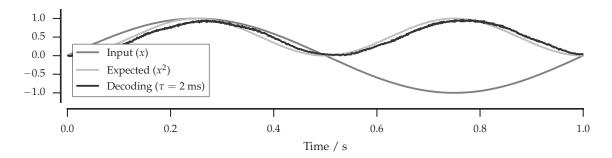

which approximates the form of  $x^2$ . Figure 2.10 shows how the use of these decoders can compute a different function from the same spiking output that was shown in Figure 2.5. Once again, with more neurons a 'cleaner' decoding may be achieved (as in Figure 2.11).

These new decoders  $\mathbf{D}^f = \begin{pmatrix} \frac{1}{75} & \frac{1}{100} \end{pmatrix}$ , may be used to form the synaptic weight matrix specifying the connection to another pair of 'on' and 'off' neurons. Using the same encoders as previously,  $\mathbf{E} = \begin{pmatrix} +1 & -1 \end{pmatrix}^{\mathsf{T}}$ , results in the synaptic weight matrix:

$$\omega^f = \begin{pmatrix} +1 \\ -1 \end{pmatrix} \begin{pmatrix} \frac{1}{75} & \frac{1}{100} \end{pmatrix} = \begin{pmatrix} \frac{1}{75} & \frac{1}{100} \\ -\frac{1}{75} & -\frac{1}{100} \end{pmatrix}$$

The weight matrix is such that *regardless* of the value represented by the presynaptic population – i.e., whichever of the presynaptic-'on' or the presynaptic-'off' neuron is

**Figure 2.10** – Decoding  $x^2$  from a pair of neurons. The left panel shows the tuning curves of the two neurons. The input to the neurons, the resulting spikes and a decoding of the spikes which reproduces an estimate of the square of the input are shown in the right panel.

**Figure 2.11** – Decoding the square of the value represented by an ensemble of 100 neurons. The input to the ensemble, the expected output (the square of the input) and the measured output are shown. Note that the output from the ensemble is both less noisy and a closer approximation of the value  $x^2$  than that produced by the smaller ensemble in Figure 2.10.

firing – the postynaptic-'on' neuron will be excited and the presynaptic-'off' neuron will be inhibited. Since the decoders of the presynaptic population were selected to compute the square of the value represented by the ensemble, the result of which is never negative, it is not surprising that the weights in the synaptic matrix act to excite the postsynaptic-'on' neuron and inhibit the postsynaptic-'off' neuron.

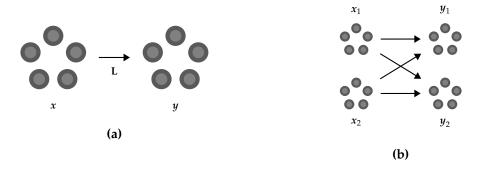

Instead of computing a function of the value represented by an ensemble we may wish to transform it with a linear operator, **L**. For example, we might wish to rotate the 2-dimensional value represented by an ensemble by the angle  $\theta$ . This may be achieved by premultiplying the decoders by the desired transform:

$$\mathbf{L}d_{i} = \begin{pmatrix} \cos\theta & -\sin\theta \\ \sin\theta & \cos\theta \end{pmatrix} d_{i} \tag{2.4}$$

Figure 2.12 shows how a linear operator can 'rotate' the value decoded from an ensemble.

We may combine this technique with the previous example. Suppose that instead of decoding  $x^2$  from an ensemble we wished to decode  $-\frac{1}{2}x^2$  we could modify our previous decoders  $\mathbf{D}^f = \left(\frac{1}{75}\frac{1}{100}\right)$  by premultiplying them by  $-\frac{1}{2}$  to result in  $\mathbf{D}^g = \left(-\frac{1}{150} - \frac{1}{200}\right)$ . As before, multiplying by the encoders allows us to create a synaptic weight matrix between two pairs of neurons which results in the value  $-\frac{1}{2}x^2$  being applied to the postsy-

**Figure 2.12** – Applying a linear transform to the decoding of an ensemble. Premultiplying the decoders of an ensemble by a linear transform applies that transform to the decoding of the ensemble – in this case a  $\frac{1}{4}\pi$  rotation has been applied.

naptic population:

$$\omega^g = \begin{pmatrix} +1 \\ -1 \end{pmatrix} \begin{pmatrix} -\frac{1}{150} & -\frac{1}{200} \end{pmatrix} = \begin{pmatrix} -\frac{1}{150} & -\frac{1}{200} \\ \frac{1}{150} & \frac{1}{200} \end{pmatrix}$$

Unlike the weight matrix,  $w^f$ , derived using decoders for  $x^2$ , this weight matrix causes the postsynaptic-'off' neuron to be excited and the postsynaptic-'on' neuron to be inhibited regardless of the value represented by the presynaptic pair. Since  $-\frac{1}{2}x^2$  is never positive this pattern of connectivity is to be expected.

## **Dynamics**

Synaptic connections between neurons are characterised not only by the weighting but also by the *shaping* they impart to the spikes which they carry. This shaping can be modelled as a linear transfer function. By exploiting the presence of this transfer function a number of dynamic systems may be implemented neurally (Eliasmith 2005; Eliasmith and Anderson 2004).

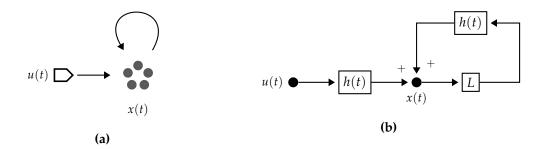

Figure 2.13(a) shows a simple neural network consisting of a single, recurrently connected, ensemble fed by the value u(t) and representing the value x(t). Assuming that the synaptic filter model h(t) is used for both the connection into the ensemble and the recurrent connection, and that the linear transform  $\mathbf{L}$  is applied by the recurrent connection then this neural system may be approximated by the block diagram shown in Figure 2.13(b). Evaluating the block diagram results in  $x(t) = h(t) * u(t) + h(t) * \mathbf{L}x(t)$ . Or, in the Laplace domain:

$$X(s) = H(s)U(s) + H(s)\mathbf{L}X(s)$$

$$= H(s) (U(s) + \mathbf{L}X(s))$$

Letting  $H(s) = \frac{1}{\tau s + 1}$ , the transfer function for a first-order low-pass filter with time constant  $\tau$ , results in:

$$X(s) = \frac{U(s) + \mathbf{L}X(s)}{\tau s + 1}$$

$$\tau s X(s) + X(s) = U(s) + \mathbf{L}X(s)$$

$$s X(s) = \frac{U(s) + \mathbf{L}X(s) - X(s)}{\tau}$$

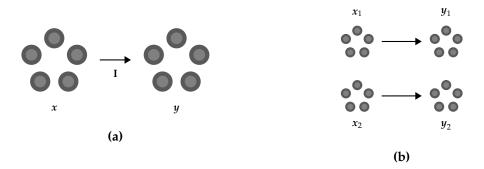

**Figure 2.13** – Using a recurrent connection to implement a dynamic system. A recurrently connected ensemble representing x(t) is shown in (a), alongside the recurrent connection the ensemble is being fed the value u(t). If the synaptic filter model applied on both connections in (a) is h(t) then an approximate block diagram for the system is as shown in (b). The use of a small number of clustered dots to represent a neural ensemble is common to the field and will be reused throughout this thesis.

Which, after applying the inverse Laplace transform, is:

$$\dot{x} = \frac{u(t) + (\mathbf{L} - \mathbf{I}) x(t)}{\tau} \tag{2.5}$$

Consequently, through choice of **L** we can determine the dynamics of x. For example, to create an integrator with dynamics  $\dot{x}(t) = v(t)$  (where v and x are scalars) we could let **L** = 1 and  $u(t) = \tau v(t)$ :

$$\dot{x} = \frac{u(t) + (\mathbf{L} - 1)x(t)}{\tau} = \frac{\tau v(t) + (1 - 1)x(t)}{\tau} = v(t)$$

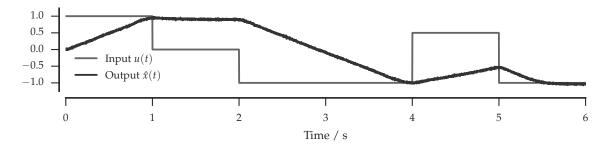

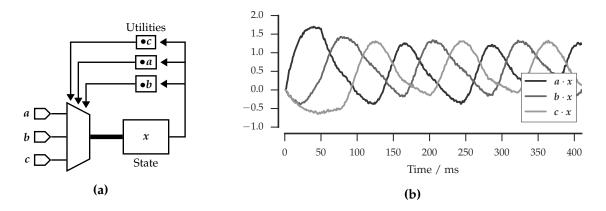

A simulation of this network, with  $\tau=100\,\mathrm{ms}$ , is shown in Figure 2.14. Attractor networks like this can be used to build memories to store vectors, which, as shown in the next section, can be used to represent *token*-like values.

**Figure 2.14** – Simulation of a neurally implemented integrator. The neural network simulated here is as presented in Figure 2.13.

## 2.3 The Semantic Pointer Architecture

Using the Neural Engineering Framework it is possible to construct neural implementations of control-theory like structures. However, not all cognitive processes are best described by dynamic systems. For example, language consists of *tokens* (words) which are combined together to form more structured tokens (phrases and sentences). Since *symbolic*, computational-like, processing seems to be so important in human cognition it has long been argued it must be accounted for in any theory of cognition. Unfortunately, mapping structured symbolic representations to neural networks is non-trivial (Smolensky 1990) and has been hotly debated (Fodor and Pylyshyn 1988; Smolensky 1988).

In the Semantic Pointer Architecture (SPA) (Eliasmith 2013; Eliasmith, Stewart, et al. 2012) each *symbol*, such as the word 'cheese', is represented by a vector in a high-dimensional space. By combining different vectors together with different operators new, structured, symbols may be formed and computations performed. Since the Neural Engineering Framework describes how vectors could be represented and transformed by neural networks the combination of the SPA and NEF presents a method by which symbol-like processing can be implemented in neural form.

## Representing and operating on symbols

Vectors are a natural way to represent symbols since they support inference of *semantic relationships*: symbols which are semantically similar (e.g., *horse* and *donkey*) may be assigned vectors which are close within the high dimensional space. By using a sufficiently high dimensional space, spurious relationships between vectors can be avoided since the likelihood of any two vectors being similar is vanishingly small. Relatedness between a pair of vectors-representing-symbols can be measured by computing their dot product.

Vector addition is one method by which symbols in a vector symbolic architecture may be combined. Since addition preserves *relatedness* it is ideal for producing new symbols. For example, the vector representing *pet fish*, PET + FISH, could be expected to have similarities with the vector representing *pet mice*, PET + MICE. However, addition is not good at constructing *syntactic representations* of the form *mice eat cheese*. This symbol could be expressed as MICE + EAT + CHEESE but this vector could not be differentiated from that which would be used to represent the symbol *cheese eat mice*. What is needed, in addition to the addition operator, is a way to *bind* symbols together to pro-

duce new, distinct, symbols. In the Semantic Pointer Architecture this is achieved by use of *circular convolution* (Plate 1995).

Circular convolution of two vectors,  $a \otimes b$ , results in a vector, of the same dimensionality, which is highly dissimilar from either of the original vectors, a or b, but which contains sufficient information that either of the originals may be retrieved given some information about the other. Specifically, the circular convolution of two n-dimensional vectors, a and b is defined as:

$$(a \circledast b)_i = \sum_{j=0}^{n-1} a_j b_{i-j \mod n}$$

(2.6)

which, due to the convolution theorem, may also be expressed as:

$$a \circledast b = \mathcal{F}^{-1} \left( \mathcal{F} a \odot \mathcal{F} b \right) \tag{2.7}$$

where,  $\mathcal{F}$  is the discrete Fourier transform,  $\mathcal{F}^{-1}$  its inverse and  $\odot$  the element-wise multiplication operator.

Using circular convolution to bind *placeholder* tokens (e.g., **SUBJ** for *subject*, **OBJ** for *object* and **VRB** for *verb*) to the constituents of a sentence is one way to construct syntactic representations. Doing this allows us to express *mice eat cheese* as

$$S = MICE \circledast SUBJ + EAT \circledast VRB + CHEESE \circledast OBJ$$

which is clearly distinct from the expression which would represent *cheese eat mice*.

For the following example the symbols MICE, EAT, CHEESE, SUBJ, OBJ and VRB were all represented by randomly selected, 128 dimension, vectors of length 1. The compound expression S contains pairs of these symbols bound together using the circular convolution operation defined above. Each of these bound pairs is strongly dissimilar from the original symbols from which it was formed. Table 2.1 shows the dot product similarity between the compound symbols composing S and each of the original symbols from the vocabulary. Since S was formed as the summation of the bound pairs it is similar to each of them.

Symbols can be *unbound* from a compound symbol to retrieve information from a complex representation. To unbind a symbol we construct a pseudo-inverse of the sym-

|                       | MICE  | EAT   | CHEESE | SUBJ  | OBJ   | VRB   | S    |

|-----------------------|-------|-------|--------|-------|-------|-------|------|

| MICE ® SUBJ           | -0.03 | 0.05  | 0.03   | 0.00  | 0.10  | 0.01  | 0.60 |

| $EAT \circledast VRB$ | 0.07  | -0.19 | 0.08   | -0.14 | -0.03 | 0.09  | 0.61 |

| <b>CHEESE ® OBJ</b>   | 0.10  | -0.02 | -0.18  | -0.08 | 0.12  | -0.03 | 0.58 |

| S                     | 0.08  | -0.09 | -0.04  | -0.12 | 0.11  | 0.04  | 1.00 |

**Table 2.1** – Similarity between compound symbols and their constituents. Each compound symbol,  $\mathbf{A} \circledast \mathbf{B}$ , is also represented by a 128-dimensional vector which has little similarity (as measured by dot product) to either of its constituent symbols.

bol and bind it with the compound symbol using the circular convolution operator. For example, to unbind **SUBJ** from **MICE**  $\circledast$  **SUBJ** we would construct the inverse symbol **SUBJ**\* and bind it with the compound symbol, **MICE**  $\circledast$  **SUBJ**  $\circledast$  **SUBJ**\*. The pseudo-inverse (with respect to circular convolution) of an n-dimensional vector a can be constructed as  $a^* = (a_0, a_{n-1}, a_{n-2}, \ldots, a_1)$ . However, since this is only an p-seudo-inverse the result of (**MICE**  $\circledast$  **SUBJ**)  $\circledast$  **SUBJ**\* is not exactly **MICE**. Plate (1995,  $\S$ II.E) provides a demonstration of why the pseudo-inverse has this shape.

This same technique can be used to unbind terms from compound expressions that were constructed through the addition of bound symbols. For example, to determine the subject of the expression **S**, *mice eat cheese*, we would compute:

$$S \circledast SUBJ^* \approx MICE$$

$$(MICE \circledast SUBJ + EAT \circledast VRB + CHEESE \circledast OBJ) \circledast SUBJ^* \approx MICE$$

Table 2.2 shows the similarity between the result of unbinding different symbols from S and the original symbols from the vocabulary. It is clear that each of the unbound symbols,  $S \otimes x^*$ , is most similar to the symbol that was originally bound with x – for example,  $S \otimes SUBJ^*$  is most similar to MICE.

Implementations of this form of vector-based representation often replace the output of an unbinding operation with a canonical symbol from the vocabulary to reduce the

|                       | MICE  | EAT   | CHEESE | SUBJ  | OBJ   | VRB   | S     |

|-----------------------|-------|-------|--------|-------|-------|-------|-------|

| S ⊛ SUBJ*             | 0.51  | 0.02  | -0.03  | -0.16 | 0.05  | 0.03  | -0.26 |

| $S\circledast VRB^*$  | -0.10 | 0.52  | -0.14  | 0.04  | -0.05 | 0.12  | 0.06  |

| $S \circledast OBJ^*$ | 0.01  | -0.07 | 0.50   | 0.05  | -0.18 | -0.04 | -0.20 |

| S ⊛ MICE*             | -0.27 | 0.04  | 0.03   | 0.49  | 0.01  | -0.10 | 0.07  |

**Table 2.2** – Similarity of unbound symbols to vectors in the original vocabulary.

noise presented to later stages of computation. For example, since the result of unbinding **SUBJ** from **S** is most similar to **MICE** (the dot product was 0.51, see the first row of Table 2.2) the vector **MICE** will be presented to further stages of computation rather than the value of  $\mathbf{S} \circledast \mathbf{SUBJ}^*$ . In the Semantic Pointer Architecture this form of 'cleanup' is achieved with an autoassociative memory (Stewart, Tang, and Eliasmith 2011).

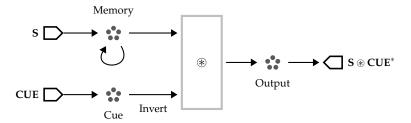

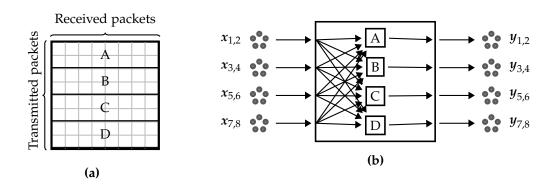

The 'question answering' example used above that extracted the subject, object and verb from the expression **S** can be implemented as a neural network using the principles of the Neural Engineering Framework. Figure 2.15 shows the top-level view of such a network. One input to the network is used to store the expression **S** in a memory and the other provides a series of *cues*. Each cue is inverted and fed to a neural network which implements circular convolution. Output from the memory is also fed to the circular convolution network to produce the 'answer' to the 'question' provided by the *cue*.

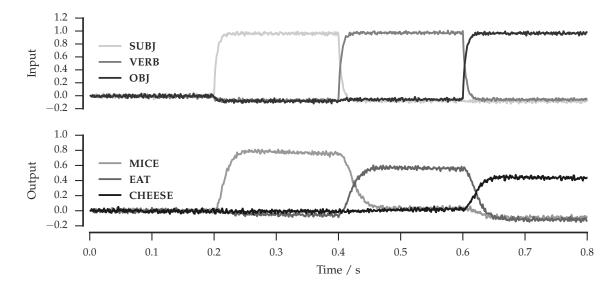

Figure 2.16 shows the results of a simulation of this network. The top panel of the figure shows the dot product between the input cue and each of the symbols **SUBJ**, **VRB** and **OBJ**. No cues were provided for the first 0.2s of the simulation, during which the expression **S** was stored in the memory. Subsequently, each of the cues was presented for a period of 0.2s. The lower panel shows the dot products between the output of the network and each of the symbols **MICE**, **EAT** and **CHEESE**. As expected, the output of the network was most similar to **MICE** when given the cue **SUBJ**, to **EAT** when given the cue **VRB** and to **CHEESE** when given the cue **OBJ**.

**Figure 2.15** – High-level view of a symbol unbinding neural network. The structure of the circular convolution network (marked ' $\circledast$ ') is described later in the thesis.

**Figure 2.16** – Simulation of a neural implementation of symbol unbinding. The upper panel shows the input cues being applied to the neural network and the lower panel shows the effect of unbinding each cue against an expression, **S**, stored in a memory. Each line represents the time-varying similarity between a symbol in the vocabulary and the input or output value of interest.

#### Symbols and compressed representations

In the previous example we used a number of randomly selected vectors to represent base symbols (SUBJ for *subject* and so on). These base vectors were combined using addition and circular convolution to construct new vectors of the same size to represent new symbols. Necessarily these new vectors are somewhat compressed relative to their original constituents, evidence of which can be seen in the levels of dissimilarity found when unbinding base symbols from a compound symbol. However, new vectors may be formed not only through the combination and compression of existing vectors of the same dimensionality but also through the compression of vectors of higher dimensionality. Tang and Eliasmith (2010) extend the work of Hinton and Salakhutdinov (2006) to show that Deep Belief Networks (DBNs) can be used to construct compressed representations of inputs such as sensory stimuli. Consequently, some symbols in the Semantic Pointer Architecture may be represented by vectors which are derived from the characteristics of the referent of the symbol in some external modality such as vision or sound. Since SPA uses the dot product of vectors to determine their similarity, using external stimuli to form the vectors that are the input of a neural system is a reasonable way to ensure that similar input stimuli are translated into functionally similar vectors.

## 2.4 Cognitive architectures and Spaun

Section 2.1 described, and provided simple models of, the basic components of the nervous system. In Section 2.2, these components were combined into larger units which could represent and transform multi-dimensional values. Finally, methods for using multi-dimensional values to represent symbol-like values and for using these symbols in computation-like processes were introduced in Section 2.3. Each of these sections represented a different level of scale and complexity – from basic components through to complex representations. A similar story would take us from transistors to logic gates to combinatorial and sequential logic, and finally to processors.