# AN ANALYSIS OF CACHE PARTITIONING TECHNIQUES FOR CHIP MULTIPROCESSOR SYSTEMS

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Engineering and Physical Sciences

2008

By Konstantinos Nikas School of Computer Science

## Contents

| Ał | ostra | ct                                  | 10 |

|----|-------|-------------------------------------|----|

| De | eclar | ation                               | 11 |

| Co | opyri | ght                                 | 12 |

| Ac | kno   | wledgements                         | 13 |

| 1  | Intr  | oduction                            | 14 |

|    | 1.1   | Chip Multiprocessor Architectures   | 15 |

|    |       | 1.1.1 Wire Delays                   | 15 |

|    |       | 1.1.2 Limited Parallelism           | 15 |

|    |       | 1.1.3 Design Complexity             | 16 |

|    | 1.2   | Memory Hierarchy Design Challenges  | 17 |

|    | 1.3   | Research Aims                       | 19 |

|    | 1.4   | Terminology                         | 19 |

|    | 1.5   | Thesis Overview                     | 20 |

| 2  | Cac   | he Systems                          | 22 |

|    | 2.1   | Cache Design                        | 22 |

|    |       | 2.1.1 Single Processor Systems      | 23 |

|    |       | 2.1.2 Chip Multithreaded Systems    | 27 |

|    | 2.2   | Bloom Filters                       | 33 |

|    |       | 2.2.1 Description                   | 33 |

|    |       | 2.2.2 Applications of Bloom filters | 34 |

|    | 2.3   | Summary                             | 35 |

| 3  | Jan   | naica and Simulation Framework      | 36 |

|    | 3.1   | The Jamaica Architecture            | 36 |

|   | 3.2 | Simulation Environment                            | 38 |

|---|-----|---------------------------------------------------|----|

|   | 3.3 | Software Environment                              | 39 |

|   | 3.4 | Benchmark Descriptions                            | 39 |

|   |     | 3.4.1 Java Grande Benchmarks                      | 40 |

|   |     | 3.4.2 NAS Parallel Benchmarks                     | 41 |

|   |     | 3.4.3 Benchmark Configuration                     | 42 |

|   | 3.5 | Summary                                           | 43 |

| 4 | Cac | he Replacement Policy                             | 44 |

|   | 4.1 | Evaluation of LRU                                 | 44 |

|   |     | 4.1.1 Single Core Systems                         | 44 |

|   |     | 4.1.2 Dual Core System                            | 50 |

|   |     | 4.1.3 Quad Core System                            | 56 |

|   |     | 4.1.4 Conclusion                                  | 57 |

|   | 4.2 | Static Cache Partitioning                         | 57 |

|   | 4.3 | Conclusions                                       | 61 |

| 5 | Dyn | amic Cache Partitioning                           | 62 |

|   | 5.1 | LRU Variation                                     | 63 |

|   |     | 5.1.1 Overview                                    | 63 |

|   |     | 5.1.2 Evaluation                                  | 63 |

|   | 5.2 | Monitoring Schemes                                | 66 |

|   |     | 5.2.1 Overview                                    | 66 |

|   |     | 5.2.2 Cache-Partitioning Aware Replacement Policy | 68 |

|   |     | 5.2.3 Utility-Based Cache Partitioning            | 71 |

|   | 5.3 | Partitioning 'on the fly'                         | 74 |

|   |     | 5.3.1 Description                                 | 74 |

|   |     | 5.3.2 Evaluation                                  | 75 |

|   |     | 5.3.3 Conclusions                                 | 78 |

|   | 5.4 | Summary                                           | 79 |

| 6 | AN  | ew Cache Partitioning Scheme                      | 81 |

|   | 6.1 | Adaptive Bloom Filter Cache Partitioning          | 82 |

|   |     | 6.1.1 Motivation                                  | 82 |

|   |     | 6.1.2 Description                                 | 83 |

|   |     | 6.1.3 Partitioning the Cache                      | 86 |

|   |     | 6.1.4 Simulation Results                                                                                                                                                                                                                                       | 87                          |

|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|   | 6.2 | Implementation Considerations                                                                                                                                                                                                                                  | 92                          |

|   |     | 6.2.1 Bloom Filter Arrays                                                                                                                                                                                                                                      | 92                          |

|   |     | 6.2.2 Monitoring Period                                                                                                                                                                                                                                        | 94                          |

|   | 6.3 | Cost Analysis                                                                                                                                                                                                                                                  | 95                          |

|   |     | 6.3.1 Partitioning Algorithm                                                                                                                                                                                                                                   | 95                          |

|   |     | 6.3.2 Hardware Overhead                                                                                                                                                                                                                                        | 03                          |

|   | 6.4 | Comparison with Other Schemes                                                                                                                                                                                                                                  | 106                         |

|   | 6.5 | Summary                                                                                                                                                                                                                                                        | 09                          |

| 7 | Con | iclusions 1                                                                                                                                                                                                                                                    | 10                          |

| - |     |                                                                                                                                                                                                                                                                | -                           |

| - |     | Cache Partitioning                                                                                                                                                                                                                                             | 11                          |

| - |     |                                                                                                                                                                                                                                                                | 11                          |

| - |     | 7.1.1 Adaptive Bloom Filter Cache Partitioning                                                                                                                                                                                                                 |                             |

| _ | 7.1 | 7.1.1 Adaptive Bloom Filter Cache Partitioning17.1.2 Cache Partitioning Evaluation1                                                                                                                                                                            | 11                          |

| _ | 7.1 | 7.1.1 Adaptive Bloom Filter Cache Partitioning       1         7.1.2 Cache Partitioning Evaluation       1         Future Work       1                                                                                                                         | 111                         |

| _ | 7.1 | 7.1.1 Adaptive Bloom Filter Cache Partitioning       1         7.1.2 Cache Partitioning Evaluation       1         Future Work       1         7.2.1 Many-core Architectures       1                                                                           | 111<br>12<br>13             |

| - | 7.1 | 7.1.1 Adaptive Bloom Filter Cache Partitioning       1         7.1.2 Cache Partitioning Evaluation       1         Future Work       1         7.2.1 Many-core Architectures       1         7.2.2 Multithreaded Workloads       1                             | 111<br>12<br>13<br>13       |

| - | 7.1 | 7.1.1 Adaptive Bloom Filter Cache Partitioning17.1.2 Cache Partitioning Evaluation17.1.2 Cache Partitioning Evaluation1Future Work17.2.1 Many-core Architectures17.2.2 Multithreaded Workloads17.2.3 Power Consumption1                                        | 111<br>12<br>13<br>13<br>13 |

| - | 7.1 | 7.1.1 Adaptive Bloom Filter Cache Partitioning17.1.2 Cache Partitioning Evaluation17.1.2 Cache Partitioning Evaluation1Future Work17.2.1 Many-core Architectures17.2.2 Multithreaded Workloads17.2.3 Power Consumption17.2.4 Exposure to Higher System Levels1 | 111<br>12<br>13<br>13<br>14 |

### Bibliography

## List of Tables

| 1.1 | Memory hierarchy of developed CMPs                            | 18  |

|-----|---------------------------------------------------------------|-----|

| 3.1 | Benchmarks' configuration                                     | 42  |

| 4.1 | System's configuration                                        | 45  |

| 4.2 | Benchmarks' cache space requirements                          | 50  |

| 4.3 | Average number of ways occupied by <i>heap</i> and co-runners | 54  |

| 4.4 | Results of quad core system simulations                       | 56  |

| 6.1 | Number of possible partitions                                 | 96  |

| 6.2 | Storage overhead per processor                                | 104 |

| 7.1 | Comparison of LRU and cache partitioning                      | 112 |

# **List of Figures**

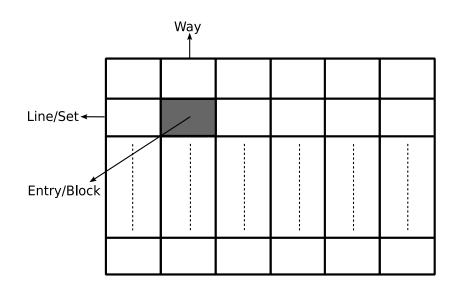

| 1.1  | Example of a 6-way set associative cache                                          | 20 |

|------|-----------------------------------------------------------------------------------|----|

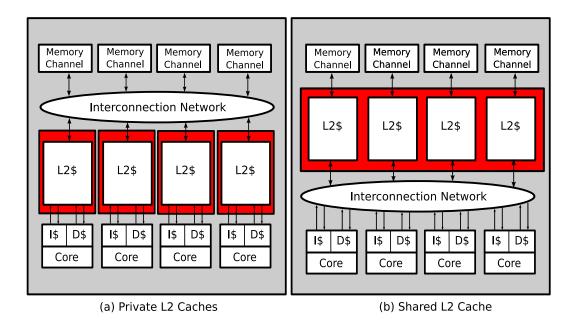

| 2.1  | L2 Cache Designs                                                                  | 29 |

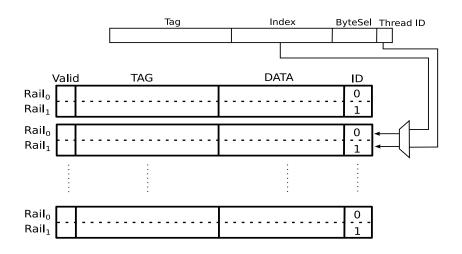

| 2.2  | A two-rail thread associative cache [65]                                          | 32 |

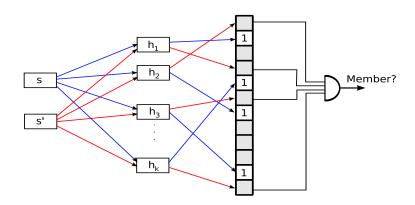

| 2.3  | Example of a Bloom filter                                                         | 33 |

| 3.1  | The Jamaica architecture                                                          | 37 |

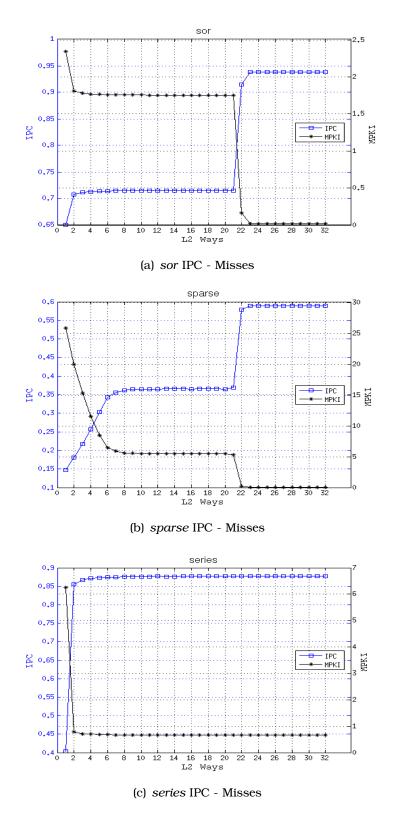

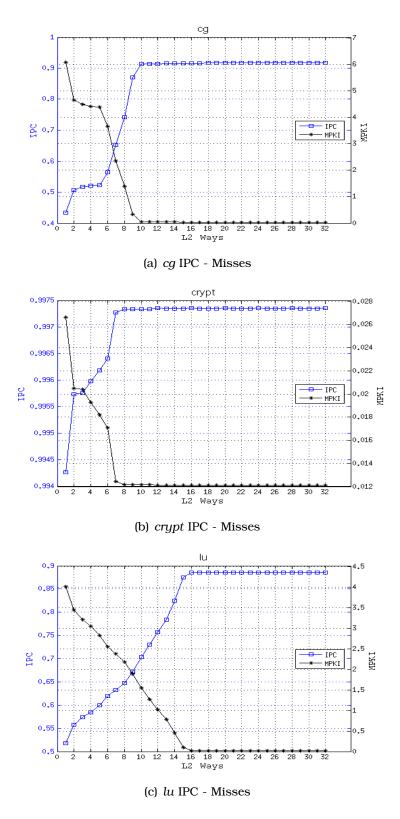

| 4.1  | Low utility applications                                                          | 46 |

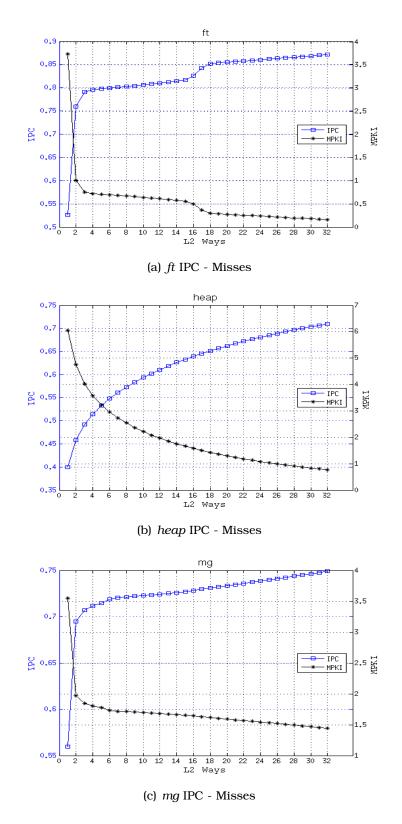

| 4.2  | High utility applications                                                         | 48 |

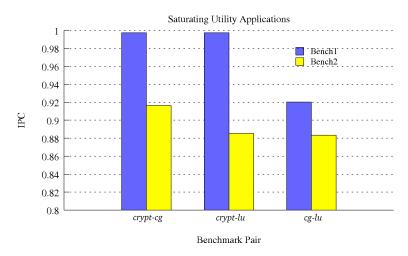

| 4.3  | Saturating utility applications                                                   | 49 |

| 4.4  | Dual core system                                                                  | 51 |

| 4.5  | Performance of saturating utility benchmarks                                      | 51 |

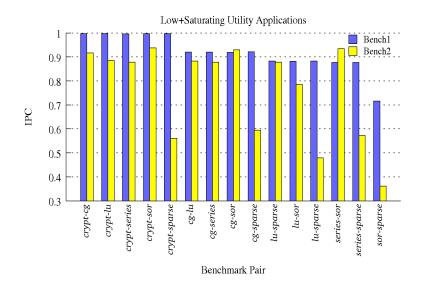

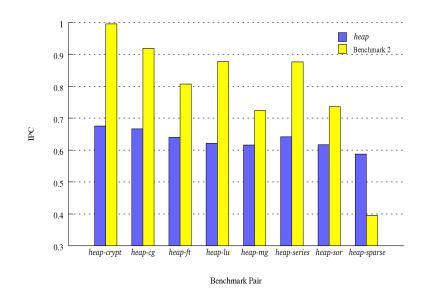

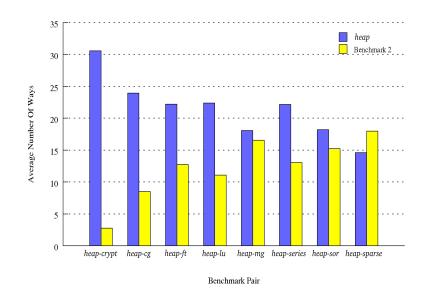

| 4.6  | Performance of low and saturating utility benchmarks                              | 52 |

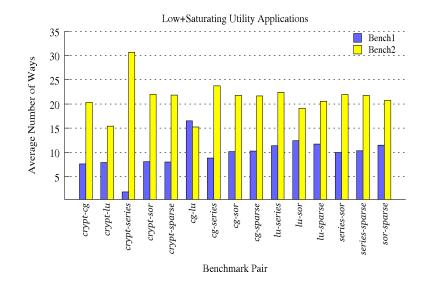

| 4.7  | Average L2 cache ways occupancy                                                   | 53 |

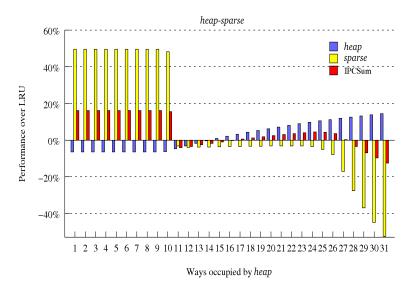

| 4.8  | Performance of <i>heap</i> and co-runners                                         | 54 |

| 4.9  | L2 cache ways occupancy for <i>heap</i> and co-runners                            | 55 |

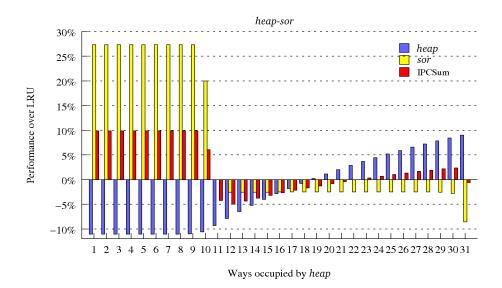

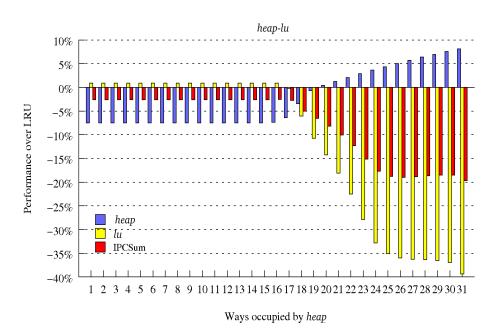

| 4.10 | Performance gains/losses for <i>heap</i> and <i>sor</i> for different partitions  | 58 |

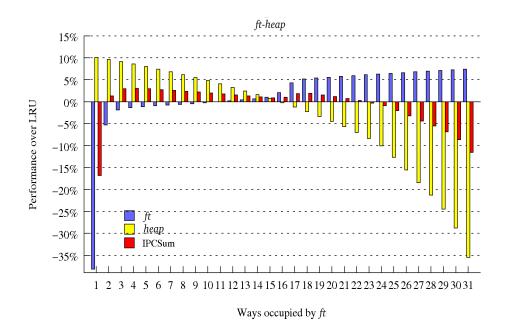

| 4.1  | l Performance gains/losses for <i>ft</i> and <i>heap</i> for different partitions | 59 |

| 4.12 | 2 Performance gains/losses for <i>heap</i> and <i>lu</i> for different partitions | 60 |

| 4.13 | BExample of non optimal static partitioning                                       | 61 |

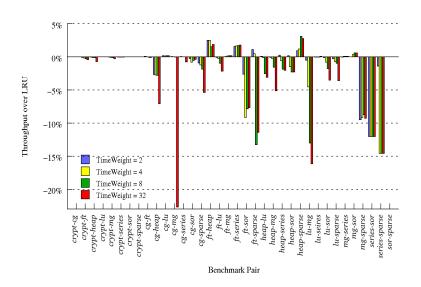

| 5.1  | Throughput over LRU for different time weights                                    | 64 |

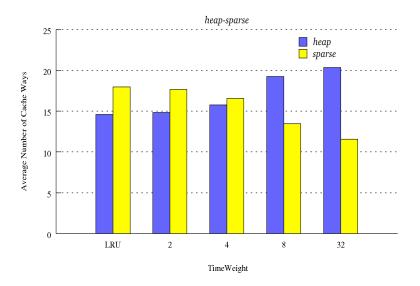

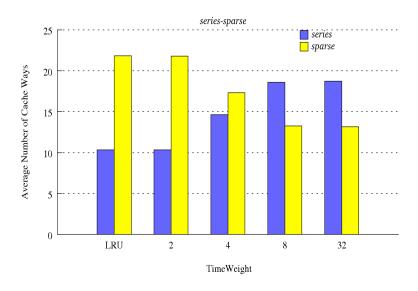

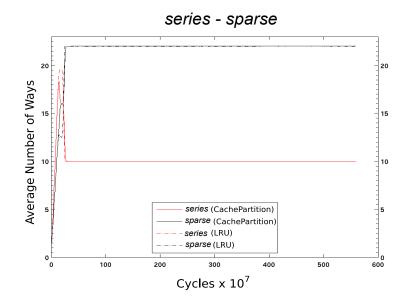

| 5.2  | Average number of cache ways occupied by <i>heap</i> and <i>sparse</i>            | 64 |

| 5.3  | Performance over LRU for static cache partitioning scheme                         | 65 |

| 5.4  | Average number of cache ways occupied by series and sparse                        | 66 |

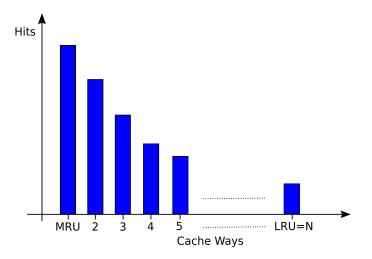

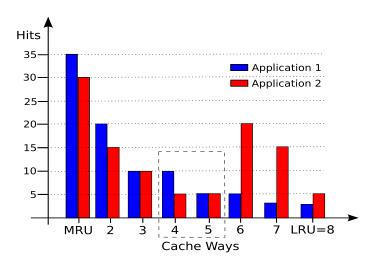

| 5.5  | Distribution of an application's hits                                             | 67 |

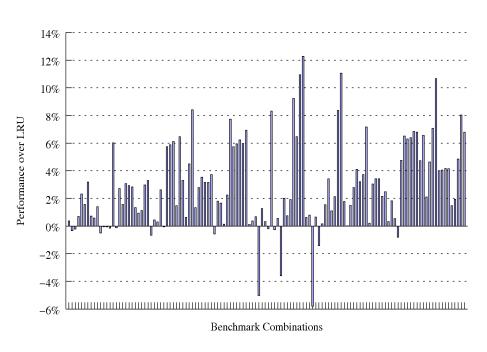

| 5.6  | Cache partitioning aware replacement performance over LRU for                     |    |

|      | a dual core system                                                                | 70 |

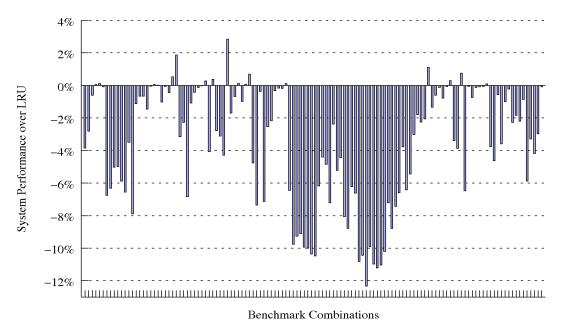

| 5.7 Cache-partitioning aware replacement performance over LRU for                 |      |

|-----------------------------------------------------------------------------------|------|

| a quad core system                                                                | 70   |

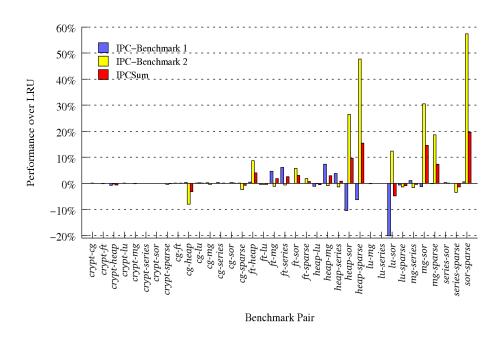

| 5.8 Utility-based partitioning scheme's performance over LRU for a                |      |

| dual core system                                                                  | 72   |

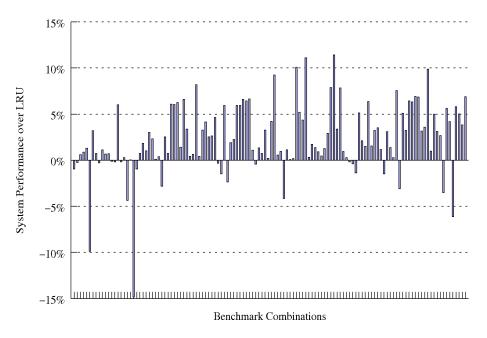

| 5.9 Utility-based partitioning scheme's performance over LRU for a                |      |

| quad core system                                                                  | 73   |

| 5.10 Ideal scheme's performance over LRU for a quad core system $\ . \ .$         | 74   |

| 5.11 Performance over LRU when repartitioning every near miss $\ldots$            | 76   |

| 5.12L2 cache ways occupancy for heap and sparse                                   | 76   |

| 5.13L2 cache ways occupancy for series and sparse                                 | 77   |

| 5.14 Example of 2 applications' profiles that share a L2 cache                    | 79   |

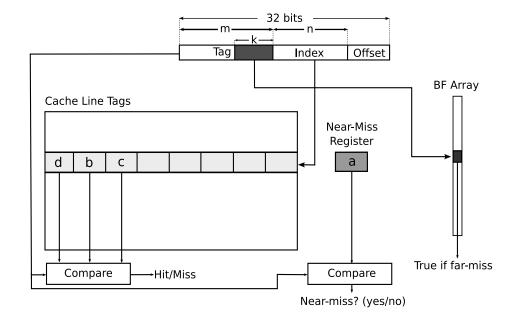

| 6.1 Monitoring components of the adaptive Bloom filter cache parti-               |      |

| tioning scheme                                                                    | 84   |

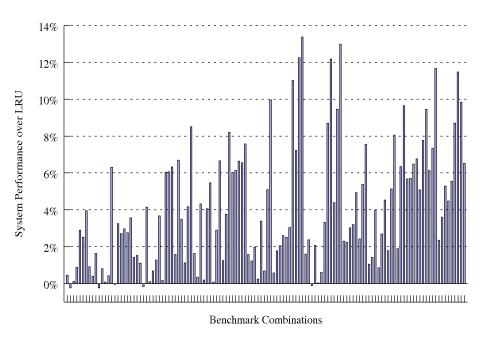

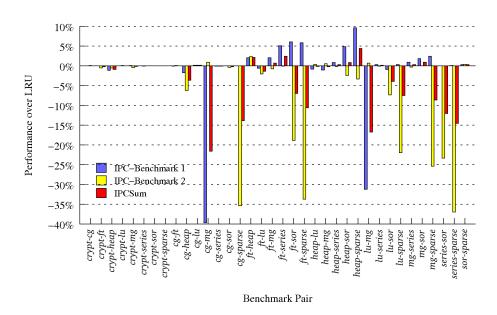

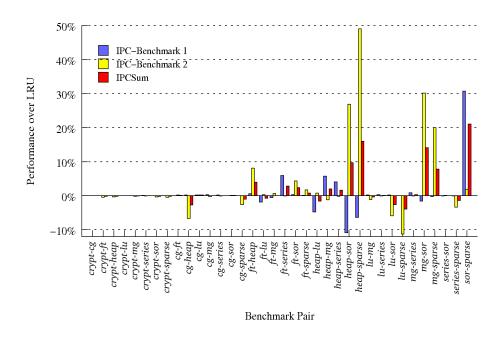

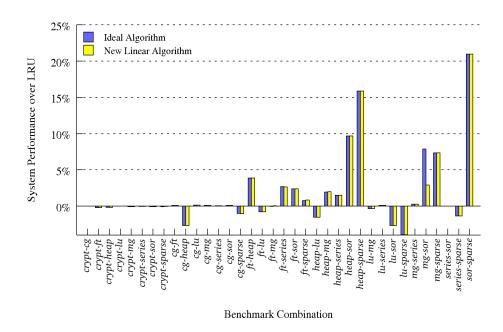

| 6.2 Performance over LRU for a dual core system                                   | 88   |

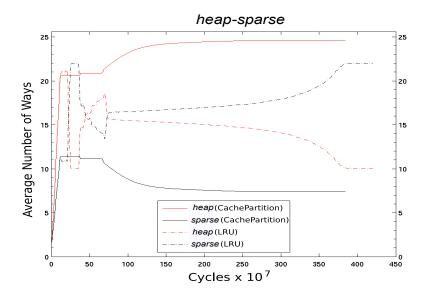

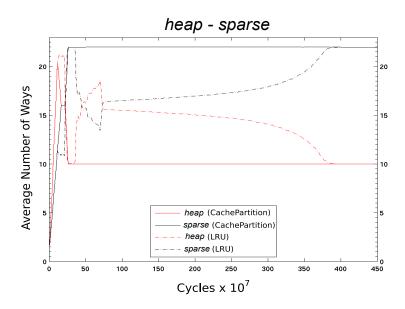

| 6.3 L2 cache ways occupancy for <i>heap</i> and <i>sparse</i>                     | 88   |

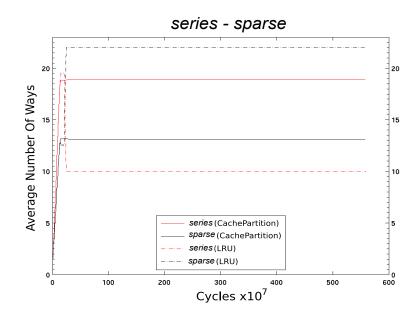

| 6.4 L2 cache ways occupancy for <i>series</i> and <i>sparse</i>                   | 89   |

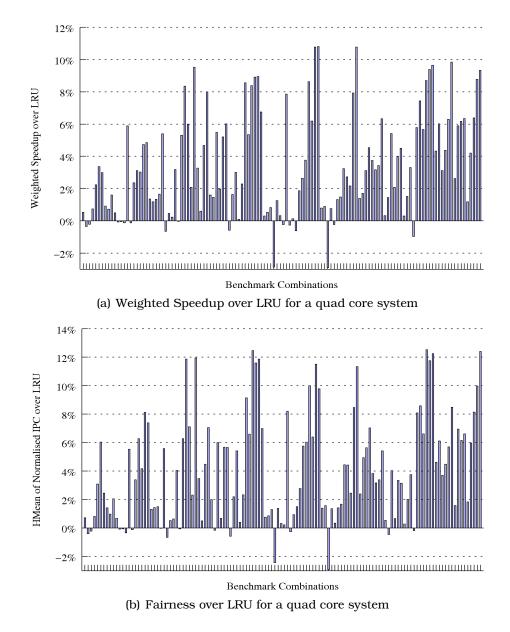

| 6.5 Performance over LRU for a quad core system                                   | 90   |

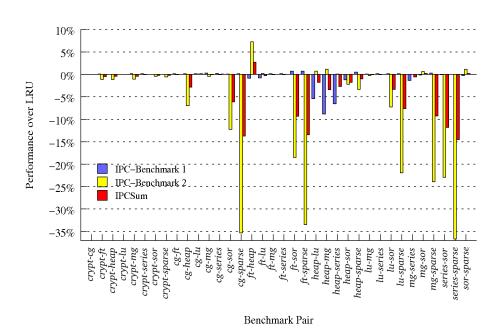

| 6.6 Evaluation on weighted speedup and fairness metrics                           | 91   |

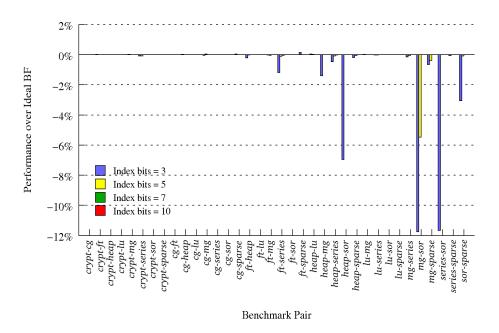

| 6.7 Effect of different Bloom filter arrays' sizes for a dual core system         | 93   |

| 6.8 Effect of using 32-bit instead of 32-Kbit Bloom filter arrays for a           |      |

| quad core system                                                                  | 94   |

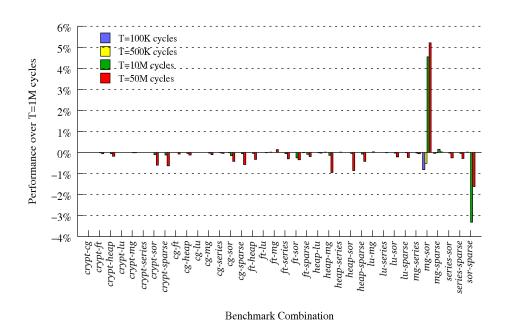

| 6.9 Effects of different monitoring periods for a dual core system                | 95   |

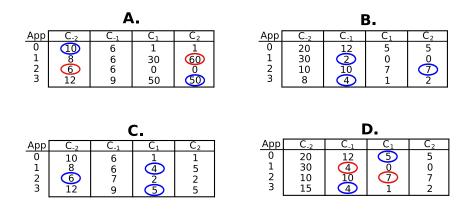

| 6.10 Four examples of the partitioning algorithm for a quad core system           | ı 98 |

| 6.11 Comparison of new and old partitioning algorithm for a dual core             |      |

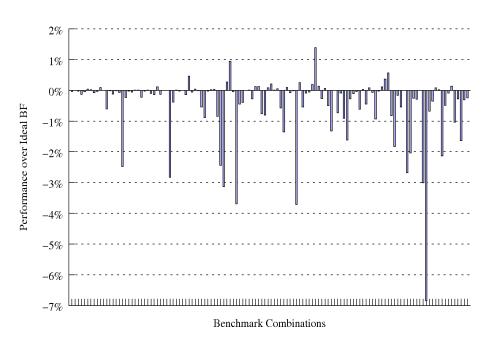

| system                                                                            | 100  |

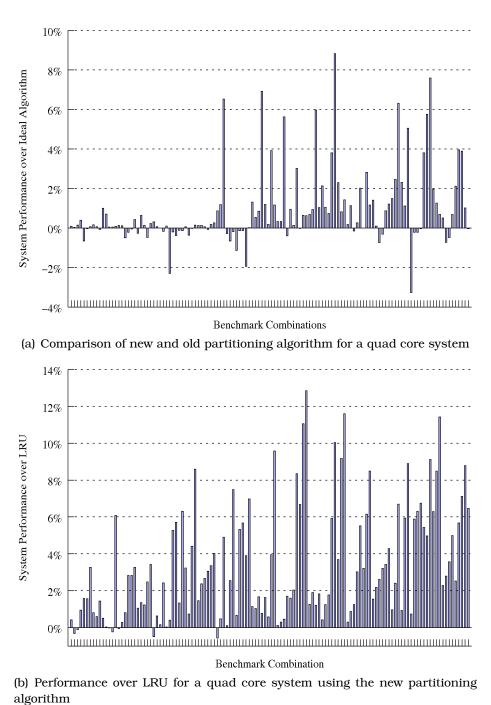

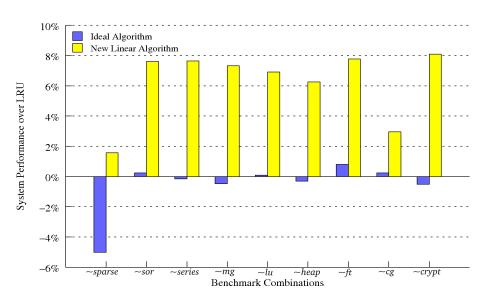

| $6.12\mathrm{Effects}$ of the new partitioning algorithm for a quad core system . | 101  |

| 6.13Comparison of new and old partitioning algorithm for a system                 |      |

| with 8 cores                                                                      | 102  |

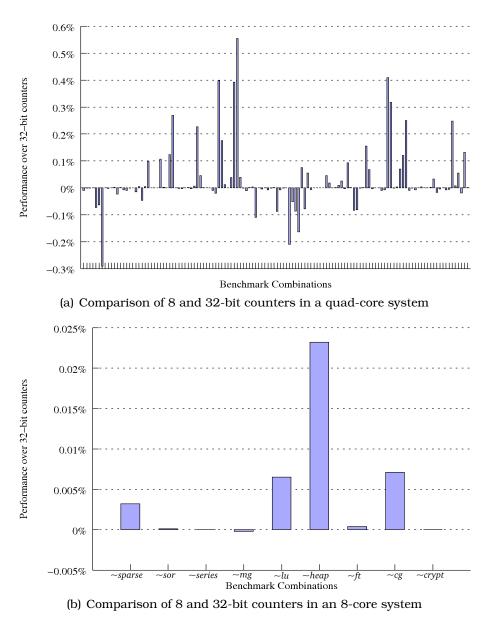

| 6.14 Performance using 8-bit counters over a system that uses 32-bit              |      |

| counters                                                                          | 103  |

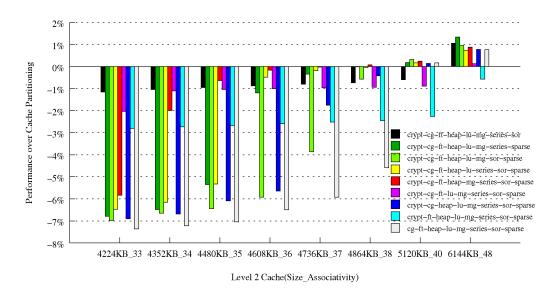

| 6.15 Performance of a 4MB, 32-way associative L2 cache using cache                |      |

| partitioning against bigger caches employing the LRU policy $\ldots$              | 105  |

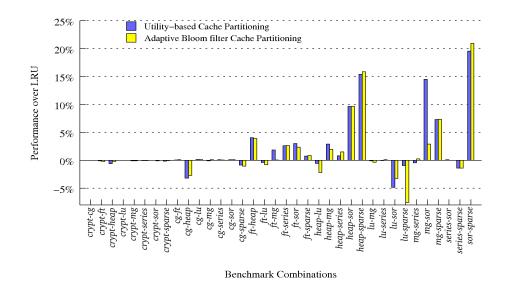

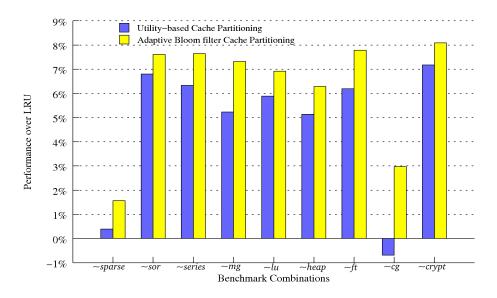

| 6.16 Comparison of the utility-based and adaptive Bloom filter cache              |      |

| partitioning schemes for a dual-core system                                       | 106  |

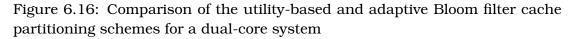

| 6.17 Comparison of the utility-based and adaptive Bloom filter cache |     |

|----------------------------------------------------------------------|-----|

| partitioning schemes for a quad-core system                          | 107 |

| 6.18 Comparison of the utility-based and adaptive Bloom filter cache |     |

| partitioning schemes for an eight-core system                        | 108 |

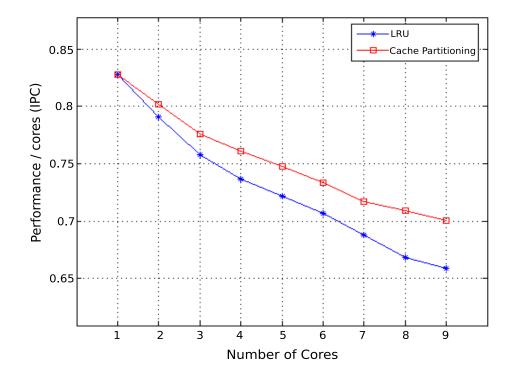

| 7.1 Performance normalised with number of cores for LRU and cache    |     |

| partitioning                                                         | 113 |

# List of Algorithms

| 1 | Partitioning Algorithm |  | • |  | • |  | • |  | • |  | • | • | • | • | • | • | • |  |  | • |  |  | • | • | • | 97 | 7 |

|---|------------------------|--|---|--|---|--|---|--|---|--|---|---|---|---|---|---|---|--|--|---|--|--|---|---|---|----|---|

|---|------------------------|--|---|--|---|--|---|--|---|--|---|---|---|---|---|---|---|--|--|---|--|--|---|---|---|----|---|

## Abstract

Currently, there is a trend to increase the number of processors on a single chip leading to the development of chip multiprocessor (CMP), and eventually manycore, architectures. Cache design has been extensively studied in the context of uniprocessor systems and computer architects have transfered existing policies and cache design techniques from uniprocessors to the new architectures. A typical example of such a migration is the employment of the Least Recently Used (LRU) replacement policy, which is widely accepted as the best line replacement policy for uniprocessor caches. However the parameters are different in CMP systems, as the sharing of the cache hierarchy amongst several concurrent threads imposes new constraints and creates new challenges. It is important, therefore, to reevaluate the effectiveness of these policies in CMP architectures.

This thesis investigates the interference between threads that run simultaneously on CMPs sharing different levels of the cache hierarchy and evaluates cache partitioning as a means of alleviating its consequences. Several schemes are studied and their advantages and drawbacks are used as a guide for the development of a novel, low-cost cache partitioning scheme that achieves better performance than LRU and shows increasing promise over alternative schemes as the number of on-chip processors increases.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the "Copyright") and s/he has given The University of Manchester the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

- ii. Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the John Rylands University Library of Manchester. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

- iii. The ownership of any patents, designs, trade marks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and exploitation of this thesis, the Copyright and any Intellectual Property Rights and/or Reproductions described in it may take place is available from the Head of School of School of Computer Science (or the Vice-President).

## Acknowledgements

This research was completed under the supervision of Dr. Jim Garside to whom I am obliged. I would like to thank him for all the help, encouragement, support and constructive feedback he has given me over the last four years. I would also like to thank all the members of the APT group. Special thanks go to Dr. Jeremy Singer for efficiently proofreading this thesis in record time.

I would also like to thank all my friends, new and old ones. Especially Teta, Dimitris and Nikos for making life here more enjoyable and Aris, Antreas and Ioanna in Greece for their 24/7 phone support.

Finally, and certainly not least, I would like to thank my parents for encouraging me to keep on chasing my dreams, for their continued help and support all these years. I have come this far because of you.

## **Chapter 1**

## Introduction

As is well known, the feature size of silicon fabrication technology is continuously shrinking. In fact, in the last decade only, it has been scaled down from 350nm to 45nm [26]. This has enabled the improvement of system performance in two ways. Firstly, designers have been increasing system operating frequency at a rapid rate by exploiting the smaller and faster transistors and by building deeper pipelines, thus reducing the number of levels of logic per cycle. Secondly, the increasing transistor budgets have been utilised by several microarchitectural techniques, like superscalar issue, out-of-order issue, on-chip caching and deep pipelines supported by sophisticated branch predictors [57].

Unfortunately, as has been recently noted [19, 7], the future effectiveness of these approaches is limited due to the emergence of two main constraints. Firstly, the increase in the number of transistors and their switching frequency leads to an overall growth in power consumption and energy. Additionally, it is becoming extremely difficult to remove the dissipated heat from the chip. Secondly, as the feature size is decreased, wire delays do not scale efficiently and have become a major design limitation for large integrated circuits.

These problems have caused a change in the design paradigm of the microprocessor industry. Nowadays Chip Multi-Processors (CMPs) are being developed by all the main vendors such as AMD [3], IBM [29], Intel [40] and Sun [36]. However, the sharing of the on-chip resources amongst the cores imposes new constraints and creates new challenges for designers. This thesis focuses on the sharing of cache between concurrently running applications and evaluates cache partitioning schemes as a mean of optimising the overall system performance. The remainder of this chapter presents the case for CMP architectures, outlines the cache hierarchies of some of the developed systems and concludes with an overview of the rest of the thesis.

### **1.1 Chip Multiprocessor Architectures**

As mentioned previously, CMP architectures have been developed to provide solutions to the problems facing microprocessor designers. This section presents a short overview of some of these solutions.

#### 1.1.1 Wire Delays

The signal delay for a wire increases in proportion to the product of its resistance and capacitance. As feature size decreases, the wires' section gets smaller and the resistance and capacitance per unit length increase. In the past few years increasingly larger fractions of the clock cycles have been consumed by the propagation delay of signals on wires, reducing the number of logic gates reachable within a cycle.

On the other hand, CMPs incorporate multiple processors on the same chip, with each core occupying a relatively small area. Therefore, the critical paths within each processor circuit are minimised and the effects of wire delays reduced. In these systems only the wires of the communication network between processors and caches need to be long. These are less frequently used compared to wires inside the cores and, therefore, less latency critical.

#### 1.1.2 Limited Parallelism

Many processors are designed to exploit Instruction-Level Parallelism (ILP). More specifically, independent instructions found within an instruction stream are sent to multiple functional units to be executed concurrently. By allowing more than one instruction to be executed per clock cycle, the performance of the system is improved. However, this approach is limited by instruction dependencies and long-latency operations [62]. Thread-Level Parallelism (TLP) offers an attractive alternative to ILP. A thread is defined as a separate process with its own instructions and data. It could either represent an independent program or a process that is part of a parallel program consisting of multiple processes. In contrast to ILP, which exploits parallel operations within a code segment, TLP extracts parallelism by executing multiple threads which are inherently parallel.

Single processor systems have two options to exploit TLP. In "fine-grained multithreading" the execution of multiple threads is interleaved by switching between threads on each instruction. The second option, "coarse-grained multithreading", switches threads on costly stalls, for example L2 cache misses, or at specific time quantums.

CMPs are specifically designed to exploit TLP. In fact, by providing many processors, they can achieve even finer-grained parallelism than single processor systems that exploit TLP, as multiple threads can execute simultaneously.

### 1.1.3 Design Complexity

Recently Intel presented the Montecito processor [39]. Its 1.7 billion-transistors have signalled the start of the era of billion transistor architectures. However, as the number of transistor rises, the design complexity increases as well. The International Technology Roadmap for the Semiconductor Industry (ITRS) 2005 [1] has recognised that in order to maintain design quality, design implementation productivity must be improved to the same degree as design complexity is scaled.

Design replication offers an attractive solution to the complexity problem and is exploited in CMP designs. For example, Sun's Niagara architecture [36] employs eight identical SPARC processors. The modular nature of these systems allows the designers to reuse components, thus cutting down design and verification time.

### 1.2 Memory Hierarchy Design Challenges

CMPs have recently emerged as an attractive alternative to uniprocessor systems. However this shift in the design paradigm has created new challenges. One of these is the design of the memory hierarchy. The high number of threads running simultaneously increases the demand on the memory bandwidth. Cacheing helps to alleviate this, but the problems of cache design for CMPs are not yet fully understood.

Firstly, these are shared memory systems and all the processors are assumed to see the same memory space. In practice this is not directly feasible as different levels of the cache hierarchy could be shared amongst different numbers of processors. CMPs could exploit their multiple cores to schedule parallel threads that execute the same instruction stream but on independent data sets, as is the case in parallel programs such as raytracer [56] and several server applications. In a different scenario, the working sets of the parallel threads could overlap, as is the case for databases. Sharing the cache hierarchy is a straightforward solution; however shared caches exhibit a higher access time and the bandwidth requirements of the system are increased. On the other hand, private caches have lower hit latencies but the effective cache capacity of the system is reduced as cache entries are often replicated in multiple private caches.

Clearly there is a trade-off and the designers need to consider each system's requirements and specifications to make wise decisions. The majority of the proposed CMPs today keep the L1 caches private for each processor to avoid increasing their access time and share the next levels of the cache hierarchy. Table 1.1 outlines the memory hierarchies of Niagara [36], Power 5 [29] and Montecito [39] and reveals the different decisions made by the designers regarding cache sizes and associativity and the sharing or not of specific levels of the cache hierarchy.

Another important challenge that the designers of CMPs face is the selection of an efficient cache replacement algorithm. The architectures described in Table 1.1 employ the random, the Least Recently Used (LRU) and the Not Recently Used (NRU) policies. These policies have migrated from the single processor

|                          | Sun Niagara   | IBM Power 5   | Intel Montecito |             |  |  |  |  |  |  |

|--------------------------|---------------|---------------|-----------------|-------------|--|--|--|--|--|--|

| Processors/chip          | 8             | 2             | 2               |             |  |  |  |  |  |  |

| Threads/processor        | 4             | 2             | 2               |             |  |  |  |  |  |  |

| Instruction Cache        | 16KB          | 64KB          | 1               | 6KB         |  |  |  |  |  |  |

| per processor            | 4-way         | 2-way         | 4               | -way        |  |  |  |  |  |  |

| Data Cache               | 8KB           | 32KB          | 1               | 6KB         |  |  |  |  |  |  |

| per processor            | 4-way         | 4-way         | 4               | -way        |  |  |  |  |  |  |

|                          | write-through |               | write           | -through    |  |  |  |  |  |  |

| Write Policy             | no allocation | write-through | no allocation   |             |  |  |  |  |  |  |

|                          | on writes     |               | on writes       |             |  |  |  |  |  |  |

| L1 replacement<br>policy | Random        | LRU           | LRU             |             |  |  |  |  |  |  |

|                          | shared        | shared        | private         |             |  |  |  |  |  |  |

| On-chip L2 Cache         | 3MB           | 1.875MB       | I\$ 1MB         | D\$ 256KB   |  |  |  |  |  |  |

|                          | 12-way        | 10-way        | 8-way           | 8-way       |  |  |  |  |  |  |

| Write Policy             | write-back    | write-back    | write-back      |             |  |  |  |  |  |  |

| L2 replacement<br>policy | Random        | LRU           | NRU             |             |  |  |  |  |  |  |

|                          |               | off-chip      | on-chi          | p (private) |  |  |  |  |  |  |

| L3 Cache                 | -             | 36MB          | 2MB             |             |  |  |  |  |  |  |

|                          |               | 10-way        | 6-way           |             |  |  |  |  |  |  |

Table 1.1: Memory hierarchy of developed CMPs

design domain and they are *"thread-blind"*, as they select which cache entry should be rejected regardless of which thread brought it into the cache or which thread suffered the cache miss. This, however, can cause problems in a CMP architecture and have a significant impact on the performance of the system.

More specifically, when each core is used to execute a different application, multiple working sets compete for the cache space. The employment of a thread-blind replacement policy allows interference, as data belonging to one thread may be evicted by data blocks belonging to other threads. A typical example is the execution of streaming applications. These applications exhibit a small amount of temporal locality and pollute the caches with data that will not be accessed again in the near future. A thread-blind replacement policy is not able to identify and deal with these pathological cases and severe performance problems such as cache thrashing and thread starvation could be caused.

Designers have tried to deal with this problem by increasing the cache's size

and associativity. However, the effectiveness of this approach is limited due to area and power constraints and other alternatives are needed, highlighting the importance of research in this field.

### 1.3 Research Aims

In the previous section it became apparent that different factors need to be taken into consideration in order to propose a cache hierarchy that will satisfy all the requirements. As it seems likely that the number of processors integrated on a silicon chip will continue to increase in the near future, policies should scale to accommodate an increasing number of competing threads whilst maximising overall instruction throughput.

This work studies the interference between threads that run simultaneously on CMPs sharing different levels of the cache hierarchy and evaluates cache partitioning as a mean of alleviating its consequences. Different schemes are studied and the results of the analysis are used as a guide to develop a novel scheme that can optimise the overall performance of the system at a low cost in terms of hardware overhead and complexity.

## 1.4 Terminology

In general this work adopts the terminology that Smith used in his detailed survey of cache design [55]. The following list of definitions clarify some of the terms used throughout this thesis. For convenience, Figure 1.1 shows an example of a 6-way set associative cache illustrating the usage of these terms.

- **Entry/Block** : An entry is a set of words with a common tag, distinguished only by the least significant bits of the memory address. There are typically 4 or 8 words long.

- **Line/Set** : A line or set is a collection of entries, the tags for which are checked in parallel during a cache access.

- **Way** : The number of ways is defined by the "degree of associativity" of the cache and is equal to the number of entries contained in a line.

Figure 1.1: Example of a 6-way set associative cache

### 1.5 Thesis Overview

This chapter has highlighted the advantages of CMP architectures and the problems that this research attempts to investigate. The remainder of the thesis is arranged as follows.

Chapter 2 reviews several schemes that attempt to improve the efficiency of cache hierarchies both in the single processor and the CMP domain.

Chapter 3 provides a short overview of the Jamaica CMP that provided the test bench for the evaluation of the different cache partitioning schemes. It also presents the simulation platform and the benchmarks used during these studies.

Chapter 4 evaluates the employment of the LRU replacement policy in CMPs and presents evidence that a cache partitioning scheme can improve the performance of the system.

Chapter 5 introduces cache partitioning schemes that have been proposed by other researchers. They are evaluated together with other schemes that were developed during this work but failed to improve the overall performance of the system. The advantages and drawbacks of each scheme are identified and then used to guide the development of a novel partitioning scheme.

Chapter 6 describes this novel scheme, evaluates its performance and analyses its complexity and hardware overhead.

Finally, Chapter 7 concludes this thesis by summarising the contributions made in addition to suggesting future expectations and possibilities.

## **Chapter 2**

## **Cache Systems**

Designers are responsible for selecting the appropriate cache according to the requirements of the system. The cache design space is big, as there are many variables that can affect the system's behaviour and performance. These include the total size of the cache, its associativity, the size of each cache line, the policy according to which lines are placed or replaced inside the cache array and the actual placement of the cache in the architecture and its distance from the processing cores. The increasing number of transistors per chip widens this range of options, as it is now possible to bring bigger caches closer to the processor or introduce multi-level cache hierarchies on chip.

This chapter presents several proposals aimed at improving the performance of the cache hierarchy for both single processor and CMP systems.

### 2.1 Cache Design

A straightforward solution to increase the cache's effectiveness and thus improve the overall performance, would be to increase the cache's size and associativity. Consequently, the cache would be able to hold more data blocks and reduce conflicts between data lines that map on the same cache line. This approach is primarily limited by the available area on the chip. Additionally, it makes the cache slower and more power hungry, which could ultimately have a negative effect on the system. Clearly, the effectiveness of this solution is limited and designers have been searching for other alternatives.

### 2.1.1 Single Processor Systems

Cache design has been extensively studied in the context of traditional uniprocessor systems. The schemes that are presented here attempt to adapt dynamically to the characteristics of the running programs and improve the performance of single processor systems.

#### Selective Caching

One group of these schemes has been looking at what needs to be put into the cache. Tyson *et al.* tried to reduce the average data access time by dynamically deciding whether to cache a particular data item based on the address of the instruction generating the request [63]. Their experiments showed that less than 5% of the total load instructions are responsible for causing over 99% of all cache misses. Based on that, they built "miss prediction tables", associating a 2-bit counter with each load instruction. The counter is incremented each time a load causes a miss and decremented in case of a hit. While the counter is at its highest value, the line is not stored in the cache.

González *et al.* proposed the "Dual Data Cache" which consists of two independent subcaches [20]. One is called "temporal cache" and is designed to exploit just temporal locality, while the other, named "spatial cache", is targetted on spatial locality as well. When the processor issues a memory request, both subcaches are looked up in parallel but, in case of a miss, the data that is brought from the next level of the memory hierarchy may be placed in one of the two subcaches or nowhere. The decision is based on a prediction of the type of the locality the memory reference exhibits. To make the prediction, the system uses a "Locality Prediction Table" which associates a memory reference with the instruction that issued the memory request and its past behaviour.

Johnson suggested the use of hardware monitors to track run-time memory access patterns [28]. More specifically, she used counters to monitor the access frequency of regions of memory. These were then used to guide caching decisions, such as cache bypassing, spatial locality optimisations and cache remapping. A history table was also used by Collins *et al.* [13]. In their scheme one entry per cache set is used to store the last evicted tag. On a miss, the tag of the requested line is compared to the stored tag of the most recently evicted line from that set. If they are the same, a conflict miss has been identified, otherwise it is a capacity miss. This classification of misses is used as a prediction of future miss classification and incorporated into various decisions, like victim cache design, cache prefetching or cache exclusion mechanisms. For example, only lines that were brought into or forced out of the cache due to a conflict miss are stored into the victim cache.

#### **Hashing Functions**

Another approach to reducing the cache miss ratio is the employment of different hashing functions. Bodin *et al.* proposed "skewed associativity" to improve the system's performance [6]. In an *X*-way associative cache, similarly to other traditional cache structures, the memory address is hashed with the number of lines to deduce which line to access. An *X*-way skewed associative cache, however, employs different mapping functions for each way. On a cache access, these functions are used in parallel causing the system to access a different line in each way. Thus, the possibility of aliasing is reduced.

González *et al.* evaluated XOR-based mapping functions and concluded that they constitute a powerful technique for reducing conflict misses [21]. Later, Kharbutli proposed "prime displacement" [31]. This hashing function obtains the cache index by adding an offset, equal to a prime number multiplied by the tag bits, to the index bits of the memory address.

#### **Cache Replacement Policy**

Other studies target the cache replacement policy. Peir *et al.* developed a design called "adaptive group-associative" cache [47]. This scheme extends a direct-mapped cache by using a history table to track the lines that have been referenced recently. When a miss occurs, the line being replaced is checked against the entries of the table. If it has been referenced recently, it is placed into another location in the cache that has not been accessed in the recent past instead of being evicted. A small directory is used to keep track of the lines that have been so displaced. Wong *et al.* suggested that implementing effective replacement algorithms might become more important than reducing conflict misses [66]. They modified the LRU policy for the L2 cache, so that lines which exhibit temporal locality are not replaced in preference to lines that have a low probability of being reused in the near future.

Kampe *et al.* proposed a "self-correcting" LRU replacement policy [30]. They identified three types of mistakes made by LRU. The first is created by blocks that are accessed only once, at the time of the miss. These blocks should have bypassed the cache. The second mistake is caused by blocks that exhibit some spatial locality or short term temporal locality. These are referenced more than once while being in the MRU position and are not accessed again before they are evicted. An ideal policy would remove them as soon as they leave the MRU position. The third mistake occurs when a block, which was evicted because it was in the LRU position, is accessed immediately after it was replaced. These blocks should be kept for a longer period. Detected mistakes are recorded into a "Mistake History Table", which is then used to refine the replacement decisions.

Kharbutli *et al.* suggested also that one of the main drawbacks of the LRU policy is that a line which is no longer needed occupies useful space for a long time until it becomes the LRU and is evicted from the cache [32]. This dead time is increased with larger degrees of associativity. To deal with this problem they proposed a counter-based cache replacement scheme, where each block is associated with a counter that records the number of accesses to that block. When the value of this counter reaches a threshold, the line becomes eligible for eviction.

Qureshi *et al.* detected a drawback of the set-associative cache in that it cannot adapt its associativity, as lines in the data array are statically mapped to entries in the tag array [48]. This means that when a miss occurs, a victim has to be identified within the target set, which prevents the cache from exploiting underutilised sets. To solve this problem, the tag array is expanded to hold more tags than the associativity dictates. Pointers are then used to map a valid tag entry to a location in the data array. When a miss occurs and an

invalid entry exists in the accessed line of the tag array, the replacement victim is supplied by the data array, which implements a global replacement policy. Thus, each line could contain a different number of valid tags, implementing a "demand-based" associativity that dynamically adapts to the access patterns of the running program.

#### Data Placement

A different set of schemes try to deal with the increasingly significant wire delays. Rises in on-chip communication delays affect the latency of large on-chip caches, making their hit time a function of a line's physical position within the cache. Therefore, Kim *et al.* suggested that traditional, monolithic cache designs with a single, uniform access time will be ineffective in future designs and proposed breaking the cache into banks that can be accessed at different latencies [34]. When a hit occurs to a cache line, it is swapped with a line in the bank that is the next closer to the cache controller. Thus, heavily used lines will migrate towards banks that are quickly accessed, while infrequently accessed lines will be demoted into farther banks with higher access time.

Chishti *et al.* exploited sequential tag-data access to decouple data from tag placement and define "Distance Associativity" [11], where a data block is placed at a certain distance from the core and thus suffers a certain latency. The data array is broken into different groups, each one with a different latency. The tag-data decoupling enables data blocks from the same cache set to be stored either in the same group or in a different one. Initially all cache blocks are placed in a fast group and then the rarely accessed blocks are demoted to slower groups. Thus, the majority of accesses happen to the fastest group, while the swaps between different groups are minimised, in contrast to the proposal by Kim *et al.* [34]. Thus this system results in higher performance and lower energy consumption.

#### **Cache partitioning**

Another set of studies target the sharing of the cache between different access streams. Stone *et al.* studied the optimal allocation of cache memory among multiple access streams [58]. They showed that LRU typically comes close to

achieving optimal performance and they focused on partitioning a cache between the instruction and data access streams of a single workload.

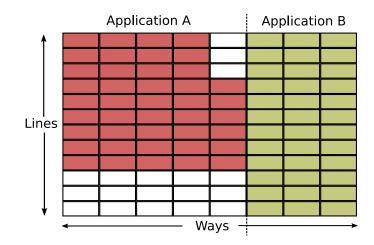

Chiou *et al.* were motivated by the presence of an increasing amount of streaming data and the development of multi-threaded parallel processing applications [10]. They recognised that these result in memory access pattern that exhibit less temporal locality and pollute the caches with data that will not be accessed again in the near future. They proposed a novel scheme, where a set-associative cache is partitioned at the granularity of a way and specific data is restricted to be only placed into a particular subset of the cache's ways. The difference from older static partitioning schemes is that the partitioning is dynamic, as the restrictions can be modified or even be completely removed changing the partitioned cache to a normal one.

Suh *et al.* developed an analytical cache model that depends on offline profiling of applications [59]. Using these offline miss rates the model can estimate the overall miss rate. This estimation is then used by a partitioning unit to determine an optimal partition of the caches that minimises the miss rates.

#### Summary

A 'simple' cache hierarchy is not always adequate and a number of more elaborate schemes for improving the performance of the system have been proposed. These range from selective caching depending on whether a memory reference exhibits temporal or spatial locality to modified versions of the LRU replacement policy and cache partitioning. All these proposals have been evaluated in uniprocessors but it is likely that the parameters are different in CMPs.

#### 2.1.2 Chip Multithreaded Systems

Most previous studies of caches have been related to uniprocessors. There is now a trend to increase the number of processors on a single chip and, in the CMP model, these often share the memory hierarchy. However this sharing imposes new constraints and affects the cache utilisation. Therefore, it is necessary to reevaluate cache design for CMPs. One of the major challenges is that the sharing of any level of the cache hierarchy allows interference, as data belonging to one thread may be evicted by operations by other threads. This interference impacts the running processes non-uniformly and could cause performance problems, like cache thrashing and thread starvation. Therefore different proposals have been made to improve the sharing of the cache and thus the overall performance of the system.

#### Thread scheduling

A group of proposals tries to tackle the cache contention problem by making appropriate scheduling decisions. Kihm *et al.* provided a set of counters for each thread, each of which is associated with a group of cache sets and records the accesses to these cache lines [33]. This monitoring was used to predict future access patterns for each thread, which were then exposed to the operating system scheduler. The scheduler then attempted to select threads that exploit different regions of the cache and thus can operate efficiently in parallel.

Chandra *et al.* studied the impact of the inter-thread cache contention on CMP architectures and proposed an analytical model to predict the impact of cache sharing on parallel running threads [8]. The input of the model is the isolated L2 cache access profile for each thread and the output is the number of extra L2 cache misses for each thread that shares the cache. Thus this model can be used by the scheduler to make the appropriate decisions.

A similar approach was employed by Fedorova [16]. An analytical model was proposed to estimate the L2 cache miss rate that a thread would have if the cache were shared equally among all the threads. The output was then used by the scheduler to adjusts the thread's share of CPU cycles in proportion to its deviation from its fair miss rate. Thus performance variability due to cache sharing was reduced.

#### **Non-Uniform Caches**

A different set of proposals tries to explore the range of sharing policies of large banked caches, mainly L2, between different on chip processors. More precisely, the L2 banks can be managed in two basic ways, as shown in Figure 2.1. They either form a 'single', large cache shared by all the processors or each

one is treated as a private L2 cache. The private scheme has low hit latency, providing good performance when the working set fits into the cache; however the effective cache capacity is reduced as each processor is allowed to use only its private L2 slice. Therefore, it is possible for a core to exhibit a high miss rate due to its working set not fitting into its slice while there is empty space in the other banks.

Figure 2.1: L2 Cache Designs

On the other hand, the shared scheme reduces the off-chip miss rates by increasing the effective cache capacity, as a core could potentially use all the available L2 cache space. However each bank could have a different access latency, depending on the interconnection network and the distance of the bank from the accessing core. The higher latency of a hit in a remote L2 slice combined with the increased bandwidth requirements and the coherence overhead can harm the performance of the system.

Huh *et al.* tried to bridge this gap by modifying the shared scheme [25]. Instead of mapping a data block statically to a specific L2 bank, they proposed dynamic mapping by allowing a block to be stored in one of multiple banks. Using proper placement and migration policies their scheme enables the cache to place frequently accessed blocks in the banks closest to requesting CPU. Zhang *et al.* created a hybrid of the private and the shared scheme [68]. In their system the L2 cache is shared, but when a line is evicted from the L1 cache, they attempt to keep a copy of the victim line in the local L2 slice. Thus, a subsequent miss can be serviced by the local L2 using this replica instead of bringing the original line from the remote L2 slice.

The same problem was tackled by Chishti *et al.* [12]. They expanded their previous work on distance associativity [11] to CMP architectures and proposed three different mechanisms. The first one, called "controlled replication", places copies of data lines close to the requesters while trying not to reduce the effective on-chip capacity too much. The second mechanism provides fast access to read-write shared data without making copies or incurring coherence misses. The third suggestion, called "capacity stealing", enables a core to migrate its less frequently accessed data to a cache slice with less capacity demand.

The above proposals start out with a banked shared cache and attempt to incorporate some of the advantages of using private L2 caches by using data migration and replication. Recently, Chang *et al.* proposed "Cooperative caching" [9], which employs private L2 caches and uses a collection of mechanisms to create a globally managed, aggregate on-chip cache via the cooperation of the different on-chip caches. These mechanisms include a replication-aware replacement policy and global replacement for inactive data.

#### **Cache Partitioning**

Suh *et al.* extended their previous work [59] by using a set of hardware counters to gather information about the running processes [60]. This information was then used to determine the cache partitioning. The novelty of this scheme is that the optimal partition of the cache is calculated dynamically to capture the time changing characteristics of each thread; then every thread is assigned a space allocation limit. In the event of a cache miss, an extra cache block will be allocated to the thread if and only if its current allocation is below this limit.

Kim et al. noted that an operating system enforces thread priorities assuming

that the progress of each thread is uniformly affected by the sharing of the resources [35]. When this assumption of fair hardware is not met, then problems like thread starvation or priority inversion arise. Therefore they introduced different metrics to evaluate cache fairness and proposed the substitution of the 'thread-blind' LRU replacement policy by static and dynamic partitioning algorithms that lead to a partition which optimises fairness.

Following a similar approach, Iyer proposed a framework for enabling Quality of Service (QoS) in CMP systems [27]. This scheme tries to improve the shared cache efficiency by providing prioritised service to different threads. The priority can be enforced by three different mechanisms: set partitioning, selective cache allocation and heterogeneous cache regions. The first mechanism allows threads with a higher priority to occupy more ways in a line than lower priority threads. The second one associates a cache space allocation limit with each priority level. The number of lines occupied by each thread is monitored and used to determine whether the allocation of a new line is allowed or not. The final mechanism maps heterogeneous cache structures, such as set-associative caches, stream buffers and victim caches, that implement different replacement policies to different memory access streams based on their priority levels.

Settle *et al.* proposed using global cache reuse behaviour to control the cache space available to each thread [54]. In one of their schemes, when the thread ID of the cache request differs from that of the normal LRU candidate, the cache controller checks the line's reuse counter to determine the impact this eviction could have on the system performance. If the reuse counter is higher than a threshold value, the line is not suitable for eviction. Instead the next least recently used line is evaluated and the process is repeated until a suitable candidate is found. If none is found, the normal LRU candidate is used.

Wang *et al.* developed a scheme called "thread-associative memory" [65], where thread-specific information is explicitly incorporated into the on-chip cache. More specifically, it employs a set-associative cache, where each way within a set is grouped into N "rails", where N is the number of concurrent threads sharing the cache. An example of a two-rail thread associative cache is shown in Figure 2.2. The cache address is extended to include the thread ID, which is

then used to determine which rail to access. By not allowing a thread to access a rail owned by another thread, cache replacements for concurrent threads are decoupled, thereby avoiding inter-thread conflicts. The system also uses an "enable" bit, so that if the performance degrades or only one thread is using the cache, the thread-associative mapping is disabled and the whole cache is used.

Figure 2.2: A two-rail thread associative cache [65]

Qureshi *et al.* developed a low hardware overhead monitoring circuit to estimate the utility of the cache resources for each running application [49]. Based on the observation that a reduction in misses correlates with a reduction in CPI, these estimations are used by an algorithm to divide the cache amongst the competing applications in an optimal way that will reduce the number of misses. A similar scheme was developed by Dybdahl *et al.* [15]. The two proposals differ on the amount of information gathered about each application and the way the partition sizes are modified each time the partitioning algorithm is executed.

#### Summary

The aforementioned studies have shown that a 'simple' cache hierarchy does not perform efficiently under the extra strain imposed by the sharing of on-chip resources amongst the concurrently running threads of a CMP architecture. A group of these advocate the partitioning of the cache to improve the overall performance of the system.

The work presented in this thesis was primarily influenced by these cache partitioning schemes and focused mainly on the last two proposed by Qureshi *et al.* [49] and Dybdahl *et al.* [15]. The two systems were evaluated and their advantages and drawbacks were identified and used as a guide for the development of a different cache partitioning scheme that aims to improve the system's performance at a low cost.

### 2.2 Bloom Filters

In the process of developing a new cache partitioning scheme different ways of monitoring the cache contents were examined. One of these is the Bloom filter [5], which is briefly introduced here.

#### 2.2.1 Description

A Bloom filter is a probabilistic algorithm to quickly test membership in a large set using multiple hash functions into an array of bits [5]. It consists of an array *A* of *m* bits and *k* hash functions  $\{h_1, h_2, ..., h_k\}$ . In an empty filter, all bits in *A* are zero. To add item *s* to the filter,  $h_1(s)$  is computed and the value is used to index into A, where  $A[h_1(s)]$  is set to one. This process is repeated for all the hash functions, as shown in Figure 2.3.

Figure 2.3: Example of a Bloom filter

To test for the presence of s', the bits  $A[h_1(s')]$ ,  $A[h_2(s')]$ , ...,  $A[h_k(s')]$  are looked up. If all these bits are one, the set membership test returns true, but if any are zero the test returns false. For these membership tests, false negatives are impossible. False positives, however, are possible, as any or all of the bits indexed by applying the hashing functions to s' could have been set due to the insertion of other elements into the filter. This problem is also known as "*aliasing*". The probability of such filter errors depends on the number n of items inserted into the set, the number k of hash functions, their effectiveness and the size m of array A. Assuming "good" hash functions, this possibility is given approximately by :

$$prob = \left(1 - e^{-kn/m}\right)^k \tag{2.1}$$

#### 2.2.2 Applications of Bloom filters

Bloom filters have been successfully applied to a variety of fields. They have been used for text analysis [4] and the development of spell checking programs [42, 45], in databases to estimate the size of joins [43, 44] and access the files that cache the modifications of the database's records [22, 50] and in network applications [17, 53, 64].

Recently, Bloom filters have also been introduced into the computer architecture domain. Peir *et al.* used them to implement a hit/miss predictor that identifies cache misses early in the pipeline [46]. This early identification of cache misses is used by the processor to schedule instructions that are dependent on loads more accurately and to prefetch data into the cache.

Ricci *et al.* applied them on a CMP system where the L2 cache was split into several banks, with each bank having a different access latency depending on its proximity to the core [51]. In their system, each processor maintains as many Bloom filters as the number of the L2 cache banks and each filter stores information about the contents of one of the banks. On a L1 cache miss, the processor checks the filters and for those that return a hit, their associated L2 cache bank is looked up. Therefore the number of banks that need to be searched for a line is reduced. Moore *et al.* described a "Thread-Level Transactional Memory" system, where Bloom filters are used to detect potential conflicts between different coherence transactions [41].

In summary, Bloom filters provide a cost effective way to store information. Therefore, they have been added to systems to track the contents of caches or to identify conflicts of coherence transactions. The work presented in this thesis exploited them in a similar way to monitor cache misses, as it is described in Chapter 6.

### 2.3 Summary

Cache design has been extensively studied for uniprocessor systems. However, nowadays, CMP architectures have emerged, where the available on-chip cache is shared between several threads. This sharing imposes new constraints and creates new challenges that need to be tackled in order to ensure that the performance of the system is improved.

This chapter presented a variety of previous proposals, like the use of nonuniform caches, efficient thread scheduling and cache partitioning. The work presented in the next chapters belongs to the last category. Several partitioning systems were evaluated and the results of the analysis were used to develop a novel scheme that aims to improve the overall system's performance at a low cost.

The next chapter outlines the Jamaica CMP architecture and the *jamsim* simulation platform that was used to evaluate the different cache partitioning schemes. Finally, the software environment used to run applications on the Jamaica architecture is described.

## **Chapter 3**

# Jamaica and Simulation Framework

The work presented in this thesis is intended to be as generic as possible and, therefore, applicable to different CMP systems. Nevertheless, it was based on the Jamaica architecture, which provided a test bench for the evaluation of the different cache partitioning schemes that were studied.

This chapter provides a short overview of the Jamaica architecture as well as a description of the simulator and the benchmarks that were used.

### 3.1 The Jamaica Architecture

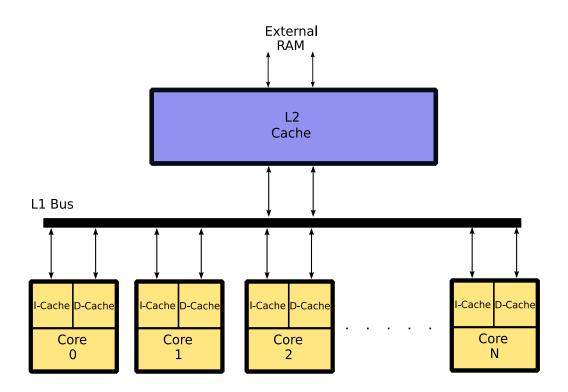

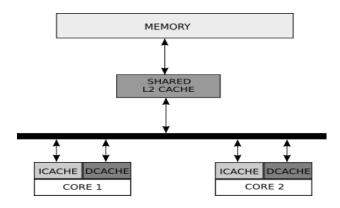

Jamaica (JAva Machine And Integrated Circuit Architecture) is a simulated CMP proposed by Wright [67]. As shown in Figure 3.1, the architecture originally consisted of N cores sharing a L2 cache. The system was later extended by Horsnell [24] to include multi-level cache hierarchies. However, this work will focus on the part of the system illustrated in Figure 3.1.

Each processor has its own private instruction and data L1 caches, which are connected through a shared bus to an on chip L2 cache. The L2 cache is unified and *inclusive*, i.e. it includes all the lines contained in the L1 caches. The requests that miss in the second level of the memory hierarchy are forwarded to the next level, which for this work is considered to be the main memory. To

Figure 3.1: The Jamaica architecture

limit the amount of traffic on the interconnect, the caches implement a writeback policy.

Additionally, a lazy allocation policy is implemented within the multi-level hierarchy. On a cache miss, a request is generated and propagated into the network without allocating a line to hold the response. This occurs at each successive level in the hierarchy and no line is allocated until a response transaction is received. When the response is received by the cache, the LRU policy is used to determine which block should be rejected to create the necessary space for the new entry.

The system maintains sequential consistency to allow for standard shared memory programming. To be coherent, the caches snoop the L1 bus and implement the PIMMS coherence protocol [24]. PIMMS is an extension of the MOESI protocol [61] with additional states to support multi-level cache hierarchies.

In general, Jamaica is an architecture similar to other proposed CMP systems. Niagara [36], developed by Sun, has 8 cores and each one has its own private L1 instruction and data caches while they all share an on-chip L2 cache through a crossbar. Power 5 [29], developed by IBM, has 2 cores. Each processor has private instruction and data caches and they share an on-chip L2 cache through a bus. Intel developed Core Duo CMP [40], where 2 cores share a L2 cache through a bus. Therefore, it is justified to assume that the novel cache partitioning scheme developed in this work and evaluated on the Jamaica architecture will be applicable to other CMP systems.

## 3.2 Simulation Environment

A Java simulation platform, called *jamsim* [23], has been developed to execute binaries created for the Jamaica ISA. Jamsim supports different models of simulation, namely functional and cycle-level simulations. The former are fast as they employ an abstract model of the architecture and can be used for system software development. The latter use components implemented in sufficient detail to account for pipeline stalls, interconnection bus and queue contention, cache access contention and memory channel queueing<sup>1</sup>. Therefore, cycle-level simulations are slow but essential for quantitative evaluation of the system.

Additionally, the simulator provides the option of using components at different levels of modelling. As this work was focused on the caches, this option was exploited. More specifically, functional models of the processors were used to generate memory access traces that were used to exercise the memory hierarchy, which was modelled in full detail.

Jamsim is a structural simulation platform, where each hardware component is mapped to a different simulator component implemented by a Java class. Exploiting object oriented programming techniques, the cache models were easily extended to include the different cache partitioning schemes that constitute the target of this work.

<sup>&</sup>lt;sup>1</sup>Jamsim does not simulate TLBs, as software execution is performed by a virtual machine, presented in Section 3.3, which is responsible for the handling of the address space between the running processes.

Finally, the simulation platform is parameterisable, as the user can select the number of cores, the size and associativity of the caches, the speed of the bus as well as which cache partitioning scheme to use.

# 3.3 Software Environment

The Jamaica instruction set is different from other common sets. Therefore, it is supported by a number of tools that enable the compilation and execution of applications. Software execution is performed by the Jamaica Virtual Machine (JaVM) [14], which is a port of the Jikes Research Virtual Machine (RVM) [2] to the Jamaica architecture. The JaVM compiles and optimises Java bytecode to native machine code allowing the execution of unmodified Java applications on top of the Jamaica architecture.

The Jikes RVM, and thus the JaVM, is an M : N thread model, scheduling execution of an arbitrarily large number (M) of Java threads over a finite number (N) of virtual processors. To serve the purposes of this work, the virtual machine was configured to create one virtual processor for each simulated core. Then, to ensure that each application of the simulated workload would execute on the same processor for the duration of the simulation, the virtual machine was modified to allow the user to force a Java thread to execute on a specific core.

Therefore, to evaluate the performance of the studied cache partitioning schemes, a set of Java applications was developed. Each one creates as many Java threads as the simulated processors, assigns a different benchmark to each thread and ships it to a specific core to be executed. The benchmarks used to create these workloads are presented in Section 3.4.

# **3.4 Benchmark Descriptions**

To evaluate the different cache partitioning schemes, a set of applications was selected from the "Java Grande Forum" benchmark suite [56] and the "NAS Parallel Benchmarks" [18]. This section provides an overview of each application.

### 3.4.1 Java Grande Benchmarks

The Java Grande Forum suite includes both sequential and multithreaded benchmarks. As the major scope of this work was to study how the cache is shared amongst different competing applications, the workloads were created by mixing different sequential applications. The sequential suite consists of three types of applications; low-level operations, kernels and large scale applications. From these benchmarks, six kernels were selected.

#### Crypt

The *crypt* benchmark performs IDEA (International Data Encryption Algorithm) encryption and decryption of an array of N bytes. It creates 3 byte arrays which hold the initial, the encrypted and the decrypted data.

#### HeapSort

The *HeapSort* benchmark sorts an array of N integers using a heap sort algorithm. It is a memory and integer intensive application. From this point it will be referred to as *heap*.

#### LUFact

The *LUFact* benchmark solves an  $N \times N$  linear system using LU factorisation followed by a triangular solve. This is a Java version of the well known Linpack benchmark. It is memory and floating point intensive, as the algorithm creates several sub-matrices and then calculates the LU decomposition inside each matrix. Hereafter, it will be referred to as *lu*.

#### Series

The series benchmark computes the first N Fourier coefficients of the function

$$f(x) = (x+1)^x$$

(3.1)

over the interval [0,2]. This benchmark heavily exercises transcendental and trigonometric functions. It creates a two dimensional array of doubles, which holds the computed Fourier coefficients.

#### SOR

The *sor* benchmark performs 100 iterations of successive over-relaxation on a  $N \times N$  grid. The benchmark contains three loops, the outer iteration loop and two inner loops over the row elements to process the relaxation.

#### Sparse

The *sparse* benchmark performs a sparse matrix multiplication. It uses an unstructured sparse matrix stored in compressed-row format with a prescribed sparsity structure. This kernel exercises indirect addressing and non-regular memory references. A  $N \times N$  sparse matrix is used for 200 iterations.

### 3.4.2 NAS Parallel Benchmarks

The NAS Parallel benchmarks were developed by NASA to help evaluate the performance of supercomputers and are recognised as a standard indicator of computer performance. They are derived from computational fluid dynamics (CFD) applications and they consist of five kernels and three pseudo-applications. Their implementations include both serial and parallel versions. From this suite three applications were selected.

#### CG

The *cg* benchmark estimates the largest eigenvalue of a symmetric positive definite sparse matrix by the inverse power method. The core of *cg* is a solution of a sparse system of linear equations by iterations of the conjugate gradient method. This kernel tests unstructured computations and communications.

#### FT

The ft benchmark contains the computational kernel of a 3-D Fast Fourier Transform (FFT). Each ft iteration performs three sets of one-dimensional FFTs, one set for each dimension. The benchmark creates 8 double arrays, which are used to hold the computed values.

#### MG

The *mg* benchmark uses a V-cycle Multi Grid method to compute the solution of the 3-D scalar Poisson equation. The algorithm works iteratively on a set of grids that are made between the coarsest and the finest grids. It tests both short and long data movement.

### 3.4.3 Benchmark Configuration

The benchmarks described in Section 3.4 were selected in an attempt to create a representative mix of applications with different cache space demands. As presented in Chapter 4, some benefit as the cache size increases, some have a small working set and others suffer a large number of compulsory misses.

The selected benchmarks are required to exercise the cache hierarchy of the system. At the same time, as the simulations are a lot slower compared to real system execution, it is essential that their execution time is limited. Therefore they were appropriately configured and the parameters that were used are presented in Table 3.1.

| Benchmark | Parameters                              |  |  |  |

|-----------|-----------------------------------------|--|--|--|

| crypt     | 500000 bytes                            |  |  |  |

| cg        | configuration 0                         |  |  |  |

| ft        | configuration 0                         |  |  |  |

| heap      | 2000000 integers                        |  |  |  |

| lu        | matrix = $500 \times 500$               |  |  |  |

| mg        | configuration 2                         |  |  |  |

| series    | 800 Fourier coefficients                |  |  |  |

| sor       | grid = $600 \times 600$                 |  |  |  |

| sparse    | matrix = 30000× 30000, iterations = 250 |  |  |  |

Table 3.1: Benchmarks' configuration

The benchmarks were executed without any garbage collection. However, this should not have any effects on the validity of the simulation results, as these benchmarks create a small amount of objects. For example, as it was described in Section 3.4.1, *heapsort* creates only one array of *N* integers and performs  $N \times logN$  comparisons between its elements.

## 3.5 Summary

This chapter outlined the Jamaica CMP architecture. Each processor has its own private L1 instruction and data caches, while they all are connected to an on-chip, unified L2 cache through a shared bus. The caches are kept coherent by snooping the bus and implementing an appropriate coherence protocol. This system provided the test bench for the evaluation of the various cache partitioning schemes that were the scope of this work.

Jamsim, the simulation platform, was extended to implement all these partitioning techniques and used to run several workloads. Finally, this chapter presented the different benchmarks that were mixed to create these workloads as well as their configuration.

# **Chapter 4**

# **Cache Replacement Policy**

In case of a miss, an entry of the accessed line needs to be rejected from the cache to create space for the new entry that has been requested by the running application. System designers typically employ the LRU policy to identify the replacement victim, as it is considered to be the best available replacement policy. The CMP domain has inherited this policy from uniprocessors, by default.

However, several people [60, 35, 27, 33, 49] have recently questioned the validity of that decision. More specifically, evidence has been presented that LRU could degrade the performance of a system by not allocating the cache resources optimally amongst the competing processes.

To study the efficiency and applicability of the LRU policy in CMP systems, several combinations of benchmarks were executed. This chapter presents the results of these simulations and identifies the drawbacks of LRU and their impact on the overall performance of the system.

## 4.1 Evaluation of LRU

### 4.1.1 Single Core Systems

First, the simulator was used to run the selected benchmarks on a single processor system to create a profile for each application. This profile provides information about the benchmark's working set size, shows the maximum performance each process can achieve and can be used to estimate roughly the

| Processor Core  | e Functional Model                                    |  |  |

|-----------------|-------------------------------------------------------|--|--|

| L1 Caches       | ICache and DCache : 32KB, 32B line-size               |  |  |

|                 | 4-way, LRU                                            |  |  |

| L1-L2 Bus Speed | 1/2 of processor speed                                |  |  |

| L2 Cache        | 4MB, 32B line-size, 32-way, LRU, 16 cycles hit latend |  |  |

| Memory          | 100 cycles access latency                             |  |  |

Table 4.1: System's configuration

relative performance of the system when the cache is shared by these applications.