# INVESTIGATING THE SCALABILITY OF TILED CHIP MULTIPROCESSORS USING MULTIPLE NETWORKS

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Engineering and Physical Sciences

2009

By Preethi Sam School of Computer Science

## Contents

| A        | Abstract 10    |                 |                                                                                                                                                                               |  | 10 |           |

|----------|----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----|-----------|

| D        | Declaration 11 |                 |                                                                                                                                                                               |  |    | 11        |

| С        | opyri          | $\mathbf{ight}$ |                                                                                                                                                                               |  |    | 12        |

| A        | ckno           | wledge          | ements                                                                                                                                                                        |  |    | 13        |

| 1        | Intr           | oducti          | tion                                                                                                                                                                          |  |    | <b>14</b> |

|          | 1.1            | Motiv           | $vation \ldots \ldots$                                                             |  |    | 14        |

|          | 1.2            | Why (           | CMPs?                                                                                                                                                                         |  |    | 18        |

|          | 1.3            | Design          | n Challenges in CMPs                                                                                                                                                          |  |    | 20        |

|          | 1.4            | Resear          | $\operatorname{urch} \operatorname{Aim} \ldots \ldots$ |  | •  | 20        |

|          | 1.5            | Contri          | $\operatorname{ributions}$                                                                                                                                                    |  |    | 21        |

|          | 1.6            | Thesis          | s Layout                                                                                                                                                                      |  | •  | 21        |

|          | 1.7            | Public          | cations $\ldots$                                                                             |  | •  | 22        |

| <b>2</b> | Bac            | kgrou           | nd                                                                                                                                                                            |  |    | <b>23</b> |

|          | 2.1            | On Cl           | hip Networks                                                                                                                                                                  |  |    | 23        |

|          |                | 2.1.1           | Network Topologies                                                                                                                                                            |  |    | 24        |

|          |                |                 | 2.1.1.1 Direct Networks                                                                                                                                                       |  |    | 25        |

|          |                |                 | 2.1.1.2 Indirect Networks                                                                                                                                                     |  |    | 26        |

|          |                |                 | 2.1.1.3 Shared Medium Interconnects                                                                                                                                           |  |    | 27        |

|          |                |                 | 2.1.1.4 Commonly Used OCNs                                                                                                                                                    |  |    | 27        |

|          |                | 2.1.2           | Routing Protocols                                                                                                                                                             |  |    | 28        |

|          |                |                 | 2.1.2.1 Deterministic Routing                                                                                                                                                 |  |    | 29        |

|          |                |                 | 2.1.2.2 Adaptive Routing $\ldots \ldots \ldots \ldots \ldots$                                                                                                                 |  |    | 30        |

|          |                |                 | 2.1.2.3 Topology Agnostic Routing                                                                                                                                             |  |    | 31        |

|       | 2.1.3 Flow Control                                        |

|-------|-----------------------------------------------------------|

|       | 2.1.4 Switching Technique                                 |

|       | 2.1.5 Deadlock Avoidance                                  |

| 2.2   | Cache Coherency Protocols                                 |

|       | 2.2.1 Snoop Based Cache Coherency Protocol                |

|       | 2.2.2 Directory Based Cache Coherency Protocols           |

|       | 2.2.2.1 Directory Design Alternatives                     |

| 2.3   | Alternative to Snoop and Directory Protocols              |

|       | 2.3.1 Token Coherence                                     |

|       | 2.3.2 Multicast Snooping                                  |

|       | 2.3.3 Bandwidth Adaptive Snooping                         |

| 2.4   | Tile Based CMPs                                           |

|       | 2.4.1 Tilera                                              |

|       | 2.4.2 TRIPS                                               |

|       | 2.4.3 OS Based Coherence                                  |

|       | 2.4.4 Priority Based Cache Coherent NoC                   |

|       | 2.4.5 DiCo: Efficient Cache Coherency for Tiled CMPs      |

|       | 2.4.6 Virtual Hierarchies                                 |

|       | 2.4.7 Network Based Coherence                             |

|       | 2.4.8 Proximity Aware Directory                           |

|       | 2.4.9 Alternative Home Node in Directory Based Tiled CMPs |

|       | 2.4.10 Tera Scale                                         |

| 2.5   | Summary                                                   |

| 3 Jar | maica                                                     |

| 3.1   | Processor Architecture                                    |

| 3.2   | Token Ring                                                |

| 3.3   | Locking Mechanism                                         |

| 3.4   | Interrupt Mechanism                                       |

| 3.5   | Bus Transactions                                          |

| 3.6   | Simulation Details                                        |

| 3.7   | Summary                                                   |

| 4 A ' | Tiled Bus CMP                                             |

| 4.1   | Motivation                                                |

| 4.2   | System Architecture                                       |

|          | 4.3  | Processor Tile                                                                                                                                    |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.4  | Router Architecture                                                                                                                               |

|          | 4.5  | L2 Tile                                                                                                                                           |

|          | 4.6  | Central Arbiter                                                                                                                                   |

|          | 4.7  | Cache Coherency Protocol                                                                                                                          |

|          | 4.8  | Lock Unit Description                                                                                                                             |

|          |      | 4.8.1 Synchronization Primitives                                                                                                                  |

|          |      | 4.8.2 Hardware Queue Based Locking in Tiled Bus CMP $\ldots$ . 85                                                                                 |

|          |      | 4.8.3 Modification to Jikes RVM                                                                                                                   |

|          |      | 4.8.4 Operation using the lock unit                                                                                                               |

|          |      | 4.8.5 Problem with stale LOCKGNT                                                                                                                  |

|          | 4.9  | Simulation Details                                                                                                                                |

|          | 4.10 | Summary                                                                                                                                           |

|          | 4.11 | Summary of Request and Response Messages                                                                                                          |

| <b>5</b> | A D  | ual Mesh CMP 97                                                                                                                                   |

|          | 5.1  | System Architecture                                                                                                                               |

|          | 5.2  | Deadlock Avoidance                                                                                                                                |

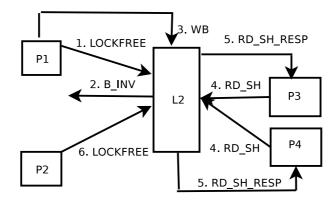

|          | 5.3  | Cache Coherency Protocol                                                                                                                          |

|          |      | 5.3.1 Read Miss                                                                                                                                   |

|          |      | 5.3.2 Write Miss $\ldots \ldots $ |

|          |      | 5.3.3 Writebacks and Evictions                                                                                                                    |

|          |      | 5.3.4 Stale UP Problem                                                                                                                            |

|          |      | 5.3.5 Sink Deadlock                                                                                                                               |

|          | 5.4  | Locking Protocol                                                                                                                                  |

|          | 5.5  | Simulation Details                                                                                                                                |

|          | 5.6  | Summary                                                                                                                                           |

|          | 5.7  | Summary of Request and Response Messages                                                                                                          |

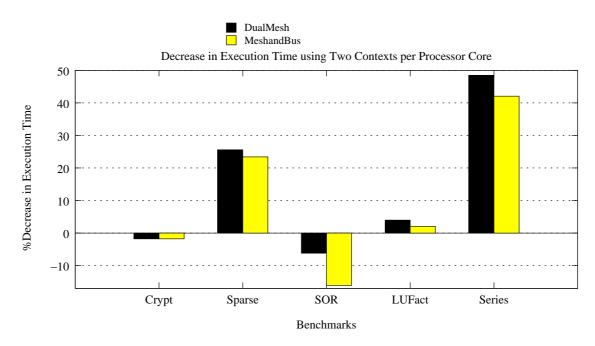

| 6        | Res  | ılts 117                                                                                                                                          |

|          | 6.1  | Benchmarks                                                                                                                                        |

|          | 6.2  | Simulator Configuration                                                                                                                           |

|          | 6.3  | Speedup                                                                                                                                           |

|          | 6.4  | Summary                                                                                                                                           |

|          |      |                                                                                                                                                   |

| <b>7</b> | Conclusion and Future Work |             | 135 |  |

|----------|----------------------------|-------------|-----|--|

|          | 7.1                        | Future Work | 136 |  |

| Bi       | bliog                      | graphy      | 139 |  |

## List of Tables

| 2.1 | Cache Line State Description             | 6 |

|-----|------------------------------------------|---|

| 4.1 | Cache Line State Description             | 7 |

| 4.2 | Type field: L1 and L2 Requests           | 8 |

| 4.3 | Type field: L1 and L2 Responses          | 8 |

| 4.4 | Control fields within the packet header  | 9 |

| 4.5 | L1 Request vs. L2 Response               | 5 |

| 4.6 | L2 Request vs. L1 Response               | 6 |

| 5.1 | L1 Request vs. L2 Response for Dual Mesh | 5 |

| 5.2 | L2 Request vs. L1 Response for Dual Mesh | 6 |

| 6.1 | Processor and L2 Combinations            | 0 |

| 6.2 | Multi Threaded Processor Configuration   | 0 |

# List of Figures

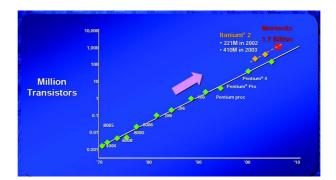

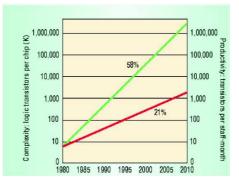

| 1.1  | Moore's Law [Bha05] $\ldots$                                                        | 15 |  |

|------|-------------------------------------------------------------------------------------|----|--|

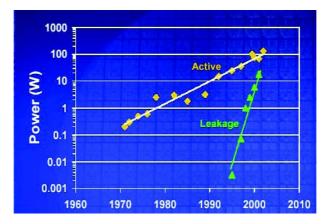

| 1.2  | Active and Leakage Power increases as process technology improves                   |    |  |

|      | over the years [Bha05] $\ldots$                                                     | 16 |  |

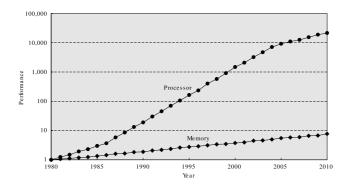

| 1.3  | Relative Performance of DRAMs w.r.t. Processor [HP03] $\ldots$ .                    | 16 |  |

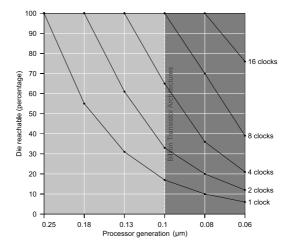

| 1.4  | Reachability of the signal with shrinking process technologies [Mat97]              | 17 |  |

| 1.5  | Productivity vs. Increasing transistor count [Bha05]                                | 19 |  |

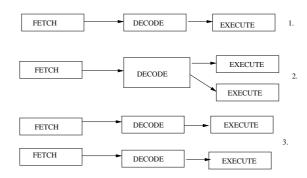

| 1.6  | Different types of parallelism: 1.Single-Issue 2.ILP 3.TLP [Wri01]                  | 19 |  |

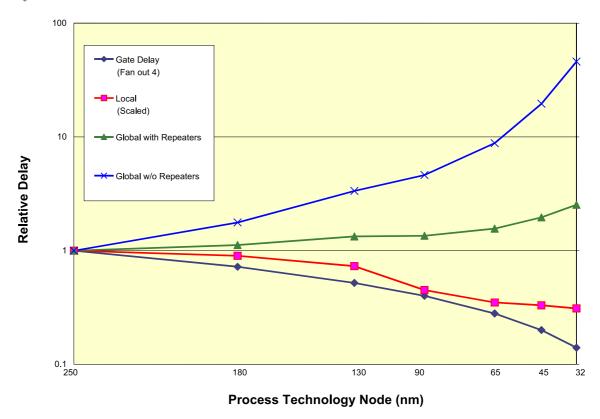

| 2.1  | Wire Delays Projections On Chip for different metal layers [itr05]                  | 24 |  |

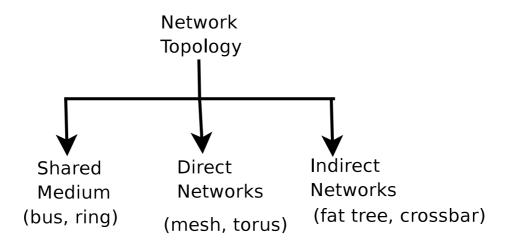

| 2.2  | Classification of Network Topologies [DYL03]                                        | 25 |  |

| 2.3  | Various Types of OCNs [ODH+07] [DYL03]                                              | 26 |  |

| 2.4  | Concentrated Mesh $[BD06]$                                                          | 28 |  |

| 2.5  | Mesh Network Using DOR                                                              | 29 |  |

| 2.6  | Dimension Order Routing Algorithm                                                   | 30 |  |

| 2.7  | Classic Example of Deadlock                                                         | 33 |  |

| 2.8  | The MOESI state diagram [Sun03]                                                     | 35 |  |

| 2.9  | Snoop based Symmetric Shared Memory Multiprocessor $\left[ \mathrm{HP07} \right]$ . | 39 |  |

| 2.10 | Simple Directory Based Scheme [CSG99]                                               | 40 |  |

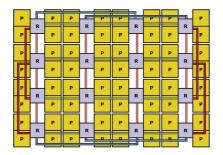

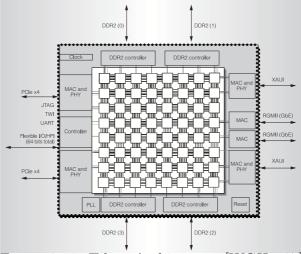

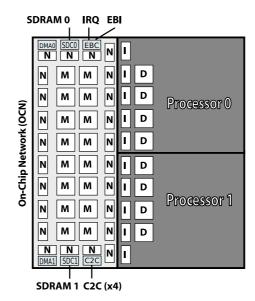

| 2.11 | Tilera Architecture [WGHea07]                                                       | 49 |  |

| 2.12 | TRIPS Tile Architecture [GCM <sup>+</sup> 06]                                       | 51 |  |

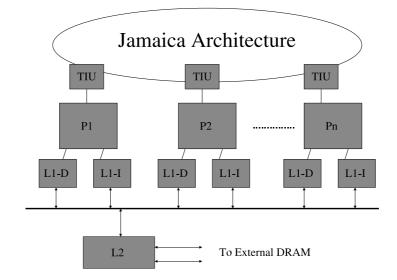

| 3.1  | Jamaica Architecture[Wri01]                                                         | 60 |  |

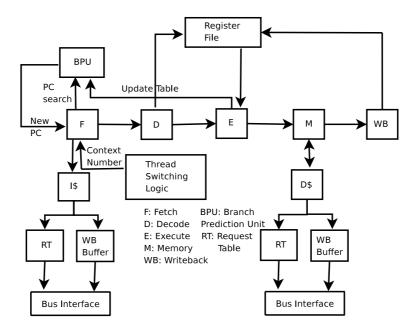

| 3.2  | Jamaica Processor Core[Hor07]                                                       | 61 |  |

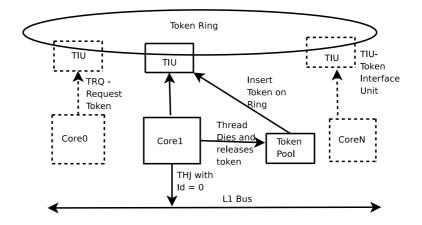

| 3.3  | Processor interface to the Token Ring Network<br>[Hor07]                            | 62 |  |

| 3.4  | Jamaica Bus Transaction[Wri01]                                                      | 66 |  |

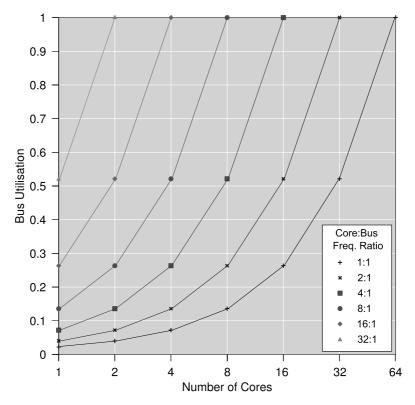

| 4.1  | Bus Clock Speed vs. Scalability of Processors [Hor07]                               | 69 |  |

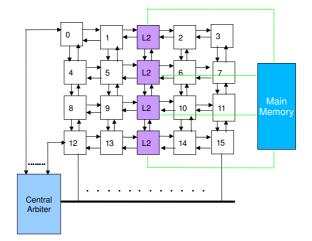

| 4.2  | Tiled-Bus Based CMP                                                                 | 70 |  |

| 4.3  | Structure of Processor Tile                                                         | 72 |  |

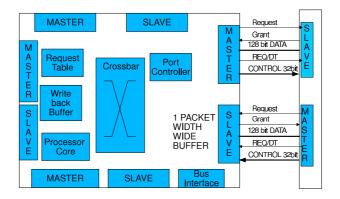

| 4.4  | Crossbar Logic within Processor Tile                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.5  | Message Format                                                                                                                                                        |

| 4.6  | L2 Tile Structure                                                                                                                                                     |

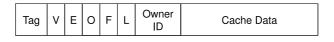

| 4.7  | L2 Cache Line Structure                                                                                                                                               |

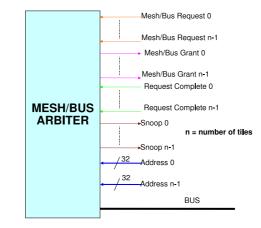

| 4.8  | Central Arbiter                                                                                                                                                       |

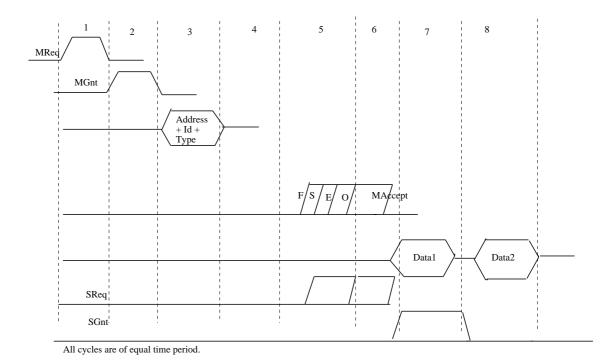

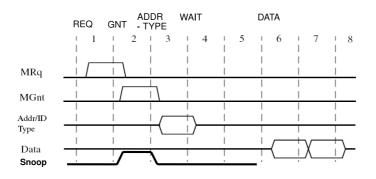

| 4.9  | Timing Diagram of the JAMAICA bus                                                                                                                                     |

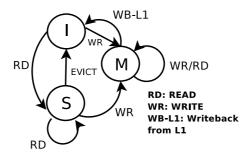

| 4.10 | L1 Cache State Transitions                                                                                                                                            |

| 4.11 | L2 Cache State Transitions                                                                                                                                            |

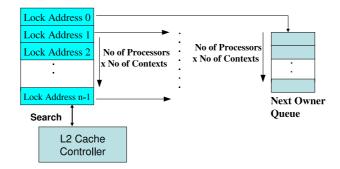

| 4.12 | Lock Unit                                                                                                                                                             |

| 4.13 | Original and Modified Locking Code in JaVM                                                                                                                            |

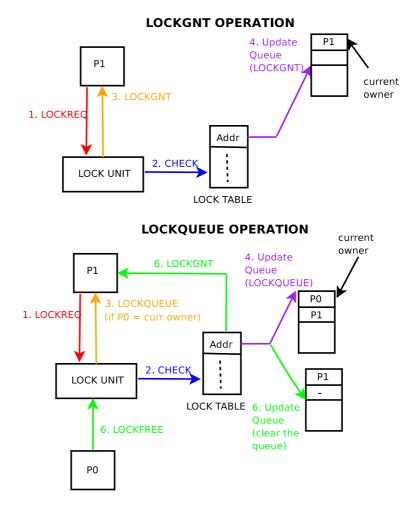

| 4.14 | Queuing Lock Protocol                                                                                                                                                 |

| 4.15 | Stale STL_C case                                                                                                                                                      |

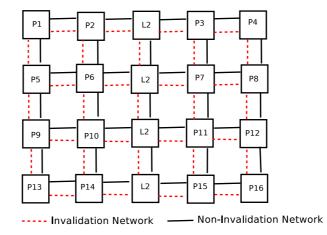

| 5.1  | Dual Mesh CMP                                                                                                                                                         |

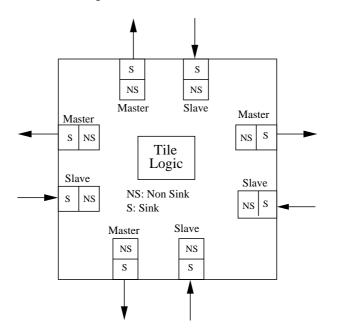

| 5.2  | Tile with Sink channels    99                                                                                                                                         |

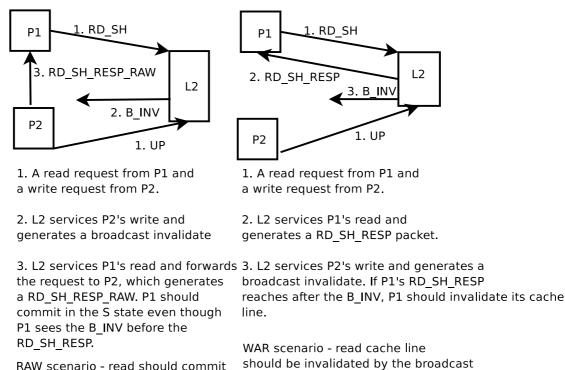

| 5.3  | RAW and WAR operation                                                                                                                                                 |

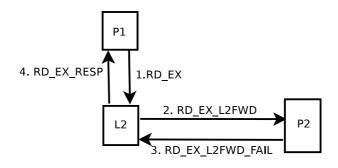

| 5.4  | RD_EX to $S(SO)$ line evicted from L1                                                                                                                                 |

| 5.5  | RD_EX to M or S(SO) line in L2 $\ldots \ldots \ldots$ |

| 5.6  | Stale UP                                                                                                                                                              |

| 5.7  | Deadlock Avoidance within the sink channels                                                                                                                           |

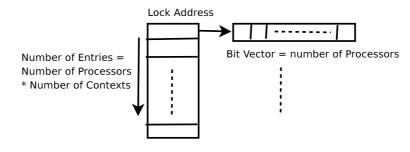

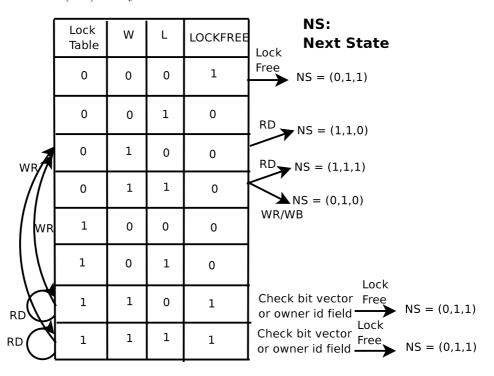

| 5.8  | Lock Unit at L2                                                                                                                                                       |

| 5.9  | A state table describing the combinations for LOCKFREE to succeed 112                                                                                                 |

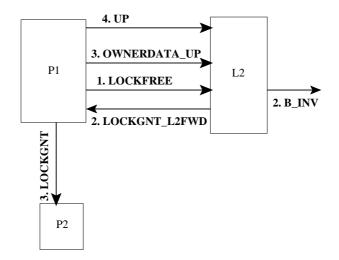

| 5.10 | Stale LockFree Detection at L2                                                                                                                                        |

| 6.1  | Performance Improvement using Dual Context Processor Cores vs.                                                                                                        |

|      | Single Context                                                                                                                                                        |

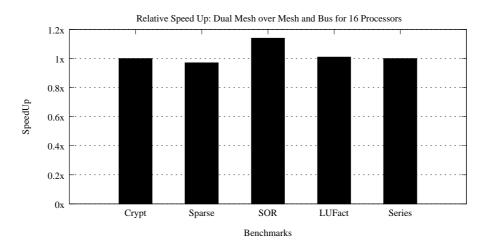

| 6.2  | Relative Speedup Obtained by Using Dual Mesh over Mesh and                                                                                                            |

|      | Bus for 16 Processors                                                                                                                                                 |

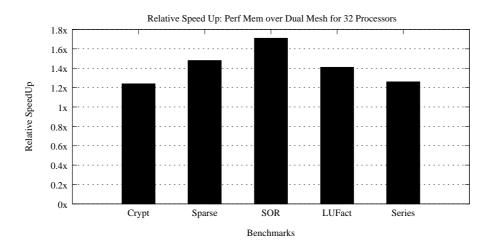

| 6.3  | Relative Speedup Obtained by Using Perfect Memory over Dual                                                                                                           |

|      | Mesh for 32 Processors                                                                                                                                                |

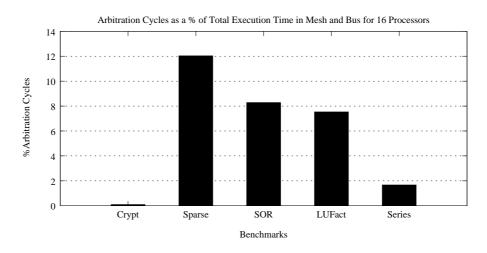

| 6.4  | Arbitration Cycles as $\%$ of the Total Execution Time: Mesh and                                                                                                      |

|      | Bus                                                                                                                                                                   |

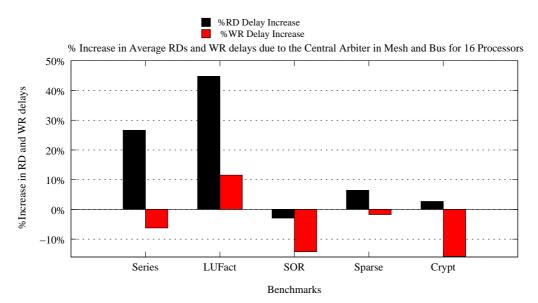

| 6.5  | %<br>Increase in Average Read and Write Delays in Mesh and Bus                                                                                                        |

|      | over Dual Mesh                                                                                                                                                        |

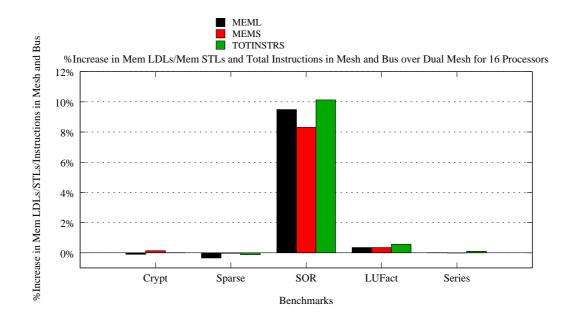

| 6.6  | Increase in instruction count in Mesh and Bus over Dual Mesh 124                                                                                                      |

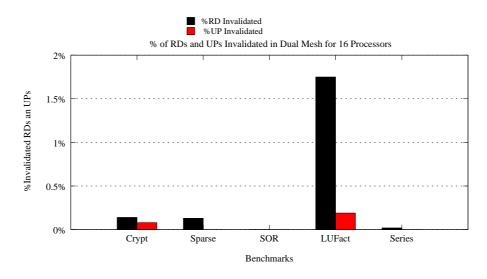

| 6.7  | $\%$ of Invalidated RD and UPs in Dual Mesh $\ldots \ldots \ldots \ldots \ldots \ldots 125$                                                                           |

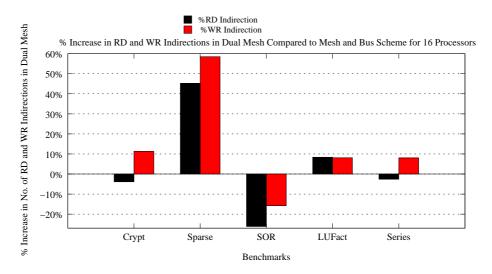

| 6.8  | Increase in Read and Write Indirections in Dual Mesh over Mesh                                                            |     |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

|      | and Bus                                                                                                                   | 125 |

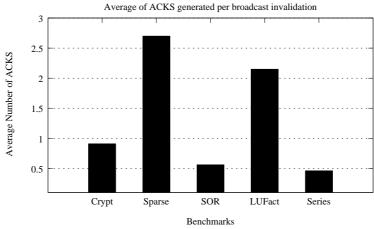

| 6.9  | Average Number of ACKS that are generated per Broadcast In-                                                               |     |

|      | validation on a 16 Processor Dual Mesh Configuration                                                                      | 125 |

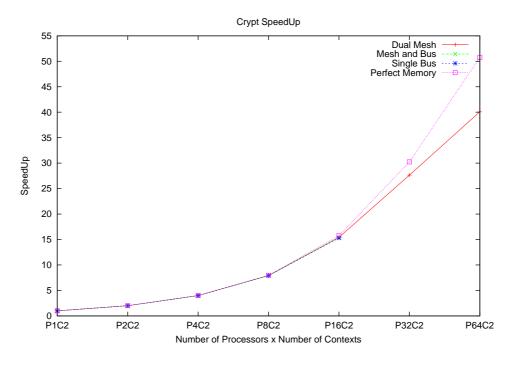

| 6.10 | Speedup Crypt                                                                                                             | 126 |

| 6.11 | Read and Write Latencies with Varying Processor and DataSet                                                               |     |

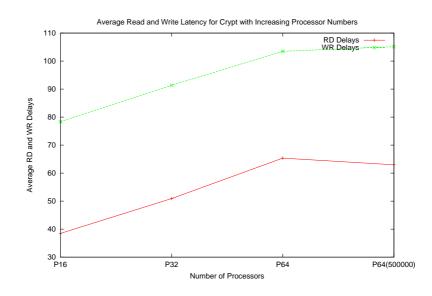

|      | Configurations for Crypt: Dual Mesh                                                                                       | 127 |

| 6.12 | Maximum Delay on the Mesh Network with Varying Number of                                                                  |     |

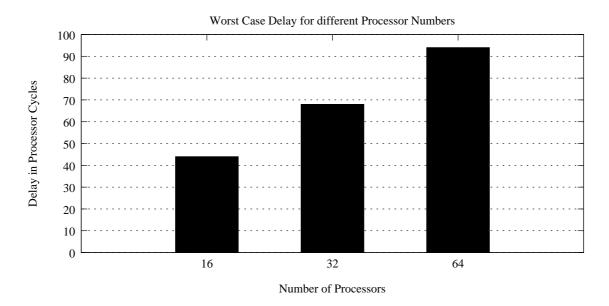

|      | Processor Nodes without Contention                                                                                        | 128 |

| 6.13 | Computation to Communication Ratio For Crypt Varying Number                                                               |     |

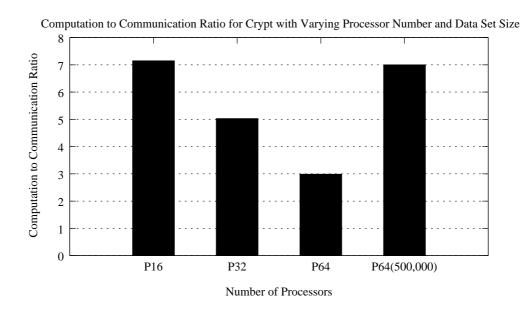

|      | of Processor Nodes and DataSet Size                                                                                       | 128 |

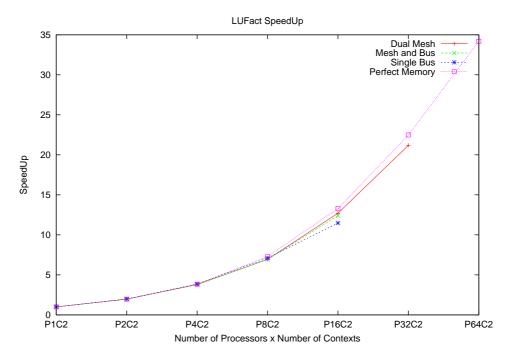

| 6.14 | Speedup LUFact                                                                                                            | 129 |

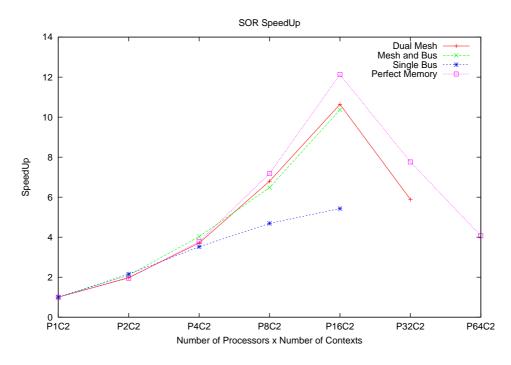

| 6.15 | Speedup SOR                                                                                                               | 130 |

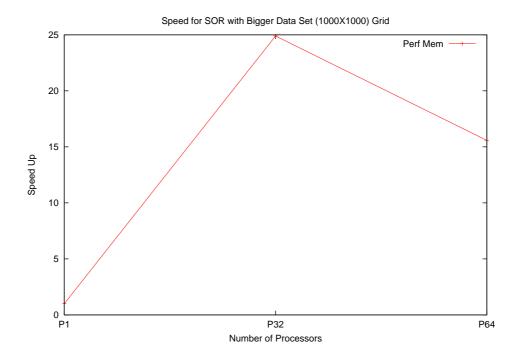

| 6.16 | Speedup SOR for 1000X1000 with Perfect Memory $\ldots \ldots \ldots$                                                      | 131 |

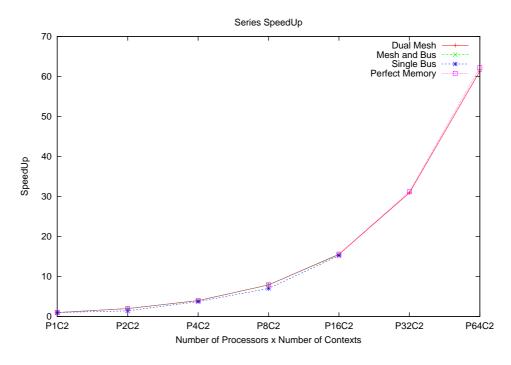

| 6.17 | Speedup Series                                                                                                            | 131 |

| 6.18 | % of Indirections, MM acccess and Hits within the L2 for 16 pro-                                                          |     |

|      | cessors: Dual Mesh and Mesh and Bus $\ \ldots \ $ | 132 |

| 6.19 | Speedup Sparse                                                                                                            | 133 |

| 6.20 | Relative Speedup: Using Single Bus over Dual Mesh for 16 Processors                                                       | 134 |

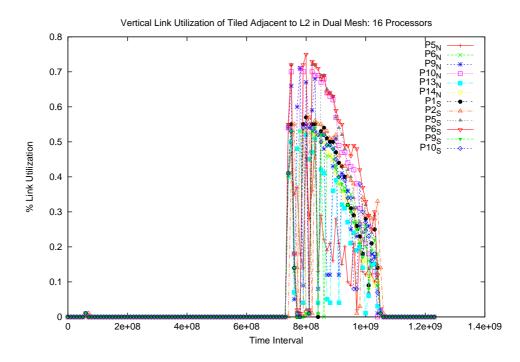

| 7.1  | Link Activity on Vertical Links on L2 Tiles on a Dual Mesh $\ .\ .$ .                                                     | 137 |

| 7.2  | Link Activity on Vertical Links on Tiles Adjacent to L2 on a Dual                                                         |     |

|      | Mesh                                                                                                                      | 138 |

## Abstract

The era of billion and more transistors on a single silicon chip has already begun and this has changed the direction of future computing towards building chip multiprocessors (CMP) systems. Nevertheless the challenges of maintaining cache coherency as well as providing scalability on CMPs is still in its initial stages of development. This thesis therefore investigates the scalability of cache coherent CMP systems.

Previous studies have shown that single bus based cache coherent CMPs do not scale. Directory based CMPs systems provide better scalability, but have overhead in terms of the space for a full map directory as well as latency in providing for broadcasting of writes to widely shared data.

In this thesis the idea of using two separate (multiple) networks is explored for providing a combination of snoop and directory based protocols on a CMP. The cache coherency traffic is split over two separate interconnects. A limited directory based scheme with low space overhead is used over one network for handling all requests and non-broadcast based cache coherency responses. The second network is specifically used for supporting broadcast based invalidations to widely shared data. The cache coherency protocol is optimized by removing the need to generate acknowledgement messages during writes to widely shared data, as required by directory protocols. A combination of homogeneous and heterogeneous networks is implemented giving rise to two architecturally different CMP systems. The performance of both these CMP architectures is evaluated using multithreaded benchmarks. Results do confirm that the homogeneous networks based scheme is a promising design for small and medium sized CMP systems.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the "Copyright") and s/he has given The University of Manchester the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

- ii. Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the John Rylands University Library of Manchester. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

- iii. The ownership of any patents, designs, trade marks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and exploitation of this thesis, the Copyright and any Intellectual Property Rights and/or Reproductions described in it may take place is available from the Head of School of School of Computer Science (or the Vice-President).

## Acknowledgements

I would like to thank Dr. Ian Watson for giving me an opportunity to pursue a PhD and for all the help and support during the study. I would also like to thank members of the APT group. Special thanks to members of the JAMAICA group for all the motivation and help, especially Matt for all the guidance and inputs with regards to designing the cache coherency protocol and debugging the simulator.

Many Thanks to all my friends in Manchester (as well as in India and US) for making my stay enjoyable inspite of the numerous pressures associated with the PhD. Special thanks to Uncle Partha and Aunt Winifred for being like a family to me in Manchester, Hande for being such a great roomate and Varsha for being a true and lasting friend.

Last but not the least, I thank GOD for giving me loving parents and family members. Without their prayers and constant encouragement this PhD would not be possible.

## Chapter 1

## Introduction

### 1.1 Motivation

In the past, parallel machines were relegated to research based and high performance scientific applications. These applications are used to model physical phenomena that are costly, and in some instances impossible to observe without their occurance [CSG99]. Examples include, simulation of weather forecast, interaction between astronomical bodies (N-body simulations), crash analysis in automobiles and studying molecular dynamics as required by chemical and pharmaceutical industries [CSG99]. In contrast, uniprocessor (single processor chip) systems dominated the desktop computing market. With the explosion of the internet, databases and server computing based applications started to encroach the realm of parallel applications. While on the desktop side, gaming, multimedia and mobile computing started fuelling the need for higher performance.

Since its inception around 1970's, and upto the mid 80's [HP07], performance enhancement in uniprocessors was sustained by technological improvements in process generation, resulting in doubling of transistors on a single chip as predicted by Moore's Law (Figure 1.1 [Bha05]) and increase in processor clock frequency. From mid 80's until about 2002, increased on-chip transistor budgets gave rise to several microarchitecture enhancements such as wider pipelines, out of order processing for increased throughput in terms of more number of instructions per cycle, better branch prediction mechanisms and larger on-chip cache memory [HP07]. However, after 2002, the returns from these architectural enhancements and increase in clock frequency started to diminish mainly due to the following factors:

Figure 1.1: Moore's Law [Bha05]

• Power Consumption

Power consumption within a processor can be classified as static and dynamic power. Static power is equivalent to the power consumed by a circuit when it is in its quiescent state, primarily due to leakage currents (current that flows through transistors when they are in the off state). While dynamic power is the power consumed when transistors switch within a circuit [BKJN99]. The formula for static [HP07] and dynamic power [Bha05] is given by equation 1.1 and equation 1.2 [KM08] respectively:

$$P = I_{static} * V \tag{1.1}$$

$$P = C * V^2 * f \tag{1.2}$$

Where  $P = power consumed I_{static} = leakage current C = load capac$ itance V = voltage of operation f = frequency of operation

Frequency  $\propto$  Voltage. Therefore, P  $\propto$  frequency<sup>3</sup>. It is estimated that almost 40% of the chip's power consumption is due to superscalar uniprocessor core on-chip [Bha05]. Reducing the power consumed using techniques such as voltage scaling or local clock gating [EB00] leads to lower performance in uniprocessor (superscalar processors) systems [Bha05] and does not account for power consumed when wires are driven through idling processor cores [KFJ+03]. Therefore, there is a non-linear increase in power as frequency increases. Figure 1.2 shows how power due to leakage current is catching up with active power.

Figure 1.2: Active and Leakage Power increases as process technology improves over the years [Bha05]

• Memory Wall

In the past twenty years, DRAM<sup>1</sup> sizes have increased by about 40% per year [HP07] and their access latencies have decreased by 76%. However, these enhancements in off-chip memory latencies is unparalleled to the increase in processor clock frequencies (120 times) as compared to 15 times for the clock frequency for the DRAM. Figure 1.3 shows the relative improvement in performance for DRAMs and processors. Therefore, in order to avoid the long wait times to access memory, processor cores normally contain a hierarchy of caches. Apart from using caches, multithreaded and speculative processor cores, and software [GGV90] and hardware prefetching [BC91] is used to reduce the effect of the penalty associated with memory access.

Figure 1.3: Relative Performance of DRAMs w.r.t. Processor [HP03]

<sup>&</sup>lt;sup>1</sup>Dynamic Random Access Memory

• Wire Delay

With shrinking feature sizes (minimum size of a transistor or wire in the X or Y dimension on chip) [HP07], wires become thinner and transistor size and CMOS switching times decrease. The resistance of a wire of length 1 is calculated using the formula as given below [BKJN99][Ye03]:

$$R = \frac{\rho \times l}{A} \tag{1.3}$$

where  $\rho$  is a constant; l = length of the wire and A = cross-section area of the wire. As the wires becomer thinner, A decreases and hence R increases. The delay for propagating a signal through a wire is given by the equation [HP07]:

$$\tau = \mathbf{R} \times \mathbf{C} \tag{1.4}$$

We see that the delay is proportional to R and C. In order to reduce R and thereby the delay, according to equation 1.3, l needs to decrease. Therefore, the wire gets shorter in length. If the wire length decreases, the distance travelled by the signal on the wire also decreases, which means that in a single clock cycle only a certain number of gates are traversed. Figure 1.4 shows the percentage of a processor die that is reached with reducing feature sizes.

Figure 1.4: Reachability of the signal with shrinking process technologies [Mat97]

• Saturating Instruction-Level Parallelism (ILP)

The main objective of any newly developed processor system is to enhance system performance. On uniprocessors executing sequential applications, this aim is achieved by issuing independent instructions simultaneously within the processor pipeline and provide for multiple execution units to process these instructions. Such processors are known as out-of-order (OOO) processors. If the *Decode* stage within the processor pipeline, resolves instruction dependencies then it is known as a superscalar processor. If the compiler identifies a window of instructions that could be executed in parallel then such processors are known as Very Large Instruction Word (VLIW). OOO processors became popular around the mid 90's with Intel's P6 microarchitecture [Int98]. However the number of comparisons to be made in order to determine independent instructions increases as the square of the window size [HP07], assuming all instructions were register based. In reality, the storage space required for a window, branch prediction mechanism, limited number of functional units(integer and floating point *Execute* units) and registers cause the actual number of instructions that are issued in parallel to be less than the window size [HP07]. One of the most powerful OOO processor is the Dual Core IBM Power 5 that has an issue width of 8 instructions from a single thread  $[SKT^+05]$ . However, studies in the past have shown that the average parallelism in terms of number of instructions that can be executed simultaneously is 7 [Wal90].

In addition to the above mentioned issues, design productivity is of great concern to the  $IC^2$  industry. Figure 1.5 shows the gap between productivity and complexity as number of transistors increase.

## 1.2 Why CMPs?

The main goal of a CMP system is to use multiple simple scalar or moderately complex superscalar cores that work in tandem to improve or better the throughput of a complex superscalar uniprocessor core. It addresses the power consumption problem, by using relatively lower frequency based processor cores in

<sup>&</sup>lt;sup>2</sup>Integrated Circuit

Figure 1.5: Productivity vs. Increasing transistor count [Bha05]

Figure 1.6: Different types of parallelism: 1.Single-Issue 2.ILP 3.TLP [Wri01]

constrast to a single high speed uniprocessor core. It alleviates the chip area reachability problem by partioning its architecture, thereby using smaller length wires to interconnect logic within and between cores and curtailing the wire delay. Given that the cores on a CMP are simple, they do not occupy large area on chip giving more room for incorporating a larger portion of the memory hierarchy on chip. Most CMPs offer L2 and L3 caches on chip thereby hiding memory latency as the bandwidth offered on chip is higher than off-chip. The saturating limits within ILP and the design complexity associated in hardware has led application and system developers to develop different means of extracting parallelism. One such instance of parallelism is Thread Level Parallelism (TLP), as shown in Figure 1.6. CMP systems can use TLP to their benefit simply because there are several processors that are potentially available to execute these threads in parallel.

## 1.3 Design Challenges in CMPs

The transition from uniprocessor to CMP systems has already been made for both high end server as well as desktop machines, as seen in Sun's Niagara, and Intel and AMD's quad and dual core systems. However, there are some key design challenges for CMPs, mainly, the cache coherency issue and architecture scalability. A major difference between uniprocessor and multiprocessor systems is that uniprocessors do not need to address the issue of cache coherency. However, CMP systems are in essence, architecturally, a smaller version of cache coherent multiprocessor systems. Since CMPs are targeted towards applications that will most likely use the shared memory programming paradigm (a detailed explanation of cache coherency in shared memory systems is given in Chapter 2, Section 2.2), there is a need for a cache coherency protocol to be implemented over such systems. Apart from handling cache coherency, CMP systems should be scalable (in terms of number of processor cores on a single chip) in order to achieve faster execution speeds for parallel applications. It is a known fact that bus based CMP systems do not scale [Wri01][Hor07]. Therefore, alternative switch based interconnect topologies (again, a detailed explanation of on-chip switched networks is given in Chapter 2, Section 2.1), are becoming popular with many CMP systems. One of the most popular switched interconnect is the mesh topology that is being used to integrate multiple processor cores (tiles) on a single chip [DT01][WGHea07]. However, the bigger challenge is to maintain cache coherency on such unordered networks and at the same time achieve application scalability.

### 1.4 Research Aim

The previous sections have listed some of the core problems with increasing chip densities that are addressed by CMP systems. They also highlight the design challenges, namely, the scalability of cache coherent CMPs. Therefore, this thesis explores the scalability of cache coherent tile (interconnection of processor and memory tiles) based CMP systems (tiled CMPs) using multiple networks. It uses an extended version of a formerly developed cycle accurate simulator [Hor07] to model multiple networks and a combination of snoop and directory based cache coherency.

### **1.5** Contributions

The contributions of the thesis are as follows:

- It uses a novel combination of homogeneous and heterogenous networks to evaluate the scalability of a cache coherent tiled CMP system.

- It adapts the bus based snoop protocol and the limited directory based protocol to perform on multiple networks.

- It optimizes the limited directory based cache coherency protocol for write invalidates to widely shared data by eliminating the need for acknowledgement messages.

### 1.6 Thesis Layout

The structure of the thesis is as follows:

Chapter 2 provides an overview of the basic components of tiled CMPs, namely on-chip interconnection networks and cache coherency protocol. It also includes a review of related work for Tiled CMPs in the literature.

Chapter 3 presents the JAMAICA bus based CMP. It provides details of the processor architecture, the bus interface, the token ring network and the MOESI cache coherency protocol used. It also gives details of the simulator modelling the architecture.

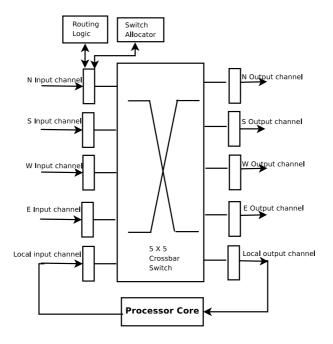

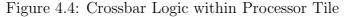

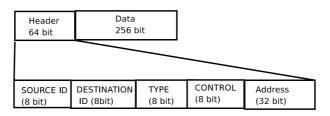

Chapter 4 provides a detailed description of the heterogenenous tiled architecture - mesh and bus. It includes details of the architecture of the tile and the mesh network. It explains the cache coherency protocol, the design of the dedicated hardware based queuing lock unit and the changes made to the JAMAICA simulator in order to implement this design.

Chapter 5 provides a detailed description of the homogenous tiled architecture - dual mesh. The main architectural differences between the dual mesh and mesh and bus schemes are discussed. The modifications made to the cache coherency protocol, network deadlock problems encountered during simulations and the solutions provided for it, are presented.

Chapter 6 evaluate the performance of the mesh and bus and dual mesh architectures using multithreaded benchmarks. It compares the relative performance of the dual mesh over the mesh and bus and single bus based architectures. Chapter 7 concludes the thesis based on the performance analysis of the two architectures and suggests future enhancements to the dual mesh scheme in order to improve its performance.

## 1.7 Publications

- HiPEAC Workshop on Interconnection Network Architectures: On-Chip, Multi-Chip January 2007, Ghent, Belgium: Presented an abstract on the design of a Tiled-Bus based CMP.

- ACACES 2006 2nd International Summer School, Italy, July 2006 Presented a poster A Lock Unit for the JAMAICA CMP

- Accepted paper in the Second Workshop on Programmability Issues for Multi-Core Computers (MULTIPROG'09): A Dual Mesh Tiled CMP

## Chapter 2

## Background

This chapter provides an insight into network based cache coherent chip multiprocessor (CMP) systems. It explains the basic components for on-chip networks (OCNs) - topology, routing, flow control, switching; followed by a general discussion on cache coherency protocols as well as alternatives to it. It reviews the design of some Tiled CMPs cited in both industry and academia.

### 2.1 On Chip Networks

With the onset of embedded systems, wherein multiple intellectual property (IP) blocks on chip have to be connected in a manner which reduces the latency and power consumption - factors that are critical for the performance of the realtime system, the design of OCNs has generated great interest within the research community as well as industry. Motivation for networks on chip for homogeneous CMP systems stems from the fact that, as process technology shrinks, latency and power become important deciding factors in the performance of systems. With shrinking feature sizes and the associated wire delay problem (shorter wire lengths for signal reachability - (Chapter 1), long interconnects, such as buses and others that rely on global wiring, will be required to clock at a much smaller frequency compared to the processor, in order to maintain signal reachability throughout the chip and ensure the in order property of the network. This means that signal propagation delays on global wires grows logarithmically as opposed to that on local wires [itr05], as shown in Figure 2.1. Also, network topologies that rely on global wiring will dissipate more power than their local counterparts, because of repeaters added to the long wires to maintain signal integrity

#### CHAPTER 2. BACKGROUND

[DT01]. OCNs on the other hand have several advantages over global interconnects. Firstly, depending on the topology, they require smaller length wires to interconnect components on chip, thereby reducing the power dissipation. They allow for structuring wiring resources, which simplifies layout on chip, increasing and sharing the bandwidth among components and hence enhancing scalability [DT01]. They can use local clocks, thereby reducing the area, power and clock skew problems associated with global clock trees [OS02]. Given these advantages, OCNs have been favoured over traditional bus based interconnects in many CMP systems.

Figure 2.1: Wire Delays Projections On Chip for different metal layers [itr05]

### 2.1.1 Network Topologies

Network topologies define the various paths that exist between a communicating source and its destination. Multiprocessor and multicomputer systems use a variety of network topologies, such as hierarchical buses, trees, ring, meshes, hypercubes, crossbar [DYL03] [Sta97] [CSG99]. A broad classification of various types of networks is shown in Figure 2.2. All these topologies can be used both

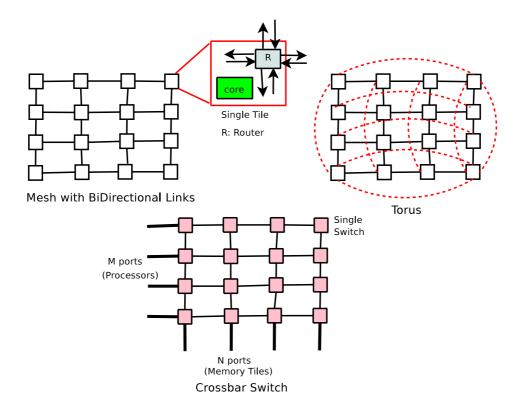

on and off-chip. Off-chip networks are constrained by the pin bandwidth. In this discussion we concentrate on OCNs. OCNs normally divide a message into packets and transmit them as information carriers between communicating nodes. This mode of transportation is known as packet switching, wherein a packet enters a network and traverses through it without knowing the path that it is going to take to reach its destination. Another mode of transportation is circuit switching, that which is used by traditional land line phone networks. In circuit switching a route from source to destination is reserved in advance before sending the packet. Although, this scheme guarantees packet delivery within a certain period of time, it cannot compete with packet switching in terms of adaptability, in an ever changing network traffic scenario. Also, the idea of reserving a network resource (buffers or channel/links) way ahead in time can lead to inefficient utilization of that resource. Some of the commonly used OCN topologies are shown in Figure 2.3.

Figure 2.2: Classification of Network Topologies [DYL03]

#### 2.1.1.1 Direct Networks

Direct networks, as their name implies, connect to neighbouring devices directly, while remote devices are accessed using several hops. Each node within a direct network uses a router to interconnect with other neighbouring nodes. The routers per node perform switching and arbitration. They are also known as orthogonal networks, i.e. there is at least one link in each dimension of the network, for every node [DYL03]. This also makes the routing protocol easier to implement.

Figure 2.3: Various Types of OCNs [ODH<sup>+</sup>07] [DYL03]

Direct networks are the preferred topology given the on-chip area constraints and wiring availability [DT01][GK08]. Examples include meshes, tori, hypercubes, etc. Equation 2.1 shows the average latency that a packet encounters when travelling through a direct network from source s to destination d [BD06][KBD07]:

$$L(s,d) = T_h + T_s + T_w \tag{2.1}$$

where,  $T_h = Ht_r$ , is the header delay given by H (the hop count) and  $t_r$  the router traversal delay;  $T_s = L/W$  is the serialization delay, with L = the packet length and W = the channel width (the number of wires that connects two adjacent communicating nodes;  $T_w$  is the time taken to send the packet over the wires.

#### 2.1.1.2 Indirect Networks

Indirect networks use multiple switches connected in a manner so as to form a centralized switch for interconnecting multiple communicating nodes [DYL03].

The centralized switch is responsible for packet routing and arbitration. Examples include crossbars and multistage interconnection networks (MIN) (such as butterfly, omega, clos, fat tree). The number of switches required for crossbars is  $N^2$ , and that for MINs is  $(N/k)(log_k N)$ , where N is the number of communicating input and output ports and k is the number of input/output ports per switch (switch degree). In order to reduce the number of switches, MINs use bristling, a technique wherein multiple ports are connected to a single switch. This is used in fat tree networks [HP07].

#### 2.1.1.3 Shared Medium Interconnects

Shared medium interconnects, such as arrays, buses and rings are characterized by a single link that is shared by all components. Buses, for example also provide for total order. Although they are simpler to implement, these networks are not scalable and require arbitration in order to access the network [DYL03].

#### 2.1.1.4 Commonly Used OCNs

Mesh networks are by far the most popular [WGHea07] [GKS<sup>+</sup>07], mainly because of the short channel distances between neighbouring nodes resulting in one cycle hop delay and thereby addressing the wire delay problem for deep submicron technologies. However, as the number of nodes increases, the router radix (connectivity of the router) is increased to reduce the hop latency. Equation 2.2 gives the power dissipated in sending a flit (basic flow control unit, normally the minimum amount of information that can be transmitted over the physical link [DYL03]) per hop [DT01]:

$$P_{hop} = P_{iocontrl} + P_{wire} \tag{2.2}$$

where,  $P_{iocontrl}$  is the power dissipated in the input and output controller of the transmitting node and total power dissipated because of this factor is dependent on the number of hops;  $P_{wire}$  is the power dissipated as the flit traverses the wire and the total power dissipated because of this factor is dependent on the length of the wire.

In topologies such as torus, the power dissipation increases mainly because of the varying wire lengths to interconnect different nodes [BD06] [DT01]. Therefore, nowadays a more popular topology is the concentrated mesh. Concentrated meshes increase the radix of a router using the concept of bristling, wherein each router node services four processing nodes. The router itself is then connected to four such routers using the mesh network links and express links as shown in Figure 2.4. Express links connect a router situated on the edge of the mesh network to other alternating edge routers. This layout improves area efficiency, the hop latency (more connectivity compared to a torus) and does not require complex wiring layout (no large varying wire lengths), thereby reducing power dissipation. However, the disadvantage of this scheme is that there is an increase in design complexity of the router resulting in larger router delay. Recent papers have proposed high radix router based concentrated mesh, also known as the flattened butterfly topology, to reduce the routing latency and power dissipation [KBD07]. Each router within a row of the 2-D mesh network connects to all other routers in that row as well as all routers within the same column. This type of network incorporates the high radix feature of indirect networks on a symmetric direct network. Although this scheme uses varying wire lengths similar to the torus network, it reduces the hop count (lower than the concentrated mesh) and therefore reduces the total power dissipated in the input and output controllers, which compensates for the increase in power due to wiring complexity.

Figure 2.4: Concentrated Mesh [BD06]

### 2.1.2 Routing Protocols

A routing algorithm determines the path between source and destination and gives an indication of how effectively the bandwidth on this path is utilized [Pin06] [DYL03]. The routing algorithm also determines how the load is distributed within the network [HP07]. The main purpose of a routing algorithm is to guarantee packet delivery to its destination. It does this by restricting certain

paths within the network. Depending on the number of paths restricted routing algorithms are classified as deterministic or adaptive. Subcategories within each class of routing determine whether the route for the packet to be sent is computed in advance and set within the header of the packet (source routing), or if the route is computed on the fly, given the information about the source and destination (distributed routing) [DYL03]. Source routing is simpler to implement, but requires prior knowledge of traffic conditions before the route is computed and is almost obsolete in OCN [GLD06]. Distributed routing is harder to implement requires fixed hardware tables (not scalable) or finite state machines for determining the link on which the packet needs to be sent [DYL03]. The reason distributed routing is preferred over source routing is because it is more adaptive to changing network conditions.

#### 2.1.2.1 Deterministic Routing

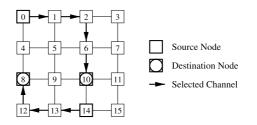

In this routing scheme, the path from source to destination is always fixed. The most popular routing algorithm in this category is the Dimension Order Routing Protocol (DOR) [SB77], which is used for direct networks, such as meshes, tori and hypercubes. In this routing protocol, the packet changes its dimension only when the link or channel needed to the send the packet is not on the same dimension [HP07]. Figure 2.6 shows the DOR algorithm and Figure 2.5 shows a mesh network using the DOR algorithm to route packets [DYL03]. DOR is also known as a minimal routing algorithm because it selects the shortest path from source to destination and always ensures that the packet is progressing towards the destination.

Figure 2.5: Mesh Network Using DOR [DYL03]

```

Algorithm: XY Routing for 2-D Meshes

Inputs: Coordinates of current node (Xcurrent, Ycurrent)

and destination node (Xdest, Ydest)

Output: Selected output Channel

Procedure:

Xoffset := Xdest - Xcurrent;

Yoffset := Ydest - Ycurrent;

if X offset < 0 then

Channel := X - ;

endif

if X offset > 0 then

Channel := X+:

endif

if Xoffset = 0 and Yoffset < 0 then

Channel := Y - ;

endif

if Xoffset = 0 and Yoffset > 0 then

Channel := Y + ;

endif

if X offset = 0 and Y offset = 0 then

Channel := Internal;

endif

```

Figure 2.6: Dimension Order Routing Algorithm [DYL03]

### 2.1.2.2 Adaptive Routing

In this routing scheme, multiple paths exist between a source and destination. The path can change depending on the traffic level within the network [DYL03]. This type of routing algorithm provides better load balancing and is also fault tolerant [CSG99]. It is also know as non-minimal routing because the packet may get routed in a direction away from the destination in order to avoid or reduce traffic congestion [DYL03]. The hardware required to make these routing decisions is complex and hence could potentially increase the route calculation time. Depending on the number of channels that are available for routing, fully and partially adaptive routing algorithms exist [DYL03].

#### 2.1.2.3 Topology Agnostic Routing

Routing algorithms that are topology dependent are not fault tolerant because failure of a single link within the network could lead to stalling the system [CSG99]. Therefore, protocols that do not make any assumptions about the underlying network, also known as topology agnostic algorithms, are proposed. One such algorithm is the  $Up^* - Down^*$  routing algorithm [SBB+91]. In this routing algorithm, it is necessary for the node that is generating a packet to determine the topology of the network and create a tree based on the location of the source and destination. Further on, it assumes that nodes within a tree are interconnected using bi-directional links. Similar to tree routing, packets move up the tree towards the root and then down towards the destination. Restrictions to the routing protocol requires that a packet cannot re-traverse in a direction(up/down), once taken. Another algorithm in this category, also known as segment based routing [MFD+06], proposes to divide the network into segments and places route turn restrictions within each segment, allowing non-minimal routing within a segment.

### 2.1.3 Flow Control

Flow control is technique that is used to prevent a sender from sending packets at a rate that is faster than that the receiver can process [HP07]. It helps in controlling the traffic congestion level in the network [DYL03]. There are different flow control schemes, the simplest one involving performing a handshake protocol between the sender and receiver (request and ack scheme). Another scheme, Stop and Go, notifies a sender that the receiver's buffers are nearly full and the sender should stop sending packets. Credit based flow control allows a sender to keep track of the number of available buffers at the receiver end. The sender maintains a count (credit) of the number of buffers at the receiver and decrements a counter every time it sends a packet. The receiver on accepting the packet and freeing the buffer, sends a credit increment message to the sender [Pin06]. A more recent flow control technique known as Adaptive Bubble flow control [PIB<sup>+</sup>01] relies on ensuring at least two packet buffers free at the receiver before the packet is sent out of the sender.

### 2.1.4 Switching Technique

Switching techniques allow a packet to get forwarded through the network based on the buffer requirements. There are three main switching techniques used, Store and Forward (S&F), Virtual Cut-Through (VCT) and Wormhole [DYL03]. S&F switching technique buffers the complete packet before sending to the next node in the route direction. VCT allows for packet pipelining once the header packet is received at a node, i.e. the header is forwarded to the next node before the trailing packets arrive from the sending node. If the header packet is blocked due to congestion, then the complete message is buffered, similar to S&F [DYL03]. Wormhole applies switching to flits, in order to save buffer space. The packet is split into flits and they are transmitted through the network similar to that in VCT, except that packet does not buffer at flit blockage [DYL03]. The greater chance of message blockage in wormhole scheme requires the network to be associated with extra buffers per physical channel (virtual channels) and flow control techniques [DS87].

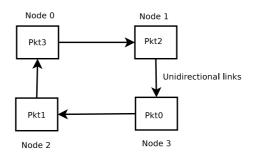

### 2.1.5 Deadlock Avoidance

For packet progression through a network, network resources (buffers, channels/links) must be available. Non-availability of a link or buffer that is blocked results in a packet waiting for the resource to be freed and hence leads to deadlock of the system. During deadlock, there is no progression of packets through the network. All networks are prone to deadlock because they do not contain infinite buffer resources [HP07] [HGR07]. A simple deadlock scheme is illustrated in Figure 2.7, where in all packets are destined for alternating nodes, with each node unable to send its packet because the successive node buffers are full. The cause of a deadlock is due to the formation of a cycle by the turns contained in a packet's route [DYL03]. This deadlock can be broken by adding extra buffers per physical channel. These buffers are also known as Virtual Channels [DS87]. Virtual channels are one of the most popular ways to avoid deadlock, especially for adaptive routing based networks. However they consume extra space and power on chip [HGR07].

While the routing algorithm is responsible for controlling packet flow through the network, one of the easiest ways to avoid deadlock is through using a deadlock free routing algorithm, e.g. DOR. DOR ensures that path taken by a packet from source to destination never forms cycles. It does this by allowing the packet to perform only a single change in dimension (direction) when moving from source to destination. DOR is restrictive in the number of paths that a packet can take and therefore the turn model [GN92] was proposed to provide a minimal combination of *turns* that a packet can make without creating cycles in its route. The turn model does not require addition of VCs. The  $Up^* - Down^*$  routing algorithm is a instance of the turn model and is a partially adaptive routing algorithm [DYL03].

Another proposal for avoiding deadlock is to use flow control. Credit based flow control is shown to be most effective in avoiding deadlock, by controlling the amount of traffic that enters the network [HGR07]. If deadlock is detected then packets are dropped to ensure forward progress in the network [DYL03]. Apart from deadlocks, networks are also prone to livelock. Livelock occurs when a packet travels through the network towards the destination but gets rerouted in a different direction every time because of blocked buffers [DYL03]. This situation normally occurs in routing protocols that allow non-minimal routing. Livelock occurrence probability is reduced by limiting the number of non-minimal routes taken.

Figure 2.7: Classic Example of Deadlock [DS87]

### 2.2 Cache Coherency Protocols

Studies in the past have shown that computation intensive applications, such as scientific workloads, databases and internet applications support inherent parallelism and can perform better if this parallelism feature is exploited by the underlying hardware [HP07] [CSG99]. The quest for higher speed in application executions as well as the growth in microprocessors fuelled by the enhancement in VLSI technology, gave rise to multiprocessor systems [CSG99]. Multiprocessor systems, utilise multiple microprocessors to speed up the execution time of a single parallel application or can run several applications to produce increased performance. Unlike their uniprocessor counterpart, multiprocessor systems require an enhanced communication based programming model and this gives rise to two types of parallel programming paradigms, namely shared memory and message passing. Message passing models require explicit programmer defined messages to be exchanged among communicating processors [PTM96]. Also data distribution plays a key role in the performance of such systems. Programming such systems is non-trivial as each processor uses a separate address space, unlike uniprocessors that use a single address space. On the other hand, the shared memory programming model is simpler to program as it achieves communication through a shared single address space and allows for easy porting of parallel applications [PTM96]. Parallel programs that run on shared memory multiprocessors always need to ensure that the value of data being read is the last written <sup>1</sup> [HP07]. However, having multiple copies of the same data in different caches in multiprocessor systems poses problems in maintaining this constraint. Cache coherency protocols use hardware or software techniques in order to ensure this condition [HP07]. Of the hardware based cache coherency protocols, the simplest one is the snoop based protocol, wherein all caches snoop a bus or any ordered network to maintain the correct state of the cache line. Snoop based multiprocessor systems are also known as symmetric shared memory multiprocessor systems because the access time to the shared memory is uniform irrespective of the location of the processor. One of the popular cache coherency protocols is the non-inclusive based, MOESI. It is a combination of the Dragon (MOESI with

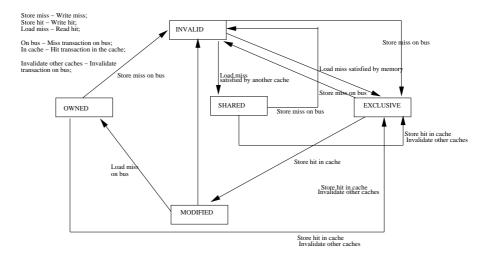

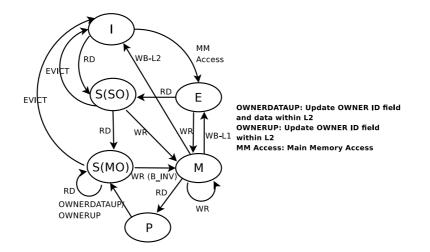

write invalidate feature to Shared cache lines) and CRAC (with the Owned state transfer feature between L1 caches) cache coherency protocols [AB86]. The state diagram for the MOESI protocol is shown in Figure 2.8 and Table 2.1 explains the various cache states.

While cache coherency protocols provides data consistency for a single location by deciding on what value of shared data is read [HP03]. Memory consistency models on the other hand handles the data consistency for multiple locations [Ste05]. It decides when the value of the data can be read [HP03]. In short, memory consistency is a formal specification of how ordering of reads and writes

<sup>&</sup>lt;sup>1</sup>Sequentially consistent memory model

Figure 2.8: The MOESI state diagram [Sun03]

should take place within a program [Dig95]. All memory consistency models require programmers to devise mechanisms to ensure correctness of program execution [Dig95]. Memory consistency models for multiprocessor systems are classified broadly as either sequential or relaxed consistent. Sequentially consistency models require that program order is maintaind within a processor and that writes to a single location are seen in the same order by all processors (write serialization) [Lam79]. Although memory operations from different processors may be interleaved, they should commit in the same order as if the program was being executed sequentially on a single processor, i.e. a memory operation is atomic and completes in the same order that it was issued [Dig95].

Relaxed consistency models optimize on the commit ordering of reads and writes to different addresses within a processor as well as on different processors. Relaxed models are normally classified depending on the read and write ordering they relax, i.e. either read-after-write (RAW) or write-after-write (WAW) or read-after-read (RAR) and write-after-read (WAR) [Dig95]. All relaxed consistency models maintain the write serialization property [Dig95]. However, they require programmers to use special instructions known as fence instructions to overide program order and introduce synchronizing operations for accessing shared memory [Dig95]. Use of relaxed memory models allows for implementation of hardware and software optimizations on the application.

| Cache State | State Description                              |

|-------------|------------------------------------------------|

| М           | Modified-Line is dirty and the latest copy of  |

|             | the data exists in only one L1 cache which is  |

|             | responsible for writeback to main memory.      |

| 0           | Owned-Line is dirty and shared between mul-    |

|             | tiple L1 caches. L2 is not inclusive. The L1   |

|             | cache that contains the O cache line is re-    |

|             | sponsible for a writeback to memory.           |

| Е           | Exclusive-Line is clean and a copy of the data |

|             | exists in only one L1 and L2 cache.            |

| S           | Shared-Line is clean and exists in one or more |

|             | L1 caches and the L2.                          |

| Ι           | Invalid-Cache line contains invalid data in    |

|             | L1.                                            |

Table 2.1: Cache Line State Description

### 2.2.1 Snoop Based Cache Coherency Protocol

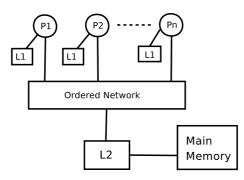

In snoop based cache coherency protocols, broadcast is used as a means to maintain the state of a cache line. All caches snoop a bus or any ordered interconnect to determine the current state of the cache line. Bus based snoop cache coherency protocols have been used extensively in the past on most multiprocessor systems but suffer from lack of scalability, because a single interconnect (lower bandwidth) is used for broadcast traffic. Another disadvantage of snoop based system is the interference caused by processor and bus interfaces trying to access or snoop the cache tags at the same time instant, resulting in the reduced performance of the system [ASHH88]. A solution to this problem is to use duplicate tags [ARM06] [ASHH88]. But this increases the power and space overhead within the system. Duplicate tag based snoop systems also have the requirement of ensuring that any updates to duplicate tags and original cache tags is atomic in nature. In order to increase the snoop bandwidth, systems such as Sun's FirePlane servers use separate address and data networks, the former being ordered and the latter is unordered [Cha02]. Alternatively, in order to reduce the broadcast snoop traffic and power dissipation associated with snooping the cache tags, schemes such as course-grained coherence tracking and JETTY filters have been proposed and their working is described below [CSL+06] [BDH+99] [MMFC01]. Figure 2.9 shows a snoop based multiprocessor system.

• Course Grained Coherence [CSL+06]

Course grained coherence relies on tracking snoop requests for large regions of memory within each processor node. Each snoop request is mapped to a memory region. Two different schemes are used in order to store the region information.

In the first scheme, cache lines from multiple regions are hashed to the same entry. To implement this, two tables are used, the first one is a hash table into the line count of the cache lines from multiple regions - indicating a line from a region *may be* present in the cache, and the second a non-shared table that tracks regions (using the address) that are not shared. If a processor generates a request it takes the following actions:

- It first checks its non-shared table to see if the request's region is not shared. If no information is available, then the request is broadcast, else the line is fetched from memory.

- On a broadcast, other processors check their hash region table and if the line count is > 0 for the memory region corresponding to the broadcast address, then the non-shared table is checked.

- If an entry is present in the non-shared table it is invalidated.

Along with the hash and non-shared tables, the data and instruction caches are also checked and their state is updated on a cache hit. Data and state information is then provided to the requesting processor.

- The requesting processor, on receiving data and state, will increment its own hash table and update its cache states. It sets an entry in the non-shared table, if the data was provided by memory.

Although this method is space efficient and does not require evicting entries from the hash table, it does not provide high accuracy in predicting the existence of a line from a region.

The second scheme, has higher space overhead and maintains a single table (region coherence array - RCA) whose entries provide for a oneto-one mapping between the cache line and the memory region. An RCA entry also contains the number of lines from a region that are cached by the processor and the state of the region, i.e. if the region is shared or modified. RCA's are checked by both local cache requests and by snoop broadcasts. If an RCA entry matches a broadcast request, it updates its own state to shared as well as takes the necessary cache action. The limitation of this scheme is that on eviction of an RCA entry, the corresponding cache lines have to be invalidated or written back to main memory. The effect of this disadvantage is reduced by using a policy that requires evicting regions with small number of cached lines. The space overhead for an RCA configuration of 512B with same number of lines as the L1 cache is about 5.9% of a 1 MB L2 cache area. The scheme has been shown to reduce broadcasts by 55-97% on some of the benchmarks that were evaluated and an overall decrease in runtime execution by about 8.8% on average.

#### • JETTY Filters [MMFC01]

JETTY filters (per processor) are used to snoop requests over the bus in order to determine if it is worthwhile accessing the L1 or L2 cache for the same request. It derives its inspiration from the fact that most snoop requests miss in L1 or L2 caches and hence cause wastage of power when accessing their tags. For efficient working of the JETTY filter it is imperative that the structure of the filter is small enough so as to not waste space as well as energy in searching the filter itself. Also, the filter should never mis-predict, i.e. a request for a cached line should always be allowed to snoop the L1 and L2 tags. Three types of JETTY filters are described. The first one keeps track of cache requests that were snooped and missed within the L1 and L2 of the processor. The second one keeps track of all cached lines and finally the third one is a hybrid version that is a combination of the first two methods. On average, around 41% power reduction was observed from the hybrid version compared to accessing the cache tags during every snoop request. Of all the three types of JETTY filters the hybrid version gave the best performance for power reduction. These filters act as duplicate cache tag arrays and help in reducing the latencies caused when both processor and snoop interfaces try to access the cache tags simultaneously.

Figure 2.9: Snoop based Symmetric Shared Memory Multiprocessor [HP07]

### 2.2.2 Directory Based Cache Coherency Protocols

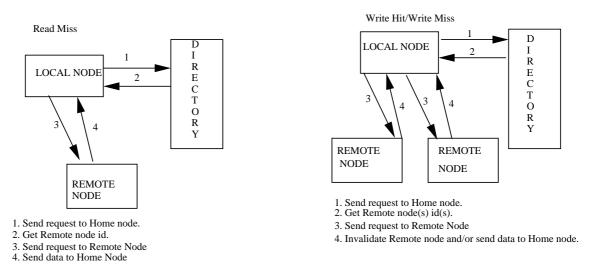

For highly scalable systems, the shared memory is physically distributed across various nodes and a switched network is used to interconnect them. These types of multiprocessors are known as distributed shared memory system and they use directory based cache coherency protocols [HP07]. Directories are separate memory modules that maintain the state of every cached line along with a vector that indicates the list of sharers for that cache line. They can be either centralized or distributed among nodes to keep track of the state of the shared data within the local memory in the node. Schemes with both static and dynamic directory entry placement have been described in the literature [PTM96]. A simple directory protocol is shown in figure 2.10 [HP07]. Nodes within this protocol scheme are classified as either local (where the request originates), home (where the directory for the requested memory word resides) or remote (other nodes that contain the same memory block in their caches). For a read miss, the request from the local node is forwarded to the home node, which in turn either supplies the data if it is in memory or forwards the request to the remote node where the actual data resides. The local node gets the data and if the remote node supplied the data, it updates its own cache and also the state of the directory entry in the home node to indicate the list of sharers for this address. For a write request, the local node sends invalidation messages or update messages to all the sharers and waits for an acknowledgement from each of them thus guaranteeing that the write was seen by all sharers. The list of sharers is fetched from the home node. The local node now has exclusive access to the cache line and the directory in the home node is updated with the new owner information. Ordering is ensured during read and write access by the directory that waits for an acknowledgement message from

Figure 2.10: Simple Directory Based Scheme [CSG99]

the requestor and does not allow any new request for the same address to proceed until the original request for that address has completed.

#### 2.2.2.1 Directory Design Alternatives

The design of the directory has significant impact on the latency introduced due to indirection during coherence transactions among processor nodes [PTM96]. The full map directory is not very efficient in terms of space complexity  $(O(N^2))$ and because cache lines are normally shared by a small number of processors, several alternatives schemes have been proposed to reduce this overhead. Note that all schemes provide reduced performance compared to the full map directory as a trade off over smaller space overhead.

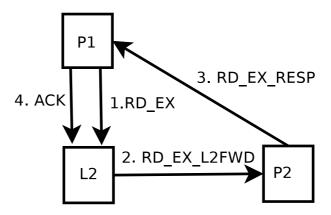

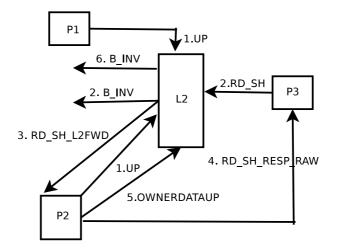

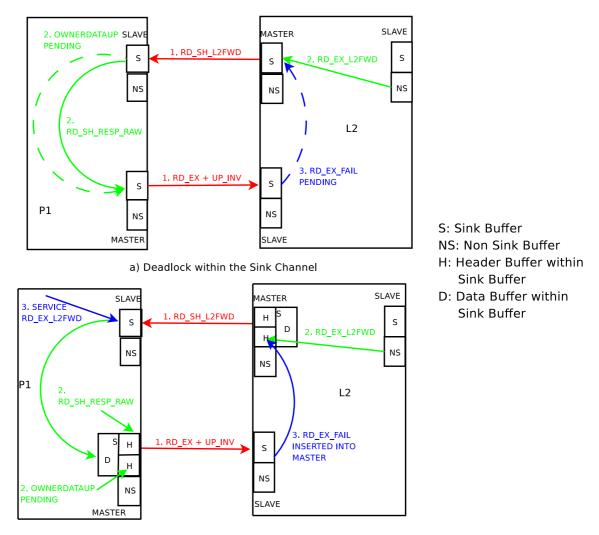

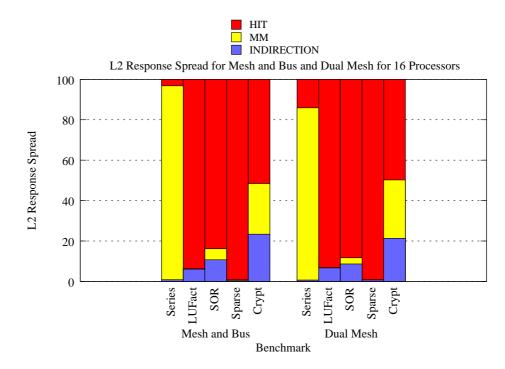

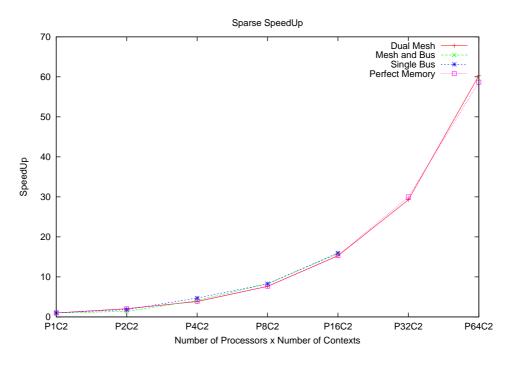

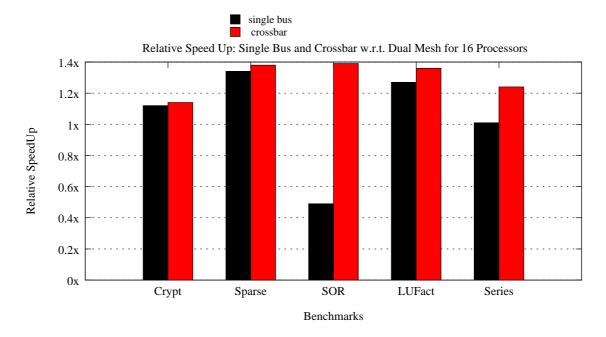

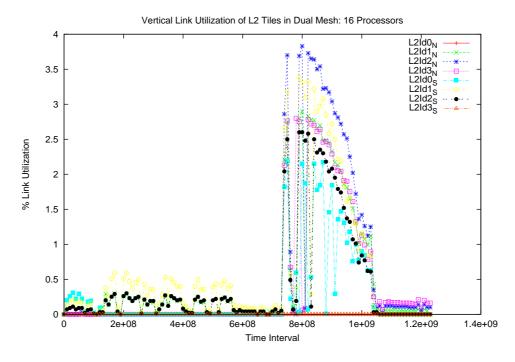

• SCI - Scalable Coherent Interface [PTM96][NS92]