# HIGH PERFORMANCE OPTIMIZATIONS IN RUNTIME SPECULATIVE PARALLELIZATION FOR MULTICORE ARCHITECTURES

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2013

By Paraskevas Yiapanis School of Computer Science

## Contents

| A  | bstrac | et      |                                                       | 10 |

|----|--------|---------|-------------------------------------------------------|----|

| De | eclara | tion    |                                                       | 11 |

| Co | opyri  | ght     |                                                       | 12 |

| A  | cknov  | vledgme | ents                                                  | 13 |

| 1  | Intr   | oductio | n                                                     | 15 |

|    | 1.1    | There   | is Something about Parallelism                        | 16 |

|    | 1.2    | The R   | ise of Multi-core Architectures                       | 17 |

|    | 1.3    | Challe  | enges in Parallel Programming                         | 18 |

|    |        | 1.3.1   | Discovering Available Parallelism                     | 19 |

|    |        | 1.3.2   | Reasoning about Shared Mutable Data                   | 19 |

|    |        | 1.3.3   | Optimizing for Performance                            | 20 |

|    | 1.4    | Auton   | natic Parallelization                                 | 21 |

|    |        | 1.4.1   | Manual and Automatic Parallelization                  | 21 |

|    |        | 1.4.2   | Runtime Automatic Parallelization                     | 22 |

|    | 1.5    | Specu   | lative Parallelization                                | 23 |

|    |        | 1.5.1   | Phases of Speculative Parallelization                 | 23 |

|    |        | 1.5.2   | Performance Potentials of Speculative Parallelization | 24 |

|    | 1.6    | Motiva  | ation                                                 | 26 |

|    | 1.7    | Contri  | butions                                               | 27 |

|    | 1.8    | Public  | ations                                                | 28 |

|    | 1.9    | Thesis  | Structure                                             | 29 |

| 2  | Fun    | dament  | tals of Runtime Parallelization                       | 31 |

|    | 2.1    | Introd  | uction                                                | 31 |

|   | 2.2 | Inspec  | tor/Executor: An Overview                                   | 32 |

|---|-----|---------|-------------------------------------------------------------|----|

|   |     | 2.2.1   | Inspector/Executor                                          | 32 |

|   |     | 2.2.2   | Inspector/Executor for Fully Parallel Loop Identification   | 32 |

|   |     | 2.2.3   | Earlier Work on Inspector/Executor                          | 34 |

|   |     | 2.2.4   | Weakness                                                    | 34 |

|   | 2.3 | Specul  | lative Parallelization                                      | 34 |

|   |     | 2.3.1   | Brief Description                                           | 34 |

|   |     | 2.3.2   | Design Specification                                        | 35 |

|   |     | 2.3.3   | Other Implementation Details                                | 42 |

|   |     | 2.3.4   | General Considerations                                      | 43 |

|   | 2.4 | Transa  | actional Execution                                          | 44 |

|   |     | 2.4.1   | What is a Transaction?                                      | 44 |

|   |     | 2.4.2   | Database Transactions                                       | 45 |

|   |     | 2.4.3   | Transactional Memory                                        | 45 |

|   | 2.5 | Summ    | ary                                                         | 46 |

| 3 | Adv | anced T | <b>Fopics in Runtime Parallelization</b>                    | 47 |

|   | 3.1 | Introdu | uction                                                      | 47 |

|   | 3.2 | Execut  | tion Model                                                  | 48 |

|   |     | 3.2.1   | Inspector/Executor                                          | 48 |

|   |     | 3.2.2   | Speculative Parallelization                                 | 49 |

|   |     | 3.2.3   | Speculative Parallelization with Inspection Support         | 50 |

|   |     | 3.2.4   | Decoupled Software Pipelining with Speculation Support      | 51 |

|   | 3.3 | Metad   | ata and Version Management                                  | 53 |

|   |     | 3.3.1   | Speculation with Decoupled Shadow Data                      | 53 |

|   |     | 3.3.2   | Speculation with Shared Shadow Data                         | 56 |

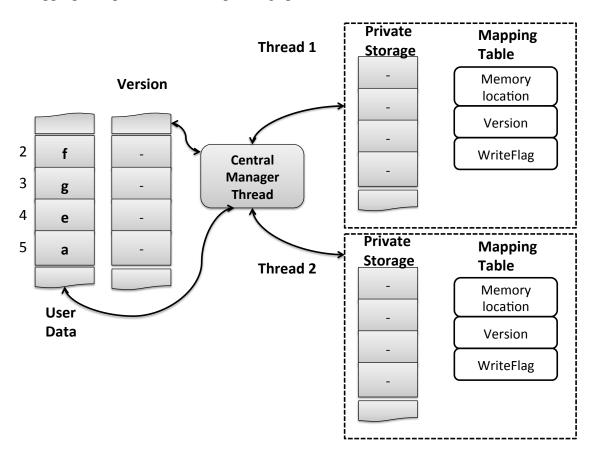

|   |     | 3.3.3   | Speculation using a Centralized Manager Thread              | 59 |

|   | 3.4 | Confli  | ct Detection, Rollback, and Commit                          | 62 |

|   |     | 3.4.1   | Lazy Conflict Detection                                     | 63 |

|   |     | 3.4.2   | Eager Conflict Detection                                    | 66 |

|   | 3.5 | Work S  | Scheduling                                                  | 70 |

|   | 3.6 | Summ    | ary                                                         | 71 |

| 4 | Min | ITLS:   | In-Place Speculative Parallelization with Parallel Rollback | 73 |

|   | 4.1 | Introdu | uction                                                      | 73 |

|   | 4.2 | MiniJ   | ΓLS: System Description                                     | 74 |

|   |     |         |                                                             |    |

|   |                                                           | 4.2.1                                                                                                                                  | General Concept                                               | 74                                                                                                                                   |

|---|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                           | 4.2.2                                                                                                                                  | Metadata                                                      | 74                                                                                                                                   |

|   |                                                           | 4.2.3                                                                                                                                  | Speculative Operations                                        | 77                                                                                                                                   |

|   |                                                           | 4.2.4                                                                                                                                  | Conflict Detection                                            | 78                                                                                                                                   |

|   |                                                           | 4.2.5                                                                                                                                  | Scheduling Policy and Ordering                                | 79                                                                                                                                   |

|   |                                                           | 4.2.6                                                                                                                                  | Rollback and Recovery                                         | 80                                                                                                                                   |

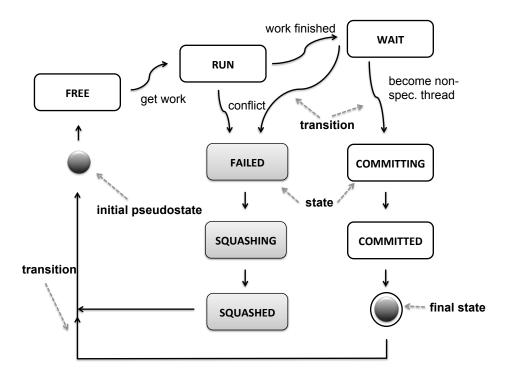

|   |                                                           | 4.2.7                                                                                                                                  | Speculative Thread Lifecycle                                  | 81                                                                                                                                   |

|   | 4.3                                                       | Summ                                                                                                                                   | ary                                                           | 82                                                                                                                                   |

| _ |                                                           | 1 4                                                                                                                                    |                                                               | 0.4                                                                                                                                  |

| 5 |                                                           |                                                                                                                                        | g Speculative Runtime Parallelization using Inspector Threads |                                                                                                                                      |

|   | 5.1                                                       |                                                                                                                                        |                                                               | 84                                                                                                                                   |

|   | 5.2                                                       |                                                                                                                                        | OR: System Description                                        | 85                                                                                                                                   |

|   |                                                           | 5.2.1                                                                                                                                  | General Concept                                               | 85                                                                                                                                   |

|   |                                                           | 5.2.2                                                                                                                                  | Metadata                                                      | 85                                                                                                                                   |

|   |                                                           | 5.2.3                                                                                                                                  | Speculative Operations                                        | 86                                                                                                                                   |

|   |                                                           | 5.2.4                                                                                                                                  | Speculative Thread Lifecycle                                  | 89                                                                                                                                   |

|   |                                                           | 5.2.5                                                                                                                                  | Inspector Threads                                             | 90                                                                                                                                   |

|   | 5.3                                                       | Summ                                                                                                                                   | ary                                                           | 92                                                                                                                                   |

|   |                                                           |                                                                                                                                        |                                                               |                                                                                                                                      |

| 6 | Eval                                                      | uation                                                                                                                                 | and Results                                                   | 94                                                                                                                                   |

| 6 | <b>Eva</b> l<br>6.1                                       |                                                                                                                                        | and Results                                                   | <b>94</b><br>94                                                                                                                      |

| 6 |                                                           | Introdu                                                                                                                                |                                                               |                                                                                                                                      |

| 6 | 6.1                                                       | Introdu                                                                                                                                | ection                                                        | 94                                                                                                                                   |

| 6 | 6.1                                                       | Introdu<br>Evalua                                                                                                                      | tion Methodology                                              | 94<br>94                                                                                                                             |

| 6 | 6.1                                                       | Introdu<br>Evalua<br>6.2.1                                                                                                             | action                                                        | 94<br>94<br>94                                                                                                                       |

| 6 | 6.1                                                       | Introdu<br>Evalua<br>6.2.1<br>6.2.2<br>6.2.3                                                                                           | action                                                        | 94<br>94<br>94<br>95                                                                                                                 |

| 6 | 6.1<br>6.2                                                | Introdu<br>Evalua<br>6.2.1<br>6.2.2<br>6.2.3                                                                                           | action                                                        | 94<br>94<br>94<br>95<br>96                                                                                                           |

| 6 | 6.1<br>6.2                                                | Introdu<br>Evalua<br>6.2.1<br>6.2.2<br>6.2.3<br>MINIT                                                                                  | action                                                        | <ul> <li>94</li> <li>94</li> <li>94</li> <li>95</li> <li>96</li> <li>99</li> </ul>                                                   |

| 6 | 6.1<br>6.2                                                | Introdu<br>Evalua<br>6.2.1<br>6.2.2<br>6.2.3<br>MINIT<br>6.3.1                                                                         | action                                                        | 94<br>94<br>95<br>96<br>99<br>99                                                                                                     |

| 6 | 6.1<br>6.2                                                | Introdu<br>Evalua<br>6.2.1<br>6.2.2<br>6.2.3<br>MINIT<br>6.3.1<br>6.3.2                                                                | action                                                        | <ul> <li>94</li> <li>94</li> <li>94</li> <li>95</li> <li>96</li> <li>99</li> <li>99</li> <li>99</li> </ul>                           |

| 6 | 6.1<br>6.2                                                | Introdu<br>Evalua<br>6.2.1<br>6.2.2<br>6.2.3<br>MINIT<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                                              | action                                                        | <ul> <li>94</li> <li>94</li> <li>94</li> <li>95</li> <li>96</li> <li>99</li> <li>99</li> <li>99</li> <li>103</li> </ul>              |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>             | Introdu<br>Evalua<br>6.2.1<br>6.2.2<br>6.2.3<br>MINIT<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                                              | action                                                        | <ul> <li>94</li> <li>94</li> <li>94</li> <li>95</li> <li>96</li> <li>99</li> <li>99</li> <li>99</li> <li>103</li> <li>105</li> </ul> |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>             | Introdu<br>Evalua<br>6.2.1<br>6.2.2<br>6.2.3<br>MINIT<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>LECTO                                     | action                                                        | 94<br>94<br>95<br>96<br>99<br>99<br>99<br>103<br>105                                                                                 |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>             | Introdu<br>Evalua<br>6.2.1<br>6.2.2<br>6.2.3<br>MINIT<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>LECTC<br>6.4.1                            | action                                                        | 94<br>94<br>95<br>96<br>99<br>99<br>99<br>103<br>105<br>109                                                                          |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>             | Introdu<br>Evalua<br>6.2.1<br>6.2.2<br>6.2.3<br>MINIT<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>LECTC<br>6.4.1<br>6.4.2<br>6.4.3          | action                                                        | 94<br>94<br>95<br>96<br>99<br>99<br>99<br>103<br>105<br>109<br>109                                                                   |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul> | Introdu<br>Evalua<br>6.2.1<br>6.2.2<br>6.2.3<br>MINIT<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>LECTC<br>6.4.1<br>6.4.2<br>6.4.3<br>MINIT | action                                                        | 94<br>94<br>95<br>96<br>99<br>99<br>99<br>103<br>105<br>109<br>109                                                                   |

|         | nclusions and Future Work                 | 12           |

|---------|-------------------------------------------|--------------|

| 7.1     | Summary and Conclusions                   | . 12         |

| 7.2     | Future Directions                         | . 12         |

|         | 7.2.1 Scheduling Partially Parallel Loops | . 12         |

|         | 7.2.2 Method-Level Speculation            | . 12         |

|         | 7.2.3 Adaptive Selection of TLS System    | . 12         |

|         | 7.2.4 Hardware Support                    | . 124        |

| Bibliog | raphy                                     | 12           |

| A Bas   | seline Systems Description                | 13           |

| A.1     | Introduction                              | 13           |

| A.2     | Baseline used for MINITLS: SPLIP          | 13           |

|         | A.2.1 Metadata                            | 13           |

|         |                                           |              |

|         | A.2.2 Algorithm Outline                   |              |

| A.3     |                                           | . 13         |

| A.3     | -                                         | . 13<br>. 13 |

Word Count: 29934

## **List of Tables**

| 1.1 | Thesis structure                                                     | 30 |

|-----|----------------------------------------------------------------------|----|

| 3.1 | Advances in the literature of speculative parallelization            | 49 |

| 3.2 | Design choices for main work in the literature of speculative paral- |    |

|     | lelization.                                                          | 72 |

# **List of Figures**

| 1.1 | Speculative parallelization phases.                                     | 24 |

|-----|-------------------------------------------------------------------------|----|

| 1.2 | Speculative parallelization of various applications from four important |    |

|     | benchmark suites. The graph shows the improvement percentage from       |    |

|     | speculative parallelization over sequential application runtime         | 25 |

| 1.3 | Speculative parallelization speedup over sequential for Sparse bench-   |    |

|     | mark (SPECjvm2008)                                                      | 26 |

| 2.1 | a) A loop to be parallelized. b) Stripped-down version of the loop to   |    |

|     | be executed by the inspector threads. c) Auxiliary data to facilitate   |    |

|     | inspection                                                              | 33 |

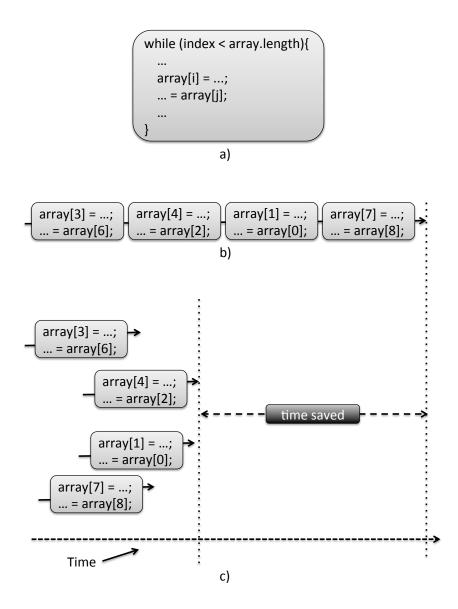

| 2.2 | a) Code fragment of loop to be parallelized. b) Sequential execution.   |    |

|     | c) Sample parallel execution.                                           | 36 |

| 2.3 | a) Speculative loop execution without dependencies. b) Speculative      |    |

|     | loop execution with dependency. c) Re-execution of offending threads.   | 37 |

| 2.4 | a) Metadata or shadow data associated with user data structure. b)      |    |

|     | Metadata associated with every speculative thread                       | 38 |

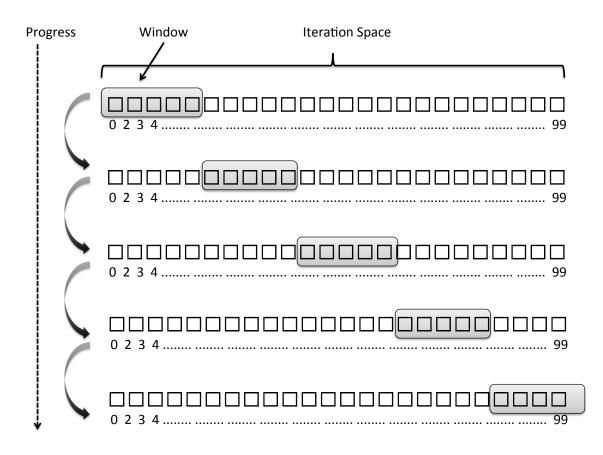

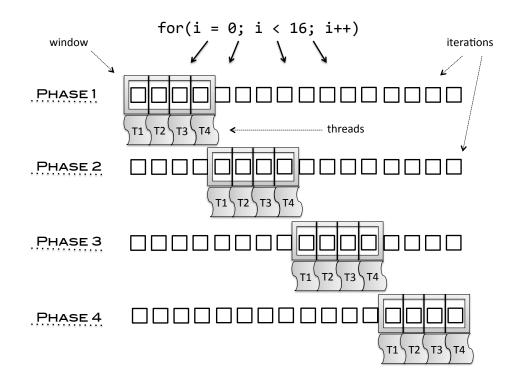

| 2.5 | Sliding window scheduling                                               | 42 |

| 3.1 | The various design points that make up a speculative parallelization    |    |

|     | system                                                                  | 48 |

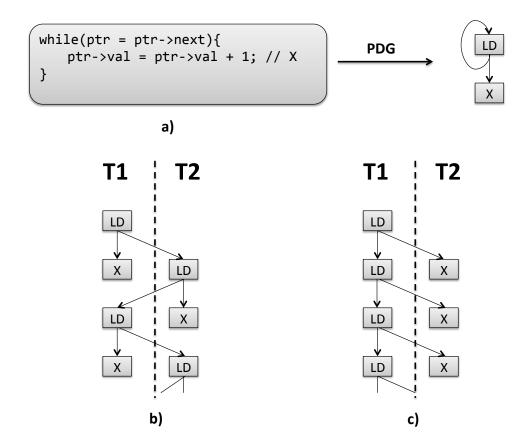

| 3.2 | a) Linked-list traversal. b) DOACROSS scheduling. b) DSWP schedul-      |    |

|     | ing. This example appears in [ORSA05a]                                  | 52 |

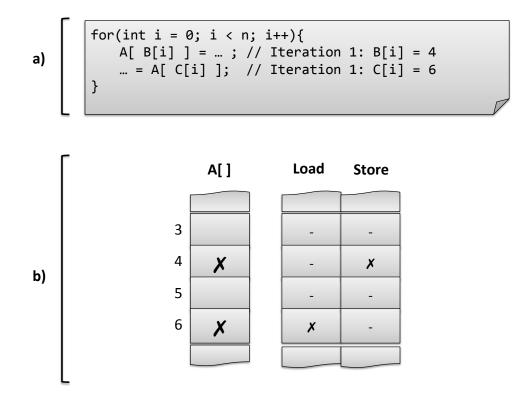

| 3.3 | DOALL test [RP94a] basic data structures                                | 55 |

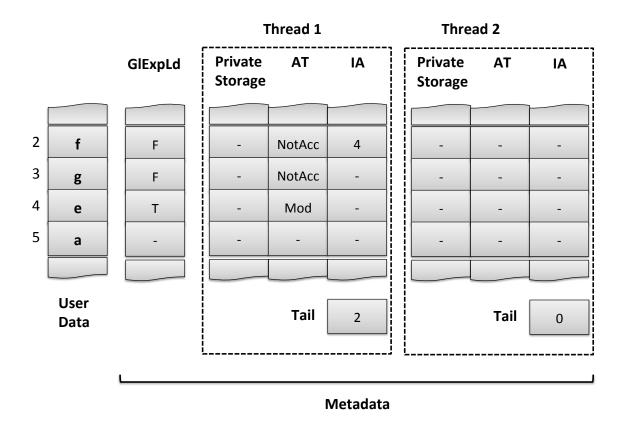

| 3.4 | The data structures used by Cintra and Llanos [CL03, CL05]. "AT"        |    |

|     | stands for Access Type,"IA" stands for Indirection Array, and "GIEx-    |    |

|     | pLd" stands for Global Exposed Load. The values inside the "GlEx-       |    |

|     | pLd" can be either true (T) or false (F).                               | 58 |

| 3.5 | Metadata used for CorD [TFNG08].                                        | 60 |

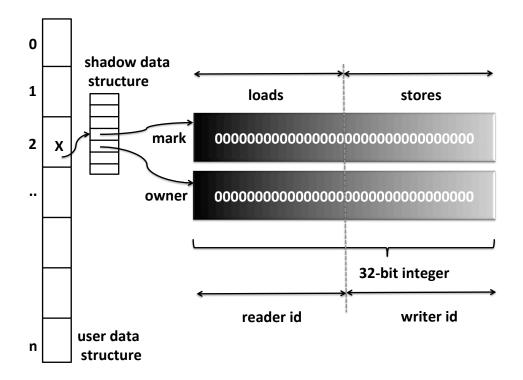

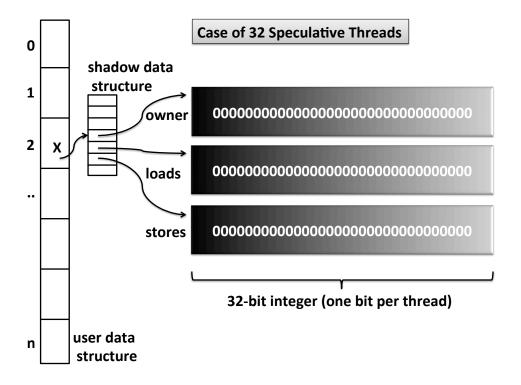

| 4.1 | Shadow data structure in MiniTLS                                                       | 76  |

|-----|----------------------------------------------------------------------------------------|-----|

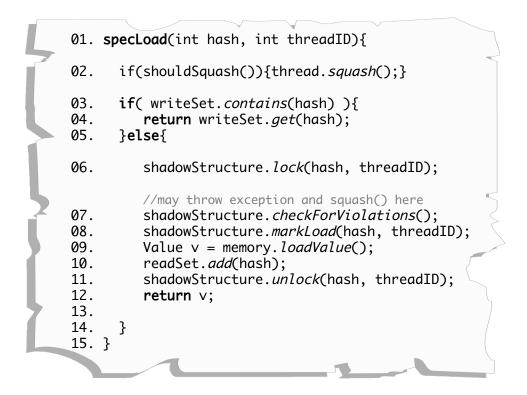

| 4.2 | Speculative load in MiniTLS                                                            | 78  |

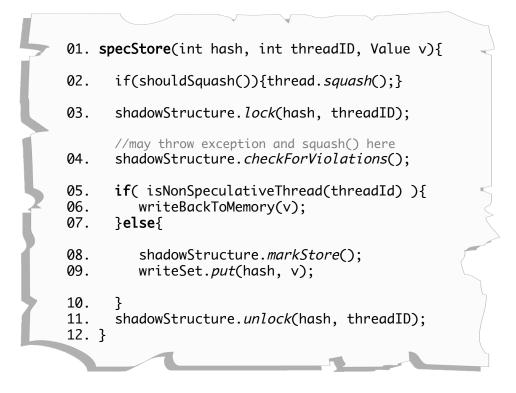

| 4.3 | Speculative store in MiniTLS                                                           | 79  |

| 4.4 | Four-thread sliding window scheduling policy for 16 iterations                         | 80  |

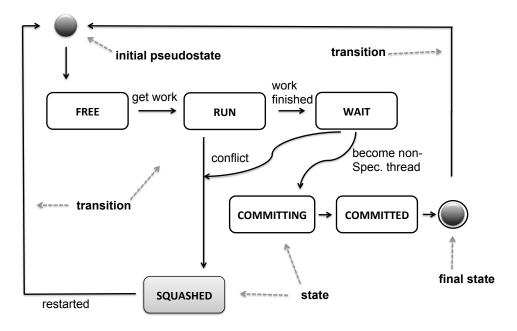

| 4.5 | Speculative thread lifecycle in MiniTLS                                                | 82  |

| 5.1 | Shadow data structure of Lector. $\ldots$                                              | 86  |

| 5.2 | Speculative store in Lector. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$     | 87  |

| 5.3 | Speculative load in Lector                                                             | 88  |

| 5.4 | Speculative thread lifecycle in Lector                                                 | 90  |

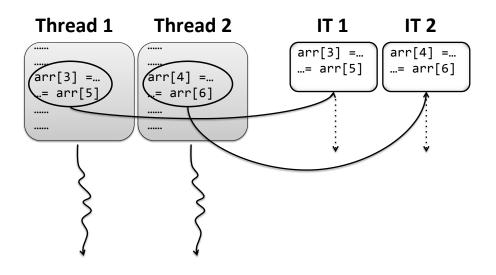

| 5.5 | Inspector threads are created by replicating the memory accesses from                  |     |

|     | speculative threads. "IT" stands for Inspector Thread                                  | 92  |

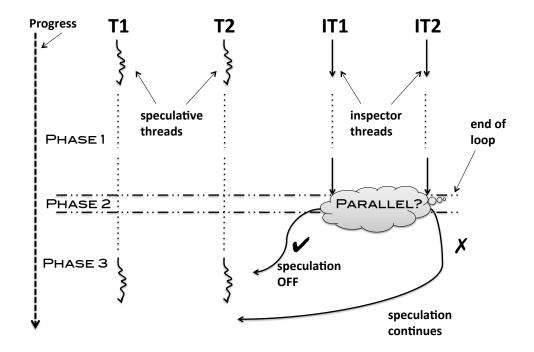

| 5.6 | Phase 1: Lightweight inspector threads (IT) execute concurrently with                  |     |

|     | TLS threads. Phase 2: ITs complete execution earlier than TLS threads                  |     |

|     | and test if the loop is DOALL. Phase 3: Depending on the outcome                       |     |

|     | of phase 2, either speculation continues as normal, or speculation is                  |     |

|     | turned off ( <i>i.e.</i> non-speculative parallel execution)                           | 93  |

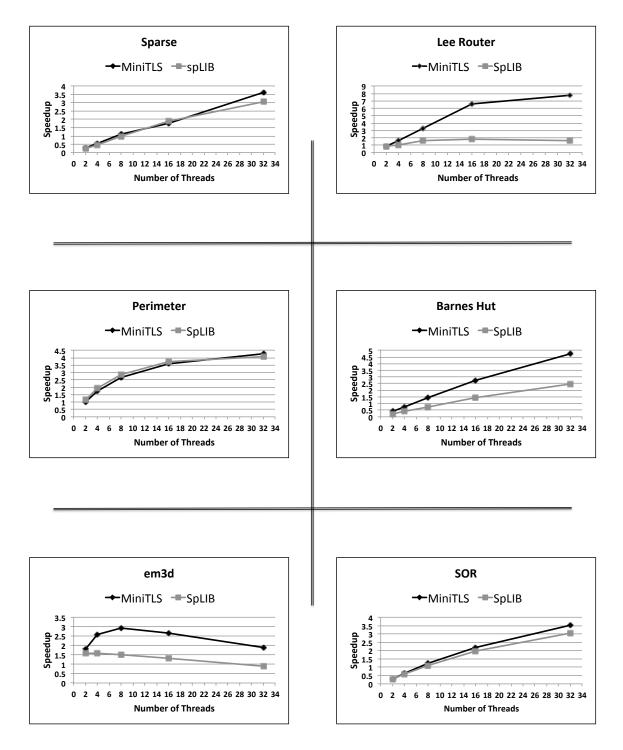

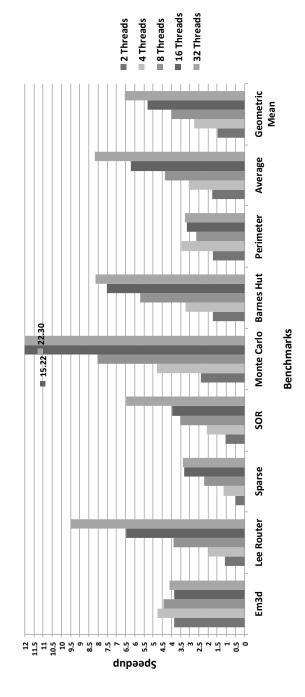

| 6.1 | Speedup results for MiniTLS. Sequential execution is denoted by 1 in                   |     |

|     | the y axis                                                                             | 100 |

| 6.2 | Time spent on speculation for Sparse. The y axis is intersected at the                 |     |

|     | sequential time.                                                                       | 101 |

| 6.3 | Speedup comparison of MiniTLS and SpLIP                                                | 102 |

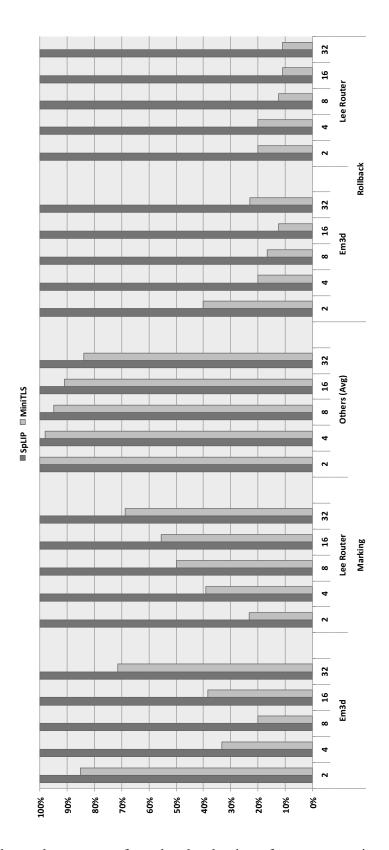

| 6.4 | Shows the amount of overhead reduction of MiniTLS against SpLIP.                       |     |

|     | The graph is normalized (baseline SpLIP). The first part shows reduc-                  |     |

|     | tion of speculative read/write marking. The second part reduction of                   |     |

|     | rollback time.                                                                         | 104 |

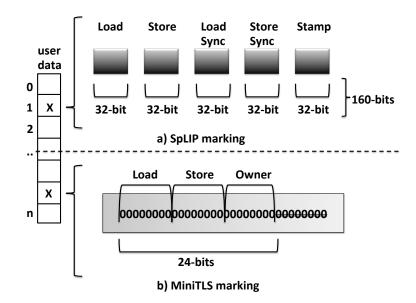

| 6.5 | Space required for 8 speculative threads using a) ${\tt SpLIP}$ and b) ${\tt MiniTLS}$ |     |

|     |                                                                                        | 105 |

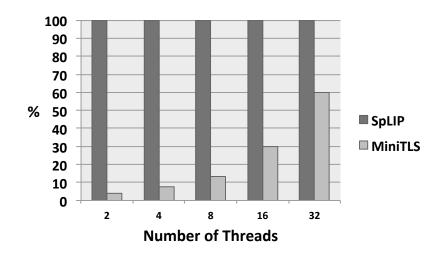

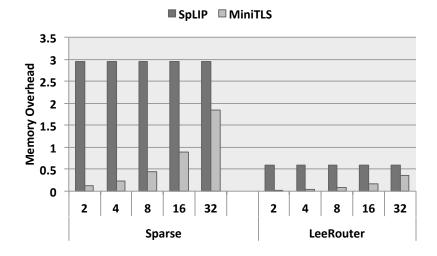

| 6.6 | Normalized (baseline SpLIP) space overhead comparison between Mini?                    | ΓLS |

|     | and SpLIP.                                                                             | 106 |

| 6.7 | Memory overhead of MiniTLS and SpLIP compared to the sequential                        |     |

|     | version.                                                                               | 107 |

| 6.8 | Speedup results for Lector against the sequential execution. Sequen-                   |     |

|     | tial execution is denoted by 1 in the y axis                                           | 111 |

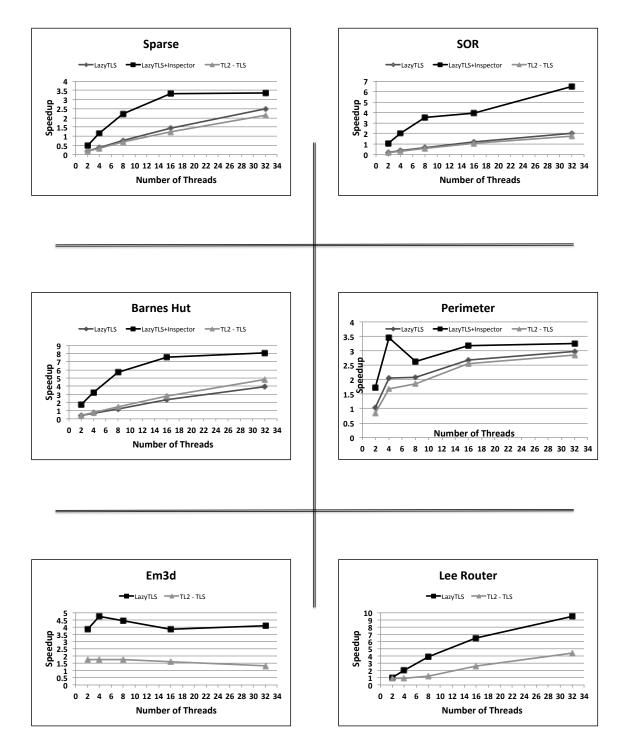

| 6.9 | Speedup comparison between LazyTLS, Lector, and TL2TLS                                 | 112 |

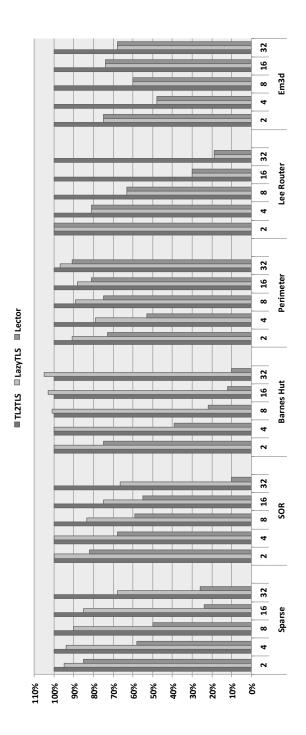

| 6.10 | Normalized speculative overhead reduction with baseline the TL2TLS    |     |

|------|-----------------------------------------------------------------------|-----|

|      | system                                                                | 114 |

| 6.11 | Speedup results for Lector vs. MiniTLS against the sequential execu-  |     |

|      | tion. Sequential execution is denoted by 1 in the y axis              | 117 |

| 6.12 | Memory overhead of MiniTLS and Lector compared to the sequential      |     |

|      | version of the Sparse benchmark                                       | 118 |

| 6.13 | Speedup comparison between speculative and manual parallel execu-     |     |

|      | tion for the Sparse benchmark (with the sequential version of Sparse  |     |

|      | used as baseline denoted by speedup == 1). $\ldots$ $\ldots$ $\ldots$ | 118 |

| A.1  | Metadata organization for SpLIP [OMH09]                               | 136 |

| A.2  | Metadata organization for TL2 [DSS06]                                 | 139 |

## Abstract

## HIGH PERFORMANCE OPTIMIZATIONS IN RUNTIME SPECULATIVE PARALLELIZATION FOR MULTICORE ARCHITECTURES Paraskevas Yiapanis A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy, March 2013

Thread-Level Speculation (TLS) overcomes limitations intrinsic with conservative compile-time auto-parallelizing tools by extracting parallel threads optimistically and only ensuring absence of data dependence violations at runtime.

A significant barrier for adopting TLS (implemented in software) is the overheads associated with maintaining speculative state. Previous TLS limit studies observe that on future multi-core systems it is likely to have more cores idle than those which traditional TLS would be able to harness.

This thesis describes a novel compact version management data structure optimized for space overhead when using a small number of TLS threads. Furthermore, two novel software runtime parallelization systems were developed that utilize this compact data structure. The first one, MiniTLS, is optimized for fast recovery in the case of misspeculations by parallelizing the recovery procedure. The second one, Lector, is optimized for performance by using lightweight helper threads, along with TLS threads, to establish whether speculation can be withdrawn avoiding that way any speculative overheads.

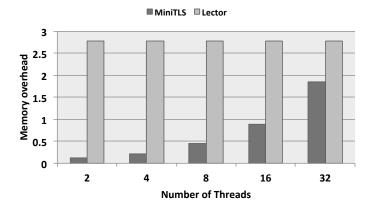

Facilitated by the novel compact representation, MiniTLS reduces the space overhead over state-of-the-art software TLS systems between 96% on 2 threads and 40% on 32 threads.

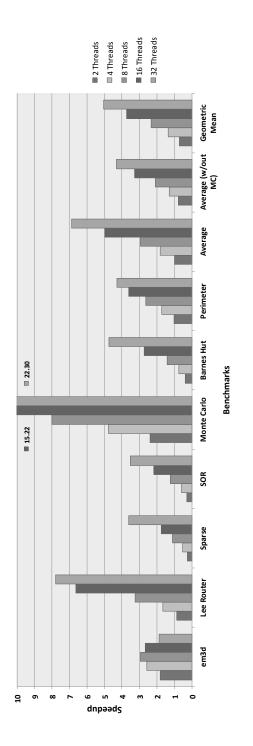

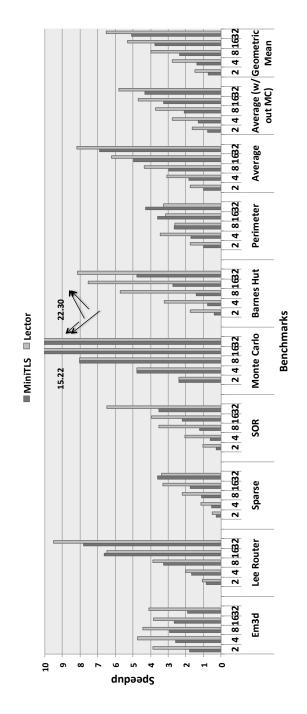

MiniTLS and Lector were applied to seven Java benchmarks performing on average 7x and 8.2x faster, respectively, against the sequential versions and on average 1.7x faster than the current state-of-the-art in software TLS for 32 threads.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx? DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester. ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses

## Acknowledgements

First of all, I would like to express my sincere gratitude to my principal supervisor Mikel Luján. With his immense knowledge and interesting research ideas he guided me on choosing a very interesting path to follow and to writing this thesis. He has been very patient with me and extremely supportive. Always trying to fit me into his busy schedule, especially when I was appearing out of the blue in his door without appointment.

I would also like to thank my co-supervisor Gavin Brown. Especially the first year of my PhD when my direction was still not clear, both Gavin and Mikel have been very supportive providing me with the right tools in order to pursue research. Without them, this thesis would not have been possible.

I would like to express my very great appreciation to John Keane for introducing me to the world of research and parallel computing, and for encouraging me to pursue a PhD.

During my PhD I was lucky to work with two great guys, Isuru Herath and Demian Rosas. We started the PhD at the same time and we spent endless hours the last 4 years "solving" the world's problems (except from computing problems). If it was not for them some of the world's problems would have been unresolved. They are very good friends as well as research partners. I feel happy the way their career continued but sad we will not be working together (at least in the near future).

Also, I would like to thank the people from the iTLS project (both Manchester and Edinburgh teams) for sharing their knowledge in their area of expertise, especially the Manchester team: Jeremy Singer and Adam Pocock.

I would like to thank Rose Date for being such a good friend. It is amazing how much energy she has and how pleasant and happy personality she always carries. I am sad she is not brewing coffee in the computer science school any more.

This thesis is dedicated to my parents for their unconditional love and moral support all those years. My brother, friends from Cyprus, and friends I met in Manchester also deserve to be acknowledged for their moral support.

Lastly, I wish to thank Laura. She was the one closest to me during the time of this PhD, doing everything possible to support me and being very understanding, especially during the most stressful periods.

## **Chapter 1**

## Introduction

The world of computer architecture has undergone major changes over the last years. Multi-core computers have dominated the market as quad-core availability can be found from personal computers [Inc12] to mobile devices [Sam12]. Although this imposes major challenges in terms of software development, researchers in software that now live the *multi-core revolution* are faced with the chance to exploit intriguing ideas to adapt to those changes. A sequential software application alone will not realize any performance improvements unless changes are introduced to the code, new language constructs are build (or new languages), or novel underlying mechanisms that automatically transform the code into something more meaningful to the current architectures.

This chapter answers the following questions:

#### Why parallelism is important?

Why computer architectures have gone multi-core?

Can automatic parallelization be a solution to parallel programming?

#### What solutions this thesis provides?

Certain sections of this chapter include a paragraph in italic type (such as this one). While various concepts become more clear, such paragraphs explain where the discussion is headed.

### **1.1** There is Something about Parallelism

Even though the last few years terms such as "dual-core" and "quad-core" have become very popular, parallelism *per se* was always important for computer architects.

Evidence of parallelism can be traced back to the early 1960s when computer architects James Thornton and Seymour Cray designed one of the first supercomputer known as Control Data Corporation (CDC) 6600 [Tho70]. A typical machine of that period would use a single Central Processing Unit (CPU), to operate the entire system. The CDC 6600 designers took a different approach from that. They designed simpler and faster CPUs that could only perform specific tasks instead of driving the entire system. For example, some CPUs would handle arithmetic and logic operation, others would handle memory or Input/Output (I/O) operations. Such a design allowed the machine to run faster not only because of the simpler and faster processors but also because operations from different CPUs could run in parallel with each other. Subsequently Cray Research, a supercomputer manufacturer found by Seymour Cray, popularized a special type of processor architecture known as the Vector processor by introducing a series of supercomputers starting with the CRAY-1 in 1976 [Rus78]. Vector processors contain special instructions that can operate on a set of data elements (as opposed to the traditional instructions that operate on a single data element). For instance, obtaining the sum of two vectors could be accomplished using only one such vector instruction.

Vector instructions were very efficient for vector or array operations but they also had several drawbacks such as significant processor state requirements and complicated instruction sets which resulted in higher costs. In the early 1990s advances in CMOS technology, the common technology used for integrated circuits, allowed more transistors to fit in a single die. Furthermore, the die could be clocked faster as feature size shrank. Rapid changes in CMOS technology allowed higher price-to-performance ratio, displacing slowly the widespread use of vector architectures that mainly continued to use Bipolar technology<sup>1</sup>.

Another form of parallelism in processor designs can also be observed since 1985; nearly all of them since then are using *pipelining* to overlap the execution of instructions and improve performance [HP11]. In *pipelining* each instruction is divided into different stages and a set of instructions are in various stages at any given time. This

<sup>&</sup>lt;sup>1</sup>A processor could be implemented on a single chip in CMOS. The same processor would require multiple chips in old vector machines.

concept allows instructions to be overlapped in a simultaneous fashion forming an example of *Instruction-Level Parallelism (ILP)*. ILP is a fundamental idea used by processors in order to take advantage of available parallelism in a sequential application.

There are a number of hardware techniques that extend the basic concept for pipelining such as dynamic multiple-issue (superscalar) execution, out-of-order execution, register renaming, speculative execution and branch prediction. In *superscalar* execution, the hardware components are replicated allowing multiple instructions to be launched in one clock cycle. *Out-of-order* execution allows instructions to be executed out of order as soon as their operands are available. Possible hazards can be avoided by register renaming. *Speculative* execution overcomes control dependencies by speculating on the outcome of branches and proceeds execution as if the guesses were correct. Underlying mechanisms are necessary in order to support incorrect speculations. *Branch prediction* allows the processor to fetch and execute instructions without waiting for the resolution of a branch condition.

The fact that transistors preserved Moore's trend (known as *Moore's Law* [Moo65]), that is, getting smaller and more numerous, enabled architects to add more memory, deeper pipelines, and promote in general techniques such as the ones explained above. Consequently single-thread performance was continuously improving.

### **1.2** The Rise of Multi-core Architectures

While more transistors enabled the evolution of more complex processor designs and higher clock rates, another factor was waiting its turn to put an end to this pattern: *power consumption*. The main source of power dissipation in CMOS technology is *dynamic power*. Power is calculated using the following formula [PH08]:

$$P = CV^2 f$$

where P is power dissipation, C is Capacitive Load, V is voltage, and f is the frequency the transistors switch. Frequency is a function of the clock rate and higher frequencies imply more power consumption. One obvious way to minimize power is to lower voltage. However, lowering voltage sufficiently for today's demands appears to cause static power dissipation due to leakage current that flows even when a transistor is off. A way to remedy this problem was to increase cooling or turn off parts of the chip not currently in use. Consequently, due to the high cost of power and cooling mechanisms, computer designers decided to explore different avenues in microprocessor performance. In order to effectively utilize the increasing number of transistors computer manufacturers were forced to turn to *Chip Multiprocessors (CMPs)*, where multiple *cores*<sup>2</sup> exist on the same chip. With the main reason being the *Power Wall* along with diminishing returns from complex superscalar designs the hunt for parallelism has shifted from instruction level into thread level (Thread-level Parallelism -TLP). Software developers cannot rely any more on the latest processor with higher clock speeds to improve their application performance. The parallelism token has now passed to the developers themselves. Applications must be structured in a specific way in order to take advantage of the multiple cores. Programmers must break down the application into independent parts in order to keep the hardware as busy as possible.

There are different ways parallelism can be expressed. Predominantly there are two models namely *shared-memory* and *message passing*. Message passing may be implemented by combining the power of multiple machines together forming a *cluster* and programming the application in a way so that data are communicated between different machines using messages. Famous libraries for programming that model include the *Message Passing Interface (MPI)* [For93]. Shared memory model usually refers to the multi-core machines where every core is sharing the same address space (apart from any local caches) and shared data must be protected by some *locking* primitive. Notable libraries for shared memory programming include Java<sup>TM</sup> threads and POSIX threads.

The rest of the discussion will be focused on shared-memory models. Threads will be treated as the main execution unit. Parallel programs are divided into parts that are in turn mapped to threads in order to execute in parallel on the available cores. The terms 'processor' and 'core' will be treated equally and used interchangeably throughout the discussion.

## **1.3 Challenges in Parallel Programming**

Since the computer industry is turning its attention towards multi-core architectures and clock speeds have reached an upper bound, parallel programming is gaining more momentum as it is the most prevalent way of speeding up an application. However,

<sup>&</sup>lt;sup>2</sup>Core is used more commonly nowadays to refer to a processor on the chip.

writing parallel applications, also known as *concurrent programming*, is a very challenging task compared to the sequential paradigm [OB96, MG99]. The following sections review some of the major challenges in concurrent programming.

#### **1.3.1** Discovering Available Parallelism

It is not always possible to express an application in parallel and even when it is the speedups are not guaranteed to grow linearly with the number of cores. A well known computer scientist noted that the maximum expected improvement depends on the fraction of the application that can be parallelized. For a program to enjoy linear speedups, the parallel fraction should comprise nearly 100% of the total application. If only 30% of the total application can be parallelized, then only that portion can observe speedups. The remaining 70% will still execute sequentially. This observation is commonly known as *Amdahl's law* [Amd67] and is expressed using the following formula:

speedup =

$$\frac{1}{(1-P)+\frac{P}{N}}$$

where *P* is the fraction of the job that can be executed in parallel and *N* the number of cores. Assuming that 1 is the time for a single core to complete the job, the parallel part takes P/N and the sequential part takes (1 - P). Therefore speedup is obtained as the ratio between the sequential (single core) time and parallel time.

#### **1.3.2 Reasoning about Shared Mutable Data**

Even when the parallel fraction is relatively large, the lunch is usually not given for free. In many cases programs rely on processing elements from a data structure such as an *array*, a *list*, or a *tree*. When the program is expressed as a parallel implementation, it is likely that a given data structure can be accessed by multiple threads simultaneously. Thus, the programmer must reason and decide how shared data are going to be accessed in a predictable way to maintain correctness of the results at all times. Usually this is accomplished by the use of *locks*, which are language synchronization primitives used to provide mutual exclusion of a critical section accessed by multiple threads.

#### **1.3.3** Optimizing for Performance

Even when a programmer is able to reason how to write the parallel code to execute correctly, there is still the performance issue. Below are some considerations that need to be taken into account if one wishes to optimize for performance.

#### Lock Granularity

The *granularity* of which locks are used can play a vital role on that. *Coarse-grained* locking granularity is simpler to use but offers limited concurrency whereas *fine-grained* locking offers better performance but sometimes at the cost of higher complexity [HS08]. Imagine for example a program where multiple threads access a shared list to add or remove elements from it. Under coarse-grain locking a thread might lock the entire list using a global lock (a lock that is responsible to lock the list and also it is shared among all threads) before modifying it. This is an extreme scenario and clearly it removes all concurrency. In fine-grain locking usually more than one lock is associated with different portions of the code (the list in this example) so threads must ensure that the correct locks are acquired and released to avoid *deadlocks*<sup>3</sup> or *livelocks*<sup>4</sup>.

#### **Task Granularity and Load Balancing**

The minimum execution time of the parallel portion of the algorithm is the length of the longest running parallel task (assuming *n* tasks running on *n* processors) [YHM<sup>+</sup>08]. While this implies formulating tasks as small as possible, they should be broken down to a minimum size that at least amortizes the cost of creating and managing them. When an application is broken down into multiple parts, an efficient scheduling mechanism is required that prevents situations where some cores are busy while others are idle. Such a situation can lead to performance losses due to inefficient utilization of the architecture. In this context, this phenomenon is known as *load imbalance*.

#### **Architectural Considerations**

To complicate even further the life of the programmer, cases where response time is critical or cases where all possible performance must be exploited, require the data structures to be designed in a way that takes into account the processor's cache. If a processor operates on a given memory location, it is also likely to access the nearby

<sup>&</sup>lt;sup>3</sup>In a deadlock, threads are waiting for each other to release a lock so neither can progress.

<sup>&</sup>lt;sup>4</sup>Livelock is similar to deadlock but threads involved might change in regard to one another.

location(s) as well. This is known as *spatial locality*. In order to take advantage of the spatial locality observation processors operate at larger portions of the cache (a group of neighboring words than just a single word) called *cache lines*. On the one hand spatial locality is desirable since the cache may hold a significant portion of the data accessed by a processor minimizing the accesses to main memory (which are slower than cache accesses). On the other hand placing data that might be accessed by multiple processors/threads nearby increases the possibility of *false sharing*. This occurs when processors access distinct data but still triggering a conflict because the data happens to lie in the same cache line. Furthermore, the size of the data objects accessed by a thread at a regular basis could be designed to reflect the size of the cache lines or local cache in general. This may prevent any performance losses due to misaligned accesses. Data objects could be aligned by a technique known as *padding* which adds some meaningless bytes between data objects so that they can fit at a memory offset equal to some multiple of the cache line. Moreover, since cache size changes from architecture to architecture, portability is lost (performance-wise due to optimization mismatch).

### **1.4 Automatic Parallelization**

The challenges explained above emphasize the difficulties in understanding and developing parallel programs, let alone debugging them since their runtime behavior might be non-deterministic.

#### **1.4.1** Manual and Automatic Parallelization

Despite the difficulties, this is the prevalent way to program in order to take advantage of what current architectures have to offer. Apart from having a programmer with parallel programming knowledge to perform the transformation from sequential to parallel manually, there is also the possibility of using a tool that can transform a sequential program into a parallel one automatically. Such tool is referred to as a *parallelizing compiler*. Although the easy way sounds appealing both methods, manual and automatic, have their advantages and disadvantages.

**Manual Parallelization** is usually superior than using an automatic tool [OB96]. The programmer not only can apply domain knowledge to the problem but also can

benefit from using profiling to guide the optimization. Profiling can help to find places that optimizing is more beneficial, or explain why some optimization might not work as efficient as expected. The obvious downside of manual parallelization is the time and effort required. The programmer may spend hours, days, or even months trying to parallelize the code and get the most out of it [OB96].

**Automatic parallelization** aims to automate the process of transforming a sequential application into a semantically equivalent parallel one. Automatic parallelization is still difficult but the burden moves from the developer to the parallelizing compiler engineer. One of the problems that arise from using a parallelizing compiler is that the output of the code might be almost unrecognizable from the sequential code and difficult to read [OB96]. That makes it difficult for the programmer to influence compiler decisions. Nevertheless, there has been work where *machine learning* was applied in order to replace traditional target-specific and inflexible heuristics for task scheduling with more sophisticated and adaptive decisions [TWFO09].

#### **1.4.2 Runtime Automatic Parallelization**

Traditionally automatic parallelization is performed *offline* (at compile time). This entails some form of data dependence analysis to decide whether the portions wished to be parallelized are independent, in terms of data accesses, from each other. Some notable parallelizing compilers include Polaris [BEF<sup>+</sup>95], SUIF [WFW<sup>+</sup>94], and Intel<sup>®</sup> C++ compiler.

Offline automatic parallelization is very effective with counted loops that manipulate array accesses with affine indices, where memory dependence analysis can be precisely performed. Although promising and inexpensive, in terms of application performance, offline automatic parallelization is sometimes limited mainly due to insufficient runtime information or the inability of the parallelizing compiler to perform the transformation due to complex inter-procedural relationships. For example, it is difficult to perform static dependence analysis on code that makes extensive use of pointers, which is typical for modern languages such as C++ or Java. More sophisticated memory dependence analysis (such as points-to analysis [NKH04]) can help, but parallelization often fails due to unresolved memory accesses. Also when subscripted subscripts are used to access array elements, the actual memory locations may not be available until runtime. Furthermore, loops with unknown number of iterations make it hard to parallelize since there is no information on how to schedule the loop (*e.g.* the loop might terminate abruptly due to a runtime condition). For these reasons *Speculative Parallelization* also known as *Thread-Level Speculation (TLS)*, a runtime technique for automatic parallelization has gained attention over the last few years. Speculative parallelization is designed to overcome the offline parallelization shortcomings at the expense of introducing additional runtime overheads. There is more detail regarding those overheads in the next section.

Both manual and automatic parallelization have their advantages and disadvantages as explained earlier. The focus of the discussion will be on automatic runtime parallelization and specifically using speculation.

## **1.5** Speculative Parallelization

#### **1.5.1** Phases of Speculative Parallelization

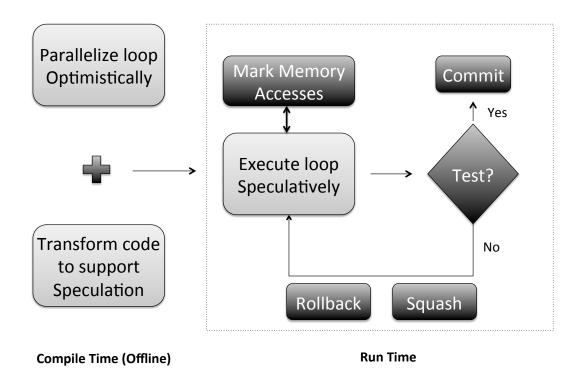

There are two main phases in speculative parallelization, as illustrated in Figure 1.1. The first phase takes place offline and the sequential program is optimistically (without knowing if the program will actually be parallelizable) transformed into a parallel one, assuming that the parallel execution will maintain the sequential semantics of the original program; *i.e.* no data dependencies.

Also, some extra code is inserted mainly to maintain meta-data that will facilitate in runtime tests that provide correctness. The second phase takes place at runtime. While the application executes, each parallel running thread collects and maintains information regarding all of its memory accesses. For example, any updates (stores) from a given thread are kept locally to that thread, instead of written immediately back to memory, until proven to be correct. Since those threads have not proven to be successful while still executing, they are called *speculative threads*. During, or at the end of speculative execution, an inspection phase takes place to ensure that there were no violations of the sequential semantics of the application (referred to as *test* in Figure 1.1). If a thread did not conflict with another, then it is safe to propagate its modifications back to memory, an action which is called *commit* in this context. Otherwise the offending thread has to *squash*, that is, discard any temporary (local) modifications and re-execute its code. When threads squash, a procedure initiates to ensure that those threads will undo their modifications properly and leave the memory state as it was before the squash occurred. This procedure is called *rollback*.

The focus of this discussion is on the runtime phase of Speculative Parallelization

Figure 1.1: Speculative parallelization phases.

and specifically on looking how to reduce the main overheads arising from such a system. The main overheads lie in the phases depicted with darker boxes in Figure 1.1. That is, marking memory accesses, testing for correctness, committing, squashing, and rollbacking.

#### **1.5.2** Performance Potentials of Speculative Parallelization

The performance potentials of speculative parallelization were assessed in a recent study [ISK<sup>+</sup>10] conducted in collaboration between the University of Edinburgh and the University of Manchester, work in which the author of this thesis was involved. The study evaluated a mixture of different design aspects of speculative parallelization in a simulation environment in order to establish an upper bound on performance. The goal was to offer an architecture-agnostic characterization of the potentials of speculative parallelization. Applications were tested from a variety of application domains (*e.g.*)

scientific and business domains) and programming styles (*e.g.* procedural and objectoriented styles). Implementation details regarding this study can be found in Appendix B.

#### Findings

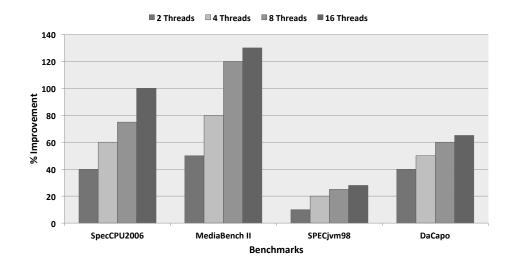

Figure 1.2 shows results from speculative loop parallelization (*i.e.* loop iterations are mapped into threads and execute speculatively) extracted from the limit study [ISK<sup>+</sup>10]. The *x* axis shows applications from four important benchmark suits. The *y* axis shows the average improvement percentage of speculative runtime parallelization over sequential runtime. That is, how much an application may improve when speculative parallelization is applied.

Figure 1.2: Speculative parallelization of various applications from four important benchmark suites. The graph shows the improvement percentage from speculative parallelization over sequential application runtime.

What is notable in the graph of Figure 1.2, is that the improvement does not seem to grow linearly with the number of threads. For instance, MediaBench II shows 50% improvement with 2 threads but only 130% improvement with 16 threads. Therefore, instead of showing about 8x more improvement for 8 threads, it is nearly 3x. A similar

pattern is observed with the other benchmarks as well. The key conclusion drawn from these experiments is that *most of the speculative parallelism can be exploited with a small number of threads*.

The topic of discussion is implementing software speculative parallelization systems optimized to reduce the overheads associated with this paradigm for a small number of threads.

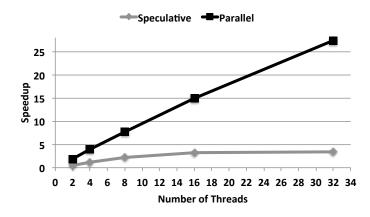

### **1.6** Motivation

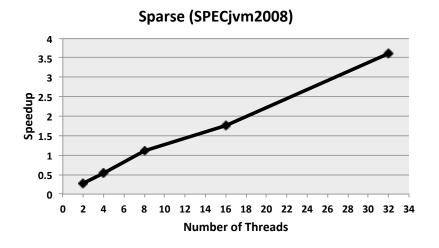

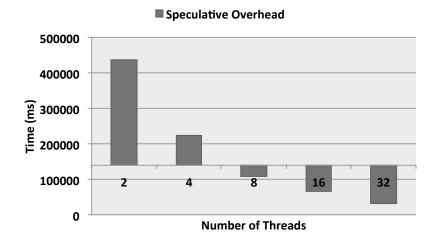

Previous work on *Speculative Parallelization (Thread-Level Speculation - TLS)* looked at hardware implementations [HWO98, OHL99, CMT00, MG02, CO03, SCZM05, PO05, JEV07, LPH<sup>+</sup>09, MLC<sup>+</sup>09, KRL<sup>+</sup>10] as well as in software [DYR02, CL05, OMH09, MHHM09, TFNG08, TFG10, RKM<sup>+</sup>10, KJL<sup>+</sup>12], just to name a few. However, no widely available architecture or compiler has incorporated Speculative Parallelization. Nonetheless, the published limit studies suggest that it could be profitable to use Speculative Parallelization [PZH<sup>+</sup>09, ISK<sup>+</sup>10], although research should focus on optimizing for a small number of threads. Motivated by this potential, experiments were conducted to verify whether this applies in a real machine, besides limit studies. Figure 1.3 shows the speedup results, up to 32 threads, of one of the new software TLS proposed in this thesis (MiniTLS; described in Chapter 4) for the Sparse Matrix Multiplication benchmark part of the SPECjvm2008 suite on a UltraSPARC T2 machine.

Figure 1.3: Speculative parallelization speedup over sequential for Sparse benchmark (SPECjvm2008).

Further details of the experiments appear in Chapter 6.

To this end, this thesis proposes two software speculative parallelization systems optimized to reduce the overheads associated with the TLS paradigm for a small number of threads. The next section elaborates further on the contributions of the thesis.

### **1.7 Contributions**

At a high level, there are two main design approaches that have been followed by the software speculative parallelization literature, in terms of how a system maintains its speculative state. These two approaches are known as *lazy* and *eager* version management. Chapter 2 explains both in detail. Two novel speculative parallelization systems are presented, one for each of these design directions. The contributions (Chapters 4, 5, and 6) are the following:

- A compact data structure to represent the dependency tracking for a speculative parallelization system (Chapter 4). The experiments show space overhead reduction of 5x on average compared to state-of-art approaches (Chapter 6).

- MiniTLS, a software speculative parallelization system for Java applications, that relies on eager memory data management, is presented (Chapter 4). Speculative threads modify directly data which needs rollback when misspeculation occurs. This eager treatment provides faster execution in the absence of data dependencies. Speculatively parallelized applications are able to run more than 4x faster on average than their sequential versions (Chapter 6).

- MiniTLS outperforms state-of-the-art software speculative parallelization systems by being nearly 2x faster and it is the first to parallelize the rollback process under Eager Version Management (Chapter 6).

- A second novel software speculative parallelization system, Lector, using lazy version management (Chapter 5). Compared with a state-of-the-art lazy speculative parallelization, Lector shows performance improvements on average of 1.7x faster (Chapter 6).

- A novel algorithm for accelerating TLS systems applicable to any type of implementation (Chapter 5). The results show that applying this technique, improves speedup on average 1.7x for 2 threads increasing close to 8.2x speedups with 32 threads (Chapter 6).

### **1.8 Publications**

The material of this thesis from Chapters 4, 5, and 6 appears in the following Journal publication:

• OPTIMIZING SOFTWARE RUNTIME SYSTEMS FOR SPECULATIVE PARALLELIZA-TION. **Paraskevas Yiapanis**, Demian Rosas-Ham, Gavin Brown, Mikel Luján. In *ACM Transactions on Architecture and Code Optimization (TACO)*, 9 (4), 39, January 2013.

#### **Other Related Publications**

- ARCHITECTURAL SUPPORT FOR EXPLOITING FINE GRAIN PARALLELISM. Demian Rosas-Ham, Isuru Herath, **Paraskevas Yiapanis**, Mikel Luján, Ian Watson. In *Proceedings of the 14<sup>th</sup> IEEE International Conference on High Performance Computing and Communications*, June 2012.

- TOWARD A MORE ACCURATE UNDERSTANDING OF THE LIMITS OF THE TLS EXECUTION PARADIGM. Nikolas Ioannou, Jeremy Singer, Salman Khan, Polychronis Xekalakis, **Paraskevas Yiapanis**, Adam Pocock, Gavin Brown, Mikel Luján, Ian Watson, Marcelo Cintra. In *Proceedings of the International Symposium on Workload Characterization (IISWC)*, December 2010.

- ONLINE NONSTATIONARY BOOSTING. Adam Pocock, **Paraskevas Yiapanis**, Jeremy Singer, Mikel Luján and Gavin Brown. In *Proceedings of the International Workshop on Multiple Classifier Systems (MCS)*, LNCS 5997, pp 205-214, 2010.

- STATIC JAVA PROGRAM FEATURES FOR INTELLIGENT SQUASH PREDICTION. Jeremy Singer, **Paraskevas Yiapanis**, Adam Pocock, Mikel Luján, Gavin Brown, Nikolas Ioannou, Marcelo Cintra. In *Proceedings of the 4<sup>th</sup> Workshop on Statistical and Machine Learning Approaches to Architecture and Compilation (SMART)*, January 2010.

- MINING STATIC FEATURES FOR SQUASH PREDICTION IN THREAD-LEVEL SPECULATION. **Paraskevas Yiapanis**, Jeremy Singer, Adam Pocock, Mikel Luján, Gavin Brown. In the 5<sup>th</sup> International Summer School on Advanced Computer Architecture and Compilation for Embedded Systems (ACACES), July 2009.

• FUNDAMENTAL NANO-PATTERNS TO CHARACTERIZE AND CLASSIFY JAVA METHODS. Jeremy Singer, Gavin Brown, Mikel Luján, Adam Pocock, **Paraskevas Viapanis**. In *Proceedings of the Workshop on Language Descriptions, Tools and Applications (LDTA)*, March 2009.

### **1.9** Thesis Structure

The rest of the thesis is organized as follows: Chapter 2 provides an introduction to runtime and speculative parallelization. The main design options when implementing such systems in software are also discussed. Chapter 3 elaborates, through related work, on advanced techniques for runtime parallelization with focus on speculative parallelization. Chapter 4 describes the first system, MiniTLS, as well as the novel parallel rollback algorithm. It is illustrated how advantage is taken of the information provided by speculative parallelization limit studies to optimize MiniTLS. Oancea et al. [OMH09] introduced a top performing software speculative parallelization work using eager memory management. Their contribution was how to eliminate any associated synchronization when accessing the data structures holding the dependency information. Oancea et al. [OMH09] traded-off increasing the size of the eager memory management data structures to remove synchronization and optimize performance. Hereafter, it is referred to the speculative parallelization software developed by Oancea et al. [OMH09] as SpLIP (SpLIP is described in detail in Appendix A). In the experiments the performance delivered by MiniTLS vs. SpLIP is compared directly (the experiments appear in Chapter 6). Chapter 5 describes the second system, Lector as well as the novel idea of using inspector threads in the role of helper threads. Lector is compared against TL2 [DSS06] in the performance results. Chapter 6 reports the speedup results as well as speculative operations and memory overhead comparisons using seven Java benchmarks, with three belonging to SPECjvm2008. Note that two of the seven benchmarks do include data-dependencies. Finally, Chapter 7 summarizes the thesis and presents potential future directions. The thesis includes also two appendices. Appendix A provides implementation details of the two baseline systems used in the experiments presented in Chapter 6: SpLIP [OMH09] and TL2 [DSS06]. Appendix B provides implementation details for the limit study on speculative parallelization mentioned in Chapter 1 (current chapter) from Ioannou et al. [ISK<sup>+</sup>10] conducted in collaboration between the University of Edinburgh and the University of Manchester.

| CHAPTER 1  | Introduction, Motivation, Contributions, Publications                |

|------------|----------------------------------------------------------------------|

| CHAPTER 2  | Fundamentals of Runtime Parallelization                              |

| CHAPTER 3  | Advances in Runtime Parallelization (including related work)         |

| CHAPTER 4  | MiniTLS: In-place Speculative Parallelization with Parallel Rollback |

| CHAPTER 5  | Lector: Reducing Speculative Overhead via Inspector Threads          |

| CHAPTER 6  | Experimental Results from MiniTLS and Lector                         |

| CHAPTER 7  | Conclusions, Future Work                                             |

| APPENDIX A | Baseline Implementation Details (SpLIP [OMH09] and TL2 [DSS06])      |

| APPENDIX B | TLS Limit Study [ISK <sup>+</sup> 10] Implementation Details         |

Table 1.1 shows concisely the structure of this thesis.

Table 1.1: Thesis structure.

30

## Chapter 2

# **Fundamentals of Runtime Parallelization**

### 2.1 Introduction

In recent years multicore chips became the standard configuration in commercial computing. In order to harness the power they have to offer, applications need to be structured in such a way that will yield efficient utilization of the available resources. Parallel programming accomplishes that by dividing the computation across the available processors (or threads), yet this process involves experienced software engineers in this type of programming model. A promising idea is to have the compiler automatically restructure a sequential program into a parallel version. Sometimes this is not possible due to insufficient information during offline compilation. A solution is to proceed with parallel execution speculatively until sufficient information is collected, providing mechanisms to maintain sequential program correctness. Such a solution is known under the names of *Speculative Parallelization*, *Thread-Level Speculation*, or *TLS* in short. All three terms will be used interchangeably throughout the rest of the chapter as well as the rest of the thesis.

This chapter explains speculative parallelization and its mechanics as well as the major design requirements for such an execution model. However, before examining speculative parallelization, the chapter begins with an overview of an earlier model for runtime parallelization. This model is identified as *Inspector/Executor*. A brief discussion to areas of similar interest as TLS, such as *Transactional Memory* and *Database Systems Transactions*, is also provided.

## 2.2 Inspector/Executor: An Overview

#### 2.2.1 Inspector/Executor

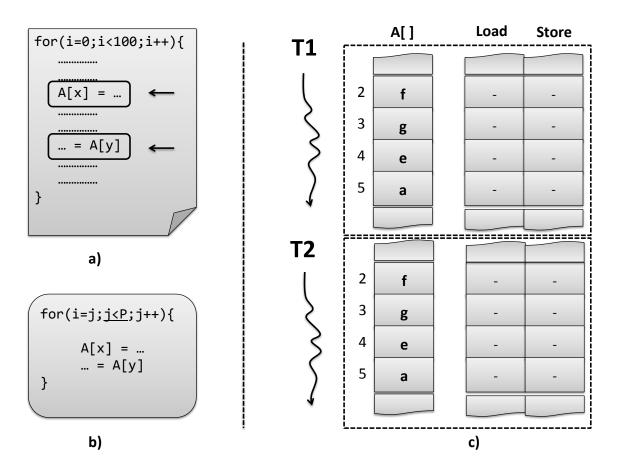

Early work on Runtime Parallelization involved a technique known in the literature as Inspector/Executor [ZY87, SMC89, SM91, SMC91, CTY94, RP94b]. As the name implies this method involves the generation of two versions of the loop to be parallelized during compilation. The first version, called *Inspector*, would simply execute a stripped version of the original loop that contains only accesses to shared mutable data, investigating whether the loop contains any data dependencies that prevent it from being parallelized. Figure 2.1a shows a candidate loop for parallelization. The assumption is that the memory accesses from variables x and y to locations of array A cannot be verified until runtime. Furthermore, the code surrounding the memory accesses to A (represented with dots in Figure 2.1a) does not perform any updates to locations shared across different iterations (it could be just because of the nature of the code or after some compiler transformation). The Inspector is not required to replicate all of the computation done by the original program (only memory accesses), and thus could be executed quicker. Figure 2.1b shows the stripped version of the code from Figure 2.1a that is required by the inspector. The stripped version of the loop will be replicated across multiple inspector threads and each thread will inspect a different portion of the *iteration space* (the set of loop iterations L, in this example 0 < L < 100and *i* is used to traverse the iteration space, where 0 < i < L).

#### 2.2.2 Inspector/Executor for Fully Parallel Loop Identification

One of the most notable *Inspector/Executor* models in the runtime parallelization literature was proposed by Rauchwerger and Padua [RP94b]. Their approach used the inspector to simply detect whether or not a loop is fully parallel. Such loops, are known as *DOALL* loops. In [RP94b] each inspector thread would be allocated its own portion (chunk of iterations) of the stripped version of the original loop (from j to P in Figure 2.1b, where from j to P is a chunk of iterations allocated to a specific thread). Each thread will also make use of some thread-local auxiliary data reflecting each memory location of A that can be accessed during parallelization (see Figure 2.1c). In this simplified version, each inspector thread will mark any loads or stores performed during the execution of its portion of iterations. A location in the thread-local auxiliary arrays *Load*[] or *Store*[] is marked to indicate the corresponding action by a particular thread.

At the end of the inspection phase, all inspector threads will check each others findings to ensure that the same memory location was not accessed by different threads in a way that violates the sequential semantics of the loop. For instance, if two threads perform a store at the same memory location but in the wrong order the resulting value would be unpredictable. The only valid way multiple threads can access the same memory location does not affect its value then threads are safe to read in any order they wish from there. The second version, called *Executor*, will execute the loop in parallel across multiple threads, given that the inspector version indicated so. Otherwise the loop will be executed sequentially.

Figure 2.1: a) A loop to be parallelized. b) Stripped-down version of the loop to be executed by the inspector threads. c) Auxiliary data to facilitate inspection.

#### 2.2.3 Earlier Work on Inspector/Executor

The focus of earlier attempts of the *Inspector/Executor*, such as the one proposed by Zhu and Yew [ZY87], was mainly on partially parallel loops and they were using the inspector phase to order the iterations in groups that contained parallel iterations. Within those groups, iterations could execute in parallel between them, but the groups themselves have to be separated using synchronization. Their scheme was divided in multiple stages with each stage including both an inspector and an executor. Every stage would gather information (inspection phase) of which iterations are allowed to execute in parallel without any conflicts and record this information into an auxiliary data structure. Then, the executor would execute those iterations in parallel with the aid of the auxiliary data structure. The next stage would do the same and the process would continue in a repetitive fashion until all iterations of the loop finish. Later work, such as Saltz *et al.* [SMC91], provide more optimized versions of the loop among processors and then reordering the iterations within each partition at runtime.

#### 2.2.4 Weakness

Clearly there are certain conditions that have to be met in order for this technique to work efficiently. The main drawback of this technique is that an adequate stripped version of the original loop is not always possible to be extracted. If the memory accesses to be analyzed during inspection constitute the majority of the loop's computation, the *Inspector* eventually executes nearly the same amount of computation as the *Executor* version [Rau98]. This was the main reason that led research towards speculative runtime parallelization.

### 2.3 Speculative Parallelization

#### 2.3.1 Brief Description

Assume, for the sake of the argument, that one wishes to parallelize the loop shown in Figure 2.2a. Similarly, assume that the array indexes cannot be resolved until runtime. That is, there is no feasible means of performing any static analysis (manual or automatic) to prove correct parallel executions by eliminating the possibility of data dependencies across threads. This can be the case for example, where i or j are the

result of accessing an indirection array. Therefore, standard parallelizing compilers must conservatively produce sequential code for the loop in order to guarantee correct execution. Consider now the instance of sequential execution shown in Figure 2.2b. Clearly the values populated for the array indexes did not yield any data dependencies amongst them, and thus, the compiler could have generated a parallel code such as the one in 2.2c and allow the application to run in parallel.

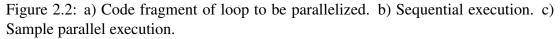

Speculative Parallelization (Thread-level Speculation - TLS), circumvents this conservatism by executing the threads (which are formed by loop iterations in this case) in parallel assuming that the run-time values of *i* and *j* will not trigger any cross-thread conflicts. For instance, in this case TLS would execute the loop iterations in parallel, while at the same time underlying mechanisms would monitor every speculative access to ensure that the parallel execution will produce the same results as if the program was executed sequentially. In addition, any memory updates are stored locally to the thread rather than written-back to main memory. Figure 2.3a shows the case where all speculative threads executed successfully and thus are allowed to *retire* or *commit* by propagating the buffered updates back to main memory. Sometimes we have the case of a memory dependency like the one shown in Figure 2.3b. In this case, a thread (or iteration) has loaded a value that was not produced by the correct store. This action causes a *Read-After-Write (RAW)* data dependence violation. As a result, the offending threads need to *squash* by initiating the *rollback* procedure (in this case discard any buffered updates) and re-execute in the correct order (see Figure 2.3c).

#### 2.3.2 Design Specification

Implementing the underlying mechanisms that will guarantee correct execution in TLS requires certain design decisions. From the brief description given above in Section 2.3.1 the main requirements for supporting speculative parallelization can be categorized as follows (also identified by Cintra and Llanos [CL03, CL05]):

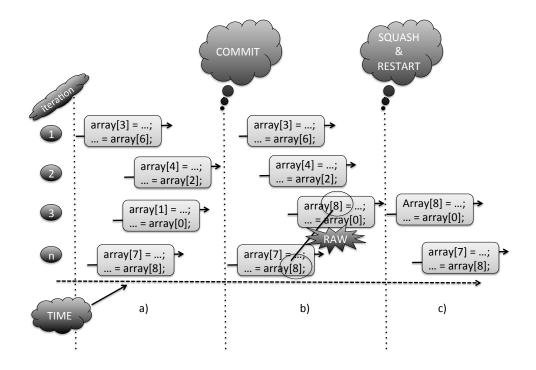

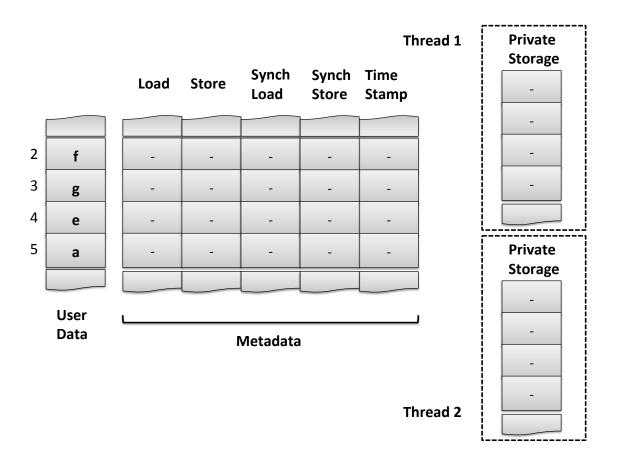

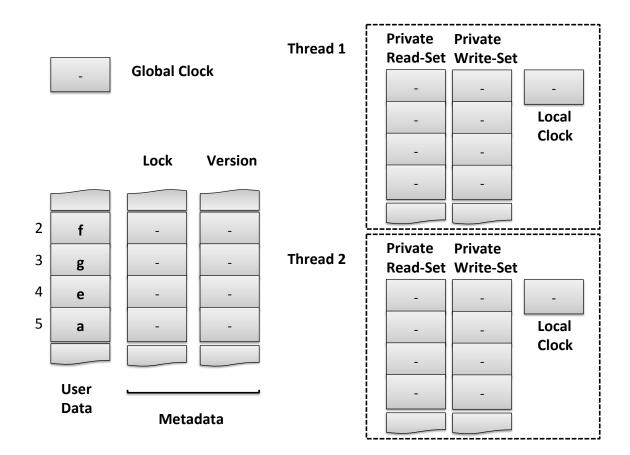

- **Metadata management.** A way to know which memory locations are accessed and by which threads. This will facilitate to identify whether or not any threads have accessed memory locations in a way that is not desirable.

- **Version management.** A way to manage speculative data. When threads execute speculatively, different versions of the data are produced. A mechanism is required to manage temporary (speculative) data and maintain consistency among operations.

- **Detect data dependence violations.** A way to identify potential data dependence violations.

- **Commit and rollback operations.** A way to maintain main memory at a correct state. That is, to be able to commit the correct values and rollback execution to a correct state when necessary.

- Scheduling speculative threads. An efficient way to schedule speculative work and threads.