# Self-Timed Logic and the Design of Self-Timed Adders

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2010

By

Balasubramanian Padmanabhan

**School of Computer Science**

## **Contents**

| Lis | t of Ta  | bles                                             | 6  |

|-----|----------|--------------------------------------------------|----|

| Lis | t of Fig | gures                                            | 8  |

| Glo | ssary (  | of Abbreviations                                 | 12 |

| Abs | stract   |                                                  | 20 |

| Dec | claratio | on                                               | 21 |

| Cor | pyright  | t                                                | 22 |

| _   | dication |                                                  | 23 |

|     |          |                                                  | 24 |

|     |          | edgements                                        |    |

| 1   | Intr     | roduction                                        | 25 |

|     | 1.1      | Motivation and Context                           | 28 |

|     | 1.2      | Research Contributions                           | 29 |

|     | 1.3      | Publications                                     | 30 |

|     | 1.4      | Structure of the Thesis                          | 31 |

| 2   | Fun      | ndamentals of Asynchronous Circuits              | 33 |

|     | 2.1      | Handshake Mechanism and Data Representation      | 33 |

|     | 2.2      | Bounded and Unbounded Delay Models               | 39 |

|     | 2.3      | C-element and Indicatability                     | 47 |

|     | 2.4      | Function Block – Definition and Characterisation | 52 |

|     | 2.5      | Summary                                          | 54 |

| 3   | Self     | E-Timed Combinational Logic                      | 55 |

|     | 3.1      | Seitz's Method.                                  | 57 |

|     | 3.2      | Singh's Approach                                 | 60 |

|     | 3.3      | Direct Logic and Reduced Direct Logic Styles     | 61 |

|     | 3.4      | Delay Insensitive Minterm Synthesis Technique    | 64 |

|     | 3.5      | Dual-Rail Combinational Logic                    | 66 |

|     | 3.6      | David et al.'s Approach                          | 67 |

|     | 3.7      | Toms' Approach                                   | 72 |

|   | 3.8  | Folco   | et al.'s Approach                                            | 75           |

|---|------|---------|--------------------------------------------------------------|--------------|

|   | 3.9  | Circui  | ts with Partial Acknowledgement                              | 79           |

|   | 3.10 | NCL 1   | Based Methods                                                | 81           |

|   |      | 3.10.1  | NCL_D Approach                                               | 84           |

|   |      | 3.10.2  | NCL_X Approach                                               | 86           |

|   |      | 3.10.3  | Block-Level Relaxation.                                      | 87           |

|   | 3.11 | Summ    | nary                                                         | 88           |

| 4 | Func | ction B | lock Realisation                                             | 90           |

|   | 4.1  | Termi   | nologies and Definitions                                     | 91           |

|   |      | 4.1.1   | Support Set and Dependency Set                               | 91           |

|   |      | 4.1.2   | Cubes Support Intersection Set and Cubes Dependency          | Intersection |

|   |      |         | Set                                                          | 92           |

|   |      | 4.1.3   | Cubes Relativity Set                                         | 92           |

|   |      | 4.1.4   | Variables Identification                                     | 92           |

|   | 4.2  | Ortho   | gonality and SI Decomposition                                | 93           |

|   |      | 4.2.1   | Mutual Orthogonality Set and Degree                          | 93           |

|   |      | 4.2.2   | Sum-of-Products and Orthogonal Sum-of-Products Forms         | 94           |

|   |      | 4.2.3   | Criteria for SI Decomposition                                | 94           |

|   |      | 4.2.4   | Primary and Secondary SI Cubes                               | 95           |

|   |      | 4.2.5   | Datapaths Employing 1-of-n Codes                             | 96           |

|   | 4.3  | Gener   | al Synthesis Models                                          | 98           |

|   |      | 4.3.1   | Architecture for Strongly Indicating Circuits                | 98           |

|   |      | 4.3.2   | Modifications to Suit Weak-Indication Timing Model           | 100          |

|   | 4.4  | Set Th  | neory Based Heuristic for Compact Realisation of Function Bl | ocks102      |

|   |      | 4.4.1   | Deriving MOSOP Expression from MSOP Expression               | 102          |

|   |      |         | 4.4.1.1 Support Set and Dependency Set                       | 104          |

|   |      |         | 4.4.1.2 CSI Set, CDI Set and Polarity Eliminated CDI Set     | 104          |

|   |      |         | 4.4.1.3 Describing Mutually Disjoint Cubes                   | 105          |

|   |      |         | 4.4.1.4 Disjoint Set and Degree of Disjointness              | 105          |

|   |      |         | 4.4.1.5 Deducing MDSOP Form                                  | 106          |

|   |      |         | 4.4.1.6 MDSOP Cost of Combinational Benchmarks               | 109          |

|   | 7 1  | Tree Constructs                                                         | 176 |

|---|------|-------------------------------------------------------------------------|-----|

| 7 | Self | -Timed Multi-Operand Addition                                           | 176 |

|   | 6.5  | Summary and Inferences                                                  | 173 |

|   | 6.4  | Evaluation with Four-Bit CLA Generator                                  | 170 |

|   | 6.3  | Evaluation with Two-Bit CLA Generator                                   | 168 |

|   |      |                                                                         |     |

|   |      | 6.2.2 Type 2 Architecture – Topology with Least Significant RCA Section |     |

|   |      | 6.2.1 Type 1 Architecture – Fundamental Topology                        |     |

|   | 6.2  | Section Carry Based CLA Architectures                                   |     |

|   | 6.1  | Background                                                              | 160 |

| 6 | Self | -Timed Section Carry Based Carry-Lookahead Adders                       | 159 |

|   | 5.6  | Summary                                                                 | 157 |

|   |      | 5.5.3 Impact on Dual-Bit Adders Adopting Heterogeneous Encoding         | 155 |

|   |      | 5.5.2 Impact on Dual-Bit Adders Utilising Dual-Rail Encoding            | 152 |

|   |      | 5.5.1 Impact on a Single-Bit Adder Based on Hybrid Input Encoding       | 151 |

|   | 5.5  | Redundant Logic Insertion                                               |     |

|   | 5.4  | Bottlenecks with Increase in Order                                      |     |

|   | 5.3  | Hybrid Adders                                                           |     |

|   |      | 5.2.2 Incorporating Heterogeneous Data Encoding                         |     |

|   |      | 5.2.1.3 Comparative Evaluation                                          |     |

|   |      | 5.2.1.2 Global Weak-Indication                                          |     |

|   |      | 5.2.1 Adopting Dual-Kan Data Encoding                                   |     |

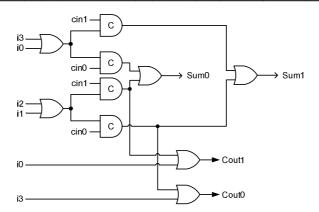

|   | 3.2  | Dual-Bit Adder Designs and Their Evaluation                             |     |

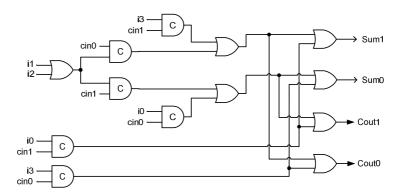

|   | 5.2  | 5.1.2 Employing Hybrid Input Data Encoding                              |     |

|   |      | 5.1.1 Using Dual-Rail Data Encoding                                     |     |

|   | 5.1  | Single-Bit Adders and Their Evaluation                                  |     |

| 5 |      | -Timed Carry-Ripple Adders                                              | 124 |

| _ | 4.5  | Summary                                                                 |     |

|   | 4.5  | 4.4.2 System Configuration                                              |     |

|   |      | 4.4.1.7 MOSOP Cost of Function Blocks                                   |     |

|   |      | 4.4.1.7 MOSOD Cost of Function Pleaks                                   | 112 |

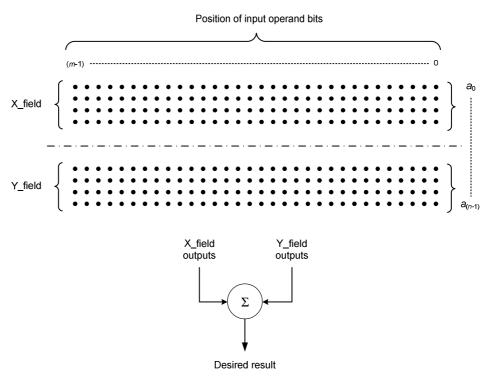

|          | 7.2    | Bit-Partitioning Scheme                           | 178 |

|----------|--------|---------------------------------------------------|-----|

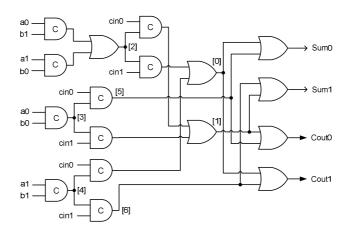

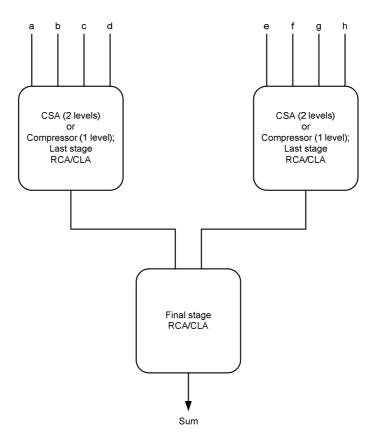

|          |        | 7.2.1 CSA Based Multi-Operand Addition            | 180 |

|          |        | 7.2.2 Compressor Based Multi-Operand Addition     | 181 |

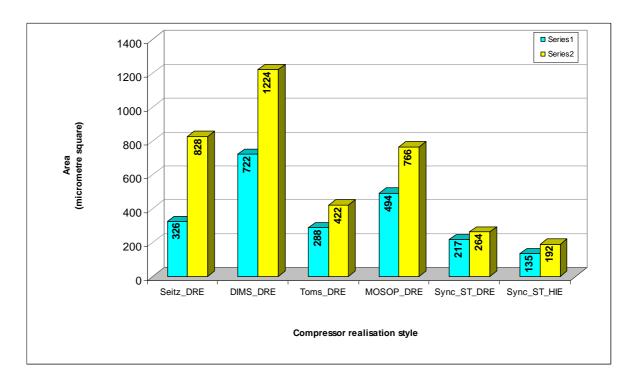

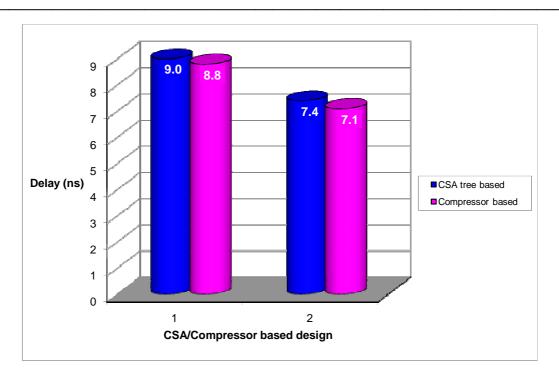

|          | 7.3    | Evaluation and Comparison                         | 184 |

|          | 7.4    | Summary and Inferences                            | 188 |

| 8        | Con    | nclusions and Scope for Further Work              | 192 |

|          | 8.1    | Summarising the Thesis Contributions              | 192 |

|          | 8.2    | Multi-Level Synthesis of Weak-Indication Circuits | 195 |

| Refe     | erence | es                                                | 198 |

| Appendix |        | 214                                               |     |

## **List of Tables**

| 2.1  | Data representation in dual-rail and 1-of-4 encoding schemes                         |

|------|--------------------------------------------------------------------------------------|

| 4.1  | SOP and DSOP cubes for some combinational benchmarks, generated by                   |

|      | Espresso                                                                             |

| 4.2  | DSOP cubes of various combinational benchmarks corresponding to different            |

|      | methods                                                                              |

| 4.3  | Cost of ST realisation of combinational benchmark functions                          |

| 4.4  | Delay, area and power metrics corresponding to different approaches for implementing |

|      | C17 function block                                                                   |

| 4.5  | Delay, area and power metrics corresponding to different ST approaches for realising |

|      | 32:1 MUX function block                                                              |

| 4.6  | Delay, area and power corresponding to different ST approaches for realising 1:32    |

|      | DEMUX function block                                                                 |

| 5.1  | Delay and area metrics corresponding to different 32-bit ST RCAs130                  |

| 5.2  | Listing critical path elements of the various ST RCAs                                |

| 5.3  | Delay, area and power metrics of 32-bit ST RCAs incorporating HIE                    |

| 5.4  | Delay, area and power of various dual-rail dual-bit adder based 32-bit ST            |

|      | RCAs142                                                                              |

| 5.5  | Delay, area and power parameters of heterogeneously encoded 32-bit ST RCAs           |

|      | incorporating DB adders (with extra logic)146                                        |

| 5.6  | Delay, area and power parameters of 32-bit heterogeneously encoded ST RCAs           |

|      | (without extra logic)147                                                             |

| 5.7  | Delay, area and power metrics of 32-bit dual-rail encoded hybrid ST RCAs148          |

| 5.8  | Delay, area and power metrics of dual-bit and triple-bit adder based 48-bit ST       |

|      | RCAs                                                                                 |

| 5.9  | Comparing delay, area and power parameters of redundant and non-redundant 32-bit     |

|      | hybrid input encoded ST RCAs                                                         |

| 5.10 | Comparing delay and area metrics of redundant and non-redundant logic dual-bit adder |

|      | based 32-bit ST RCAs employing DRE                                                   |

| 5.11 | Comparing delay, area and power of hybrid and non-hybrid DSSC_CCAO_globa             |

|------|--------------------------------------------------------------------------------------|

|      | adder incorporating redundant logic, evaluated using a 32-bit ST RCA                 |

|      | structure                                                                            |

| 5.12 | Delay, area and power of NRL and RL dual-bit adder based 32-bit ST RCAs with         |

|      | HE156                                                                                |

| 5.13 | Reference text for various ST adder blocks                                           |

| 6.1  | Delay, area and power for 32-bit ST addition based on Type 1 topology with 2-bit     |

|      | CLA                                                                                  |

| 6.2  | Delay, area and power parameters of 32-bit ST addition based on Type 2 adder         |

|      | architecture with two-bit SCBCLA                                                     |

| 6.3  | Delay, area and power for 32-bit ST addition based on Type 2 adder architecture with |

|      | two-bit CLA and RCA topology corresponding to Seitz, DIMS and Toms                   |

|      | methods                                                                              |

| 6.4  | Delay, area and power metrics for 32-bit ST addition based on Type1, Type 2 and      |

|      | Hybrid adder architectures with four-bit SCBCLA logic172                             |

| 6.5  | Comparing ST ripple carry and hybrid CLA adders in terms of delay and area           |

|      | components for different word widths                                                 |

| 6.6  | Comparing ST ripple carry and hybrid CLA adders in terms of power dissipation for    |

|      | different word widths175                                                             |

| 7.1  | Delay, area and power parameters corresponding to bit-partitioned CSA based ST       |

|      | addition of 8 input operands, each of size 32 bits                                   |

| 7.2  | Delay, area and power metrics corresponding to bit-partitioned compressor based ST   |

|      | addition of 8 input operands, each of size 32 bits                                   |

| 7.3  | Area and power figures for bit-partitioned ST addition of 8 inputs, each of width 32 |

|      | bits, using RCAs and CLA adders                                                      |

## **List of Figures**

| 1.1  | A typical synchronous system stage                                                      | 25 |

|------|-----------------------------------------------------------------------------------------|----|

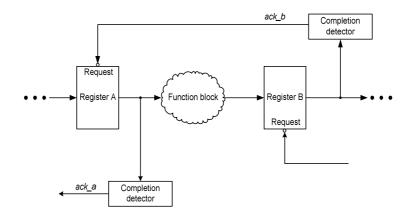

| 1.2  | A typical asynchronous system stage                                                     | 29 |

| 2.1  | Bundled-data encoding and 2-phase handshaking                                           | 34 |

| 2.2  | Timing diagram of a 2-phase handshake protocol [71]                                     | 34 |

| 2.3  | Delay-insensitive (dual-rail) data encoding and 4-phase handshaking                     | 35 |

| 2.4  | Timing diagram of a 4-phase handshake discipline [71]                                   | 36 |

| 2.5  | Fundamental mode system configuration                                                   | 40 |

| 2.6  | Illustration of isochronic fork assumption with respect to a primary gate input         | 44 |

| 2.7  | Illustration of DI, QDI and SI delay models                                             | 45 |

| 2.8  | Schematic, specification and circuit realisation of a 2-input C-element                 | 47 |

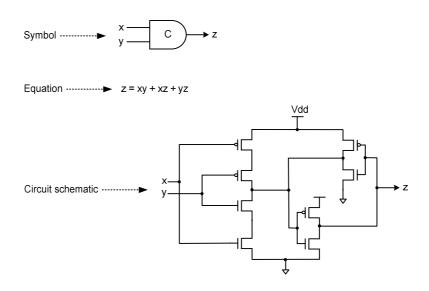

| 2.9  | Different gate level implementations of a 2-input Muller element                        | 49 |

| 2.10 | Different gate level implementations of a 3-input Muller element                        | 51 |

| 2.11 | Gate level realisation of a 4-input Muller element                                      | 52 |

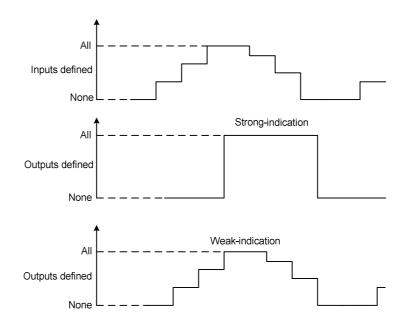

| 2.12 | Depicting strong and weak-indication phenomena                                          | 54 |

| 3.1  | Enumerating the state space based on input order                                        | 56 |

| 3.2  | Seitz's strong-indication full adder                                                    | 59 |

| 3.3  | Seitz's weak-indication full adder                                                      | 60 |

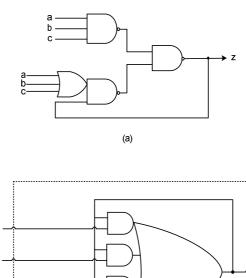

| 3.4  | Realisation of a 4-input AND gate based on Singh's approach                             | 61 |

| 3.5  | 2-input AND gate based on direct logic style                                            | 62 |

| 3.6  | Martin's full adder (reduced direct logic style)                                        | 63 |

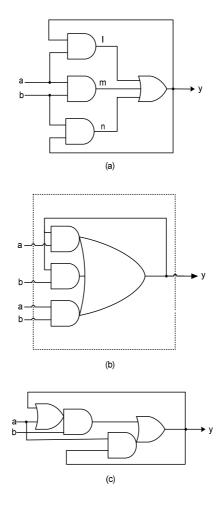

| 3.7  | Hazards due to naïve decomposition of a C-gate                                          | 64 |

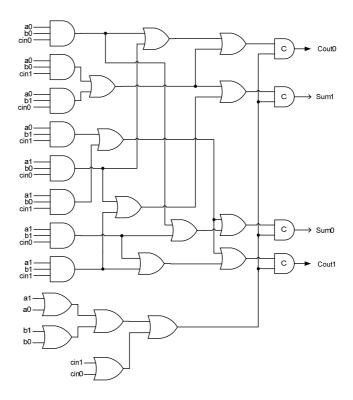

| 3.8  | Strong-indication full adder based on DIMS approach                                     | 65 |

| 3.9  | Weak-indication full adder based on DIMS approach                                       | 65 |

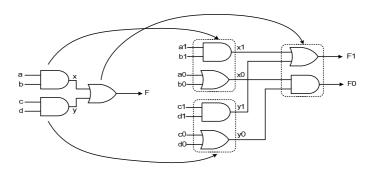

| 3.10 | DRCL realisation of $F = ab + cd$                                                       | 67 |

| 3.11 | Realising $X = a'b'c + abc'$ and $Y = a'bc' + ab'c$ using David et al.'s method         | 70 |

| 3.12 | Weakly indicating realisation, based on modifications to David et al.'s method          | 71 |

| 3.13 | Full adder synthesised using Toms' approach                                             | 75 |

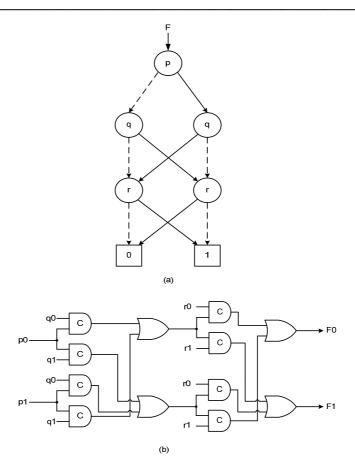

| 3.14 | BDD and circuit solution for $F = (p \oplus q \oplus r)$ based on Folco et al.'s method | 77 |

| 3.15 | Full adder synthesised using Folco et al.'s approach                                    | 79 |

| 3.16 | Implementing a multi-output circuit on the basis of partial acknowledgement81     |

|------|-----------------------------------------------------------------------------------|

| 3.17 | Static CMOS M-of-N implementation for $Z = ab + cd$ 83                            |

| 3.18 | NCL_D system configuration [126] [127]84                                          |

| 3.19 | NCL_D based logic equivalent for the function, $Z = ab + cd$ 85                   |

| 3.20 | NCL_X system configuration [127]86                                                |

| 3.21 | NCL_X equivalent for the function, $Z = ab + cd$ 87                               |

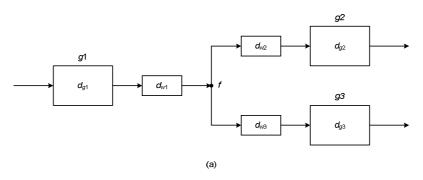

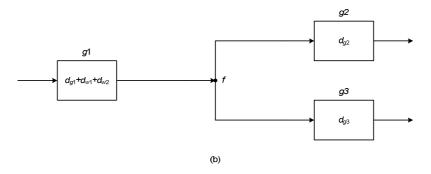

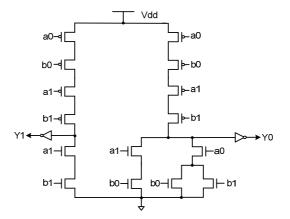

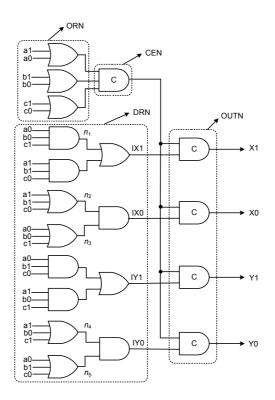

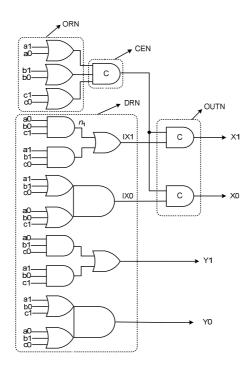

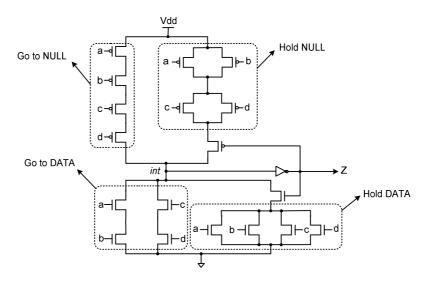

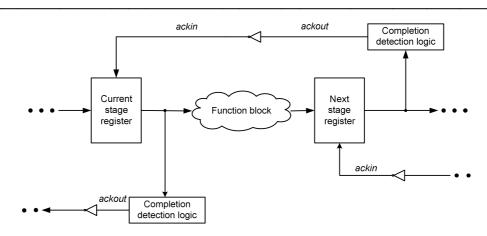

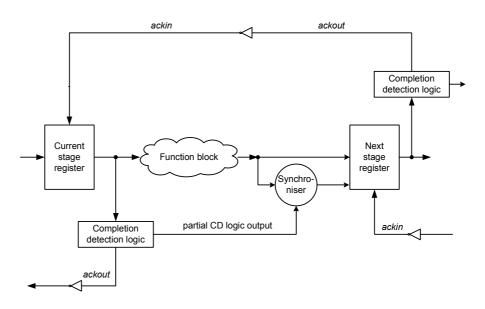

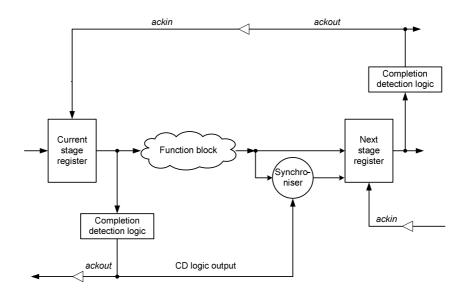

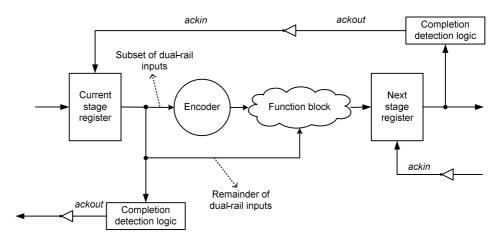

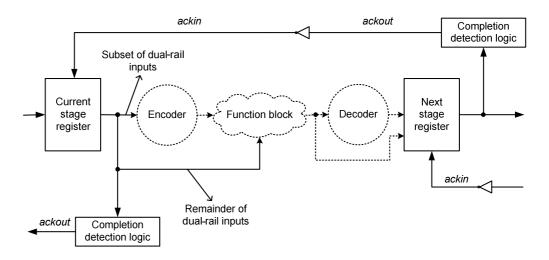

| 4.1  | Typical ST system configuration                                                   |

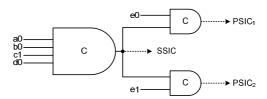

| 4.2  | Depicting PSICs and SSIC99                                                        |

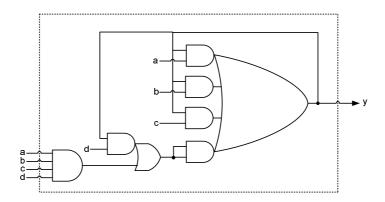

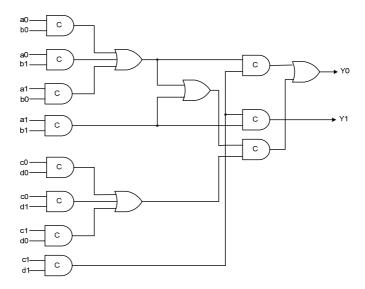

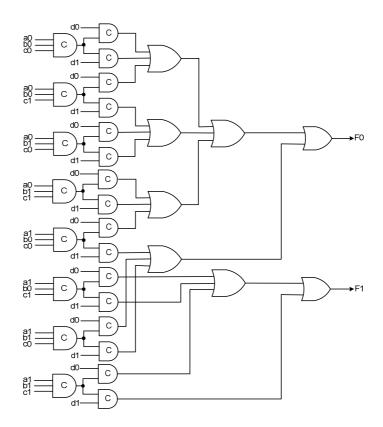

| 4.3  | SI decomposed strongly indicating realisation of <i>check</i> function block100   |

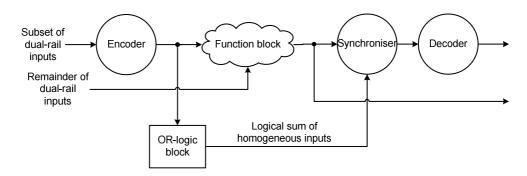

| 4.4  | System architecture for weak-indication circuits                                  |

| 4.5  | Cube-variable support matrix of SOP form of <i>newtag</i> , based on Espresso110  |

| 4.6  | Cube-variable support matrix of DSOP form of <i>newtag</i> , based on Espresso110 |

| 4.7  | Cube-variable support matrix of DSOP form of newtag, based on the MDSOP           |

|      | heuristic                                                                         |

| 4.8  | System topology in support of the proposed MOSOP heuristic for function           |

|      | blocks                                                                            |

| 4.9  | Illustrating CD of intermediate outputs for MUX logic tree based on Seitz's       |

|      | method                                                                            |

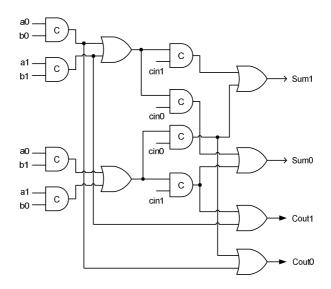

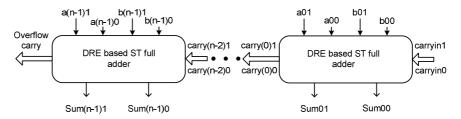

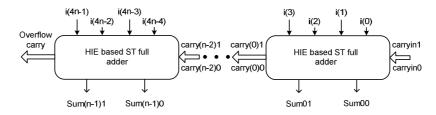

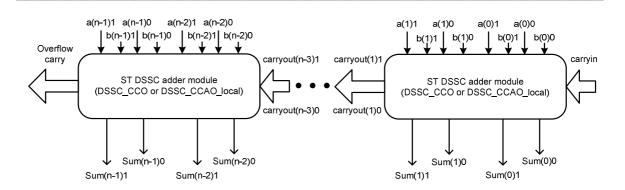

| 5.1  | <i>n</i> -bit dual-rail encoded ST carry-ripple adder architecture127             |

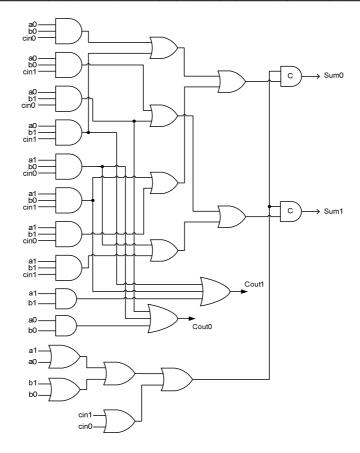

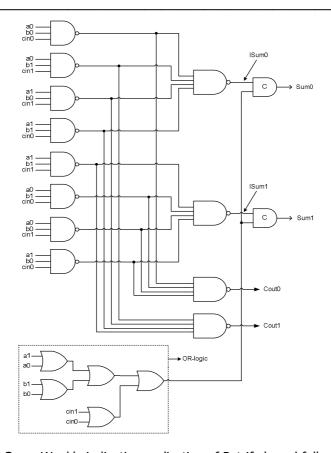

| 5.2  | Weakly indicating realisation of Petrify based full adder block                   |

| 5.3  | Proposed weak-indication full adder module                                        |

| 5.4  | Architecture of the <i>n</i> -bit hybrid input encoded ST RCA                     |

| 5.5  | Hybrid input encoded full adder based on Toms' approach                           |

| 5.6  | Proposed hybrid input encoded full adder block                                    |

| 5.7  | ST system architecture highlighting input protocol conversion and data            |

|      | processing                                                                        |

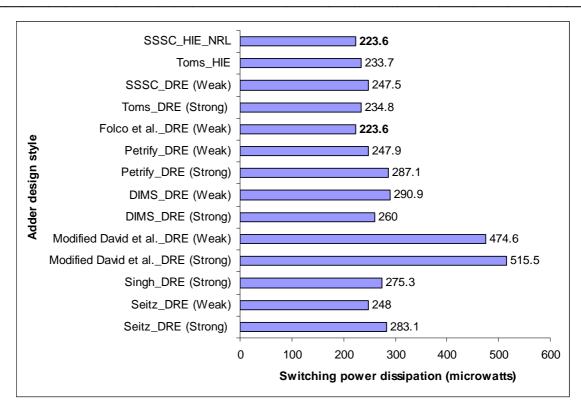

| 5.8  | Analysis of switching power dissipation of various 32-bit ST RCAs135              |

| 5.9  | Dual-rail encoded <i>n</i> -bit carry-ripple adder architecture featuring local   |

|      | indication                                                                        |

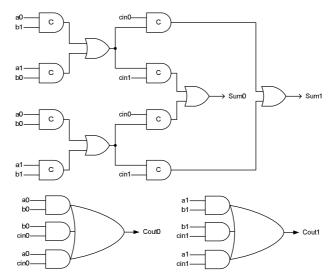

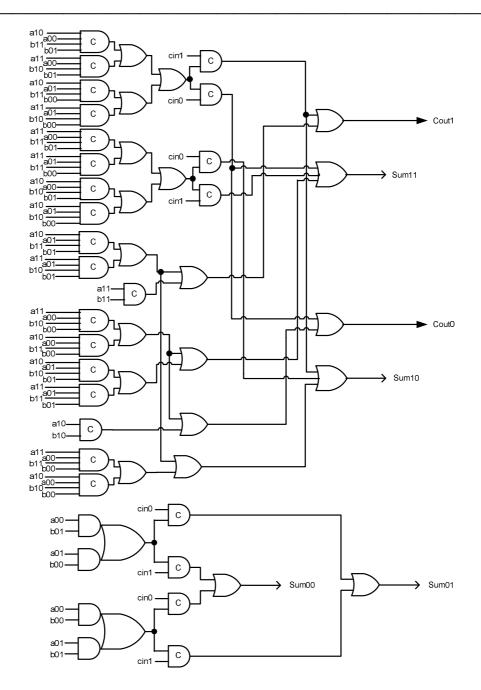

| 5.10 | Weak-indication DSSC_CCO adder module                                             |

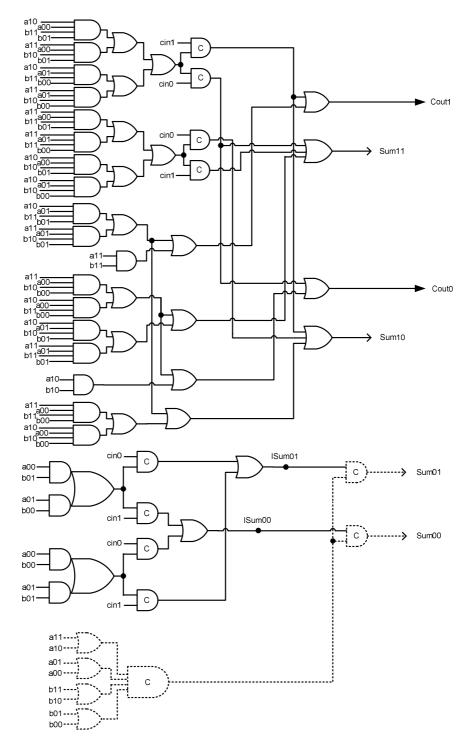

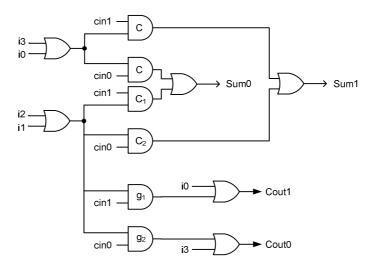

| 5.11 | Weakly indicating DSSC_CCAO_local adder block                                     |

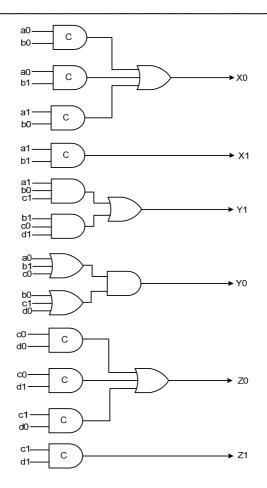

| 5.12 | DSSC_CCAO_global adder module                                                         |

|------|---------------------------------------------------------------------------------------|

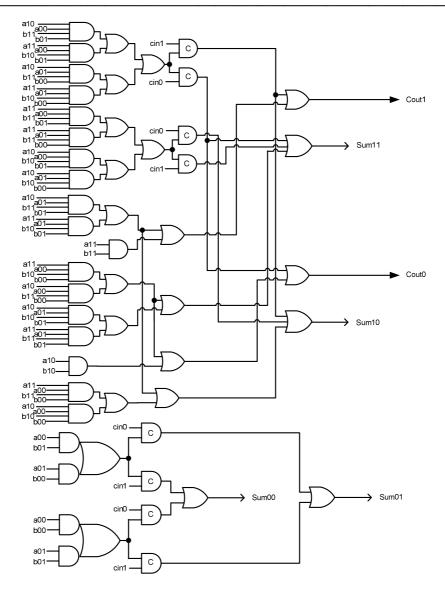

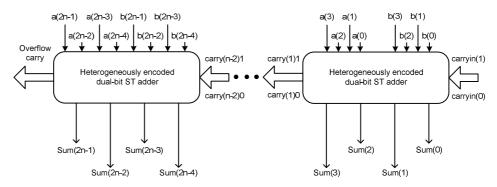

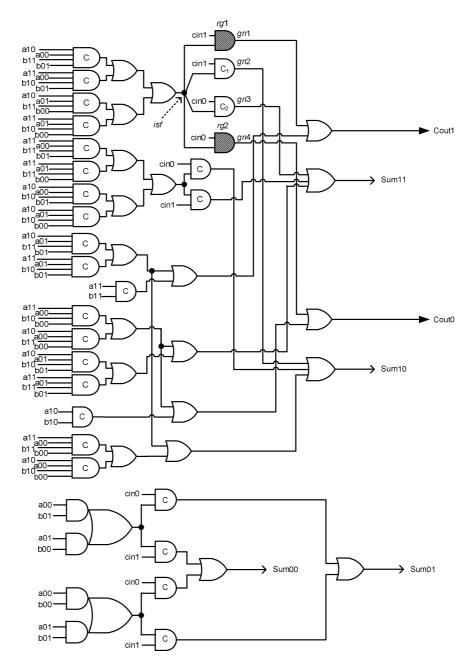

| 5.13 | Heterogeneously encoded dual-bit adder block based <i>n</i> -bit ST RCA structure144  |

| 5.14 | Weakly indicating heterogeneously encoded dual-bit adder module, corresponding to     |

|      | local indication144                                                                   |

| 5.15 | ST system configuration handling heterogeneously encoded inputs and                   |

|      | outputs                                                                               |

| 5.16 | Modifications to the ST system configuration handling heterogeneously encoded         |

|      | inputs and outputs to pave the way for global indication                              |

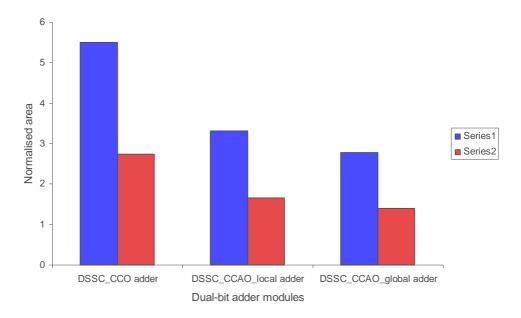

| 5.17 | Highlighting the area expense of dual-bit adder blocks in comparison with single-bit  |

|      | adder modules148                                                                      |

| 5.18 | Hybrid input encoded ST full adder with logic redundancy                              |

| 5.19 | Showing redundant logic insertion in DSSC_CCO adder module                            |

| 5.20 | Highlighting redundant logic insertion in DB_HE_local adder module156                 |

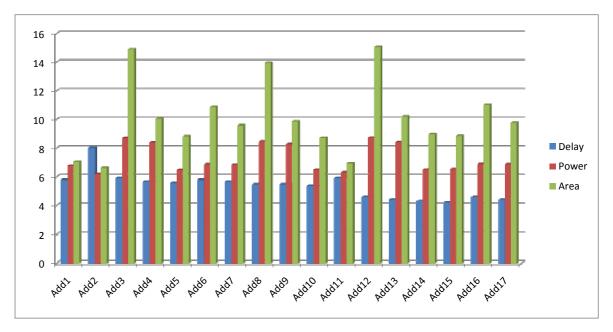

| 5.21 | Depicting the delay, power and area metrics of various ST adder blocks for performing |

|      | 32-bit addition based on the RCA topology                                             |

| 6.1  | Carry output description using generate and propagate signals                         |

| 6.2  | Output carry representation on the basis of generate, propagate and kill              |

|      | functions                                                                             |

| 6.3  | Carry output representation assuming $P = a+b$                                        |

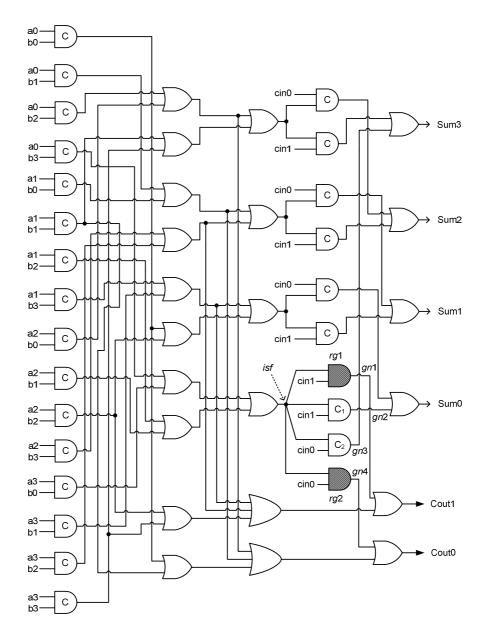

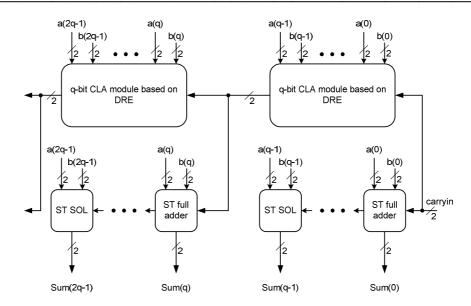

| 6.4  | Type 1 ST section carry based CLA adder architecture based on DRE165                  |

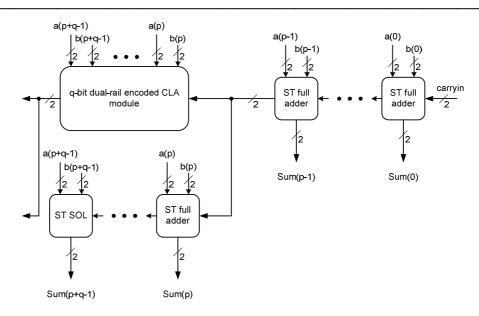

| 6.5  | Type 1 ST section carry based CLA adder architecture based on HIE166                  |

| 6.6  | Type 2 ST section carry based CLA adder topology based on DRE                         |

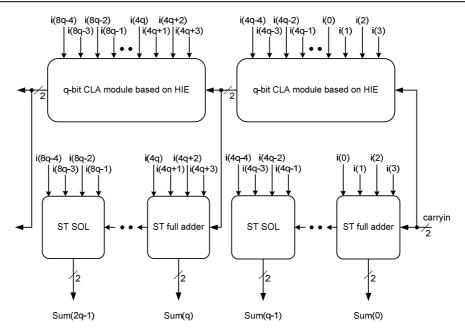

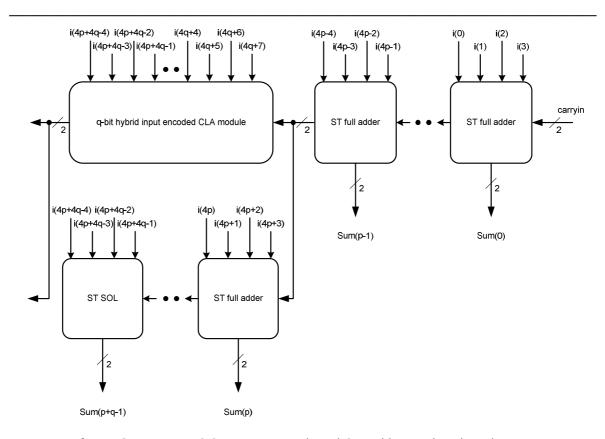

| 6.7  | Type 2 ST section carry based CLA adder topology based on HIE168                      |

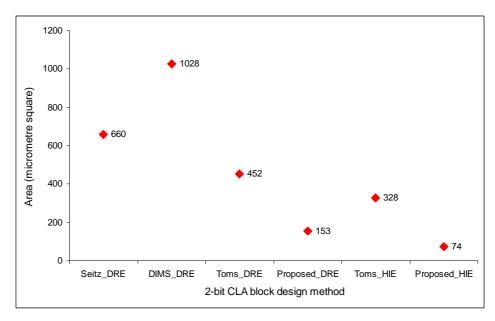

| 6.8  | Relative comparison of area occupancy of two-bit CLA module designs169                |

| 6.9  | Highlighting the merit of HIE CLA adder topology over HIE RCA topology with           |

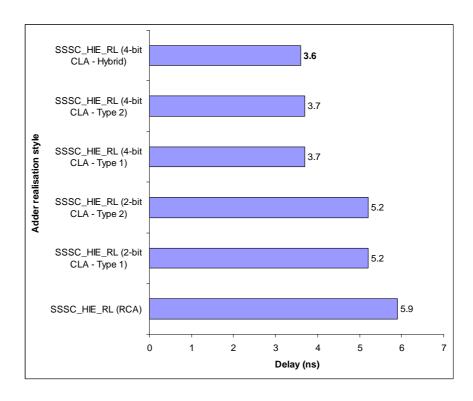

|      | respect to delay parameter                                                            |

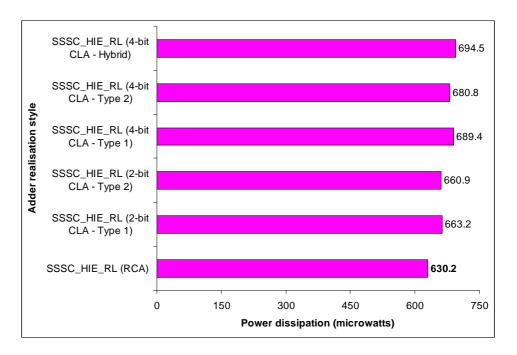

| 6.10 | Portraying the power increase of HIE CLA adder architecture in comparison with HIE    |

|      | RCA architecture                                                                      |

| 7.1  | Illustration of bit-partitioned multi-input addition scheme                           |

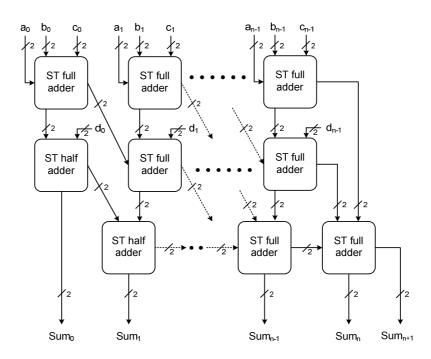

| 7.2  | ST version of a typical <i>n</i> -bit CSA for adding four operands                    |

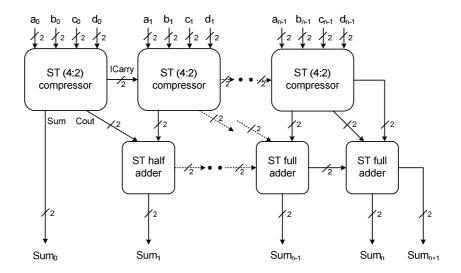

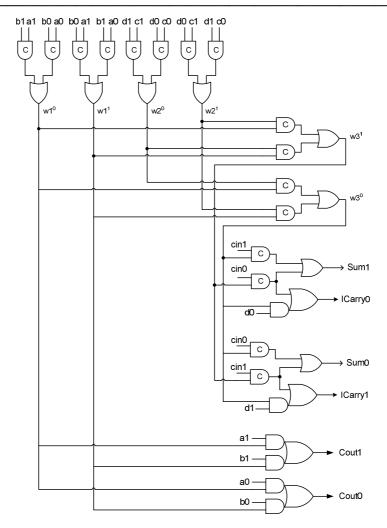

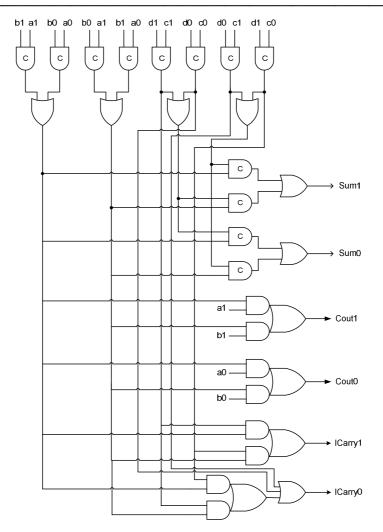

| 7.3  | ST logic compressor based multi-input adder to add four operands 181                  |

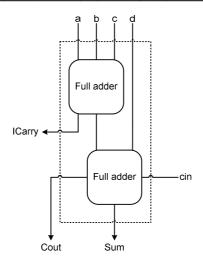

| 7.4  | A synchronous (4:2) logic compressor implemented using two full adders182            |

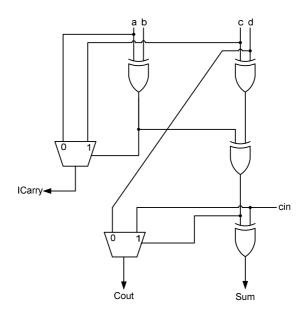

|------|--------------------------------------------------------------------------------------|

| 7.5  | A synchronous (4:2) compressor design based on discrete gates                        |

| 7.6  | ST (4:2) logic compressor block with carry input                                     |

| 7.7  | ST (4:2) logic compressor module without input carry                                 |

| 7.8  | Area comparison of ST (4:2) compressors realised using different methods188          |

| 7.9  | Describing positioning of CLA adders as a replacement for RCAs in the multi-operand  |

|      | adder                                                                                |

| 7.10 | Latency metrics for CLA adders and carry-ripple adders to perform bit-partitioned ST |

|      | addition of 8 inputs, each of width 32 bits190                                       |

## **Glossary of Abbreviations**

#### **General Acronyms:**

```

ack – Acknowledgement (signal)

```

ALU - Arithmetic and Logic Unit

AND2 – 2-input AND gate

**AND3** – 3-input AND gate

AND4 – 4-input AND gate

AO222 – Complex gate implementing the function, F = AB + CD + EF

AO2222 – Complex gate implementing the function, F = AB + CD + EF + GH

**BDD** – Binary Decision Diagram

**CAD** – Computer-Aided Design

**CD** – Completion Detection

**CDI** – Cubes Dependency Intersection (set)

**CDI**<sub>PE</sub> – Polarity Eliminated Cubes Dependency Intersection (set)

**CE2** – 2-input C-element

CE3 – 3-input C-element

CE4 – 4-input C-element

**CEN** – C-element Network

**CMOS** – Complementary Metal Oxide Semiconductor

**CR** – Cubes Relativity (set)

**CSI** – Cubes Support Intersection (set)

**DAG** – Directed Acyclic Graph

**D**(C) – Dependency set of a cube, C

**DDJ** – Degree of Disjointness

**DEMUX** – Demultiplexer

**DI** – Delay-Insensitive

**DIMS** – Delay-Insensitive Minterm Synthesis

**DJ** – Disjoint (set)

**DMO** – Degree of Mutual Orthogonality

**DRCL** – Dual-Rail Combinational Logic

**DRE** – Dual-Rail Encoding

**DRN** – Dual-Rail Network

**DSOP** – Disjoint Sum of Products

ITRS – International Technology Roadmap for Semiconductors

LI – Literals Identification

MDD – Multi-valued Decision Diagram

**MDSOP** – Minimum Disjoint Sum-of-Products

MIMO – Multiple-Input Multiple-Output

**MO** – Mutual Orthogonality (set)

MOSOP – Minimum Orthogonal Sum-of-Products

**MSOP** – Minimum Sum-of-Products

**MUX** – Multiplexer

NCL – Null Convention Logic

NCL\_D - Null Convention Logic utilising DIMS technique

NCL\_X – Null Convention Logic with Explicit Completion Detection

nMOS – n-type Metal Oxide Semiconductor

**OBDD** – Ordered Binary Decision Diagram

**OR2** – 2-input OR gate

**OR3** – 3-input OR gate

**ORN** – OR-gates Network

**OSOP** – Orthogonal Sum-of-Products

**OUTN** – Output Network

**PLA** – Programmable Logic Array

**pMOS** – p-type Metal Oxide Semiconductor

**PSIC** – Primary Speed-Independent Cube

**QDI** – Quasi-Delay-Insensitive

req – Request (signal)

**RISC** – Reduced Instruction Set Computer

**ROBDD** – Reduced Ordered Binary Decision Diagram

**RTZ** – Return-To-Zero

**SBDD** – Shared Binary Decision Diagram

S(C) – Support set of a cube, C

**SI** – Speed-Independent

SIA – Semiconductor Industry Association

**SIC** – Speed-Independent Cube

**SIMCAO** – Strongly Indicating MUX with C-elements, AND gates and OR gates

**SIMCO** – Strongly Indicating MUX with C-elements and OR gates

**SOP** – Sum-of-Products

SSIC – Secondary Speed-Independent Cube

**ST** – Self-Timed

**VI** – Variables Identification

WIDCAO – Weakly Indicating DEMUX with C-elements, AND gates and OR gates

**WIDCO** – Weakly Indicating DEMUX with C-elements and OR gates

#### **Adder Acronyms:**

**CCSA** – Carry Completion Sensing Adder

**CLA** – Carry-Lookahead (adder)

**Compressor based (with RCAs)** – Bit-partitioned multi-operand adder employing compressors for the input field partitions with RCAs constituting the final stage of the partitions as well as the final multi-operand adder stage

**Compressor based (with CLA adders)** – Bit-partitioned multi-operand adder employing compressors for the input field partitions with CLA adders constituting the final stage of the partitions as well as the final multi-operand adder stage

**CPA** – Carry-propagate Adder

**CSA** – Carry Save Adder

**CSA tree based (with CLA adders)** – Bit-partitioned multi-operand adder employing CSA tree structures for the partitions with CLA adders constituting the final stage of the partitions as well as the final multi-operand adder stage

CSA tree based (with RCAs) – Bit-partitioned multi-operand adder employing CSA tree structures for the partitions with RCAs constituting the final stage of the partitions as well as the final multi-operand adder stage

**DB** – Dual-Bit

**DB\_HE\_global** – Dual-bit (adder) based on heterogeneous encoding corresponding to global weak-indication

**DB\_HE\_local** – Dual-bit (adder) based on heterogeneous encoding corresponding to local weak-indication

**Decomposed\_DIMS\_DSSC** – Dual-bit adder based on the speed-independent decomposed version of DIMS approach that adopts dual-rail encoding

**DIMS\_compressor\_DRE** – (4:2) logic compressor design based on the speed-independent decomposition of DIMS solution, utilising dual-rail encoding

**DIMS\_DRE** (strong) – Single-bit strong-indication adder based on DIMS approach adopting dual-rail data encoding

**DIMS\_DRE** (weak) – Single-bit weak-indication adder based on DIMS approach adopting dual-rail data encoding

**DSSC** – Dual-Sum Single-Carry (adder)

**DSSC\_CCAO\_global** – Dual-Sum Single-Carry (adder) with C-elements, Complex gates, AND gates and OR gates corresponding to global weak-indication

**DSSC\_CCAO\_local** – Dual-Sum Single-Carry (adder) with C-elements, Complex gates, AND gates and OR gates corresponding to local weak-indication

**DSSC\_CCO** – Dual-Sum Single-Carry (adder) with C-elements, Complex gates and OR gates **Folco et al.\_DRE** (**weak**) – Weak-indication single-bit adder based on Folco et al.'s method, adopting dual-rail data encoding

**G** – Generate (function)

**HE** – Heterogeneous Encoding

**HIE** – Hybrid Input Encoding

**Hybrid\_DSSC\_CCAO\_global** – Hybrid adder incorporating both DSSC\_CCAO\_global and SSSC\_DRE adders that corresponds to global weak-indication

**Hybrid\_DSSC\_CCAO\_local** – Hybrid adder incorporating both DSSC\_CCAO\_local and SSSC\_DRE adders that corresponds to local weak-indication

**Hybrid\_DSSC\_CCO** – Hybrid adder incorporating both DSSC\_CCO and SSSC\_DRE adders

**Hybrid\_TSSC\_CCO** – Hybrid adder featuring an optimal combination of TSSC\_CCO and SSSC\_DRE adder modules

**Modified David et al.\_DRE** (**strong**) – Modified David et al.'s single-bit adder based on dual-rail data encoding featuring strong-indication

**Modified David et al.\_DRE (weak)** – Modified David et al.'s single-bit adder based on dual-rail data encoding featuring weak-indication

**Modified\_Seitz\_DSSC** – Dual-bit adder adopting dual-rail data encoding based on a modification of Seitz's approach

**MOSOP\_compressor\_DRE** – (4:2) logic compressor design based on the MOSOP heuristic, utilising dual-rail encoding

**OS** – Overturned Stairs (tree structure)

**P** – Propagate (function)

**Petrify\_DRE** (**strong**) – Single-bit strong-indication version of full adder synthesised using Petrify tool, based on dual-rail data encoding

**Petrify\_DRE** (weak) – Single-bit weak-indication version of full adder synthesised using Petrify tool, based on dual-rail data encoding

**RCA** – Ripple Carry Adder

SCBCLA – Section Carry Based Carry-Lookahead

**Seitz\_compressor\_DRE** – (4:2) logic compressor design based on a modification of Seitz's approach, based on dual-rail data encoding protocol

**Seitz\_DRE** (**strong**) – Seitz's single-bit adder featuring strong- indication based on dual-rail data encoding

**Seitz\_DRE** (**weak**) – Seitz's single-bit adder featuring weak-indication based on dual-rail data encoding

**Singh\_DRE** (**strong**) – Singh's single-bit adder based on dual-rail data encoding featuring strong-indication

**SOL** – Sum Only Logic

SSSC\_DRE - Single-Sum Single-Carry (adder) adopting dual-rail data encoding

**SSSC\_DRE** (**CPA**) – A simple carry-propagate adder featuring single-bit adders that are based on conventional dual-rail data encoding

**SSSC\_DRE** – **Hybrid** – Hybrid section carry based CLA adder constructed using single- sum single-carry adder modules based on dual-rail data encoding, including a 3-bit CLA generator module in the most significant nibble position

**SSSC\_DRE** (**Hybrid with 4-bit CLA**) – Hybrid 4-bit CLA logic based adder incorporating single-bit adder modules, 4-bit CLA modules and a 3-bit CLA module in the most significant nibble position

**SSSC\_DRE** – **Type 1** – Type 1 section carry based CLA architecture constructed using single-sum single-carry adder modules based on dual-rail data encoding

**SSSC\_DRE** – **Type 2** – Type 2 section carry based CLA architecture constructed using single-sum single-carry adder modules based on dual-rail data encoding

SSSC\_HIE – Single-Sum Single-Carry (adder) with Hybrid Input Encoding

**SSSC\_HIE\_NRL** – Single-Sum Single-Carry Hybrid Input Encoded (adder) with Non-Redundant Logic

**SSSC\_ HIE\_NRL** – **Hybrid** – Hybrid section carry based CLA adder constructed using single-sum single-carry adder modules with no redundant logic based on hybrid input encoding, including a 3-bit CLA generator module in the most significant position

**SSSC\_HIE\_NRL** – **Type 1** – Type 1 section carry based CLA architecture constructed using single-sum single-carry adder modules with no redundant logic based on hybrid input encoding

**SSSC\_ HIE\_NRL – Type 2** – Type 2 section carry based CLA architecture constructed using single-sum single-carry adder modules with no redundant logic based on hybrid input encoding

**SSSC\_HIE\_RL** – Single-Sum Single-Carry (adder) based on hybrid input encoding incorporating redundant logic

**SSSC\_HIE\_RL** (**2-bit CLA – Type 1**) – Type 1 CLA adder architecture built using single-bit adders based on hybrid input encoding with redundant logic and 2-bit CLA modules.

**SSSC\_HIE\_RL** (**2-bit CLA – Type 2**) – Type 2 CLA adder architecture built using single-bit adders based on hybrid input encoding with redundant logic and 2-bit CLA modules.

SSSC\_HIE\_RL (4-bit CLA – Type 1) – Type 1 CLA adder architecture built using single-bit adders based on hybrid input encoding with redundant logic and 4-bit CLA modules.

SSSC\_HIE\_RL (4-bit CLA – Type 2) – Type 2 CLA adder architecture built using single-bit adders based on hybrid input encoding with redundant logic and 4-bit CLA modules.

**SSSC\_HIE\_RL** (**4-bit CLA – Hybrid**) – Hybrid CLA adder architecture built using single-bit adders based on hybrid input encoding with redundant logic and 4-bit CLA modules but with a 3-bit CLA module in the most significant nibble position.

**SSSC\_HIE\_RL** (**CPA**) – A simple carry-propagate adder featuring single-bit adders that are based on hybrid input encoding with redundant logic

**SSSC\_ HIE\_RL – Hybrid** – Hybrid section carry based CLA adder constructed using single-sum single-carry adder modules with redundant logic based on hybrid input encoding, including a 3-bit CLA generator module in the most significant position

**SSSC\_HIE\_RL** – **Type 1** – Type 1 section carry based CLA architecture constructed using single-sum single-carry adder modules with redundant logic based on hybrid input encoding

**SSSC\_ HIE\_RL** – **Type 2** – Type 2 section carry based CLA architecture constructed using single-sum single-carry adder modules with redundant logic based on hybrid input encoding

**Sync\_ST\_compressor\_DRE** – Proposed (4:2) logic compressor design employing dual-rail encoding, based on a translation of the synchronous version

**Sync\_ST\_compressor\_HIE** – Proposed (4:2) logic compressor design employing hybrid input encoding for primary inputs, based on a conversion of the synchronous version

**Toms\_compressor\_DRE** – (4:2) logic compressor design based on Toms' approach, based on dual-rail encoding

**Toms\_compressor\_HIE** – (4:2) logic compressor design based on Toms' approach, based on hybrid input data encoding

**Toms\_DB\_HE** – Toms' dual-bit adder based on heterogeneous encoding

**Toms\_DRE** (strong) – Strongly indicating single-bit adder based on Toms' approach, employing dual-rail data encoding

**Toms\_DSSC** – Dual-bit adder synthesised using Toms' approach that utilises dual-rail data encoding

**Toms\_HIE** – Hybrid input encoded single-bit adder synthesised using Toms' approach, utilising dual-rail data encoding

TSSC – Triple-Sum Single-Carry (adder)

**TSSC\_CCO** – Triple-Sum Single-Carry (adder) with C-elements, Complex gates and OR gates

#### **Abstract**

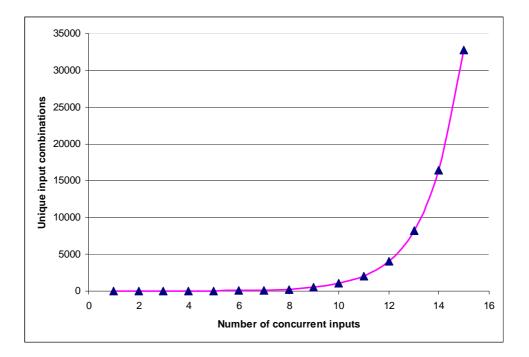

The unorthodox methods usually employed for synthesising self-timed combinational logic incur substantial area overhead. A novel heuristic is proposed on the basis of set theory to considerably alleviate the problem of input state space explosion that besets function block realisations featuring several concurrent inputs. The heuristic has been implemented in Java and a system configuration in support of this heuristic is also presented. The proposed heuristic also forms the basis for realising many self-timed adders. The performance potential of various single-bit and dual-bit adder blocks, which adopt widely preferred homogeneous or heterogeneous delay-insensitive data encoding styles, are analysed on the basis of the selftimed carry-ripple adder architecture. Within this framework, hybrid adder schemes are also considered. With the intent of significantly reducing the datapath delay, the concept of redundant logic insertion has been put forward. Subsequently, to further improve the latency of dual-operand adders, self-timed section carry based carry-lookahead architectures have been proposed that outperform the basic self-timed carry-propagate adder topology. Finally, a bit-partitioning scheme for self-timed addition of multiple operands is described and a new self-timed logic compressor design is discussed. The impact of carry save adder and compressor tree structures, forming part of the input field partitions, on multi-operand addition is analysed through a case study, showing that the latter may be preferable compared to the former for self-timed multi-input addition.

## **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

### Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the "Copyright") and s/he has given The University of Manchester the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

- ii. Copies of this thesis, either in full or in extracts, may be made **only** in accordance with the regulations of the John Rylands University Library of Manchester. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

- iii. The ownership of any patents, designs, trade marks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and exploitation of this thesis, the Copyright and any Intellectual Property Rights and/or Reproductions described in it may take place is available from the Head of School of Computer Science (or the Vice-President).

Dedicated to my parents,

Mr. Padmanabhan Ramachandran

&

Mrs. Sumathi Padmanabhan

And my grandmothers,

Smt. Ganga Baghi Rathi (late)

&

Smt. Jayalakshmi

### Acknowledgements

I thank my God for blessing me with health and strength throughout my PhD programme.

I express my gratitude to my supervisor, Dr. Doug Edwards for the opportunity to pursue my PhD in UK. I thank him for his kind support and encouragement. Especially, I thank him for his very helpful comments and suggestions with regard to the draft versions of my thesis.

I thank my advisor, Prof. Steve Furber for directing me to my supervisor when I first contacted him mentioning my research interest. I also thank him for his support and encouragement, especially at an important stage of my research study.

I thank the EPSRC, UK for the significant partial financial support and the School of Computer Science for the bursary.

I thank my dear family members, whose love, care and concern, great support and encouragement have been invaluable and have brought me thus far. Especially, I thank my parents for their financial support at the start of my research and also in helping to pay the difference in my tuition fee during the three years of my PhD.

Finally, I thank all the members of the APT group, especially Will, for providing me some study materials at the start of my research, having few discussions in between and for certain valuable comments on selected portions of my thesis draft, Jeff and Eustace for some inputs about EDA tools in the initial stages, Sohini for the ACiD-WG 2005 summer school handouts and few clarifications, Jeremy for proof-reading a couple of chapters of my thesis draft, Viv Woods for his encouragement and Danil of Newcastle University for some interesting exchanges. Thanks are also due to Charlie and Lilian for trouble-shooting the system (not a self-timed system!) faults as *early* as possible.

### Chapter 1

#### Introduction

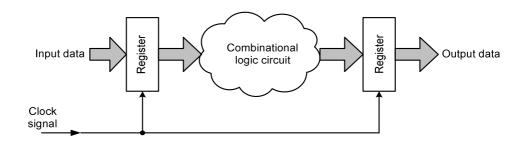

A majority of the present-day digital systems are clock based or synchronous, which assume that signals are binary and time is discrete. In general, synchronous systems comprise a number of subsystems that change from one state to another depending on a global clock signal, with flip-flops (registers) being used to store the different states of the subsystems. A conventional synchronous system is portrayed by figure 1.1.

Figure 1.1: A typical synchronous system stage

The state updates within the registers are carried out on the rising edge (positive edge) or falling edge (negative edge) of the global clock – single edge triggering. The state of the global clock permits either data loading or data storage. Since the overall clock utilisation is only 50% for single edge triggered systems, double edge triggered flip-flops were subsequently proposed in the literature with the motive of increasing the system throughput as data can be loaded on both the rising and falling clock edges and data is retained when the clock signal does not toggle [1] [2]. However, this usually comes at the expense of a larger silicon footprint due to greater number of transistors and more interconnects for the dual edge triggered flip-flop and consequently leads to more power consumption. Preserving the original data rate as that of single edge triggered flip-flop designs whilst operating at half the system clock frequency might be helpful in reducing the dynamic power dissipation as the transitions could be reduced by half, but eventually this may be offset by more leakage power dissipation [2], which is becoming dominant in deep submicron technologies. Moreover, this mechanism

tends to forego the advantages associated with single edge triggering in that its set-up and hold times are larger compared to conventional flip-flops and any deviation from its 50% duty cycle can lead to timing failures in critical paths upsetting the system behaviour [3]. In addition, it is more sensitive to noise apart from introducing complexity in system design and as such, the specification on jitter tolerance is more stringent which complicates the design of the system phase lock loop. As a result, synchronous designs with rising or falling edge triggering have been predominant, being the mainstream of digital system architectures; nevertheless, it is becoming increasingly difficult to overcome some fundamental limitations inherent in this approach.

The International Technology Roadmap for Semiconductors (ITRS) predicts that system-wide synchronisation is becoming infeasible owing to increasing silicon complexity [33]. A clock-based system can operate correctly only if all parts of the system see the clock at the same time, which can happen only if the delay on the clock wire is negligible. However, with advances in technology, the systems tend to get bigger and bigger in terms of the number of transistors and as a result the delay on the clock wires can no longer be ignored. The problem of clock skew is thus a major bottleneck for many system designers. Since the clock signal controls all flip-flops to sample and store their input data synchronously, it tends to be highly loaded and the problem becomes more severe. A widely preferred solution is to distribute the global clock using a clock network (clock tree) with clock buffers and thereby control the clock skew. Consequently, this results in an increase in the capacitance of the clock net and also suffers from increased activity (typically two transitions per net per cycle), even ignoring possible hazard activity on such nets.

The primary factors that govern the clock skew in a typical synchronous digital system are as follows:

- resistance, capacitance and inductance of the interconnection material used for the clock distribution network

- clock distribution network architecture, buffering schemes and clock buffers used

- fabrication process variation over the chip area

- number of processing elements in the system and the load presented by each element to the clock distribution network

- rise and fall times and the clock frequency

Various clock distribution strategies have been developed, with the most common and general approach being the use of buffered trees for equipotential clock distribution. However, to distribute high-speed clock signals, symmetric trees like the H-tree are preferred compared to the asymmetric buffered clock distribution tree structure. The H-tree network is the most widely used clock distribution network [4] – [6] to minimise the clock skew. It was shown in [7] that for an  $N \times N$  array of processing elements, the clock pulse rise time and the clock skew associated with it are O(N<sup>3</sup>). Hence, with increase in N, the clock skew is likely to increase rapidly and become a stumbling block. Therefore, a distributed buffering scheme is often resorted to for synchronous digital integrated circuits by introducing buffers in the clock distribution network. However, the disadvantages of this approach are the extra area overhead and the increase in design sensitivity to process variations. Also, it has to be noted that buffers are the primary source of the total clock skew within a well-balanced clock distribution network. Since global clock periods are now commonly less than half a nanosecond, variations in delay by tens of picoseconds can seriously degrade the performance and reliability of highspeed synchronous systems [8]. With Moore's law [9] having been a driving force through process generations, supported by continual innovations in processes and device materials [10], to relentlessly pursue after greater integrated circuit densities, and with variability of process and device parameters assuming ever greater significance [11] [12] as devices are scaled down to more narrow dimensions, the above problem might only get exacerbated. The bottom-line is that clock management is becoming increasingly difficult and solving it in today's high-speed complex system-on-chip designs appears to be a complex and costly affair.

The second major problem faced by designers is power dissipation, which is a very important metric that has gained significance with the phenomenal growth of portable electronics. For mobile electronic applications, the average power consumption has become the most critical design concern. For maximum efficiency, all gates in the system should be performing useful work. However in synchronous systems, this is not usually the case. Consequently, synchronous systems tend to consume more power than necessary. Many gates switch unnecessarily since they are connected to the clock and not because they have to process new input data. However, to circumvent this problem, clock gating is widely employed so as not to enable those sub-systems that are not required for any useful activity. The biggest gate is the clock driver itself which might occupy considerable area and must

switch even if a small part of the system has something useful to do: the global clock, in general, was found to account for 15%-45% of the system power budget [13] and in a processor case study [14], it was found to be responsible for 34% of the total system power dissipation.

#### 1.1 Motivation and Context

The problems of clock skew and power dissipation have been the major drivers for the worldwide resurgence of interest in asynchronous design – notable major projects include [15] - [29]. The design of clock-free or asynchronous systems has thus become attractive for digital system designers during the past two decades although asynchronous logic was explored from the infancy of integrated circuit design [30] - [32]. But synchronous design provided a far more efficient vehicle for exploiting the technology in commercial applications. The 2006 Semiconductor Industry Association's (SIA's) ITRS report on design stated that the percentage of designs driven by handshake clocking (asynchronous signalling) would rise from 11% in 2008 to 40% by 2020. The latest ITRS update on design [33] predicts that design re-use (as a percentage of all logic) would increase from a current figure of 38% to 55% by 2020. Over this period, parameter uncertainty (as a percentage effect on sign-off delay) is projected to increase from 10% to 25%. In fact, reliability has been labelled as one of the five crosscutting design challenges, which drives home the point that design robustness is becoming an increasing priority in deep submicron technologies. The above projections tend to forecast and necessitate a considerable shift in the design paradigm from conventional synchronous logic to asynchronous logic, as the latter benefits owing to its ability to tolerate supply voltage, process parameter and temperature variations [15]. Due to the absence of a global clock reference, asynchronous circuits tend to have better noise and electro-magnetic compatibility properties than synchronous circuits [34]. Also, they feature greater modularity permitting convenient design reuse [36]. Asynchronous operation by itself does not imply low power, but often suggests low power opportunities based on the observation that asynchronous circuits only consume power when and where active [35] [36]. The recent demonstration of the potential advantages of the world's first 8-bit physically flexible asynchronous microprocessor design over a synchronous flexible version in terms of power and noise figures by Karaki et al. from Seiko Epson's Technology Platform Research Centre [37], which utilises

4-phase handshaking and quasi-delay-insensitive design style, endorses the future of self-timed design techniques for even unconventional electronics.

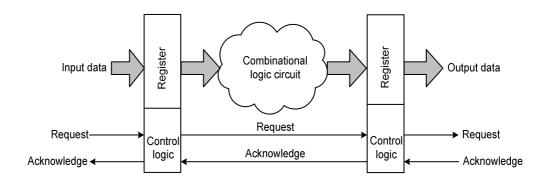

Asynchronous circuits assume that signals are binary but the notion that time is not discrete. An *asynchronous system* is one in which there is no global synchronisation within the system; subsystems within the system are synchronised locally by the communication protocols between them. The results produced by the subsystems in an asynchronous system can be consumed by other subsystems as soon as they are generated without having to wait for a global clock tick. Moreover in asynchronous systems, a sub-system can easily be replaced by another subsystem with the same functionality but with different performance, but this is not a straightforward task in case of a synchronous system as the clock period might have to be recomputed. An asynchronous system stage that involves request/acknowledge handshake (signal exchange) signalling protocol is shown in figure 1.2. However, robust asynchronous systems embed the request information within the data wires and are usually referred to as *self-timed systems*. Self-timed systems are characterised by the absence of any timing reference to which all the operations are synchronised – being in stark contrast to synchronous systems where all operations are synchronised to the global clock signal.

**Figure 1.2:** A typical asynchronous system stage

#### 1.2 Research Contributions

Based on the research undertaken on self-timed combinational logic realisation and especially with respect to datapath elements, the original contributions of this thesis are summarised as follows:

- Formulation of speed-independent decomposition rules using set-theoretic principles.

- General multi-level synthesis models to realise strong or weak-indication combinational logic, which consider the entire input space.

- A set theory based heuristic for compactly synthesising combinational logic of arbitrary size as self-timed circuits and a system configuration in support of the proposed heuristic.

- Design of self-timed carry-ripple adders which feature local or global indication property and proposition of the concept of logic redundancy insertion for delay reduction.

- Self-timed section carry based carry-lookahead architectures that greatly minimise the latency of dual-operand addition in comparison with the ripple carry topology.

- A combinational bit-partitioning strategy addressing self-timed multi-operand addition and the design of a self-timed logic compressor.

#### 1.3 Publications

The following list of publications gained and papers to be submitted for review corresponds to the contributions resulting from this research work.

- P. Balasubramanian and D.A. Edwards, "Efficient realization of strongly indicating function blocks," *Proc. IEEE Computer Society Annual Symposium on VLSI*, pp. 429-432, 2008.

- P. Balasubramanian and D.A. Edwards, "A new design technique for weakly indicating function blocks," *Proc.* 11<sup>th</sup> IEEE Workshop on Design and Diagnostics of Electronic Circuits and Systems, pp. 116-121, 2008.

- P. Balasubramanian and D.A. Edwards, "A delay efficient robust self-timed full adder," Proc. 3<sup>rd</sup> IEEE International Design and Test Workshop, pp. 129-134, 2008.

- P. Balasubramanian and D.A. Edwards, "Power, delay and area efficient self-timed multiplexer and demultiplexer designs," Proc. 4<sup>th</sup> IEEE International Conf. on Design and Technology of Integrated Systems in Nanoscale Era, pp. 173-178, 2009.

- > P. Balasubramanian, D.A. Edwards and C. Brej, "Self-timed full adder designs based on hybrid input encoding," *Proc.* 12<sup>th</sup> IEEE Symposium on Design and Diagnostics of

Electronic Circuits and Systems, pp. 56-61, 2009.

- > P. Balasubramanian and D.A. Edwards, "Dual-sum single-carry self-timed adder designs," Proc. IEEE Computer Society Annual Symposium on VLSI, pp. 121-126, 2009.

- > P. Balasubramanian and D.A. Edwards, "Heterogeneously encoded dual-bit self-timed adder," *Proc.* 5<sup>th</sup> IEEE Conf. on Ph.D. Research in Microelectronics and Electronics, pp. 120-123, 2009.

- > P. Balasubramanian and D.A. Edwards, "Self-timed realization of combinational logic," *Accepted for presentation in the 19<sup>th</sup> International Workshop on Logic and Synthesis*, 2010.

- > P. Balasubramanian and D.A. Edwards, "Redundancy insertion and latency reduction in self-timed adder blocks," to be submitted for review.

- > P. Balasubramanian and D.A. Edwards, "Self-timed section carry based carry-lookahead adder architectures," to be submitted for review.

#### 1.4 Structure of the Thesis

The organisation of this thesis is as follows:

- Chapter 2 discusses the fundamentals of self-timed systems. Specifically, the basics underlying robust asynchronous datapath logic implementation are explained.

- \* In Chapter 3, various self-timed combinational logic realisation schemes are reviewed.

- \* In Chapter 4, new terminologies are proposed to describe logic operations on the basis of set theory. Necessary criteria for speed-independent datapath logic decomposition are discussed and a general multi-level synthesis model is proposed for strong or weak-indication function block designs based on the dual-rail data encoding protocol, which can be extended to address any 1-of-n data encoding scheme. A set theory based procedure to derive two-level minimum orthogonal sum-of-products form is elucidated and the complexity involved in extending this heuristic to multiple levels is highlighted. A system configuration proposed to facilitate strongly or weakly indicating function block implementations on the basis of the above heuristic is then presented. Examples of a multiplexer and demultiplexer are considered to highlight the benefits of this strategy.

- Single-bit and dual-bit self-timed adder designs that utilise homogeneous or heterogeneous delay-insensitive data encoding schemes are discussed in Chapter 5. Modifications to a

speed-independent adder, in order to properly embed the property of indication (acknowledgement) into it are also mentioned. The carry-ripple adder topology has been considered for evaluation of the adder modules. The concept of redundant logic insertion that facilitates significant delay reduction in a logic cascade is then explained.

- In Chapter 6, novel self-timed section carry based carry-lookahead architectures for reducing the latency associated with conventional self-timed dual-operand carry-ripple addition are presented. An analytical estimation of the hardware complexity involved in realising higher-order carry-lookahead modules is also provided.

- \* Chapter 7 first discusses conventional tree structures for performing multi-operand addition. A combinational bit-partitioning scheme for performing self-timed multi-operand addition is then described. A (4:2) logic compressor is designed and addition of multiple operands using adders/logic compressors is separately examined through a case study.

- An overall summary of the thesis contents is first discussed in Chapter 8. Next, the issues involved in extending the two-level heuristic that has been proposed to implement arbitrary combinational logic functions as self-timed circuits into multiple levels are mentioned, and a feasible solution is then presented. This presents an interesting direction for further research in the domain of self-timed logic.

### Chapter 2

## **Fundamentals of Asynchronous Circuits**

The fundamentals of asynchronous systems such as handshake protocols, bundled-data and delay-insensitive data encoding schemes, modes of operation, various classes of asynchronous circuits based on the timing models adopted, Muller's C-element and the concept of indication, and the notion of a function block are discussed briefly in this chapter. References [38] – [40] provide a good introduction and comprehensive overview of asynchronous design methodologies in general. This chapter is intended to provide only a snapshot of the relevant details, with emphasis on topics of interest in the context of the subject matter of this thesis.

#### 2.1 Handshake Mechanism and Data Representation

Asynchronous systems come in many flavours with the most prominent among them being bundled-data and dual-rail data encoding schemes. The communication protocol among these systems can also assume two forms: 2-phase (transition signalling) and 4-phase (level-sensitive signalling). Bundled-data encoding with 2-phase signalling and dual-rail data encoding with 4-phase signalling have been the popular choices in asynchronous circuit design until now and so they will be described here to provide relevant background information. In fact, dual-rail data encoding with level sensitive signalling continues to attract attention, as it is tolerant to variations in logic elements and communicating signal wires and hence has become attractive for deep submicron technologies [29] [37] [67].

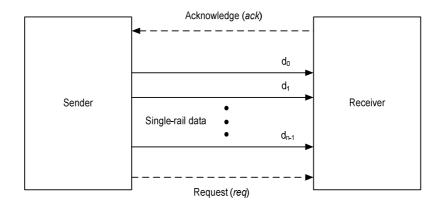

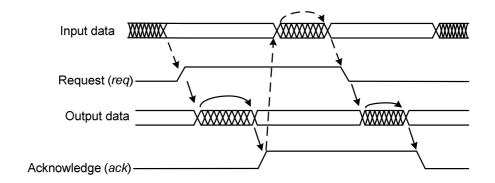

The bundled-data protocol uses a request wire and an acknowledge wire and a set of single-rail data wires for data communication between the sender and receiver, as shown in figure 2.1. Hence, apart from the data bundle, there are two control wires: request (req) and acknowledge (ack). Together, they form a channel or medium of communication. In a typical 2-phase handshake protocol, the sender initiates the handshake mechanism with the data at hand by issuing a request to the receiver (by a transition on the req wire) and the receiver accepts the data and issues an acknowledgement (by a transition on the ack wire) to the sender. This completes a single transaction and sets the tone for a subsequent transaction, as

depicted in the timing diagram of figure 2.2. The relations represented by solid arrows are functional constraints, while those indicated by dashed arrows are domain constraints. The crosshatched areas of input data and output data signify the time periods (intervals) during

which data values may change; otherwise the data are stable and defined.

Figure 2.1: Bundled-data encoding and 2-phase handshaking

**Figure 2.2:** Timing diagram of a 2-phase handshake protocol [71]

It can be noticed that every transition on the *req* wire, both falling and rising, initiates a new request. Two-phase signalling is particularly useful for the realisation of high-speed Micropipelines [41]. Alternatively, the receiver can initiate the handshake process. Hence, if the sender is the active party who initiates the handshaking with the receiver being the passive party, then the channel is called *push channel* as the sender pushes the data to the receiver. Alternatively, if the receiver is the active party with the sender being the passive party, then

the channel is known as *pull channel* as the receiver pulls the data from the sender. Traditionally, the request wire is used to inform the receiver about the validity of the data on the data bundle. This inherently places a constraint on the *req* wire, known as the bundling constraint. According to this constraint, the *req* wire must be asserted only after the bundled-data is valid at the receiver end. This is necessary to ensure that data wavefronts do not overlap and the system does not enter into a deadlock state. In other words, after a transition in the *ack* wire from the receiver to the sender that the data has been used; the sender can send the next set of data to the receiver. A micropipeline is delay-insensitive once the bundling constraints are met. Since there is no upper bound on the delays between consecutive events and even though the *req* wire is asserted after the data becomes valid at the transmitter end, arbitrary wire delays mean that this condition may not hold at the receiver; therefore, bundled-data protocols are not delay-insensitive.

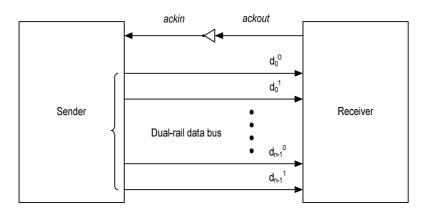

In contrast to bundled-data encoding, dual-rail encoding does not use a separate req wire; instead the req signal is embedded within the data wires. Moreover, each data wire x is represented using two data wires x0 and x1, as shown in figure 2.3.

Figure 2.3: Delay-insensitive (dual-rail) data encoding and 4-phase handshaking

A transition on the x0 wire indicates that a *zero* has been transmitted, while a transition on the x1 wire indicates that a *one* has been transmitted. Since the request is embedded within the data wires, a transition on either x0 or x1 informs the receiver about the validity of the data. The condition of both x0 and x1 being a zero at the same time is referred to as the *spacer* or *empty data*. Both x0 and x1 are not allowed to transition simultaneously as it is illegal and

invalid. The channel requiring (n+2) data wires in a bundled-data system would now comprise (2n+1) data wires with dual-rail signalling; nonetheless, the latter approach makes the signalling robust and therefore can tolerate random variations in wire delays when the bundling constraint cannot be guaranteed. With reference to figure 2.3, the 4-phase handshake protocol can be explained as follows<sup>1</sup>:

- The dual-rail data bus is initially in the spacer state. The sender transmits the codeword (valid data). This results in 'low' to 'high' transitions on the bus wires (i.e. any one of the rails of all the dual-rail signals is assigned a logic 'high' state), which correspond to non-zero bits of the codeword.

- After the receiver receives the codeword, it drives the *ackout* (*ackin*) wire 'high' ('low').

- The sender waits for the *ackin* to go 'low' and then resets the data bus (i.e. it is driven to the spacer state).

- After an unbounded, but finite (positive) amount of time, the receiver drives the *ackout* (*ackin*) wire 'low' ('high'). A single transaction is now said to be complete and the system is ready to proceed with the next transaction.

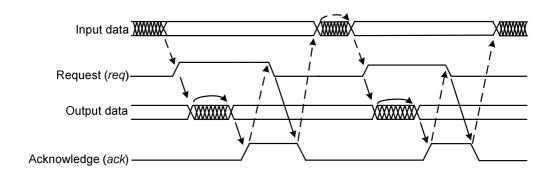

Figure 2.4: Timing diagram of a 4-phase handshake discipline [71]

The timing diagram for the 4-phase asynchronous signalling protocol is shown in figure 2.4, with the *req* wire explicitly shown to describe the handshaking process. It can be observed that four transitions are required to complete a transaction with this approach and there is an intermediate return-to-zero (RTZ) phase of both the *req* and *ack* wires preceding

-

<sup>&</sup>lt;sup>1</sup> The explanation remains valid for data representation using any delay-insensitive data encoding scheme.

every transaction as the signalling convention is level-sensitive: valid data corresponding to logic high and spacer data corresponding to logic low. Comparing figures 2.2 and 2.4, it can be seen that the number of transactions processed during the same time interval is double in case of the bundled-data system employing 2-phase signalling compared to the encoded system employing 4-phase signalling convention. Though in principle every transition represents a meaningful event in case of the 2-phase protocol, such interface implementations require more logic and are more complex as circuits that process transitions require state. The increase in logic complexity may lead to more power consumption than was saved by fewer control transitions. This was the case with the low-power asynchronous ARM processor, AMULET1 [16]. The lack of a distinct low power advantage led to an improved implementation, AMULET2e [22], in which RTZ signalling convention was employed and performance improvement and power reduction over AMULET1 were reported [42]. Although the improvements were effected owing to enhanced design expertise and architectural improvements as well, nevertheless, it substantiated the reasoning that power and performance attributes cannot be solely judged on the basis of the number of control transitions per event.

It was mentioned earlier that in case of the dual-rail data encoding scheme, the input combination of both x0 and x1 being simultaneously high is not allowed because the coding scheme is unordered [43]. A coding scheme is said to be unordered, when none of its code words is contained in any other codeword. In simple terms, the positions of ones in a codeword are never a subset of the positions of ones in a different codeword (example, '01' and '10'). In fact, the dual-rail code is the simplest member of the general family of delayinsensitive m-of-n codes [44], where m lines are asserted 'high' out of a total of n physical lines to represent a codeword and the size (i.e. the number of unique symbols) of a generic m-of-n code is given by the binomial co-efficient n choose  $m = \frac{n!}{m!(n-m)!}$ . The dual-rail code is

ideally suited for representing a single bit of information. To represent two bits of information at a time, the dual-rail code can be concatenated as shown in Table 2.1 or can equivalently be represented by means of a single 1-of-4 code. Indeed, the 1-of-4 encoded values of single-rail inputs given in Table 2.1 represent only one of many possible encodings and an arbitrary choice is considered here for illustration. As can be seen from Table 2.1, two non-redundant

bits of information are represented at a time by asserting only half of the physical lines as logic 'high' in a 1-of-4 code in comparison with a dual-rail code, though both require the same number of physical lines. As a result, the 1-of-4 encoding approach requires only half as many transitions as that of a dual-rail encoding approach. Consequently, the dynamic power dissipation of the former scheme is very likely to be better than that of the latter due to reduced switching activity. This phenomenon was confirmed with the practical example of an ARM thumb instruction decoder [45]. However, considering the additional encoding and decoding circuitry required for 1-of-4 encoded datapaths in comparison with dual-rail code [50], the power savings gained are likely to diminish. This shall be articulated when dealing with self-timed dual-bit adders in Chapter 5.

| Single-rail inputs |   | Dual-rail encoded data |         | 1-of-4 encoded data |    |    |    |

|--------------------|---|------------------------|---------|---------------------|----|----|----|

| Α                  | В | (A1 A0)                | (B1 B0) | E0                  | E1 | E2 | E3 |

| 0                  | 0 | (0 1)                  | (0 1)   | 0                   | 0  | 0  | 1  |

| 0                  | 1 | (0 1)                  | (1 0)   | 0                   | 0  | 1  | 0  |

| 1                  | 0 | (1 0)                  | (0 1)   | 0                   | 1  | 0  | 0  |

| 1                  | 1 | (1 0)                  | (1 0)   | 1                   | 0  | 0  | 0  |

**Table 2.1:** Data representation in dual-rail and 1-of-4 encoding schemes

Though higher order encoding schemes are possible, nevertheless, apart from the dual-rail (or 1-of-2) code that allows easier mapping between conventional binary functions, the other widely used delay-insensitive code is the 1-of-4 code. This is due to the reason that for self-timed datapaths, encoding (by sender) and membership test and decoding (by receiver) are important aspects and consequently, encoding and decoding complexity is dependent on the message space to be coded [46]. Completion detection circuits, which detect the arrival of valid/empty data, perform the membership test [47] for the delay-insensitive unordered codes. In short, completion detection circuits perform validity/neutrality test of input code words. Both dual-rail and 1-of-4 codes can be considered to belong to the class of one-hot codes or 1-of-*n* codes, which is a subset of the generic family of *m*-of-*n* codes [44] [48]. The other important reason for the non-usability of higher order 1-of-*n* codes is the degradation of coding efficiency, and so self-timed logic realisations are usually based on dual-rail and 1-of-4 codes. Given this, higher order *m*-of-*n* codes with better efficiency are preferred for inter-chip

communication [49] [50]. The efficiency of a code is determined by the rate R (that specifies the number of bits per wire) and is equal to  $\log_2 \frac{M}{n}$  [44]. Here, M represents the size of the code or the number of data values represented and n denotes the number of physical wires. In general, a 1-of-n code can represent k single-rail inputs, where  $k = \log_2 n$ . For example, to represent 8 single-rail binary inputs, a direct one-hot code representation would demand 256 physical lines (1-of-256 code), whereas only 16 physical lines would be required by a dual-rail coding scheme and a similar count for a 1-of-4 encoding scheme. Hence, for encoding with direct one-hot codes, the number of physical lines required is of  $O(2^k)$  and therefore concatenation of lower order 1-of-n codes might lead to a better solution. When a dual-rail code and a 1-of-4 code are used to represent exactly one bit and two bits of information respectively, they are said to be *complete* [51]. A code is said to be complete, if and only if it contains all code words as implied by its definition. Even with one missing codeword, it would be labelled *incomplete*. A delay-insensitive coding scheme, in general, is required to be unordered and complete [74]. In this context, it may be noticed that the coding efficiency of complete dual-rail and 1-of-4 data encoding schemes is equal to 0.5.

### 2.2 Bounded and Unbounded Delay Models

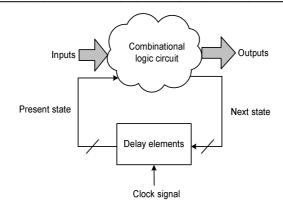

Asynchronous circuit design methodologies can generally be categorised based on the timing models. Bounded delay models assume that the delay in all circuit elements and wires is known (thereby bounded). Circuits based on this model, coupled with the fundamental mode assumption, are generally referred to as Huffman circuits [31]. This is shown in figure 2.5. There are two basic assumptions underlying this model: i) only one input to the circuit is allowed to change at a time, and ii) the present-state entries of the combinational logic can change only after the logic has settled in response to a new input – this condition, when viewed along with the first constraint leads to the understanding that multiple input changes would necessitate multiple iterations by the non-regenerative logic thereby increasing the number of cycles required to complete computation.

**Figure 2.5:** Fundamental mode system configuration

The fundamental mode restriction basically implies that before every external input transition, the entire system should have settled to a stable state with respect to a previous input transition. Burst-mode design style, developed by Nowick et al. [52] [53], based on an earlier work by Davis et al. [54], still requires the fundamental mode assumption but only between transitions in different input bursts. Instead of the overly restrictive fundamental mode assumption, burst-mode design permits simultaneous application of multiple inputs or a burst of inputs (i.e. multiple input changes are permitted), which is comparable with a synchronous system specification. No input burst can be a subset of another input burst leaving the same state, so that the system can determine when a complete input burst has occurred without any ambiguity. Fundamental mode and burst-mode circuits explicitly add delays in order to avoid certain hazard cases and are therefore non-robust design styles in the presence of variability. This also complicates the delay-fault testing of such circuits. Even though a circuit may not have any defects that can cause incorrect function, it might contain defects that could slow its operation. The delay-fault models attempt to classify these types of defects and their effects on the circuit. The two basic models used are: (i) gate delay or transitional fault model [55], where a single gate is assumed to take too long to produce an output, and (ii) the path delay fault model [56], where certain paths in the circuit may take too long to be exercised. In a typical synchronous circuit, such faults would require the chip to be clocked at a slower rate, whereas in an asynchronous circuit, since there is no clock-based synchronisation, it may end up in incorrect circuit operation that might be difficult to fix. Though delay-fault testing is not solely an issue with bounded delay models and may be problematic for unbounded delay models as well, the less pervasive timing assumptions of the latter facilitate comparatively easier testing, as they are more robust than the former. The

assumed, where the environment must wait for a circuit to stabilise before responding to the

bottom-line in fundamental mode circuits [32] is that environmental timing constraints are

outputs. This requirement is identical to the hold time requirement for a simple latch or a flip-

flop [57].