# Branch Prediction Strategies for Low Power Microprocessor Design

# A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF MASTER OF SCIENCE IN THE FACULTY OF SCIENCE

Richard York

Department of Computer Science

1994

# **Contents**

| <b>1. Introduction</b>                         | 4  |

|------------------------------------------------|----|

| 1.1 Current Power Consumption Requirements     | 5  |

| 1.1.1 Heat Extraction and Power Distribution   | 6  |

| 1.2 Battery Technology                         | 7  |

| 1.3 CMOS Power Dissipation                     | 8  |

| 1.3.1 Circuit Technology                       | 9  |

| 1.3.2 Lowering the Supply Voltage              | 1  |

| 1.3.3 Clock Rate Reduction                     | 2  |

| 1.4 Improved System Architecture               | 3  |

| 1.4.1 Cache Architecture                       | 3  |

| 1.4.2 Register and Operand Accessing           | 4  |

| 1.4.3 Operand size                             | 5  |

| 1.4.4 Instruction Bandwidth and Density        | 5  |

| 1.4.5 Uses and Effects of Pipelining           | 6  |

| 1.4.6 Parallelisation                          | 7  |

| 1.5 Conclusions                                | 8  |

| 2. Architectural Factors                       | 29 |

| 2.1 Clock Rate                                 | 9  |

| 2.2 Clock Gating and Distribution              | 2  |

| 2.3 Cache Structure                            | 3  |

| 2.4 Improving Pipeline Occupancy               |    |

| 2.5 Register Usage                             | 9  |

| 2.6 Instruction Encoding                       | 1  |

| 2.7 Asynchronous Design                        | 5  |

| 2.8 Decision Making and Branching Strategy     | 6  |

| 2.9 Conclusions                                | 6  |

| 3. A Review of Instruction Branch Strategies 4 | 8  |

| 3.1 Programming Style and Behaviour            | 8  |

| 3.1.1 Conditional Instruction Skipping         |    |

|                                                | 2  |

|    | 3.3 Types of Branch                                |

|----|----------------------------------------------------|

|    | 3.3.1 Branch Target Calculation                    |

|    | 3.4 Branch Implementation                          |

|    | 3.5 Past Branch Prediction Schemes                 |

|    | 3.5.1 Multiple Instruction Pipelines               |

|    | 3.5.2 Loop Buffers                                 |

|    | 3.5.3 Branch Target Prefetching                    |

|    | 3.5.4 Delayed Branches                             |

|    | 3.5.5 Branch Target Cache                          |

|    | 3.5.6 A Shared Pipeline                            |

|    | 3.5.7 Branch Removal                               |

|    | 3.5.8 Taken/Not Taken Bits                         |

|    | 3.6 Recent Branch Prediction Schemes               |

|    | 3.6.1 Prediction With Masked Squashing             |

|    | 3.6.2 Procedure Call Stack                         |

|    | 3.6.3 Branch Correlation                           |

|    | 3.6.4 Hardware Loop Support                        |

|    | 3.6.5 Storing Prediction Flags in the Cache        |

|    | 3.7 Summary                                        |

| 4. | Requirements and Design of a Branch Predictor . 81 |

|    | 4.1 AMULET1 Architecture                           |

|    | 4.2 AMULET2 Structure                              |

|    | 4.2.1 Address Interface                            |

|    | 4.2.2 Decode Pipe                                  |

|    | 4.2.3 Execute Pipe                                 |

|    | 4.3 Evaluating Predictability                      |

|    | 4.3.1 Branch Behaviour and Types                   |

|    | 4.4 Possible Prediction Strategies                 |

|    | 4.4.1 Branch Target Buffer                         |

|    | 4.4.2 Opcode-Based Prediction                      |

|    | 4.4.3 Chosen Prediction Scheme                     |

|    | 4.5 BTC Structural Design                          |

|    | 4.5.1 Finite BTC Sizes                             |

|    | 4.6 Conclusions and Summary                        |

| 5.1 Asynchronous Logic                            |

|---------------------------------------------------|

| 5.2 Additions to be made to AMULET2               |

| 5.2.1 Address Interface                           |

| 5.2.2 Data Interface                              |

|                                                   |

| 5.2.3 Instruction Decode                          |

| 5.2.5 Instruction Decode                          |

| 5.2.4 Decode 2 and Operand Fetch                  |

| 5.2.5 ALU Stage and Branch Recovery               |

| 5.3 The Effects of Self-Modifying Code on the BTC |

| 5.4 Conclusions                                   |

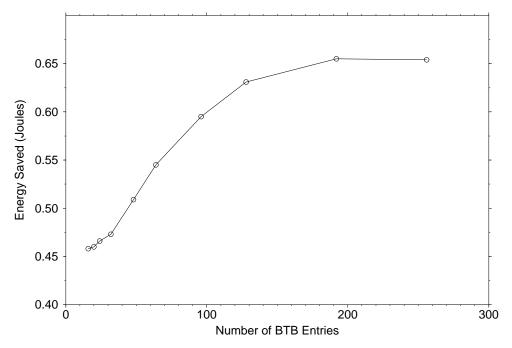

| 6. AMULET2 BTC Evaluation                         |

| 6.1 Power consumption                             |

| 6.2 Potential Power Savings                       |

| 6.2.1 Improved CAM Design                         |

| 6.3 Improvement in Throughput                     |

| 6.4 Summary                                       |

| 7. Conclusions                                    |

| 7.1 Cache Technology                              |

| 7.2 Instruction Set Design                        |

| 7.3 AMULET2 BTC                                   |

| 7.4 Asynchronous Design                           |

| 7.5 Further Research                              |

| Appendix A: Example Output                        |

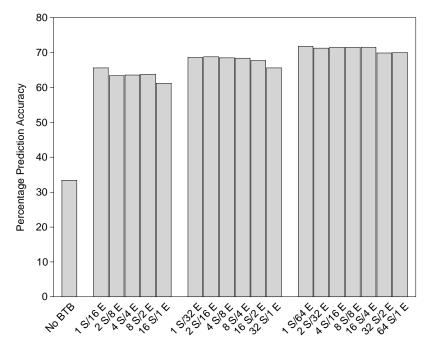

| Appendix B: Direct-Mapped BTC Performance 150     |

| Appendix C: The ARM Microprocessor156             |

| C.1 The ARM2                                      |

| C.2 ARM2 Instruction Set                          |

| C.3 The ARM6                                      |

| References and Bibliography                       |

# **List of Figures**

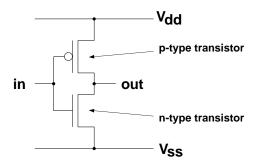

| Figure 1.1 : Simple CMOS inverter                              |

|----------------------------------------------------------------|

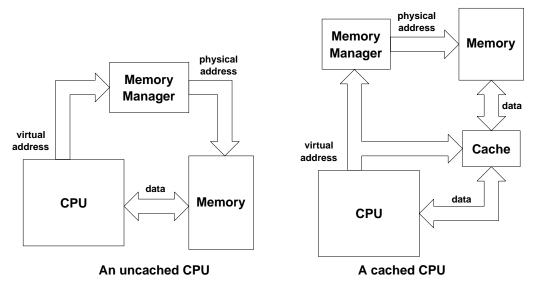

| Figure 1.2 : Cached and uncached CPUs                          |

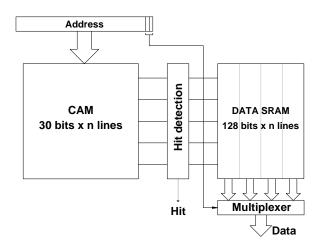

| Figure 2.1 : Fully associative cache structure                 |

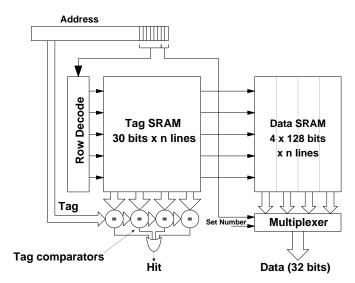

| Figure 2.2 : Four-way set associative cache                    |

| Figure 2.3 : Decoded instruction cache structure               |

| Figure 2.4: Non-decoded instruction cache structure            |

| Figure 2.5 : CRISP instruction alignment mechanism             |

| Figure 3.1 : Non-pipelined branch execution                    |

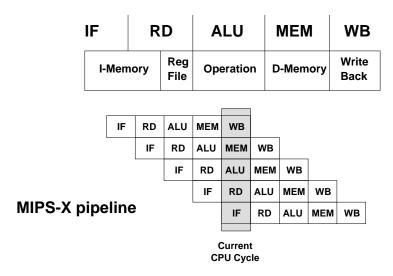

| Figure 3.2 : MIPS-X pipeline structure                         |

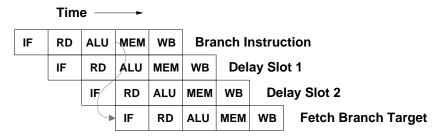

| Figure 3.3: MIPS-X branch execution                            |

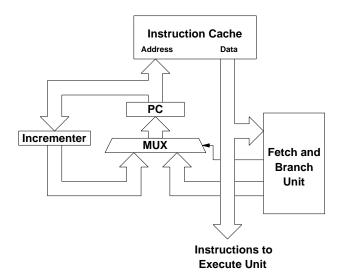

| Figure 3.4 : Remote instruction fetch unit                     |

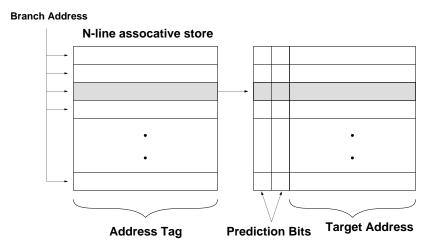

| Figure 3.5 : Branch target cache structure                     |

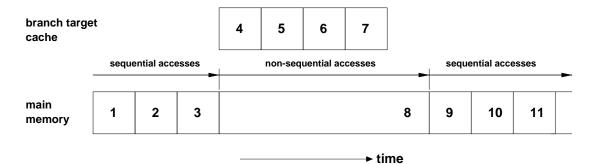

| Figure 3.6: AM29000 branch target cache operation              |

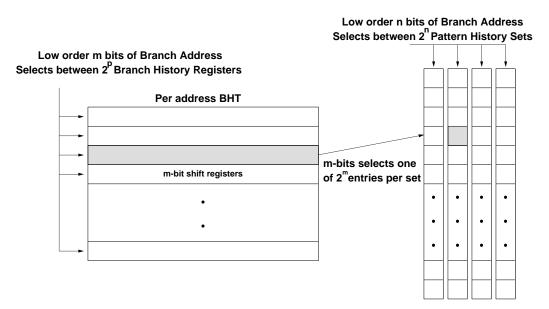

| Figure 3.7: Branch correlation implementation                  |

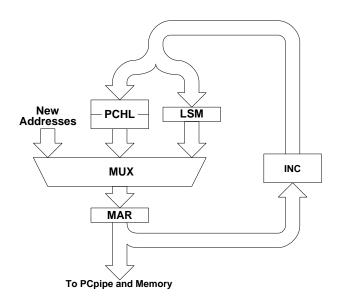

| Figure 4.1 : AMULET2 address interface                         |

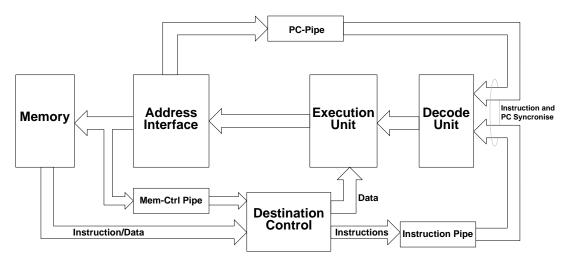

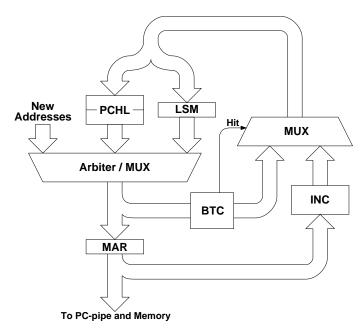

| Figure 4.2 : AMULET2 instruction fetching                      |

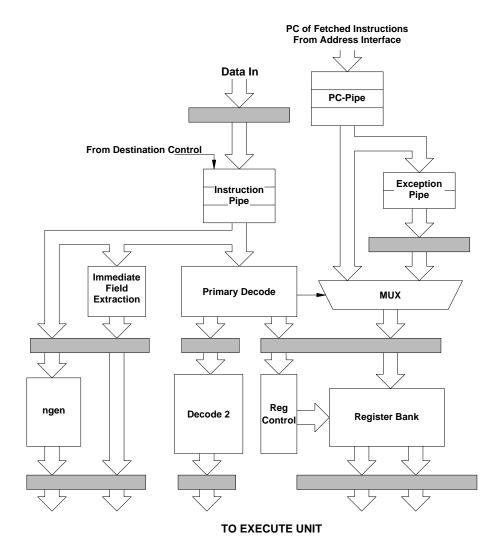

| Figure 4.3 : AMULET2 decode pipeline                           |

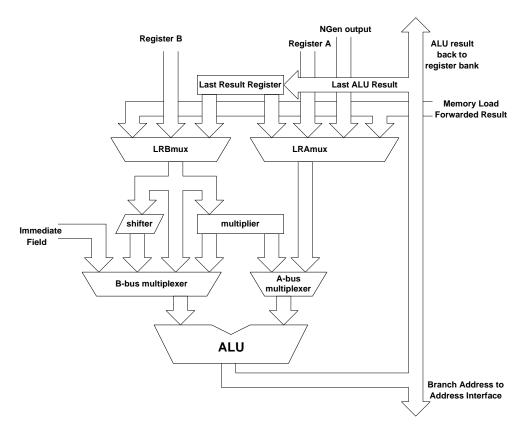

| Figure 4.4 : AMULET 2 execute pipe structure                   |

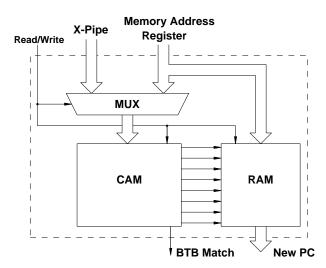

| Figure 4.5 : Address interface with added BTC                  |

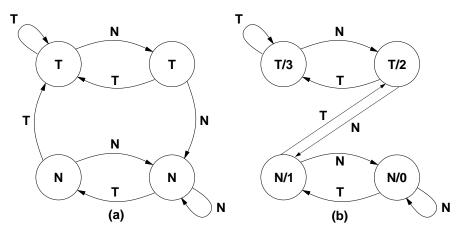

| Figure 4.6 : Prediction state diagrams                         |

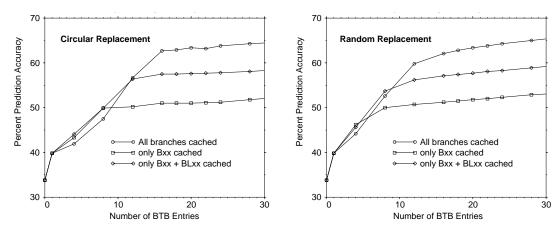

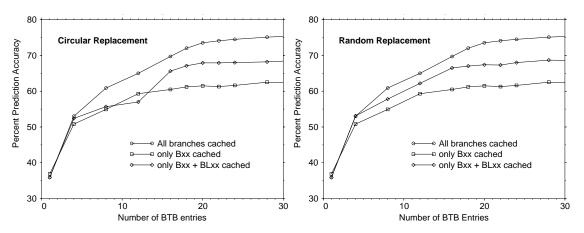

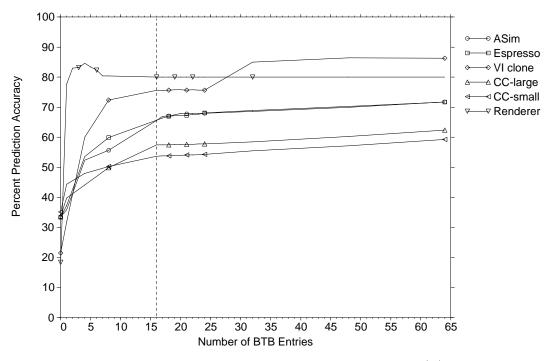

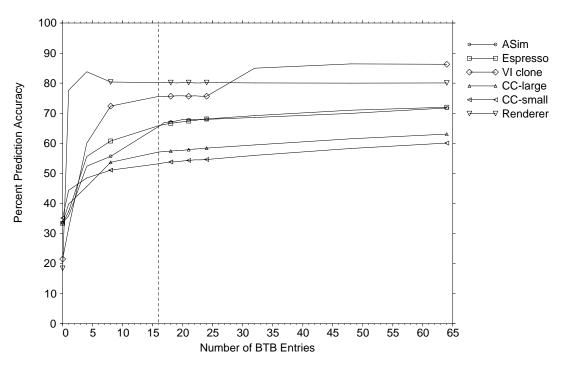

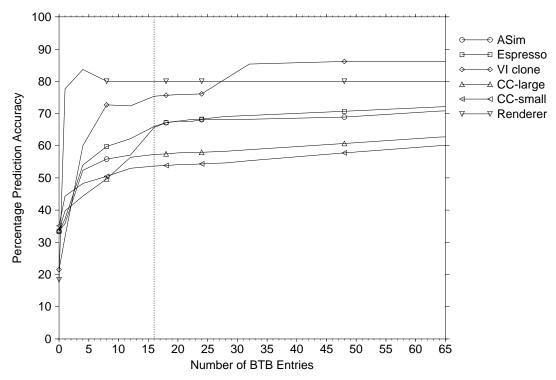

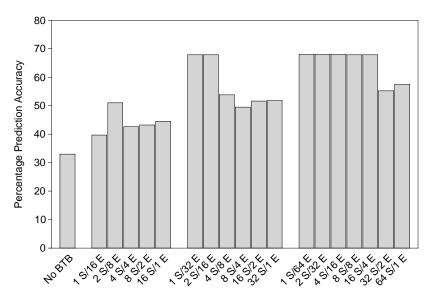

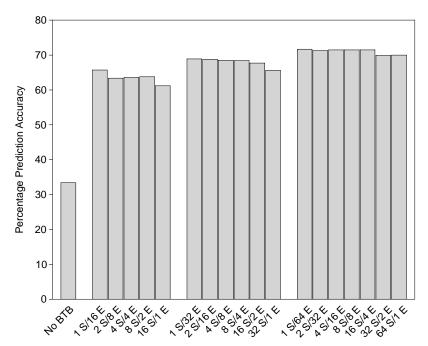

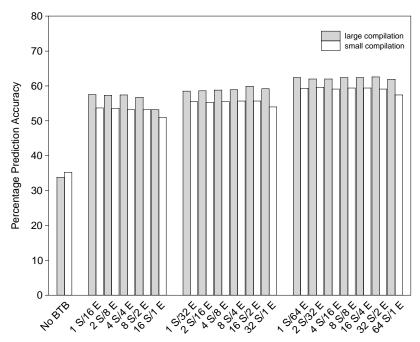

| Figure 4.7: Circular and random replacement for C compiler 105 |

| Figure 4.8 : Circular and random replacement for ASim          |

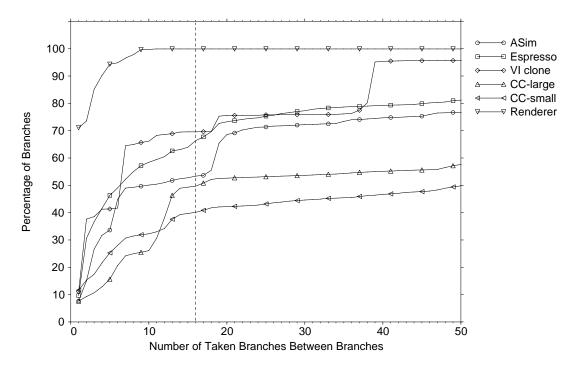

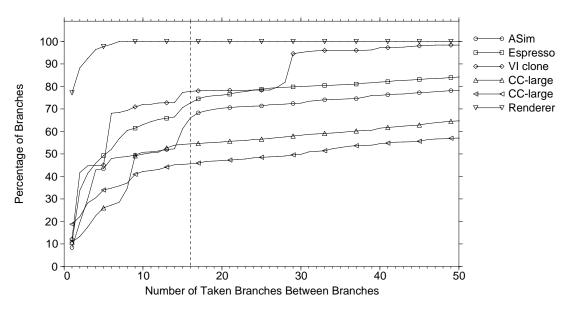

| Figure 4.9 : Cumulative branch distances                           |

|--------------------------------------------------------------------|

| Figure 4.10 : Cumulative branch distances, B(L)xx only             |

| Figure 4.11 : Performance of circular replacement, B(L)xx only 108 |

| Figure 4.12: Performance of random replacement, B(L)xx only 109    |

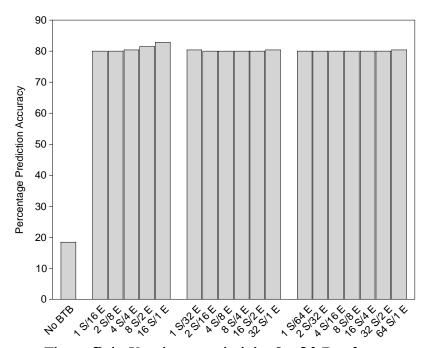

| Figure 4.13 : Performance of GODS replacement, B(L)xx only 110     |

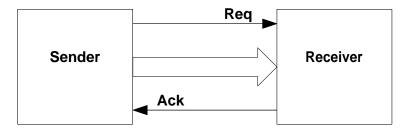

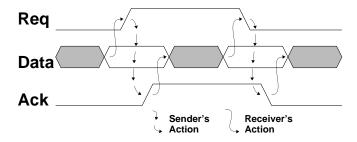

| Figure 5.1: Two phase signalling convention                        |

| Figure 5.2: Micropipeline handshake signals                        |

| Figure 5.3: Bundled data handshake sequence                        |

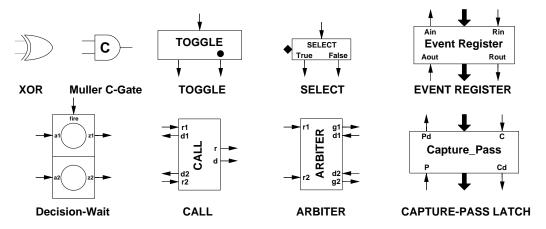

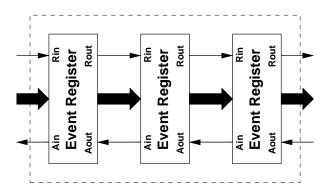

| Figure 5.4: Micropipeline building blocks                          |

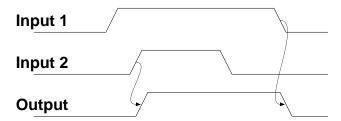

| Figure 5.5: Muller C-Gate operation                                |

| Figure 5.6: Three element asynchronous pipeline                    |

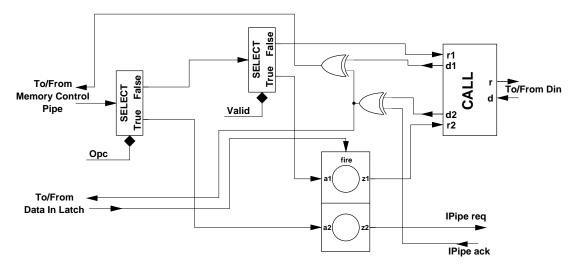

| Figure 5.7: AMULET destination control block                       |

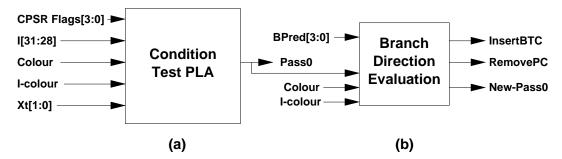

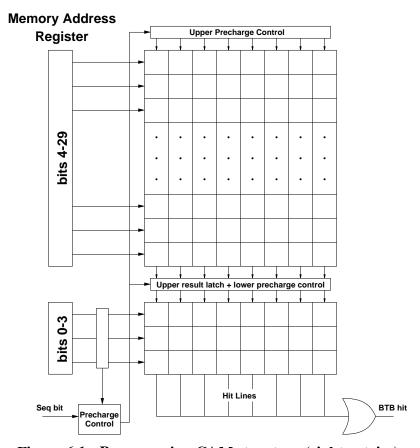

| Figure 5.8: BTC internal structure                                 |

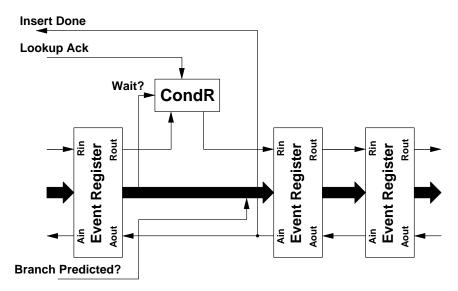

| Figure 5.9 : Split three stage micropipeline                       |

| Figure 5.10: Modified condition code evaluation                    |

| Figure 5.11 : BTC execute control logic                            |

| Figure 6.1: Power-saving CAM structure (eight entries)             |

| Figure 7.1: Graph of BTC size against resulting energy savings 141 |

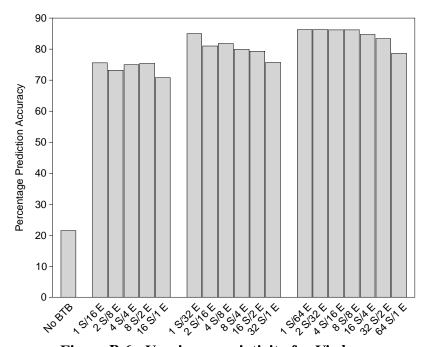

| Figure B.1 : Varying associativity for ASim                        |

| Figure B.2 : Varying associativity for Dhrystone                   |

| Figure B.3: Varying associativity for Espresso                     |

| Figure B.4: Varying associativity for 3d-Renderer                  |

| Figure B.5: Varying associativity for C compiler                   |

| Figure B.6: Varying associativity for Vi clone                     |

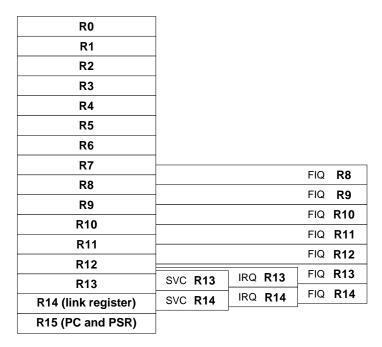

| Figure C.1 : ARM2 Register allocation                              |

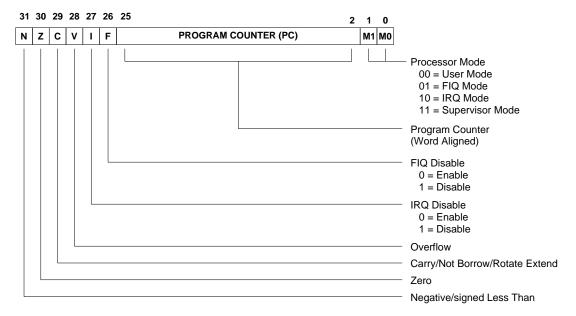

| Figure C.2 : ARM2 PC and PSR format     | • | • | • | • |  |  | • | • | • | • | • | . 1 | 158 |

|-----------------------------------------|---|---|---|---|--|--|---|---|---|---|---|-----|-----|

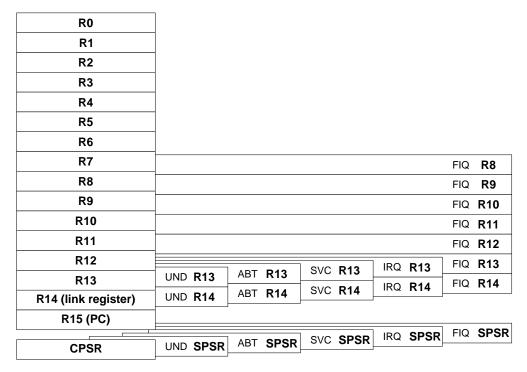

| Figure C.3 : ARM6 register allocation . |   |   |   |   |  |  |   |   |   |   |   | . 1 | 159 |

# **List of Tables**

| Table 1.1 : Power consumption of portable computer components 15       |

|------------------------------------------------------------------------|

| Table 3.1 : Basic branch direction statistics                          |

| Table 3.2 : Size of forward branch offsets                             |

| Table 3.3: Branch delay slot filling success rates 67                  |

| Table 3.4 : CRISP static and dynamic performance analysis              |

| Table 4.1 : ARMulator benchmarks, ideal prediction                     |

| Table 4.2 : Performance of each branch type                            |

| Table 4.3 : Performance of Bxx instructions                            |

| Table 4.4 : Performance of BLxx instructions                           |

| Table 4.5 : Example ARM condition code examination                     |

| Table 4.6: BTFNT prediction results                                    |

| Table 4.7: Two bit branch prediction rules                             |

| Table 4.8: BTC performance for different forms of control transfer 104 |

| Table 6.1: Performance of 20 entry BTC; cyclic replacement             |

| Table 7.1: Energy costs and savings for a 20 entry BTC                 |

#### **Abstract**

Current interest in lower power design has arisen from two areas of application. The first is the fast emerging market for portable, battery-powered, equipment which often requires significant computing power. Secondly, for very high performance processors, there are limits to the heat that can be successfully removed from the package; this in turn puts upper limits on the number of transistors that can be fabricated in a single package. With the number of transistors on a single chip likely to rise to 100 million by the end of the decade the problems of power must be tackled now.

This thesis first examines circuit-level and architectural factors which affect power consumption, with the latter considered in more detail. Pipeline occupancy is identified as being important in many systems for both high throughput and power efficiency. Branch prediction is often used to reduce pipeline stalls; later chapters examine branch mechanisms currently in use and possible branch prediction schemes for accurate speculative execution. The architecture and design of a branch target cache for AMULET2, a low power asynchronous microprocessor, is considered. Finally possible power savings are evaluated and further schemes yielding much higher prediction accuracy are considered.

# **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or institute of learning.

# Copyright

Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without permission (in writing) of the Author.

The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of Department of Computer Science.

# Acknowledgements

The Author would like to thank many people who have given a great deal of help and advice during the years research. These include all of the members of the AMULET group for their readiness to give advice and for providing useful feedback on my ideas.

My supervisor, Dr. J.V. Woods for much time spent discussing the work undertaken and for advice in preparation of this thesis.

Prof. S. B. Furber for suggesting the course of part of my research, particularly the Branch Target Cache, and for discussing the finer points of its architecture.

Much of the software used for benchmarking the BTC is from the public domain, and I would like to thank the authors for releasing the software for general public use.

Finally I would like to express gratitude for the grant I received during my MSc, in the form of an ARM scholarship jointly funded by the Department of Computer Science and Advanced RISC Machines Limited.

# The Author

The Author obtained a B.Sc. (I) in Computer Engineering from the University of Manchester in 1993. This thesis reports the work carried out during the Author's year as a member of the AMULET research group at the University of Manchester.

The AMULET (Asynchronous Microprocessor Using Low Energy Techniques) group comprises a number of research projects exploring the potential of asynchronous logic for low power and high speed applications.

#### 1. Introduction

In recent years the design of low power systems has become very important, with the demand for portable computer equipment such as PDA's (Portable Digital Assistants), notebook computers, communications devices etc., creating a large demand for low power IC's. The combination of demanding applications such as handwriting recognition, which require high processing performance, and long battery life has driven chip designers to concentrate on the power consumption aspects of microprocessors and associated peripheral chips, such as ethernet and RS232 drivers, hard and floppy drive controllers.

The need for more power-efficient desktop machines should also not be ignored. It has been estimated by the US Environmental Protection Agency (EPA) [22] that at the current time around 5% of the USA's commercial sector energy requirements is for desktop computers, rising to around 10% by the end of the decade.

For many desktop computers lower power consumption, or more accurately lower heat output, has become a necessity. Processors such as the DEC Alpha [28] dissipate around 30 watts. If this is not successfully removed, overheating and unreliability will occur. Effective removal of large amounts of heat requires careful design of the heat sinks, air flow etc, and the inclusion of one or more (noisy) fans to ensure an adequate airflow. In a portable machine, where there are many more restrictions on air flow, fans are normally impractical and so there are clearly limits to the amount of heat which can be removed. An Alpha-based notebook machine would obviously be quite a challenge!

This thesis suggests architectural improvements which will allow much lower power processors to be built.

#### 1.1 Current Power Consumption Requirements

Research at Intel [24] has shown that around 50% of power consumed in an office is used by PC's and monitors. Of these the majority of the power used is in the monitor and the often inefficient power supply. The same often applies to portable computers, though the power supply is normally much more efficient. A breakdown of the power consumption for each component is shown below in table 1.1.

| Component          | Power (Watts) |

|--------------------|---------------|

| CPU+2Mbytes memory | 3.65          |

| Screen backlight   | 1.43          |

| LCD                | 0.32          |

| Hard drive motor   | 1.10          |

| Maths coprocessor  | 0.65          |

| Floppy drive       | 0.50          |

| Keyboard           | 0.49          |

| Interfaces         | 0.07          |

| Total              | 8.21          |

**Table 1.1: Power consumption of portable computer components**

The table demonstrates how the processor and memory system constitute 44% of the power in a notebook machine. Other factors such as the back light, screen and hard drive are also significant, and in particular the provision of the back light may seem an unnecessary luxury. Removing it, however, is a problem unless display technology becomes significantly better.

An average PC at the current time may use around 1300kWH per year. Cutting this by simple techniques such as automatically shutting the machine down when not required (a PC is in use on average only 15% of the time) will provide significant savings. Further savings will require much more effort, with power regulation of individual components of the PC becoming necessary. Improvements in power consumption of the system are made more difficult by the ever **increasing** power demands of micro-chips. This trend will have to be reversed or will cancel many of the gains currently being

made in the rest of the system.

#### 1.1.1 Heat Extraction and Power Distribution

For any type of IC package there is a limit to the temperature that the die can tolerate before it fails to function correctly. This is normally around 175°C. The heat generated must be conducted through the packaging and into the surrounding fluid, normally air. This heat conduction causes a temperature gradient from the die to the outside of the package, and this must be taken into account when carrying out package and die temperature calculations.

The more conductive the package the faster the heat is removed from the die for a certain fluid temperature around the package. A plastic package is normally rated at around 1 watt; a ceramic one around 10 watts. Also the effect of temperature on the lifetime of the silicon should not be ignored. It is estimated that up to 150°C the life expectancy of a semiconductor junctions halves for every 10-15°C rise in temperature. Above 150°C the lifetime halves for every 5-10°C. It is likely therefore that any device that can claim very low heat output should also be able to claim increased long term reliability.

#### **Active and Passive Heat Sinks**

The addition of a heat sink allows the surface area and therefore the dissipation of the package to be increased. A typical IC heat sink will have a thermal resistance of around 40°C/watt, ie for every watt that it dissipates its surface temperature rises by 40°C above the ambient temperature. Heatsinks increase the bulk of the package, and need plenty of air space around them to work correctly, making highly integrated systems difficult to build.

An active heat sink employs a component such as a Peltier-effect heat pump to extract heat from the package. Many high-power processors now build a small fan into the heatsink to force air past the fins. Other technologies have been developed such as the thermosiphon employed in the DEC BIPS chip (a 150W ECL microprocessor) [23]. This consists of a sealed boiler and condenser using a volatile liquid to transport the heat efficiently to air-cooled external fins. This has a thermal resistance of around 0.32°C/watt, allowing the die to consume 150W while being maintained below 100°C. The designers have estimated that in quantity the cost excluding the die would be \$150. This is not a very practical technology for high volume microprocessors, but does demonstrate what is possible at the current leading edge.

#### **Current Supply and Distribution**

The higher currents required for devices such as the BIPS chip have to be supplied and distributed around the die. This normally requires a large number of pins exclusively for power and ground, plus large power rails on the die itself. The BIPS part has 162 power connections, constituting 26% of the pins, and gold bus bars over the die to distribute the current. In the design of PCBs it is quite normal to allocate two complete layers to power supply and ground. This may also become necessary on chip as the transient currents of an IC continue to rise. These high currents are worsened by the global clocking enforced by synchronous processors. The DEC Alpha for example has to supply transient currents of approximately 80A on each clock period [28].

#### Cost

With all of these schemes the cost of the packaging and cooling employed rises very rapidly as soon as the power consumption rises above a few watts. For volume production of low cost electronics these techniques are too costly and normally the only available packaging is plastic or perhaps ceramic.

#### 1.2 Battery Technology

In a portable system the source of power is often rechargeable batteries. The type and number of batteries is of major importance; too few and frequent charging is required; too many and the machine becomes large, heavy and expensive. Batteries are also difficult and expensive to dispose of due to their heavy metal content; this is compounded by their relatively fixed and often short life span.

The voltages required by the system can restrict the choice of battery voltage. There are often a number of supplies required, for example ±12V, +5V and 20V+ to drive an LCD. Either these are supplied direct from the battery or DC-DC converters are employed to generate all of the potentials from one supply. These converters have, in the past, been rather inefficient, often no better than 70%, though recently this has been pushed up to 80-90% over a large range of current loads (150:1). With the movement towards lower chip supply voltages (see section 1.3.2) this problem is likely to get worse, with systems needing a mix of 2V, 3V, 3.3V and 5V supplies!

#### 1.3 CMOS Power Dissipation

For low power design the static consumption is very important. This is defined to be the power drawn by a circuit when its components are not switching. The dynamic consumption is the power required by circuits when they are switching. Most new VLSI design is implemented in CMOS technology since it has the useful characteristic of very low static current consumption. This generally allows a system doing no work to use zero power. Technologies such as bipolar ECL have large static currents, with much smaller dynamic effects and are therefore of less interest to the low power designer.

Energy is used every time a CMOS gate switches its output. The factors that should be considered for power consumption in a system are :-

- 1. The number of gates.

- 2. The size of the gates.

- 3. The track capacitances.

- 4. The energy consumed per gate per transition.

The energy dissipated for each gate output is easily calculated. This is given below:

$$Energy = \frac{1}{2}C_L \Delta V^2$$

Where  $C_L$  is the total switching capacitance of the gate and  $\Delta V$  is the change in output voltage. This equation represents the energy required to charge or discharge the output capacitance seen by the gate. This occurs when the output switches, either from a low to a high or a high to a low level.

Other lesser factors affecting energy consumption include the short circuit and leakage current and are discussed later. In a synchronous system there is likely to be a global clock which drives many gates. If this clock runs at a frequency **f** the power is often given for the system as:

$$Power = C_L V^2 f \cdot n$$

In this case **n** is the average number of gates that switch per clock. This will be inaccurate since it makes assumptions about the average load (and voltage swing for dynamic circuits) of each gate.

To improve the energy consumption of a system there are two major factors in the power equations that can be reduced; these are the switching capacitance  $C_L$  and the supply voltage  $V_{dd}$ . The former is generally referred to as nodal capacitance and will be examined first, by looking at the circuit technology used for CMOS design.

#### 1.3.1 Circuit Technology

The term 'circuit technology' generally includes the cells and components with which the design is implemented, for example the *cell library* generally supplied with a VLSI CAD package. This cell library provides a set of components with which the designer can implement the required logic. This usually consists of basic gates, eg AND and OR, but may also apply to much larger components such as register cells and ALU 'slices'. Cells may also be custom designed by the engineer, for critical parts of the system, for

example the data-path. This allows much greater control over the characteristics of the cells, for example propagation delay, input capacitance etc. which all affect the power consumed.

To study the effects of the different parameters consider the simple CMOS inverter shown in figure 1.1:

Figure 1.1 : Simple CMOS inverter

The layout of the inverter allows a number of different parameters to be varied. These include the individual transistor sizes and cell topology. Varying these parameters allows a cell to be designed with characteristics precisely tuned for the particular circumstances. Some of these parameters are now considered in more detail.

#### **Transistor Sizing**

The gain of a MOS transistor is set by the ratio of the gate to channel lengths. Normally this ratio is shown as W/L. The larger this ratio the greater the gain of the transistor, but also the greater the input capacitance due to the larger gate area. A p-channel transistor is weaker for the same W/L ratio than an n-channel one; both must be of equal gain for equal rise and fall times when driving capacitive loads, ie other gate inputs. The increased input capacitance of the wider p-channel gate, needed for equal transistor gains, presents an increased load to preceding stages. Relaxing the requirement for equal rise and fall times will therefore allow a reduction in nodal capacitance.

#### **Short Circuit Current**

As the input to a gate rises or falls both transistors in the stack may be momentarily turned on, and current flows direct from  $V_{dd}$  to  $V_{ss}$ . The duration of the short circuit current is proportional to the rise time of the input; the slower the rise time the longer both transistors are conducting and therefore the greater the energy dissipated. The rise time is affected by the nodal capacitance; the larger the capacitance the slower the rise time. Short circuit current is also affected by the threshold voltages of the transistors. This is the point at which the transistor begins to conduct, and if  $V_{dd} = V_{tn} + V_{tp}$  (threshold of n and p transistors) as one transistor switches off the other switches on, resulting in no short circuit current.

#### Summary

The parameters considered above are clearly all interlinked with, for example, the transistor ratios affecting the output edge times, which consequently affects the short circuit current in the gate being driven, requiring an adjustment in the transistor ratios....

The development of cells must be an iterative process in which the effects of combining different cells with interconnecting tracks and gate loads is considered and simulated until the required speed-power performance is achieved.

It is clear from this that the semi-custom designer (who uses only the provided standard cells) has less control over the power consumption of the circuit than a full custom designer. What is needed is a way of allowing the possible cell parameters, such as the transistor sizing, to be optimised by the designer so that energy is expended only where necessary. A power simulator can aid this process by allowing the designer to study the areas of the circuit which are contributing most to the energy consumption.

#### 1.3.2 Lowering the Supply Voltage

A reduction in power can be obtained by simply lowering the supply voltage. Since the power is proportional to  $V^2$  (section 1.3) significant reductions can be made. The lower

supply does however increase the propagation delay and the rise and fall times of the gate. In detail the rise time is given by:

$$T_{pRise} = \frac{2.57C_I}{\beta_p V_{dd}}$$

Where  $\beta_p$  is the gain of the p-channel transistor and  $C_L$  is the load capacitance of the gate. The derivation of this can be found in [46]. To evaluate  $T_{pFall}$  substitute  $\beta_n$  for  $\beta_p$ . This shows that both  $T_{pRise}$  and  $T_{pFall}$  increases as  $V_{dd}$  drops (speed inversely proportional to  $V_{dd}$ ), whereas the energy decreases proportional to  $V_{dd}^2$  (energy per transition proportional to  $V_{dd}^2$ ), making a reduction in supply voltage beneficial. Lowering the supply from 5V to 3V reduces the power by approximately 2.7 times but also reduces the speed by 1.7 times, for the same capacitive load. As process technology improves the feature size will reduce; this results in a reduction in the gate capacitance which reduces the propagation delay of the cells. The speed of the interconnections does not however scale so easily [56], and as feature size falls the interconnect delays will predominate.

Currently 3.3V and 3V are popular supply voltages. Further reductions may require that the threshold voltage of the MOS transistors be decreased, something that becomes difficult at low voltages, for example less than 1V, and the corresponding drop in noise immunity will cause other problems.

Reductions in the supply voltage will continue, though only where it is acceptable to sacrifice some of the performance and noise immunity of the system for a reduction in power consumption.

#### 1.3.3 Clock Rate Reduction

In a synchronous system, since power is directly proportional to clock frequency, f, halving the system clock rate will also halve the power consumed. This is a simple

technique often used in portable equipment, where the processing load is constantly evaluated and the system clock rate adjusted to suit. Complete shutdown of the system is also possible, with some form of restart mechanism then required to react to external events that require processing activity. In both cases the energy used to carry out a required task does not change; the system is ensuring that, when there is no activity, the processor doesn't waste energy.

#### 1.4 Improved System Architecture

Architecture can best be described as the high level structure and strategy selected by the designer for the system. Decisions such as the cache structure, size of register bank, the number of bits in a register and the external size of data buses all constitute the architecture of the microprocessor and can have a significant impact on its throughput and power efficiency.

#### 1.4.1 Cache Architecture

Most processors include a cache either on or off the chip. The cache is normally situated between the processor and the main memory and decouples the two components (figure 1.2). A cache relies on the fact that at any time there is a current working set of data and instructions in use by the program. This is due to temporal and spatial locality - the former indicating that over a certain period of time there will be a number of commonly accessed elements and the latter that there is a high probability that if location x is read, location x+1 will also be read immediately. This working set is held in the cache and any requests for these data or instructions is satisfied from it without having to access the main memory. This serves to reduce the number of accesses made to the memory and, since the cache access time is normally much faster than main memory, allows the processor to run at a higher throughput. It is only forced to slow down when a request can not be satisfied by the cache and data has to be fetched from main memory.

Figure 1.2 : Cached and uncached CPUs

A cache may allow power to be saved by reducing the number of (expensive) accesses to main memory, replacing them with (cheaper) local accesses. A cached processor itself will, however, often consume **more** power than its uncached counterpart. This does not take account of the increased throughput and reduced power in the rest of the system. Overall, cacheing may be used as a power saving feature, with the additional benefit of faster operation, though when low power is relatively unimportant some cache designs will often sacrifice lower power for higher performance.

#### 1.4.2 Register and Operand Accessing

A microprocessor spends much of its time shifting data from one place to another, with some intermediate processing. The movement of data from place to place inevitably involves the use of buses, and the more global the bus the more power and time is required to drive it. To move data from the (off-chip) main memory to an (on-chip) cache costs around 10 times as much as moving data from the cache to the execution unit. This is due to the much higher capacitance of tracks on the PCB and the input load of other IC's, compared to interconnections within the same chip. This principal also applies on chip, but with proportionally lower costs; a processor's execution unit may fetch most of its operands from a register bank. Layout considerations result in a 64 entry register bank being further away from the execute unit than one with 16 entries.

Accesses to a larger register bank are likely to cost more in time and energy than for accessing a more compact and local 16 entry alternative.

#### 1.4.3 Operand size

The basic unit of information in a processor is normally the word. The word size is often used to classify the processor type, for example a 16- or 32-bit processor and indicates the size of the internal registers, and functional units that operate on them. It also indicates the width of the address bus for contemporary processors since address or pointer operations require the ability to perform arithmetic on complete addresses, and therefore the register width must be at least as wide as the address bus. Older 8-bit processors utilised 16-bit address buses and had to specify memory pointers using pairs of 8-bit registers. As the word size of processors increases it becomes more important to make full use of the available information content. Using a 64-bit register to manipulate small integers that could easily fit into an 8- or 16-bit register is wasteful since the entire 64-bit data path must be activated. Either the style of programming must improve to allow fuller use of the data path width, or the instruction encoding must allow the use of particular 'slices' of the register width. The Motorola 680x0 [52] is one example of a processor allowing byte, half word and word operations on its registers.

#### 1.4.4 Instruction Bandwidth and Density

Each operation a processor carries out is specified by an instruction read from memory. Once read it must be decoded to establish what operations must be carried out. The size of the instruction and the way in which the operation is encoded affects the ease of decoding. A 'typical' 32 bit RISC processor, such as the ARM or SPARC, uses a 32-bit fixed length instruction. The semantic content of the instruction will vary depending on the complexity of the operation required. A simple arithmetic operation such as the addition of two registers, writing the result to a third, may only need around 16 bits of information (4 bits to specify each register plus a further four for the operation); thus with a fixed 32-bit instruction approximately 50% of the instruction is unused. A more

complex operation such as the restoration of a number of registers from the stack following a procedure call may require a full 32 bits.

There is always a trade off between instruction compactness and ease of decoding. For the last 10 years, with the popularity of RISC processing, the latter has been considered more important. Recently however, studies evaluating instruction set compactness have demonstrated the apparent wastefulness of 32-bit fixed length instructions [29]. Section 2.6 looks at this in detail, with suggestions as to where the trade offs should be made.

#### 1.4.5 Uses and Effects of Pipelining

A simple processor will normally fetch an instruction, decode it and then carry out the specified operation, before beginning to fetch the next. Most of the processor therefore lies unused for much of the time. For example, while the next instruction is being fetched the decoding logic and ALU are not required.

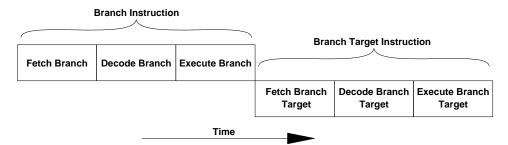

If a number of instructions are allowed to execute concurrently, each using a different part of the processor, the total time to execute one instruction stays approximately the same but the **rate** at which instructions complete increases. This is known as *pipelining*. Problems are encountered with pipelining when one instruction affects the execution of the next, for example a compare followed by a conditional branch. This is known as a *control hazard* and has to be detected to ensure that the correct result is generated. Similarly if a register is written to by an instruction and then read by the following one, care must be taken to ensure the correct ordering of the operations. This is known as a *data hazard*.

Data and control hazards reduce the throughput of the processor from its theoretical peak. For example, on average, the instruction stream normally consists of around 14% taken branches [30]. This means that a simple three stage pipeline (fetch, decode, execute) with a peak of 1 instruction per cycle actually ends up executing around 0.75 instructions per cycle, a 25% reduction on the peak rate. This is wasteful, since the

energy used for speculative execution past taken branches has generated no useful results. To enable a processor to approach its peak rate, branch prediction and other techniques must be employed to avoid pipeline stalls. These are discussed further in section 2.8 and chapter 3.

#### 1.4.6 Parallelisation

Most silicon designers optimise their systems for speed, and one possible technique is to employ circuit parallelisation to reduce the delays through the logic. For example a multiplier may well employ a simple adder, with control circuitry to implement multiplication by repeated addition. The use of multiple adders and carry save adders to merge results together in parallel clearly costs silicon area but can result in significant gains in speed. Another example of the application of parallelism is the ripple-carry adder. This has a very slow worst case delay which must be accommodated by the clock period. If a carry look-ahead adder is implemented, which calculates some or all of the carries in parallel, the worst case delay is reduced, allowing the clock period to be reduced.

If, instead of using parallel hardware to **increase** the throughput **at the same clock rate**, it is used to maintain the **same** throughput at a **lower clock rate** power savings might be made. Under these circumstances power is reduced by dropping the supply voltage [43]. As discussed earlier this will reduce the speed of the system but will also cause a proportionally greater reduction in power.

Pipelining a functional unit can also have a similar effect on clock rate requirements. If an adder operating in one pipeline period is split into two stages, and the previous clock rate is maintained, each stage caries out half the computation in the same time period and therefore can have a lower supply voltage. There is a slight area overhead due to the pipeline registers and an increase in the number of nodes driven, but even taking these into account Chandrakasan et. al. [43] estimate a power reduction of 2.5.

These techniques are of greatest interest in applications where there is a certain throughput requirement, and once this is met there is nothing to be gained by further speed improvements. For example a CODEC (COder-DECoder) or MPEG (a data format defined by the Motion Picture Experts Group for video compression) (de)compression chip. This may also apply to many microprocessor applications. In an application such as a PDA, once the response time for a particular task drops below a fraction of a second there is no point in increasing the speed any further.

#### 1.5 Conclusions

Both the circuit technology and architecture have major effects on the power consumed by a processor. Although they can both be considered in isolation, to achieve the best results they must both be addressed when designing a new processor and its support chips.

This thesis concentrates on the architectural impacts of processor design. The circuit level studies are not of principal interest and they will not be discussed further. The next chapter goes into more detail on the various components of a processor and how design decisions affect the power consumption of the finished product.

#### 2. Architectural Factors

The previous chapter discussed the general factors that affect the energy requirements of a system. Both circuit and architectural levels were considered; this chapter explores the impact of various architectural features in more detail, with suggestions as to where trade-offs and improvements can and should be made.

#### 2.1 Clock Rate

As mentioned in section 1.3.3 reducing the clock rate of a system will generally reduce the power consumption, but not the overall energy required for a task to be completed. In addition in a complex system different components can be run at differing rates depending on the processing required of them. The processor is obviously a prime candidate for varying the clock rate, as are the other related components such as the memory system, i/o controllers etc.

When a processor is running, monitoring the amount of useful processing is easy to achieve. For example, in a multi-tasking operating system, the scheduler can monitor the number of system calls or the CPU load, something already done in most systems (the CPU meter). The scheduler can then adjust the system clock rate to account for a lower CPU load (using either specific instructions, or an external programmable clock divider), or increase it if there is a sudden demand for processing. The rate at which this occurs can vary; with a fine grain scheme slowing the processor down between key presses is possible. The granularity refers to the rate at which the throughput is evaluated and the clock is adjusted.

Complete shutdown of the processor is more difficult, but obviously yields much greater savings when practical, ie where the processing occurs in bursts. Examples

might include an embedded system logging data periodically or a PDA which is turned 'off' most of the time, but is actually idling waiting for the user to interact with it. The shutdown is normally instigated by the execution of a *halt* or *wait* instruction and the restart by the occurrence of an interrupt. This is very common in micro-controllers oriented towards embedded systems. The other system components are likely to be controlled using programmable i/o.

Dynamic logic will enforce a lower bound on the clock rate of a system. This is because some of the internal state of the processor is held dynamically using the capacitive properties of the internal nodes. If the clock is taken away for more than a certain time these nodes will discharge and the processor will lose its state. In this case halting the processor completely requires some form of state saving and restoration. For example the MIPS R4200 [31] employs built in clock rate reduction by 75%, plus a state-saving power down mode. In a system built with DRAM (Dynamic Random Access Memory) and other dynamic peripherals, some form of refresh must always be present and for efficient processing on restart the cache contents may also have to be maintained.

The principal difficulty encountered with saving and restoring processor state is that the overheads involved are high, precluding fine grain use of the feature. Granularity refers to the size of the time step over which a change is made; the smaller the time step the finer the granularity of the control. MIPS however claim that the R4200 [31] takes only 10us to preserve total state.

#### **PowerPC**

The PowerPC 603 microprocessor has a very aggressive power-saving architecture. A number of shutdown features are present and these are;

• Doze mode puts the 603 into a state where all activity is stopped except for Time Base/Decrementer updates and bus snooping. Whilst in this mode a number of events, including an external asynchronous interrupt, a system management

interrupt, a decrementer interrupt, a reset (hard or soft), or a machine check will bring the 603 back to normal operation.

- Nap mode provides further savings, with only the Time Base operating. During the

Doze and Nap modes, the PLL (Phase-Locked Loop) continues to run and the

transition to the full-on state takes only a few processor cycles after an interrupt

assertion.

- Sleep mode provides the lowest power consumption. Whilst in this state no functional units are operating and in addition the PLL may be shut down. To return to normal operation the system logic enables the PLL again and then asserts an interrupt. In addition a hard or soft reset may return it to normal operation.

#### Intel 80x86

Intel's system-management mode (SMM) provides an extra interrupt line (SMI#) to allow a hardware timer to force a trap to power-management software. Many Intel processors are designed using static logic to allow the clock to be halted easily. Extra instructions also provide varying levels of power saving, for example to allow partial shutdown of the core while still carrying out cache snooping to maintain consistency in a multiprocessing environment.

All current processors are designed so that their peak heat output can be successfully dissipated by the packaging. If the processor instead specifies a maximum time it would be allowed to run at full speed, before slowing down, it would be possible to under-rate the packaging. This is unlikely to have a major impact on the usability of the system as most processing bursts would fit into the time periods allowed for full speed running. The throughput would only be affected in the event of a long period of sustained processing.

#### **Conclusions**

In most systems containing a microprocessor the processing requirements are sporadic. During periods of relative inactivity the best strategy must be a complete or partial shutdown of the system. This should give almost zero consumption during these times and may be the main strategy employed by PC manufacturers to make their PC's 'greener'. For machines that have a much higher average load, such as a file server, more radical solutions must be employed to reduce the power.

#### 2.2 Clock Gating and Distribution

Clock gating involves disabling the clock signal to a particular area of the chip and is employed in synchronous systems to cut the power consumed by functional units which are currently not required. A typical example might by the floating point unit, which is often idle but will continue to be clocked on every cycle. The gating is likely to be controlled by the instruction decoder, which, for each instruction cycle would only enable those blocks which require clocking.

Clock gating can be a solution to some of the problems of controlling power consumption but it does generate others. The main problem arises due to the extra skew and delay that is inserted into the clock path across the chip. Clock skew is the time difference between clock edges at different parts of the chip. This is already a significant problem for very high clock rate systems such as the DEC Alpha, where the 5ns clock period can tolerate a skew of only a fraction of a nanosecond across the whole chip. Careful simulation has been carried out to verify that the design, which has the clock driving 63000 separate loads, would function correctly. The addition of extra gate delays in the clock distribution introduces further skew, making this verification more difficult.

The PowerPC 603, as well as providing various features to control clock rate, also employs extensive clock gating on a number of units including the fixed- and floating point units, the system unit, the load/store unit and the caches.

Another factor which affects the possible savings to be made are the data buses and control lines that feed the clock-gated blocks. These large busses still have to drive the

capacitive loads present, even though the blocks are not using the information being presented to them.

#### **Conclusions**

The problems noted above have meant that, until recently, clock gating has not been popular as a power saving feature. For low speed systems and designs where the clock skew can be controlled, clock gating is beneficial. It is not clear what the control overhead would be for cycle-by-cycle gating, but it is likely much of the required control information is already evaluated in the normal instruction decoding.

Local clock generation might also be possible for functional units. This is similar to clock gating, since the unit is only operational when its local clock is activated, but where it differs is in the lack of synchronisation to the global clock. This embodies some of the ideas of asynchronous design, but with the implementational efficiency of a clocked design. Pipelining these functional units may however prove to be difficult.

#### 2.3 Cache Structure

The cache is a critical component of any processor, since its performance has a major impact on throughput [47]. In addition, it is accessed for virtually every cycle of the processor and its size (the cache often dwarfs the processor core) results in its consuming a significant proportion of the total power. Some of the factors to consider are:-

- Degree of associativity. A fully associative cache allows a data element to occupy any entry in the cache. The less associative the cache the more restrictions placed on the locations a particular entry may occupy. This also generally results in a larger cache being required to achieve the same hit rate. The hit rate is the percentage of accesses that are satisfied by the cache.

- Number of lines. A line may hold a number of sequential data words.

- The number of words per line. If there are few words per line the cache utilisation will be high but so will the proportion of silicon used for the tag, since every line requires a tag entry. Many caches have four words (16 bytes) per line. The longer the line the greater the likelihood of 'dead' or unused areas in the cache. It is normal to fetch a complete line on a cache miss; if data is fetched unnecessarily, power and memory cycles will be wasted. Long lines do however allow the exploitation of sequential transfer modes present in most DRAM devices; this saves power in comparison with the same number of 'discrete' accesses.

- Number of read and write ports. For memory-based architectures such as the Intel 80x86 the cache must normally have two read ports and one write port, to allow one instruction to read its arguments while another writes back its result. More ports may be needed if complex features such as non-blocking reads are to be supported. For RISC designs however most operands are sourced from a register bank, reducing the bandwidth required of the (data) cache and allowing fewer read and write ports.

- Write strategy. A cache is normally designed to be either write through or write back. The former directs all memory writes from the CPU direct to memory, updating the cache entry in parallel. The latter writes only to the cache, copying the contents back to memory at a later time. This significantly reduces the writes to external memory, saving bandwidth and power.

- Cache consistency. This is only an issue for multiprocessing systems that share memory. If one processor writes to memory while another holds a cached copy of the original data the latter needs to be told that its copy is no longer valid. There are many protocols suggested to allow support this, such as MESI (Modified, Exclusive, Shared, Invalid). Cache snooping will require extra accesses to check whether bus accesses refer to data present in the local cache, using more power. This may be significant where there are many processors communicating with each other via shared memory.

Cache structures vary from fully associative to direct mapped, with two or four set associativity being popular. The number of sets refers to the number of possible locations in the cache that an individual address can occupy. High degrees of associativity require some form of parallel lookup mechanism, usually implemented as a CAM (Content Addressable Memory). This allows a comparison of the address against all of the set entries in parallel. The power consumption of this block is generally affected by the hit detection mechanism. The 'hit' lines normally need to be precharged high on every cycle and then conditionally discharged if any bit fails to match. Lines that are not pulled low are then detected as a hit. Generally all but one of the hit/miss lines will be discharged on every cycle. It is difficult to build CAM cells whose outputs do not swing their outputs to the supply rails, and therefore use less energy to detect a hit. A fully associative cache is shown in figure 2.1.

Figure 2.1: Fully associative cache structure

For low associativity caches the construction is normally based on SRAM technology. A 4-way set associative cache is shown in figure 2.2. A lookup involves selecting a set, normally from 1 (Direct mapped) to 8 (8 way set associative) and then checking the tag to ensure validity. Although a CAM isn't required, large blocks of SRAM are used, which have long, highly capacitive busses that need large currents to drive them on every cycle. Simple schemes detect differential voltage swings using sense amplifiers. More advanced designs detect current differences in two lines to determine the data.

These are analogue components and consume a lot of power, but reduce the voltage swings on the long hit line busses to a fraction of a volt.

Figure 2.2 : Four-way set associative cache

The real benefit of using low associativity caches is that the access time of the cache is low. CAMs are slow due to the hit detection mechanism and the fact that the data must be accessed after the hit detection. A direct mapped cache allows the tag and the data to be accessed in parallel, with the hit detection being done at the same time as the reading of the data. This allows very fast access times, important for high clock rate processors. Of course, for power efficiency, the hit should be determined before the RAM is, possibly unnecessarily, accessed. If the hit rate is shown to be high enough however parallel accessing of the CAM and RAM may be acceptable. More importantly, accessing the tag RAM and data RAM in series can be slow; if the data RAM is accessed in parallel with the tag RAM however, all four words (in this example) must be read, with the tag contents selecting the required word at the end of the access. Thus four times as much data is read than is required on every read.

#### **Multi-Level Caches**

A simple single level cache is easy to build and provides reasonable hit rates, but to guarantee near 100% hit rates the cache needs to be very large. Often this can not be built as a single cache and so a secondary level of cacheing before the main memory is

added to 'catch' accesses that miss in the primary cache. This is often built off-chip and is direct mapped due to its size (256K bytes or more). The power-saving advantages of multi-level cacheing are less clear and need to be examined.

#### **Programming Style**

The hit rate of a cache can vary a great deal depending on the access patterns of the programs being run. Cache *thrashing* is a behaviour observed by some programs whose access patterns cause most entries to be thrown out of the cache before they are used again. This is particularly common with direct mapped and low associativity caches, where a large number of addresses map to only a few entries. Thrashing causes a great deal of power to be wasted, both in unsuccessful cache lookups and the resulting very high main memory traffic.

Many architecture handbooks, such as the DEC Alpha and MIPS documents, provide detailed guidelines on how to avoid the problems of thrashing, but this is rarely implemented automatically by the compiler. Because of the effects of thrashing, direct mapped caches have taken time to become widely adopted, but because they are easy to construct are now very popular.

#### **Conclusions**

Overall a cache may be used as a power saving feature in a processor because the energy required to access the cache can be much lower than that of main memory. However the cache will also be a major power consumer in a high speed processor. A large, fully associative cache with a simple hit detection mechanism will consume many watts of power and may actually be comparable with the energy costs of accessing main memory. This can be reduced by better hit detection mechanisms to reduce the effect of the inevitable cycling of long bus lines. These include current sense amps to allow swings of a fraction of a volt to be detected. Spatial locality should also be exploited to reduce the number of full lookups on the cache. This can be effective since the line length is chosen to make the best use of the CAM, but often a full lookup

is still carried out for each access in the line. If the sequential nature of program code is exploited, many of the cache lookups become unnecessary because of the knowledge that the previous access was a hit and therefore the current request may also hit the same line. The processor core can help the cache in establishing this by providing information to indicate when the address is sequential. It is not then necessary to compare the whole address, but only the lower bits to determine when line 'wrap around' has occurred.

If designed with low power in mind the use of a single cache can give good performance and power benefits, but there is still a large difference between the cost of a cache and a main memory access. The addition of one or more further caches allows a finer-grain memory hierarchy to be built. As an example consider a 2 level cache. Closest to the processor is a very fast, cheap cache designed to satisfy maybe 80% of accesses. This is low for many caches but at the next level out is a much larger cache, possibly with a completely different structure, designed to satisfy maybe a further 15%. The remaining 5% of accesses then have to be fetched from main memory. A problem here is that if an item is to be read from main memory a primary and secondary cache access still occurs, wasting power.

With the peak throughput of processors increasing faster than the access times of bulk memory, cache hit rates of better than 98% will become necessary if the processor performance is not to be degraded by cache misses.

# 2.4 Improving Pipeline Occupancy

The occupancy of a pipeline is important. On every clock period each stage in the pipeline evaluates a result based on the outputs of the previous stage. If the utilisation of the pipeline is low, with bubbles introduced due to data dependencies and taken branches, many of the results are never used. If this is the case a shorter pipeline with fewer interdependencies may give more efficient power utilisation. An example of this

is the MIPS R4400 eight stage 'super-pipeline' [48]. The branching mechanism has had to be very carefully designed to ensure only a two stage 'bubble' is introduced for a taken branch. For pipelined ALU's, interdependencies between one instruction and the next may cause the pipeline to halt whilst the previous instruction finishes. These problems are caused by the compiler's inability to separate the generation of results and their reuse in the code. Superscalar processors put even greater requirements on the compiler writers to extract the maximum instruction-level parallelism from the code to maintain power efficiency.

# 2.5 Register Usage

Virtually all instructions specify a number of operands which must be fetched, processed and then stored. The operands may be simple registers, constants or memory references. By far the most frequent access for a RISC processor is to a register, followed by constants and then memory references least of all. The architecture is likely to be optimised towards the former two access types, such that irrespective of the instruction type the processor will not need to stall. Towards this aim the register bank is likely to have the required number of read and write ports to satisfy all possible instructions, normally two reads and a write per cycle. For a non load-store architecture the frequency of memory operations increases dramatically, with many instructions allowed to specify a memory-addressed operand as a parameter. This is the case for the Intel x86 architecture and here, since the register bank is less well used, it may be acceptable to reduce the number of ports, requiring some infrequent instructions to take multiple cycles to read their operands. This will make it smaller, since fewer read buses and associated hardware are needed, and this in turn is likely to reduce the length of the remaining buses and any parasitic capacitances, making it more power efficient.

In a simple architecture all the reads and writes normally occur exactly as they are specified. Although the instructions specify a particular sequence of operations it may be that a different or simpler set of transfers can be used to achieve the same effect with

greater power efficiency. Reusing the last result of an arithmetic operation is one simple example. It has been shown [29] that 29% of ALU results are reused in the next operation, and 20% of produced results are only used once. Detection and use of this information provides the opportunity to reduce register bank operations, replacing them with much simpler result recycling.

Explicit result reuse, using an accumulator or similar structure would make this process simpler since the decode logic does not have to detect when reuse can occur, and allow a more compact instruction encoding. Extension of an accumulator into a stack, eg the T9000 [41], or a queue would allow a greater amount of flexibility in reuse, but with an increased cost for the simple case. The short term storage may well be no more than one or two entries, since it would be difficult to make use of these values across block boundaries especially for a queue. A stack is an example which can be used to pass parameters between code blocks, and the CRISP [32] (and the commercial version, called the Hobbit) optimises this by maintaining the top of the memory stack within a specific on-chip stack-cache.

Register renaming has been employed to increase performance by allowing speculative execution to proceed further. This is unlikely to have a significant effect on power dissipation, since it allows an increased amount of speculative execution, many of whose results will be later thrown away. The only beneficial effect this would have is to increase throughput, allowing the clock rate and therefore supply voltage to be lowered. Generally speculative execution must have a high probability of being correct or power will be wasted in generating incorrect results, ie the pipeline usage will be low.

#### Conclusions

Some form of result reuse is necessary for reducing accesses to the register bank. Whether the reuse is explicit, using an accumulator or set of accumulators, or detected by the operand fetching unit is perhaps not important, though explicit specification reduces the decode overhead but increases the instruction size.

# 2.6 Instruction Encoding

The choice of instruction encoding affects a number of parameters in the design of a processor:-

- The available memory bandwidth. The more compact the encoding the less instruction data needs to be fetched from the main memory and cache.

- The complexity of the instruction fetch unit. A compact instruction encoding invariably implies variable length instructions, which are likely to be more difficult to fetch and extract from cache lines than the fixed word-long RISC schemes.

- Instruction decoding. The more compact the encoding the more difficult it is to extract the required information. A simple 32-bit encoding often fixes the position of fields such as the source and destination register numbers, making extracting them trivial and allowing the decode stage to be very short, or non-existent.

Code size assessments have indicated that 32 bit RISC code occupies 150-200% of the space of its equivalent CISC code [30]. A simple test to measure the information content in a binary is to compress it with a standard compression tool, to remove any redundancy in the encoding. SPARC binaries show around a 55% size reduction, but this is likely to be an over estimate due the greater compressability of text embedded within the binary. A study of SPARC and 68020 code size [26] shows that for a number of Unix binaries the SPARC code was only 22% larger than its CISC equivalent. These figures are for **static** code size however, and for power and memory bandwidth it is the average **dynamic** size that is important for power consumption. A RISC instruction set is normally optimised for the frequently executing CISC instructions (the so called 20%-80% rule [30]), and therefore for a dynamic trace the semantic content and size of the average RISC instruction may be closer to that of a CISC instruction. Studies to back this up have not yet been carried out however.

An experiment conducted to measure the memory usage in a typical working environment showed that only approximately 40% of the memory usage of a Sun

workstation was for program space. This was for a simple setup of processes, with no major applications running. As applications are run the proportion of code space drops, showing that there is little incentive to increase the instruction compactness, at least for the purposes of reducing memory demands. Improved cache usage is however a more interesting benefit. A compact encoding will allow a larger working set to be maintained in the cache which will help to reduce the effects of cache thrashing.

Another incentive to improve code density is to reduce the required memory bandwidth for fetching instructions. This seems unimportant in cached systems where the cache supplies most of the instructions; when multi-processor systems which share a common bus to memory are constructed, instruction bandwidth does again become important since processors are competing for a share of a fixed bandwidth. The lower the individual demands of a processor the more processors can share a single bus. For example if a processor requires 20% of the bandwidth of a bus, up to four or five could share one bus to the shared memory system.

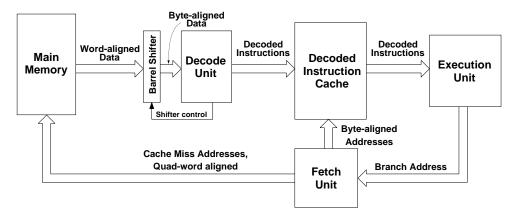

A decoded instruction cache (DINC) is one way of reducing the problem of reading non word-aligned instructions from memory (figure 2.3). This is a cache of pre-decoded instructions, normally of a fixed width, with information such as the source and destination operands stored in fixed positions. This means that almost all the required decoding for the execution pipeline is carried out 'in advance'; this reduces the depth of the main pipeline and removes the need to decode some instructions repeatedly. This is of benefit in loops and other repeating structures where an instruction would normally have to be decoded every time it is fetched from the cache. The reduction in pipeline depth also helps reduce the problems of pipeline latency; this causes wasted cycles when executing branches (see section 2.1.8).

Figure 2.3 : Decoded instruction cache structure

A DINC is likely to be byte addressed, differing from the main cache which is likely to be word or quad-word addressed.

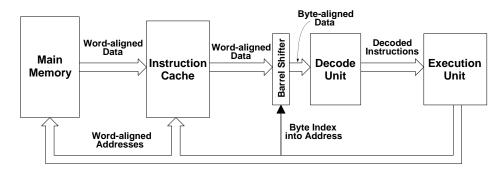

The alternative to a DINC is to decode after the cache (figure 2.4); this maybe of reduced size since the cache stores the instructions in the same compact form as main memory, but will increase the decoding requirement. This is the 'conventional' scheme with a standard cache. A barrel shifter is inserted before the decode unit to extract the instruction from the word-aligned data.

Figure 2.4: Non-decoded instruction cache structure

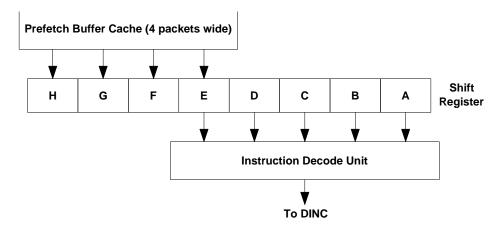

The barrel shifter must take in complete cache lines and provide instructions to the decode unit, one per clock cycle. This is a difficult task to accomplish, and is likely to result in the addition of a number of extra pipeline stages to the fetch unit, increasing the latency when a branch is taken. The CRISP [32] uses a small line cache to hold a number of 16 bit packets before the barrel shifter. This is shown in figure 2.5.

Figure 2.5: CRISP instruction alignment mechanism

An instruction occupies either one, three or five packets, and as each instruction is clocked into the decode unit the shift register moves to the right to occupy the 'holes' created. Whenever there is space in the shift register four packets are loaded into it from the prefetch buffer cache to keep it full. This mechanism allows one instruction per cycle to be delivered to the decode unit, except where two five packet instructions follow each other; the compiler should rarely need to generate this sequence.

Asynchronous techniques may be of benefit here to build a more efficient realignment mechanism. The addition of an elastic pipeline between the shifting register structure and the decode unit decouples the instruction fetch and realignment from the execute stages. This allows increased tolerance of sequences of full length instructions or stalls due to cache misses. Of course synchronising to this pipeline would then be difficult, and flushing of the queue could cause latency problems but it is an area that is worth investigation.

#### **Conclusions**

Extracting and decoding instructions could easily become a bottleneck in a variable length instruction processor. The shifting and queueing needed to extract the instructions from a word-aligned stream adds extra pipeline stages, possibly eliminating much of the power saved by the lower instruction bandwidth. The extra pipe stages also increase the latency of non-sequential instruction fetches after a break in the flow of

control. Some of these problems can be addressed by a byte-addressable cache, but an alignment mechanism would still be required.

Another limiting factor is that the lower bandwidth needed to execute a typical program may be largely offset by the extra decode overhead. In this case the instruction may be expanded into a fixed length form, which might be much larger than a standard 32 bit instruction. This is the case for the CRISP where the decoded format is 192 bits wide. The only appreciable gains then appear to be in better cache utilisation. The reduction in main memory requirements, which is largely static, do not seem significant.

A better choice may be to allow variable length instructions, but provide fewer variations, for example 2/4 bytes, to make the extraction simpler. However it may be that simplicity and regularity is best, with better use made of a fixed length instruction format.

# 2.7 Asynchronous Design

It has been suggested that asynchronous design offers significant advantages when building low power systems, because of its elimination of the global clock, a major power consumer in synchronous systems. The different parts of the processor can become autonomous, self-timed blocks, triggered only when required. This avoids many of the problems of global clock distribution together with the 'built-in' clock gating that occurs (functional units are only 'fired' when needed). In very high clock rate systems, clock gating (section 2.1.2) is difficult to incorporate because it increases the clock skew that is inevitably present. Asynchronous designs only 'clock' the required blocks when needed, so giving the same benefits of cycle-by-cycle clock gating in a synchronous system.

Asynchronous design works well where there are few interdependencies between blocks. If synchronisation is required significant time penalties are often incurred which are not easily hidden; it is therefore important to design an asynchronous pipeline with a smooth and rarely interrupted flow of information from one end to the other. It is also not clear whether the overheads of the asynchronous handshake signals outweigh the advantages gained by tolerance of infinitely variable delays.

The design of a branch predictor for an asynchronous processor is studied in depth later in this thesis.

# 2.8 Decision Making and Branching Strategy

Measured throughput of current simple and medium complexity processors is fairly low when compared to their theoretical peak. Many pipeline stalls occur due to program interdependencies and changes in the flow of control. The latter forces stalls and/or wasted effort due to incorrect speculative execution past the branch. A general term for a branch is a *control transfer instruction* (CTI). Efficient representation of the conditional code and the ability of the processor to evaluate, in advance, the likely flow of control, results in accurate speculative execution and therefore high power efficiency. The next chapter goes on to examine this in greater detail, exploring different ways of specifying loop and conditional structures and the possible ways of reducing the number of CTI's required in a program. Branch prediction strategies are also examined in terms of the power requirements and the improved performance obtained.

## 2.9 Conclusions

Clock rate reduction allows the throughput of the system to be closely matched to the processing load required. Asynchronous systems may do this automatically; if no processing is required the processor will 'stall' until the next request for an operation arrives. This stalling may result from an explicit instruction being executed; a polling loop in the program is an inefficient way of waiting for work to be done.

For asynchronous systems, although clock gating can be 'automatic', the problems of buses driving unused functional blocks remains (section 2.2). Buses in asynchronous

systems may, in general be kept local, however if a resource is shared, for example a write bus into a register bank, frequently driving a result onto it will be costly. This is offset however by the reduction in the number of 'ports' that need to be provided, in this example to the register bank.

A more compact instruction encoding may seem a reasonable way to improve cache usage and reduce the power consumed in fetching the instructions. However the overheads in implementing a variable length instruction processor such as the CRISP seem to give no noticeable benefits over a fixed length architecture such as the ARM when the final power consumption is compared (120mW for ARM700, 210mW for CRISP, with both providing similar throughput). This is likely to because the compact encoding has to be expanded quite early into a fixed length structure, often larger than a normal 32 bit instruction, and the extra stages that this adds to the pipeline can make flushes expensive. The CRISP mechanism of turning all instructions into branches, with destination addresses accompanying each instruction, is interesting but again seems to result in an overhead which cancels out many of the gains produced by branch folding.

In a pipelined system energy must be efficiently used. Pipelines should not be allowed to evaluate incorrect or unrequired results. This restricts the use of speculative execution since energy is wasted if the decisions made turn out to be incorrect. Strictly speaking unless predictions are 100% correct, power is wasted in comparison with a scheme which always stalls until a branch is resolved; few stalling architectures provide an acceptable throughput for current applications however. The branch mechanism chosen for an architecture and the way in which it is implemented will have a major effect on the efficiency of speculative execution. This is due to the high frequency of taken branches found in almost all instruction sequences. The next chapter examines instruction branch strategies in detail, together with an analysis of a number of branch prediction schemes, both past and current.

# 3. A Review of Instruction Branch Strategies