# LEARNING IN SPIKING NEURAL NETWORKS

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2012

By Sergio Davies School of Computer Science

## Contents

| Li              | st of [ | <b>Fables</b> |                                          | 6  |  |  |  |  |  |  |

|-----------------|---------|---------------|------------------------------------------|----|--|--|--|--|--|--|

| List of Figures |         |               |                                          |    |  |  |  |  |  |  |

| Li              | st of A | Algorith      | ıms                                      | 11 |  |  |  |  |  |  |

| Al              | bstrac  | et            |                                          | 12 |  |  |  |  |  |  |

| De              | eclara  | tion          |                                          | 13 |  |  |  |  |  |  |

| Co              | opyrią  | ght           |                                          | 14 |  |  |  |  |  |  |

| A               | cknow   | ledgem        | ients                                    | 16 |  |  |  |  |  |  |

| Tł              | he Au   | thor          |                                          | 19 |  |  |  |  |  |  |

| 1               | Intr    | oductio       | on to neural networks                    | 20 |  |  |  |  |  |  |

|                 | 1.1     | Neura         | l networks                               | 20 |  |  |  |  |  |  |

|                 |         | 1.1.1         | Biological neural networks               | 21 |  |  |  |  |  |  |

|                 |         | 1.1.2         | Artificial neural networks               | 23 |  |  |  |  |  |  |

|                 | 1.2     | Uses c        | of neural networks                       | 27 |  |  |  |  |  |  |

|                 | 1.3     | Adapt         | ability (plasticity) in neural networks  | 28 |  |  |  |  |  |  |

|                 |         | 1.3.1         | Plasticity in biological neural networks | 29 |  |  |  |  |  |  |

|                 |         | 1.3.2         | Plasticity in artificial neural networks | 32 |  |  |  |  |  |  |

|                 | 1.4     | Staten        | nent of the problem and objectives       | 36 |  |  |  |  |  |  |

|                 | 1.5     | Contri        | butions                                  | 37 |  |  |  |  |  |  |

|                 | 1.6     |               | ations                                   | 37 |  |  |  |  |  |  |

|                 |         | 1.6.1         | Journal articles                         | 37 |  |  |  |  |  |  |

|                 |         | 1.6.2         | Conference papers                        | 38 |  |  |  |  |  |  |

|   | 1.7  | Works    | hops, conferences and invited talks       | 40 |

|---|------|----------|-------------------------------------------|----|

|   | 1.8  | Structu  | are of the thesis                         | 42 |

| 2 | Neu  | ral netv | vork simulators                           | 44 |

|   | 2.1  | Introdu  | uction                                    | 44 |

|   | 2.2  | Catego   | prization of SNN simulators               | 44 |

|   |      | 2.2.1    | Hardware simulators                       | 45 |

|   |      | 2.2.2    | Software simulators                       | 47 |

|   |      | 2.2.3    | Learning in modern simulators             | 48 |

|   | 2.3  | Review   | v of main simulators developed            | 48 |

|   |      | 2.3.1    | Hardware                                  | 49 |

|   |      | 2.3.2    | Software                                  | 51 |

|   |      | 2.3.3    | SpiNNaker                                 | 54 |

|   | 2.4  | Summ     | ary                                       | 54 |

| 3 | SpiN | Naker    | project overview                          | 56 |

|   | 3.1  | Introdu  | uction                                    | 56 |

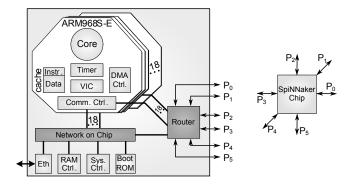

|   | 3.2  | Descri   | ption of the SpiNNaker project            | 56 |

|   | 3.3  | Hardw    | are                                       | 57 |

|   |      | 3.3.1    | Chip architecture                         | 57 |

|   |      | 3.3.2    | Chip interconnections                     | 59 |

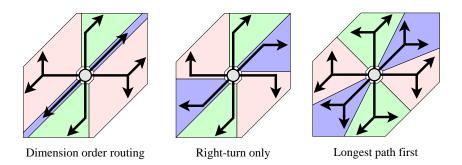

|   |      | 3.3.3    | Interconnection router                    | 61 |

|   |      | 3.3.4    | External connections                      | 65 |

|   |      | 3.3.5    | Boards                                    | 65 |

|   | 3.4  | Softwa   | are                                       | 68 |

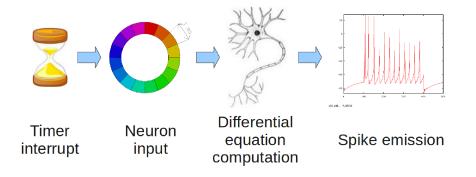

|   |      | 3.4.1    | The neuron simulator                      | 69 |

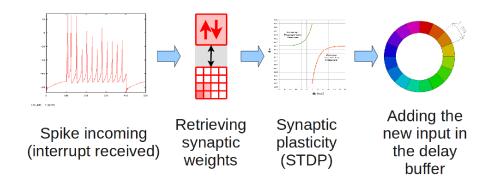

|   |      | 3.4.2    | The incoming spike handler                | 70 |

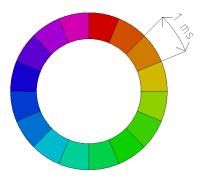

|   |      | 3.4.3    | A common point: the circular delay buffer | 71 |

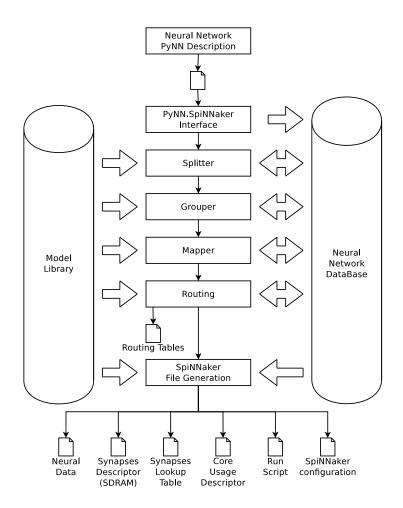

|   | 3.5  | Pacma    | n                                         | 72 |

|   | 3.6  | Neuro    | n models available                        | 74 |

|   |      | 3.6.1    | Izhikevich neuron                         | 74 |

|   |      | 3.6.2    | Leaky Integrate-and-Fire neuron           | 75 |

|   |      | 3.6.3    | Poisson spike source generator neuron     | 76 |

|   |      | 3.6.4    | Spike source neuron                       | 76 |

|   |      | 3.6.5    | Spike source live neuron                  | 76 |

|   |      | 3.6.6    | NEF interface neurons                     | 77 |

|   |      |          |                                           |    |

|   | 3.7  | Plasticity models available                                | 77 |

|---|------|------------------------------------------------------------|----|

|   | 3.8  | Summary                                                    | 77 |

| 4 | Spik | keServer                                                   | 78 |

|   | 4.1  | Introduction                                               | 78 |

|   | 4.2  | Real-time systems background and introduction              | 79 |

|   | 4.3  | Architecture of the SpiNNaker system                       | 80 |

|   |      |                                                            | 81 |

|   | 4.4  |                                                            | 81 |

|   | 4.5  |                                                            | 88 |

|   | 4.6  | Discussion                                                 | 90 |

|   | 4.7  | Summary                                                    | 91 |

| 5 | Рори | ulation-based routing                                      | 92 |

|   | 5.1  | Introduction                                               | 92 |

|   | 5.2  |                                                            | 92 |

|   | 5.3  |                                                            | 94 |

|   |      | 5.3.1 Multicast communications in SpiNNaker                | 94 |

|   | 5.4  |                                                            | 95 |

|   | 5.5  | Multicast route generation                                 | 99 |

|   |      | 5.5.1 Implementing LPF for the SpiNNaker system            | 01 |

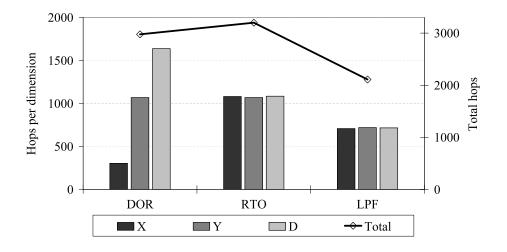

|   | 5.6  | Routing tests                                              | 02 |

|   |      | 5.6.1 One population per core, local projections only      | 03 |

|   |      | 5.6.2 One population per core, system-wide connectivity 10 | 04 |

|   |      | 5.6.3 The thalamocortical model                            | 05 |

|   | 5.7  | Discussion                                                 | 07 |

|   | 5.8  |                                                            | 10 |

| 6 | The  | STDP-TTS learning model 1                                  | 11 |

|   | 6.1  | Introduction                                               | 11 |

|   | 6.2  | Background                                                 | 12 |

|   |      | 6.2.1 Introduction to synaptic plasticity                  | 12 |

|   |      | 6.2.2 Learning in biological neural networks               | 13 |

|   |      | 6.2.3 Algorithmic techniques for synaptic plasticity       | 16 |

|   | 6.3  | Architecture of the SpiNNaker system                       | 19 |

|   | 6.4  | The STDP TTS learning rule                                 | 20 |

|   | 6.5  | Statisti | cal feature extraction                       | 121        |

|---|------|----------|----------------------------------------------|------------|

|   |      | 6.5.1    | Post-processing of the statistical function  | 122        |

|   |      | 6.5.2    | The STDP-TTS learning algorithm              | 125        |

|   | 6.6  | Networ   | rk description and input generation          | 125        |

|   | 6.7  | Simula   | tion results from SpiNNaker                  | 128        |

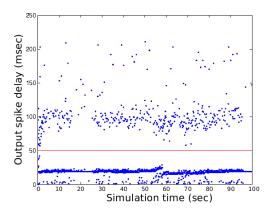

|   | 6.8  | Manipu   | lation of the "L" parameter                  | 131        |

|   | 6.9  | Observ   | ations on the learning behaviour             | 132        |

|   | 6.10 | Influen  | ce of the parameters                         | 145        |

|   |      | 6.10.1   | Increasing maximum synaptic weight           | 145        |

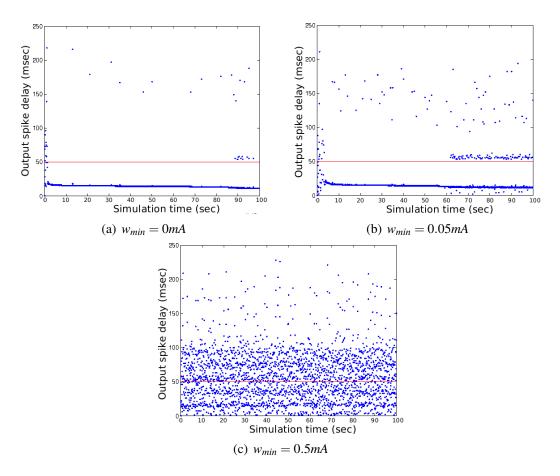

|   |      | 6.10.2   | Incrementing minimum synaptic weight         | 145        |

|   |      | 6.10.3   | Incrementing LTP amplitude parameter         | 147        |

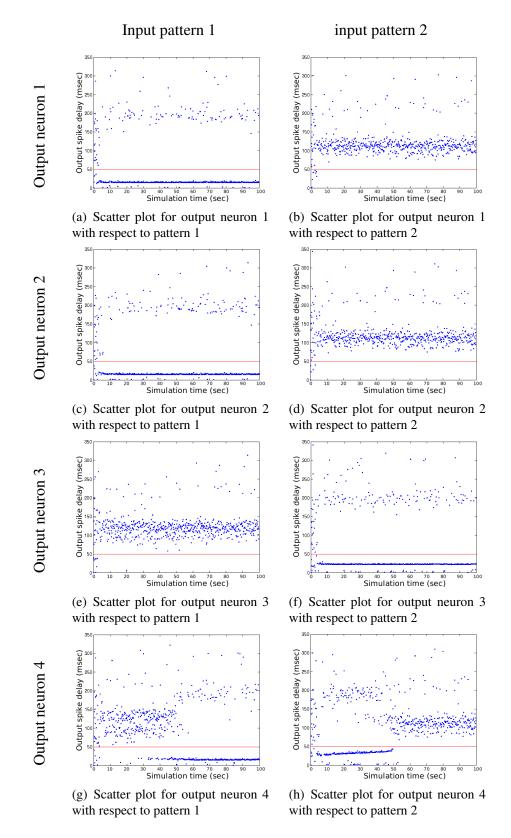

|   | 6.11 | Multip   | le input patterns                            | 147        |

|   | 6.12 | Perform  | nance evaluation                             | 150        |

|   |      | 6.12.1   | Computational requirements                   | 150        |

|   |      | 6.12.2   | Memory occupation                            | 153        |

|   | 6.13 | Discus   | sion                                         | 154        |

|   | 6.14 | Summa    | ary                                          | 156        |

| 7 | Cond | lusion   | and future work                              | 157        |

|   | 7.1  |          | ikeServer evolution: multiple channels       | 157        |

|   | 7.2  |          | nfiguring SpiNNaker                          | 157        |

|   | 7.3  |          | DP TTS learning rule                         | 150        |

|   | 7.4  |          | work                                         | 160        |

|   | 7.1  | 7.4.1    | Dynamic adaptation of the learning parameter | 160        |

|   |      | 7.4.2    | The re-fetch model                           | 160        |

|   |      | 7.4.3    |                                              |            |

|   |      | 7.4.4    | Other plasticity models                      | 161        |

|   | 7.5  |          | ic rewiring and structural plasticity        | 162        |

|   | 1.5  | 7.5.1    | Synaptogenesis                               | 162        |

|   |      | 7.5.2    | Synaptic pruning                             | 162        |

|   | 7.6  |          |                                              | 163<br>164 |

|   | 1.0  | Summa    | ary                                          | 104        |

Word Count: 37306

## **List of Tables**

| 1.1 | Comparison between spiking neuron models (Izhikevich, 2004)                                                                                                                           | 26  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Comparison between features of spiking neural network simulators.<br>Question marks identify features that were not easily possible to asso-<br>ciate with the particular simulators. | 55  |

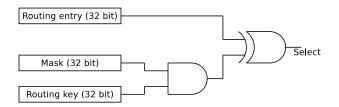

| 3.1 | Matching condition on the basis of the fields "Routing entry" and "Mask", as described in Fig.3.7                                                                                     | 62  |

| 3.2 | Table of direction for multicast routing entries. The vectors are OR-ed to multicast the same packet to multiple directions                                                           | 63  |

| 3.3 | Table of directions for Point to Point routing entries                                                                                                                                | 64  |

| 5.1 | Set of routing keys used and unused for each size of the neural population.                                                                                                           | 97  |

| 5.2 | Example of routing for three neural populations                                                                                                                                       | 98  |

| 6.1 | Computation requirements for each learning algorithm (values are approximated).                                                                                                       | 151 |

| 6.2 | Example of memory requirements for each learning algorithm in the case of 100 neurons each receiving input from other 100 neurons                                                     | 154 |

| 7.1 | Comparison of computational requirements and memory occupation for the three learning algorithms available on SpiNNaker                                                               | 159 |

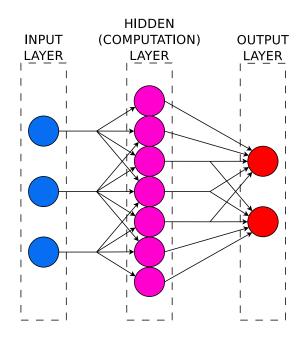

| 1.1  | General structure of a simple feed-forward artificial neural network.   |    |

|------|-------------------------------------------------------------------------|----|

|      | Each coloured disc is a neuron, and each arrow is a synapse             | 20 |

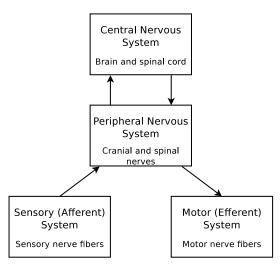

| 1.2  | Simplified structure of the nervous system in vertebrate animals        | 22 |

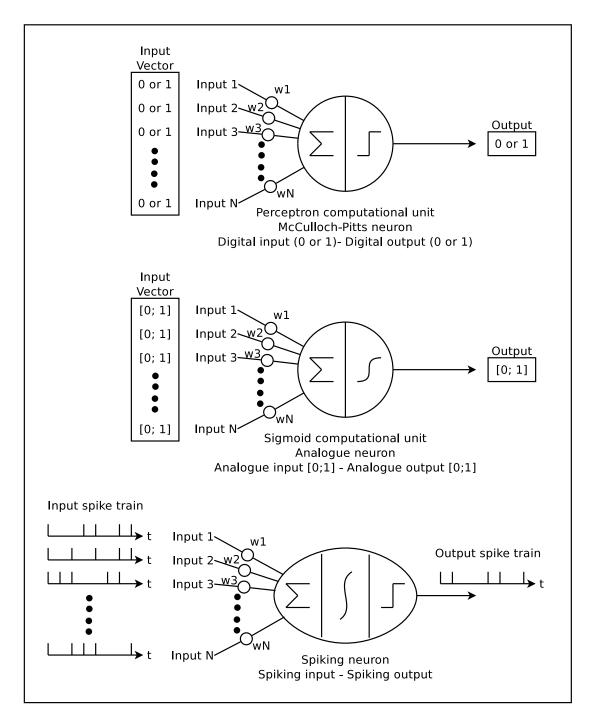

| 1.3  | Classes of artificial neurons.                                          | 24 |

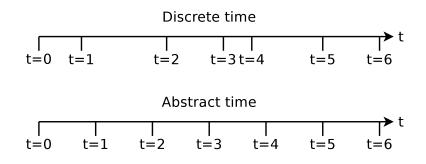

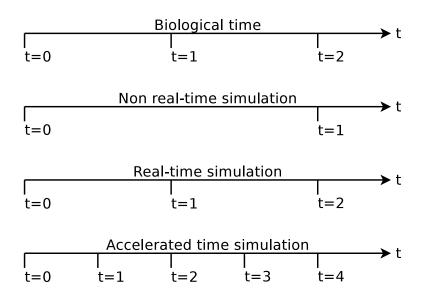

| 2.1  | Difference between abstract-time simulator and discrete-time simulator. | 46 |

| 2.2  | Relation between simulation time and biological time                    | 47 |

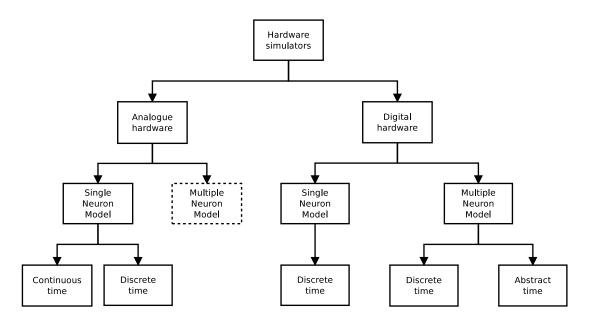

| 2.3  | Hierarchical representation of hardware neural network simulators       | 48 |

| 2.4  | Hierarchical representation of software neural network simulators       | 49 |

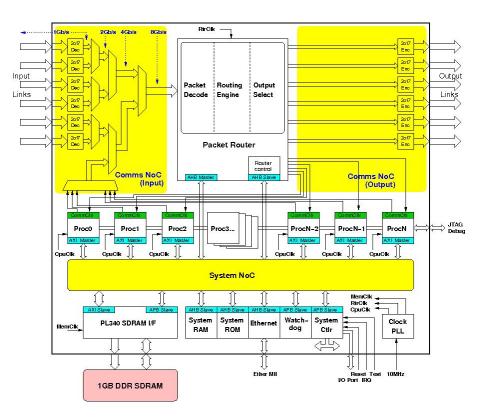

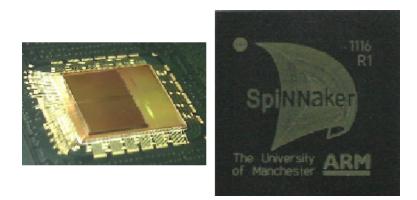

| 3.1  | Block diagram of the full SpiNNaker chip                                | 58 |

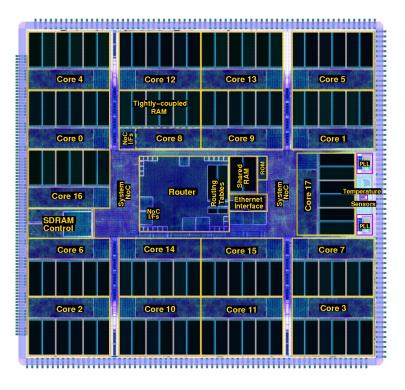

| 3.2  | Layout of the SpiNNaker chip with labels identifying each functional    |    |

|      | block                                                                   | 58 |

| 3.3  | SpiNNaker chip package: the die of the SDRAM memory chip is             |    |

|      | mounted on the top of the SpiNNaker chip.                               | 59 |

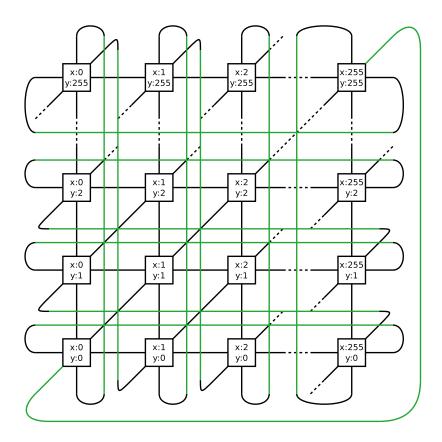

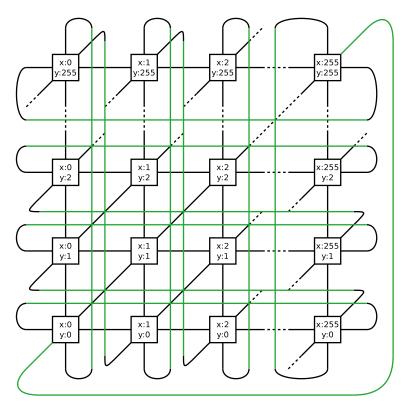

| 3.4  | Two-dimensional grid of SpiNNaker chips with the needed connec-         |    |

|      | tions (in green) to form the toroidal shape                             | 60 |

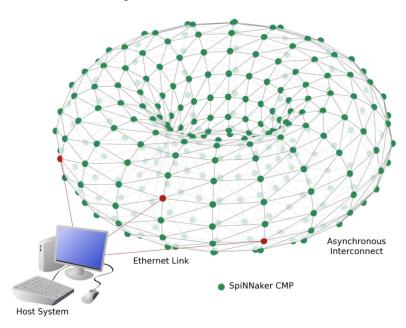

| 3.5  | Appearance of the SpiNNaker chip network                                | 60 |

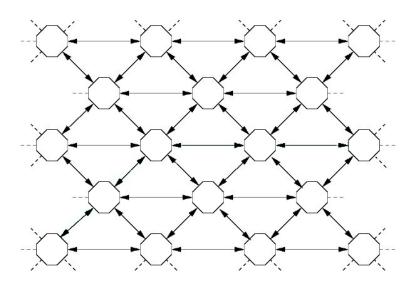

| 3.6  | Hexagonal shaped SpiNNaker chip network                                 | 61 |

| 3.7  | Circuit used to select a matching routing entry.                        | 62 |

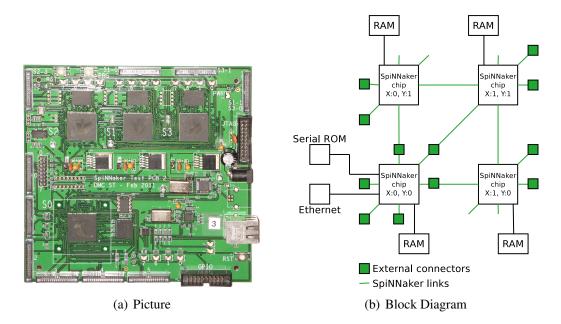

| 3.8  | First release of the SpiNNaker board                                    | 66 |

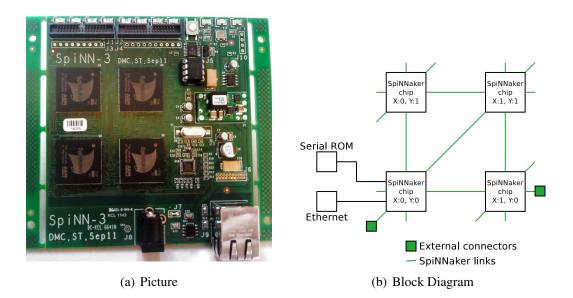

| 3.9  | "BunnyBoard"                                                            | 66 |

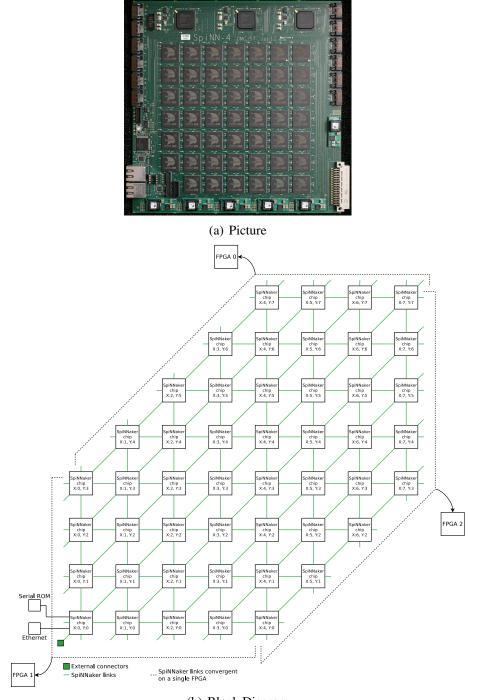

| 3.10 | 48-chip SpiNNaker board.                                                | 67 |

| 3.11 | Block description of SpiNNaker neuron simulator software                | 69 |

| 3.12 | Description of the routing key structure.                               | 70 |

| 3.13 | Block description of SpiNNaker incoming spike handler software          | 70 |

| 3.14 | Depiction of the circular buffer used for simulating the synaptic delay | 72 |

| 3.15 | Block diagram of the partition and configuration software (PACMAN).     | 73 |

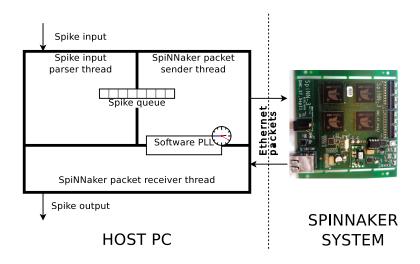

| 4.1  | Schematic diagram of the SpikeServer software                            | 82  |

|------|--------------------------------------------------------------------------|-----|

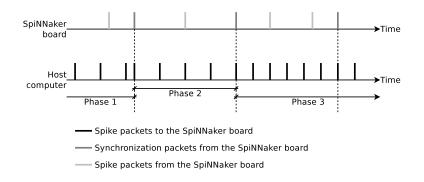

| 4.2  | Diagram of the phases of the software PLL (see the description in the    |     |

|      | text)                                                                    | 86  |

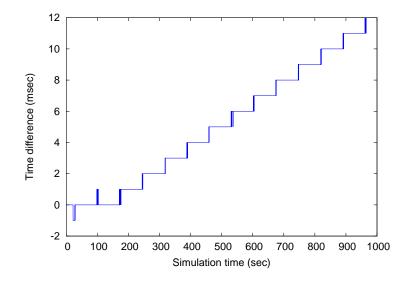

| 4.3  | Depiction of time drift between the host and the SpiNNaker board. No     |     |

|      | synchronization routine is used in this experiment                       | 88  |

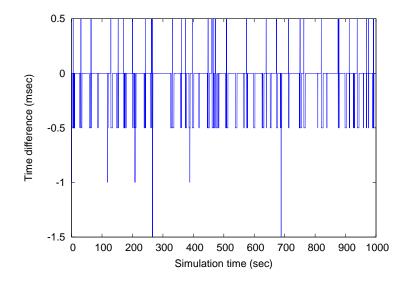

| 4.4  | Depiction of time drift between the host and the SpiNNaker board,        |     |

|      | with the software PLL synchronization technique applied                  | 89  |

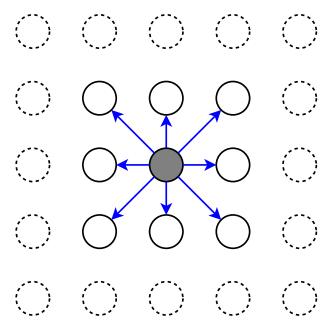

| 5.1  | Schematic of the SpiNNaker chip with the view of the routing directions. | 95  |

| 5.2  | Description of the routing key structure                                 | 95  |

| 5.3  | Two-dimensional grid of SpiNNaker chips with the needed connec-          |     |

|      | tions (in green) to form the toroidal shape                              | 98  |

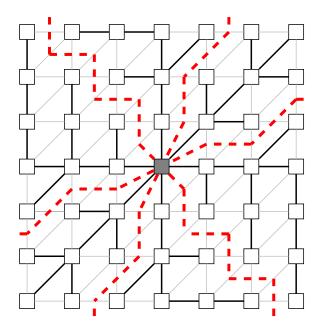

| 5.4  | Shape of the routes generated with each algorithm                        | 99  |

| 5.5  | Network resources needed by each algorithm.                              | 100 |

| 5.6  | Links selectable by the "Longest Path First" algorithm.                  | 101 |

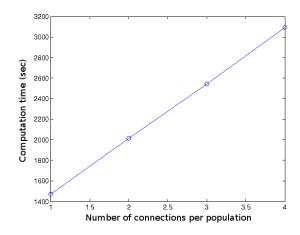

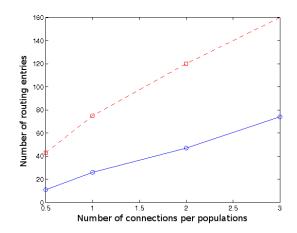

| 5.7  | Results of the routing test with local projections only. The graph       |     |

|      | presents the linear relation between the number of connections per       |     |

|      | source population (inter-population connections) and the time required   |     |

|      | for the computation (in seconds).                                        | 103 |

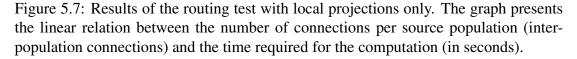

| 5.8  | Results of the routing test with long-range projections only. The graph  |     |

|      | presents the relationship between the number of connections per source   |     |

|      | population (inter-population connections) and the time required for the  |     |

|      | computation (in seconds).                                                | 104 |

| 5.9  | Results of the routing test with long-range projections only. The graph  |     |

|      | presents the relationship between the number of connections per source   |     |

|      | population (inter-population connections) and the number of entries in   |     |

|      | the routing tables. The blue solid line with circles represents the min- |     |

|      | imum number of routing entries. The red dashed line with squares         |     |

|      | represents the maximum number of routing entries                         | 105 |

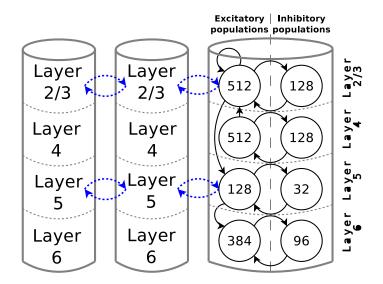

| 5.10 | Details of the thalamocortical model test.                               | 106 |

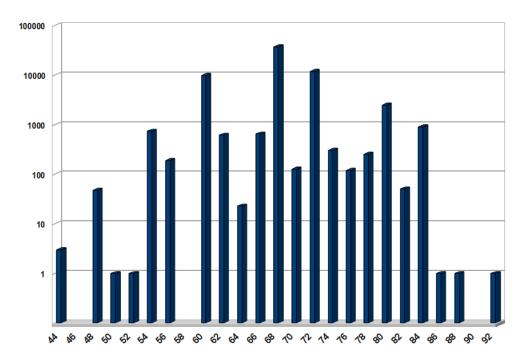

| 5.11 | Histogram of the number of entries in the routing tables. On the hori-   |     |

|      | zontal axis the number of entries in the routing tables. On the vertical |     |

|      | axis the number of occurrences for the particular number of entries.     | 108 |

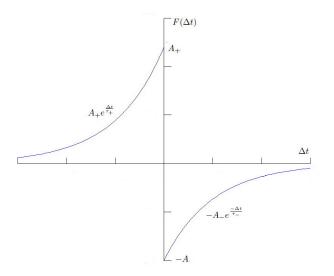

| 6.1  | STDP curve. The horizontal axis represents the time between pre- and                       |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | post-synaptic spikes ( $\Delta t = t_{pre} - t_{post}$ ). The vertical axis represents the |     |

|      | synaptic weight modification.                                                              | 114 |

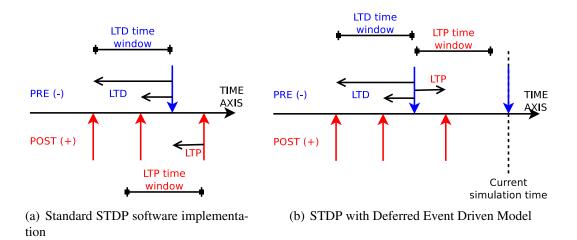

| 6.2  | Implementation of the standard STDP learning rule                                          | 120 |

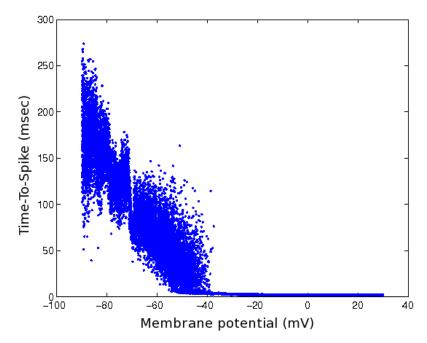

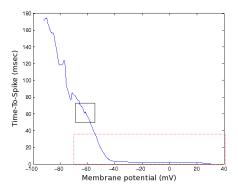

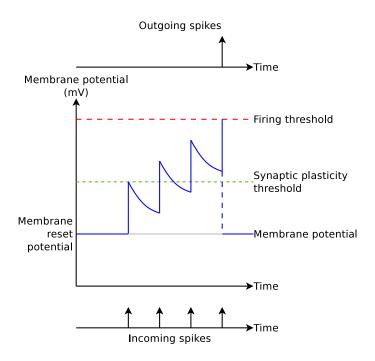

| 6.3  | Example of computation of the Time-To-Spike (TTS) of a neuron                              | 121 |

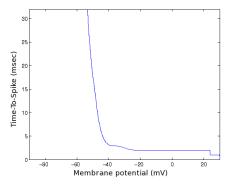

| 6.4  | Function that relates the membrane potential in $mV$ (on the horizontal                    |     |

|      | axis) and the estimated time to spike in <i>msec</i> (on the vertical axis)                | 123 |

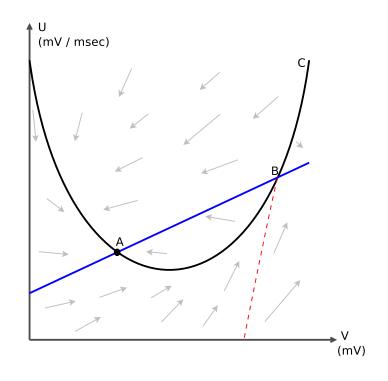

| 6.5  | Izhikevich neuron state phase plane The horizontal axis is the mem-                        |     |

|      | brane potential variable <i>v</i> . The vertical axis is the membrane recovery             |     |

|      | variable <i>u</i> . The black parabola represents the nullcline for the $\dot{v}$ equa-    |     |

|      | tion. The blue line represents the nullcline for the $\dot{u}$ equation. The red           |     |

|      | dashed line represents the separatrix between the attraction domain of                     |     |

|      | the equilibrium point A (left of separatrix) and the domain where the                      |     |

|      | neuron reaches eventually the spiking condition (right of separatrix)                      | 124 |

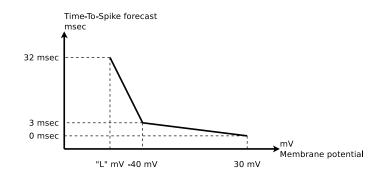

| 6.6  | Relation between membrane potential and time to spike of the neuron.                       | 125 |

| 6.7  | Depiction of LTP trigger mechanism                                                         | 126 |

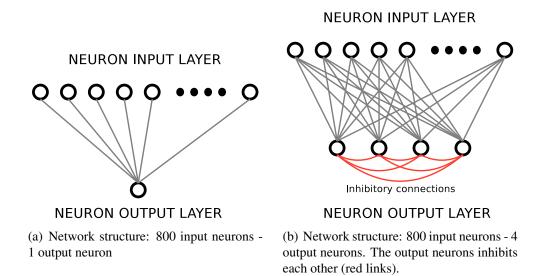

| 6.8  | Structure of the neural networks used in the tests: 800 input neurons                      |     |

|      | and 1 or 4 output neurons.                                                                 | 127 |

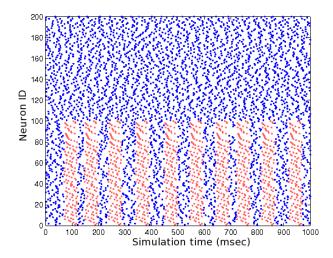

| 6.9  | Example of raster plot of the input pattern for an input layer of 200                      |     |

|      | neurons and pattern sent to the first half of this population. The input                   |     |

|      | pattern is highlighted in red. In the simulation the input was generated                   |     |

|      | for 800 input neurons of which only half will receive the input pattern.                   | 128 |

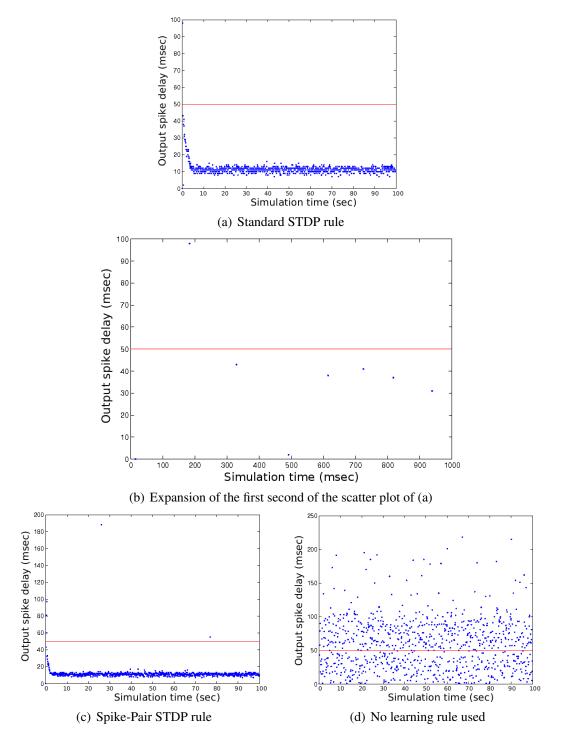

| 6.10 | Scatter plots for simulations using various learning rules                                 | 130 |

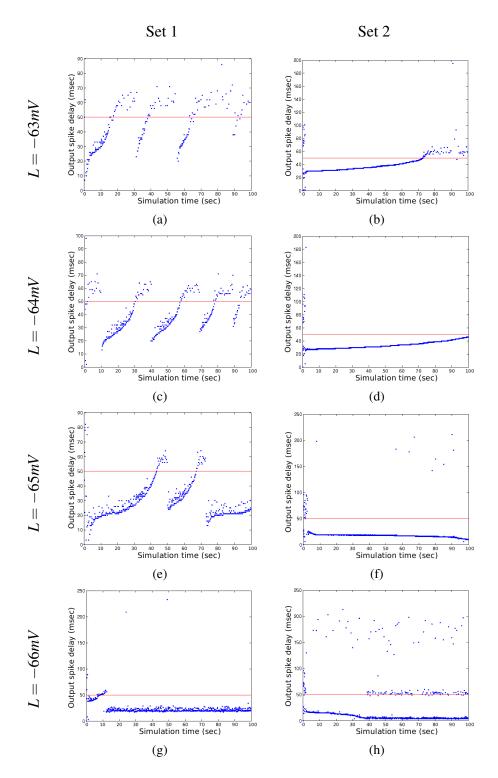

| 6.11 | Scatter plots for STDP with TTS forecast - $-66mV \le L \le -63mV$ .                       |     |

|      | Set 1 has synaptic weights in the interval $[0; 0.4]mA$ . Set 2 has synaptic               |     |

|      | weights in the interval $[0; 1.5]mA$                                                       | 133 |

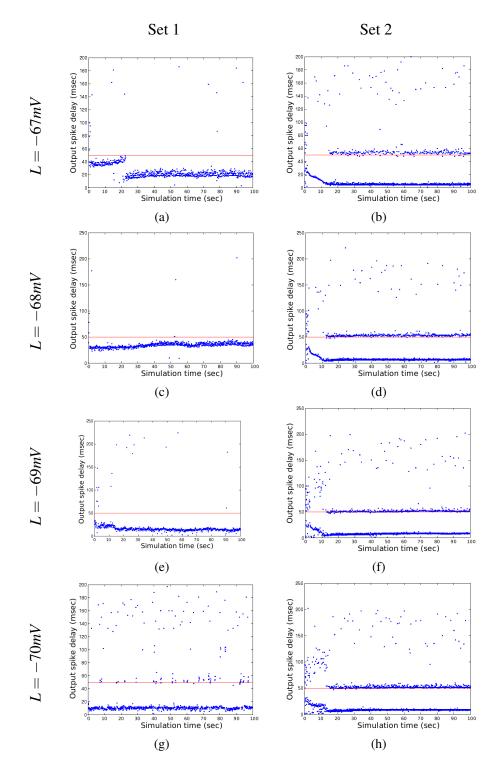

| 6.12 | Scatter plots for STDP with TTS forecast - $-70mV \le L \le -67mV$ .                       |     |

|      | Set 1 has synaptic weights in the interval $[0; 0.4]mA$ . Set 2 has synaptic               |     |

|      | weights in the interval $[0; 1.5]mA$                                                       | 134 |

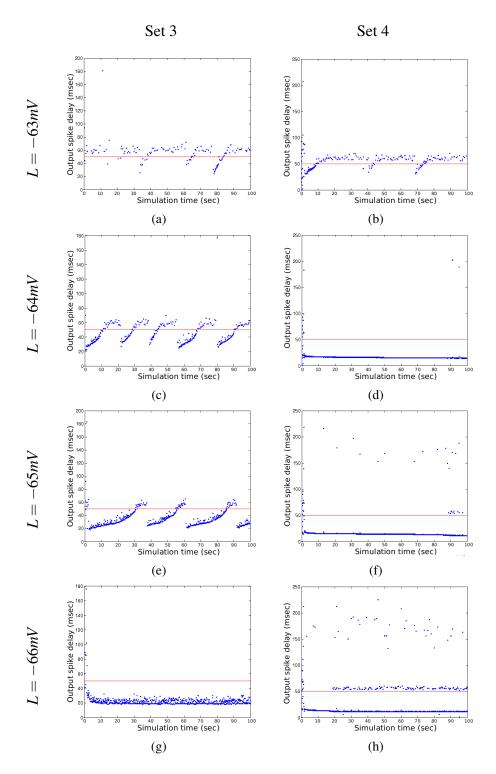

| 6.13 | Scatter plots for STDP with TTS forecast - $-66mV \le L \le -63mV$ . Set                   |     |

|      | 3 has synaptic weights in the interval $[0;0.4]mA$ . Set 4 has synaptic                    |     |

|      | weights in the interval $[0; 1.5]mA$ . The seed of the random number                       |     |

|      | generator used to generate the input and the initial synaptic weights                      |     |

|      | for both sets of experiments has been changed from the experiments in                      |     |

|      | Fig.6.11 and 6.12                                                                          | 135 |

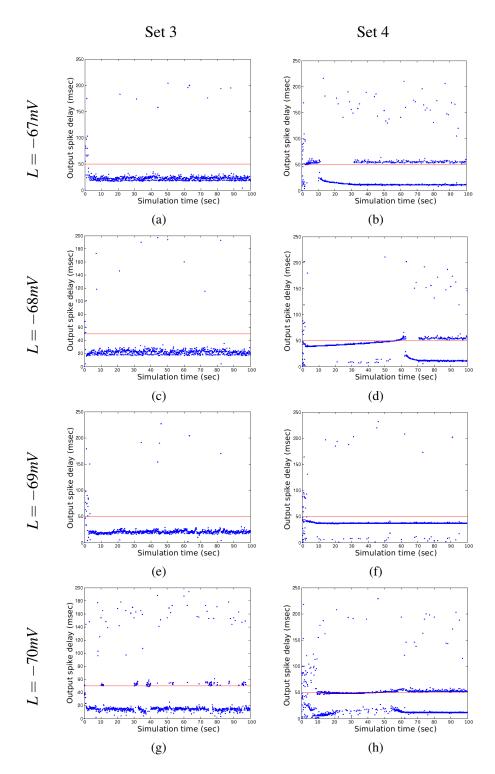

| 6.14 | Scatter plots for STDP with TTS forecast - $-70mV \le L \le -66mV$ . Set |     |

|------|--------------------------------------------------------------------------|-----|

|      | 3 has synaptic weights in the interval $[0; 0.4]mA$ . Set 4 has synaptic |     |

|      | weights in the interval $[0; 1.5]mA$ . The seed of the random number     |     |

|      | generator used to generate the input and the initial synaptic weights    |     |

|      | for both sets of experiments has been changed from the experiments in    |     |

|      | Fig.6.11 and 6.12                                                        | 136 |

| 6.15 | Scatter plot of a network with 100 input neurons using the STDP TTS      |     |

|      | learning rule.                                                           | 137 |

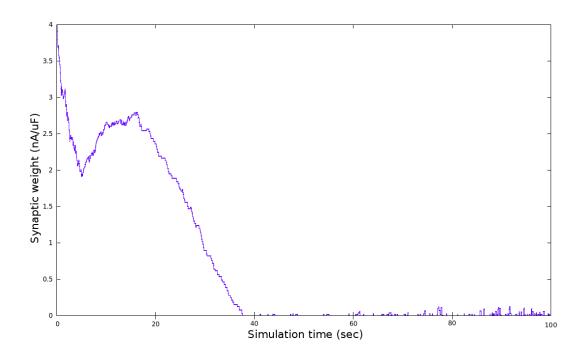

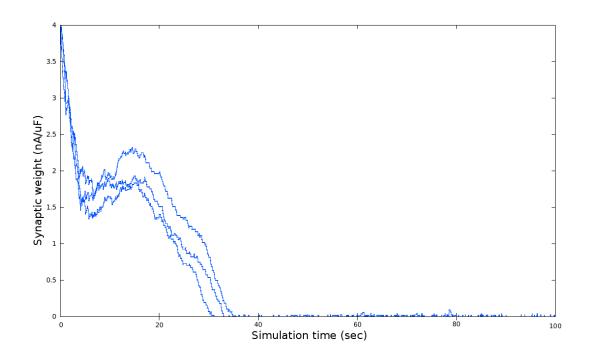

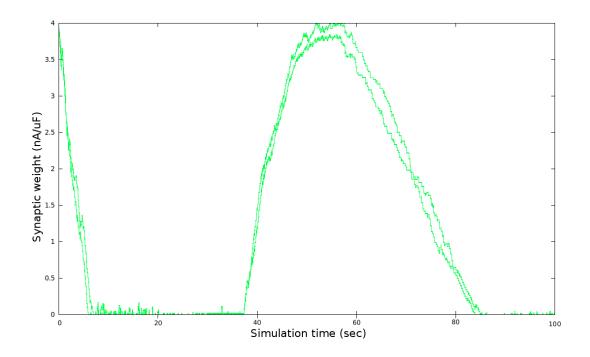

| 6.16 | Evolution of the weights for the synapses that carry only noise          | 138 |

| 6.17 | Representation of the input pattern.                                     |     |

|      | Each row represents the input to each single neuron. Each column rep-    |     |

|      | resents the input injected in each millisecond for all the neurons. A    |     |

|      | "1" in the matrix (highlighted by a red cell) identifies a spike emitted |     |

|      | by a specific input neuron in a specific millisecond. The last row iden- |     |

|      | tifies the number of spikes which the output neuron receives in each     |     |

|      | millisecond. The last column marks the neurons which send multiple       |     |

|      | input spikes in a single pattern                                         | 139 |

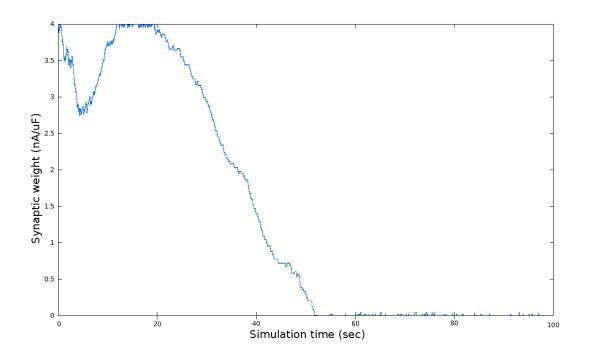

| 6.18 | Evolution of the weights for the synapse of input neuron 22, millisec-   |     |

|      | ond 12 of the pattern                                                    | 141 |

| 6.19 | Evolution of the weights for the synapse of input neuron 34, millisec-   |     |

|      | ond 16 of the pattern                                                    | 141 |

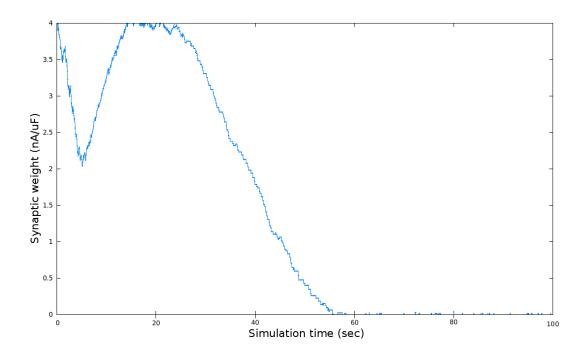

| 6.20 | Evolution of the weights for the synapse of input neurons 11, 24 and     |     |

|      | 46, millisecond 23 of the pattern                                        | 142 |

| 6.21 | Evolution of the weights for the synapse of input neuron 42, millisec-   |     |

|      | ond 24 of the pattern.                                                   | 142 |

| 6.22 | Evolution of the weights for the synapse of input neuron 16, millisec-   |     |

|      | ond 25 of the pattern.                                                   | 143 |

| 6.23 | Evolution of the weights for the synapse of input neurons 39 and 45,     |     |

|      | millisecond 37 of the pattern.                                           | 143 |

| 6.24 | Scatter plot using the STDP TTS learning algorithm changing the min-     |     |

|      | imum allowed synaptic weight                                             | 146 |

| 6.25 | Scatter plot using a learning rule with the STDP curve that uses $A_+ =$ |     |

|      | 0.3, while the other parameters are set as before                        | 147 |

| 6.26 | Scatter plots for STDP with TTS forecast - two input patterns, four      |     |

|      | output neurons.                                                          | 149 |

# **List of Algorithms**

| 1 | Error backpropagation                                  | 34  |

|---|--------------------------------------------------------|-----|

| 2 | Parser of the spikes to be sent to the SpiNNaker board | 83  |

| 3 | Sender of the spikes to the SpiNNaker system.          | 84  |

| 4 | Data receiver from the SpiNNaker system                | 85  |

| 5 | Timer resynchronization routine                        | 87  |

| 6 | The Spike Timing Dependent Plasticity (STDP) algorithm | 117 |

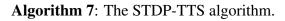

| 7 | The STDP-TTS algorithm.                                | 126 |

Abstract

### Abstract

### LEARNING IN SPIKING NEURAL NETWORKS

Sergio Davies A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy, 2012

Artificial neural network simulators are a research field which attracts the interest of researchers from various fields, from biology to computer science. The final objectives are the understanding of the mechanisms underlying the human brain, how to reproduce them in an artificial environment, and how drugs interact with them. Multiple neural models have been proposed, each with their peculiarities, from the very complex and biologically realistic Hodgkin-Huxley neuron model to the very simple "leaky integrate-and-fire" neuron. However, despite numerous attempts to understand the learning behaviour of the synapses, few models have been proposed. Spike-Timing-Dependent Plasticity (STDP) is one of the most relevant and biologically plausible models, and some variants (such as the triplet-based STDP rule) have been proposed to accommodate all biological observations. The research presented in this thesis focuses on a novel learning rule, based on the spike-pair STDP algorithm, which provides a statistical approach with the advantage of being less computationally expensive than the standard STDP rule, and is therefore suitable for its implementation on stand-alone computational units. The environment in which this research work has been carried out is the SpiNNaker project, which aims to provide a massively parallel computational substrate for neural simulation. To support such research, two other topics have been addressed: the first is a way to inject spikes into the SpiNNaker system through a non-real-time channel such as the Ethernet link, synchronising with the timing of the SpiNNaker system. The second research topic is focused on a way to route spikes in the SpiNNaker system based on populations of neurons. The three topics are presented in sequence after a brief introduction to the SpiNNaker project. Future work could include structural plasticity (also known as synaptic rewiring); here, during the simulation of neural networks on the SpiNNaker system, axons, dendrites and synapses may be grown or pruned according to biological observations.

Declaration

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

### Copyright

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx? DocID=487 ), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.man chester.ac.uk/library/aboutus/regulations ) and in The University's policy on presentation of Theses

To Nathaële, for her support and patience. To William and Maria Rosaria, for their help and encouragement.

### Acknowledgements

I wish to thank all those who helped me getting to the University of Manchester: my parents, Nathaële, and all the friends who encouraged and supported me in following my idea (sometime, giving me a kick and encouraging me to move on). The names are too many to list here, so that I realize right now how many friends I can count on. A particular acknowledgement goes to Leslie who helped me with my English, when, at the beginning of this adventure, it was far from being reasonable!

And a big thank you goes to all those people that I met during my stay in Manchester and that have been with me during these three years, who celebrated with me achievements and who helped me to relax when I was too stressed.

In the same way, I cannot forget all the friends that from Italy have always continued to give me their support even at 3,000*Km* distance!

Secondly, but not in importance, a big thank you to everyone at the University of Manchester who helped me in completing this course.

I would like to thank my supervisor, Professor Steve Furber, for his precious guide during this Ph.D. course.

Also a kind "Thank you!" goes to Dr. Jim Garside, my co-supervisor, a very helpful guide who has always been free for long discussions.

Special thanks go to Dr. John Viv Woods, for all the cooperation in preparing this thesis and for patiently proof-reading all the papers that I have written for publication. In particular I admire that he has always a smile on his face and a joke to say to keep up the spirit.

A kind thank you goes to all those within the SpiNNaker group (and broader within the APT group) who supported me during these three years, introducing me to the neural network community. Some of them became friends even out of the lab, with a beer or a badminton racket in the hand! In particular I would like to thank Alexander Rast, Cameron Patterson, Javier Navaridas, Luis Plana and Thomas Sharp (alphabetically sorted) for making these three years always interesting.

#### Acknowledgements

I am grateful to the Engineering and Physical Science Research Council (EPSRC) which funded my Ph.D. course.

A "Thank you!" also goes to Dr. David Lester, who introduced me to wine tasting. Some days it became hard to work after those kind of practical lessons!

Another <u>special</u> "Thank you!" goes again to Professor Steve Furber for funding my travels around the globe for research and presentations:

- 25th April 2010 8th May 2010 CapoCaccia cognitive neuromorphic engineering workshop Capocaccia, Sardinia, Italy;

- 27th June 2010 14th July 2010 Telluride neuromorphic cognition engineering workshop — Telluride, Colorado, U.S.A.;

- 18th July 2010 23rd July 2010 International Joint Conference on Neural Networks (IJCNN) 2010 held within the World Congress on Computational Intelligence (WCCI) 2010 — Barcelona, Spain;

- 4. 22nd November 2010 25 November 2010 International Conference On Neural Information Processing (ICONIP) 2010 Sydney, Australia;

- 5. 3rd May 2011 5th May 2011 ACM Computing Frontiers conference Ischia, Campania, Italy;

- 6. 6th May 2011 14th May 2011 CapoCaccia cognitive neuromorphic engineering workshop Capocaccia, Sardinia, Italy;

- 26th June 2011 16th July 2011 Telluride neuromorphic cognition engineering workshop — Telluride, Colorado, U.S.A.;

- 18th July 2011 Invited talk at University of California S. Diego S.Diego, California, U.S.A.;

- 9. 19th July 2011 Invited talk at Qualcomm and Brain Corporation S.Diego, California, U.S.A.;

- 10. 20th July 2011 Invited talk at Salk institute S.Diego, California, U.S.A.;

- 11. 28th July 2011 Invited talk at University of Stanford California, U.S.A.;

- 31st July 2011 5th August 2011 International Joint Conference on Neural Networks (IJCNN) 2011 — San Jose, California, U.S.A.;

SERGIO DAVIES

- 13. 12th September 2011 13th September 2011 FACETS-ITN neuromorphic systems workshop Heidelberg, Germany;

- 29th April 2012 13th May 2012 CapoCaccia cognitive neuromorphic engineering workshop Capocaccia, Sardinia, Italy;

- 15. 10th June 2012 15th June 2012 International Joint Conference on Neural Networks (IJCNN) 2012 held within the World Congress on Computational Intelligence (WCCI) 2012 — Brisbane, Australia;

- 16. 1st July 2012 21st July 2012 Telluride neuromorphic cognition engineering workshop — Telluride, Colorado, U.S.A.

Total: about 150,000*Km*;  $\approx$  3.75 times the earth circumference, in  $\approx$  4.5 months! Considering the term of three years for my Ph.D., I have been travelling at  $\approx$  6*Km/h* for the whole period, writing 1 word of this thesis every  $\approx$  4.0*Km*! The Author

### **The Author**

Sergio Davies was born in 1981 in Naples, Italy. He graduated in 2006 from the University of Naples "Federico II" in telecommunication engineering with a specialization in computer science.

During his studies he met Prof. G. Ventre and Prof. G. Iannello who introduced him in the research world benchmarking parallel architectures in the Computer Science Department (DIS) at the University of Naples.

After graduation he started a Ph.D. course at the University of Salerno on pattern recognition applied to high speed motorways, but a lack of funds forced him to quit it.

He then entered industry in 2007 working for Nolan, Norton Italia - KPMG. He provided IT strategic advice to Banks, Ministries, public institutions and big telecommunication companies.

In 2009 he applied for a Ph.D. position at the University of Manchester, where he started the course in late September working in the SpiNNaker group supervised by Prof. Steve Furber.

His main research interest is synaptic plasticity in spiking neural networks. He is also interested in self-reconfiguring architectures for spiking neural networks simulation, with the idea of experimenting synaptic rewiring models in the SpiNNaker system.

## **Chapter 1**

### **Introduction to neural networks**

### **1.1** Neural networks

The term "neural network" is used to refer to a circuit of neurons that performs information processing using an approach to the problem different from the usual algorithmic computation of modern computer systems. The basic computational units of neural networks are neurons which may be either biological, or simulated mathematically on a computational substrate (e.g. a standard computer, an analogue circuit, etc).

Figure 1.1: General structure of a simple feed-forward artificial neural network. Each coloured disc is a neuron, and each arrow is a synapse.

SERGIO DAVIES

A simple example of a feed-forward neural network can be expressed in the threelayer network depicted in Fig.1.1, where each layer performs a simple task and the whole network performs an algorithm.

The group of neurons on the left is the input layer whose task is to collect stimuli from the external world; these neurons behave in a way similar to the sensory neurons in humans. The middle layer is the computational layer, which processes information received by the input layer (or perceived by senses in life forms); these neurons can be compared with the brain in humans. Finally, the output layer, on the right, generates the output stimuli of the network; these neurons are similar to the motor neurons in humans.

More complex structures of neural networks may include recurrent connections (connections between neurons of the same layer) or backward propagation: a feedback channel from the computation and/or the output layer to the previous layer(s). Further examples of neural network architectures exist in the literature.

This short and simplified example did not define any characterization of the neurons and synapses in use. However, on the basis of the characteristics of these components, the class of neural networks, and the type of algorithm that they perform, can be defined. The two main classes into which neural networks are divided are defined by the type of neuron in use: biological neurons (therefore biological neural networks) and artificial neurons (therefore artificial neural networks).

In this first chapter the biological aspects of neural networks are examined so that it is possible to compare them with the models used in artificial neural networks. After the comparison there is a description of the objective of this research work with the contributions and the structure of this thesis.

### **1.1.1** Biological neural networks

Biological neural networks are those formed by biological neurons which are connected to carry out the functionalities typical of the nervous system in biological life forms.

However, not all multicellular life forms on the earth have a nervous system. For example, sponges are very old life forms comprising colonies of cells which do not have a nervous system (Sanes et al., 2000) to allow electrical communication between the various part of the body. In particular the presence and the complexity of the nervous system has evolved during the various historical eras.

In the evolutionary scale, with regard to the nervous system, after the sponges it

Figure 1.2: Simplified structure of the nervous system in vertebrate animals.

is possible to find the "Radiata" branch: life forms which have a radial symmetry. In these life forms it is possible to identify a "top" and a "bottom", but not "left" and "right" sides; jellyfish are an example of this class of animal. These life forms have a simple nerve net which allows reactions to external stimuli and in some cases even complex behavioural patterns (Garm et al., 2007).

Life forms having the most complex neural system belong to the "Bilateria" branch. These are the life forms which are (approximately) symmetric with respect to a longitudinal axis, and for which it is possible to define a "left" and a "right" side in addition to a "top" and a "bottom". This branch includes the human race which has the most complex nervous system known in nature:  $\approx 100$  billion neurons (average) (Williams and Herrup, 1988) and 0.15 quadrillion ( $1.5 \times 10^{14}$ ) synapses in just the neocortex (Pakkenberg et al., 2003).

More generally, in the "Bilateria" branch, the "Vertebrate" subphylum occurs. In individuals of this subphylum, the nervous system can be divided into two interconnected halves (Kandel et al., 2000): the peripheral nervous system and the central nervous system. However, these two parts differ only from an anatomical point of view (see Fig.1.2). From a functional point of view there is a strict relationship between the peripheral and the central nervous system. The peripheral nervous system is the Input/Output interface for the central nervous system; stimuli collected through the senses are sent through the peripheral nervous system, as sequences or trains of spikes, to the central nervous system, where they are processed (by means of spikes, with the help of neuromodulators). The central nervous system is the main processing

unit for this information where all physical and behavioural reactions are processed and subsequently stimuli are sent back through the peripheral nervous system to the motor system generating the physical reaction.

### 1.1.2 Artificial neural networks

Artificial neural networks are circuits made by the interconnection of artificial neurons, which mimic the behaviour of biological neurons. This type of neural network needs to be simulated through a custom component designed for this purpose. Simulators comprise hardware (analogue or digital) or software (digital) components which compute mathematical models of biological neurons and biological synapses.

If neural networks are classified according to computational units (i.e. neurons and synapses), it is possible to distinguish three classes of algorithms (Maass, 1997) which differ between them by the types of input/output signals they are able to process and to emit: binary signals, continuous values and spike events (see Fig.1.3). This research work focuses on the third class of artificial neural networks: networks with spiking neurons; however, for completeness, here we describe also the other two classes of artificial neurons.

The first class of artificial neural networks features neurons, also called perceptrons, which are composed each of two sections: a sum and a threshold. The sum part receives input from a set of weighted synapses (in Fig.1.3  $w1, \ldots, wN$  represent the set of input weights) and performs a thresholding function on the result of the sum. Both the input and the output have values that may be equal to either 0 or 1 (discrete values).

The second class of artificial neural networks is composed by neurons which perform a two-stage computation: a sum of values received through weighted synapses, and a sigmoid function evaluator whose input is the result of the sum previously computed. The second computational stage gives the name to the neurons, which are also called sigmoidal units. The inputs can be any real-valued number, and the output is defined by the transfer function – the sigmoid unit for example limits outputs to [0; 1], whereas the hyperbolic function produces outputs in the range [-1; 1].

The third class of neural network is composed by spiking neurons: neurons which communicate through short signals, called spikes. This class of neural network has two main differences when compared with the previous two classes. In the first place, this class of neurons introduce the concept of time in the simulation, while earlier the neural networks were based on abstract steps of simulation. In addition, such neurons present similarities to biological neurons, as they both communicate using short signals, which

Figure 1.3: Classes of artificial neurons.

in biology are electric pulses (spikes), also known as action potentials.

In biology, the axon of a neuron is connected to the dendrites of another neuron through synapses. Such structures have the ability to "pump" electrical charges from the intracellular medium into the post-synaptic neuron. The amount of charge is a

characteristic of the specific synapse and the specific neurotransmitter in use.

In artificial neural networks, to develop a mathematical model that reproduces such a process, various parameters are used (synaptic weight, synaptic delay, synaptic current function, etc.), to represent the characteristics of each synapse. For the synaptic plasticity discussed in this work, we focus in particular on the synaptic weight parameter; however, other parameters are also presented for completeness. In particular, in Fig.1.3, the set  $w1, \ldots, wN$  represents the input synaptic weight for each of the synapses.

Each spiking neuron of this class is composed of three computational stages: a sum for all of the neuron's input current, which is then integrated over time (the second stage of the computation), and then, when the neuron's membrane potential (the potential difference between the two sides of the cellular membrane) raises above a threshold, in the third stage of the computation, a spike is emitted and the membrane potential returns to a reset value. The mathematical model of such spiking neurons is generally described through Ordinary Differential Equations (ODE). Sections 3.6.1 and 3.6.2 present examples of such models.

Table 1.1, proposed by Dr. E. Izhikevich (Izhikevich, 2004), compares several neuron models in terms of biophysical meaning, the types of biological neurons that the model is able to replicate, the ability to exhibit autonomous chaotic behaviour and the number of (floating-point) operations required for each step of simulation (with the hypothesis of a 1*msec* simulation step). A "+" in the table means that the model is able to reproduce it. A white space means that theoretically the model allows the specific behaviour, but it was not possible to find the appropriate parameters (in a reasonable amount of time).

|                                   |                    |                    |                 |                     |          |                   |                      |         |            |                 | 0              | 600          | 180    | 200            |

|-----------------------------------|--------------------|--------------------|-----------------|---------------------|----------|-------------------|----------------------|---------|------------|-----------------|----------------|--------------|--------|----------------|

| Number of FLOPS                   | S                  | 10                 |                 | 13                  |          | 10                | 2                    |         | 13         | 72              | 120            | 90           | 18     | 12             |

| Chaos                             | '                  | 1                  |                 |                     |          | +                 | ı                    | _       | +          | ı               | +              | •            |        | +              |

| Inhibition-induced bursting       | ī                  |                    |                 | ı                   |          | ı                 | ı                    |         | +          | ı               |                | ı            |        |                |

| Inhibition-induced spiking        |                    | 1                  |                 | 1                   |          | ı                 | ı                    |         | +          | +               | +              | +            |        | +              |

| Accommodation                     | ,                  |                    |                 |                     |          | +                 | ı                    |         | +          | +               | +              | +            | +      | +              |

| Depolarizing after-potential      | ,                  | +                  |                 | +                   |          | +                 | ı                    |         | +          | ı               | +              | 1            | +      | +              |

| Bistability                       | ī                  | 1                  |                 | +                   |          | +                 | +                    |         | +          | ÷               | +              | +            |        | +              |

| Threshold variability             |                    | ı                  |                 | ı                   |          | ı                 | +                    |         | +          | +               | +              | +            | +      | +              |

| Rebound burst                     | ı                  | ı                  |                 | +                   |          | ı                 | I                    |         | +          | ı               | +              |              | +      | +              |

| Rebound spike                     | ī                  | 1                  |                 | +                   |          | +                 | ı                    |         | +          | ÷               | +              | +            | +      | +              |

| Integrator                        | +                  | +                  |                 | +                   |          | +                 | +                    |         | +          | I               | +              | +            | +      | +              |

| Resonator                         |                    |                    |                 | ı                   |          | +                 | ı                    |         | +          | +               | +              | +            | +      | +              |

| Subthreshold oscillations         | ī                  | ı                  |                 | ī                   |          | +                 | ı                    |         | +          | +               | +              | +            | +      | +              |

| Spike latency                     | ,                  | I                  |                 | ı                   |          | ı                 | +                    |         | +          | +               | +              | +            | +      | +              |

| Class 2 excitable - spike latency | ı                  | 1                  |                 | ı                   |          | +                 | ı                    |         | +          | I               | +              | +            | +      | +              |

| Class 1 excitable                 | +                  | +                  |                 | +                   |          | +                 | +                    |         | +          | +               | +              | +            | +      | +              |

| Spike Frequency adaptation        | ,                  | +                  |                 | +                   |          | ı                 | ı                    |         | +          | ı               | +              | ı            | +      | +              |

| Mixed mode                        | 1                  |                    |                 | ı                   |          | ı                 | ı                    |         | +          | ı               |                | ı            |        |                |

| Phasic bursting                   | ı                  | 1                  |                 | +                   |          | ı                 | ı                    |         | +          |                 |                |              |        |                |

| Tonic Bursting                    | ,                  | ı                  |                 |                     |          | ı                 | I                    |         | +          | I               | +              | ı            | +      | +              |

| Phasic spiking                    | ,                  | ı                  |                 | +                   |          | +                 | ı                    |         | +          | +               | +              | +            | +      | +              |

| Tonic spiking                     | +                  | +                  |                 | +                   |          | +                 | +                    |         | +          | +               | +              | +            | +      | +              |

| Biophysically meaningful          | ,                  | ı                  |                 | ı                   |          | ı                 | ı                    |         | I          | I               |                | +            | ı      | +              |

| Neuron Models                     | Integrate-and-Fire | Integrate-and-Fire | with auaptation | Integrate-and-Fire- | or-Burst | Resonate-and-Fire | Quadratic Integrate- | anu-rue | Izhikevich | FitzHugh-Nagumo | Hindmarsh-Rose | Morris-Lecar | Wilson | Hodgkin-Huxley |

Table 1.1: Comparison between spiking neuron models (Izhikevich, 2004).

### **1.2** Uses of neural networks

Research on neural networks has generated increasing interest over the last few years. Research groups applied them successfully to various tasks, such as (Misra and Saha, 2010):

- Pattern and sequence recognition;

- Data processing (filtering, clustering and compression);

- System identification and control;

- Game playing and decision making;

- Medical diagnoses;

- High energy physics;

- Image/object recognition;

- Image segmentation;

- Generic image/video processing;

- Finger print feature extraction;

- Autonomous robotics;

- Optical character/handwriting recognition;

- Acoustic sound recognition;

- Real-time embedded control;

- Security control units (e.g. in airports) use automatic face recognition to raise security levels (Zhang and Fulcher, 1996);

- Control theory with neural networks the Neural Engineering Framework (Eliasmith and Anderson, 2004)

- ... and much more...

As artificial neural networks get closer to biological examples, it becomes possible to emulate parts of the biological nervous system to study processes which normally happen in the brain, but are not yet completely understood. In particular, spiking neural network simulators allow the study of the extent to which theory can approximate reality in the study of processes such as:

- Verification of how theoretic models approximate biological processes;

- The study of mental illnesses by emulating brain disorders;

- Testing how drugs affect the brain;

The final scope of research involving spiking neural networks is to understand how the human brain works. Since the beginning of computer science, when the first computer executed its program, processors have always consumed high levels of electrical power compared with biological neural networks (e.g. the human brain (Furber, 2008)), but are not even near to being able to mimic what nature created: the brain. This is an aggregate of neural cells which is very power efficient, where each element does a very small computation, but this computation is extremely fast.

The power of the brain is believed to stem from the massive parallelism of interconnected elements, and this is a source of inspiration for novel projects. Scientists try to emulate these characteristics on the basis that these may represent the future of computer technology.

### **1.3** Adaptability (plasticity) in neural networks

Biological neural networks have the remarkable ability to be able to adapt to the surrounding environment, and to improve their performance (according to a specific measure) in accomplishing specific tasks. Artificial neural networks have been designed to replicate such behaviour, with some degree of accuracy, even though the complete process is not yet fully understood.

The learning ability in biological neural networks is shown in the modification of the parameters of a network (e.g. synaptic weight modification) so that it preserves the experience gained through the learning process.

However learning cannot be defined uniquely, as there are too many activities involved, and this process may be seen from different points of view. For example, the meaning of learning in an educational environment is quite different from the meaning of the same word in a psychological sense or in a biological environment.

For the purpose of this thesis, the definition of learning in neural networks given by S. Haykin (Haykin, 1999) is most suitable:

"Learning is a process by which the free parameters of a neural network are adapted through a process of stimulation by the environment in which the network is embedded. The type of learning is determined by the manner in which the parameter changes take place"

In this definition there is a process involved, where these steps need to take place:

- 1. The environment in which the network resides gives stimuli to the network;

- The free parameters of the network are modified according to the incoming stimuli;

- 3. The network generates a new output corresponding to the incoming stimuli from the environment, where modifications occur because of the changes described in the previous step.

The second of these steps is fully described through a *learning algorithm*: a welldefined set of rules which describe how the modifications in the network occur as a consequence of the incoming stimuli.

After modifications take place, the network generates an output, and therefore interacts with the environment. The *learning paradigms* depend on the type of environment which surrounds and provides training signals to the neural network.

### 1.3.1 Plasticity in biological neural networks

In biology the connection between two neurons shows a high degree of plasticity in the parameters which characterize it. The weight of the synapse is one (and perhaps the most studied) of these parameters. Other parameters which can be influenced concern the speed of propagation of signals between the two neurons (Bakkum et al., 2008), the generation of new connections (Sanes et al., 2000), the cancellation of existing connections which have a very low influence on the post-synaptic neuron (Sanes et al., 2000), and others.

This thesis focuses, in particular, on synaptic weight modification, because this is the most studied in biology and therefore provides the largest amount of supporting material to be emulated using an artificial neural network simulator.

The first hypothesis for the underlying mechanism of the synaptic weight modification was proposed by Hebb in 1949 (Hebb, 1949):

"When an axon of cell A is near enough to excite cell B and repeatedly or persistently takes part in firing it, some growth process or metabolic changes take place in one or both cells such that A's efficiency as one of the cells firing B, is increased"

Hebb, D.O. (1949), "The organization of behavior", New York: Wiley, p. 62

"When one cell repeatedly assists in firing another, the axon of the first cell develops synaptic knobs (or enlarges them if they already exist) in contact with the soma of the second cell."

Hebb, D.O. (1949), "The organization of behavior", New York: Wiley, p. 63

"The general idea is an old one, that any two cells or systems of cells that are repeatedly active at the same time will tend to become 'associated', so that activity in one facilitates activity in the other."

Hebb, D.O. (1949), "The organization of behavior", New York: Wiley, p. 70

This mechanism has often been summarized as "cells that fire together, wire together". However, more biologically detailed mechanisms have been described in the last 30 years. Synaptic weights have shown the ability to be either enhanced (potentiated) or depressed, and the time range over which these modifications lasts can span from few milliseconds to a lifetime (Cowan et al., 2001).

These modifications have been associated with adaptation to sensory input and short-term memory as well as long-term memory (collection of experiences), and others.

It is possible to identify two main forms of synaptic plasticity connected with learning and memory which act on the synaptic weights where the difference is the time scale: short-term and long-term plasticity. In addition to these, there is one further form of adaptation of neural networks which spans a time period which is longer than the life of an individual: evolution (Nolfi et al., 1994).

Here a small set of the biological processes involved in short-term and long-term plasticity is presented. Detailed description of the biological events is left to more appropriate sources. It is necessary only to be aware that these processes do take place in biological neural networks.

### Short-term plasticity

This type of synaptic plasticity leads to modifications in synaptic weights which disappear in a short time (in the range between tens of milliseconds and minutes (Cowan et al., 2001)). The modifications involve either enhancement or depression of the synaptic signal, respectively named short-term enhancement and short-term depression.

The weight modification may be a consequence of the signals which pass through the synapse (homeosynaptic plasticity) or may depend on a third neuron, different from the pre-synaptic and post-synaptic neurons, which acts on the synapse (heterosynaptic plasticity).

### Homeosynaptic plasticity

This modification acts on the pre-synaptic transmitter release from the synaptic knob either facilitating or inhibiting the release of the neurotransmitters. The general rule (Zucker and Regehr, 2002) describes this learning rule on the basis of the inter-spike time carried by the synapse: if this is less than 20msec the synapse is depressed (Paired Pulse Depression - PPD). On the other side, if the inter-spike time is in the range 20-500msec, then the synapse is potentiated (Paired Pulse Facilitation - PPF) (Cowan et al., 2001).

### Heterosynaptic plasticity

This modification acts on the pre-synaptic transmitter release and is regulated by signals extrinsic to the synapse on which it acts. The modifications induced may be either inhibition or facilitation. In biology there are many examples of heterosynaptic inhibition processes, but fewer examples are available for the facilitation process (Cowan et al., 2001).

### Long-term plasticity

Plasticity forms that act for longer times are also present in the brain. Generally it is possible to divide them into two major categories: NMDA (N-Methyl-D-Aspartic acid) receptor-based plasticity and NMDA receptor-independent plasticity (Cowan et al., 2001). While, for the first type of plasticity, there is still some discussion on the expression mechanism, for NMDA receptor-independent plasticity, scientists have agreed that this mechanism occurs at the pre-synaptic end in the hippocampus, cerebellum and corticothalamic synapses.

NMDA receptor-independent plasticity has been widely studied and a learning algorithm, called Spike Timing Dependent Plasticity (STDP), has been proposed as a result of the effects generated in the biological experiments. The suggested rule was first proposed by Bi and Poo in 1998 (Bi and Poo, 1998) and described the biological mechanism, from a phenomenological point of view, without detailed analysis of all the biological elements involved. This algorithm has subsequently been reviewed and improved by others (Abarbanel et al., 2002).

The effects studied in the experiments suggested that the precise timing of the incoming and outgoing spikes may be the cause for the Long Term Depression (LTD) and Long Term Potentiation (LTP) of the synapse. This will be discussed later in the thesis in chapter 6 (as background of the learning algorithm that is proposed).

### **1.3.2** Plasticity in artificial neural networks

In artificial neural networks there are various aspects of the learning process. It is important to define the environment in which the neural network is trained, this is called the "learning paradigm"; the "learning rule" defines the algorithm through which the neural network adapts to the incoming stimuli and there are several possible tasks that a neural network may be trained to do. These three parameters (learning paradigms, learning rules and learning tasks) are described in the next paragraphs (Haykin, 1999).

### Learning paradigms

There are four main paradigms which describe the learning environment in which the neural network operates:

1. **Supervised learning**: In artificial neural networks this learning paradigm is characterized by the presence of sets of inputs and knowledge about the desired

SERGIO DAVIES

outputs. Having knowledge of both inputs and outputs, the network is able to configure itself to apply the transfer function over inputs not previously seen. In this case the network benefits from the presence of a teacher (the desired output) through an error function which induces a modification in the parameters of the internal structure of the network.

An example of learning rule for neural networks composed by sigmoidal units, which uses this learning paradigm, is error-backpropagation, used in Multi-Layer Perceptrons. The biological realism of such an algorithm (described with pseudo-code in Algorithm 1) has been disputed (Stork, 1989), but some implementations claim to be biologically plausible (e.g. van Ooyena and Roelfsemab, 2003).

The supervised learning paradigm has also been applied to spiking neural networks using a modified version of STDP as the learning rule (Strain et al., 2006). The STDP learning rule will be discussed later in chapter 6.

- 2. Unsupervised learning: This learning paradigm is characterized by the presence of only input training patterns, for which no output is provided. Thus the network must learn to adapt through the "experience" collected from the injected patterns. Once the network has adapted to the statistical regularities of the injected input, it forms an internal representation of the features of the input, and is therefore able to generate new classes based on this representation. This learning paradigm will be used later in this thesis to perform tests for learning algorithms. An example rule of this learning paradigm is the STDP algorithm (Bi and Poo, 1998), which is presented and discussed in-depth in chapter 6. In particular, this algorithm has been extracted after the study of biological phenomena, and is therefore biologically plausible;

- 3. **Reinforcement learning**: In nature, animals learn how to behave not only by observing specimens of the same race or through a "teacher". Often they experiment with new behaviours in a trial and error process where a reward is present. The right behaviour receives a positive reward and therefore is reinforced; actions that did not produce the desired outcome are penalized. The whole process, here described, has been called "reinforcement learning" in connection with the reward function that reinforces the correct behaviour. A link between the theory behind this type of learning and its biological implementation in neural networks has been found only recently (Ponulak and Kasinski, 2011).

**Algorithm Name**: ERROR BACKPROPAGATION **Description**: This algorithm is the basic method to propagate the synaptic weight modification in an MLP network which was initialized with random synaptic weights. In this example a 3-layer network is considered;

apply\_input(input); output = compute\_output(); compute\_error(output, desired\_output); weights\_variation\_output\_layer = compute\_synaptic\_weights\_update(weights\_output\_layer, output); weights\_variation\_hidden\_layer = back\_propagate\_synaptic\_weights\_modification(weights\_variation\_output\_layer, weights\_hidden\_layer); update\_synaptic\_weights();

### **Function description**:

apply\_input(): applies the specific input to the Multi-Layer Perceptron; compute\_output(): computes the output for the Multi-Layer Perceptron; compute\_error(): computes the new synaptic weights as a function of the error between the actual output and the desired output;

*compute\_synaptic\_weights\_update()*: computes the synaptic weight update for the synapses from the hidden layer to the output layer, given the current synaptic weights and the error value;

back\_propagate\_synaptic\_weights\_modification(): computes the synaptic weight

update for the synapses from the input layer to the hidden layer, given the

weight update for the synapses from the hidden layer to the output layer;

update\_synaptic\_weights(): applies the synaptic weights update appropriately;

Algorithm 1: Error backpropagation

An example rule of such a learning paradigm applied to neural networks composed by sigmoidal units is the Q-Learning rule (Watkins and Dayan, 1992), which uses temporal differences to estimate the expected reward (Q(s, a)) of doing a particular action (a) while in a particular state (s). This learning rule is described by the formula (1.1):

$$Q(s_t, a_t) \leftarrow Q(s_t, a_t) + \alpha(s_t, a_t) \times (R_{t+1} + \gamma \times \max_{a_{t+1}} Q(s_{t+1}, a_{t+1}) - Q(s_t, a_t))$$

$$(1.1)$$

where:

- $\alpha(s_t, a_t)$  is the learning rate for the specific action and state ( $0 < \alpha \le 1$ );

- $R_{t+1}$  is the reward observed after performing action  $a_t$ ;

- $\gamma$  is a discount factor ( $0 \le \gamma < 1$ );

This learning paradigm has been applied also in spiking neural networks using STDP as learning rule with a modulatory signal (Farries and Fairhall, 2007).

4. **Evolutionary learning**: Biological evolution is the process through which individuals are selected as the ones that have best adapted to the environment:

> "[...] any being, if it vary however slightly in any manner profitable to itself, under the complex and sometimes varying conditions of life, will have a better chance of surviving, and thus be NATURALLY SE-LECTED." Darwin (1859), "On the origin of species" (6th edition), New York: P.F. Collier, p. 15.

This happens through adaptation to the environment on the time span of generations: life forms that have achieved a better adaptation to the environment are also able to live longer and reproduce more. Therefore, through natural selection, the "winning" genes are the most diffused across the individuals of a particular population. As evolution has been described in biology, similar processes can be also described in numerous other fields (Holland, 1975). In particular it has been described in artificial neural networks through evolutionary algorithms. In the experiments ran by Pavlidis et al. (2005), multiple copies of the same structure of the neural network are reproduced on a computational system. Each of these copies is able to learn independently from the others. The network evolves bringing from one generation to the subsequent only the populations of neurons that perform their task in the most effective way.

### Learning rules

Learning algorithms for neural networks may be based on a series of principles. Here we cite some of them, leaving detailed explaination to more appropriate sources (e.g. Haykin, 1999):

- Error-correction learning: The output generated by the network is compared with (i.e. subtracted from) the requested output, and this error signal is used to make the appropriate changes to the synaptic weights. This rule is used in a supervised learning environment.

- **Memory based learning**: All the injected inputs are compared with those previously stored in memory. The input is then attributed to the class of its closest neighbour that is present in memory.

- **Hebbian learning**: The basis of this learning algorithm was described at the beginning of section 1.3.1 with the quotation of Hebb's postulate. The STDP learning rule belongs to this category.

- **Competitive learning**: The output neurons of a network compete among themselves to become active, inhibiting the others. This rule is used later in this thesis in addition to the Hebbian learning rule described earlier.

### Learning tasks

There is a long list of possible tasks to test the learning ability of neural networks (Haykin, 1999). The research in this thesis focuses on a pattern recognition task which includes a learning phase using a set of injected spikes: the network has to extract and memorize the statistical properties of the injected spike pattern and determine if it belongs to a known pattern. This is discussed later in chapter 6.

### **1.4** Statement of the problem and objectives

Implementing learning (in particular the STDP algorithm, as described later in section 6.3) on an event-based architecture, such as the SpiNNaker system, is computationally very complex, and very expensive from a memory occupation point of view; this is described in section 6.12.1.

The aim of this research is to provide a novel learning algorithm for a neuromorphic system, requires less computational power and occupies less memory compared with other learning rules currently studied, but provides learning features comparable to other algorithms.

# **1.5** Contributions

In this thesis three main contributions will be presented:

- 1. A novel implementation of a learning rule suitable for neuromorphic implementation; the rule presented will be called STDP-TTS (Spike Timing Dependent Plasticity with Time-To-Spike forecast).

- 2. A novel approach to multicast packet routing in the SpiNNaker system; throughout this thesis this topic will be referred to as "population-based routing";

- 3. A real-time host computer interface to inject spikes into the SpiNNaker system. These may be generated (for example) by a capturing interface (such as a silicon retina) and injected into the system while the simulation is running;

The primary contribution of this work is the learning rule. The other two contributions were necessary to develop a suitable environment to perform the required tests to study the characterization of the novel learning rule. In particular, while the motivation for the novel learning rule was anticipated earlier as it represents part of the research problem, the specific motivations for each of the other two contributions are described in the sections 4.1 and 5.1.

# **1.6 Publications**

# **1.6.1** Journal articles

• Sergio Davies, Cameron Patterson, Francesco Galluppi, Alexander Rast, David Lester and Steve Furber

"Interfacing Real-Time Spiking I/O with the SpiNNaker neuromimetic architecture"

published in Australian Journal of Intelligent Information Processing Systems (AJIIPS) 2010, volume 11, number 1, pages 7–11 (Davies et al., 2010); This article represents the basis of the work described in chapter 4;

Sergio Davies, Alexander Rast, Francesco Galluppi and Steve Furber "A forecast-based STDP rule suitable for neuromorphic implementation" published in Neural Networks – Special Issue 2012 – Selected papers from IJCNN 2012 – August 2012, Volume 32, pages 3–14. This article covers the topic presented in the first half of the chapter 6;

SERGIO DAVIES

The author of this thesis has also contributed to the development and writing of the article listed below. However, this will not be included directly in this work.

- Alexander Rast, Francesco Galluppi, Sergio Davies, Luis Plana, Cameron Patterson, Thomas Sharp, David Lester and Steve Furber *"Concurrent Heterogeneous Neural Model Simulation on Real-Time Neuromimetic Hardware"* published in Neural Networks, Volume 24, Issue 9, Nov 2011, pages 961–978 (Rast et al., 2011a).

- Xin Jin, Mikel Lujan, Luis A. Plana, Sergio Davies, Steve Temple and Steve Furber

*"Modelling Spiking Neural Networks on SpiNNaker"* published in Computing in Science & Engineering, 2010, volume 12, number 5, pages 91–97 (Jin et al., 2010b);

# **1.6.2** Conference papers

- Sergio Davies, Alexander Rast, Francesco Galluppi and Steve Furber *"Maintaining Real-Time Synchrony on SpiNNaker"* published in the proceedings of the 8th ACM International Conference on Computing Frontiers 2011, pages 15:1–15:2 (Davies et al., 2011b). This paper describes the solution to a technical issue faced while testing the STDP TTS learning algorithm. The content of the paper is not discussed directly in this thesis, however the work presented allowed the SpiNNaker system to be able to correctly perform the required simulations.

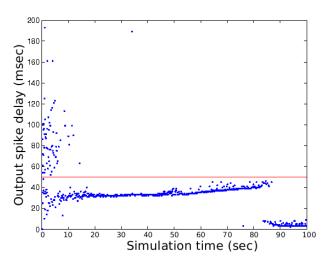

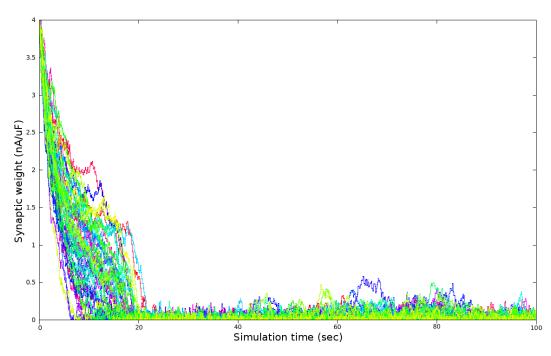

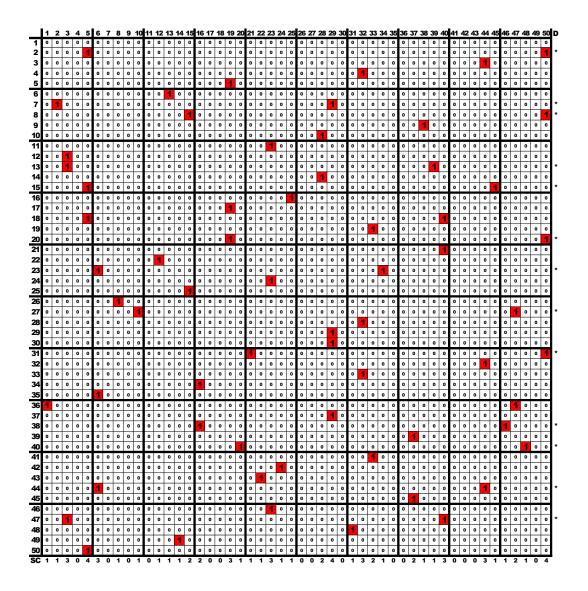

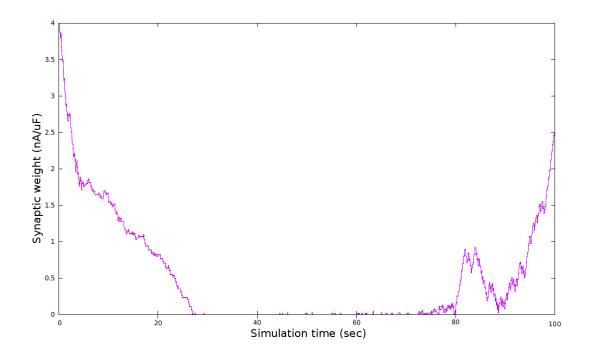

- Sergio Davies, Alexander Rast, Francesco Galluppi and Steve Furber "A forecast-based biologically-plausible STDP learning rule" published in proceedings of the 2011 International Joint Conference on Neural Networks (IJCNN), July 2011, pages 1810–1817 (Davies et al., 2011a). This paper forms part of chapter 6.