# PERFORMANCE-ORIENTED SYNTAX-DIRECTED SYNTHESIS OF ASYNCHRONOUS CIRCUITS

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2010

By

Luis Tarazona Duarte

School of Computer Science

# Contents

| $\mathbf{A}$ | bstra | act                                                  | 14 |

|--------------|-------|------------------------------------------------------|----|

| D            | eclar | ation                                                | 15 |

| C            | opyri | $_{ m ight}$                                         | 16 |

| A            | ckno  | wledgements                                          | 17 |

| 1            | Intr  | roduction                                            | 19 |

|              | 1.1   | Motivation                                           | 19 |

|              | 1.2   | Syntax-directed synthesis                            | 20 |

|              |       | 1.2.1 Tangram and TiDE                               | 21 |

|              |       | 1.2.2 Balsa                                          | 21 |

|              |       | 1.2.3 Handshake circuits and handshake components    | 21 |

|              | 1.3   | Optimising handshake circuits                        | 24 |

|              |       | 1.3.1 Push data-driven handshake circuits            | 25 |

|              |       | 1.3.2 Automated source-to-source transformations     | 26 |

|              |       | 1.3.3 Behavioural synthesis of asynchronous circuits | 26 |

|              | 1.4   | Teak                                                 | 27 |

|              | 1.5   | Aims of this research                                | 28 |

|              | 1.6   | Contribution of this research                        | 29 |

|              | 1.7   | Thesis organisation                                  | 29 |

|              | 1.8   | Publications                                         | 30 |

| 2            | Bac   | ekground                                             | 32 |

|              | 2.1   | Introduction                                         | 32 |

|              | 2.2   | Asynchronous Circuits                                | 32 |

|              | 2.3   | Handshake protocols and data encoding                | 34 |

|   |     | 2.3.1  | Bundled-data protocols                              | 35        |

|---|-----|--------|-----------------------------------------------------|-----------|

|   |     | 2.3.2  | Dual-rail protocols                                 | 38        |

|   | 2.4 | Opera  | tion modes                                          | 40        |

|   |     | 2.4.1  | Fundamental Mode Circuits                           | 41        |

|   |     | 2.4.2  | Burst-Mode circuits                                 | 42        |

|   |     | 2.4.3  | Input-output mode                                   | 42        |

|   | 2.5 | Delay  | models                                              | 42        |

|   |     | 2.5.1  | Speed-independent (SI) circuits                     | 43        |

|   |     | 2.5.2  | Delay-insensitive (DI) circuits                     | 43        |

|   |     | 2.5.3  | Quasi-delay insensitive (QDI) circuits              | 44        |

|   | 2.6 | Asyncl | hronous synthesis                                   | 45        |

|   |     | 2.6.1  | Synthesis of SI control circuits                    | 45        |

|   |     | 2.6.2  | Communicating Hardware Processes (CHP) and the Cal- |           |

|   |     |        | tech Asynchronous Synthesis Tool (CAST)             | 48        |

|   |     | 2.6.3  | Macromodular based synthesis                        | 50        |

|   |     | 2.6.4  | Desynchronisation methods                           | 50        |

|   | 2.7 | Summ   | ary                                                 | 53        |

| 3 | The | Balsa  | synthesis system and language                       | <b>54</b> |

|   | 3.1 |        | uction                                              | 54        |

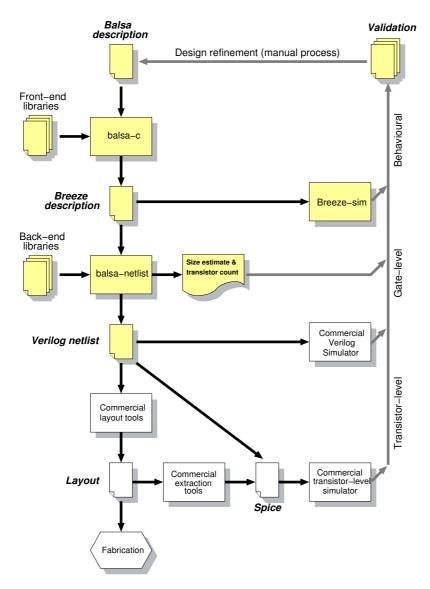

|   | 3.2 | The B  | alsa synthesis system                               | 54        |

|   |     | 3.2.1  | Balsa design flow                                   | 55        |

|   | 3.3 | The B  | alsa language                                       | 55        |

|   |     | 3.3.1  | The structure of a Balsa description                | 56        |

|   |     | 3.3.2  | Data Types                                          | 58        |

|   |     | 3.3.3  | Basic transfer commands                             | 59        |

|   |     | 3.3.4  | Dataless handshakes                                 | 60        |

|   |     | 3.3.5  | Variable assignment                                 | 60        |

|   |     | 3.3.6  | Control operators                                   | 60        |

|   |     | 3.3.7  | Iteration and conditional constructs                | 62        |

|   |     | 3.3.8  | Data processing operators                           | 64        |

|   |     | 3.3.9  | Input enclosure                                     | 64        |

|   |     | 3.3.10 | Arbitration                                         | 67        |

|   |     |        |                                                     |           |

|   |     | 3.3.11 | Permissive Concur                                   | 68        |

|   |     |        | Permissive Concur                                   | 68<br>68  |

| 4.1       Introduction       8         4.2       Related work       8         4.3       The data-driven description style       8         4.3.1       Control driven to data driven example       8         4.4       Optimising data-driven descriptions       9         4.4.1       Separating actions into concurrent loops       9         4.4.2       Broadcasting values       9         4.4.3       Adding pipeline registers       9         4.5       Optimising guards       9         4.5.1       Encoding multiple guards       10         4.6       New peephole optimisations       10         4.6.1       Removing redundant False Variables       10         4.6.2       Control of active enclosures       10         4.6.3       Unbounded read-then-write on variables       10         4.6.4       Fetch component with concurrent RTZ       10         4.6.5       Summary       11         5       Optimising Token-flow circuits and descriptions       11         5.1       Introduction       11         5.2       Teak synthesis       11         5.2.1       Teak components       11         5.2.2       Teak synthesis       12<                                                                                                                      |   | 3.4 | Summary                                                 | 78  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---------------------------------------------------------|-----|

| 4.2       Related work       8         4.3       The data-driven description style       8         4.3.1       Control driven to data driven example       8         4.4       Optimising data-driven descriptions       9         4.4.1       Separating actions into concurrent loops       9         4.4.2       Broadcasting values       9         4.4.3       Adding pipeline registers       9         4.5       Optimising guards       9         4.5.1       Encoding multiple guards       10         4.6       New peephole optimisations       10         4.6.1       Removing redundant False Variables       10         4.6.2       Control of active enclosures       10         4.6.3       Unbounded read-then-write on variables       10         4.6.4       Fetch component with concurrent RTZ       10         4.6.5       Summary       11         5       Optimising Token-flow circuits and descriptions       11         5.1       Introduction       11         5.2       Teak system       11         5.2.1       Teak components       11         5.2.2       Teak synthesis       12         5.3.1       Variables       12 <td>4</td> <td>Opt</td> <td>imising Balsa circuits</td> <td>80</td>                                                      | 4 | Opt | imising Balsa circuits                                  | 80  |

| 4.3.1 The data-driven description style       8         4.3.1 Control driven to data driven example       8         4.4 Optimising data-driven descriptions       9         4.4.1 Separating actions into concurrent loops       9         4.4.2 Broadcasting values       9         4.4.3 Adding pipeline registers       9         4.5 Optimising guards       9         4.5.1 Encoding multiple guards       10         4.6 New peephole optimisations       10         4.6.1 Removing redundant False Variables       10         4.6.2 Control of active enclosures       10         4.6.3 Unbounded read-then-write on variables       10         4.6.4 Fetch component with concurrent RTZ       10         4.6.5 Summary       11         5 Optimising Token-flow circuits and descriptions       11         5.1 Introduction       11         5.2 The Teak system       11         5.2.1 Teak components       11         5.2.2 Teak synthesis       11         5.3.1 Variables       12         5.3.2 Fork displacement       12         5.3.3 Fork-Merge-Join and Steer-Merge       12         5.3.4 Removing "go" cycles       12         5.4.1 Commonalities with Balsa optimisations       12         5.4.                                                            |   | 4.1 | Introduction                                            | 80  |

| 4.3.1 Control driven to data driven example       8         4.4 Optimising data-driven descriptions       9         4.4.1 Separating actions into concurrent loops       9         4.4.2 Broadcasting values       9         4.4.3 Adding pipeline registers       9         4.5 Optimising guards       9         4.5.1 Encoding multiple guards       10         4.6 New peephole optimisations       10         4.6.1 Removing redundant False Variables       10         4.6.2 Control of active enclosures       10         4.6.3 Unbounded read-then-write on variables       10         4.6.4 Fetch component with concurrent RTZ       10         4.6.5 Summary       11         5 Optimising Token-flow circuits and descriptions       11         5.1 Introduction       11         5.2 The Teak system       11         5.2.1 Teak components       11         5.2.2 Teak synthesis       11         5.3.1 Variables       12         5.3.2 Fork displacement       12         5.3.3 Fork-Merge-Join and Steer-Merge       12         5.3.4 Removing "go" cycles       12         5.4.1 Commonalities with Balsa optimisations       12         5.4.2 Description techniques to remove Variables       12 </td <td></td> <td>4.2</td> <td>Related work</td> <td>81</td> |   | 4.2 | Related work                                            | 81  |

| 4.4.1 Optimising data-driven descriptions       9         4.4.1 Separating actions into concurrent loops       9         4.4.2 Broadcasting values       9         4.4.3 Adding pipeline registers       9         4.5 Optimising guards       9         4.5.1 Encoding multiple guards       10         4.6 New peephole optimisations       10         4.6.1 Removing redundant False Variables       10         4.6.2 Control of active enclosures       10         4.6.3 Unbounded read-then-write on variables       10         4.6.4 Fetch component with concurrent RTZ       10         4.6.5 Summary       11         5 Optimising Token-flow circuits and descriptions       11         5.1 Introduction       11         5.2 The Teak system       11         5.2.1 Teak components       11         5.2.2 Teak synthesis       11         5.3 Optimising Teak circuits       12         5.3.1 Variables       12         5.3.2 Fork displacement       12         5.3.4 Removing "go" cycles       12         5.4.1 Commonalities with Balsa optimisations       12         5.4.2 Description techniques to remove Variables       12                                                                                                                                  |   | 4.3 | The data-driven description style                       | 82  |

| 4.4.1       Separating actions into concurrent loops       9         4.4.2       Broadcasting values       9         4.4.3       Adding pipeline registers       9         4.5       Optimising guards       10         4.5       Lencoding multiple guards       10         4.6       New peephole optimisations       10         4.6       Removing redundant False Variables       10         4.6.1       Removing redundant False Variables       10         4.6.2       Control of active enclosures       10         4.6.3       Unbounded read-then-write on variables       10         4.6.4       Fetch component with concurrent RTZ       10         4.6.5       Summary       11         5       Optimising Token-flow circuits and descriptions       11         5.1       Introduction       11         5.2       The Teak system       11         5.2.1       Teak components       11         5.2.2       Teak synthesis       11         5.3       Optimising Teak circuits       12         5.3.1       Variables       12         5.3.2       Fork displacement       12         5.3.4       Removing "go" cycles       12                                                                                                                                      |   |     | 4.3.1 Control driven to data driven example             | 84  |

| 4.4.2       Broadcasting values       9         4.4.3       Adding pipeline registers       9         4.5       Optimising guards       9         4.5.1       Encoding multiple guards       10         4.6       New peephole optimisations       10         4.6.1       Removing redundant False Variables       10         4.6.2       Control of active enclosures       10         4.6.3       Unbounded read-then-write on variables       10         4.6.4       Fetch component with concurrent RTZ       10         4.6.5       Summary       11         5       Optimising Token-flow circuits and descriptions       11         5.1       Introduction       11         5.2       The Teak system       11         5.2       Teak components       11         5.2.1       Teak components       11         5.2.2       Teak synthesis       11         5.3       Optimising Teak circuits       12         5.3.1       Variables       12         5.3.2       Fork displacement       12         5.3.3       Fork-Merge-Join and Steer-Merge       12         5.4       Description-level optimisations       12 <td< td=""><td></td><td>4.4</td><td>Optimising data-driven descriptions</td><td>90</td></td<>                                                          |   | 4.4 | Optimising data-driven descriptions                     | 90  |

| 4.4.3       Adding pipeline registers       9         4.5       Optimising guards       9         4.5.1       Encoding multiple guards       10         4.6       New peephole optimisations       10         4.6.1       Removing redundant False Variables       10         4.6.2       Control of active enclosures       10         4.6.3       Unbounded read-then-write on variables       10         4.6.4       Fetch component with concurrent RTZ       10         4.6.5       Summary       11         5       Optimising Token-flow circuits and descriptions       11         5.1       Introduction       11         5.2       The Teak system       11         5.2       Teak components       11         5.2.1       Teak components       11         5.2.2       Teak synthesis       11         5.3       Optimising Teak circuits       12         5.3.1       Variables       12         5.3.2       Fork displacement       12         5.3.3       Fork-Merge-Join and Steer-Merge       12         5.3.4       Removing "go" cycles       12         5.4.1       Commonalities with Balsa optimisations       12 <tr< td=""><td></td><td></td><td>4.4.1 Separating actions into concurrent loops</td><td>90</td></tr<>                                       |   |     | 4.4.1 Separating actions into concurrent loops          | 90  |

| 4.5 Optimising guards       9         4.5.1 Encoding multiple guards       10         4.6 New peephole optimisations       10         4.6.1 Removing redundant False Variables       10         4.6.2 Control of active enclosures       10         4.6.3 Unbounded read-then-write on variables       10         4.6.4 Fetch component with concurrent RTZ       10         4.6.5 Summary       11         5 Optimising Token-flow circuits and descriptions       11         5.1 Introduction       11         5.2 The Teak system       11         5.2.1 Teak components       11         5.2.2 Teak synthesis       11         5.3 Optimising Teak circuits       12         5.3.1 Variables       12         5.3.2 Fork displacement       12         5.3.3 Fork-Merge-Join and Steer-Merge       12         5.3.4 Removing "go" cycles       12         5.4.1 Commonalities with Balsa optimisations       12         5.4.2 Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                              |   |     | 4.4.2 Broadcasting values                               | 93  |

| 4.5.1 Encoding multiple guards 4.6 New peephole optimisations 4.6.1 Removing redundant False Variables 4.6.2 Control of active enclosures 4.6.3 Unbounded read-then-write on variables 4.6.4 Fetch component with concurrent RTZ 10 4.6.5 Summary 11  5 Optimising Token-flow circuits and descriptions 11 5.1 Introduction 11 5.2 The Teak system 11 5.2.1 Teak components 11 5.2.2 Teak synthesis 11 5.3 Optimising Teak circuits 12 5.3.1 Variables 12 5.3.2 Fork displacement 12 5.3.3 Fork-Merge-Join and Steer-Merge 13 5.4 Description-level optimisations 12 5.4.1 Commonalities with Balsa optimisations 12 5.4.2 Description techniques to remove Variables 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |     | 4.4.3 Adding pipeline registers                         | 95  |

| 4.6       New peephole optimisations       10         4.6.1       Removing redundant False Variables       10         4.6.2       Control of active enclosures       10         4.6.3       Unbounded read-then-write on variables       10         4.6.4       Fetch component with concurrent RTZ       10         4.6.5       Summary       11         5       Optimising Token-flow circuits and descriptions       11         5.1       Introduction       11         5.2       The Teak system       11         5.2.1       Teak components       11         5.2.2       Teak synthesis       11         5.3       Optimising Teak circuits       12         5.3.1       Variables       12         5.3.2       Fork displacement       12         5.3.3       Fork-Merge-Join and Steer-Merge       12         5.3.4       Removing "go" cycles       12         5.4       Description-level optimisations       12         5.4.1       Commonalities with Balsa optimisations       12         5.4.2       Description techniques to remove Variables       12                                                                                                                                                                                                             |   | 4.5 | Optimising guards                                       | 97  |

| 4.6.1 Removing redundant False Variables       10         4.6.2 Control of active enclosures       10         4.6.3 Unbounded read-then-write on variables       10         4.6.4 Fetch component with concurrent RTZ       10         4.6.5 Summary       11         5 Optimising Token-flow circuits and descriptions       11         5.1 Introduction       11         5.2 The Teak system       11         5.2.1 Teak components       11         5.2.2 Teak synthesis       11         5.3 Optimising Teak circuits       12         5.3.1 Variables       12         5.3.2 Fork displacement       12         5.3.3 Fork-Merge-Join and Steer-Merge       12         5.3.4 Removing "go" cycles       12         5.4 Description-level optimisations       12         5.4.1 Commonalities with Balsa optimisations       12         5.4.2 Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                                                               |   |     | 4.5.1 Encoding multiple guards                          | 100 |

| 4.6.2       Control of active enclosures       10         4.6.3       Unbounded read-then-write on variables       10         4.6.4       Fetch component with concurrent RTZ       10         4.6.5       Summary       11         5       Optimising Token-flow circuits and descriptions       11         5.1       Introduction       11         5.2       The Teak system       11         5.2.1       Teak components       11         5.2.2       Teak synthesis       11         5.3       Optimising Teak circuits       12         5.3.1       Variables       12         5.3.2       Fork displacement       12         5.3.3       Fork-Merge-Join and Steer-Merge       12         5.3.4       Removing "go" cycles       12         5.4       Description-level optimisations       12         5.4.1       Commonalities with Balsa optimisations       12         5.4.2       Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                   |   | 4.6 | New peephole optimisations                              | 100 |

| 4.6.3       Unbounded read-then-write on variables       10         4.6.4       Fetch component with concurrent RTZ       10         4.6.5       Summary       11         5       Optimising Token-flow circuits and descriptions       11         5.1       Introduction       11         5.2       The Teak system       11         5.2.1       Teak components       11         5.2.2       Teak synthesis       11         5.3       Optimising Teak circuits       12         5.3.1       Variables       12         5.3.2       Fork displacement       12         5.3.3       Fork-Merge-Join and Steer-Merge       12         5.3.4       Removing "go" cycles       12         5.4       Description-level optimisations       12         5.4.1       Commonalities with Balsa optimisations       12         5.4.2       Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                                                                             |   |     | 4.6.1 Removing redundant False Variables                | 102 |

| 4.6.4       Fetch component with concurrent RTZ       10         4.6.5       Summary       11         5       Optimising Token-flow circuits and descriptions       11         5.1       Introduction       11         5.2       The Teak system       11         5.2.1       Teak components       11         5.2.2       Teak synthesis       11         5.3       Optimising Teak circuits       12         5.3.1       Variables       12         5.3.2       Fork displacement       12         5.3.3       Fork-Merge-Join and Steer-Merge       12         5.3.4       Removing "go" cycles       12         5.4       Description-level optimisations       12         5.4.1       Commonalities with Balsa optimisations       12         5.4.2       Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |     | 4.6.2 Control of active enclosures                      | 104 |

| 4.6.5       Summary       11         5       Optimising Token-flow circuits and descriptions       11         5.1       Introduction       11         5.2       The Teak system       11         5.2.1       Teak components       11         5.2.2       Teak synthesis       11         5.3       Optimising Teak circuits       12         5.3.1       Variables       12         5.3.2       Fork displacement       12         5.3.3       Fork-Merge-Join and Steer-Merge       12         5.3.4       Removing "go" cycles       12         5.4       Description-level optimisations       12         5.4.1       Commonalities with Balsa optimisations       12         5.4.2       Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     | 4.6.3 Unbounded read-then-write on variables            | 105 |

| 5 Optimising Token-flow circuits and descriptions       11         5.1 Introduction       11         5.2 The Teak system       11         5.2.1 Teak components       11         5.2.2 Teak synthesis       11         5.3 Optimising Teak circuits       12         5.3.1 Variables       12         5.3.2 Fork displacement       12         5.3.3 Fork-Merge-Join and Steer-Merge       12         5.3.4 Removing "go" cycles       12         5.4 Description-level optimisations       12         5.4.1 Commonalities with Balsa optimisations       12         5.4.2 Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |     | 4.6.4 Fetch component with concurrent RTZ               | 109 |

| 5.1 Introduction       11         5.2 The Teak system       11         5.2.1 Teak components       11         5.2.2 Teak synthesis       11         5.3 Optimising Teak circuits       12         5.3.1 Variables       12         5.3.2 Fork displacement       12         5.3.3 Fork-Merge-Join and Steer-Merge       12         5.3.4 Removing "go" cycles       12         5.4 Description-level optimisations       12         5.4.1 Commonalities with Balsa optimisations       12         5.4.2 Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |     | 4.6.5 Summary                                           | 111 |

| 5.2       The Teak system       11         5.2.1       Teak components       11         5.2.2       Teak synthesis       11         5.3       Optimising Teak circuits       12         5.3.1       Variables       12         5.3.2       Fork displacement       12         5.3.3       Fork-Merge-Join and Steer-Merge       12         5.3.4       Removing "go" cycles       12         5.4       Description-level optimisations       12         5.4.1       Commonalities with Balsa optimisations       12         5.4.2       Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5 | Opt | imising Token-flow circuits and descriptions 1          | .12 |

| 5.2.1 Teak components       11         5.2.2 Teak synthesis       11         5.3 Optimising Teak circuits       12         5.3.1 Variables       12         5.3.2 Fork displacement       12         5.3.3 Fork-Merge-Join and Steer-Merge       12         5.3.4 Removing "go" cycles       12         5.4 Description-level optimisations       12         5.4.1 Commonalities with Balsa optimisations       12         5.4.2 Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 5.1 | Introduction                                            | 112 |

| 5.2.2 Teak synthesis       11         5.3 Optimising Teak circuits       12         5.3.1 Variables       12         5.3.2 Fork displacement       12         5.3.3 Fork-Merge-Join and Steer-Merge       12         5.3.4 Removing "go" cycles       12         5.4 Description-level optimisations       12         5.4.1 Commonalities with Balsa optimisations       12         5.4.2 Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 5.2 | The Teak system                                         | 113 |

| 5.3 Optimising Teak circuits       12         5.3.1 Variables       12         5.3.2 Fork displacement       12         5.3.3 Fork-Merge-Join and Steer-Merge       12         5.3.4 Removing "go" cycles       12         5.4 Description-level optimisations       12         5.4.1 Commonalities with Balsa optimisations       12         5.4.2 Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |     | 5.2.1 Teak components                                   | 113 |

| 5.3.1 Variables       12         5.3.2 Fork displacement       12         5.3.3 Fork-Merge-Join and Steer-Merge       12         5.3.4 Removing "go" cycles       12         5.4 Description-level optimisations       12         5.4.1 Commonalities with Balsa optimisations       12         5.4.2 Description techniques to remove Variables       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |     | 5.2.2 Teak synthesis                                    | 115 |

| 5.3.2 Fork displacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 5.3 | Optimising Teak circuits                                | 120 |

| 5.3.3 Fork-Merge-Join and Steer-Merge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |     | 5.3.1 Variables                                         | 120 |

| 5.3.4 Removing "go" cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |     | 5.3.2 Fork displacement                                 | 123 |

| 5.4 Description-level optimisations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |     | 5.3.3 Fork-Merge-Join and Steer-Merge                   | 124 |

| 5.4.1 Commonalities with Balsa optimisations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |     | 5.3.4 Removing "go" cycles                              | 126 |

| 5.4.2 Description techniques to remove <i>Variables</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 5.4 | Description-level optimisations                         | 128 |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |     | 5.4.1 Commonalities with Balsa optimisations            | 128 |

| 5.4.3 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |     | 5.4.2 Description techniques to remove <i>Variables</i> | 128 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |     | 5.4.3 Summary                                           | 142 |

| 6 | Lat | ch inse | ertion in Teak circuits                                    | 144 |

|---|-----|---------|------------------------------------------------------------|-----|

|   | 6.1 | Introd  | $egin{array}{cccccccccccccccccccccccccccccccccccc$         | 144 |

|   | 6.2 | Buffer  | ing cycles $\dots$                                         | 145 |

|   |     | 6.2.1   | Detecting cycles                                           | 146 |

|   |     | 6.2.2   | Complexity of finding the optimum latch insertion points . | 148 |

|   | 6.3 | Buffer  | ing single-token cycles                                    | 151 |

|   | 6.4 | Two s   | imple latching strategies for Teak circuits                | 153 |

|   |     | 6.4.1   | Analysis of the latching strategies                        | 156 |

|   | 6.5 | Specif  | ying latching and optimisation options in Teak             | 159 |

|   | 6.6 | Summ    | nary                                                       | 159 |

| 7 | Des | sign Ex | camples and Evaluation                                     | 161 |

|   | 7.1 | The na  | anoSpa processor                                           | 161 |

|   |     | 7.1.1   | The Fetch stage                                            | 162 |

|   |     | 7.1.2   | The Decode stage                                           | 163 |

|   |     | 7.1.3   | The Execute stage                                          | 164 |

|   |     | 7.1.4   | Results                                                    | 166 |

|   | 7.2 | An asy  | ynchronous Viterbi decoder                                 | 170 |

|   |     | 7.2.1   | Introduction                                               | 170 |

|   |     | 7.2.2   | Viterbi decoder algorithm                                  | 171 |

|   |     | 7.2.3   | Architecture of the asynchronous Viterbi decoder           | 172 |

|   |     | 7.2.4   | Results                                                    | 174 |

|   | 7.3 | A 32×   | 32-bit radix-8 Booth MAC                                   | 177 |

|   |     | 7.3.1   | 32-bit Multiply with 64-bit accumulation                   | 179 |

|   |     | 7.3.2   | Results                                                    | 179 |

|   | 7.4 | The na  | anoSpa Forwarding Unit                                     | 182 |

|   |     | 7.4.1   | Introduction                                               | 182 |

|   |     | 7.4.2   | Related work                                               | 183 |

|   |     | 7.4.3   | The target processor: nanoSpa                              | 185 |

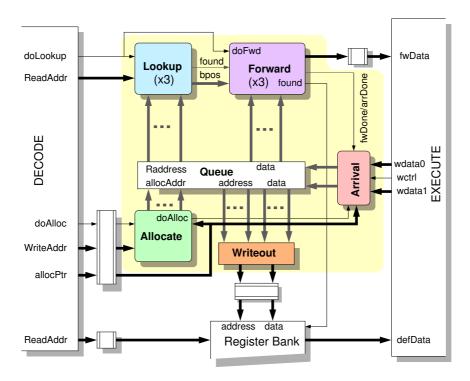

|   |     | 7.4.4   | Architecture of the nanoForward Unit                       | 185 |

|   |     | 7.4.5   | Implementation issues                                      | 187 |

|   |     | 7.4.6   | Use of the permissive <i>Concur</i>                        | 189 |

|   |     | 7.4.7   | Results                                                    | 190 |

|   | 7.5 | A slice | ed-channel wormhole router                                 | 191 |

|   |     | 7.5.1   | Introduction                                               | 192 |

|   |     | 752     | Architecture of the sliced-channel wormhole router         | 102 |

|                           |        | 7.5.3  | Results                         | 4        |

|---------------------------|--------|--------|---------------------------------|----------|

|                           | 7.6    | Summ   | ary                             | 5        |

|                           |        | 7.6.1  | Balsa                           | 5        |

|                           |        | 7.6.2  | Teak                            | 6        |

| 8                         | Con    | clusio | ns and future work 19           | 7        |

|                           | 8.1    | Balsa  |                                 | 7        |

|                           | 8.2    | Teak   |                                 | 8        |

|                           | 8.3    | Future | e work                          | 9        |

|                           |        | 8.3.1  | Description-level optimisations | 9        |

|                           |        | 8.3.2  | Peephole optimisations          | 9        |

|                           |        | 8.3.3  | Synthesis using hybrid style    | 0        |

|                           |        | 8.3.4  | Teak                            | 0        |

| $\mathbf{R}_{\mathbf{c}}$ | eferei | nces   | 20                              | <b>2</b> |

|                           | T.,    | c D    |                                 | _        |

| А                         | List   | of Ba  | lsa operators 21                | Э        |

| В                         | Bals   | a han  | dshake components 21            | 6        |

|                           | B.1    | Contro | ol components                   | 6        |

|                           |        | B.1.1  | Loop                            | 6        |

|                           |        | B.1.2  | Concur                          | 7        |

|                           |        | B.1.3  | Fork                            | 7        |

|                           |        | B.1.4  | WireFork                        | 7        |

|                           |        | B.1.5  | Sequence                        | 8        |

|                           |        | B.1.6  | Call                            | 8        |

|                           |        | B.1.7  | Sync                            | 8        |

|                           |        | B.1.8  | Arbitrate                       | 8        |

|                           |        | B.1.9  | DecisionWait                    | 9        |

|                           | B.2    | Datap  | ath components                  | 9        |

|                           |        | B.2.1  | Unary function                  | 9        |

|                           |        | B.2.2  | Binary function                 | 9        |

|                           |        | B.2.3  | CallMux                         | 9        |

|                           |        | B.2.4  | SplitEqual                      | 0        |

|                           |        | B.2.5  | CaseFetch                       | 0        |

|                           |        | B.2.6  | PassivatorPush                  | 0        |

|                           |        | B.2.7  | Variable                        | 0        |

|              | B.3 | Contro  | ol to datapth interface components               | 221         |

|--------------|-----|---------|--------------------------------------------------|-------------|

|              |     | B.3.1   | Fetch                                            | 221         |

|              |     | B.3.2   | While                                            | 221         |

|              |     | B.3.3   | Case                                             | 221         |

|              |     | B.3.4   | FalseVariable                                    | 222         |

|              |     | B.3.5   | activeEagerFalseVariable                         | 222         |

| $\mathbf{C}$ | FV  | and $a$ | eFV implementations                              | <b>22</b> 3 |

| D            | Opt | imised  | Viterbi decoder Balsa description                | <b>22</b> 6 |

| ${f E}$      | Opt | imised  | 32x32 bit Booth multiplier Balsa description     | 238         |

| F            | Opt | imised  | sliced-channel wormhole router Balsa description | <b>25</b> 0 |

| $\mathbf{G}$ | Opt | imised  | nanoSpa forwarding unit Balsa description        | 263         |

# List of Tables

| 2.1  | Dual-rail encoding for 1-bit                                             |

|------|--------------------------------------------------------------------------|

| 4.1  | BMU Simulation results                                                   |

| 4.2  | GCD Simulation results                                                   |

| 4.3  | Influence of data widths in first-read-unfold of read-write unbounded    |

|      | repetitions                                                              |

| 7.1  | Performance, area and energy for three different versions of nanoSpa.166 |

| 7.2  | Balsa nanoSpa performance, area and energy results 168                   |

| 7.3  | Teak nanoSpa performance, area and energy results 169                    |

| 7.4  | Comparison of the Balsa and Teak nano<br>Spa implementations. $$ 170     |

| 7.5  | Performance, area and energy results for the Viterbi decoder in          |

|      | Balsa                                                                    |

| 7.6  | Performance, area and energy results for the Viterbi decoder in Teak.176 |

| 7.7  | Comparison of the Viterbi decoder in Balsa and Teak 177                  |

| 7.8  | Performance, area and energy results for the MAC unit in Balsa $181$     |

| 7.9  | Performance, area and energy results for the MAC unit in Teak $181$      |

| 7.10 | Comparison of the MAC implementations using Balsa and Teak $182$         |

| 7.11 | Performance results for nanoSpa using the nFU 191                        |

| 7.12 | Energy results for nanoSpa using the nFU                                 |

| 7.13 | Balsa wormhole router simulation results                                 |

| A.1  | Balsa binary/unary operators [30]                                        |

# List of Figures

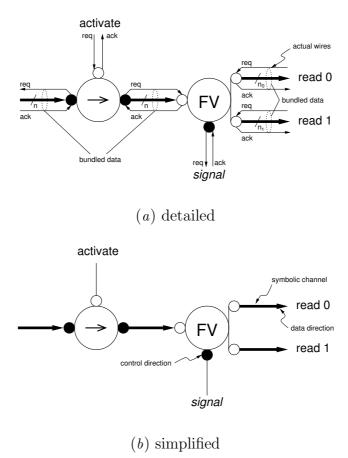

| 1.1  | A Handshake Circuit composed of a $Transferrer (\rightarrow)$ and a $False$ - |    |

|------|-------------------------------------------------------------------------------|----|

|      | Variable (FV) handshake components                                            | 22 |

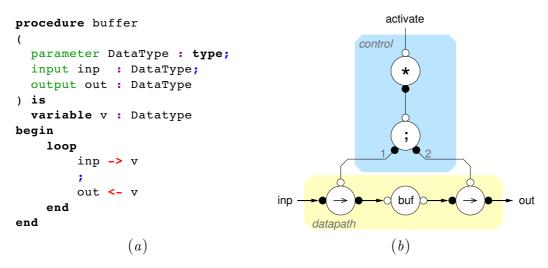

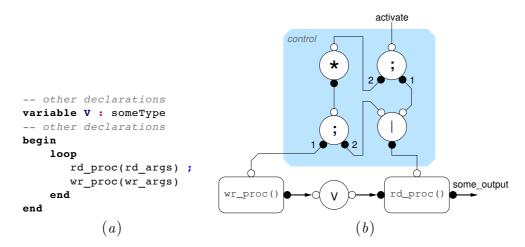

| 1.2  | 1-place buffer: (a) Balsa description, (b) handshake circuit                  | 24 |

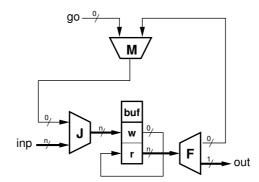

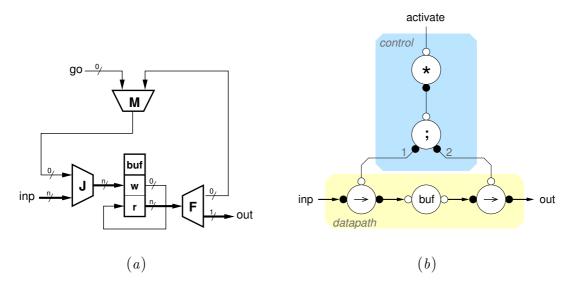

| 1.3  | Teak circuit for the 1-place buffer                                           | 27 |

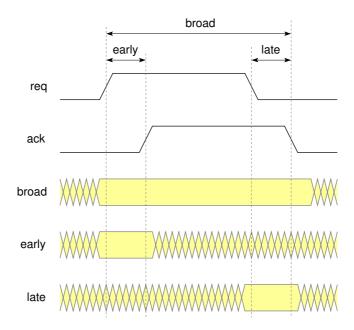

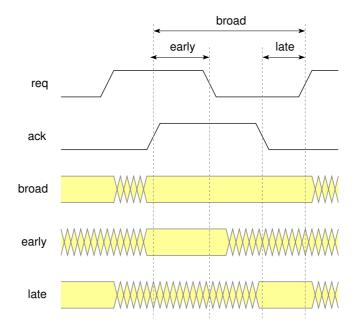

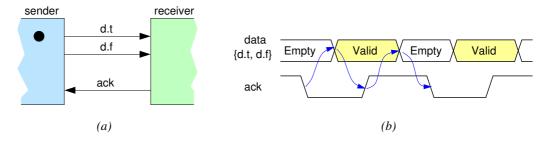

| 2.1  | Bundled-data channels                                                         | 35 |

| 2.2  | Two-phase bundled-data protocol                                               | 35 |

| 2.3  | Four-phase bundled-data protocol                                              | 36 |

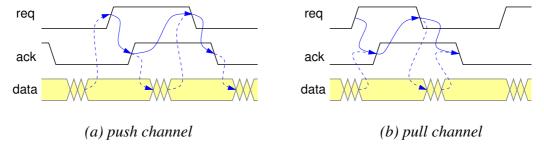

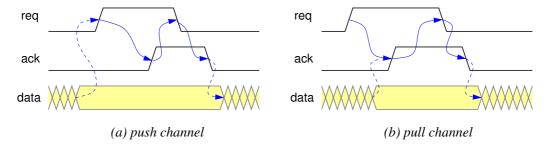

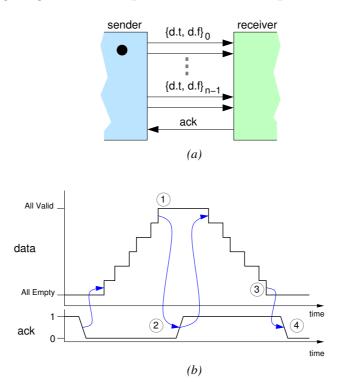

| 2.4  | Four-phase data-validity schemes for a $push$ channel                         | 37 |

| 2.5  | Four-phase data-validity schemes for a $pull$ channel                         | 37 |

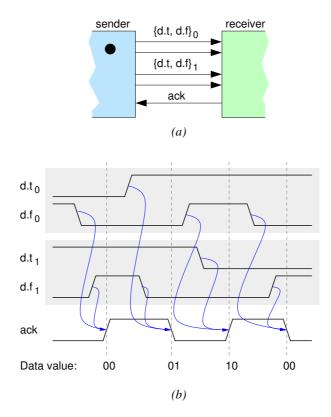

| 2.6  | Four-phase dual-rail protocol. (a) $push$ channel, (b) timing diagram.        | 39 |

| 2.7  | n-bit four-phase dual-rail protocol in a push channel                         | 40 |

| 2.8  | Two-phase dual-rail protocol in a 2-bit $push$ channel                        | 41 |

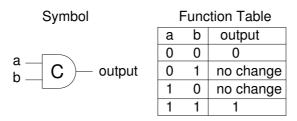

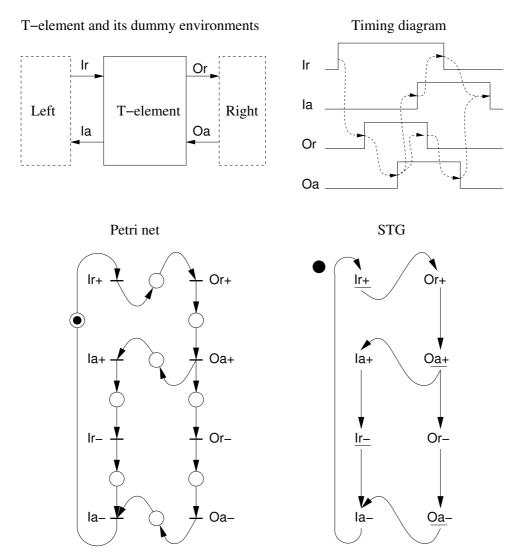

| 2.9  | The Muller C-element                                                          | 44 |

| 2.10 | A T-element connected to left and right "well behaved" environ-               |    |

|      | ments and its specification in the form of a timing diagram, a Petri          |    |

|      | net and an STG                                                                | 46 |

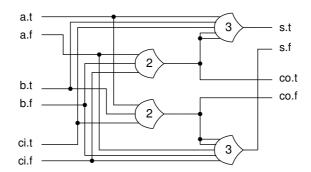

| 2.11 | A dual-rail full adder using NCL gates                                        | 52 |

| 3.1  | Balsa design flow.                                                            | 56 |

| 3.2  | The structure of a Balsa description                                          | 57 |

| 3.3  | Example of deadlocking code                                                   | 61 |

| 3.4  | An uncontrolled multiplexer (merge)                                           | 69 |

| 3.5  | Handshake circuit of the uncontrolled multiplexer                             | 69 |

| 3.6  | The description of a simple two-input adder                                   | 70 |

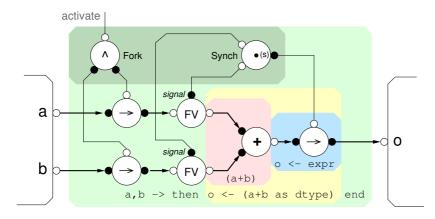

| 3.7  | Handshake circuit of the adder code in figure 3.6                             | 70 |

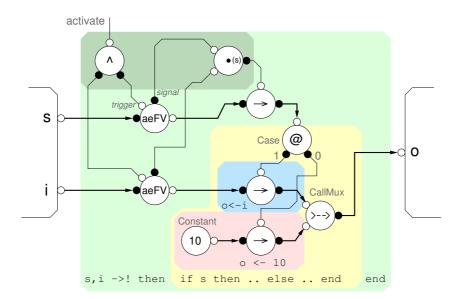

| 3.8  | Example of conditional execution                                              | 71 |

| 3.9  | Handshake circuit of the code in figure 3.8                                   | 72 |

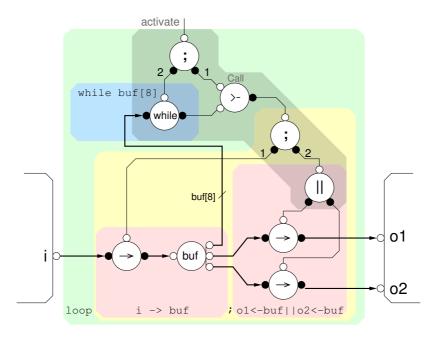

| 3.10 | An example of a finite loop and command composition                           | 73  |

|------|-------------------------------------------------------------------------------|-----|

| 3.11 | Handshake circuit of the code in figure 3.10                                  | 73  |

| 3.12 | Example of unsafe use of active eager enclosure                               | 75  |

| 3.13 | Using the permissive $Concur$ with mutually exclusive writes                  | 77  |

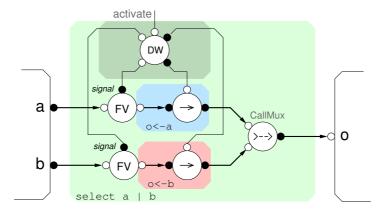

| 3.14 | Example of merging channels using the select construct                        | 77  |

| 3.15 | Example of merging channels using the permissive <i>Concur</i> opera-         |     |

|      | tor                                                                           | 78  |

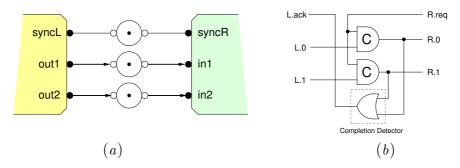

| 3.16 | (a) Interfacing of two Balsa modules with active ports using $Pas$ -          |     |

|      | sivators. (b) A 1-bit dual-rail $PassivatorPush.$                             | 79  |

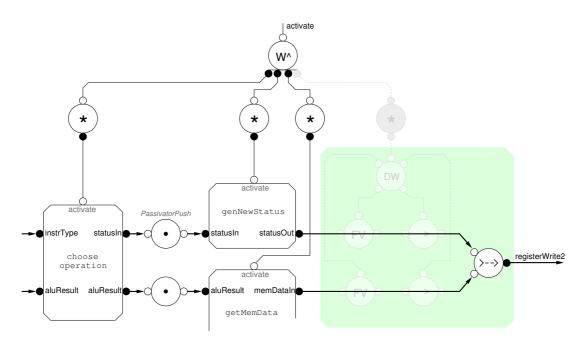

| 4.1  | The simplified control-driven SPA $EXECUTE$ stage [85]                        | 83  |

| 4.2  | The simplified data-driven SPA $EXECUTE$ stage [85]                           | 84  |

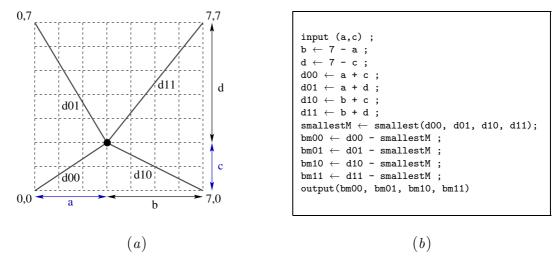

| 4.3  | Branch metric computation for a Viterbi decoder [91]                          | 85  |

| 4.4  | Initial BMU description                                                       | 86  |

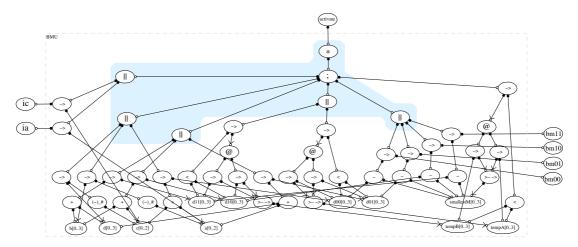

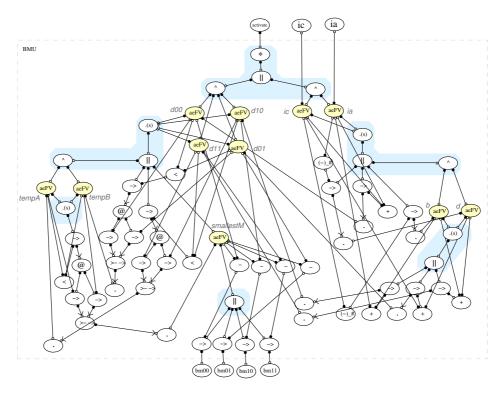

| 4.5  | Handshake circuit of the BMU                                                  | 87  |

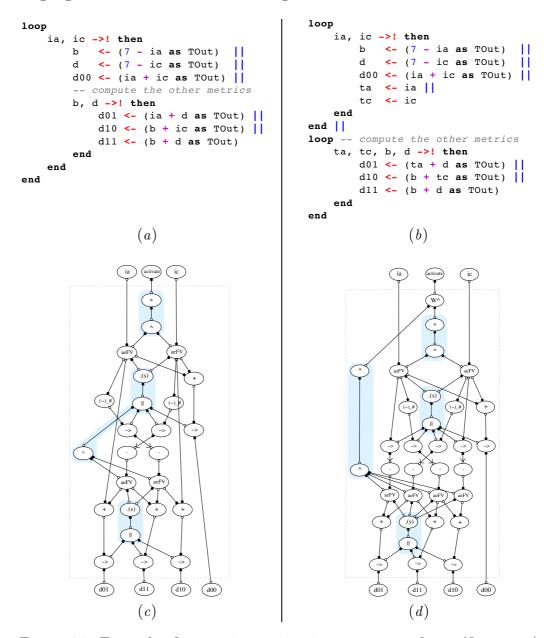

| 4.6  | First operations of the BMU: $(a)$ original, $(b)$ Data-driven                | 87  |

| 4.7  | Optimised BMU description                                                     | 88  |

| 4.8  | Handshake circuit of the optimised BMU                                        | 89  |

| 4.9  | Example of separating actions into concurrent loops (first steps)             | 91  |

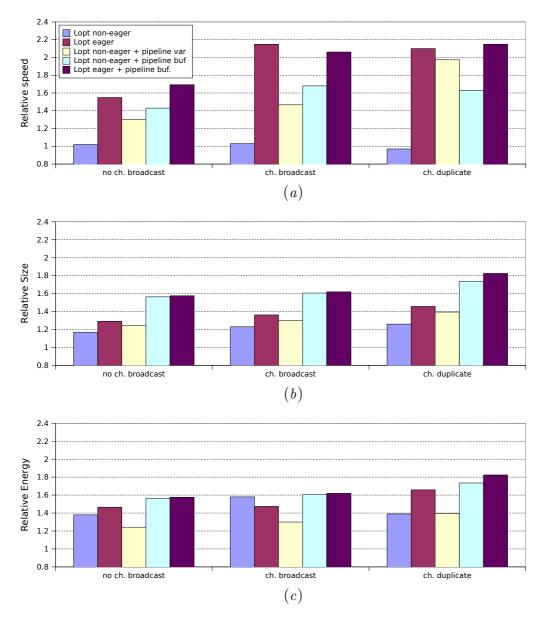

| 4.10 | Simulation results of different optimisations applied to the BMU.             | 92  |

| 4.11 | Broadcasting: $(a,c)$ Implicit broadcasting. $(b,d)$ Explicit duplication.    | 94  |

| 4.12 | Pipelining: $(a,c)$ using variables. $(b,d)$ using explicit pipeline buffers. | 96  |

| 4.13 | A pseudo-code specification of GCD [91]                                       | 97  |

| 4.14 | Two implementations of the GCD algorithm in Balsa and their                   |     |

|      | compiled handshake circuits                                                   | 99  |

| 4.15 | Simplified description of the $South$ input buffer of a sliced-channel        |     |

|      | wormhole router [90]                                                          | 01  |

| 4.16 | Optimised, simplified description of the $South$ input buffer 1               | 02  |

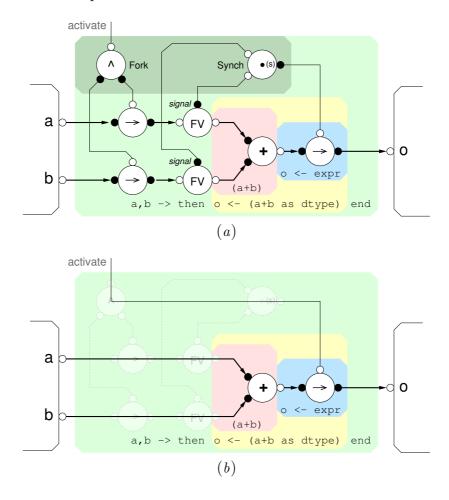

| 4.17 | Handshake circuit for example in figure $3.6$ , $(a)$ original, $(b)$ opti-   |     |

|      | mised                                                                         | .03 |

| 4.18 | (a) Fork implementation. (b) Synch implementation                             | 04  |

| 4.19 | Permanent active eager input: $(a)$ original, $(b)$ with optimised            |     |

|      | control                                                                       | .05 |

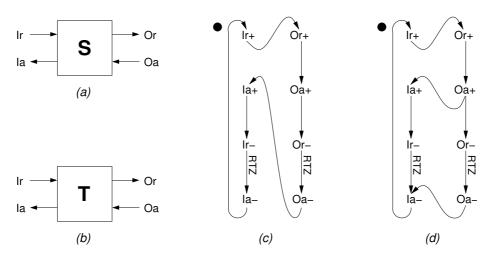

| 4.20 | (a) S-element. (b) T-element. (c) S-element STG. (d) T-element                |     |

|      | STG                                                                           | 06  |

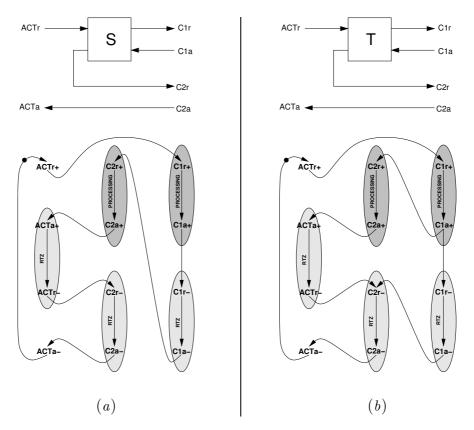

| 4.21 | Balsa sequencers: $(a)$ based on the S-element, $(b)$ based on the          |      |

|------|-----------------------------------------------------------------------------|------|

|      | T-element [89]                                                              | 107  |

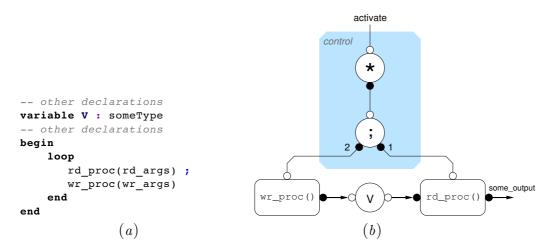

| 4.22 | Read-write loop: $(a)$ code, $(b)$ handshake circuit                        | 108  |

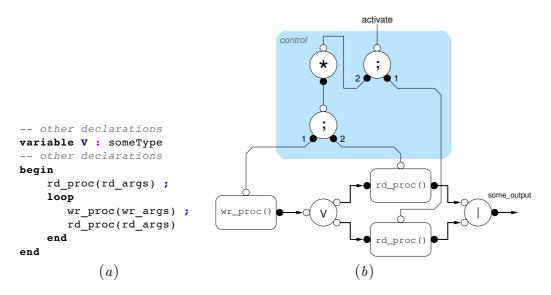

| 4.23 | First-read-unfolded version of circuit in figure 4.22                       | 108  |

| 4.24 | Optimised first-read-unfolded read-write loop                               | 109  |

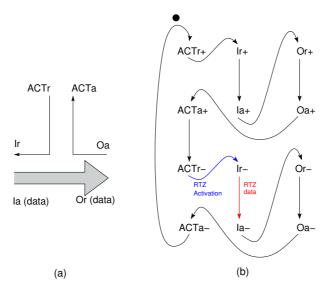

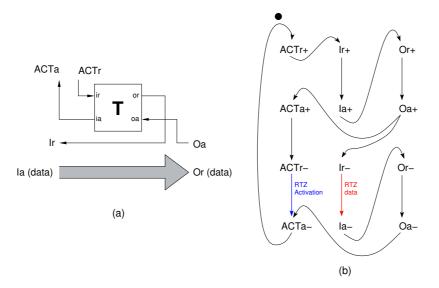

| 4.25 | Conventional Balsa dual-rail $Fetch$ : (a) circuit, (b) STG                 | 110  |

| 4.26 | Fetch with concurrent RTZ: $(a)$ circuit, $(b)$ STG                         | 110  |

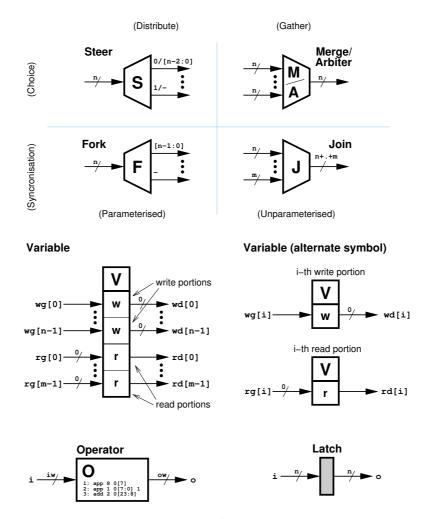

| 5.1  | Teak components                                                             | 115  |

| 5.2  | (a) Teak circuit for 1-place buffer, (b) Handshake circuit for 1-           |      |

|      | place buffer                                                                | 116  |

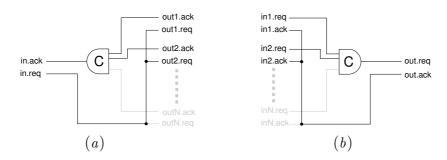

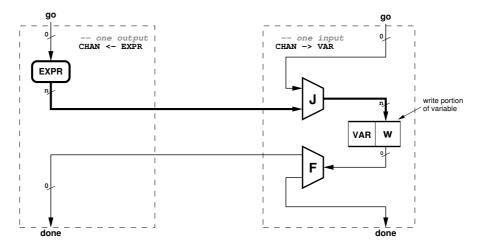

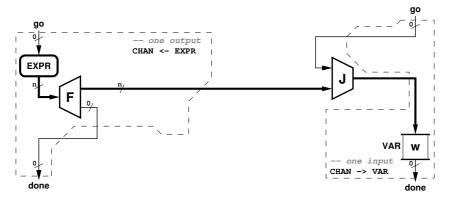

| 5.3  | Balsa-style channel implementation                                          | 117  |

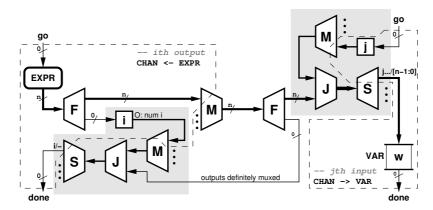

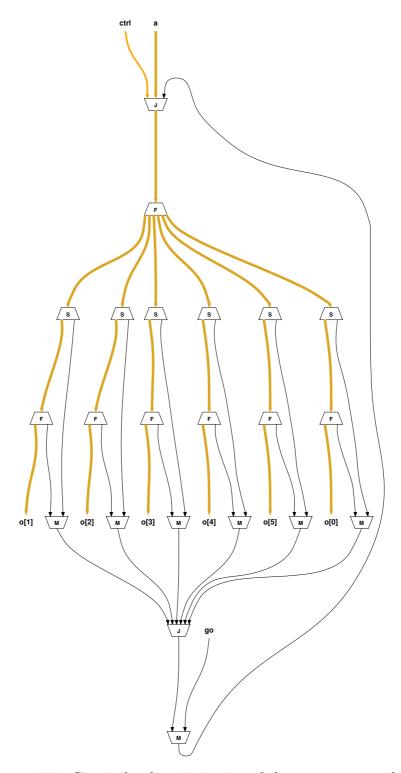

| 5.4  | Multiple-output channel implementation                                      | 118  |

| 5.5  | Channel component optimisation                                              | 118  |

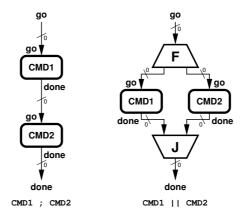

| 5.6  | Sequential/parallel composition                                             | 119  |

| 5.7  | While loop implementation                                                   | 120  |

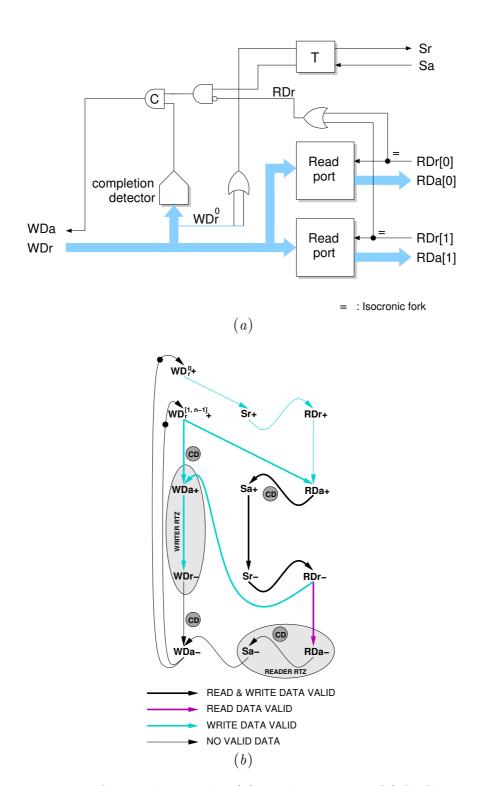

| 5.8  | Variable single read-after-write optimisation                               | 121  |

| 5.9  | Balsa code for n-bit full adder. $\hdots$                                   | 121  |

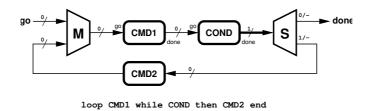

| 5.10 | Variable substitution example                                               | 122  |

| 5.11 | Sequential write to a channel                                               | 123  |

| 5.12 | Sequenced channel write example: $(a)$ original, $(b)$ after $Fork$ dis-    |      |

|      | placement                                                                   | 123  |

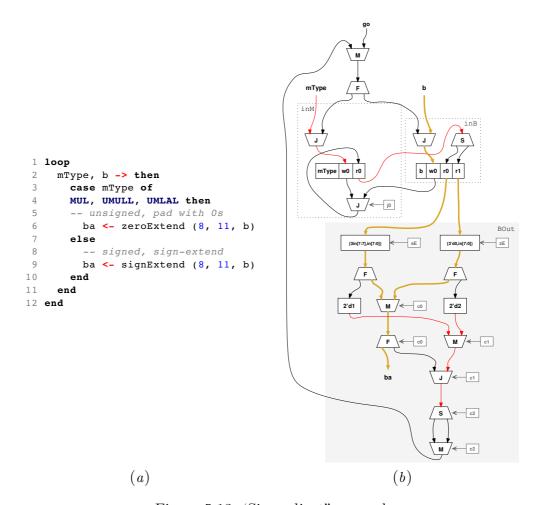

| 5.13 | 'Sign adjust" example                                                       | 125  |

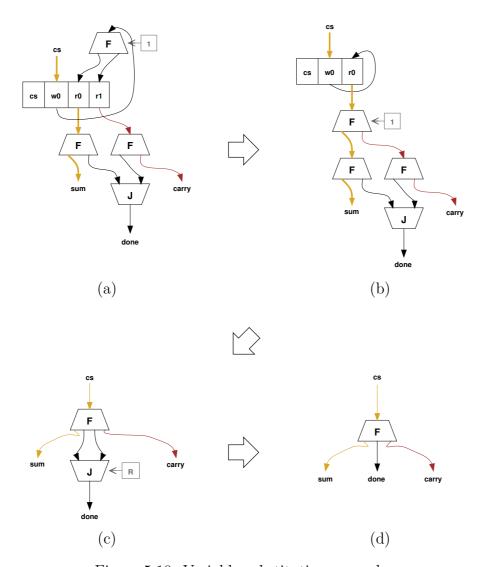

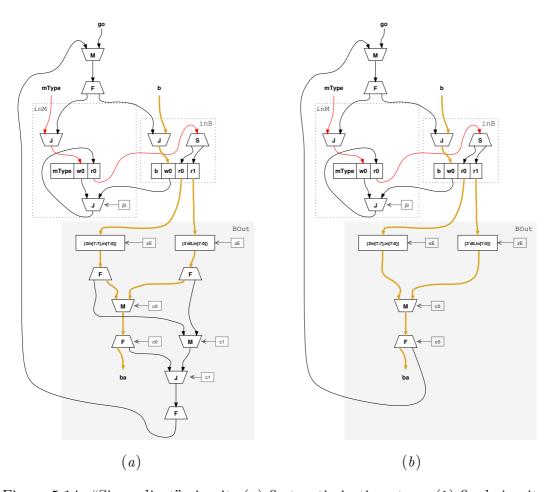

| 5.14 | "Sign adjust" circuit: $(a)$ first optimisation steps, $(b)$ final circuit. | 126  |

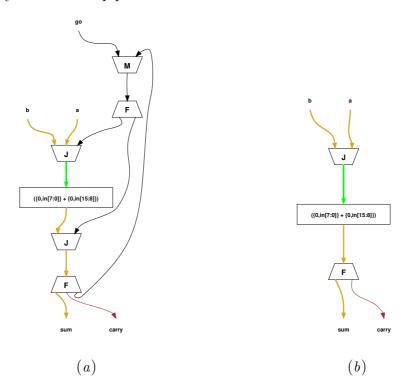

| 5.15 | Teak circuit of the N-bit adder: $(a)$ Optimised, $(b)$ With the "go"       |      |

|      | cycle removed                                                               | 127  |

| 5.16 | Avoiding <i>Variables</i> associated with conditional reads                 | 129  |

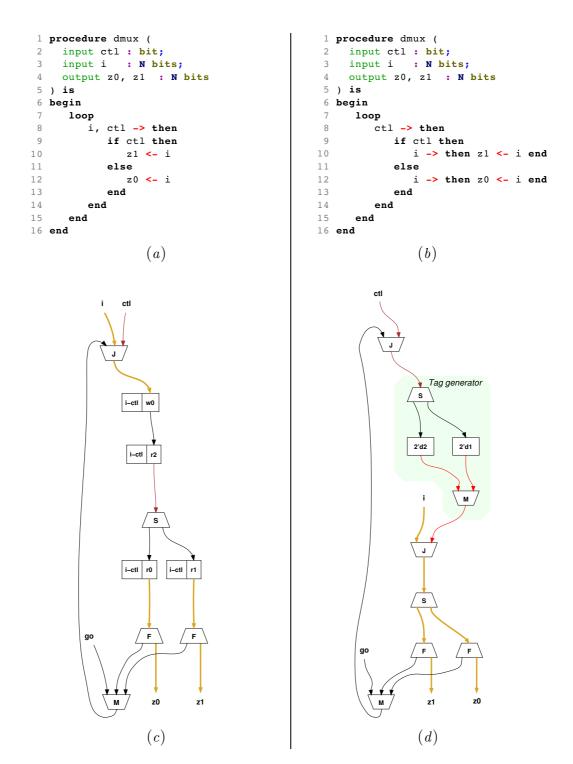

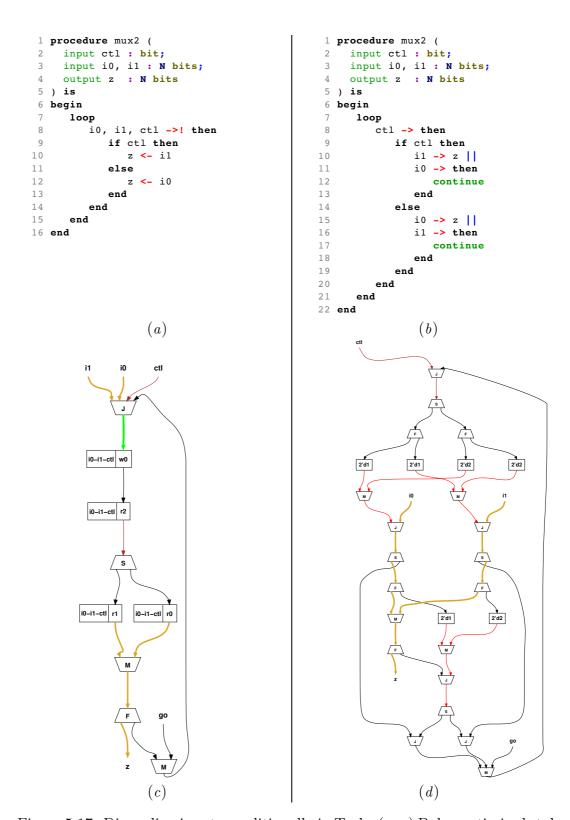

| 5.17 | Discarding inputs conditionally in Teak: $(a, c)$ Balsa-optimised           |      |

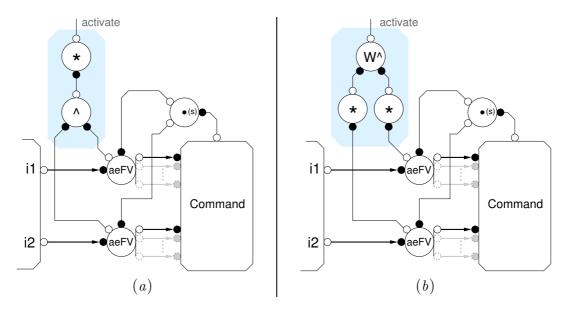

|      | style; $(b, d)$ Teak-optimised style                                        | 131  |

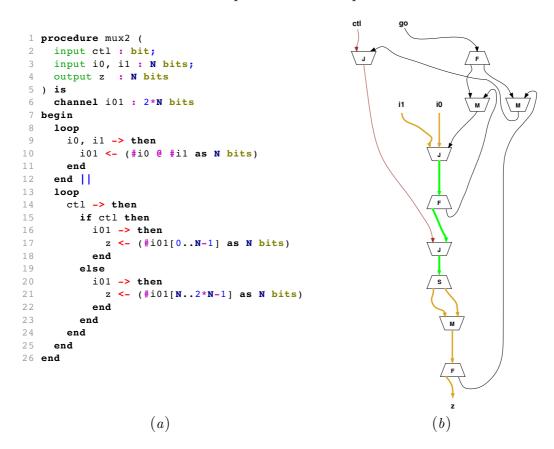

| 5.18 | Joining inputs to reduce the tagging circuitry                              | 132  |

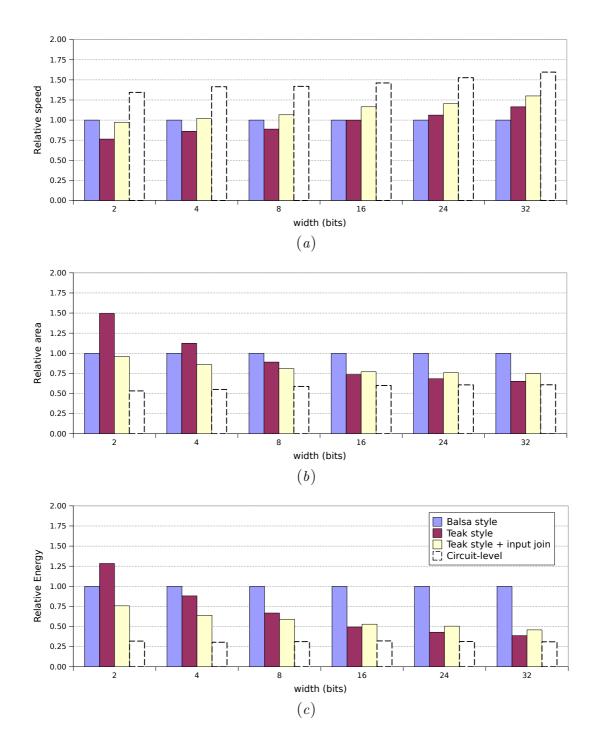

| 5.19 | Simulation results for different optimised versions of the mux example      | .134 |

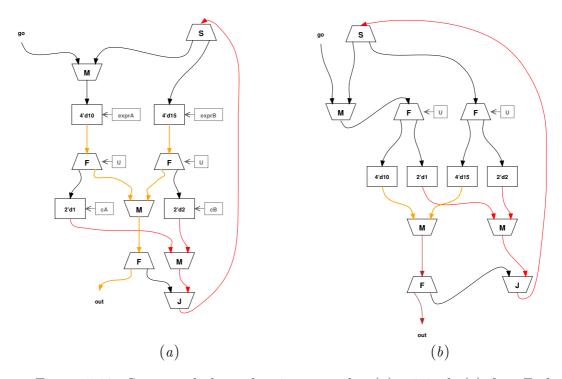

| 5.20 | steerAlu example: (a) original, (b) channel duplication to avoid            |      |

|      | conditional reads                                                           | 135  |

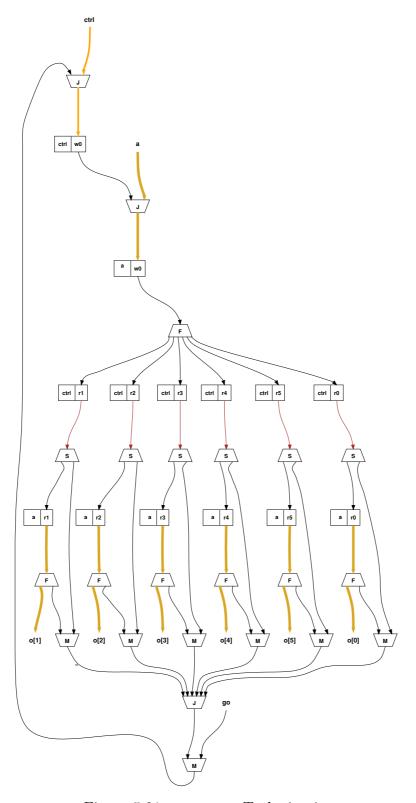

|      | steerAlu Teak circuit.                                                      | 136  |

|      | Optimised steerAlu Teak circuit                                             |      |

| 5 23 | Simulation results for the steer Alu example                                | 138  |

|      | Circuit-level conditional reads removal                                             | 140<br>141 |

|------|-------------------------------------------------------------------------------------|------------|

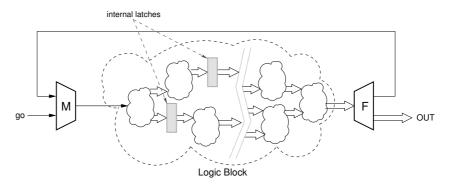

| 6.1  | The Teak single-token loop Merge - Logic block - Fork structure.                    | 145        |

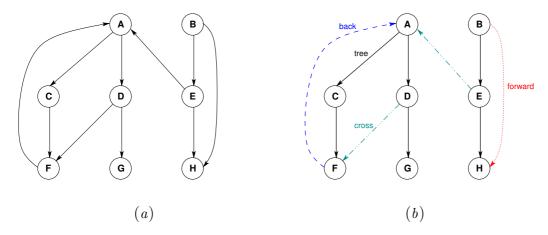

| 6.2  | (a) A directed graph and (b) a depth-first forest of the graph. $\cdot \cdot \cdot$ | 146        |

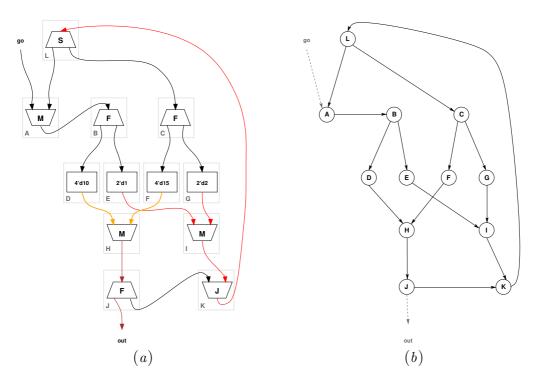

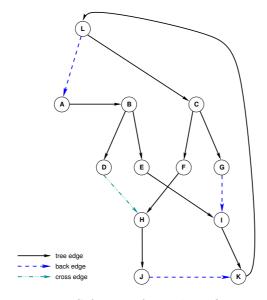

| 6.3  | Mapping of a Teak circuit into a directed graph                                     | 148        |

| 6.4  | DFS forest of graph in figure 6.3(b)                                                | 148        |

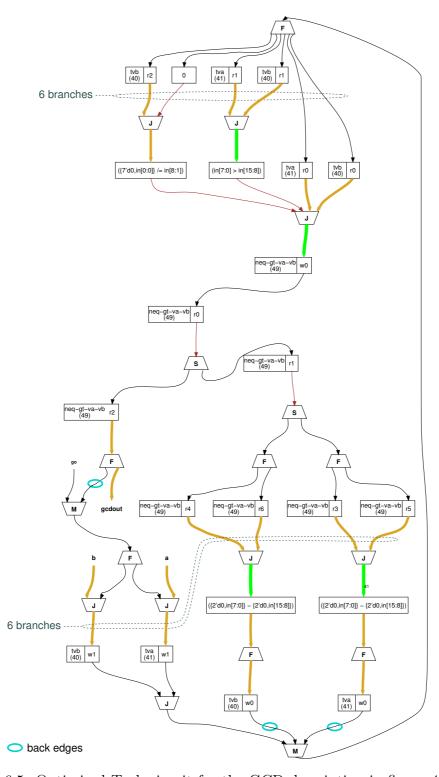

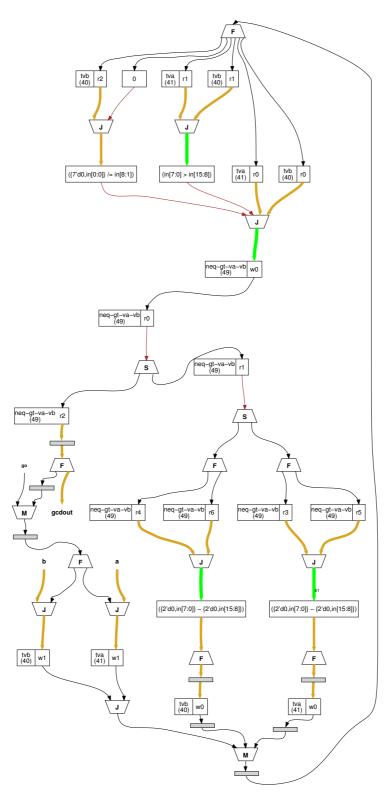

| 6.5  | Optimised Teak circuit for the GCD description in figure 4.14(b)                    | 150        |

| 6.6  | Strategy for latching all cycles of the GCD circuit of figure 6.5                   |            |

|      | based in latching back edges                                                        | 152        |

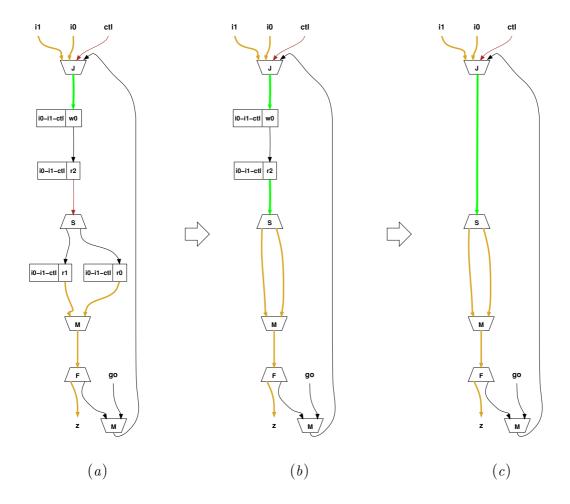

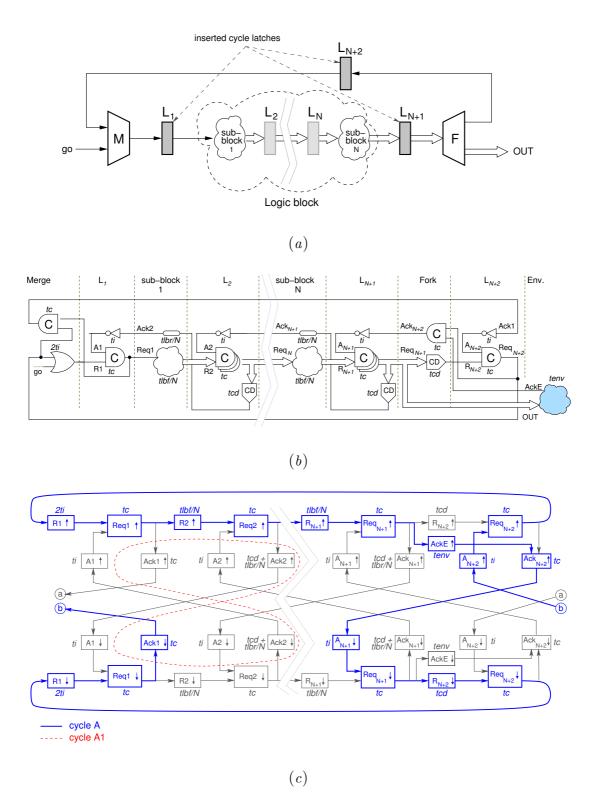

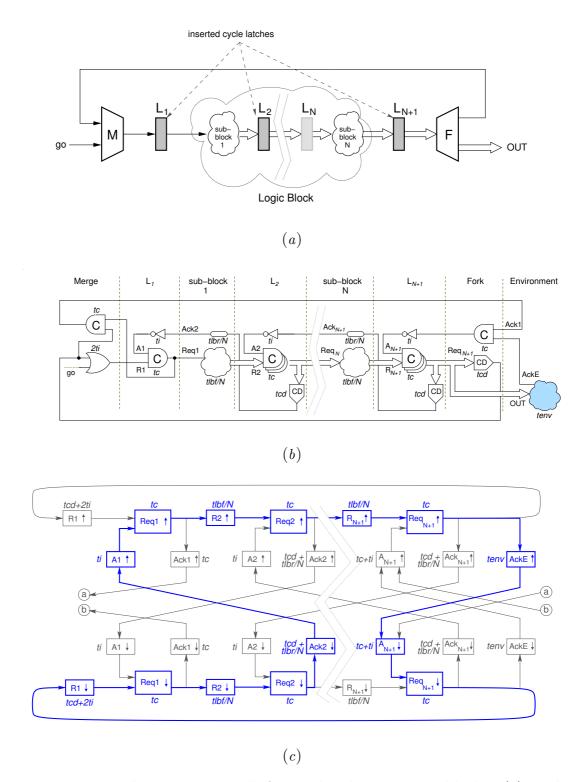

| 6.7  | Latching strategy "A" for single-token $M\text{-}LB\text{-}F$ blocks: (a) Teak      |            |

|      | circuit, $(b)$ logic circuit, $(c)$ dependency graph                                | 154        |

| 6.8  | Latching strategy "B" for single-token $M\text{-}LB\text{-}F$ blocks: (a) Teak      |            |

|      | circuit, $(b)$ logic circuit, $(c)$ dependency graph                                | 155        |

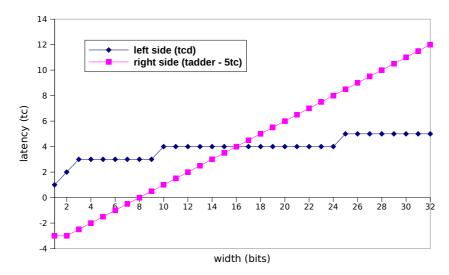

| 6.9  | Comparison of both sides of inequality $6.6$ for different data widths.             | 158        |

| 6.10 | Example of passing options at procedure-level                                       | 159        |

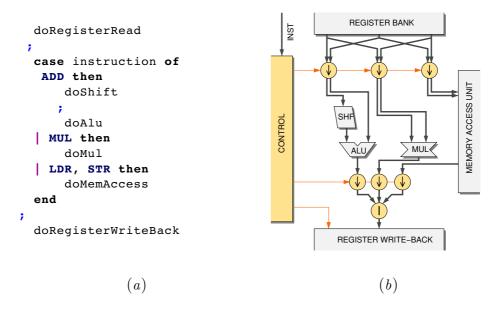

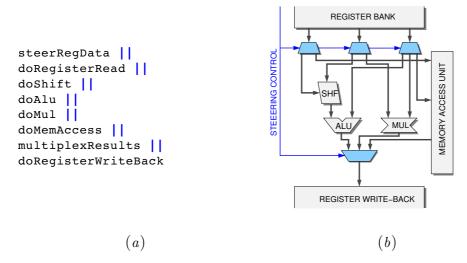

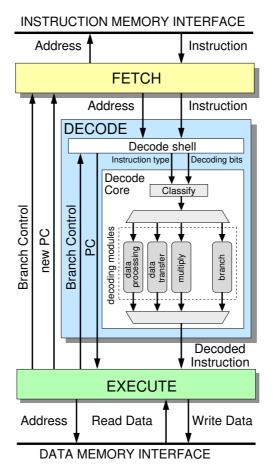

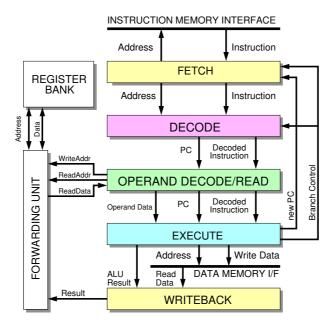

| 7.1  | The 3-stage nanoSpa pipeline showing details of the <i>Decode</i> stage.            | 163        |

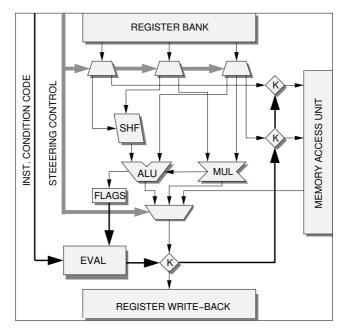

| 7.2  | Simplified nanoSpa Execute stage                                                    | 165        |

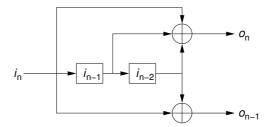

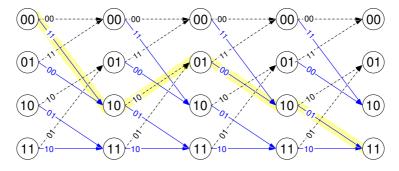

| 7.3  | A convolutional encoder with $k=3$ and code ratio = $1/2$                           | 171        |

| 7.4  | Trellis diagram for the encoder in figure 7.3                                       | 171        |

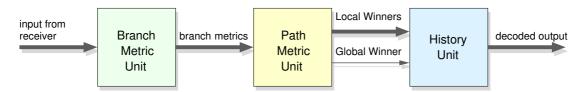

| 7.5  | Architecture of the asynchronous Viterbi decoder                                    | 172        |

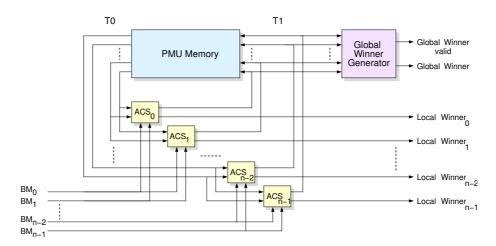

| 7.6  | The Path Metric Unit                                                                | 173        |

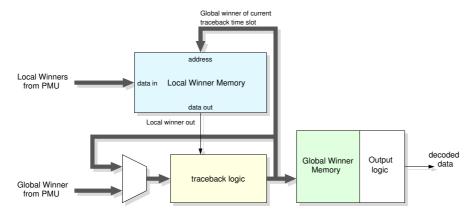

| 7.7  | The History Unit.                                                                   | 174        |

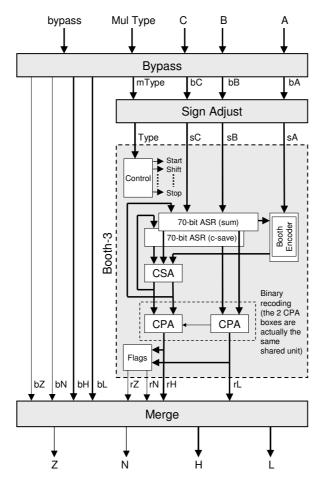

| 7.8  | Architecture of the nanoSpa multiplier unit                                         | 178        |

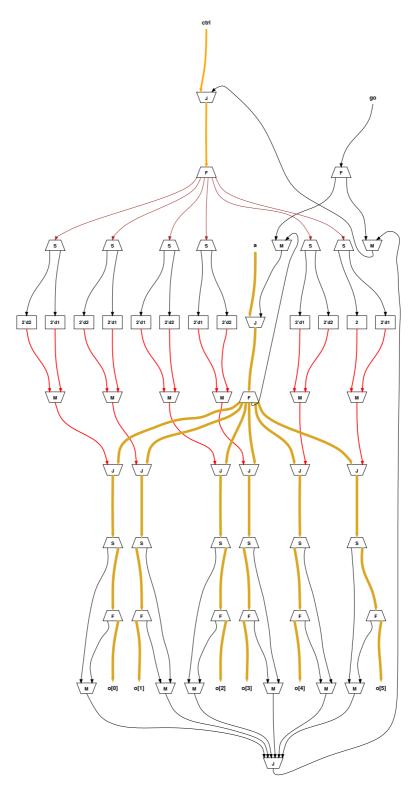

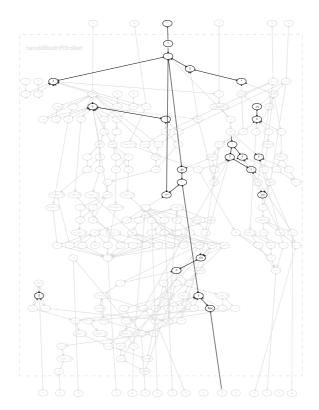

| 7.9  | An "X-ray" picture of the Booth-3 Handshake Circuit revealing its                   |            |

|      | control tree.                                                                       | 180        |

| 7.10 | Potential performance benefits of result forwarding in a 4-stage                    |            |

|      | pipeline.                                                                           | 183        |

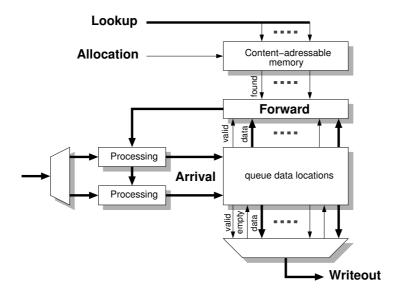

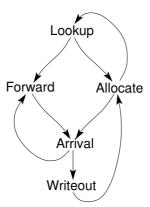

|      | AQF process model                                                                   | 184        |

| 7.12 | The 5-stage nanoSpa pipeline                                                        | 186        |

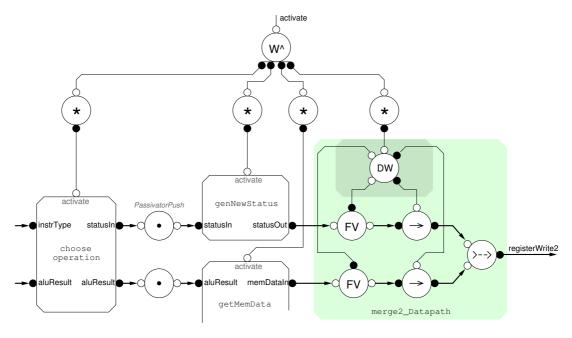

|      | The nanoForward Unit architecture                                                   | 186        |

|      | Inter-process dependencies in the nFU                                               | 187        |

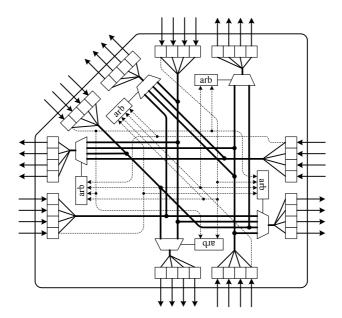

|      | Composition of actions with the permissive <i>Concur</i> inside the nFU.            |            |

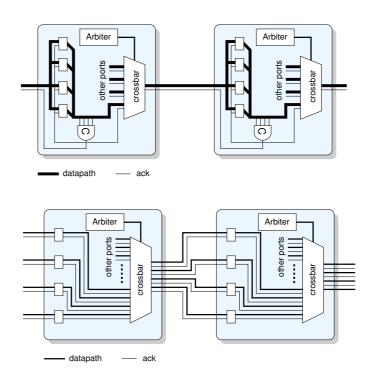

|      | Wormhole NoC datapath [90]                                                          |            |

| 7.17 | Sliced-channel wormhole router with four sub-channels [90]                          | 194        |

| C.1 | False Variable: (a) Implementation, $(b)$ STG         | 224 |

|-----|-------------------------------------------------------|-----|

| C.2 | activeEagerFalseVariable: (a) Implementation, (b) STG | 225 |

## Abstract

This thesis evaluates the capabilities and limitations of the syntax-directed approach to synthesise high-performance asynchronous systems and proposes a number of optimisations to improve the performance of the synthesised circuits.

The first part of this work explores new methods for improving the performance of asynchronous circuits synthesised from syntax-directed descriptions, targeting handshake circuits and using the Balsa synthesis system as the research framework. This includes investigating description styles and the use of language constructs that result in faster circuits. A number of new peephole optimisations based on the previous observations are also presented.

The second part investigates the performance of a new, token-flow based synthesiser for the Balsa language called *Teak*. A set of optimisations based in circuit transformations and buffering strategies are proposed in order to improve the performance of Teak circuits. These optimisations have been automated and incorporated into the Teak synthesiser.

All optimisations target dual-rail, quasi-delay-insensitive implementations as this is a robust approach that helps to reduce the impact of the timing closure problem within modern fabrication processes variability. The techniques and optimisations presented here has been tested in a set of non-trivial examples including a 32-bit RISC processor.

The use of the proposed techniques result in optimised compositions of handshake circuits and Teak components that generally synthesise into faster circuits.

# **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the "Copyright") and s/he has given The University of Manchester the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

- ii. Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the John Rylands University Library of Manchester. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

- iii. The ownership of any patents, designs, trade marks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and exploitation of this thesis, the Copyright and any Intellectual Property Rights and/or Reproductions described in it may take place is available from the Head of School of Computer Science (or the Vice-President).

# Acknowledgements

I would like to express my deep gratitude to my parents Nelly and Luis for all the love and support they have always given me. My life has been blessed by having them as my parents. Thanks to all my brothers and sisters, nieces and nephews for their support and their love. I have been missing you all a lot.

Thanks to my supervisor Doug Edwards who gave me the opportunity of doing this PhD under his supervision. Thanks to my fine proof readers Andrew Bardsley and Will Toms for all the careful reading and comments done on my writing. I must thank Andrew twice for giving me the opportunity of working with him on his Teak system and having introduced me to the beauties of the Haskell language. Many thanks to Charlie Brej for all his support, nice food, friendship and for doing the final proof read of my thesis. Thanks to Wei Song for kindly allowing me to use his router design. Thanks to Mikel Luján for his advice and support.

My special gratitude to Luis Plana for all his support, advice and encouragement. Many thanks "Luis One". Thanks to the whole Plana Oteiza family for being my family here in Manchester. Thanks to all my friends and families from Barquisimeto, Venezuela, specially to my brother José Ortiz and his family: ¡Gracias José! Thank you dear Emilia for giving me your love and support during all these years.

Thanks to the people I have met in the APT group. I have learnt many things from them. I am sure I will forget many names if I try to list them.

Finally, thanks to the School of Computer Science and EPSRC for the financial support I have received during my PhD.

| To my Parents, my nieces and nephews, my brotheres and sisters, and my families from Barquisimeto. |

|----------------------------------------------------------------------------------------------------|

|                                                                                                    |

| A mis Padres, mis sobrinas y sobrinos, mis hermanas y hermanos, y a mis familias de Barquisimeto.  |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

# Chapter 1

## Introduction

#### 1.1 Motivation