# DATA-DRIVEN HANDSHAKE CIRCUIT SYNTHESIS

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2007

By Samuel M Taylor School of Computer Science

## Contents

| Ał | ostrac | t                                      | 15 |

|----|--------|----------------------------------------|----|

| De | eclara | tion                                   | 17 |

| Co | opyrig | ht                                     | 19 |

| Ac | cknov  | ledgements                             | 21 |

| 1  | Intro  | oduction                               | 23 |

|    | 1.1    | Asynchronous synthesis methods         | 24 |

|    |        | 1.1.1 De-synchronisation based methods | 24 |

|    |        | 1.1.2 CHP based methods                | 25 |

|    |        | 1.1.3 Macromodular based methods       | 26 |

|    | 1.2    | Aims of this research                  | 27 |

|    | 1.3    | Contributions of this thesis           | 28 |

|    | 1.4    | Thesis structure                       | 28 |

|    | 1.5    | Publications                           | 30 |

| 2  | Bacl   | ground                                 | 31 |

|    | 2.1    | Handshaking                            | 31 |

|    |        | 2.1.1 Handshake protocols              | 32 |

|    |        | 2.1.2 Data encoding                    | 33 |

|    | 2.2    | Signal Transition Graphs               | 36 |

|    | 2.3    | Balsa design flow                      | 38 |

|   | 2.4  | Hand    | shake Circuits and Balsa                           | 40 |

|---|------|---------|----------------------------------------------------|----|

|   |      | 2.4.1   | Handshake circuit diagrams                         | 40 |

|   | 2.5  | Balsa   | language and compilation                           | 42 |

|   |      | 2.5.1   | Data types                                         | 42 |

|   |      | 2.5.2   | Basic commands                                     | 43 |

|   |      | 2.5.3   | Parallel and Sequence control                      | 44 |

|   |      | 2.5.4   | Conditional control                                | 45 |

|   |      | 2.5.5   | Iterative control                                  | 47 |

|   |      | 2.5.6   | Input enclosure                                    | 47 |

|   |      | 2.5.7   | Arbitration                                        | 49 |

|   |      | 2.5.8   | Data processing                                    | 49 |

|   |      | 2.5.9   | Miscellaneous connection components                | 50 |

|   | 2.6  | Imple   | menting handshake components                       | 53 |

|   |      | 2.6.1   | Control elements                                   | 54 |

|   |      | 2.6.2   | Dual-rail elements                                 | 58 |

|   |      | 2.6.3   | Completion Detection                               | 60 |

|   | 2.7  | What    | does 'performance' mean in an asynchronous circuit | 61 |

| 3 | Data | a-drive | n Circuit Style                                    | 63 |

|   | 3.1  | Contr   | ol overhead                                        | 63 |

|   |      | 3.1.1   | Balsa features to combat control overhead          | 67 |

|   |      | 3.1.2   | Data-driven style design aims                      | 70 |

|   | 3.2  | Why a   | a data-driven approach?                            | 72 |

|   | 3.3  | Why a   | a handshake circuit style approach?                | 73 |

|   | 3.4  | Why     | not a data-driven approach?                        | 73 |

|   | 3.5  | Data-   | driven circuit structures                          | 74 |

|   |      | 3.5.1   | Input                                              | 75 |

|   |      | 3.5.2   | Variables                                          | 77 |

|   |      | 3.5.3   | Data processing                                    | 78 |

|   |      | 3.5.4   | Conditionals                                       | 83 |

|   |      | 3.5.5                          | Conditional input                             | 87  |

|---|------|--------------------------------|-----------------------------------------------|-----|

|   |      | 3.5.6                          | Nested conditionals                           | 91  |

|   |      | 3.5.7                          | Arbitration                                   | 92  |

|   |      | 3.5.8                          | Arrayed variables                             | 94  |

|   |      | 3.5.9                          | Sync channels                                 | 100 |

|   | 3.6  | New i                          | nput language                                 | 100 |

|   |      | 3.6.1                          | Hello World!                                  | 101 |

|   |      | 3.6.2                          | Variables                                     | 102 |

|   |      | 3.6.3                          | Input 'control'                               | 103 |

|   |      | 3.6.4                          | Write command                                 | 103 |

|   |      | 3.6.5                          | Arrays                                        | 103 |

|   |      | 3.6.6                          | Structural iteration                          | 104 |

|   |      | 3.6.7                          | Initialisation                                | 107 |

|   |      | 3.6.8                          | Restrictions                                  | 107 |

|   | 3.7  | A note                         | e on temporal iteration                       | 111 |

| 4 | Usir | ng the c                       | lata-driven style                             | 115 |

|   | 4.1  | Integr                         | ation into Balsa design flow                  | 115 |

|   | 4.2  | Back-e                         | end implementations                           | 117 |

|   | 4.3  | Source                         | e-level optimisation                          | 118 |

|   |      | 4.3.1                          | The example                                   | 119 |

|   |      | 4.3.2                          | Avoiding speculative operation                | 120 |

|   |      | 4.3.3                          | Adding pipelining                             | 123 |

|   |      | 4.3.4                          | Discussion                                    | 126 |

|   | 4.4  | Data-c                         | driven style as a target for optimising Balsa | 126 |

| 5 | Des  | ign Exa                        | mple                                          | 131 |

|   | 5.1  | 1 Manchester Asynchronous ARMs |                                               |     |

|   | 0.1  | winter                         |                                               | 131 |

|   | 5.2  |                                | tives of this example                         | 132 |

|   |      | Object                         |                                               | 132 |

|   | 5.4  | Data-o  | driven nanoSpa          | 134 |

|---|------|---------|-------------------------|-----|

|   |      | 5.4.1   | Fetch                   | 135 |

|   |      | 5.4.2   | Decode                  | 139 |

|   |      | 5.4.3   | Register Bank           | 142 |

|   |      | 5.4.4   | Execute                 | 146 |

|   |      | 5.4.5   | Pipelining issues       | 148 |

|   | 5.5  | Simula  | ation results           | 150 |

|   |      | 5.5.1   | Dual-rail               | 151 |

|   |      | 5.5.2   | Bundled data            | 154 |

|   | 5.6  | Regist  | er bank hybrid design   | 156 |

| c | Car  | -1      |                         | 167 |

| 6 |      | clusion |                         | 157 |

|   | 6.1  |         | e work                  |     |

|   |      | 6.1.1   | Language and compiler   |     |

|   |      | 6.1.2   | Back-end and components |     |

|   |      | 6.1.3   | nanoSpa                 |     |

|   | 6.2  | Summ    | nary                    | 164 |

| A | Lang | guage ( | Grammar                 | 165 |

| B | New  | v Hand  | shake Components        | 169 |

|   | B.1  | Variab  | plePush                 | 170 |

|   | B.2  | Dup .   |                         | 173 |

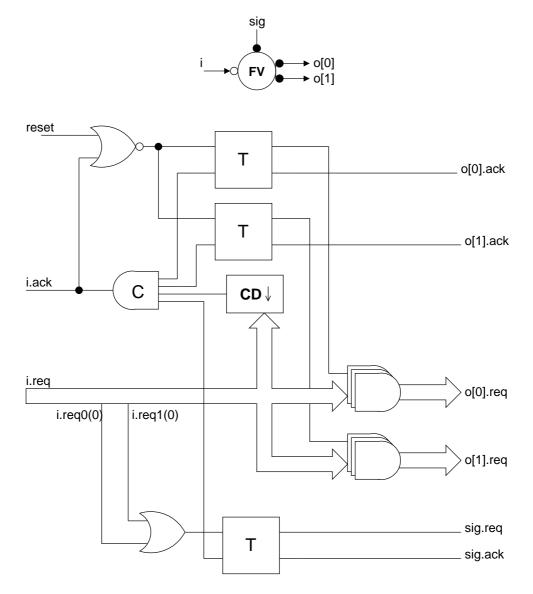

|   | B.3  | FVPus   | sh                      | 175 |

|   | B.4  | Fetch   | Push                    | 178 |

|   | B.5  | FetchF  | Reject                  | 180 |

|   | B.6  | CaseP   | Push                    | 182 |

|   | B.7  | CaseP   | PushR                   | 185 |

|   | B.8  | Mux .   |                         | 188 |

| _ | _    |         |                         |     |

| С | Data | a-drive | n nanoSpa description   | 191 |

| D | Bals | a Hands | shake Components                  | 209 |

|---|------|---------|-----------------------------------|-----|

|   | D.1  | Contro  | l components                      | 210 |

|   |      | D.1.1   | Loop                              | 210 |

|   |      | D.1.2   | Concur                            | 210 |

|   |      | D.1.3   | Fork                              | 210 |

|   |      | D.1.4   | Sequence                          | 211 |

|   |      | D.1.5   | Call                              | 211 |

|   |      | D.1.6   | Sync                              | 211 |

|   |      | D.1.7   | Arbitrate                         | 211 |

|   |      | D.1.8   | DecisionWait                      | 212 |

|   | D.2  | Contro  | l / datapath interface components | 212 |

|   |      | D.2.1   | Fetch                             | 212 |

|   |      | D.2.2   | While                             | 212 |

|   |      | D.2.3   | Case                              | 213 |

|   |      | D.2.4   | FalseVariable                     | 213 |

|   |      | D.2.5   | UnaryFunc                         | 213 |

|   |      | D.2.6   | BinaryFunc                        | 214 |

|   |      | D.2.7   | CallMux                           | 214 |

|   |      | D.2.8   | SplitEqual                        | 214 |

|   |      | D.2.9   | CaseFetch                         | 214 |

|   |      | D.2.10  | PassivatorPush                    | 215 |

|   |      | D.2.11  | Variable                          | 215 |

|   |      |         |                                   |     |

#### References

217

## **List of Figures**

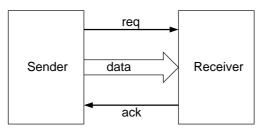

| 2.1  | Push data channel                                   | 32 |

|------|-----------------------------------------------------|----|

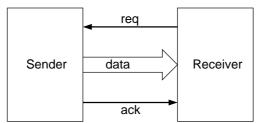

| 2.2  | Pull data channel                                   | 32 |

| 2.3  | Four-phase handshake protocol                       | 33 |

| 2.4  | Push data validity protocols                        | 34 |

| 2.5  | Pull data validity protocols                        | 35 |

| 2.6  | Four-phase dual-rail handshakes                     | 36 |

| 2.7  | Call STG                                            | 37 |

| 2.8  | Balsa design flow                                   | 39 |

| 2.9  | Handshake circuit diagram                           | 41 |

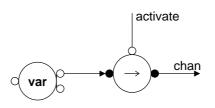

| 2.10 | Balsa channel read (and write into a variable)      | 43 |

| 2.11 | Balsa channel write (from a variable)               | 43 |

| 2.12 | Balsa assignment                                    | 44 |

| 2.13 | Balsa case example                                  | 46 |

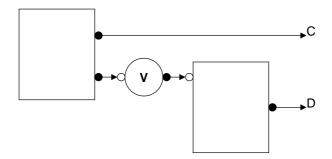

| 2.14 | Balsa While component                               | 47 |

| 2.15 | Balsa input enclosure example                       | 48 |

| 2.16 | Balsa data processing example                       | 50 |

| 2.17 | Balsa variable write from multiple possible sources | 51 |

| 2.18 | STG comparison of Fork and Concur                   | 52 |

| 2.19 | PassivatorPush component                            | 52 |

| 2.20 | C-element with two inputs                           | 54 |

| 2.21 | Sync component implementation                       | 55 |

| 2.22 | Asymmetric C-element                                | 55 |

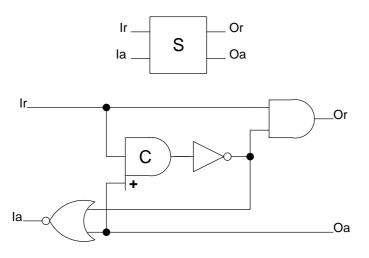

| 2.23 | S-element implementation                           | 56 |

|------|----------------------------------------------------|----|

| 2.24 | S-element STG                                      | 57 |

| 2.25 | FalseVariable control circuit                      | 57 |

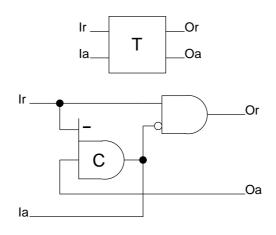

| 2.26 | T-element implementation                           | 58 |

| 2.27 | T-element STG                                      | 58 |

| 2.28 | Read Port                                          | 59 |

| 2.29 | Merge                                              | 59 |

| 2.30 | Decode                                             | 60 |

| 2.31 | Single to dual-rail converter                      | 60 |

| 2.32 | Completion Detection                               | 61 |

| 3.1  | General control-driven structure                   | 64 |

| 3.2  | General data-driven structure                      | 70 |

| 3.3  | Control-driven vs. data-driven                     | 71 |

| 3.4  | Balsa input structure                              | 75 |

| 3.5  | Data-driven input structure                        | 76 |

| 3.6  | Variable component with three read ports           | 76 |

| 3.7  | VariablePush component with three read ports       | 77 |

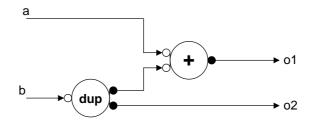

| 3.8  | Balsa data processing structure                    | 78 |

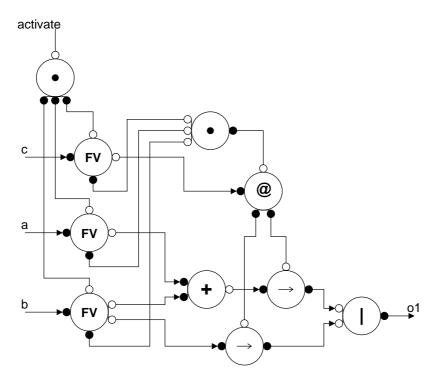

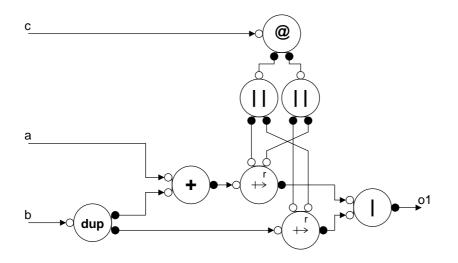

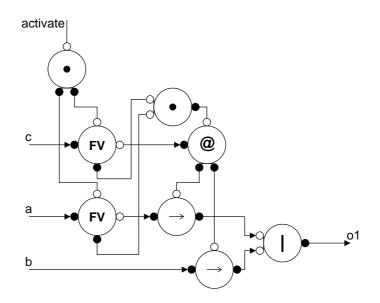

| 3.9  | Data-driven data processing structure              | 79 |

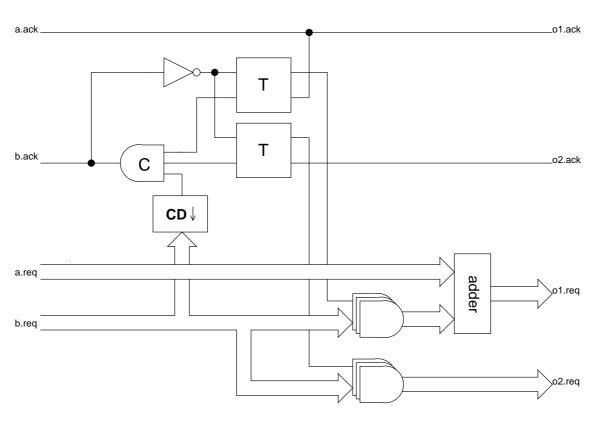

| 3.10 | Single-rail data processing control circuit        | 80 |

| 3.11 | Single-rail data-driven processing control circuit | 80 |

| 3.12 | Dual-rail data processing circuit                  | 81 |

| 3.13 | Dual-rail data-driven processing circuit           | 82 |

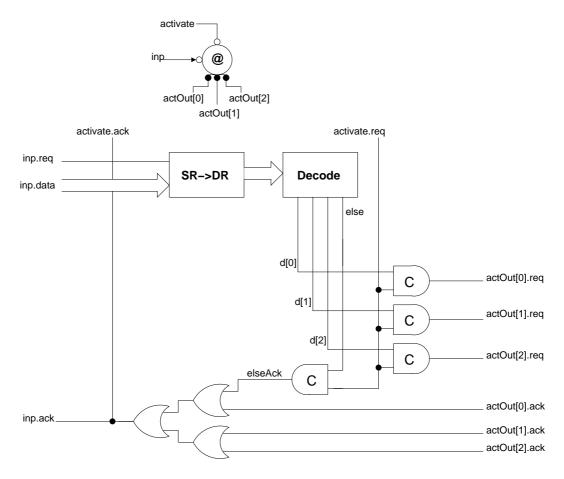

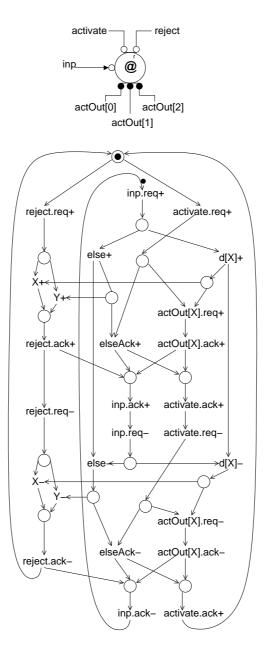

| 3.14 | Balsa conditional structure                        | 84 |

| 3.15 | Data-driven conditional structure                  | 84 |

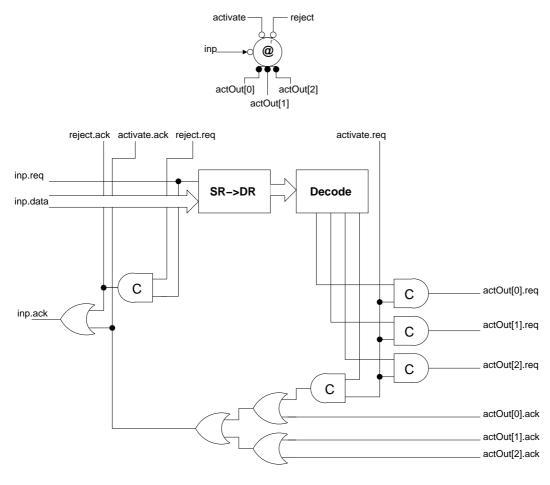

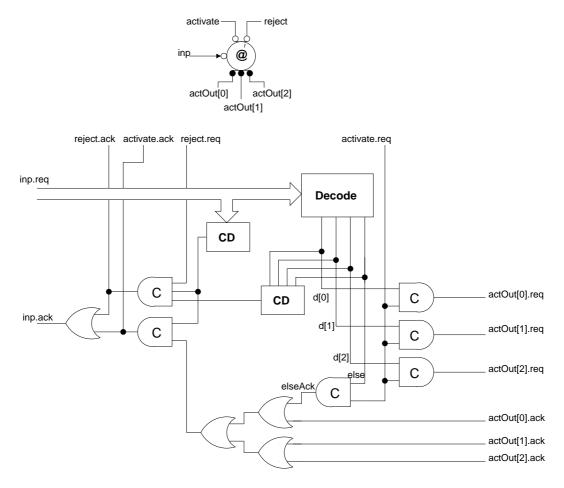

| 3.16 | Balsa conditional input structure                  | 88 |

| 3.17 | Data-driven conditional input structure            | 89 |

| 3.18 | Combining conditional and unconditional inputs     | 90 |

| 3.19 | Data-driven nested conditional structure           | 92 |

| 3.20 | Balsa arbitration structure                  | 93  |

|------|----------------------------------------------|-----|

| 3.21 | Data-driven arbitration structure            | 94  |

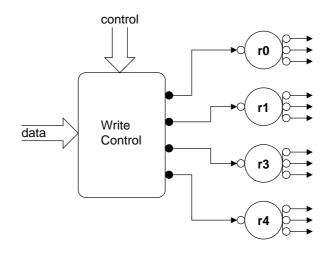

| 3.22 | Balsa single-write array variable structure  | 95  |

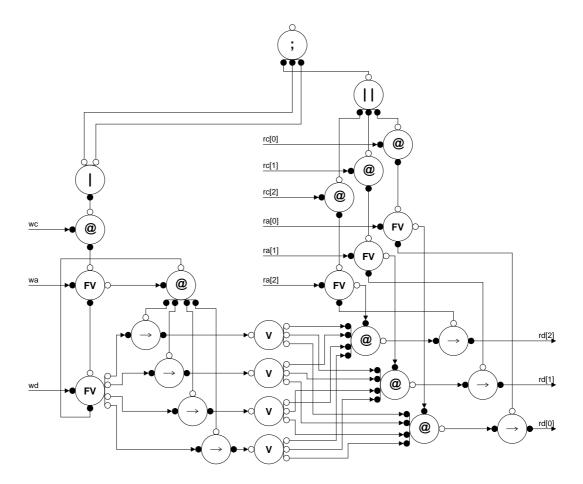

| 3.23 | Data-driven single variable array structure  | 96  |

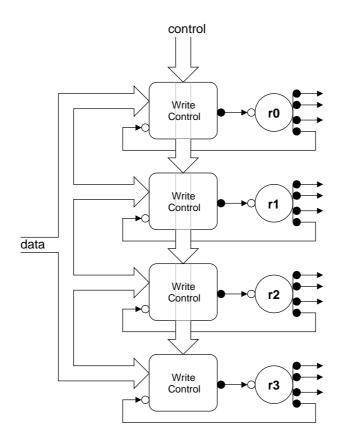

| 3.24 | Balsa general arrayed variable structure     | 98  |

| 3.25 | Sequenced sync structure                     | 100 |

| 3.26 | Data-driven one place buffer                 | 101 |

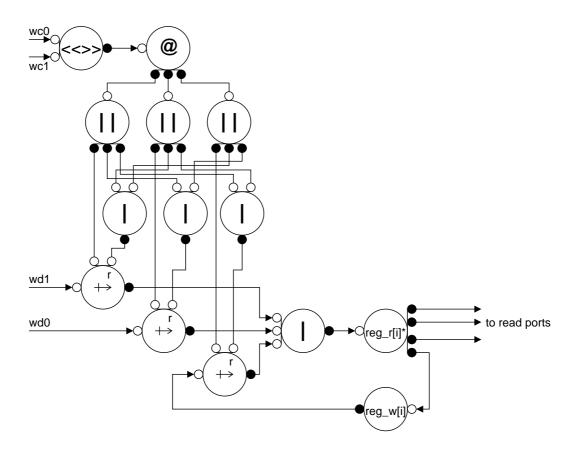

| 3.27 | Simplified register cell                     | 106 |

| 4.1  | Additions to Balsa design flow               | 116 |

| 4.2  | Unbalanced speculative operation (A)         | 119 |

| 4.3  | Speculative operation avoided (B)            | 122 |

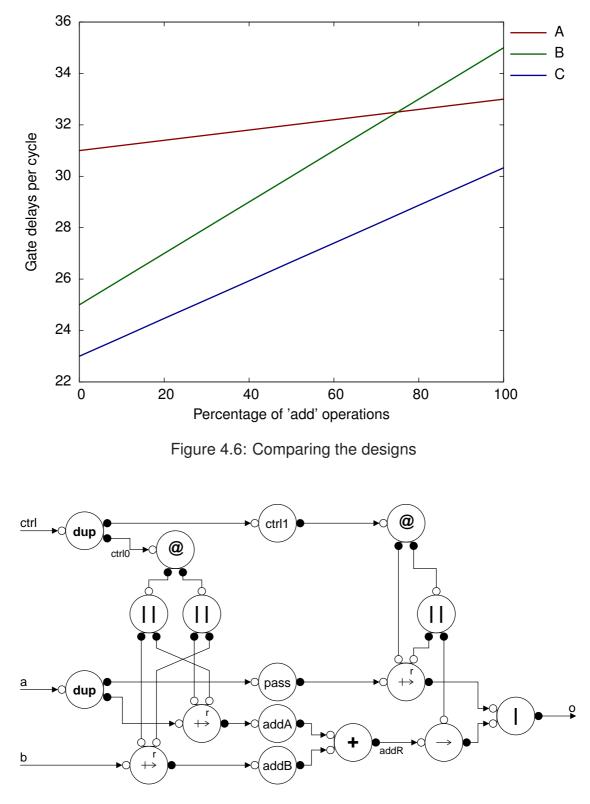

| 4.4  | Source-level optimisation example results    | 123 |

| 4.5  | Source-level optimisation example area       | 124 |

| 4.6  | Comparing the designs                        | 125 |

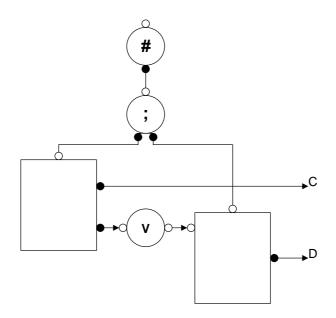

| 4.7  | Extra pipelining added (C)                   | 125 |

| 4.8  | Balsa process example                        | 128 |

| 4.9  | Data-driven process transformation           | 129 |

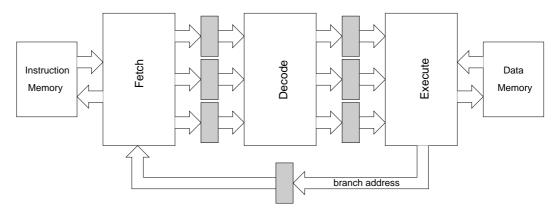

| 5.1  | nanoSpa Pipeline                             | 133 |

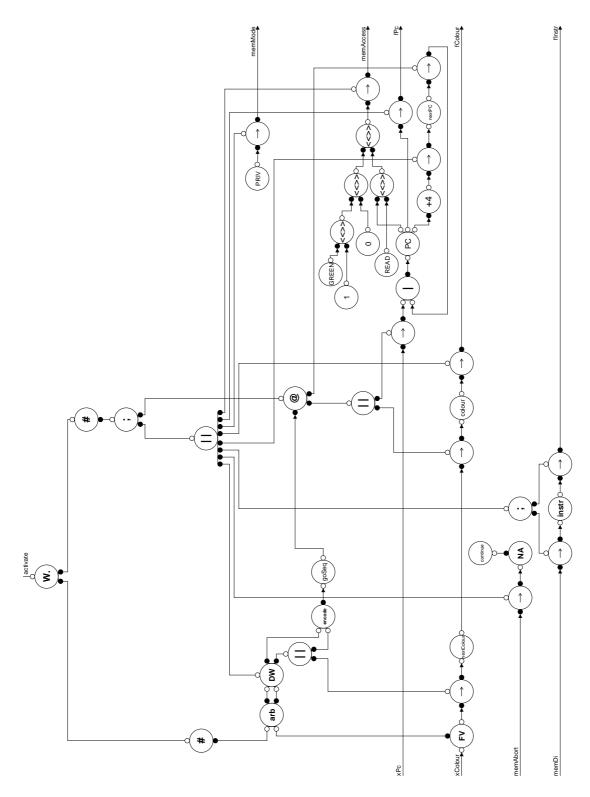

| 5.2  | nanoSpa fetch Balsa handshake circuit        | 136 |

| 5.3  | nanoSpa fetch data-driven handshake circuit  | 137 |

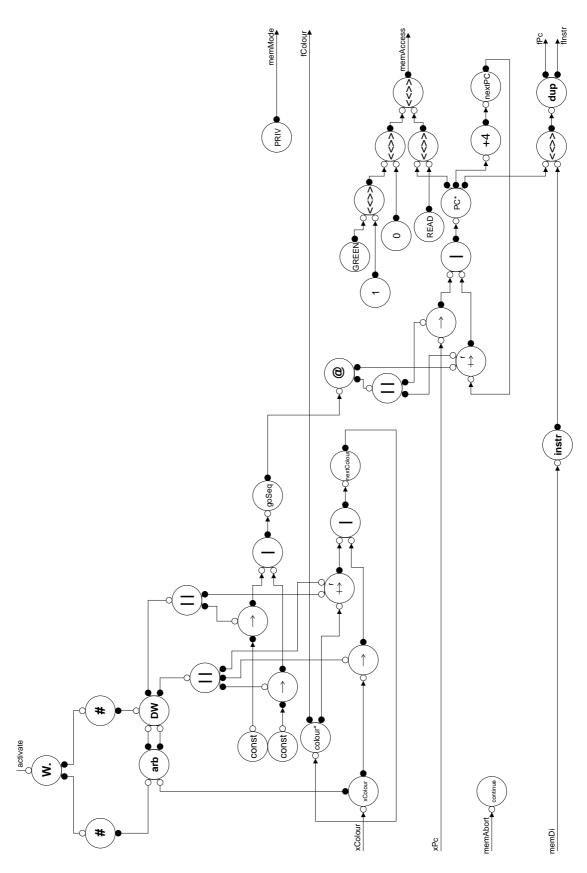

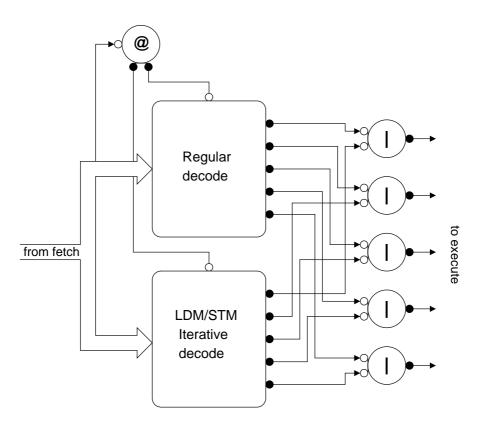

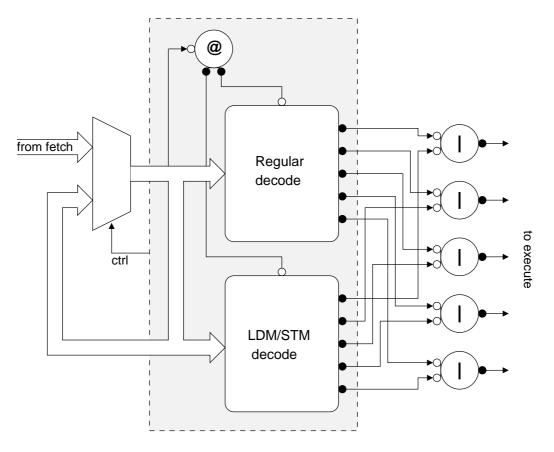

| 5.4  | nanoSpa decode structure                     | 140 |

| 5.5  | nanoSpa data-driven decode structure         | 141 |

| 5.6  | Balsa nanoSpa register write structure       | 142 |

| 5.7  | Simplified nanoSpa Balsa register bank       | 143 |

| 5.8  | Data-driven nanoSpa register write structure | 144 |

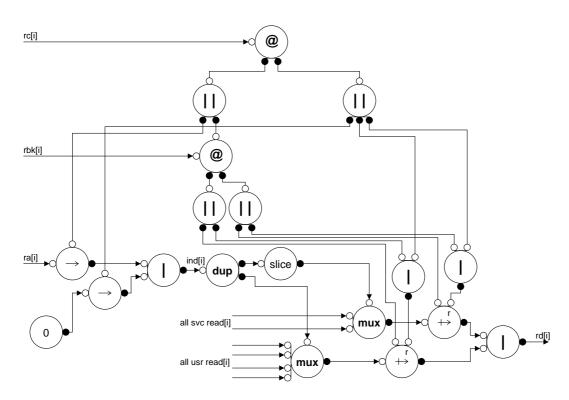

| 5.9  | Data-driven register 'cell'                  | 145 |

| 5.10 | Data-driven register read 'unit'             | 146 |

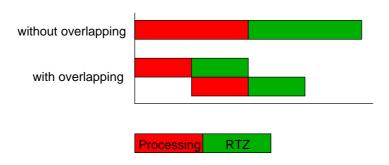

| 5.11 | Overlapping processing and RTZ               | 148 |

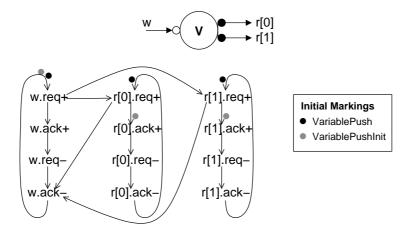

| B.1          | VariablePush STG                         | 170 |

|--------------|------------------------------------------|-----|

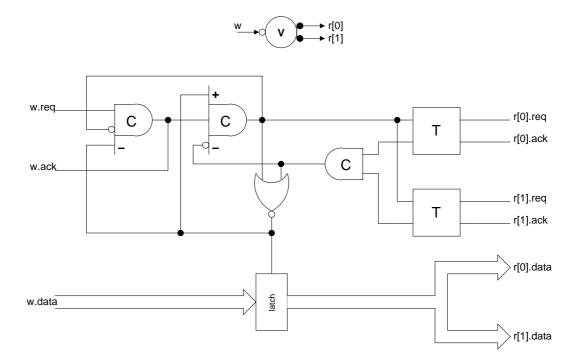

| B.2          | VariablePush bundled data circuit        | 171 |

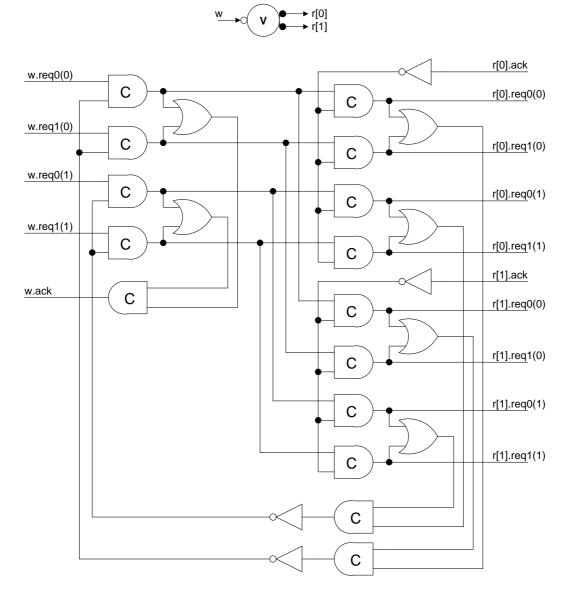

| B.3          | VariablePush dual-rail circuit           | 172 |

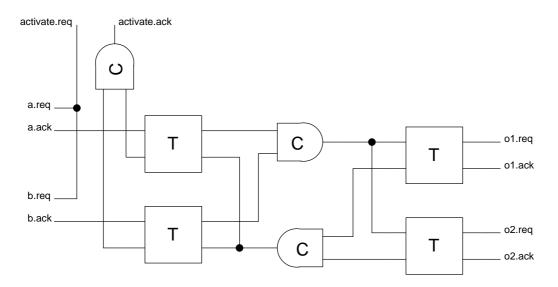

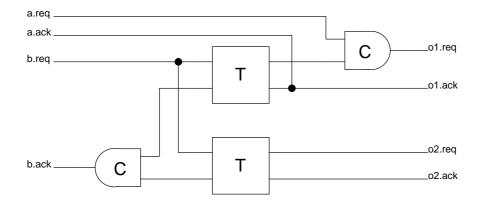

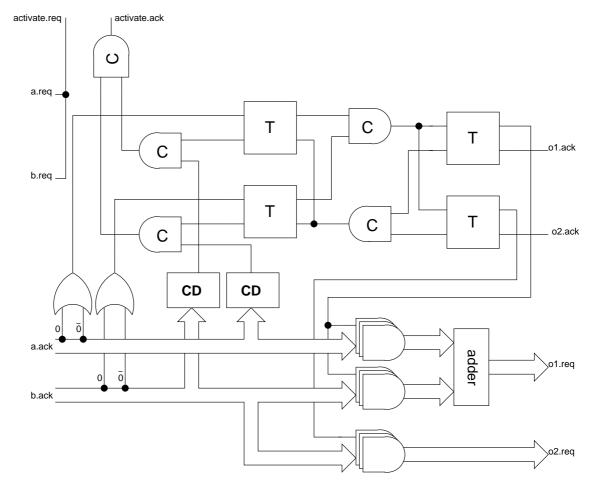

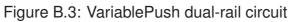

| B.4          | Dup STG                                  | 173 |

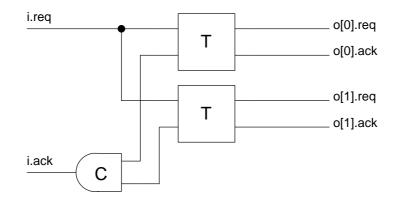

| B.5          | Dup bundled-data control circuit         | 174 |

| B.6          | Dup dual-rail circuit                    | 174 |

| B.7          | FVPush STG                               | 175 |

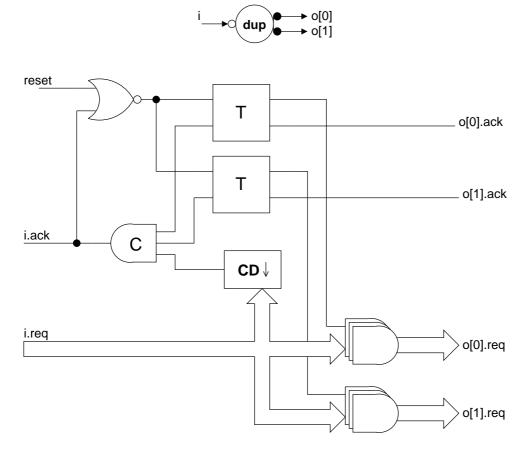

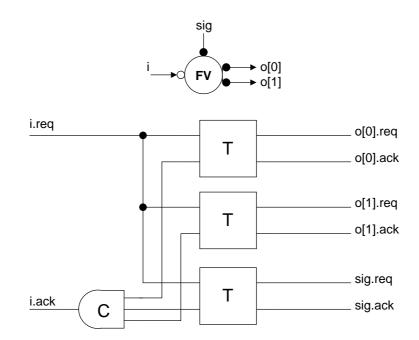

| B.8          | FVPush bundled-data control circuit      | 176 |

| B.9          | FVPush dual-rail circuit                 | 177 |

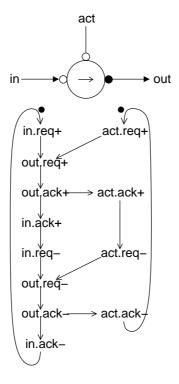

| B.10         | FetchPush STG                            | 178 |

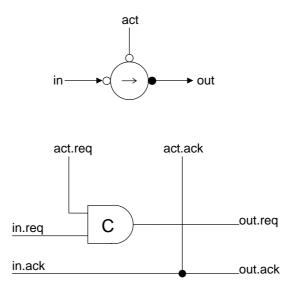

| <b>B.</b> 11 | FetchPush bundled-data control circuit   | 179 |

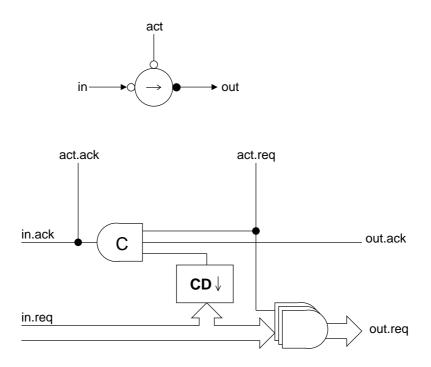

| B.12         | FetchPush dual-rail circuit              | 179 |

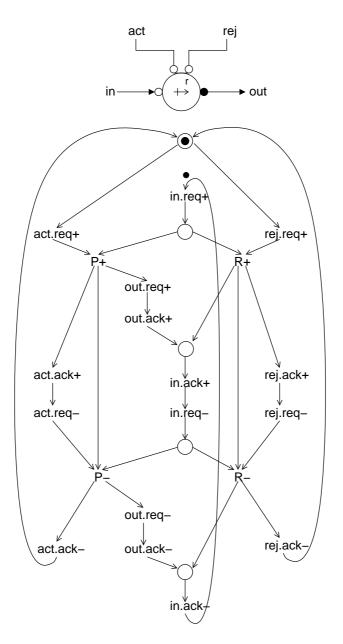

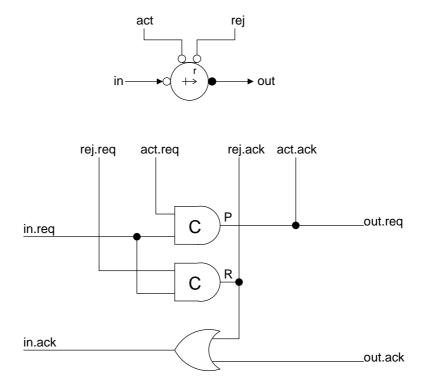

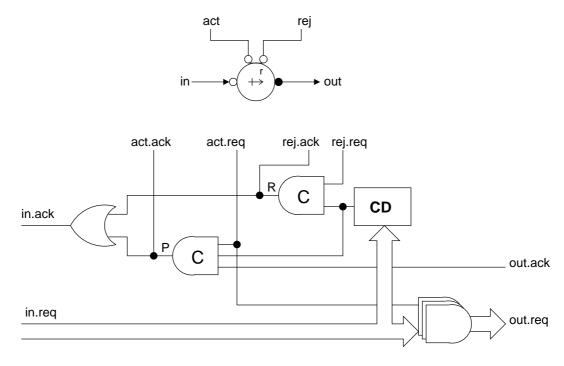

| B.13         | FetchReject STG                          | 180 |

| B.14         | FetchReject bundled-data control circuit | 181 |

| B.15         | FetchReject dual-rail circuit            | 181 |

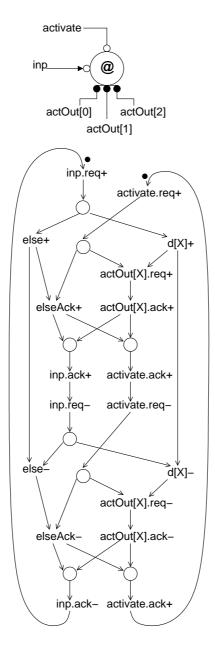

| B.16         | CasePush STG                             | 182 |

| B.17         | CasePush bundled-data circuit            | 183 |

| B.18         | CasePush dual-rail circuit               | 184 |

| B.19         | CasePushR STG                            | 185 |

| B.20         | CasePushR bundled-data circuit           | 186 |

| B.21         | CasePushR dual-rail circuit              | 187 |

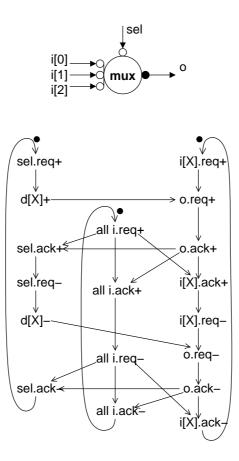

| B.22         | Mux STG                                  | 188 |

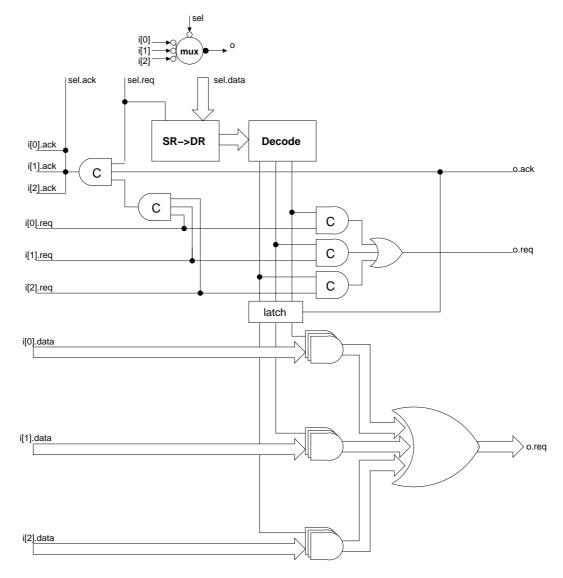

| B.23         | Mux bundled-data circuit                 | 189 |

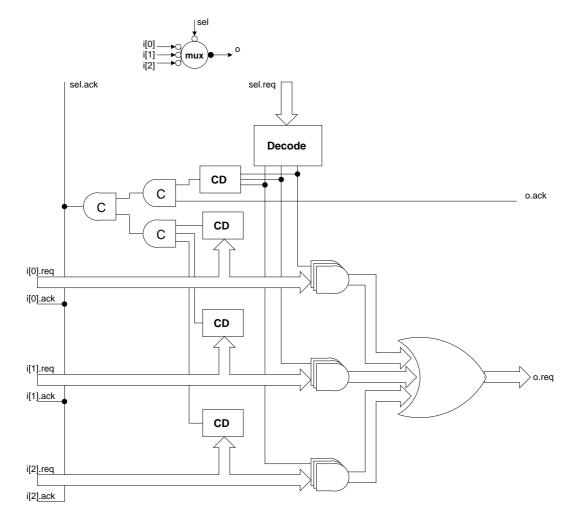

| B.24         | Mux dual-rail circuit                    | 190 |

## **List of Tables**

| 2.1 | C-element behaviour                       | 54  |

|-----|-------------------------------------------|-----|

| 2.2 | Asymmetric C-element behaviour            | 56  |

| 4.1 | Source-level optimisation example results | 124 |

| 5.1 | Dual-rail module results                  | 152 |

| 5.2 | Dual-rail nanoSpa area                    | 153 |

| 5.3 | Bundled data module results               | 154 |

| 5.4 | Bundled data nanoSpa area                 | 155 |

### Abstract

This thesis describes a novel method of synthesising asynchronous circuits based upon the Handshake Circuit paradigm used in the Balsa synthesis system but employing a data-driven style, rather than the control-driven style of conventional Balsa. This approach attempts to combine the performance advantages of data-driven asynchronous design styles with the handshake circuit style of construction for synthesising large circuits.

The integration into the existing Balsa design flow of a compiler for descriptions written in a new data-driven language is described along with the implementation of a number of new handshake components to support the new style.

The method is demonstrated using a significant design example — a 32 bit microprocessor. This example shows that the data-driven circuit style does indeed provide better performance than conventional control-driven Balsa circuits. Some qualitative discussion on the relative merits of the new description language when compared with conventional Balsa is also presented.

## **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institution of learning.

## Copyright

Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of the School of Computer Science.

## Acknowledgements

Any list such as this is inevitably incomplete and no doubt, before the ink is even dry, some names will occur to me that I shall regret failing to mention. Thanks to you all.

Thanks must go to my supervisor Doug Edwards and advisor Linda Brackenbury. Also to the members of the APT group, and particularly all those who have contributed to Balsa.

I must also express personal thanks to my friends Andrew Robinson, Ian Jason, Matt Horsnell and all the folks at Linton.

Finally, and despite the many shortcomings of his processor architecture, I must express my deepest gratitude to Luis Plana. Without his selfless assistance and support this thesis would never have been completed. Gracias mi amigo.

### **Chapter 1**

### Introduction

In recent years there has been increased interest in asynchronous or 'self-timed' techniques for digital circuit design [SF01, BJN99, BRD95]. In contrast to nearly all circuits currently designed, asynchronous circuits do not rely on the presence of a global clock. Many possible advantages are put forward for asynchronous techniques including the avoidance of problems related to clock distribution and clock skew [Fri01]. Additionally, increased modularity [SKC<sup>+</sup>99], increased robustness in the face of environmental and process variation [NS94, NSJ90, MBL<sup>+</sup>89], lower power consumption [GBvB<sup>+</sup>98, BBK<sup>+</sup>94], low electromagnetic noise [FGT<sup>+</sup>97, GBvB<sup>+</sup>98, PDF<sup>+</sup>98], improved security [MAC<sup>+</sup>02, PRB<sup>+</sup>03], and high performance [Bre06, MLM<sup>+</sup>97, WPS95, FGG98] are all claimed as possible advantages. There is perhaps more evidence to support some of these claims than others. It is not intended that this thesis should argue specifically for the advantages, or any particular advantage of asynchronous techniques over their synchronous counterpart.

The vast majority of synchronous circuits are synthesised partly or entirely using computer-aided design (CAD) tools. It is clear that if asynchronous techniques are to gain more widespread acceptance, then robust and efficient synthesis tools are a necessity. Balsa is one such tool, designed for high-level synthesis of asynchronous circuits from algorithmic language descriptions. Balsa has demonstrated that it is robust and flexible, and can be used for the rapid development of large designs. However, this speed and flexibility is achieved at the cost of performance in the resulting circuits. Competitive performance must be demonstrated before any other potential advantages of asynchronous techniques will be seriously considered by the synchronous design community.

This aim of this thesis is to contribute to knowledge in the field of synthesising large asynchronous circuits with the specific objective of improving performance. Area and power are not considered relevant factors though, on occasion, some small consideration is made where it was possible with minimal additional effort.

### 1.1 Asynchronous synthesis methods

Existing asynchronous synthesis methods may be broadly grouped into four categories. The first of these groups is restricted to the synthesis of small-scale asynchronous control circuits. Most of these methods use either Petri nets [CKK<sup>+</sup>97] or burst-mode machines [FNT<sup>+</sup>99] as specifications for asynchronous control circuits. This work in this thesis is aimed at the synthesis of large circuits inclusive of both control and datapath. Therefore, these controller synthesis methods are of limited interest although Petri nets are appropriated as a convenient method of specifying handshake component behaviour (see section 2.2).

The methods that target synthesis of large-scale circuits are described in the following three sections.

#### 1.1.1 De-synchronisation based methods

This method involves converting conventional synchronous design descriptions into asynchronous designs [CKLS06, KL02]. Typically existing CAD tools are used for much of the datapath synthesis and asynchronous control synthesis tools are used to produce controllers that replace the global clock. This approach has the advantage that designers need little specialist knowledge of asynchronous techniques. A drawback is that by using a design targeted at a synchronous implementation, potential advantages of asynchronous techniques are not exploited. For example, concurrency is restricted to the synchronous pipeline structure and so the fine-grained concurrency possible in asynchronous design is not exploited. It is also difficult to exploit the possibility for asynchronous designs to use data-dependent delays instead of the worst-case delays of synchronous design.

#### 1.1.2 CHP based methods

The CSP[Hoa85]–based Communicating Hardware Processes (CHP) language is the basis of some asynchronous synthesis systems [Mar90, RVR99, TAS]. These systems use manual or automatic program transformations to refine a design into a more concurrent version. The final program is then translated into a production-rule set which is used to generate a transistor implementation of the design.

The Caltech synthesis tools (CAST) have been used to produce some high performance circuits [MLM<sup>+</sup>97] but these rely on significant manual intervention in the synthesis flow to arrive at the most effective program transformations and also rely on the use of the PCHB (precharge half-buffer) circuit style. This circuit style is not widely used and requires a specialised cell library.

The automatic program transformations employed in CAST are not behaviour preserving and are only correct for designs that meet particular requirements. An inexperienced designer may struggle to understand and meet these requirements.

#### 1.1.3 Macromodular based methods

The term macromodular originates from the Macromodules system developed at Washington University [Cla67]. This was a system of large rack-mounted modules that were physically connected by hand. Current macromodular systems are somewhat smaller but share the basic concept of composing small pre-designed modules to produce large systems. Two prominent asynchronous synthesis tools use the handshake circuit paradigm first proposed by Van Berkel [Ber93] as the intermediate representation for the asynchronous circuits compiled from the language Tangram<sup>1</sup>. The Balsa synthesis system is heavily based on Tangram and uses the same paradigm. Balsa offers a few different features to Tangram but largely differs only in small details. The work in this thesis is based on Balsa and so the remainder of this section will describe the synthesis method of Balsa in some detail although the description is equally valid for Tangram.

Balsa is a framework for high-level synthesis of asynchronous circuits. Balsa is also the name given to the main language in which circuit descriptions are written. These descriptions are compiled into networks of communicating handshake components called handshake circuits. Handshake circuits are an attractive paradigm as they offer a level of abstraction above any particular implementation style or technology. Handshake circuits exploit the modularity of asynchronous techniques in the synthesis of large-scale systems. Each handshake component is straightforward to construct in isolation. By composing the components, very large systems may be robustly constructed. The translation employed by Balsa from language description to handshake circuit is described as syntax-directed. This means the structure of the resulting circuit is based on the syntax of the source code. This provides the advantage that the resulting circuit may be optimised for power, area or performance at the

<sup>&</sup>lt;sup>1</sup>latterly renamed as Haste

language level. The translation is also described as control-driven. The handshake circuit network features a control tree which mirrors the control flow of the language description. The overhead of this control-driven approach is a major factor in restricting the performance of this style of handshake circuit.

The work in this thesis is based upon the handshake circuit method of construction and the syntax-directed method of translation. In place of the controldriven approach, a novel style of handshake circuit is proposed, based much more on data-flow rather than control-flow. This approach is described as *datadriven*.

### 1.2 Aims of this research

The aim of this research is to improve the performance of large synthesised asynchronous circuits. The focus of the approach is on a handshake circuit representation of the circuit; that is to say, an abstract representation of the structure of the circuit which is independent of technologies, protocols, dataencodings or any other details of the actual circuit implementation. The problem of control overhead in the conventional control-driven style of handshake circuit synthesis is identified as a major obstacle to performance. Data-driven asynchronous design styles are much less prone to the problem of control overhead and so the approach of this research is to combine the benefits of a data-driven style with the convenience and flexibility of the handshake circuit paradigm which allows the robust synthesis of large circuits. To this end, the handshake circuit structures of the control-driven Balsa synthesis method have been examined and data-driven alternatives are proposed. To generate these structures, a data-driven description style is proposed and a compiler has been developed to compile these description into a handshake circuit representation. This compiler is integrated into the Balsa design flow enabling the use of existing Balsa tools for moving from the handshake circuit representation to a gate-level circuit.

The benefits of the new style are successfully demonstrated by the manual translation of an existing high performance Balsa design of significant size and complexity directly into the data-driven style.

### **1.3 Contributions of this thesis**

The contributions made by this thesis can be summarised as follows:

- A novel synthesis method for asynchronous circuits combining the performance benefits of data-driven design styles with the handshake circuit paradigm for constructing large circuits.

- A hardware description language that is specifically tailored for syntaxdirected translation into the data-driven circuit style.

- Demonstration of the use of the synthesis method in a significant design example (a microprocessor).

- Analysis of the performance improvements gained by using the datadriven method over conventional control-driven handshake circuit synthesis.

### 1.4 Thesis structure

The remainder of this thesis is divided into five chapters as follows:

Chapter 2 gives background information on asynchronous design fundamentals and on the existing Balsa synthesis system. Chapter 3 presents the main work of this thesis: a data-driven handshake circuit style and language from which this circuit style is compiled. This is preceded by a discussion of the control overhead of conventional Balsa circuits and the manner in which the data-driven style is less acutely affected by this problem.

Chapter 4 contains a range of information and ideas on the implementation and usage of the data-driven style. Some ideas for future work are briefly discussed.

Chapter 5 describes the implementation of a data-driven implementation of the nanoSpa processor. This implementation is compared with the controldriven original in an effort to evaluate the strengths and weaknesses of the proposed data-driven approach.

Chapter 6 summarises the work presented herein and offers suggestions for future work.

A number of appendices offer supplementary information of a more detailed nature:

Appendix A gives the grammar of the data-driven language.

Appendix B gives the implementations of new handshake components introduced to the Balsa component set to support the data-driven style.

Appendix C gives code for selected modules of the data-driven nanoSpa description.

Finally, appendix D gives very brief descriptions of the handshake components in the Balsa component set. These descriptions are intended to act as a reminder of the component behaviours.

### 1.5 Publications

The author has contributed to the following papers while conducting the work described in this thesis.

- Luis Plana, Doug Edwards, Sam Taylor, Luis Tarazona and Andrew Bardsley. Performance-driven syntax-directed synthesis of asynchronous processors. In *Proc. International Conference on Compilers, Architecture, and Synthesis for Embedded Systems, (CASES),* September 2007.

- Luis A. Plana, Sam Taylor, and Doug Edwards. Attacking control overhead to improve synthesised asynchronous circuit performance. In *Proc. International Conf. Computer Design (ICCD)*, pages 703-710. IEEE Computer Society Press, October 2005

- Sam Taylor and Doug Edwards. Control localisation as a means of improving handshake circuit performance. In *Seventeenth UK Asynchronous Forum*, pages 1-4.

## **Chapter 2**

## Background

This chapter contains the background information upon which the work described later in the thesis is based. The principles of asynchronous handshaking are briefly described followed by more specific background on the Handshake Circuit paradigm and the Balsa synthesis system.

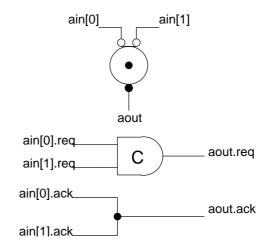

### 2.1 Handshaking

The basis of nearly all asynchronous design techniques is the concept of handshaking to provide synchronisation between communicating modules. This synchronisation is frequently used to facilitate the transfer of data between the modules. Multifarious technologies and protocols exist for the implementation of these handshakes but conceptually all rely on the exchange of a request and acknowledge signal between communicating modules. One module initiates a handshake by sending a request (req) signal and the other, when ready, responds with an acknowledge (ack). For systems that wish to abstract away the detail of the implementation of the handshake it is common to combine the control for signalling the req and ack, together with any accompanying means of transferring data, in a single conceptual unit known as a *channel*. The channel therefore forms a point-to-point link between the two modules that it

Figure 2.1: Push data channel

Figure 2.2: Pull data channel

connects, either for the purpose of making data transfers, or simply to allow the modules to synchronise.

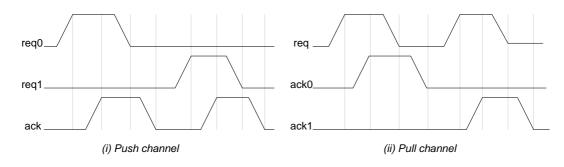

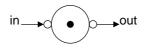

Data channels can be divided into two types: where the data moves in the same direction as the request and where the data moves in the same direction as the acknowledge (see figures 2.1 and 2.2). These two possibilities are named *push* and *pull* respectively.

#### 2.1.1 Handshake protocols

Much of this thesis is concerned with the handshake circuit structures of Balsa and of the new data-driven style. The handshake circuit paradigm provides a level of abstraction that is neutral as to which technologies and handshake protocols may be used to implement the final circuit. However, in order to implement the handshake components and produce real circuits, issues of protocol must be addressed.

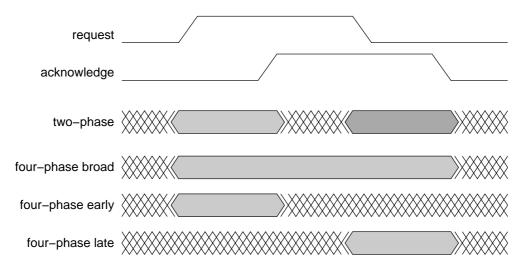

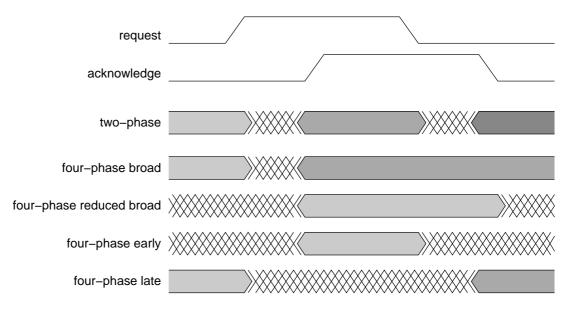

The two most widely used handshaking protocols are known as two-phase

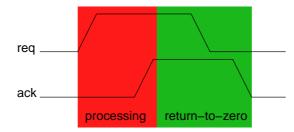

Figure 2.3: Four-phase handshake protocol

or transition signalling and *four-phase* or level-sensitive. A two-phase protocol is conceptually more straightforward in that each handshake consists of a single request event and single acknowledge event. For example, two wires may be used, one for the request and one for the acknowledge. A transition on the request wire indicates a request and a transition on the acknowledge wire indicates an acknowledge. A two-phase scheme is perhaps most notably employed in the Micropipelines style [Sut89]. Unfortunately, it is often difficult to implement efficient circuits using a two-phase protocol due to the complexity of detecting transitions on wires compared with detecting levels. This is particularly true when using a multiple-wire encoding scheme (see the next section) although it has been applied in some applications [FES00].

Four-phase handshaking uses the level of wires to indicate signals so, for example, a high request wire indicates a request and a high acknowledge wire indicates an acknowledge. Each handshake must then return the request and acknowledge to their original state before the next handshake may begin. The four-phase protocol can therefore be considered as having two sub-phases: the *processing* phase and the *return-to-zero* (RTZ) phase (see figure 2.3).

#### 2.1.2 Data encoding

Two broad categories of design style are commonly employed in asynchronous design. These are known as *bundled-data* and *delay-insensitive*. Bundled-data designs nearly always employ traditional single-rail data encoding where one

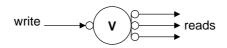

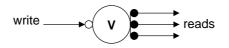

Figure 2.4: Push data validity protocols

wire represents each bit. Most commonly, additional request and acknowledge wires are bundled with the data although techniques exist that use a single wire for both request and acknowledge [BB96]. When using bundled data it is necessary to define a data validity protocol that determines where in the handshake the data is valid. For two-phase there is little option as to the data validity protocol, as there are only two events. For four-phase there are several options for the period that data must be valid. Figures 2.4 and 2.5 show the common data-validity protocols for push and pull channels respectively. The standard bundled-data Balsa back-end uses the four-phase broad protocol for push channels. For pull channels the broad protocol is less convenient as the data validity must be maintained until the request goes up in the following handshake. For this reason, the reduced broad protocol is used for pull channels. In theory, there is little to distinguish the reduced broad and early protocols as once the receiver has lowered its request then the acknowledge could be lowered and data changed immediately. In practice, the ack and data will not change immediately and so it is possible to assume a small extra period of validity will exist after the request is lowered and exploit this in component implementations.

Figure 2.5: Pull data validity protocols

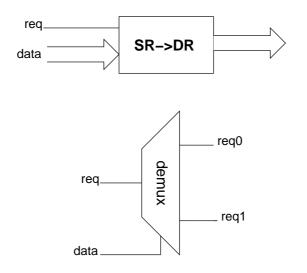

Delay-insensitive systems use multiple wire data encodings; most prevalent of these is the dual-rail encoding where two wires are used to encode each bit. A delay-insensitive encoding allows the data to signal when it is valid and the data itself signals either the request (for push channels) or acknowledge (for pull channels). One additional wire is used for the signal that is not encoded with the data. See figure 2.6 for an example of the handshakes for one-bit dualrail push and pull channels using a four-phase RTZ protocol. One of the two wires carrying the data is used in each handshake. One wire indicates a zero is being sent (req0 or ack0) and the other indicates a one is being sent (req1 or ack1). It is uncommon to use an extra wire to request or acknowledge every bit in a data channel carrying multiple bits. Instead a single extra wire is used for the channel and it is then necessary to use *completion detection* to check that all the bits have arrived and have gone away before transitioning the request or acknowledge signal.

Figure 2.6: Four-phase dual-rail handshakes

### 2.2 Signal Transition Graphs

Signal Transition Graphs (STGs) are a specific form of Petri net — a well established formalism for modelling concurrent systems. STGs are used as an input format to some asynchronous synthesis systems such as Petrify [CKK<sup>+</sup>97]. These methods rely on state-space exploration and so are only suitable for the synthesis of small controllers as for large designs the state-space quickly explodes to an unmanageable size. In this thesis STGs will be employed as a convenient method of specifying the behaviour of handshake components.

A Petri net is made up of places and transitions connected by directed arcs. Transitions indicate events in the system; in the case of circuit design these are signal transitions. Places can hold a number of tokens. Each transition may have a number of inputs and outputs which are the places that are connected to and from the transition. The operation of the Petri net proceeds by firing transitions. Transitions are enabled when all of their inputs have at least one token. When a transition fires a token is removed from each of its inputs and a token added to each of its outputs. This may then enable further transitions. The number of tokens at each place in the system at any given time is called the *marking*.

An STG is a Petri net with two specific restrictions. An STG must be onebounded which means that at all times only one token is allowed at each

Figure 2.7: Call STG

place. Only inputs may be used as transitions where choice is involved and the signal transitions represented by such inputs must be mutually exclusive. Where choice occurs, a single place has multiple transitions that could fire and consume a token. The signal transitions in the implementation must provide means of deciding which transition should fire.

Figure 2.7 shows the STG for the Balsa Call component in order to demonstrate the graphical representation of an STG. Places are drawn as circles but are usually omitted between transitions that are directly connected through a single place. A line connecting two transitions directly therefore has an implicit place in the middle. The initial marking of the circuit is shown using a filled circle either drawn within a place or next to an arc that has an implicit place. Note particularly the representation of choice between the input requests. Either req+ transition may consume the same token. As the input requests to the component are input signals and are mutually exclusive, it is possible to choose the correct transition.

The figure also shows the convention that will be used in STGs and circuit diagrams throughout this thesis for showing the expansion of channels into their constituent parts. For example, the channel **out** is expanded to out.req and out.ack. The upward transition on out.req is represented by out.req+ and the downward transition by out.req-.

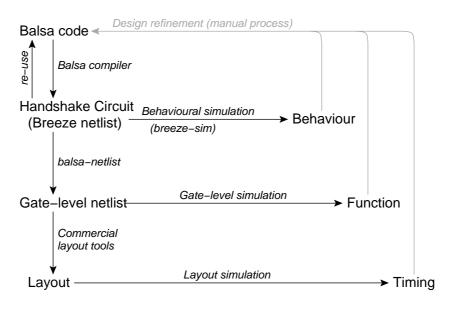

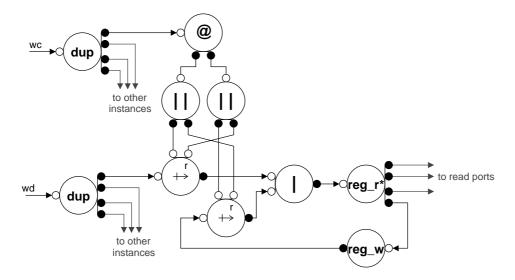

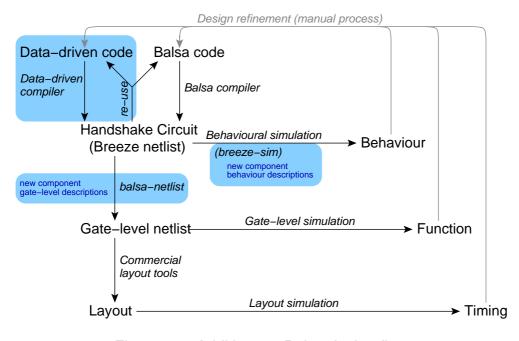

## 2.3 Balsa design flow

An overview of the Balsa design flow is shown in figure 2.8. There are two synthesis stages in this flow that are handled by tools in the Balsa framework. The first is the compilation from a Balsa code description into the handshake circuit representation using the Balsa compiler. This is frequently called the *front-end*. The breeze format is in essence simply a list of channels and handshake components. The compilation is modular and each procedure in the

Figure 2.8: Balsa design flow

language is compiled into a breeze 'part'. The compiler will import breeze descriptions when a procedure from another file is instantiated in order to ensure the interface is correctly generated.

The second stage (or *back-end*) is the replacement of each handshake component with a gate-level implementation in the chosen design style and technology performed by the balsa-netlist tool. The back-end produces a gate-level netlist which can be processed by commercial place and route tools for layout to silicon or possibly to an FPGA.

This thesis is mainly concerned with the first synthesis stage — from language description into handshake circuit. The conventional Balsa compilation process is described in some detail in the following section. This thesis describes a new compilation approach that complements the existing Balsa compiler in this design flow. The additions to the flow will be discussed in section 4.1 on page 115.

To implement the new data-driven style, many existing handshake component implementations are re-used, but in addition several new components are added to the Balsa handshake component set. Section 2.6 gives some background on common techniques that have been employed in implementing these components. The next two sections give more detail on the handshake circuit paradigm and the front-end compilation of Balsa source descriptions into handshake circuits.

# 2.4 Handshake Circuits and Balsa

The handshake circuit is a network of small components connected by channels. The network is generated by a compiler (frequently called the front-end) that translates a high-level language description into a handshake component network. The compilation involves converting each language feature into a small structure of handshake components which implements that feature and composing these smaller structures based on the syntax of the written description. This approach is often described as 'syntax-directed' or 'transparent' compilation as there is a fixed relationship between language descriptions and the circuit that they generate. Small changes in the description will produce small and predictable changes in the resulting circuit. Furthermore the direct compilation allows the construction of large-scale designs and is one of only a few proven methods for doing so in an asynchronous style.

#### 2.4.1 Handshake circuit diagrams

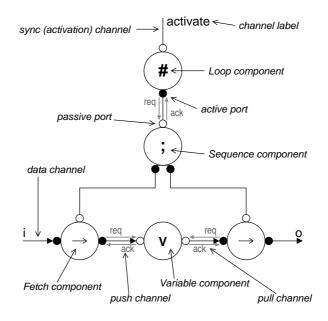

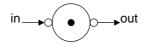

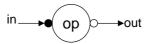

Figure 2.9 illustrates the diagrammatic representation of a small handshake circuit. Handshake components are usually rendered as a circle containing a symbol that indicates the type of component. Each component has one or more ports to which channels are connected. The *sense* of the port indicates whether it initiates communication (sends the request) or responds to communication (sends the acknowledge). The active port, drawn as a small filled circle, sends

Figure 2.9: Handshake circuit diagram

the request and the passive port, drawn as a small open circle sends the acknowledge. (Example requests and acknowledges are shown in the figure but are not usually shown.) A channel always connects an active port from one component to a passive port from another. Channels are represented by lines; arrows are added to the lines to indicate data channels where the direction of the arrow indicates the direction in which the data flows. Data channels can be further divided into two types: push channels where data flows in the same direction as the request and pull channels where data flows in the direction of the acknowledge.

Channels without data are called *sync* channels, or often *activation* channels, as they are in the most part used for the purposes of activating components in the circuit.

# 2.5 Balsa language and compilation

The Balsa language is fully described in the Balsa Manual[EBJ<sup>+</sup>06]. A brief overview will be presented here with much detailed information that is not directly relevant to this thesis being omitted. Accompanying the language descriptions are examples of the handshake circuit structures produced when the language constructs are compiled. Copious information on the compilation and handshake components employed therein may be found in [BE97, Bar00, PTE05].

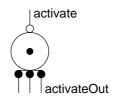

Balsa descriptions are divided into procedures. Each procedure has an implicit activation port that activates the circuit described within the procedure. In addition, each procedure may have any number of input, output, or sync (non data carrying) ports. These ports are the external interface to the procedure. From within the procedure, ports are used as if they were channels but they are read-only for input ports and write-only for output ports. In addition to ports, procedures provide scope for local channel and variable declarations. Channels in this context are a language feature and do not normally correspond to an individual channel in the handshake circuit.

The body of a procedure consists of commands, composed using control structures. Each command or structure is compiled into a small network of handshake components with an activation channel that is used to control when the command operates. The compilation connects the small network to the overall handshake circuit network by attaching the activation, and any input and output channels to the appropriate points in the overall handshake circuit.

#### 2.5.1 Data types

Balsa supports global and local type and constant declarations. Basic numeric types in Balsa can all be considered as bit vectors of a given width and can be signed or unsigned. Array, enumeration and record types are supported.

Figure 2.10: Balsa channel read (and write into a variable)

Figure 2.11: Balsa channel write (from a variable)

Ports, channels and variables are all declared as having a specific type.

Details of data types will in general be omitted from examples in this thesis as the primary interest is in the structures of the handshake circuits. The width of data involved is rarely significant to the structures, which are applied in the same fashion to data of any given width.

### 2.5.2 Basic commands

There are four basic commands in Balsa: channel reads, channel writes, continue and halt.

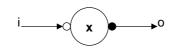

A channel read is used to write the data from a channel into a variable. It is written using the -> operator, e.g. chan -> var. It is compiled to a *Fetch* component as shown in figure 2.10. A channel read may also be used to write the data to another channel in place of the variable (e.g. chan1 -> chan2).

A channel write is used to read data from a variable and output it to a channel. It is written using the <- operator, e.g. chan <- var. It is also compiled to a Fetch component as shown in figure 2.11.

The continue command is used to perform no operation and is compiled to

Figure 2.12: Balsa assignment

a component that simply acknowledges any activation request it receives. The halt command never acknowledges an activation so that the circuit deadlocks at the point where the halt occurs. (Other independent parts of the circuit may continue operating so the entire circuit may not deadlock.)

The assignment command (:=) is also available in Balsa. It is in reality a compound command made up of a channel write and a channel read but the channel is implicit. For example, the following two code fragments are equivalent:

```

variable a, b

-- this assignment is implicitly...

a := b

-- the same as this...

channel c

c <- a || c -> b

```

The handshake circuit generated for both fragments is the same and, due to a small optimisation, does not use two Fetch components but only a single Fetch component as shown in figure 2.12.

## 2.5.3 Parallel and Sequence control

The basic commands may be composed using the concur (||) and sequence (;) operators to form compound commands. A single-place buffer may be described by composing a channel read and write in sequence as shown below.

```

procedure buf (input i : byte; output o : byte) is

variable V : byte

begin

loop

i -> V;

o <- V

end

end</pre>

```

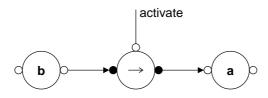

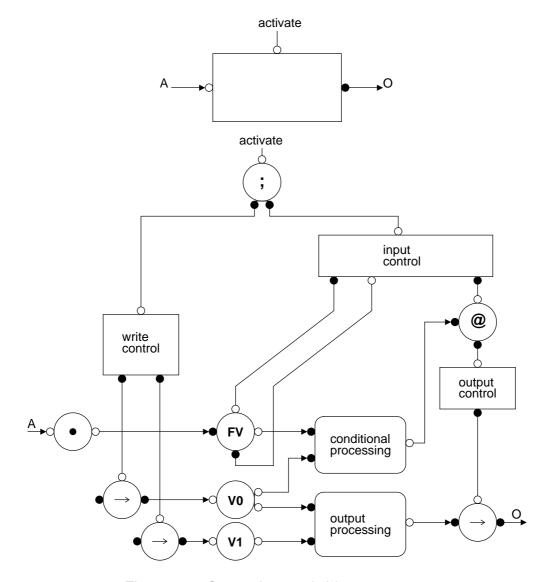

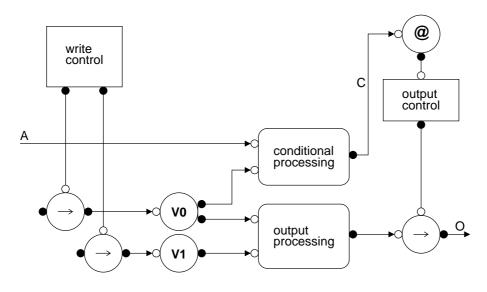

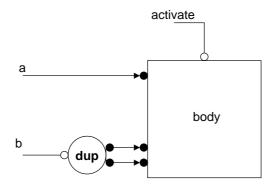

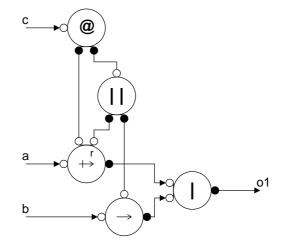

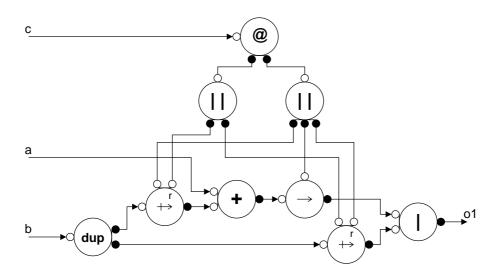

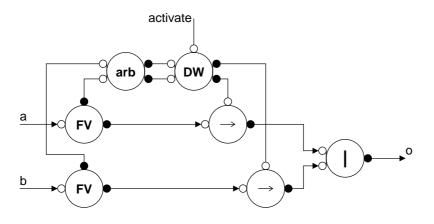

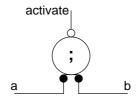

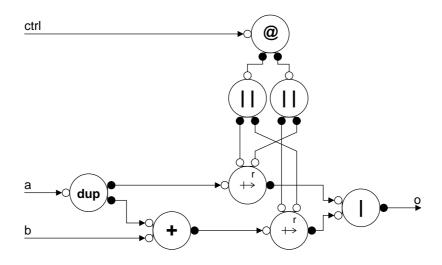

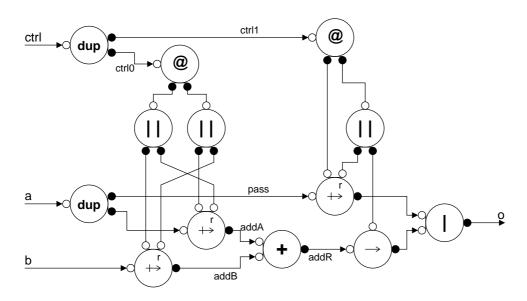

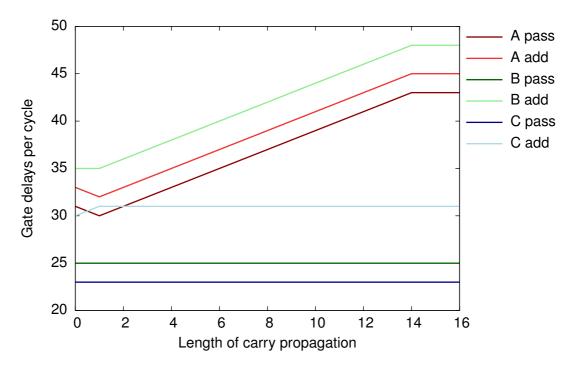

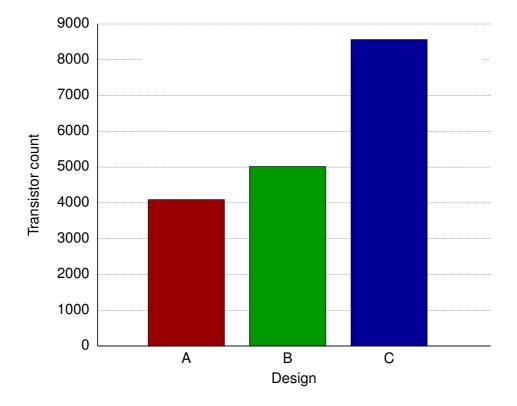

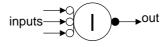

Figure 2.9 shows the handshake circuit for this example. The *Sequence* component sequentially activates its active ports so the channel read is activated first and upon its completion the channel write is activated.

The parallel operator is similar but produces a *Concur* component in place of the Sequence. This component activates its active ports in parallel and waits for them to complete before acknowledging on its passive port.

## 2.5.4 Conditional control

Conditional control is provided by the case and if structures. If is fundamentally the same as case so this discussion will use case as an example. The case construct is written as follows:

The guards may consist of a comma-separated list and must be resolvable at compile time. They must also be disjoint in that no value may be matched by more than one guard. The else clause is used to match any values not covered by the guards and is optional in Balsa even if the guards do not exhaust all

Figure 2.13: Balsa case example

possible values of the expression. If the else is omitted then the behaviour is the same as if the body of else were a continue command.

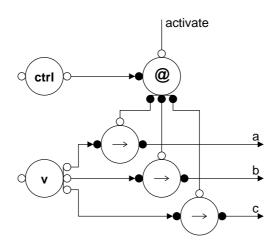

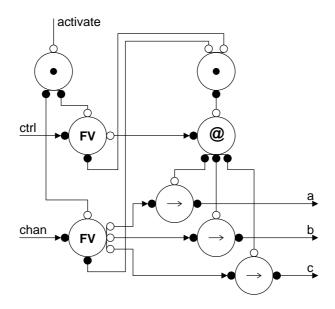

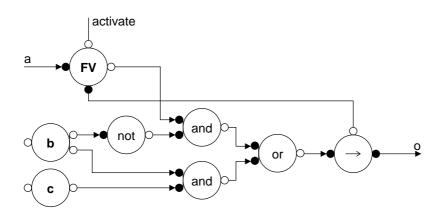

The case command is compiled to the *Case* component. The Case component has a passive activation port which when activated initiates the evaluation of the expression. The result of the expression is used to determine which of the output activation ports will be activated. For example the following code uses a case structure to select which of three channels (a, b, c) the data from variable v should be written to. This is compiled into the handshake circuit shown in figure 2.13.

```

case ctrl of

0 then

a <- v

| 1 then

b <- v

| 2 then

c <- v

end

```

Figure 2.14: Balsa While component

## 2.5.5 Iterative control

Balsa has two iterative structures, loop and while. Loop is very straightforward as it simply repeats the command given in its body indefinitely. It is compiled to the *Loop* (#) component as shown in figure 2.9. This component, upon receiving an activation, repeatedly handshakes on its output activation port and never acknowledges the input.

The second structure, while, provides finite iteration as found in most imperative programming languages. It is written as follows:

```

loop while <expression> then

<command>

end

```

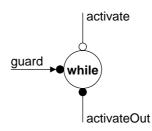

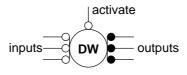

The result of the expression must be a single bit. This while loop is compiled using the *While* component (figure 2.14). Upon activation the component pulls on its guard port to get the result of evaluating the expression. If the result is 1 then the output activation is sent to activate the body of the loop and when this is completed another guard is fetched. When the result of the guard is 0 then the while loop terminates and acknowledges its activation.

## 2.5.6 Input enclosure

Input enclosure allows the handshake on one or more input channels to be held open while a command is activated. This allows the value on the channel(s) to

Figure 2.15: Balsa input enclosure example

be read as many times as desired by the enclosed command. The input channel(s) will only be released when the command has completed. For example the case construct shown in the conditional control section above may be used with channels instead of variables by using input enclosure as follows:

```

chan, ctrl -> then

case ctrl of

0 then

a <- chan

| 1 then

b <- chan

| 2 then

c <- chan

end

end

```

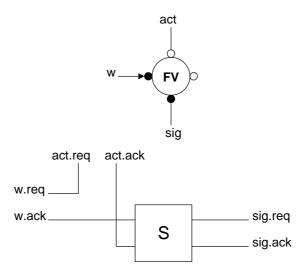

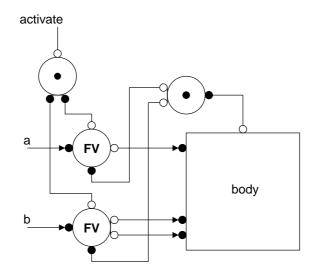

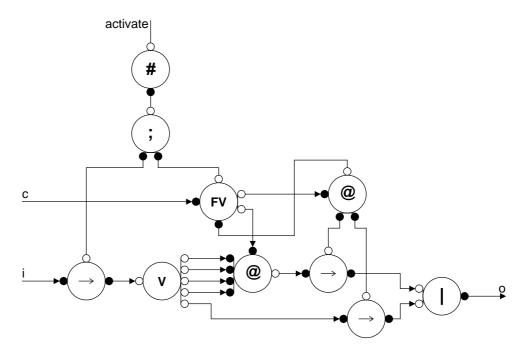

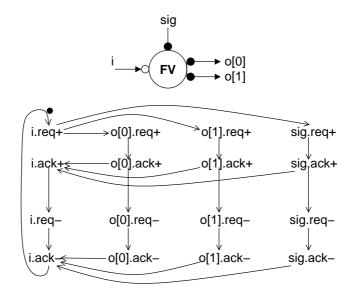

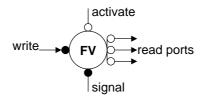

Figure 2.15 shows the handshake circuit produced by this code. The *False-Variable* (FV) component is used to implement the enclosure. Upon receiving an activation, the FV pulls the data from the required channel but it does not complete the handshake on this port. It then activates its 'signal' port to initiate the enclosed command. In this example there are two enclosed inputs

so the activation is forked to two FVs and the signals are then synchronised to ensure both inputs have arrived before activating the enclosed case command. The FV provides passive read ports, much like a Variable component, on which the data can be read zero, one or many times. Within the enclosed command the channel is treated as if it were a variable. When the enclosed command completes the FVs complete the handshake on the input channels and acknowledge their activations.

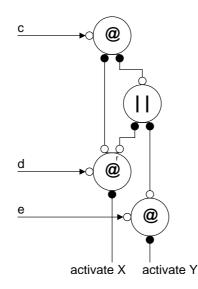

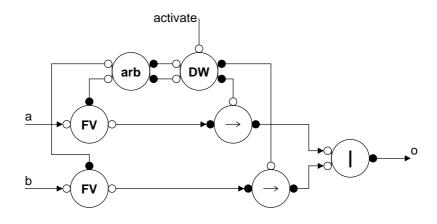

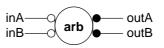

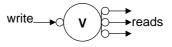

## 2.5.7 Arbitration

The arbitrate construct is used to implement conditional control based upon the arrival of communications on input channels. The syntax is as follows:

Two guards comprising a lists of channels are provided. If every channel in one of the lists have a communication pending, then that guard is true and the command for that list will be activated. If both guards become true very closely in time then it may not be possible to determine which occurred first. In this case an arbitrary decision is made. The command that is activated is enclosed by its input channels as discussed in the previous section, allowing any data on those channels to be read by the command.

#### 2.5.8 Data processing

Balsa features a number of operators that may be used to build expressions in the language. A number of operators may be compiled into hardware but several others are provided that may be used with compile-time constants but have no 'run-time' implementation.

Figure 2.16: Balsa data processing example

Expressions are used with channel write commands to generate data processing logic. For example the following code produces a tree of data processing components as shown in figure 2.16 and a Fetch component to initiate the processing.

Expressions are also used as the input to case and while structures where the Case and While components are the initiators in place of Fetch.

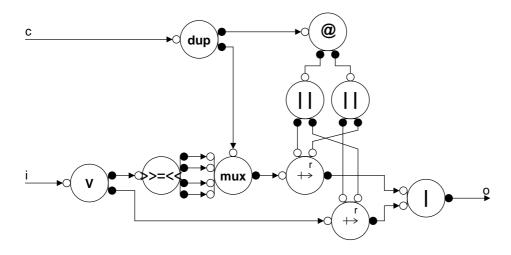

Note how the data processing structure is always a pull structure and, as a consequence of this, a single activation can be used to initiate the pulling of the data through the tree of data processing components.

#### 2.5.9 Miscellaneous connection components

The final few components to be mentioned do not correspond to any particular language structure but are used where multiple connections are made to a particular channel or variable. It has already been implied that the Variable component has a parameterisable number of read ports allowing the variable to be read from multiple locations in the code. Similarly the FalseVariable is

Figure 2.17: Balsa variable write from multiple possible sources

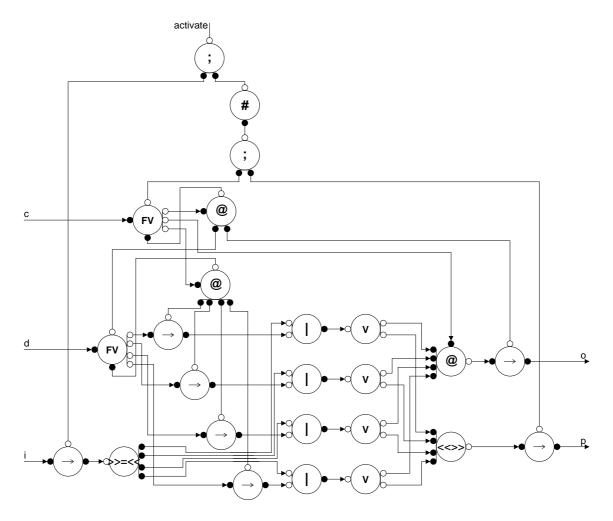

used to allow a channel to be read from multiple places. A variable and channel may also be written from multiple locations, providing they do not both attempt to perform a write concurrently. The *CallMux* component is used to merge multiple writes to a single channel or to a channel that connects to the write port of a variable. In the following code, a case statement is used to pick one channel (a, b or c) to write to variable v. The handshake circuit for this code is given in figure 2.17 which shows how the CallMux is used to merge the three possible write sources to the single write input to the Variable component.

```

case ctrl of

0 then

a -> v

| 1 then

b -> v

| 2 then

c -> v

end

```

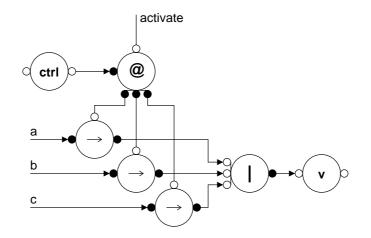

The Fork component is sometimes used in place of Concur to fork an activation to two components where the overhead of a Concur is unnecessary. In a four-phase protocol a Concur component allows independent return-tozero phases on each of its outputs whereas the Fork component synchronises

Figure 2.18: STG comparison of Fork and Concur

Figure 2.19: PassivatorPush component

following the processing phase of all the outputs before proceeding with the return-to-zero phase of all the outputs. Figure 2.18 illustrates the distinction between the two components by means of STGs. An example of the use of Fork is shown in figure 2.15 where it is used to fork the activation to each FalseVariable used for the handshake enclosure. As the two sides of the fork are symmetric, there is little advantage to be gained from having an independent return-to-zero phase in this instance.

The *Sync* component may also be encountered, often nearby a Fork as in figure 2.15. The Sync component is used to join several activations to produce a single activation that is triggered when all of the input activations have arrived.

The *Call* component (see figure 2.7) is used to merge several activations. An activation on any of the inputs is propagated to the output. The inputs must be mutually exclusive.

It can be seen in this section, that Balsa generates circuits with active inputs and active outputs. It is, of course, frequently necessary to connect an output from one process to the input of another. The *PassivatorPush* component (figure 2.19) is the used to accomplish this. PassivatorPush has a passive input and a passive output allowing data to be transferred from a push channel to a pull channel.

# 2.6 Implementing handshake components

The handshake circuit representation is independent of any particular implementation style or technology. However, in order to get meaningful results it is necessary to produce real circuits and so a particular implementation style

Figure 2.20: C-element with two inputs

| A | В | Ζ | Z' |  |  |

|---|---|---|----|--|--|

| 0 | 0 | Х | 0  |  |  |

| 0 | 1 | 0 | 0  |  |  |

| 0 | 1 | 1 | 1  |  |  |

| 1 | 0 | 0 | 0  |  |  |

| 1 | 0 | 1 | 1  |  |  |

| 1 | 1 | Х | 1  |  |  |

Table 2.1: C-element behaviour

must be selected. Tangram was originally proposed with a dual-rail implementation but a single-rail back-end is now commonly used [Pee96]. Balsa has several available back-end styles but the most commonly used are a four-phase broad bundled-data style and a dual-rail style. The broad bundled-data style in fact uses a broad protocol for push channels but a reduced broad protocol for pull channels. These two styles will be used in this thesis.

This remainder of this section introduces the asynchronous circuit elements that are used in the implementation of Balsa handshake components.

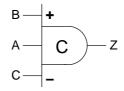

#### 2.6.1 Control elements

#### **C-element**

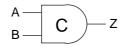

The Muller C-element [Mul62] is a ubiquitous asynchronous component. It is sometimes considered as performing an **and** of signal transitions rather than of logic levels as in a regular and gate. The output of the C-element only transitions when all of the inputs have reached the same logic level.

The symbol for the C-element is shown in figure 2.20 and the behaviour is show in table 2.1. C-elements are often used for synchronising signals. For

Figure 2.21: Sync component implementation

Figure 2.22: Asymmetric C-element

example, the Sync component described in section 2.5.9 may be implemented using a C-element as shown in figure 2.21.

The basic C-element can be extended by adding inputs that only affect transitions in one direction. Figure 2.22 shows an example asymmetric C-element and table 2.2 shows its behaviour. Inputs connected to the plus (+) symbol must be high for the output to transition from low to high while inputs connected to the minus (–) symbol must be low for the output to transition from high to low.

#### S-element

The S-element is a common component found in several handshake components. If the inputs and outputs are connected to the request and acknowledge

| Α | В | С | Ζ | Z' |

|---|---|---|---|----|

| 0 | Х | 0 | Х | 0  |

| 0 | Х | 1 | 0 | 0  |

| 0 | Х | 1 | 1 | 1  |

| 1 | 0 | Х | 0 | 0  |

| 1 | 0 | Х | 1 | 1  |

| 1 | 1 | Х | Х | 1  |

Table 2.2: Asymmetric C-element behaviour

Figure 2.23: S-element implementation

signals of channels then it implements *handshake enclosure;* that is the handshake on one side (the output handshake) of the component occurs within the handshake of the other (input handshake) side. See the STG in figure 2.24 and the implementation in figure 2.23.

For example, consider the control of the bundled data FalseVariable component used to implement input enclosure as described in section 2.5.6. The handshake on the write port of the FV must enclose the handshake on the signal port. This is accomplished as shown in figure 2.25.

#### **T-element**

The S-element was originally used exclusively in Balsa component implementations. In later revisions it was realised that often the S-element is more

Figure 2.24: S-element STG

Figure 2.25: FalseVariable control circuit

Figure 2.26: T-element implementation

Figure 2.27: T-element STG

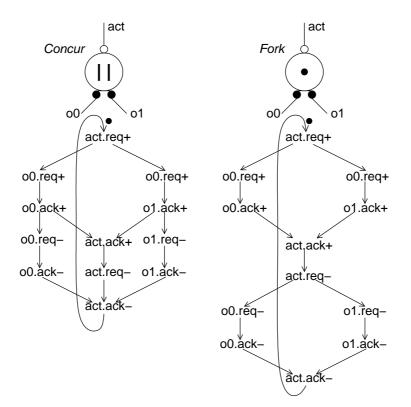

sequential than necessary [PTE05]. The T-element [NUK<sup>+</sup>94, KPWK02] implements a form of enclosure similar to the S-element but the return-to-zero phases of the handshakes are overlapped allowing more concurrent operation. The standard FalseVariable design now uses a T-element in place of the S-element shown in figure 2.25.

### 2.6.2 Dual-rail elements

It is often convenient to generalise a variable width data bundle by drawing the entire bundle as a single arrow. A few symbols are used to show how this data is processed.

Figure 2.28: Read Port

Figure 2.29: Merge

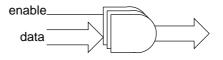

#### **Read port**

The symbol in figure 2.28 is used to represent a set of **and** gates, one for each wire in the data. The enable signal is distributed to all the **and** gates allowing the output of data to be controlled.

#### Merge

The symbol in figure 2.29 is used to represent a merging of multiple bundles of the same width. The corresponding wires from each bundle are passed through an **or** gate. In dual-rail it is imperative that data is not present on more than one input.

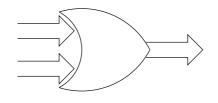

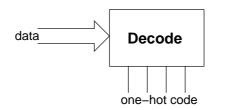

#### Decode

Decode (figure 2.30) is used to convert data into a one-hot code based on the value of the input data. In Balsa, this is achieved by specifying the values of the input data that correspond to each output wire. The specification is passed to the logic minimiser Espresso [BSVMH84, Esp] to generate an efficient circuit implementation.

Figure 2.30: Decode

Figure 2.31: Single to dual-rail converter

#### Single to dual-rail converter

This element converts single-rail data to dual-rail. This is sometimes useful, for example in order to provide a dual-rail input to the decode element. Figure 2.31 shows the implementation of the converter for each data bit.

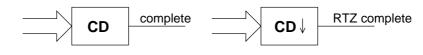

## 2.6.3 Completion Detection

The arrival of a single bit in dual-rail encoding is detected by an **or** of the two data wires. To detect the completion of a wider bundle of data a C-element is used to combine the completion of each individual bit.

Completion detection is shown as a single element on schematics as shown in figure 2.32.

Sometimes it is not necessary to use completion detection for the arrival of

Figure 2.32: Completion Detection

data but only to check that it has returned to zero. This allows the implementation to be simplified as **or** gates may be used in place of the C-elements. A downward pointing arrow is added to the CD element to indicate this variety of completion detection.

# 2.7 What does 'performance' mean in an asynchronous circuit

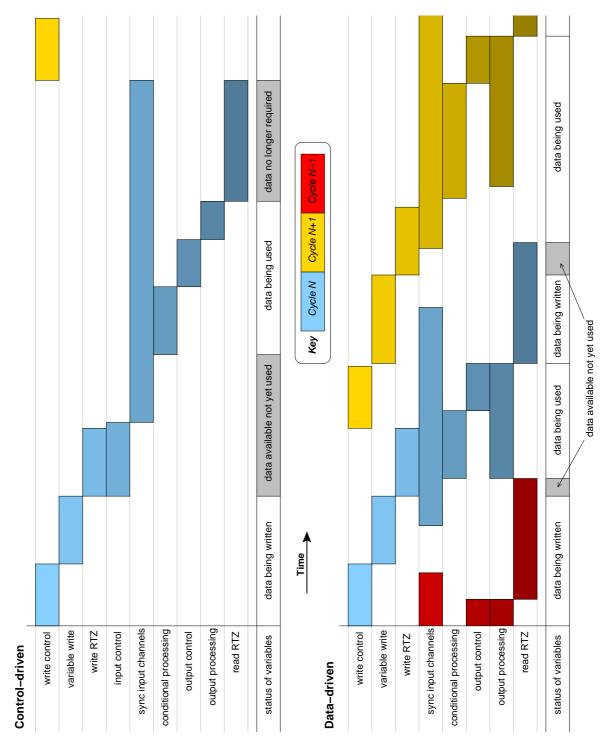

It is important to distinguish what is meant by the term 'performance' which will be used throughout this thesis. In general the term is used to mean throughput rather than latency, but of course these are not unrelated.

It is easy to determine the performance of a synchronous circuit. The latency of the worst-case delay (critical path) through the logic of the circuit determines the fastest possible clock speed. Or in practice, a target clock speed is chosen and used to determine the maximum latency of the critical path. A design is usually partitioned into pipeline stages in order to reduce the latency of the critical path. The completion of every stage is determined by the global clock and so every stage is restricted to operating at the speed of the slowest. The throughput is determined by the clock cycle.

In an asynchronous system there is no external clock to determine the completion of logic. Instead, each stage is free to individually determine when it completes. Each stage may have a fixed delay but, more often, the delay is data-dependent – the delay varies depending upon the operation being performed. In a synchronous design, each stage produces a result on a clock signal and begins the next operation on that same signal. In an asynchronous system the handshake signalling means that the cycle time is not determined solely by the latency of producing a result but also of acknowledging that result and resetting the stage back to a state where the next operation can begin.

In this thesis the throughput of an asynchronous circuit will usually be determined by measuring the average cycle time of the circuit while repeatedly performing an operation. The cycle time is the delay between producing consecutive results in the repeated operation. For modules whose operation can vary depending on data, a number of different operations will be performed to determine the variation in cycle time.

# **Chapter 3**

# **Data-driven Circuit Style**

# 3.1 Control overhead

Section 2.4 gave a brief introduction to the compilation of Balsa into handshake circuits. The resulting circuit may be roughly split into two sections: control and datapath. The datapath consists of Variable components, data processing structures and data channels. The control consists of a tree of control components connected with sync channels, which direct the movement of data around the datapath by activating interface components such as Fetch, False-Variable, and While. This style of translation is described as control-driven meaning that the control tree is responsible for initiating all datapath operations. This approach is robust and flexible but there is a significant drawback: the overhead of the control. The control is nearly always slower than the data and as control and data are frequently synchronised, the data is frequently stalled waiting for the control to catch up.

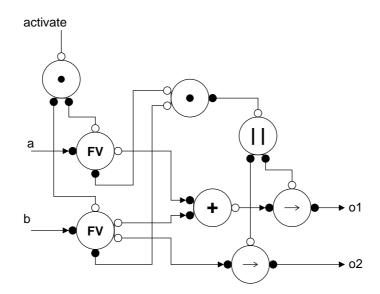

An example will now be given that attempts to demonstrate how the controldriven structure contributes to control overhead. Figure 3.1 generalises the structure of a control-driven procedure which produces an output (O) and requires an input (A). Internally the process uses two variables (V0 and V1). The

Figure 3.1: General control-driven structure

operation of this structure is extremely sequential. Firstly the portion of control labelled write is activated. The control decides whether to write some data to the Variable components. Once any data is written, it can be considered as being available for reading from the Variable components. However, the control must then complete its handshake before the right-hand side of the tree is activated.

As well as data stored in variables, data from channels may also be used by means of input enclosure. The control (here labelled input) must activate the pulling of any such data to the FV component. The input control waits for the signal from the FV indicating the arrival of the data. Once again, it is not unlikely that this data has been available for some time on channel A which is awaiting synchronisation at the PassivatorPush in order to deliver it.

All the required operands for the data processing operations have now been collected. The control may then initiate data processing operations. It may be necessary to decide what operations should be performed based on some of the data (e.g. a if a case construct is used). Therefore the control may initiate some data processing operations using a Case component for the purpose of making conditional choices. Following this, the final data processing operations that actually produce the outputs are initiated. These outputs are are written to variables or communicated on output channels.

When the variable writes and/or output communications are complete, the data in the Variables and on input channels may be considered as being no longer required. However, all the handshaking in the control for inputs, conditionals and outputs must be completed before the write control is even activated again to begin the process of deciding whether to overwrite the data in the Variables.

Note that for different processing operations, only a subset of the inputs may be required but all the inputs are synchronised with each other and the control before any operations begin. Furthermore, no inputs are released until after all data operations have completed, even though some may not be required after some operations have completed. If data were released sooner then other parts of the circuit will be allowed to proceed sooner as well.

The three principal problems in the structure of the handshake circuit that contribute to the control overhead are:

- All inputs are synchronised with each other before any further operations are begun. Data is available in Variable components before the read control is even activated. After it is activated, the control then synchronises with all channels that are used as inputs before the control begins to decide what operations to perform. If control were operating in parallel with the arrival of data, then data may not be stalled as long while the control decides what to do. The control may even have resolved itself before the data arrives. If there were no need to synchronise all inputs before any operation can proceed then processing, and control that relies on part of the data, can get a head start and operate concurrently with the arrival of the remaining data.

- The sequential activation of the read and write 'halves' of the control tree. This sequencing is needed to ensure the variable is not written and read concurrently. However, the location of the sequencing in the control tree is far away from the Variable leading to sequential operation of the two 'halves' of the control tree. More concurrent operation of the two halves of the tree should increase performance.

- Data processing operations only begin after the control initiates them due to the pull style of operation. If the data processing were to operate in parallel with the control then the overhead of the control should have a reduced impact.

#### 3.1.1 Balsa features to combat control overhead

Several modifications have been made to the existing Balsa system in an effort to reduce the impact of control overhead.

#### **Control re-synthesis**

Attempts have been made to apply control re-synthesis to the control of both Tangram [KVL96] and Balsa [CNBE02, CN02]. Control re-synthesis attempts to improve the performance of the control tree by clustering sections of the control tree, determining the overall behaviour, and synthesising a new controller to implement this behaviour using a controller synthesis tool [CKK<sup>+</sup>97, FNT<sup>+</sup>99]. By removing the communications between clusters of components, the resulting controller should improve performance over the original control tree.

Control re-synthesis is effective but limited. Improving the speed of the control tree will obviously help reduce control overhead but only so much improvement can be gained. The control still synchronises with data at the same points and so the sequential operation of the control-driven structure is still maintained. Control re-synthesis is complementary to other approaches to improving control overhead including the data-driven style introduced in this thesis.

In addition to re-synthesis it has been suggested [CN02] that the direction of the data processing in Balsa may be reversed from a pull to a push implementation to enable concurrent operation of control and data processing. However, this assumes that a Variable component will be written and read in every 'cycle' of operation. This is not usually the case in conventional Balsa as the control may only conditionally activate the read or write. The data-driven style does not offer Balsa-style variables in order to avoid this problem; datadriven variables are read and written in every cycle and therefore support a push data processing structure.

#### **Concurrent sequencer**

This technique specifically addresses the second of the three issues identified above by applying concurrent sequencing [PN98]. The original Balsa Sequence component has been enhanced to include concurrent sequence behaviour. The concurrent sequencer allows some overlapping between the write and read halves of the control. The read half of the control may be activated at the start of the return-to-zero phase of the write half, instead of waiting for the entire handshake to complete. This allows the write RTZ phase to operate concurrently with the read control. Unfortunately this cannot be done if the control is reversed so that reads precede writes as a write-after-read (WAR) hazard would be inserted [NUK<sup>+</sup>94]. In some situations a write-after-write (WAW) hazard may also prevent the use of concurrent sequencing. The Balsa compiler has been modified to automatically insert concurrent sequencing where it is safe to use it [PTE05]. Concurrent sequencing provides performance improvements but it is limited in where it can be safely applied and only allows partial overlapping of the sequenced operations.

#### 'Eager' inputs

Eager inputs use modified FalseVariable components that activate the control without waiting for the data to arrive. The control is able to proceed up until the point where synchronisation with the data is required and there it stalls until the data does arrive [PTE05]. Since the original publication, further work has shown that there are more conditions than originally thought where eager inputs may not be used, although these conditions do not occur in the nanoSpa processor used as an example design in chapter 5. There is the possibility of automatically detecting when it is safe to use eager inputs, or allowing the designer to decide where they should be used by modifications to the source language, or a mixture of both these options. At this time, neither of these options have been fully integrated into the design flow so eager inputs have

not been used in the Balsa nanoSpa used in chapter 5.