# Quality-of-Service (QoS) for Asynchronous On-Chip Networks

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science and Engineering

2004

Tomaz Felicijan

Department of Computer Science

# Contents

| Contents                                      | 2  |

|-----------------------------------------------|----|

| List of Figures                               | 6  |

| List of Tables                                | 8  |

| Abstract                                      | 9  |

| Declaration                                   | 10 |

| Copyright                                     | 10 |

| The Author                                    | 11 |

| Acknowledgements                              | 12 |

| Chapter 1: Introduction                       | 13 |

| 1.1 Thesis overview                           |    |

| 1.2 Research contributions                    |    |

|                                               |    |

| Chapter 2: Asynchronous Logic                 |    |

| 2.1 Introduction                              |    |

| 2.1.1 Advantages of asynchronous logic        |    |

| 2.1.2 Disadvantages of asynchronous logic     |    |

| 2.2 Asynchronous design methodologies         |    |

| 2.2.1 Delay-insensitive circuits              |    |

| 2.2.2 Quasi delay-insensitive circuits        |    |

| 2.2.3 Speed-independent circuits              |    |

| 2.3 Handshaking protocols                     |    |

| 2.3.1 Non return-to-zero handshaking protocol |    |

| 2.3.2 Return-to-zero handshaking protocol     |    |

| 2.4 Data encoding                             |    |

| 2.4.1 Single-rail encoding                    |    |

| 2.4.2 Delay-insensitive encoding              |    |

| 2.5 The Muller C-element                      |    |

| 2.6 Metastability                             |    |

| 2.7 Large-scale asynchronous design           |    |

| 2.8 Summary                                   | 36 |

| Chapter 3: Quality-of-Service (QoS)           | 37 |

| 3.1 Introduction                              |    |

| 3.1.1 QoS: a user's view                      | 38 |

| 3.2 Basic QoS architecture                    | 38 |

| 3.3 End-to-end QoS levels                     | 38 |

| 3.4 QoS control methods                       | 39 |

| 3.4.1 Overprovisioning                        | 40 |

| 3.4.2 Buffering                               |    |

| 3.4.3 Traffic shaping                         |    |

| 3.4.4 Resource reservation                    |    |

| 3.4.5 Admission control                       | 46 |

| 3.5 Summary                                   | 47 |

| Chapter 4: Networks-on-Chip (NoCs)            | 48 |

| 4.1        | Introduction                                              | 48       |

|------------|-----------------------------------------------------------|----------|

| 4.2        | NoC design issues                                         | 50       |

|            | 4.2.1 Wiring resources                                    | 50       |

|            | 4.2.2 Power consumption                                   | 51       |

|            | 4.2.3 Modularity                                          | 51       |

|            | 4.2.4 Hardware costs                                      | 51       |

| 4.3        | OSI reference model applied to NoCs                       | 52       |

|            | NoC services                                              |          |

|            | 4.4.1 Data integrity                                      | 55       |

|            | 4.4.2 Lossless data delivery                              |          |

|            | 4.4.3 In-order data delivery                              | 55       |

|            | 4.4.4 Time-related guaranteed services                    |          |

| 4.5        | QoS for on-chip networks                                  | 56       |

|            | 4.5.1 Guaranteed services                                 |          |

|            | 4.5.2 Best-effort services                                |          |

| 4.6        | QoS for asynchronous networks                             |          |

|            | 4.6.1 Reserving network bandwidth                         |          |

|            | 4.6.2 Buffer management                                   |          |

|            | 4.6.3 Admission control                                   |          |

| 4.7        | Summary                                                   | 63       |

|            |                                                           | <b>7</b> |

| _          | 5: The Network Layer                                      |          |

| 5.1        | Introduction                                              |          |

| 5.0        | 5.1.1 Direct networks                                     |          |

|            | Network topology                                          |          |

| 5.5        | Switching                                                 |          |

|            | 5.3.1 Circuit switching                                   |          |

|            | 5.3.2 Store-and-forward and virtual cut-through switching |          |

| 5 1        | 5.3.3 Wormhole switching                                  |          |

| 5.4        | Routing                                                   |          |

|            | 5.4.1 Algorithmic routing                                 |          |

|            | 5.4.2 Source routing                                      |          |

|            | 5.4.3 Dimension-ordered routing algorithm                 |          |

|            | Packet size and organization                              |          |

| 5.6        | QoS architecture                                          |          |

|            | 5.6.1 Principle of operation                              |          |

| <i>E</i> 7 | 5.6.2 Bandwidth allocation                                |          |

| 5.7        | Summary                                                   | //       |

| Chapter    | 6: The Data Link Layer                                    | 78       |

| -          | Data integrity                                            |          |

| 6.2        | Flow-control                                              | 79       |

| 6.3        | Medium access control                                     | 80       |

|            | 6.3.1 Asynchronous arbitration                            | 81       |

|            | 6.3.2 Proposed solution                                   |          |

|            | 6.3.3 Principle of operation                              |          |

|            | 6.3.4 Implementation                                      |          |

| 6.4        | Summary                                                   |          |

| Chapter    | ·7: The Physical Layer                                    | 88       |

| 7.1 Introduction                                                                          | 88  |

|-------------------------------------------------------------------------------------------|-----|

| 7.1.1 Power dissipation                                                                   | 89  |

| 7.1.2 Synchronization                                                                     | 89  |

| 7.2 An asynchronous ternary logic signalling system                                       |     |

| 7.2.1 ATLS system transmitter                                                             |     |

| 7.2.2 ATLS system receiver                                                                |     |

| 7.2.3 Enhanced ATLS system transmitter                                                    |     |

| 7.2.4 Test architecture and quality metrics                                               |     |

| 7.2.5 Robustness and reliability                                                          |     |

| 7.2.6 Results                                                                             |     |

| 7.3 Summary                                                                               |     |

| ·                                                                                         |     |

| Chapter 8: Router Design                                                                  |     |

| 8.1 Summary of the NoC design issues                                                      |     |

| 8.1.1 Network services                                                                    |     |

| 8.1.2 Topology and routing                                                                |     |

| 8.1.3 Switching                                                                           |     |

| 8.1.4 Packet size and organization                                                        |     |

| 8.1.5 QoS architecture                                                                    |     |

| 8.1.6 Implementation technology                                                           |     |

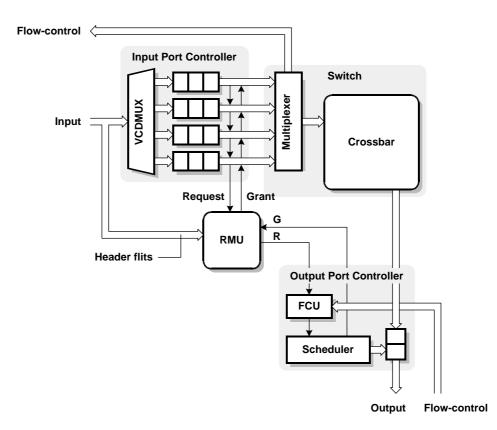

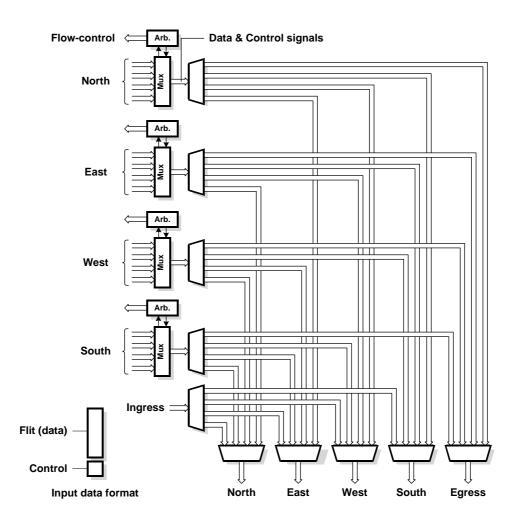

| 8.2 Top level diagram                                                                     |     |

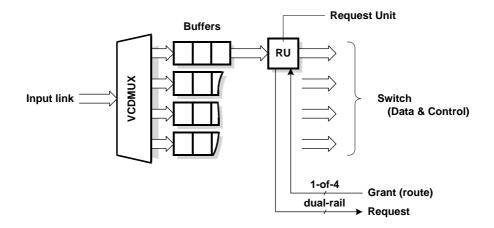

| 8.3 Input port controller                                                                 |     |

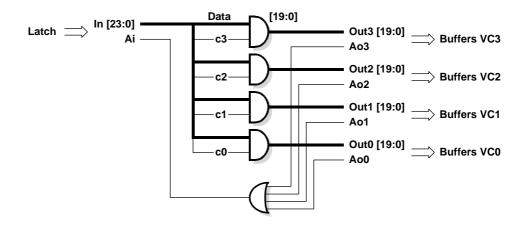

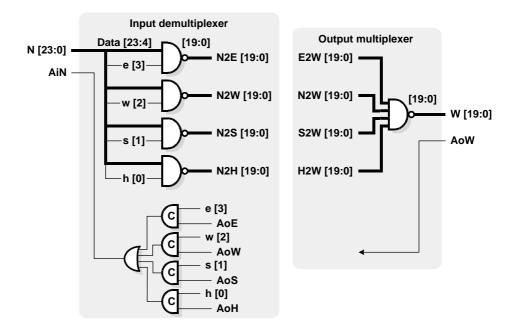

| 8.3.1 Virtual channel demultiplexer (VCDMUX)                                              |     |

| 8.3.2 Input buffers                                                                       |     |

| 8.3.3 Request unit                                                                        |     |

| 8.4 Switching fabric                                                                      |     |

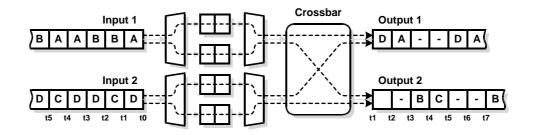

| 8.4.1 Crossbar                                                                            |     |

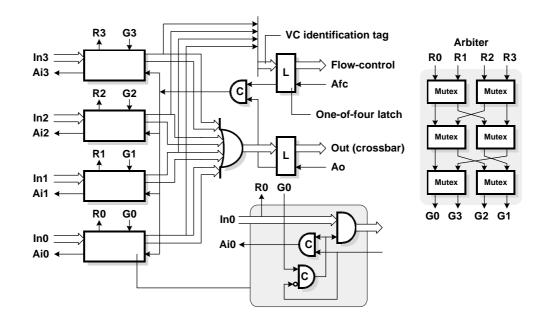

| 8.4.2 Input multiplexer and arbiter                                                       | 118 |

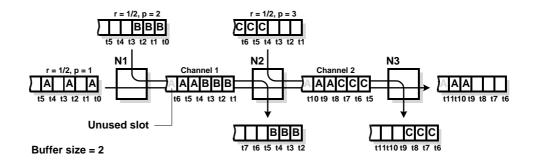

| 8.5 Output port controller                                                                |     |

| 8.5.1 Flow-control unit                                                                   | 119 |

| 8.5.2 Scheduler                                                                           | 120 |

| 8.6 Route management unit                                                                 | 122 |

| 8.7 QoS guarantees and constraints of the router                                          | 125 |

| 8.8 Summary                                                                               | 130 |

| Chapter 9: Evaluation                                                                     | 121 |

| 9.1 Network performance                                                                   |     |

| 9.1.1 Test harness                                                                        |     |

| 9.1.2 Test network traffic analysis and admission control                                 |     |

| 9.1.3 QoS traffic specifications                                                          |     |

| 9.1.4 Delay and jitter analysis                                                           |     |

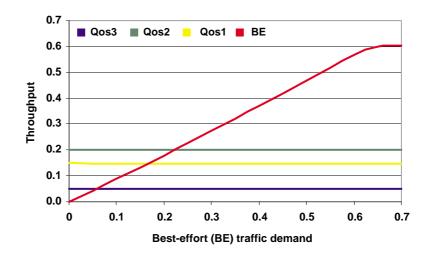

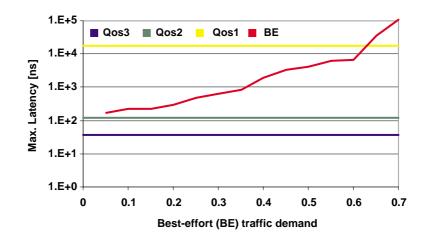

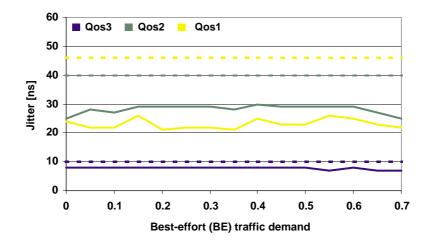

| 9.1.5 Simulation results                                                                  |     |

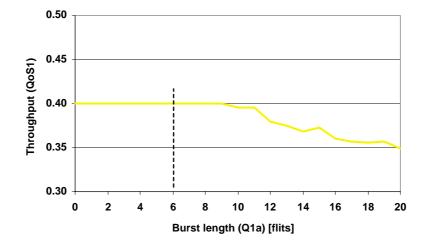

| 9.1.6 Minimum buffer constraint                                                           |     |

|                                                                                           |     |

| <ul><li>9.2 Hardware requirements</li><li>9.3 Comparison with similar solutions</li></ul> |     |

| -                                                                                         |     |

| Chapter 10: Conclusions                                                                   |     |

| 10.1 Advantages                                                                           |     |

| 10.1.1 Clock-skew                                                                         |     |

| 10.1.2 Modularity                                                                         | 155 |

| 10.1.3 Complexity                        |     |

|------------------------------------------|-----|

| 10.2 Disadvantages                       |     |

| 10.2.1 Number of virtual channels        |     |

| 10.2.2 Admission control                 | 156 |

| 10.2.3 Passive bit-rate control          | 156 |

| 10.3 Future research directions          | 157 |

| 10.3.1 Bundled-data implementation       | 157 |

| 10.3.2 Alternative scheduling algorithms | 157 |

| 10.3.3 Admission control                 | 158 |

| References                               | 159 |

# List of Figures

| 2.1 A synchronous pipeline.                                                       | 20      |

|-----------------------------------------------------------------------------------|---------|

| 2.2 An asynchronous pipeline.                                                     | 21      |

| 2.3 Circuit fragment with gate and wire delays.                                   | 26      |

| 2.4 An asynchronous communication channel.                                        | 27      |

| 2.5 Non return-to-zero handshaking protocol.                                      | 28      |

| 2.6 Return-to-zero handshaking protocol.                                          | 29      |

| 2.7 A C-element and its truth table.                                              | 32      |

| 2.8 Asymmetric C-elements and corresponding truth tables.                         | 33      |

| 2.9 CMOS implementation of a mutex.                                               | 34      |

| 3.1 High jitter (a) and low jitter (b).                                           | 40      |

| 3.2 Resolving jitter by buffering packets.                                        | 41      |

| 3.3 Leaky bucket mechanism.                                                       | 42      |

| 3.4 Time-division multiplexing.                                                   | 43      |

| 3.5 HOL blocking.                                                                 | 46      |

| 4.1 Typical bus-based SoC.                                                        | 49      |

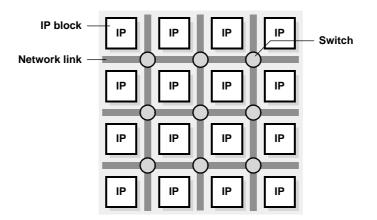

| 4.2 SoC design based on a two-dimensional mesh NoC.                               | 49      |

| 4.3 Layered approach to managing communication complexity.                        | 52      |

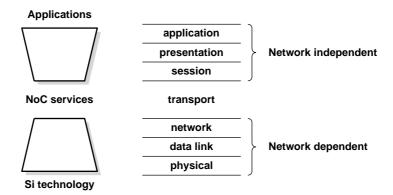

| 4.4 NoC protocol stack.                                                           | 54      |

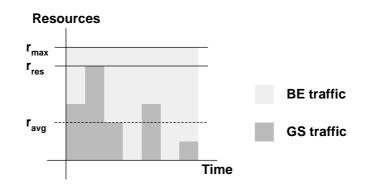

| 4.5 The effect of GS traffic on resource usage.                                   | 57      |

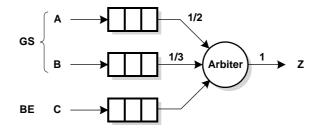

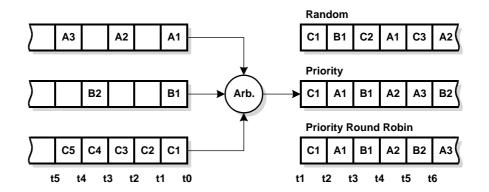

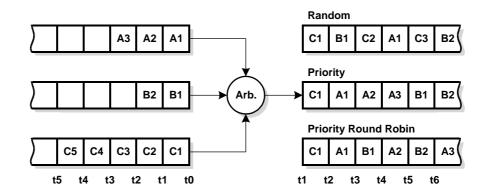

| 4.6 Three input arbiter.                                                          | 59      |

| 4.7 Uniformly distributed traffic.                                                | 60      |

| 4.8 Bursty traffic.                                                               | 60      |

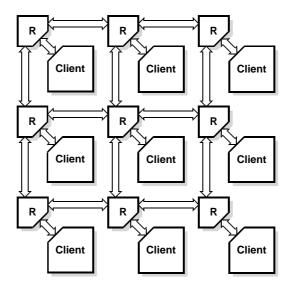

| 5.1 A two-dimensional network with bi-directional links between nodes.            | 66      |

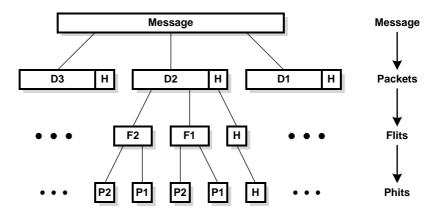

| 5.2 Message, packets, flits and phits in direct networks.                         | 67      |

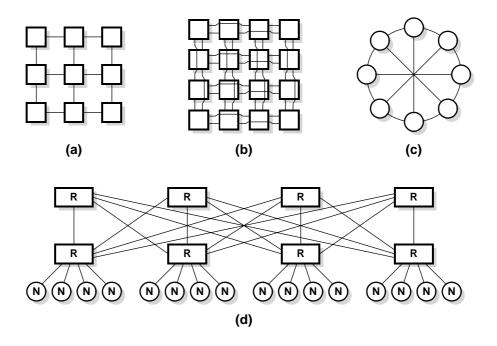

| 5.3 NoC topologies: 2D mesh (a), folded torus (b), octagon (c), and fat-tree (d). | 68      |

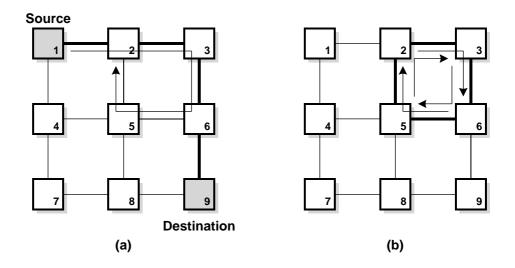

| 5.4 An example of livelock (a) and deadlock (b) in a network.                     | 71      |

| 5.5 Deterministic and adaptive routing in a 2-dimensional mesh network.           | 72      |

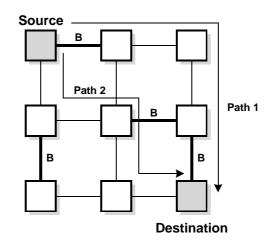

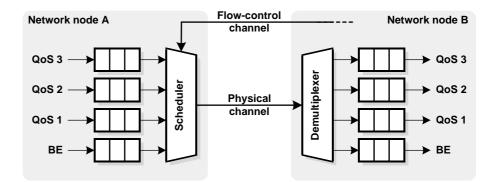

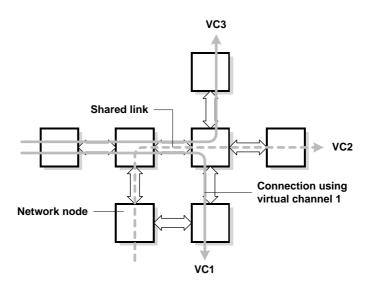

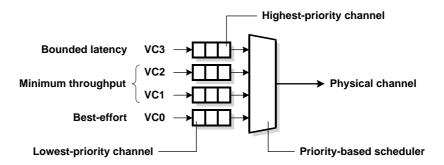

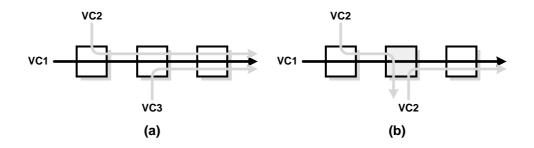

| 5.6 QoS architecture using virtual channels.                                      | 74      |

| 5.7 Multiple QoS connections sharing the same physical channel.                   | 75      |

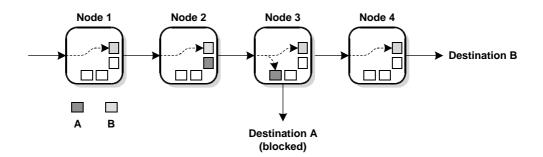

| 5.8 Blocked packet holds idle only a single virtual channel.                      | 76      |

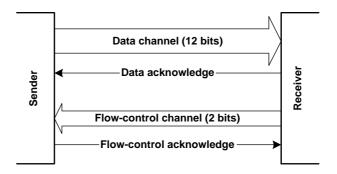

| 6.1 Unidirectional network link.                                                  | 79      |

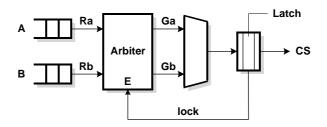

| 6.2 A single bit lock register.                                                   | 82      |

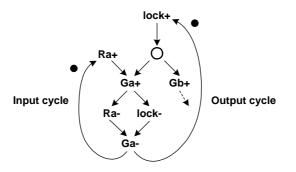

| 6.3 Principle of the operation.                                                   | 83      |

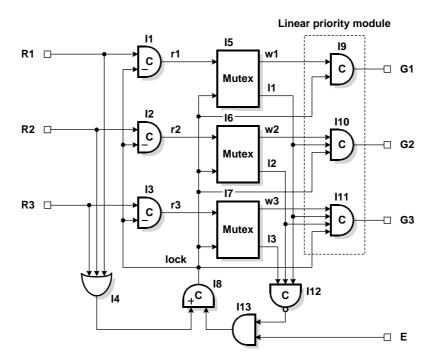

| 6.4 Partial STG of the arbitration system.                                        | 84      |

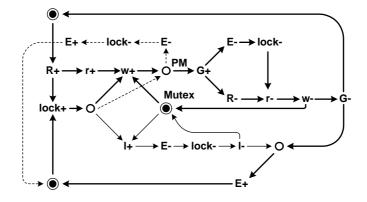

| 6.5 Circuit of the arbiter.                                                       | 85      |

| 6.6 STG of the arbiter.                                                           | 86      |

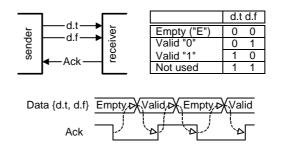

| 7.1 Dual-rail four-phase protocol.                                                | 91      |

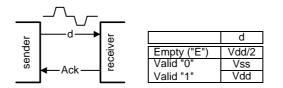

| 7.2 Principle of the ATLS system.                                                 | 92      |

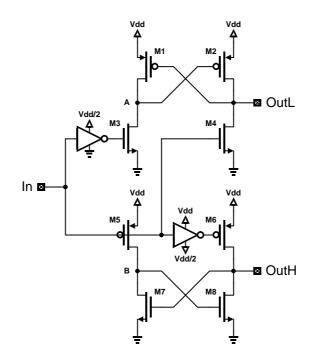

| 7.3 ATLS system transmitter.                                                      | 93      |

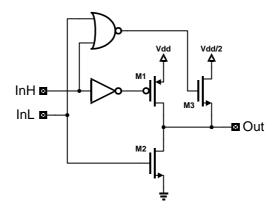

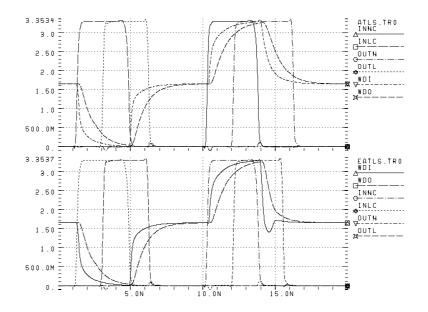

| 7.4 Output waveforms of basic (upper graph) and enhanced (lower graph) ATLS       | system. |

| 94                                                                                |         |

| 7.5 ATLS system receiver.                                                         | 95      |

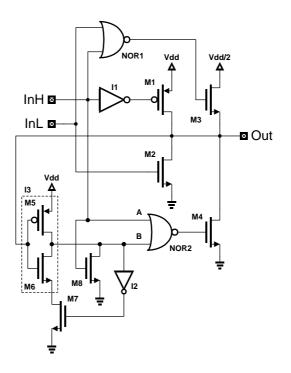

| 7.6 Enhanced ATLS system transmitter.                                             | 97      |

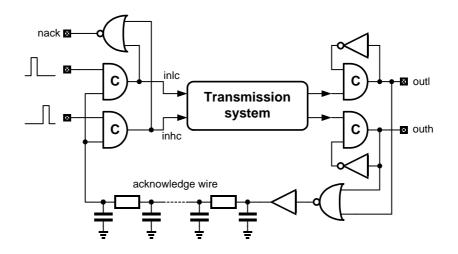

| 7.7 The simulation circuit.                                                       | 99      |

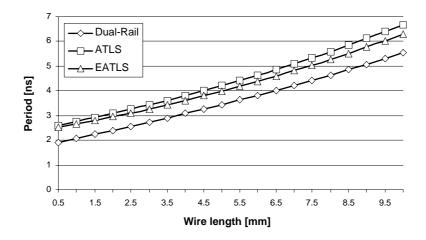

| 7.8 Period versus wire length.                                                    | 101     |

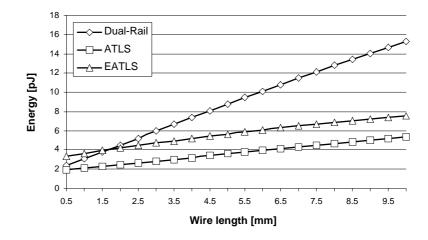

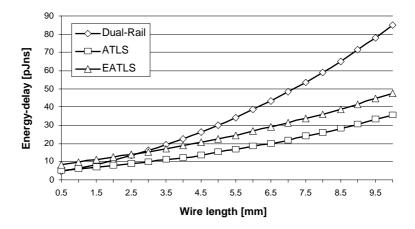

| 7.9 Energy versus wire length.                                                 | 102    |

|--------------------------------------------------------------------------------|--------|

| 7.10 Energy-delay versus wire length.                                          | 103    |

| 7.11 Period, energy and energy-delay product vs. voltage supply at 10 mm wir   | e. 104 |

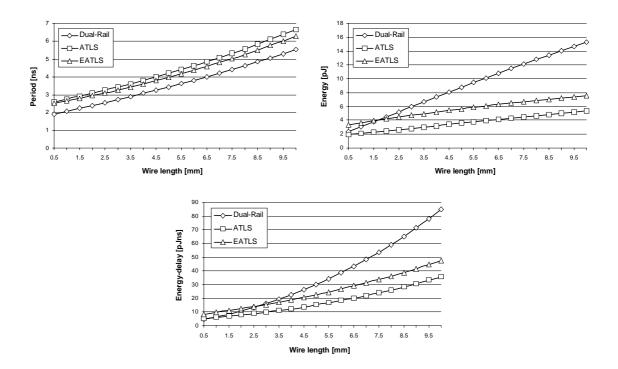

| 8.1 Organization of a packet.                                                  | 108    |

| 8.2 Time-related guaranteed services using virtual channels.                   | 109    |

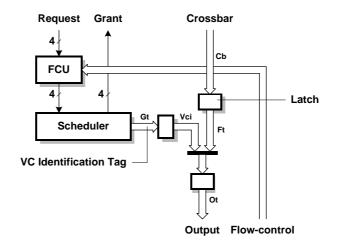

| 8.3 Top level diagram of the router.                                           | 110    |

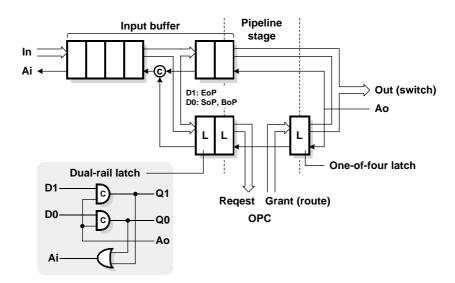

| 8.4 Input port controller.                                                     | 111    |

| 8.5 A gate-level schematic of the VCDMUX.                                      | 111    |

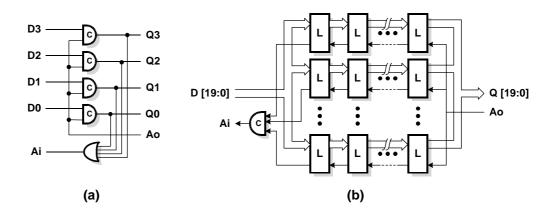

| 8.6 An asynchronous one-of-four latch (a) and an input buffer (b).             | 112    |

| 8.7 Request unit.                                                              | 113    |

| 8.8 Non-multiplexed switch.                                                    | 114    |

| 8.9 Multiplexed switch.                                                        | 115    |

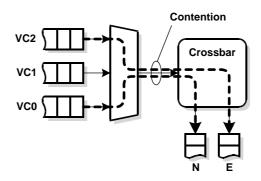

| 8.10 Contention in a multiplexed switch.                                       | 115    |

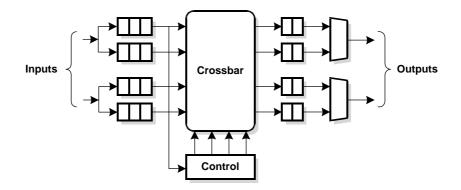

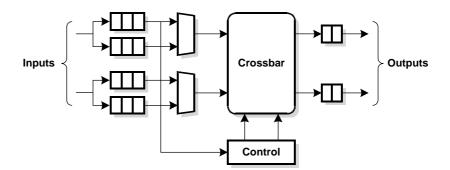

| 8.11 Partly-connected 5-by-5 crossbar switch with multiplexed inputs.          | 116    |

| 8.12 Crossbar implementation.                                                  | 117    |

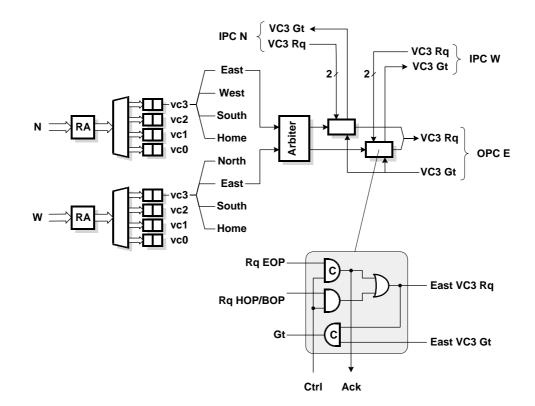

| 8.13 Crossbar arbitration.                                                     | 118    |

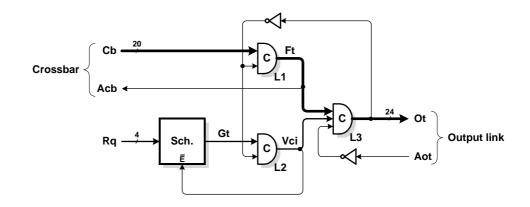

| 8.14 Output port controller.                                                   | 119    |

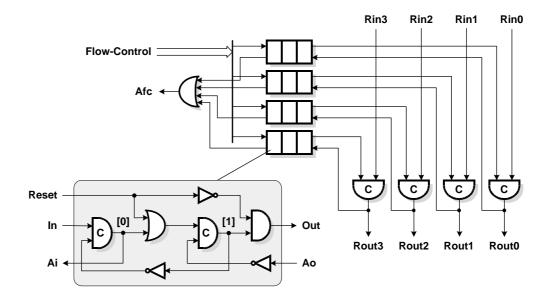

| 8.15 Flow-control unit.                                                        | 120    |

| 8.16 Scheduler: principle of operation.                                        | 121    |

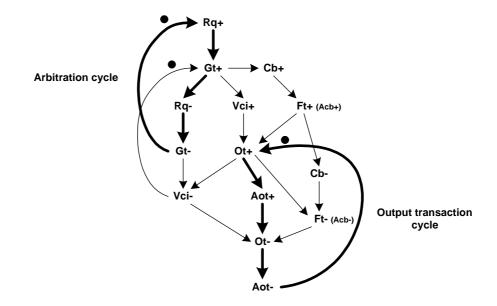

| 8.17 STG of an output port controller.                                         | 122    |

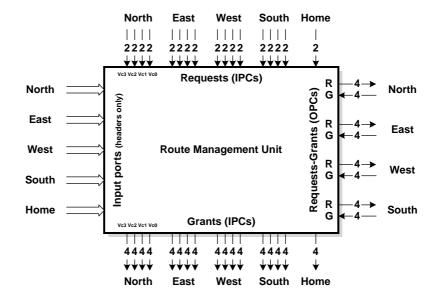

| 8.18 A RMU symbol with input and output ports.                                 | 123    |

| 8.19 The operation of the RMU.                                                 | 124    |

| 8.20 QoS constraint due to the multiplexed switch.                             | 125    |

| 8.21 Minimum buffer size QoS constraint.                                       | 128    |

| 8.22 Minimum buffer size requirement examples.                                 | 129    |

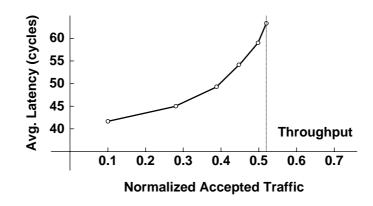

| 9.1 A typical BNF plot illustrating throughput as the maximum accepted traffic | c. 132 |

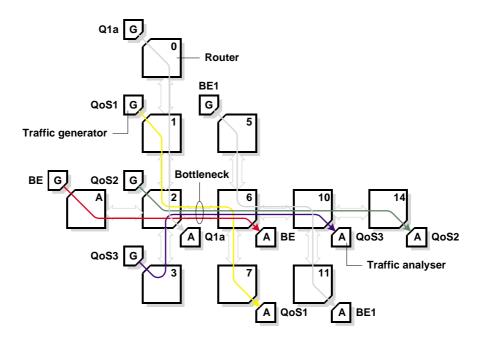

| 9.2 Test network.                                                              | 133    |

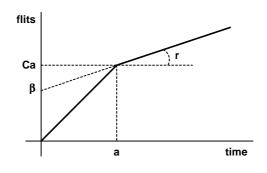

| 9.3 Linear traffic bounding function.                                          | 139    |

| 9.4 Throughput versus best-effort traffic demand.                              | 143    |

| 9.5 Maximum latency versus best-effort traffic demand.                         | 144    |

| 9.6 Jitter versus best-effort traffic demand.                                  | 145    |

| 9.7 Throughput of QoS1 versus the burst length of Q1a.                         | 147    |

# List of Tables

| 5.1 Summary of switching techniques.        | 69  |

|---------------------------------------------|-----|

| 7.1 Typical noise sources.                  | 100 |

| 7.2 Noise analysis of the proposed systems. | 104 |

| 9.1 Summary of delay analysis.              | 142 |

| 9.2 Hardware costs of the router.           | 148 |

| 9.3 Communication architecture comparison.  | 150 |

# Abstract

Networks-on-Chip (NoCs) are emerging as a new design paradigm to tackle the challenge of managing the complexity of designing chips containing billions of transistors. One of the key features of a modern NoC is the ability of the interconnect to provide Quality-of-Service (QoS) capabilities in order to accommodate different components with strict traffic characteristics and constraints. However, the adoption of NoCs as the solution for global interconnect still raises the question of which clocking strategy to use. While local wires scale in length with a technology, global wires spanning an entire chip do not - exactly the situation that leads to clock skew problems.

One way to eliminate this problem is to use asynchronous logic for an on-chip network implementation. This leaves only the issue of connecting synchronous components to an asynchronous network. Furthermore, properties such as low power, improved electromagnetic compatibility (EMC) and robustness, offer additional benefits from the use of self-timed logic for on-chip interconnect.

The research presented in this thesis describes an asynchronous on-chip network router with QoS support. The router employs a virtual channel architecture together with a priority-based scheduler to provide time-related guarantees. The resulting QoS architecture is suitable for on-chip implementation because of its low complexity and low area overhead.

Simulation results show that the proposed architecture utilizing self-timed logic is capable of providing time-related guarantees such as minimum bandwidth and bounded communication latency.

# Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# Copyright

- (1). Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

- (2). The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of the Department of Computer Science.

# **The Author**

Tomaz Felicijan obtained a University Degree in Electrical Engineering from the University of Maribor, Slovenia in 1997. He joined the Advanced Processor Technology (APT) Group at the Department of Computer Science at the University of Manchester in 2002. Since then he has been working in the area of asynchronous on-chip networks towards the Ph.D. degree and this thesis is the result of three years of research.

# Acknowledgements

First of all I would like to thank my supervisor, Prof. Steve Furber without whose guidance and support this thesis would not have been possible. Thank you Steve for giving me a chance to do this Ph.D. and all the encouragement, support and understanding.

Special thanks go to Dr. Steve Temple, Dr. Aris Efthymiou and Dr. John Bainbridge for proofreading this thesis. John also fixed my first asynchronous circuits and was a great influence at the beginning of my studies. He is greatly responsible for the success of this thesis.

I would also like to thank Dr. Kees Goossens and John Dielissen from Philips Research Laboratories in Eindhoven for many useful discussions during my internship in The Netherlands.

General thanks go to all members of the APT group at the University of Manchester and the rest of the people I bumped into and became friends with while I was trying to find my place under the sun in Manchester. The list is long, so thank you guys.

Finally, I would like to express my gratitude to my parents and my family for their eternal support and love, and to my girlfriend Sabina for being there when I needed her most.

To my grandma **Veronika Felicijan** (1911-2002) and my uncle **Martin Jurak** (1941-2003).

V spomin na staro mamo **Veroniko Felicijan** (1911-2002) in strica **Martina Juraka** (1941-2003).

# Chapter 1: Introduction

The 2001 International Technology Roadmap for Semiconductors (ITRS) [41] projects that multi-billion transistor chips will come to production by the end of this decade. As we proceed into *deep sub-micron* (DSM) technologies feature sizes will shrink well below 100 nm, supply voltages will drop under 1 V and clock frequencies will increase up to 10 GHz. This will not only introduce a whole new set of application possibilities but will also aggravate current problems in *Very-Large-Scale-Integration* (VLSI) design and, moreover, introduce several new ones.

Wire delays will predominate over gate delays and global interconnects spanning a chip will carry signals whose propagation time exceeds a clock period [39]. Synchronization over an entire chip with a single clock source will therefore become extremely hard or even impossible. One synchronization paradigm that is likely to prevail in the future is *Globally-Asynchronous-Locally-Synchronous* (GALS). The main idea of the GALS systems is to partition a chip into several sections each driven by an independent clock source. To form a functionally correct system the sections are glued together by an asynchronous interconnect fabric.

With several billion transistors on a single piece of silicon it is highly unlikely that the majority of chips in the future will be designed from scratch. On the contrary, designers will strive to reuse existing components and *intellectual property* (IP) blocks as much as possible to reduce design costs and shorten time-to-market. This will reinforce the market for IP vendors such as ARM Limited, who license designs of the same processor core to many competing semiconductor manufacturers. The success of *Systems-on-Chips* (SoCs) will rely on using appropriate design and process technologies, as well as on the ability to interconnect existing components in a plug-and-play fashion.

With many components communicating with each other on a single chip conventional point-to-point connections will become very cumbersome because the numbers of wires will increase drastically to occupy a substantial part of an ever more expansive silicon area. Moreover, point-to-point connections are often under-utilised (as little as 10% [26]) since they are used to transmit data only for a small percentage of the execution time. Most of the time they are idle. Replacing those connections with a more structural wiring approach where independent communication flows share the same physical resource could increase the overall efficiency of the system.

Although a large part of interconnect logic still consists of wires their electrical properties can be optimized and well controlled. This enables the use of more aggressive signalling techniques to reduce the power consumption by a factor of ten and increase propagation velocity by three times [23]. Wiring resources are shared between many different communication flows making utilization of the wires more efficient. For example, when one client is idle, other clients continue to make use of the network resource. Information sent from one component is encapsulated in packets which are then routed towards their destination in a well-controlled manner.

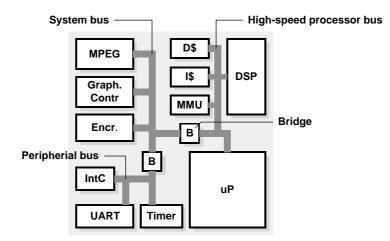

The first step in implementing a structural interconnect system was to adopt a bus architecture similar to standard backplane busses such as VME [81] and PCI [73]. AMBA [4], CoreConnect [19] and Open-Core-Protocol [62] are some of the commercially available solutions from different VLSI vendors. Although on-chip busses provide good connectivity for a small number of components it is clear that as we progress to DSM technologies with billions of transistors and tens or even hundreds of components on a single chip a bus architecture will run out of capacity. The reason for this is the lack of scalability and available bandwidth inherited by a centralised arbitration and a single shared data path, respectively. To overcome these drawbacks there is increasing interest in more sophisticated communication architectures on chips.

*Network-on-a-chip* (NoC) is a new design approach proposed as a solution to future onchip interconnect [7]. The concept is the same as in *local-area-networks* (LANs) and structures communication complexity from the physical implementation up to the application in a number of layers. Each layer provides a different set of services to clients on a common network similar to a *protocol stack* [76]. However, on-chip networks have some characteristics that make their design and implementation unique:

- Off-chip networks emphasize general-purpose communication and modularity and are strongly influenced by standardization and compatibility constraints in legacy network infrastructures. On the other hand, for on-chip networks these constraints are less restrictive because developers design the interconnect on silicon from scratch and are thus able to tailor the network architecture to a specific application.

- On-chip networks have enormous wiring resources at their disposal and it is quite easy to achieve several thousand 'pins' connecting a single IP block [26]. In contrast, off-chip networks are pin limited to far fewer than 1,000 total pins. This large difference allows the designer to trade wiring resources for network performance, making a qualitative difference in network architecture.

- On the other hand silicon area is much more restrictive for NoCs. In particular, storage space is very expensive because general-purpose on-chip memory, such as *Random-Access-Memory* (RAM), occupies a large area. Furthermore, an off-chip network node usually contains dedicated processors to implement a part of the protocol stack in order to relieve a client from communication processing. This may not be feasible for NoCs since it would result in a large proportion of the chip area being occupied by the network logic.

- Energy consumption constraints are specific to on-chip networks since a large proportion of the power in modern VLSI systems is consumed by interconnect [47], while for off-chip networks power dissipation is usually not an issue.

- On-chip networks exhibit much less non-determinism because the traffic characteristics of connected components are well known at design time. This means that almost all management of the network resources can be done at design time, eliminating complex and expensive hardware that provides dynamic resource management during operation.

The adoption of on-chip networks as the solution for future SoCs still raises the question of which clocking strategy to use for the network itself. While local wires scale in length

with a technology, global wires spanning an entire chip do not, which is exactly the situation that leads to clock-skew problems. Managing clock distribution in such a network is problematic at best.

One way to eliminate the clock-skew problem is to use asynchronous logic for the on-chip network implementation. This leaves only the issue of connecting synchronous IP blocks to an asynchronous network. Interfacing clocked and self-timed circuits is a well understood discipline for which standard solutions exist [57]. Furthermore, properties such as low power, improved *electro-magnetic compatibility* (EMC) and robustness deliver additional benefits from the use of self-timed logic for on-chip interconnect.

In an IP block re-use model it is often difficult to adapt individual components to the specific SoC they are used in. They will interact in many different ways (event-driven, data streaming, message passing, shared memory, etc.) [71]. Moreover, some components require guaranteed latency and throughput. For example, a data stream from a camera to an MPEG decoder requires about 1.5 Mbits/s throughput with a continuous transfer rate [58]. A network has to guarantee this throughput for the particular connection even when the traffic reaches saturation point. It is therefore imperative for an on-chip network to be flexible in terms of the services that it offers. The ability of a network to provide guaranteed throughput and latency to specific connections is often referred to as *Quality-of-Service* (QoS).

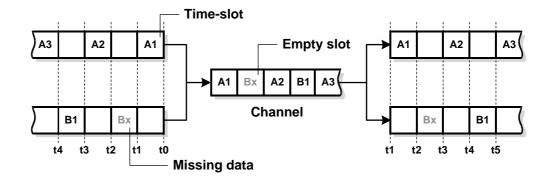

Providing QoS requires careful design at both the circuit and the system level. There are several timing constraints that have to be met in order for a system to operate inside the boundaries of the specifications. In synchronous networks a *time-division-multiplexing* (TDM) [76] technique is usually used to provide the highest level of QoS. TDM partitions the time axis into time-slots where each time-slot presents a unit of time in which a single flow can transmit data over a physical channel. QoS is provided by reserving a proportion of time-slots for a particular connection. For example, if a connection requires 50% of the available bandwidth, a network has to ensure that alternate slots are available for that particular connection.

Asynchronous networks cannot employ a conventional TDM technique because it requires global synchronization between network elements. Thus different solutions have

to be implemented. This thesis presents a detailed summary of research conducted into the feasibility of asynchronous logic providing QoS for on-chip networks.

# 1.1 Thesis overview

Chapter 2 provides an introduction to asynchronous design. The most common self-timed techniques are described and their advantages and disadvantages are discussed. The chapter does not cover all aspects of asynchronous design, but focuses mainly on the asynchronous techniques used later in this thesis. The interested reader is referred to other sources for more detailed descriptions of asynchronous logic design.

The concept of *Quality-of-Service* (QoS) is described in chapter 3. This chapter gives a review of the basic mechanisms used in packet-switched networks to support QoS. It outlines the various approaches that have been proposed, and discusses some of the trade-offs they involve.

The concept of a *Network-on-a-Chip* (NoC) is borrowed from general computer networks [76] where the communication is broken into several layers in order to reduce the complexity of the design. Although the same principles apply to networks at all scales, NoCs have some characteristics that make their design unique. Chapter 4 describes how NoCs differ from their off-chip counterparts.

The following two chapters investigate the issues involved in designing an asynchronous on-chip network with the emphasis on the ability of the interconnect to provide a preferential service for a particular connection (QoS). The chapters follow a top-down approach using the OSI (Open System Interconnection) Reference Model [88] as a framework to abstract the complexity of the interconnect. The chapters deal only with the network-dependent issues of designing an NoC, therefore only the lower two layers of the OSI reference model are described, namely the *network layer* and the *data-link layer*. These two layers are described in chapters 5 and 6, respectively.

Chapter 7 deals with the *physical layer* of an on-chip network. Two problems are addressed, namely power dissipation and synchronization. The chapter also presents a new approach to an on-chip asynchronous transmission system suitable for next-

generation asynchronous on-chip networks. It implements multivalued logic to reduce the number of wires and a low-voltage swing for lower dynamic power dissipation. The proposed signalling scheme is compared to a classical dual-rail signalling system with regard to speed, power consumption and reliability.

As a concrete example of the viability of using an asynchronous on-chip network to support QoS, chapter 8 presents a prototype of an asynchronous NoC router with the ability to provide *guaranteed throughput* and *bounded communication latency*. The architecture of the router is given together with a detailed description of the main components.

Chapter 9 presents an evaluation of the router. Performance metrics include throughput, end-to-end latency and variation in end-to-end delay (jitter). The performance of the router is evaluated in different traffic scenarios. The router is also compared to several different proposals published in the literature.

Finally, chapter 10 completes this thesis with some conclusions about the feasibility of using asynchronous logic to provide a suitable level of QoS in a modern on-chip network. The chapter also discusses some potential areas for improvement.

# 1.2 Research contributions

The work presented in this thesis investigates the ability of asynchronous logic to support *Quality-of-Service* (QoS) for an on-chip network. The result is a prototype of a self-timed on-chip network router with the capability of providing time-related guarantees, such as minimum throughput and bounded communication latency. The QoS architecture presented here is suitable for on-chip implementation because of its low complexity and low area overhead.

The following papers, based on the work presented in this thesis, have been published:

T. Felicijan and S. Furber, "An Asynchronous Ternary Logic Signalling System," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 11, no. 6, pages 1114-1119, December 2003.

- T. Felicijan and S. Furber, "Quality of Service (QoS) for Asynchronous On-Chip Networks," In Formal methods on Globally Asynchronous Locally Synchronous Systems (FMGALS'03), September 2003.

- T. Felicijan, J. Bainbridge and S. Furber, "An Asynchronous Low Latency Arbiter for Quality-of-Service (QoS) Applications," *In Proceedings of the 15th IEEE International Conference on Microelectronics (ICM'03)*, pages 123-126, December 2003.

- T. Felicijan and S. Furber, "An Asynchronous On-Chip Network Router with Quality-of-Service Support (QoS)," *In Proceedings of the IEEE System-on-Chip Conference (SOCC'04)*, pages 274-277, September 2004.

- M. Amde, T. Felicijan, A. Efthymiou, D. Edwards and L. Lavagno, "Asynchronous On-Chip Networks", to appear in the *IEE Journal of Computers and Digital Techniques*.

# Chapter 2: Asynchronous Logic

Asynchronous design has been an active area of research for several decades, however it has yet to achieve widespread use. This chapter examines the benefits and problems of self-timed logic design and introduces some of the more notable design methodologies which are used in this thesis. The interested reader is referred to other sources where extensive information on all aspects of asynchronous design can be found [66][74].

# 2.1 Introduction

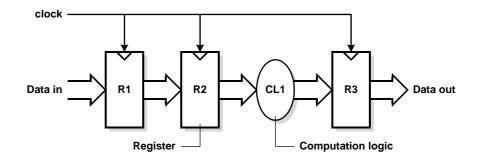

Nowadays the majority of digital chips are based on two fundamental assumptions, namely that all electrical signals are represented as binary variables and that all components share a common and discrete notion of time. Both of these assumption are made in order to simplify the design of logic systems. The binary representation of signals allows the use of Boolean logic to describe and manipulate logic constructs, and the global and discrete notion of time eliminates many of the problems with race conditions and hazards. The systems built under these assumptions are usually referred to as "synchronous". As an example of a synchronous system consider the pipeline shown in figure 2.1.

The propagation of data tokens between the pipeline stages is controlled by the global signal called *clock*. Typically, a rising edge of the clock designates valid data at the input of a pipeline stage while for the rest of the time the data is considered to be invalid. Consequently, the designer must ensure that the worst-case latency of each pipeline stage does not exceed the clock period.

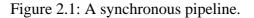

Asynchronous circuits are fundamentally different. Although electrical signals are still considered to be binary, the assumption of a global and discrete notion of time is no longer upheld. In order to perform synchronization and communication between components an asynchronous logic system uses a mechanism called *handshaking*. Instead of distributing a global synchronization signal throughout the chip, handshaking is performed locally between the components which are directly involved in the process of exchanging data, while the rest of the chip remains unaffected by the operation. Figure 2.2 shows an asynchronous implementation of the pipeline presented in the previous example.

Figure 2.2: An asynchronous pipeline.

The clock signal is replaced by a handshaking mechanism implemented in the control logic (CTL) which accompanies each register in the pipeline. In order to perform synchronization between neighbouring stages additional handshaking signals are employed (Req and Ack).

Correct operation of the pipeline is ensured by the following rule: a register may store a new data value (often referred to as a *token*) from the previous stage only when the

following stage has stored the data value the register is currently holding. The states of the previous and the following stages are signalled by the incoming request and acknowledge signals respectively. Note that some of the handshaking protocols use only an acknowledge signal while the request is incorporated into the data value, as explained later in this chapter.

#### 2.1.1 Advantages of asynchronous logic

Although it is very unlikely that asynchronous logic will ever replace the traditional synchronous approach to designing chips, there are some specific design niches where the absence of a global clock has several possible benefits that could make clockless design the optimum choice. This subsection elaborates some of the possible advantages of asynchronous logic design.

#### Clock skew

Clock skew is the difference in arrival times of the clock signal at different parts of the chip. This could violate the assumption that all components share the same notion of time, as noted above. With the advent of deep-submicron technologies clock skew has become one of the main problems in VLSI design. It is expected that by the end of this decade the latency to transmit a signal across a chip will vary between 12 and 35 clock cycles [3].

With careful design of the clock distribution network it is possible to mitigate the clock skew problem. However, solutions such as balanced clock trees [83] require a lot of additional design effort and are expensive in terms of silicon area and power consumption.

Due to the absence of a global clock an asynchronous system does not suffer from the clock skew problem and the increasing complexity of the clock distribution network.

#### Power dissipation

Synchronous circuits have to toggle clock lines, and possibly precharge and discharge signals, in parts of a circuit which may not be involved in the current operation. For

example, even though a floating-point unit in a processor may not be used in a given instruction, the unit must still be driven by the clock. Note that there are techniques being used in synchronous designs to address this problem, however the implementation of such techniques is not straightforward and requires additional control logic.

On the other hand, asynchronous systems dissipate power only when they perform a certain function while they exhibit zero power consumption when they are idle. Furthermore, the power dissipation is localized to the parts of a system which are actively involved in the current computation. Consequently, asynchronous systems have zero stand-by power consumption. Note that this is true only if the leakage currents of an asynchronous system are small enough to be negligible.

#### Average-case performance

The highest possible clock frequency of a synchronous system is limited by the worst-case combination of the following parameters:

- power supply variation,

- temperature,

- transistor speed determined by the silicon process,

- data-dependent operation time. For example, a ripple-carry adder can perform an addition with a short carry propagation distance faster than one with a long carry propagation distance.

Asynchronous circuits automatically adjust their speed of operation according to the current conditions because they are not restricted by the fixed clock frequency. As long as the worst-case combination of the parameters listed above occurs infrequently asynchronous circuits provide better than worst-case performance.

### Modularity

The most common way to improve the performance of a synchronous system is to increase the frequency of the global clock. Unfortunately this usually requires most of the system to be redesigned. In contrast, increasing the performance of an asynchronous system can be achieved by modifying only the most active part of the circuit. The only constraint a designer has to observe is that the communication protocol between the module being replaced and the rest of the system remains the same.

### Electro-magnetic compatibility (EMC)

The global synchronization mechanism implemented in synchronous systems causes most of the switching activity to occur at the same time. This concentrates the radiated energy at the harmonics of the clock frequency.

Asynchronous circuits produce distributed interference spread across the entire frequency spectrum because the local clock signals tend to tick at random points in time. In systems which use radio communication this can be a significant advantage.

### 2.1.2 Disadvantages of asynchronous logic

However, asynchronous logic also has several disadvantages, compared to synchronous logic, which have prevented its widespread use in industry.

### Complexity and lack of CAD tools

In essence, asynchronous circuits are more difficult to design than synchronous circuits. By implementing the global clock, a designer only needs to ensure that the processing of every stage finishes before the next rising edge of the clock signal. The global clock eliminates hazards (undesired signal transitions) and a designer does not have to worry about the dynamic state of the circuit.

In asynchronous systems a great deal of attention has to be given to the dynamic state of the circuit. Hazards have to be removed, or not introduced in the first place, in order to avoid an incorrect result and the ordering of operations has to be carefully ensured by the asynchronous control logic.

For complex systems, these issues become too difficult to be handled manually, therefore CAD tools have to be used in order to ensure correct designs. Unfortunately, asynchronous circuits in general cannot employ existing CAD tools that have been developed for synchronous systems. The lack of suitable CAD tools is probably the main reason that asynchronous logic design still remains mostly in the domain of academic research.

### Testability

The requirement for very high reliability of electronics systems is no longer limited to critical applications in military, aerospace or nuclear industries, where failures can have catastrophic consequences. Today, electronic systems are rigorously tested to ensure that the design implemented in silicon is free of manufacturing defects.

Testing for fabrication faults in asynchronous systems is harder because of the non deterministic elements, such as arbiters, used in the design. Furthermore, asynchronous systems tend to contain much more information than synchronous systems. As well as pipeline latches, every handshake circuit contains memory elements which have to be accounted for during the test process.

# 2.2 Asynchronous design methodologies

Asynchronous design methodologies can be broadly classified into two main categories according to the timing models they assume: bounded-delay and unbounded-delay. The *bounded-delay* model assumes that the delay in all circuit elements and wires is known, or at least bounded. In this model, circuits are designed in a similar way to synchronous circuits, and this approach was widely used in the early days of asynchronous design.

However, modern asynchronous designs use the *unbounded-delay* model where the delay of logic gates and wires is generally unknown and control circuits and state machines are designed to operate correctly regardless of the distribution of delays. The bounded-delay

model may still be used for data-path components because it generally leads to smaller implementations. Throughout this thesis only the unbounded-delay model is used, therefore the rest of this chapter focuses on this particular model of asynchronous systems.

Within the unbounded-delay model asynchronous circuits can be classified into several sub-groups according to the number of assumptions they make on gate and wire delays. The following subsections briefly explain the main sub-groups.

#### 2.2.1 Delay-insensitive circuits

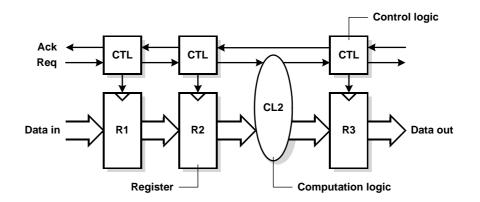

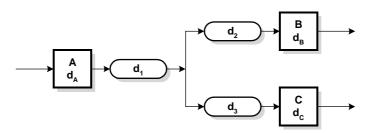

Delay-insensitive (DI) circuits represent the most robust model for designing asynchronous circuits where arbitrary delays are assumed for both logic elements and wires. Figure 2.3 shows an example of a circuit fragment with gate and wire delays.

Figure 2.3: Circuit fragment with gate and wire delays.

Three logic gates A, B and C with gate delays  $d_A$ ,  $d_B$  and  $d_C$ , respectively are shown. The output of gate A is forked to inputs of gates B and C and wires comprising the fork have delays designated as  $d_1$ ,  $d_2$ , and  $d_3$ . If the circuit operates correctly for arbitrary values of  $d_A$ ,  $d_B$ ,  $d_C$ ,  $d_1$ ,  $d_2$ , and  $d_3$  then it is said to be delay-insensitive. Unfortunately, the range of true DI circuits that can be implemented in CMOS is very limited, as proved by Martin [56].

#### 2.2.2 Quasi delay-insensitive circuits

Quasi delay-insensitive (QDI) circuits were introduced to alleviate some of the constraints set by DI circuits in order to broaden the range of the circuits that can be implemented in

a CMOS technology. The delay of gates and wires is still considered to be arbitrary, however QDI circuits assume that the delays of all ends of a forking wire are identical. Referring to figure 2.3 this means that  $d_2$  equals  $d_3$  while all the rest of the values ( $d_A$ ,  $d_B$ ,  $d_C$  and  $d_1$ ) are still arbitrary. If the delays of a forking wire are the same, the wire-fork is said to be *isochronic* [54].

Clearly, the identical delays of all ends of a forking wire are virtually impossible to achieve in a real-life design. However, if the difference in delays of forking branches is shorter than the delays in the gates to which the fork is an input  $(|d_2 - d_3| \ll d_B, d_C)$  the wire-fork may be considered as isochronic.

#### 2.2.3 Speed-independent circuits

In speed-independent (SI) circuits wire delay is considered to be negligible compared to gate delay while gate delays exhibit arbitrary values. The circuit in figure 2.3 is speed-independent if it performs correct operation for arbitrary values of  $d_A$ ,  $d_B$  and  $d_C$ , while  $d_1$ ,  $d_2$  and  $d_3$  are assumed to be insignificant ( $d_1$ ,  $d_2$ ,  $d_3 \ll d_A$ ,  $d_B$ ,  $d_C$ ). The SI assumption is valid for small circuits where all the wires are very short.

# 2.3 Handshaking protocols

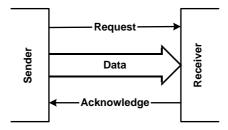

Handshaking is the mechanism that controls the flow of data tokens between the components of an asynchronous system. The mechanism has to ensure that data tokens progress from one component to the next in a well controlled manner without clashing with each other. Figure 2.4 shows an example of an interface between two asynchronous components which communicate using a handshaking protocol.

Figure 2.4: An asynchronous communication channel.

In addition to data wires two signals, namely request and acknowledge, are used to negotiate the transfer of data from a sender to a receiver. A set of wires comprising the interface is usually referred to as a channel. Figure 2.4 illustrates a typical *push channel* where the sender issues a request signal when it has data to transmit. The receiver acknowledges the reception of the data by sending an acknowledge signal back to the sender. Sometimes a *pull channel* is used in asynchronous systems (not shown in the figure) where, instead of the sender, the receiver initiates the transaction cycle by issuing a request signal when it is ready to accept new data.

The request and acknowledge between components may be passed using one of two handshaking protocols: a two-phase transition signalling protocol, sometimes referred to as a non return-to-zero protocol, or a four-phase level signalling protocol, also called a return-to-zero protocol.

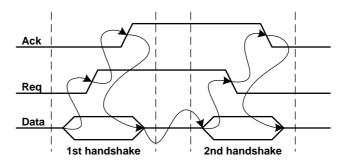

### 2.3.1 Non return-to-zero handshaking protocol

A *non return-to-zero* (NRZ) handshaking protocol [65] exchanges information using transitions of signals with rising edges equivalent to falling edges. If Req and Ack wires are assumed both to be low initially, then the sequence of events shown in figure 2.5 illustrates a waveform of an NRZ handshaking protocol using a push channel. Note that other initializations are also possible, and in particular it is not essential for the wires to start in the same state.

Figure 2.5: Non return-to-zero handshaking protocol.

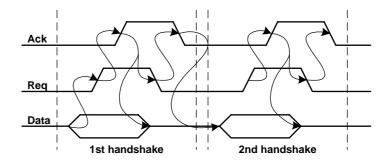

#### 2.3.2 Return-to-zero handshaking protocol

A *return-to-zero* (RTZ) handshaking protocol (four-phase signalling) [65] uses the level of signals to indicate when data is valid and when it has been acknowledged by the receiver. This scheme requires every signal used in the protocol to return to its origin (zero) state before the next transaction cycle may commence. Compared to NRZ signalling, an RTZ protocol uses twice as many transitions which leads to higher power consumption, however it often results in smaller control logic. Figure 2.6 shows a waveform of an RTZ protocol with a push channel.

Figure 2.6: Return-to-zero handshaking protocol.

# 2.4 Data encoding

In synchronous systems data is typically represented using a binary encoding scheme where each wire represents a single bit of information. In a positive logic system a  $V_{DD}$  voltage level on a signal represents logic 1 and  $V_{SS}$  represents logic 0. In addition to the single-rail encoding scheme, several others are very popular in asynchronous design.

### 2.4.1 Single-rail encoding

In a single-rail encoding scheme (also known as the *bundled-data* approach) data is represented in the same way as in a conventional synchronous system where each wire carries a single bit of information. Typically, a  $V_{DD}$  voltage level represents logic 1 and  $V_{SS}$  represents logic 0. Timing information is passed using additional request and acknowledge signals to allow for the synchronization between the sender and the receiver. The single-rail encoding scheme relies on one timing assumption, namely that the delay in the request signal must be no less than the delay in the corresponding data path.

Single-rail encoding is very popular among asynchronous designers because it results in similar area requirements to those of synchronous counterparts. Furthermore, the construction of a data-path can be done using conventional synchronous tools. However, the main drawback with single-rail encoding is that extra design effort is required in order to verify that the delays of request signals match the delays of data signals under all possible manufacturing conditions.

### 2.4.2 Delay-insensitive encoding

A code is *delay-insensitive* (DI) if it enables the receiver to unambiguously detect the complete code symbol sent by the transmitter [80]. An informal requirement for a code to be delay-insensitive is that no code symbol is contained in any other code symbol. A delay-insensitive code adds redundancy to the data so that validity information is carried along the data in the data-path. This means that the request signal is no longer required because it is implicit in the data. However, additional hardware is required at the receiver's end to detect incoming symbols.

An example of a delay-insensitive code is *one-hot* encoding where only a single wire is active at any given time. In order to transmit n bits of information  $2^n$  wires are required and a valid code symbol is represented by an active signal on one of those wires. The most common DI codes in asynchronous design are *dual-rail* and *one-of-four*.

### **Dual-rail encoding**

Dual-rail encoding uses two wires to represent a single bit of information. Typically, (0,0) indicates an empty code symbol, (0,1) and (1,0) represent logic 0 and logic 1, respectively. Note that the (1,1) combination of inputs is not used and represents an illegal code symbol.

The main problem with dual-rail encoding (and delay-insensitive design in general) is that it results in a larger area overhead than conventional single-rail circuits. Furthermore, dual-rail circuits tend to dissipate more power than their single-rail counterparts because of the increased switching activity as a result of the duplication of logic function for the true and complement cases.

#### One-of-four encoding

A one-of-four encoding scheme represents a possible solution to reduce the switching activity of a delay-insensitive system. In this case four wires are used to transmit two bits of information in parallel using one active signal to designate a valid code symbol. Combination (0,0,0,0) represents the empty code symbol, while combinations (0,0,0,1), (0,0,1,0), (0,1,0,0) and (1,0,0,0) represent numbers 0, 1, 2 and 3, respectively.

It can be observed that one-of-four encoding generates roughly 50% fewer signal transitions than dual-rail encoding when transmitting two bits of information, while the area requirement remains almost the same. Note that two dual-rail channels have to be used in order to transmit two bits of information in parallel.

### N-of-M encoding

Dual-rail encoding and one-of-four encoding are simply two examples of an N-of-M encoding scheme where N = 1. Other schemes where N > 1 are also delay insensitive and offer better wire utilization than one-hot encoding schemes. For example, a two-of-seven code employs seven wires to transmit four bits of information using only two active signals per symbol. Compared to dual-rail encoding, where eight wires are required to transmit the same number of bits using four active signals per symbol, the two-of-seven code clearly has the utilization advantage. However, the problem with N-of-M encoding schemes is that they result in larger arithmetic and completion detection circuits that make them unattractive for implementation on silicon.

# 2.5 The Muller C-element

As opposed to a synchronous circuit where the signal levels are interpreted only at discrete points in time dictated by the global clock, an asynchronous circuit is an event driven

system where a signal transition represents an event which may trigger subsequent transitions at any point in time. Typically, an asynchronous system waits for a particular transition (or sequence of transitions) to occur before changing its state and producing a new set of outputs. Consequently, the signal is not allowed to exhibit unwanted transitions (glitches) as they may be interpreted as valid events by the system. Similarly, the system itself has to ensure that every output signal transition has a meaning, and hazards and races must be avoided.

In the design of DI circuits the concept of *indication* and *acknowledgment* has been introduced where every signal transition should be acknowledged by other signal transitions to avoid hazards. As an example consider a two-input OR gate. When the output of the gate changes from 1 to 0 an observer may conclude that both inputs are now at 0. However, when the output changes from 0 to 1 the observer cannot make conclusions about both inputs as they may be in any of the following states: (0, 1), (1, 0) or (1, 1). Consequently, the OR gate only indicates when both inputs are 0. Similarly, it can be seen that an AND gate only indicates when both inputs are 1.

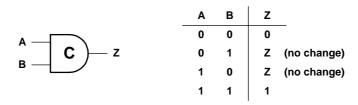

An important asynchronous primitive that is much better in this respect is the Muller Celement. Figure 2.7 shows a symbol of a symmetric two-input C-element and its truth table. When both inputs are 0 the output is set to 0, and when both inputs are 1 the output is set to one. For other input combinations the output does not change. Consequently, when the output changes its state from 0 to 1 or from 1 to 0, an observer may conclude that both inputs are now at 1 or 0, respectively.

Figure 2.7: A C-element and its truth table.

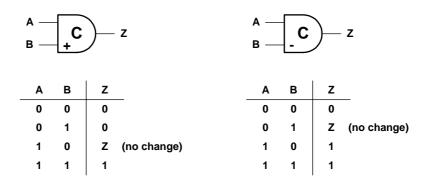

In addition to the symmetric C-element where the output changes state only when all inputs have the same value, several asymmetric variants of a C-element are possible. In an asymmetric C-element some input signals may affect only the rising or the falling edge of the output signal, but not both. Figure 2.8 shows some examples of asymmetric Celements with corresponding truth tables.

Figure 2.8: Asymmetric C-elements and corresponding truth tables.

# 2.6 Metastability

Often, asynchronous systems require that several inputs are mutually exclusive. If the environment does not ensure this property the system has to perform asynchronous arbitration upon the particular inputs. As the inputs may change at any point in time the system may become metastable.

Metastability is a situation that arises when a bistable system has to determine the ordering of two asynchronous inputs that occur in a very close time proximity [14]. When this happens it may take an indefinite amount of time for the system to resolve the situation, during which the state of the output may be neither a 0 nor a 1, but somewhere in between.

The same situation may also occur in a synchronous system when an asynchronous input does not satisfy the set-up and hold time requirements of the clocked flip-flop used to sample the input. The problem is usually accommodated by waiting for a predefined number of clock cycles before using the output of the flip-flop. However, there is always a chance that the system will fail because the output of the bistable element may still be metastable when its outputs are used. With careful engineering the probability of failure can be reduced to a very low level, although it is not possible to eliminate the possibility of failure entirely.

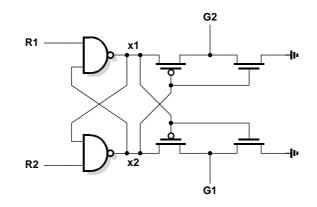

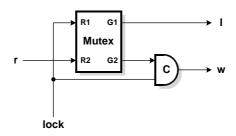

In asynchronous systems the problem of metastability is solved using an alternative approach of waiting until the metastability has resolved and the outputs have settled to a defined logic value, 0 or 1, before allowing the values to pass into the rest of the system. The operation of determining which event occurred first is called *arbitration* and is typically performed using a *mutex* structure proposed by Seitz [70]. Figure 2.9 shows a CMOS implementation of a mutex.

Figure 2.9: CMOS implementation of a mutex.

The cross-coupled NAND gates enable one input to block the other. If both inputs arrive at approximately the same time the circuit becomes metastable with both outputs x1 and x2 somewhere between  $V_{DD}$  and ground. The metastability filter prevents these undefined values from propagating to the outputs until the metastability has resolved. *G1* and *G2* are kept low until signals x1 and x2 differ by more than a transistor-treshold voltage.

Although the arbitration may take an unbounded time, in practice the probability of a bistable element remaining in a metastable state for a long period of time is insignificant.

# 2.7 Large-scale asynchronous design

As mentioned before it is unlikely that asynchronous logic will ever completely replace clock driven designs. However, there are several industrial groups that have established

themselves in the VLSI market as vendors of self-timed logic in recent years. The following sections introduce the main industrial players in the field of asynchronous design.

#### Handshake Solutions

Handshake Solutions started life as a Philips Research project in 1986. Over the last ten years the company has worked within Philips to develop a design methodology based on self-timed logic suitable for a commercial IC design environment.

The company recently introduced smart card controllers for use in electronic passport (ePassport) applications (SmartMX ICs) [37]. The ICs embedded in ePassports must have a contactless interface and incorporate large amounts of on-board memory to store biometric data. Because of its ultra-low-power clockless design, SmartMX can support these large memories without exceeding the limited power budget of contactless applications.

#### Fulcrum Microsystems

Founded in January 2000, Fulcrum Microsystems is building on research conducted at Caltech (California Institute of Technology) by the company's founding team. The company has developed a clockless design methodology that deliveres high-performance while maintaining power efficiency, and reliable operation over a wide range of operating conditions.

One of Fulcrum's most recent chips, a Terabit crossbar circuit fabricated in TSMC's 130 nm process [52], delivers performance, comparable to aggressive full-custom synchronous designs, over a wide voltage range (well beyond the operating range of synchronous designs).

### **Theseus Logic**

Theseus Logic began its operations in 1996, as a Semiconductor Intellectual Property company, dedicated to the design of clockless ICs using NULL Convention Logic<sup>™</sup> (NCL) [29]. NCL offers several advantages over conventional design approaches including: power management, reduced noise and high security, improved reliability and testability. Theseus Logic delivers solutions to many of the critical design issues facing the semiconductor industry as it marches towards smaller geometries and higher levels of integration.

#### Sun Microsystems

Sun Microsystems was one of the first companies that has acknowledged asynchronous circuits as an important element for future VLSI systems. The Asynchronous Design Group at Sun Microsystems develops high-speed circuit technologies and design methods that enable novel architectures. Their circuit technologies include asynchronous circuits, low-power circuits, and communication links. Their design methods incorporate intellectual tools and computer-aided design tools to help with circuit design, implementation, and test.

# 2.8 Summary

There are many possible reasons for considering asynchronous design. However, no single application has been identified which would make its use mandatory. This chapter has presented several advantages of asynchronous techniques, namely low power, low electromagnetic interference, modularity, etc. which are all applicable in their own niches, but modularity is the main argument for the use of self-timed design in this thesis. The reason for this is an increasing interest in GALS (Globally Asynchronous Locally Synchronous) system design that supports a heterogeneous timing environment. An asynchronous on-chip interconnect is used to connect synchronous modules which can be kept small in order to contain the clock-skew problem.

# Chapter 3: Quality-of-Service (QoS)

A modern *System on a Chip* (SoC) design consists of many different components and IP blocks interconnected by an on-chip network. These components can exhibit disparate traffic characteristics and constraints, such as requirements for guaranteed throughput and bounded communication latency. It is therefore essential for an on-chip network to support guaranteed services in order to accommodate such components sharing the same communication medium.

This chapter gives a review of the basic mechanisms used in packet switched networks to support *Quality-of-Service* (QoS). It outlines the various approaches that have been proposed, and discusses some of the trade-offs they involve.

# 3.1 Introduction

*Quality-of-Service* (QoS) is a term used in communication networks that refers to a capability of a network to provide better service for selected traffic or a selected connection over the network. The primary goal of QoS is to make dedicated bandwidth, bounded latency, and improved loss characteristics applicable to selected traffic. Furthermore, a QoS mechanism has to be able to allocate the residue of the physical bandwidth which is not used by high-priority connections to the rest of the traffic.

For example, a video data stream from a camera to an MPEG encoder is entirely static and requires high-bandwidth with predictable delay. This entirely static traffic has to share the network resources with dynamic traffic, such as processor memory references, that cannot be predicted before run-time. QoS has to guarantee this throughput for the particular connection even when the network traffic reaches saturation point.

#### 3.1.1 QoS: a user's view

A user expects applications to display a certain behaviour; in other words they must be predictable. While those expectations may be low, a certain level of fitness is always assumed. For example, a television set requires a robust user interface and is not allowed to crash or be unresponsive. Expectations are even stricter for real-time applications (e.g. involving audio and video, or control systems); a television set must be able to display 50 constant quality pictures per second, for example. The essence of QoS is therefore the offering of a predictable system behaviour to the user.

# 3.2 Basic QoS architecture

There are three fundamental aspects of QoS architecture:

- *QoS identification*. In order to provide preferential service for a specific connection or a type of traffic, it must first be identified. To identify QoS packets, the header packet has to contain information about the class of QoS that it belongs to.

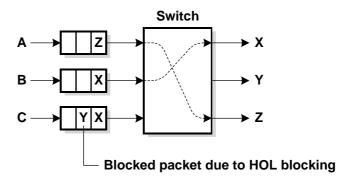

- *QoS within a single network element*. Routing, scheduling, buffering and flowcontrol provide QoS within a network element. When a packet arrives at a network node all those mechanisms have to meet the QoS demand to provide the required service for the connection.

- *QoS policy and management* is a set of methods to determine whether the current traffic characteristics of the network allow for a new QoS connection to be established. When a QoS technique has been deployed to target the particular traffic, QoS management has to test whether QoS goals have been reached. In local area networks (LANs) and wide area networks (WANs) this is an ongoing process while for on-chip networks QoS policy and management is usually conducted only once during the design process.

# 3.3 End-to-end QoS levels

A level of QoS is typically specified on an *end-to-end* basis. This means that both the hosts at each end of a connection have to satisfy QoS requirements as well as the network

connecting them. This thesis only focuses on the QoS requirements for the network (although many of the ideas could be applied to the hosts). The requirements are specified as a set of QoS parameters which include peak-to-peak cell delay variation (jitter), maximum cell transfer delay and cell loss ratio. According to these parameters network services can be classified as follows:

- *Best-effort (BE)* services make no commitments about QoS. They refer to the basic connectivity with no guarantees. An example of such a service is first-in, first-out (FIFO), or first-come, first-served (FCFS) scheduling.

- *Differentiated* services, also known as soft QoS, partition network traffic into several classes each with different requirements regarding data delivery. Packets are treated according to the class they belong to. Still no hard guarantees are made for individual flows.

- *Guaranteed Throughput (GT)* services ensure each flow has a negotiated bandwidth regardless of the behaviour of all other traffic. Multiple GT connections can share the same physical link if the probability that the aggregate traffic will reach the sum of the peak rates is small enough to satisfy loss characteristic requirements. An example of such a scheme is *weighted fair queuing* (WFQ).

- *Bounded Delay Jitter* services guarantee upper and lower bounds on observed packet delays. An example of such a scheme is circuit switching with *time division multiplexing* (TDM).

# 3.4 QoS control methods

Now that we know what QoS is, how do we achieve it? Unfortunately, no single technique provides efficient, dependable QoS in an optimum way. Instead, a variety of techniques have been developed, with practical solutions often combining several of them. This section examines some of the techniques system designers use to achieve QoS.

## 3.4.1 Overprovisioning

A simple solution is to provide so much network capacity in terms of bandwidth and buffer space that the traffic never reaches the saturation point. Unfortunately this is a very expensive solution and often not practical. To some extent, the telephone system is overprovisioned. It is very rare to pick up a phone and not get a dial tone instantly. There is simply so much capacity available that demand can always be met.

## 3.4.2 Buffering

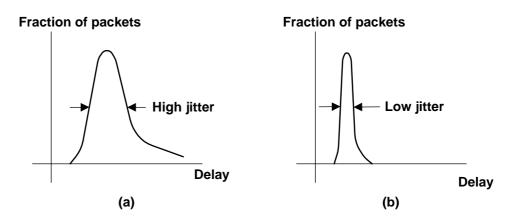

For audio and video streaming applications the variation (i.e., standard deviation) of the packet arrival time (often called *jitter*) is the main problem. High jitter, for example, where some packets arrive in 20 ms and others in 30 ms, will give an uneven quality to the sound or movie. Figure 3.1 illustrates jitter.

Figure 3.1: High jitter (a) and low jitter (b).

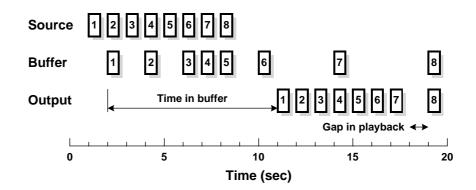

To smooth out the jitter designers often use buffers at the receiving end of a connection. Figure 3.2 shows an example of a stream of packets being delivered with substantial variation of packet delivery time. Packet 1 is sent from the server at t = 0 s and arrives at the client at t = 1 s. Packet 2 undergoes more delay and takes 2 s to arrive. As the packets arrive they are buffered on the client machine.

At t = 10 s, playback begins. At that time, packets 1 through 6 have been buffered and can be removed from the buffer at uniform intervals for smooth playback. The example shows

Figure 3.2: Resolving jitter by buffering packets.

that packet 8 has been delayed so much that it is not available for playback when its play slot comes up. This interrupts the playback until the packet arrives, creating an unwanted gap in the music or movie. This problem can be alleviated by further delaying the start of the playback at the expense of a larger buffer.

## 3.4.3 Traffic shaping

In the above example the source generates uniformly distributed traffic, but very often traffic is of a bursty nature which may cause congestion to occur in the network. Traffic shaping techniques smooth out the traffic at the source side, rather than at the client side, by regulating the average rate and burstiness of data transmission. There are several different traffic shaping techniques, however they are mostly variations of the *leaky bucket* rate control mechanism originally proposed by Turner [78].

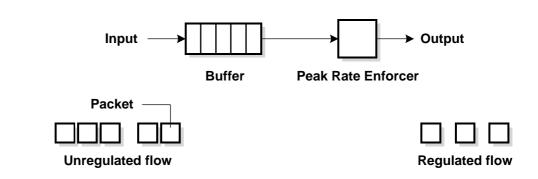

Figure 3.3 shows the principle of the leaky bucket mechanism. It consists of a finite data buffer and a peak rate enforcer. Packets enter the leaky bucket from the source and are queued in the data buffer until they are forwarded to the network. If the buffer is full at the time when a new packet arrives, the packet is discarded. The peak rate enforcer releases packets to the network at a constant rate (usually one packet per clock tick) thus generating a smooth flow of data at the input of the network. This prevents congestion in the network and consequently improves QoS.

Figure 3.3: Leaky bucket mechanism.

#### 3.4.4 Resource reservation

Although buffering and traffic shaping can improve end-to-end service they cannot guarantee minimum throughput and/or bounded communication latency for a particular connection. One approach to offer completion bounds (e.g. for a bounded communication latency) is to make absolute reservation of network resources, such as bandwidth and buffer space.

## Circuit switching and time division multiplexing

Traditional circuit switching is characterized by absolute reservation of network resources for a particular connection. Circuit switching requires a physical path to be established between a sender and a receiver prior to the transmission of the data packets. Once the path is set the sender has all the bandwidth of the connection available to send packets to the receiver. Absolute reservation of the bandwidth eliminates the necessity to buffer the packets as they propagate through the network. The main advantage of this scheme is that it simplifies the problem of making deterministic guarantees. However, circuit switching may provide very inefficient use of the bandwidth if the average throughput of the connection is much lower than the physical bandwidth.