# SPATIAL PARALLELISM IN THE ROUTERS OF ASYNCHRONOUS ON-CHIP NETWORKS

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2011

By Wei Song School of Computer Science

# Contents

| Ał | ostrac | et                            | 16 |

|----|--------|-------------------------------|----|

| De | eclara | ation                         | 17 |

| Co | opyrią | ght                           | 18 |

| Ac | know   | vledgements                   | 19 |

| Th | ne Au  | thor                          | 20 |

| I  | Int    | roduction and Background      | 21 |

| 1  | Intr   | oduction                      | 22 |

|    | 1.1    | Motivation                    | 22 |

|    | 1.2    | Research objectives           | 24 |

|    | 1.3    | Research contributions        | 25 |

|    | 1.4    | Thesis organization           | 26 |

|    | 1.5    | Publications                  | 27 |

| 2  | Asy    | nchronous Circuits            | 29 |

|    | 2.1    | General description           | 29 |

|    | 2.2    | Delay assumptions             | 30 |

|    |        | 2.2.1 Delay-insensitive       | 30 |

|    |        | 2.2.2 Quasi-delay-insensitive | 30 |

|    |        | 2.2.3 Speed-independent       | 31 |

|    |        | 2.2.4 Relaxed QDI             | 31 |

|    |        | 2.2.5 Self-timed              | 31 |

|    | 2.3    | Handshake protocols           | 32 |

|   |      | 2.3.1   | 4-phase                                  | 32 |

|---|------|---------|------------------------------------------|----|

|   |      | 2.3.2   | 2-phase                                  | 33 |

|   | 2.4  | Data e  | ncoding                                  | 34 |

|   |      | 2.4.1   | Bundled-data                             | 34 |

|   |      | 2.4.2   | Multi-rail                               | 35 |

|   | 2.5  | Perfor  | mance comparison of pipelines            | 40 |

|   | 2.6  | Arbite  | r                                        | 42 |

|   |      | 2.6.1   | Multi-way MUTEX arbiter                  | 42 |

|   |      | 2.6.2   | Tree arbiter                             | 43 |

|   |      | 2.6.3   | Ring arbiter                             | 44 |

|   |      | 2.6.4   | Static priority arbiter                  | 46 |

|   | 2.7  | Alloca  | ttor                                     | 47 |

|   |      | 2.7.1   | Virtual channel admission control        | 47 |

|   |      | 2.7.2   | Multi-resource arbiter                   | 48 |

|   | 2.8  | Summ    | ary                                      | 50 |

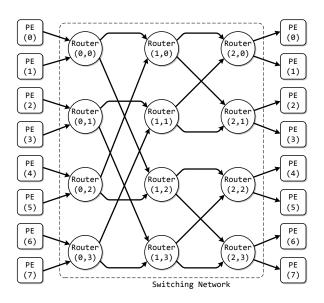

| 3 | Netv | vork-or | ı-Chip                                   | 51 |

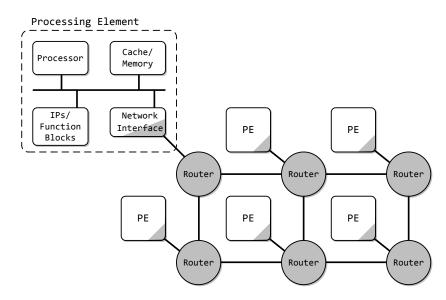

|   | 3.1  | Conce   | pts of on-chip networks                  | 51 |

|   | 3.2  | Topolo  | Dgy                                      | 53 |

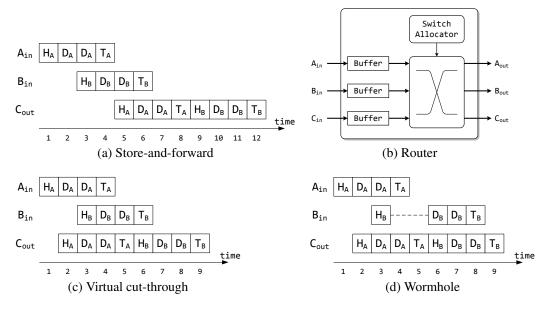

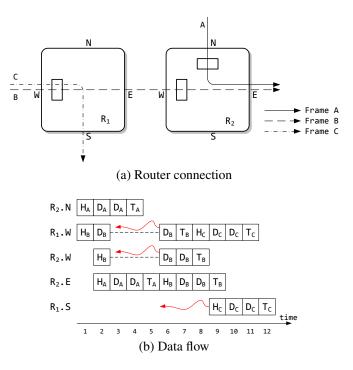

|   | 3.3  | Flow c  | control                                  | 55 |

|   |      | 3.3.1   | Circuit switched and packet switched     | 55 |

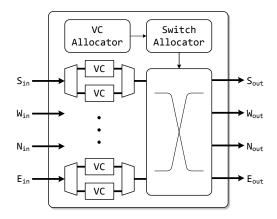

|   |      | 3.3.2   | Virtual channel                          | 58 |

|   |      | 3.3.3   | Other flow control methods               | 61 |

|   |      | 3.3.4   | Quality of service                       | 61 |

|   | 3.4  | Routin  | ng algorithm                             | 62 |

|   |      | 3.4.1   | Deterministic and non-deterministic      | 62 |

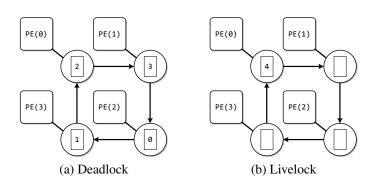

|   |      | 3.4.2   | Deadlock and livelock                    | 65 |

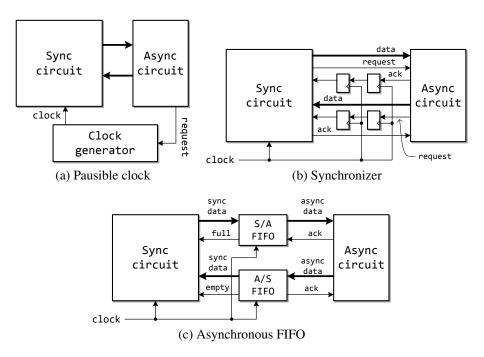

|   | 3.5  | Global  | lly asynchronous and locally synchronous | 66 |

|   | 3.6  | Previo  | us GALS NoCs                             | 69 |

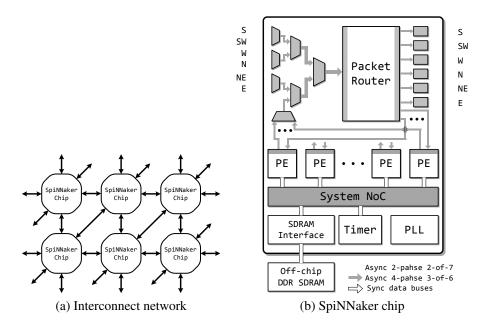

|   |      | 3.6.1   | SpiNNaker                                | 69 |

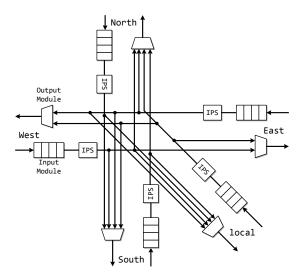

|   |      | 3.6.2   | ASPIN                                    | 70 |

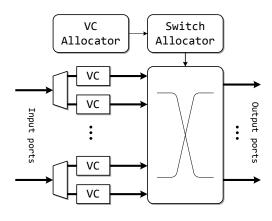

|   |      | 3.6.3   | QoS NoC                                  | 71 |

|   |      | 3.6.4   | ANOC                                     | 72 |

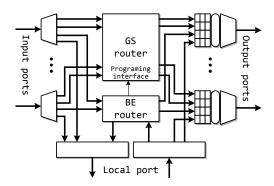

|   |      | 3.6.5   | MANGO                                    | 73 |

|   |      | 3.6.6   | QNoC                                     | 74 |

|   | 3.7  | Summ    | ary                                      | 75 |

| II | Le   | evels of Parallelism                               | 76  |

|----|------|----------------------------------------------------|-----|

| 4  | Para | allelism in the Physical Layer                     | 77  |

|    | 4.1  | Synchronization overhead                           | 77  |

|    | 4.2  | Channel slicing                                    | 79  |

|    | 4.3  | Lookahead pipeline style                           | 81  |

|    | 4.4  | A channel sliced wormhole router                   | 84  |

|    |      | 4.4.1 Router structure                             | 85  |

|    |      | 4.4.2 Performance                                  | 89  |

|    | 4.5  | Summary                                            | 91  |

| 5  | Para | allelism in the Switching Layer                    | 93  |

|    | 5.1  | Problems of the virtual channel flow control       | 94  |

|    | 5.2  | Spatial division multiplexing                      | 96  |

|    | 5.3  | An SDM router                                      | 99  |

|    |      | 5.3.1 Router structure                             | 99  |

|    |      | 5.3.2 Performance                                  | 102 |

|    | 5.4  | Behavioural level comparison                       | 102 |

|    |      | 5.4.1 Models for wormhole and SDM routers          | 103 |

|    |      | 5.4.2 Model for VC routers                         | 109 |

|    |      | 5.4.3 Performance analyses                         | 110 |

|    | 5.5  | Summary                                            | 116 |

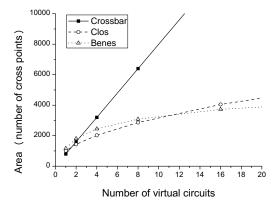

| 6  | Area | a Reduction using Clos Networks                    | 118 |

|    | 6.1  | Clos switching networks                            | 118 |

|    | 6.2  | Dispatching algorithm                              | 122 |

|    |      | 6.2.1 Concurrent round-robin dispatching algorithm | 122 |

|    |      | 6.2.2 Asynchronous dispatching algorithm           | 124 |

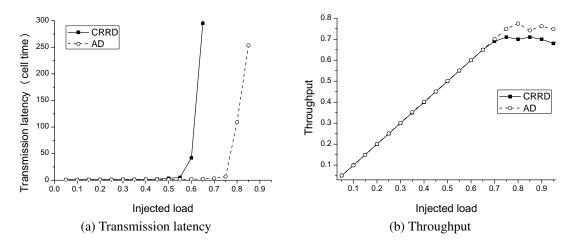

|    |      | 6.2.3 Performance of CRRD and AD                   | 128 |

|    | 6.3  | Asynchronous Clos scheduler                        | 131 |

|    |      | 6.3.1 Implementation                               | 132 |

|    |      | 6.3.2 Performance                                  | 139 |

|    | 6.4  | 2-stage Clos swtich                                | 142 |

|    | 6.5  | Summary                                            | 144 |

###

| Π  | I P   | erforr  | nance Evaluation and Conclusion                  | 145   |

|----|-------|---------|--------------------------------------------------|-------|

| 7  | An    | Asynch  | ronous SDM Router                                | 146   |

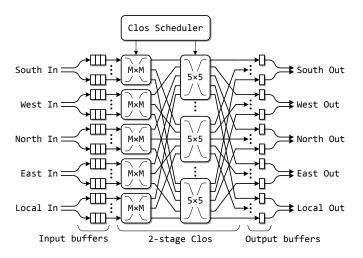

|    | 7.1   | Route   | r structure                                      | . 146 |

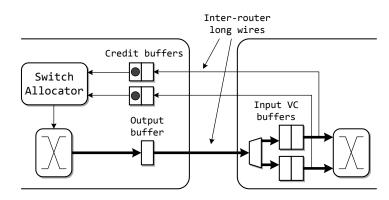

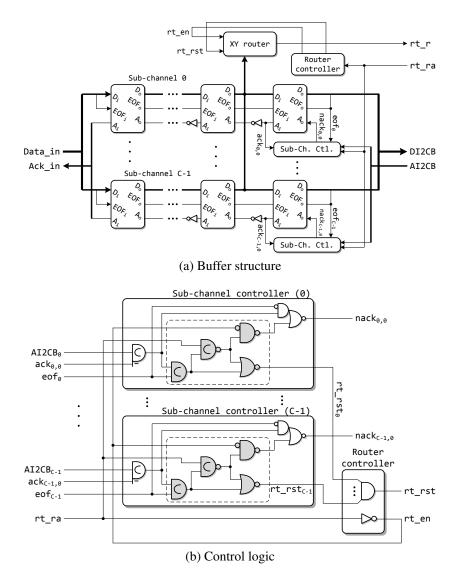

|    |       | 7.1.1   | Input and output buffers                         | . 147 |

|    |       | 7.1.2   | 2-stage Clos switch for SDM routers              | . 149 |

|    | 7.2   | Imple   | mentation                                        | . 151 |

|    |       | 7.2.1   | Implementation detail                            | . 151 |

|    |       | 7.2.2   | Area consumption                                 | . 153 |

|    |       | 7.2.3   | Router speed                                     | . 154 |

|    | 7.3   | Summ    | nary                                             | . 156 |

| 8  | Perf  | orman   | ce Evaluation                                    | 157   |

|    | 8.1   | Single  | e router evaluation                              | . 157 |

|    |       | 8.1.1   | Test environment                                 | . 157 |

|    |       | 8.1.2   | Performance                                      | . 159 |

|    | 8.2   | Netwo   | ork performance                                  | . 165 |

|    |       | 8.2.1   | Mesh network with uniform traffic                | . 165 |

|    |       | 8.2.2   | An MPEG-4 system                                 | . 167 |

|    | 8.3   | Summ    | nary                                             | . 171 |

| 9  | Con   | clusion | s and Future Work                                | 173   |

|    | 9.1   | Summ    | hary of the thesis                               | . 173 |

|    |       | 9.1.1   | Channel slicing and lookahead pipelines          | . 174 |

|    |       | 9.1.2   | SDM                                              | . 174 |

|    |       | 9.1.3   | Clos                                             | . 175 |

|    |       | 9.1.4   | Overall remarks                                  | . 176 |

|    |       | 9.1.5   | Discussion of the performance of sync/async NoCs | . 176 |

|    | 9.2   | Future  | ework                                            | . 177 |

| Bi | bliog | raphy   |                                                  | 180   |

| A] | ppen  | dix     |                                                  | 193   |

| A  | Basi  | c Elem  | ents of Asynchronous Circuits                    | 193   |

|    | A.1   | C-eler  | nents                                            | . 193 |

|   |             | A.1.1 2-input symmetric C-elem      | nent                    | 193 |

|---|-------------|-------------------------------------|-------------------------|-----|

|   |             | A.1.2 2-input asymmetric C-elex     | ment with a plus input  | 194 |

|   |             | A.1.3 2-input asymmetric C-elex     | ment with a minus input | 194 |

|   |             | A.1.4 3-input asymmetric C-elex     | ment with a plus input  | 195 |

|   | A.2         | Other cells                         |                         | 195 |

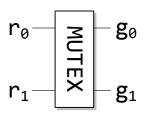

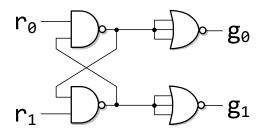

|   |             | A.2.1 MUTEX                         |                         | 195 |

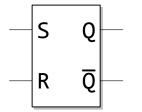

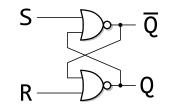

|   |             | A.2.2 RS latch                      |                         | 196 |

| B | Rep         | roduction of the QoS NoC            |                         | 197 |

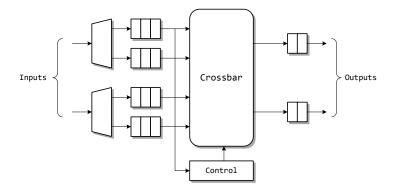

|   | <b>B</b> .1 | Router structure                    |                         | 197 |

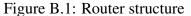

|   | B.2         | Connection of input buffers and the | ne crossbar             | 198 |

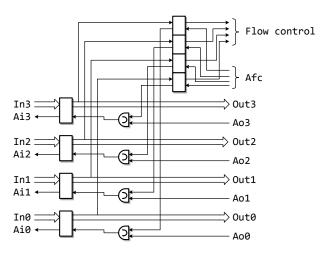

|   | B.3         | Scheduler in the output port        |                         | 199 |

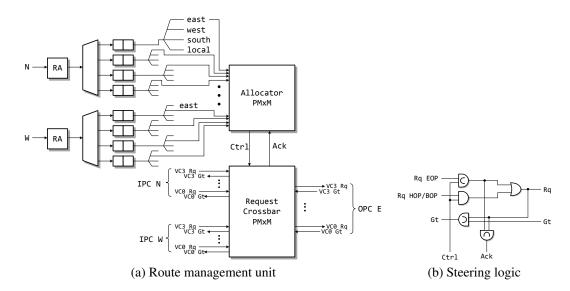

|   | B.4         | Route management unit               |                         | 199 |

| С | Deta        | iled implementation results         |                         | 201 |

|   | <b>C</b> .1 | Single router evaluation            |                         | 201 |

|   | C.2         | Network evaluation                  |                         | 202 |

|   | C.3         | MPEG-4 evaluation                   |                         | 203 |

# **List of Tables**

| 2.1 | Transition table of a 2-input C-element | 35  |

|-----|-----------------------------------------|-----|

| 2.2 | 1-of-4 code                             | 38  |

| 2.3 | 2-of-7 code                             | 39  |

| 2.4 | Average toggle rate                     | 42  |

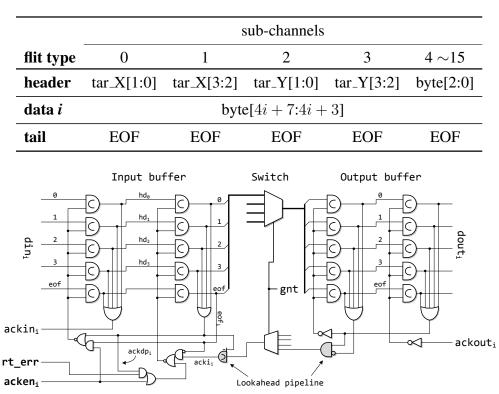

| 4.1 | Flit format                             | 86  |

| 4.2 | Router area                             | 90  |

| 4.3 | Speed performance                       | 90  |

| 5.1 | Buffer area                             | 95  |

| 5.2 | Area consumption                        | 105 |

| 5.3 | Router latency                          | 108 |

| 6.1 | Area consumption                        | 139 |

| 7.1 | Area consumption                        | 153 |

| 7.2 | Router latency                          | 155 |

| 8.1 | Frame direction distribution            | 158 |

| 8.2 | Single router performance               | 159 |

| 8.3 | Network performance                     | 166 |

# **List of Figures**

| 3.14 | MANGO router                                                                                                                  | 73  |

|------|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.15 | QNoC router                                                                                                                   | 74  |

| 4.1  | 4-bit 4-phase dual-rail pipeline                                                                                              | 78  |

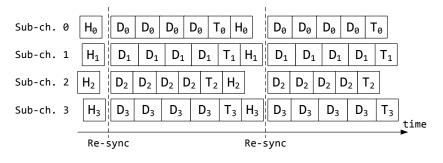

| 4.2  | Pipelined completion process                                                                                                  | 80  |

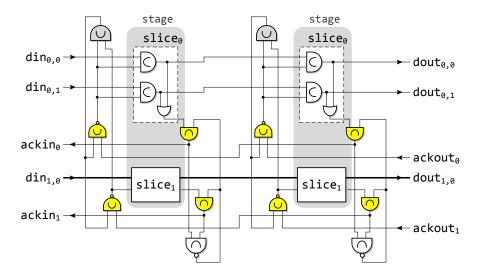

| 4.3  | Channel slicing                                                                                                               | 81  |

| 4.4  | Data flow with channel slicing                                                                                                | 82  |

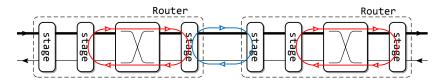

| 4.5  | Critical cycles in asynchronous on-chip networks                                                                              | 82  |

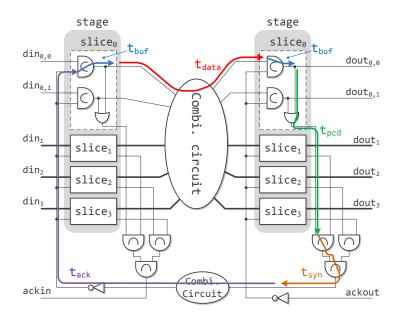

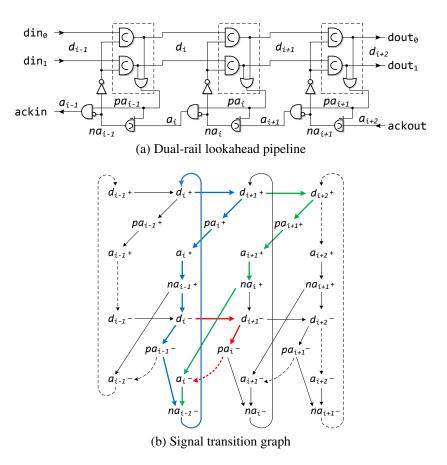

| 4.6  | Lookahead pipeline                                                                                                            | 83  |

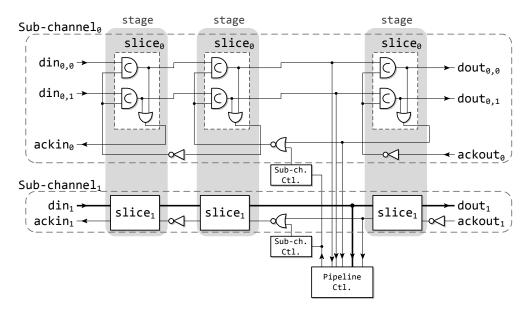

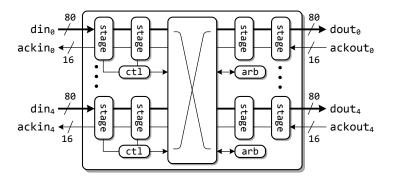

| 4.7  | A channel sliced wormhole router                                                                                              | 85  |

| 4.8  | Data path of the <i>i</i> th sub-channel                                                                                      | 86  |

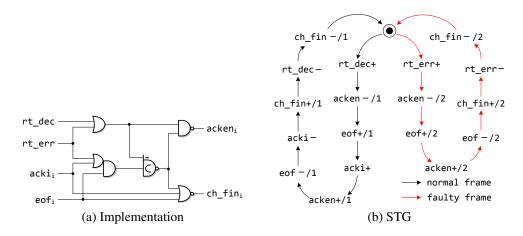

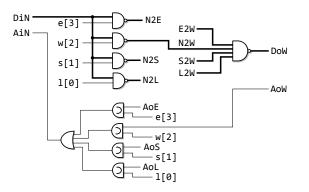

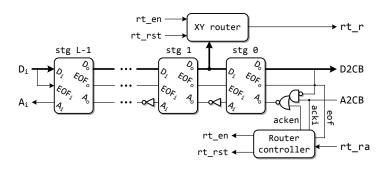

| 4.9  | Sub-channel controller                                                                                                        | 87  |

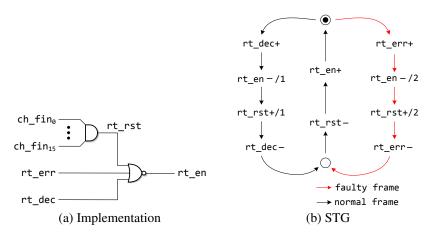

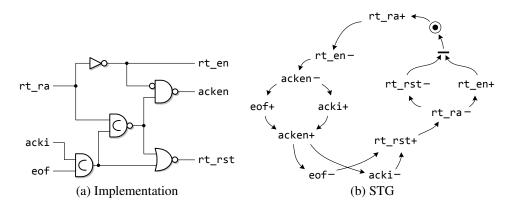

| 4.10 | Router controller                                                                                                             | 88  |

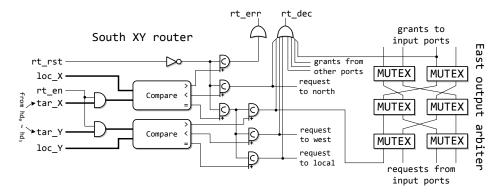

| 4.11 | XY router and output arbiter                                                                                                  | 89  |

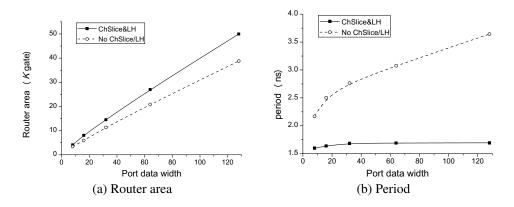

| 4.12 | Area and speed with various data widths                                                                                       | 91  |

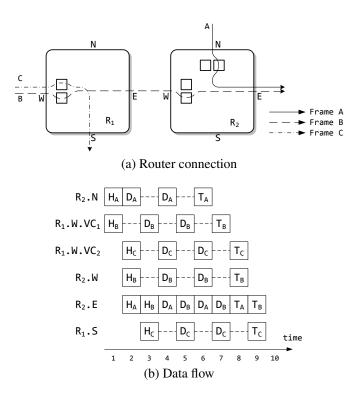

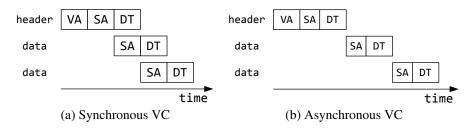

| 5.1  | Data flow of VC                                                                                                               | 94  |

| 5.2  | Crossbar in asynchronous VC routers                                                                                           | 96  |

| 5.3  | SDM router                                                                                                                    | 97  |

| 5.4  | Input buffer for a virtual circuit                                                                                            | 99  |

| 5.5  | Router controller                                                                                                             | 100 |

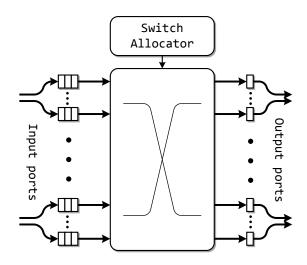

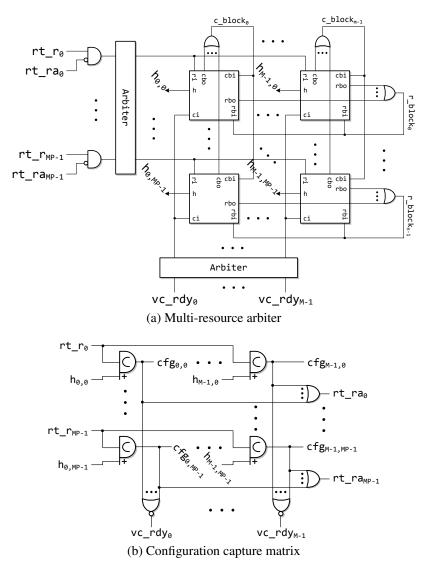

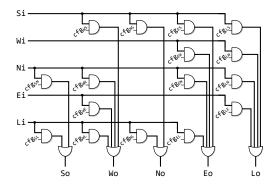

| 5.6  | Switch allocator                                                                                                              | 101 |

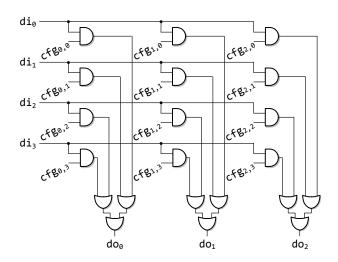

| 5.7  | A 1-bit $4 \times 3$ crossbar                                                                                                 | 104 |

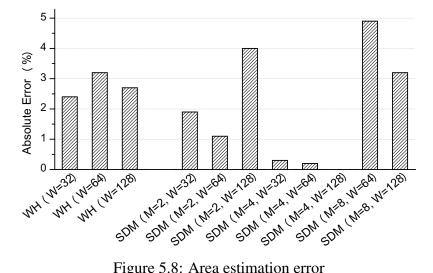

| 5.8  | Area estimation error                                                                                                         | 105 |

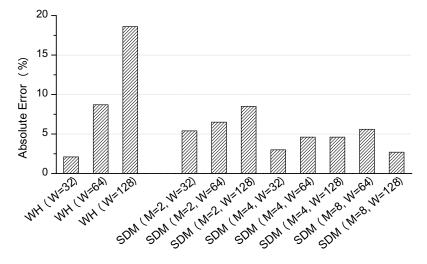

| 5.9  | Latency estimation error                                                                                                      | 108 |

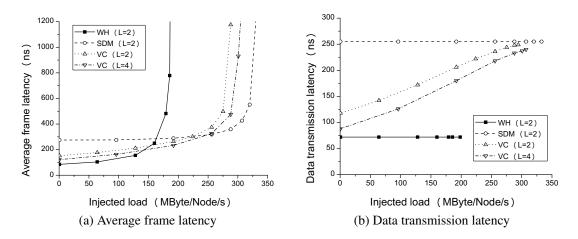

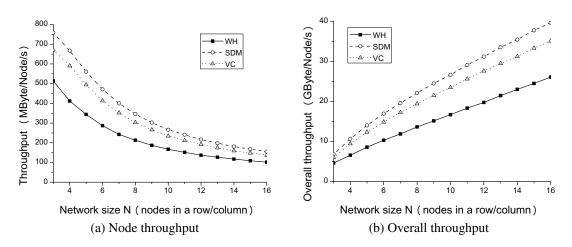

| 5.10 | Latency under various network loads ( $P = 5, W = 32, M = 4$ )                                                                | 111 |

| 5.11 | Credit based backpressure method                                                                                              | 111 |

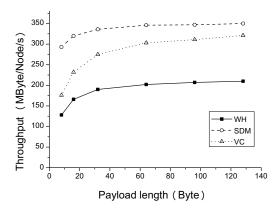

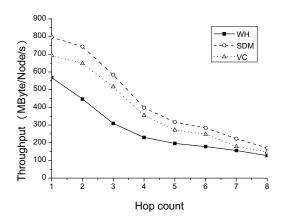

| 5.12 | Throughput with various payload lengths ( $P = 5, W = 32, L = 2$ ,                                                            |     |

|      | $M = 4)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                     | 112 |

| 5.13 | Throughput with various communication distances ( $P = 5, W = 32$ ,                                                           |     |

|      | L = 2, M = 4)                                                                                                                 | 113 |

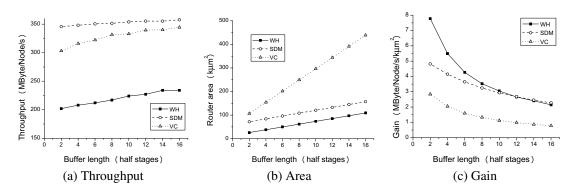

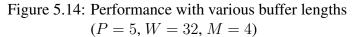

| 5.14 | Performance with various buffer lengths ( $P = 5, W = 32, M = 4$ )                                                            | 114 |

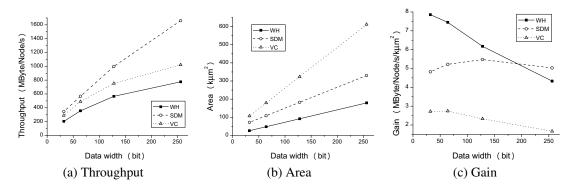

| 5.15 | Performance with various port data width $(P = 5, L = 2, M = 4)$                                                              | 114 |

| 5.16 | Network scalability $(P = 5, W = 32, L = 2, M = 4) \dots$                                                                     | 115 |

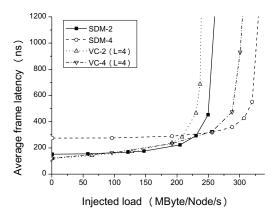

| 5.17 | Throughput with various number of virtual circuits or VCs ( $P = 5$ ,                                                         |     |

|      | $W = 32, L = 2) \dots $ | 116 |

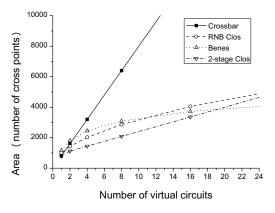

| 6.1  | Area of different switches                                                                                                                                   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

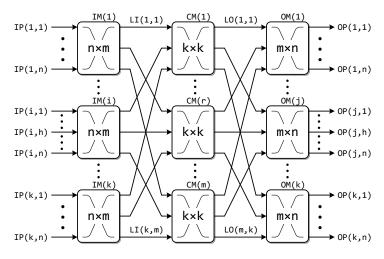

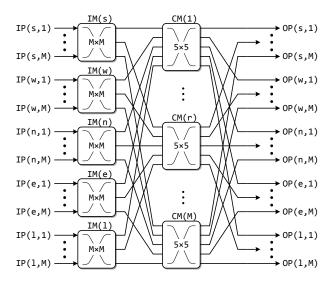

| 6.2  | General 3-stage Clos network                                                                                                                                 |

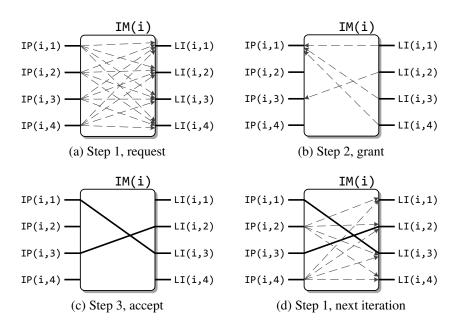

| 6.3  | Example of the matching within an IM                                                                                                                         |

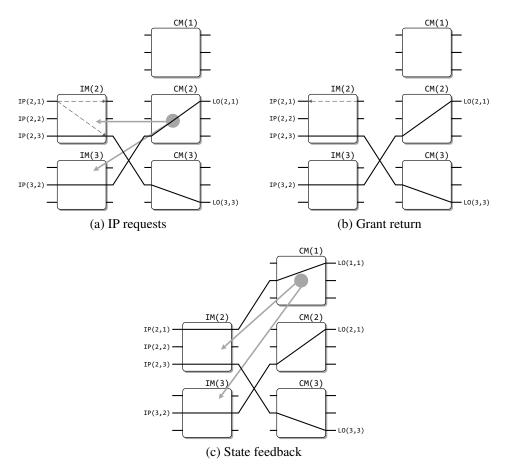

| 6.4  | State feedback scheme of the asynchronous dispatching algorithm 127                                                                                          |

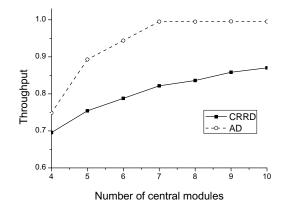

| 6.5  | Performance with non-blocking uniform traffic                                                                                                                |

| 6.6  | Throughput with various number of central modules                                                                                                            |

| 6.7  | Throughput with uniform traffic                                                                                                                              |

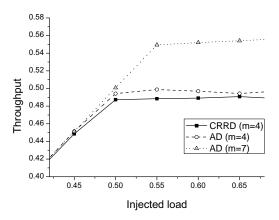

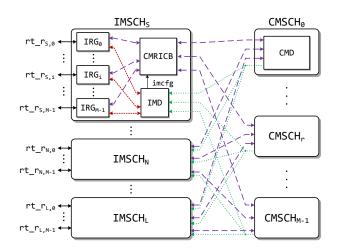

| 6.8  | An asynchronous Clos scheduler for $C(4, 8, 4) \dots $ |

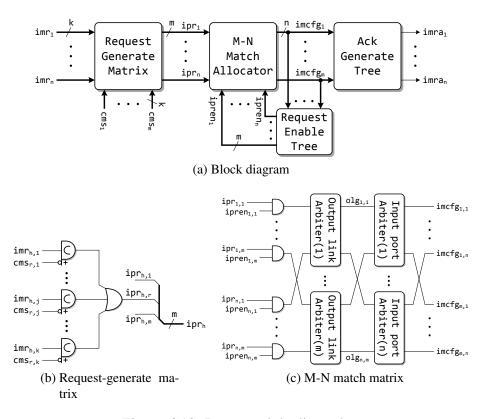

| 6.9  | Input request generator                                                                                                                                      |

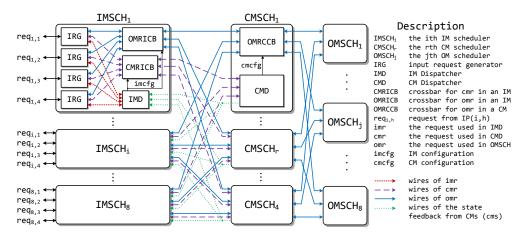

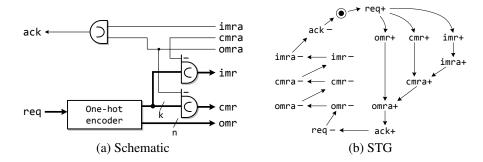

| 6.10 | Input module dispatcher                                                                                                                                      |

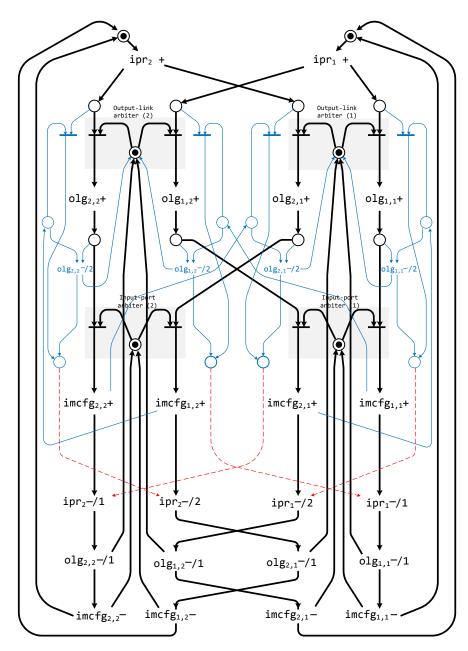

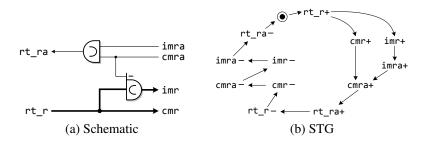

| 6.11 | STG of a $2 \times 2$ MNMA                                                                                                                                   |

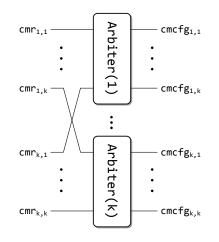

| 6.12 | Central module dispatcher                                                                                                                                    |

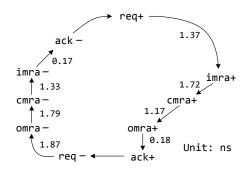

| 6.13 | Detailed allocation latency                                                                                                                                  |

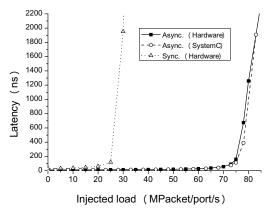

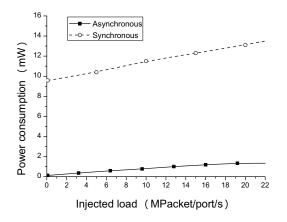

| 6.14 | Latency of Clos schedulers                                                                                                                                   |

| 6.15 | Power consumption of Clos schedulers                                                                                                                         |

| 6.16 | 2-stage Clos switch                                                                                                                                          |

| 6.17 | Area of different switches (including the 2-stage Clos switches) 144                                                                                         |

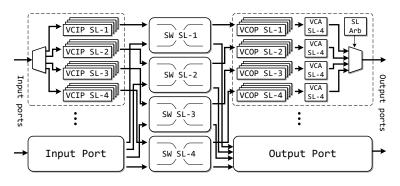

| 7.1  | Asynchronous SDM router using 2-stage Clos switch                                                                                                            |

| 7.2  | Input buffer for a virtual circuit                                                                                                                           |

| 7.3  | Output buffer for a virtual circuit                                                                                                                          |

| 7.4  | The turn model of the XY routing algorithm                                                                                                                   |

| 7.5  | An optimized central module                                                                                                                                  |

| 7.6  | Scheduler for the 2-stage Clos switch                                                                                                                        |

| 7.7  | The input request generator in an SDM router                                                                                                                 |

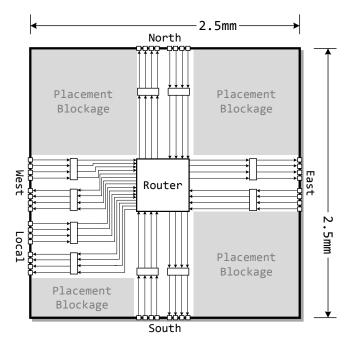

| 7.8  | Floor plan of a router tile                                                                                                                                  |

|      |                                                                                                                                                              |

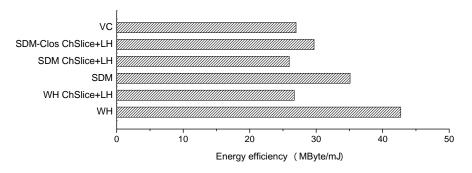

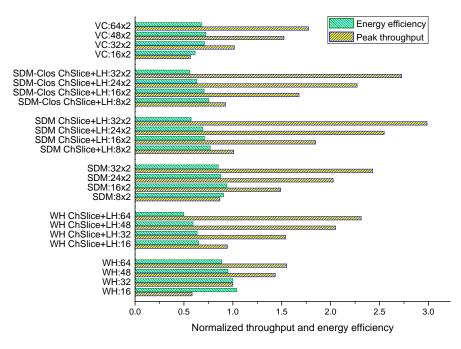

| 8.1  | Energy efficiency of a single router                                                                                                                         |

| 8.2  | Router performance with various number of virtual circuits/VCs 162                                                                                           |

| 8.3  | Router performance with various data widths                                                                                                                  |

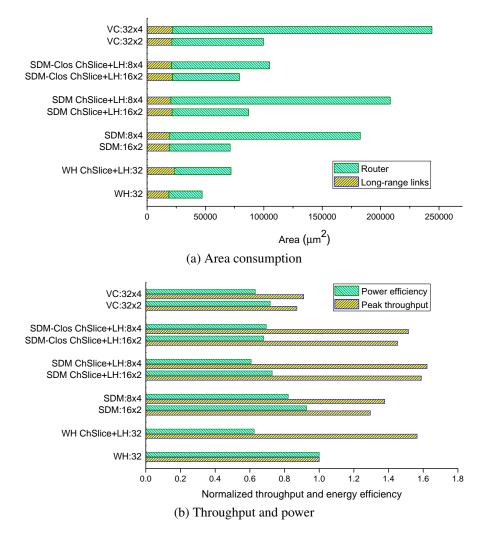

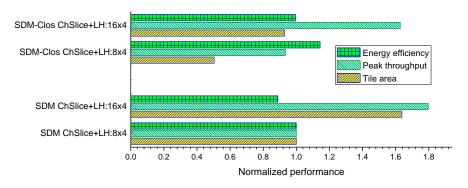

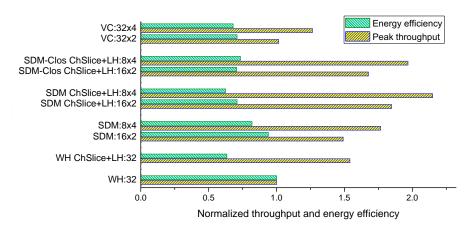

| 8.4  | Performance of SDM routers with four virtual circuits                                                                                                        |

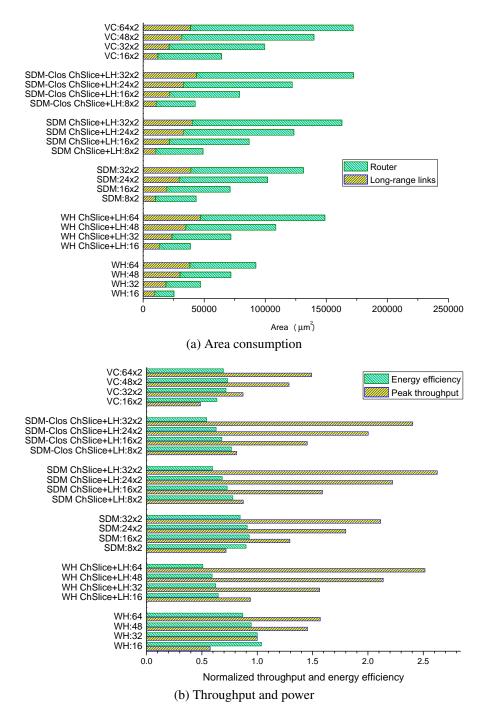

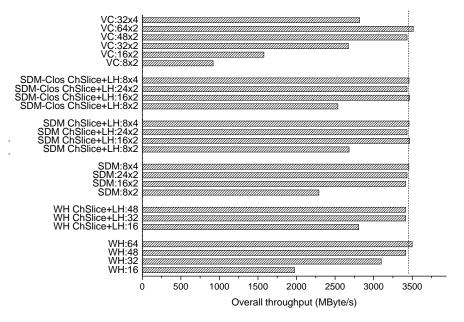

| 8.5  | Network performance with various number of virtual circuits/VCs 167                                                                                          |

| 8.6  | Network performance with various data widths                                                                                                                 |

| 8.7  |                                                                                                                                                              |

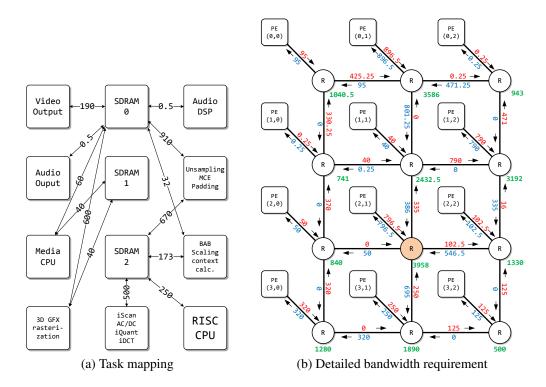

| 0.7  | Task mapping and bandwidth requirement of MPEG-4    169                                                                                                      |

| 8.8  | Task mapping and bandwidth requirement of MPEG-4169Overall throughput of the MPEG-4 NoCs169                                                                  |

| <b>B</b> .1 | Router structure                           | 198 |

|-------------|--------------------------------------------|-----|

| B.2         | Input buffer and crossbar interface        | 198 |

| B.3         | Scheduler in an output buffer              | 199 |

| B.4         | The operation of the route management unit | 200 |

# **List of Abbreviations**

| AD      | asynchronous dispatching, 125                                  |

|---------|----------------------------------------------------------------|

| ANOC    | asynchronous network-on-chip, 72                               |

| ASPIN   | asynchronous scalable programmable interconnection network, 70 |

| ATM     | asynchronous transfer mode, 118                                |

| BE      | best-effort, 62                                                |

| CD      | completion detection, 77                                       |

| ChSlice | channel slicing, 89                                            |

| СМ      | central module, 120                                            |

| CMD     | central module dispatcher, 132                                 |

| CMP     | chip multi-processor, 22                                       |

| CMRICB  | CM request forwarding crossbar in IM, 132                      |

| CMSCH   | central module scheduler, 132                                  |

| CRRD    | concurrent round-robin dispatching, 123                        |

| DI      | delay-insensitive, 30                                          |

| DOR     | dimensional order routing, 63                                  |

| DVFS    | dynamic voltage and frequency scaling, 68                      |

| EOF     | end of a frame, 85                                             |

| FF      | filp-flop, 66                                                  |

| FIFO    | first-in-first-out, 66                                         |

| GALS    | globally asynchronous and locally synchronous, 30              |

| GS      | guaranteed service, 61                                         |

| HOL     | head-of-line, 58                                               |

| IM      | input module, 120                                              |

| IMD     | input module dispatcher, 132                                   |

| IMSCH   | input module scheduler, 132                                    |

| IP      | input port, 120                                                |

| IP      | intellectual property, 51                                      |

|         |                                                                |

| IP        | internet protocol, 118                                             |

|-----------|--------------------------------------------------------------------|

| IRG       | input request generator, 132                                       |

| LH        | lookahead pipeline style, 89                                       |

| LI        | link from IM to CM, 120                                            |

| LO        | link from CM to OM, 120                                            |

| MANGO     | message-passing asynchronous network-on-chip providing guaranteed  |

|           | service through OCP interfaces, 73                                 |

| MPEG      | moving picture experts group — the name of a family of audio/video |

|           | coding standards, 157                                              |

| MPSoC     | multi-processor system-on-chip, 22                                 |

| MTBF      | mean time between failures, 68                                     |

| MUTEX     | mutual exclusive, 43                                               |

| NoC       | network-on-chip, 22                                                |

| OCP       | open core protocol, 73                                             |

| OM        | output module, 120                                                 |

| OMRCCB    | OM request forwarding crossbar in CM, 132                          |

| OMRICB    | OM request forwarding crossbar in IM, 132                          |

| OMSCH     | output module scheduler, 132                                       |

| OP        | output port, 120                                                   |

| PE        | processing element, 51                                             |

| PIM       | parallel iterative matching, 123                                   |

| QDI       | quasi-delay-insensitive, 30                                        |

| QNoC      | quality-of-service NoC, 74                                         |

| QoS       | quality of service, 61                                             |

| RNB       | rearrangeable non-blocking, 121                                    |

| RS latch  | set and reset latch, 45                                            |

| SDF       | standard delay format, 89                                          |

| SDM       | spatial division multiplexing, 25                                  |

| SI        | speed-independent, 31                                              |

| SNB       | strict-non-blocking, 121                                           |

| SoC       | system-on-chip, 22                                                 |

| SPA       | static priority arbiter, 46                                        |

| SpiNNaker | universal spiking neural network architecture, 69                  |

| STG       | signal transition graph, 31                                        |

| TDM       | time division multiplexing, 24                                     |

|           |                                                                    |

| VC   | virtual channel, 25                                                |

|------|--------------------------------------------------------------------|

| VLSI | very large scale integration, 23                                   |

| XY   | A DOR algorithm used in mesh or torus networks, first X then Y, 63 |

## Abstract

A thesis submitted for the degree of Doctor of Philosophy Title: Spatial Parallelism in the Routers of Asynchronous On-Chip Networks By Wei Song, The University of Manchester, 6th July 2011

State-of-the-art multi-processor systems-on-chip use on-chip networks as their communication fabric. Although most on-chip networks are implemented synchronously, asynchronous on-chip networks have several advantages over their synchronous counterparts. Timing division multiplexing (TDM) flow control methods have been utilized in asynchronous on-chip networks extensively. The synchronization required by TDM leads to significant speed penalties. Compared with using TDM methods, spatial parallelism methods, such as the spatial division multiplexing (SDM) flow control method, achieve better network throughput with less area overhead.

This thesis proposes several techniques to increase spatial parallelism in the routers of asynchronous on-chip networks.

Channel slicing is a new pipeline structure that alleviates the speed penalty by removing the synchronization among bit-level data pipelines. It is also found out that the lookahead pipeline using early evaluated acknowledgement can be used in routers to further improve speed.

SDM is a new flow control method proposed for asynchronous on-chip networks. It improves network throughput without introducing synchronization among buffers of different frames, which is required by TDM methods. It is also found that the area overhead of SDM is smaller than the virtual channel (VC) flow control method – the most used TDM method. The major design problem of SDM is the area consuming crossbars. A novel 2-stage Clos switch structure is proposed to replace the crossbar in SDM routers, which significantly reduces the area overhead. This Clos switch is dynamically reconfigured by a new asynchronous Clos scheduler.

Several asynchronous SDM routers are implemented using these new techniques. An asynchronous VC router is also reproduced for comparison. Performance analyses show that the SDM routers outperform the VC router in throughput, area overhead and energy efficiency.

# **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://www.campus.manchester.ac.uk/medialibrary/ policies/intellectual-property.pdf), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses.

### Acknowledgements

The four years spent in Manchester is one of my most joyful, peaceful and successful periods in life. I must express my appreciation to all the people who have helped me. I shall and will remember all the kindness and do the same in the future.

I feel deeply fortunate to be supervised by Dr. Doug Edwards. He continuously encourages me to explore all my naive ideas and always expresses concerns in the most delicate way. The whole research starts from those ideas and it is his careful guidance that leads the research to the right direction.

I have to express my gratitude to Dr. José Nuñez-Yañez whose simulation model has ignited my research in on-chip networks. I also thank all the members in the joined project, especially to Dr. Sohini Dasgupta for her help on Peri Net and STG, and Atukem Nabina and Dr. Mohammad Hosseinabady for their kind treatment in Bristol.

It is impossible to finish this PhD without the help from the members in the APT group. Thanks to Dr. Luis Tarazona, Dr. Andrew Bardsley and Dr. Will Toms for their help on Balsa. Special gratitude to Dr. Charles Brej for his support on computer issues. Thanks to Jeffrey Pepper, Eustace Painkras, Dr. Luis Plana, Dr. Steve Temple and Dr. Simon Davidson for their maintenance of EDA tools and their kindness of allowing me to use the tools even during the tape out of SpiNNaker chips. Thanks to Dr. Lilian Janin for his continuous maintenance of Stella. Thanks Dr. Zhenyu Liu for his contribution to the synchronous Clos scheduler. Thanks to Hongguang Ren for proofreading parts of the thesis.

Many friends have helped me pass the time joyfully. Many thanks to Dr. Yebin Shi, Dr. Jian Wu, Dr. Shufan Yang, Zheng Xie, and Dr. Xin Jin who directly or indirectly contribute to the progress of this research.

Finally, I will never forget Prof. Suiming Fang who had opened my interest into hardware design. I am lucky to be the son of Prof. Caifa Song and Guixia Xia who are my mentors for life and academia.

# **The Author**

Wei Song received his B.S.EE. from the College of Electronic Information and Control Engineering at the Beijing University of Technology, Beijing, P.R.China in 2005. In the same year, he was admitted through recommendation by the same college to pursue his M.S.EE. and obtained it in 2008.

From 2004 to 2006, Wei Song was also a research assistant in the Beijing Embedded System Key Lab (BESKL). He participated in the design of demodulators for several wireless communication systems including WLAN 802.11a/g, DVB-T and ATSC. He also implemented the FPGA verification platforms for most digital designs in BESKL. After leaving BESKL, he went back to his studying college and designed a real-time non-preemptive thread scheduler for a central communication controller in the hybrid electric vehicle control system. The communication controller was later patented in 2008.

Wei Song was offered a full scholarship by the EPSRC doctorate training program and began his Ph.D. study in the School of Computer Science at the University of Manchester in 2007 when he was also writing up his master dissertation. His work in Manchester is designing the asynchronous routers in an energy efficient network-onchip for dynamically reconfigurable computing platforms, supported by EPSRC.

# Part I

# **Introduction and Background**

# Chapter 1 Introduction

### 1.1 Motivation

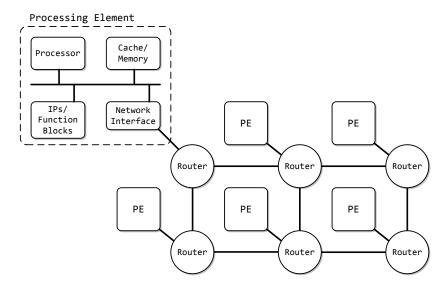

The continuously shrinking transistor geometry makes network-on-chip (NoC) [9] the practical communication fabric for state-of-the-art multi-processor system-on-chip (MPSoC) designs. Following Moore's Law, the capacity and complexity of a chip has been boosted significantly in recent decades. The function of a board level system in the last decade can be integrated into one chip in modern system-on-chip (SoC) designs. On the other hand, SoCs are no longer built from scratch because the complexity is beyond control. The fast and reliable integration of numerous reusable intellectual property (IP) blocks becomes crucial to meet the time to market requirement. As a replacement for traditional hierarchical bus systems and point to point connections, the on-chip network infrastructure provides a unified interface for new IP blocks to be easily plugged into a system. A modern MPSoC is a communication-centric system [57] lying on an on-chip network communication fabric.

Most NoCs are synchronous networks where network components are driven by the same or several global clocks. Thanks to the timing assumptions allowed by the global clock and mature electronic design automation (EDA) tools, these synchronous NoCs are fast and area efficient. However, there are several design challenges in synchronous NoCs that are difficult to resolve:

• Support for heterogeneous networks. Unlike chip multi-processor (CMP) systems where every network node is a homogeneous processor element, an MP-SoC is a heterogeneous system where network nodes are IP blocks with different functions and hardware structures. These IP blocks are provided and tested with different clock frequencies, area sizes and even working voltages. These differences complicate the network topology, compromise the latency performance of synchronous networks and make chip timing closure difficult.

- *Low power consumption*. It is crucial to reduce the power consumption of an SoC as it determines the maximum standby time of a handset device. The clock tree of synchronous on-chip networks consumes a significant amount of energy [79] and it is getting worse along with the shrinking transistor geometry.

- Tolerance to variation. Process, temperature and voltage variations affect future sub-micron VLSI designs significantly [72, 74]. According to the international technology roadmap for semiconductors, the delay uncertainty caused by variations in the sign-off timing closure will reach 32% in 2024 [60]. Traditional static timing analysis is going to be replaced by statistical timing analysis methods [14] to cope with dropping yield rate and over-conservative timing estimation. Synchronous on-chip networks alleviate this effect by considering variations in their task mapping procedure [74]. However, this works only in homogeneous networks and the routers are still working at the worst speed estimated.

Instead of using synchronous on-chip networks, asynchronous on-chip networks are a promising solution to the above challenges. The communication components in an asynchronous on-chip network are built with clockless asynchronous circuits. Data are transmitted according to certain handshake protocols which can be insensitive to delay [117]. Because of this delay insensitivity, the interface between all IP blocks to the global asynchronous on-chip network is unified by the same synchronous to/from asynchronous interface. The fact that all synchronous blocks are isolated by the asynchronous network simplifies chip-level timing closure. Also, thanks to the delay insensitivity, an asynchronous on-chip network is naturally tolerant to all variations as the delay uncertainty caused by these variations cannot affect the function of those handshake protocols. Finally, since no clock is needed in asynchronous circuits, an asynchronous on-chip network consumes zero dynamic power when no data is in transmission.

However, most asynchronous networks [3, 45, 12, 7, 38] are slower than the synchronous on-chip networks with similar structures and resources [79]. Although the global clock in synchronous circuits is power consuming, it is a speed and area efficient approach to synchronize combinational operations. Asynchronous circuits rely on handshake protocols to control data transmission. Combinational operations are explicitly detected and guarded to ensure the insensitivity to delay. The circuits used in detecting combinational operations introduce area and speed overhead. Delay insensitive asynchronous circuits are intrinsically slow.

Another issue is that, the state-of-the-art way of designing asynchronous on-chip networks is to asynchronously reproduce the structures of synchronous on-chip networks. As synchronous on-chip networks synchronize data with no speed penalty, timing division multiplexing (TDM) techniques [30] are extensively utilized. Simply reproducing such TDM structures in asynchronous on-chip networks introduces extra completion detection circuits and causes speed penalties.

Although the speed penalty of completion detection is unavoidable, as the promising advantages of asynchronous circuits are derived from those delay insensitive handshake protocols, the scale of the synchronization in asynchronous circuits can be limited to small transmission units, such as a single pipeline. The speed penalty is therefore alleviated. The following question is how to build asynchronous networks with such limited synchronization.

The solution presented in this thesis is *spatial parallelism*. TDM is not a good approach in asynchronous circuits because it brings extra synchronization and compromises speed. If the synchronization is constricted to a small scale such as a single pipeline, these pipelines are controlled distributedly. In other words, communication resources are spatially divided into unsynchronized low-level components and the speed penalty of synchronization is minimized.

### 1.2 Research objectives

The overall objective of this research is to explore the spatial parallelism in asynchronous on-chip routers. It is expected that 49% of the global signals will be driven by handshake protocols by 2024 and the latency of asynchronous signalling will be improved through 2014 [60]. Routers are the key components of an on-chip network. Improving the speed of asynchronous routers using spatial division techniques provides a feasible way of meeting the speed requirement for future chip designs and hopefully the techniques can be utilized in general asynchronous circuits beyond asynchronous on-chip networks.

#### 1.3. RESEARCH CONTRIBUTIONS

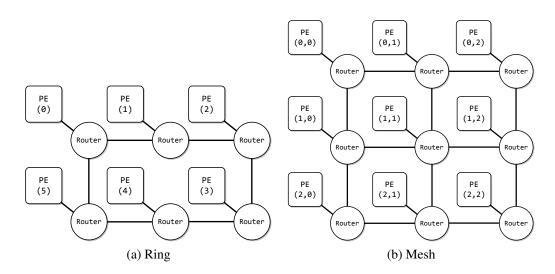

Spatial parallelism will be explored in different layers. Although there is no consensus on the definition of layers in on-chip networks, the lower communication structure can be generally separated into three layers: *routing layer*, *switching layer* and *physical layer* [41]. The data transmitted in a network are divided accordingly as *frames*, *flits* and *phits*. The physical layer refers to the basic communication resources such as buffers and channels which deliver phits from one buffer to another. A flit comprises one or several phits. The *switching layer* dynamically allocates communication resources of the *physical layer* to different flits. The hardware structure and algorithm used in this allocation process is normally named as the *control flow* method. A frame is the smallest data unit which is self-explainable to a network node. It contains one or several flits. The *routing layer* determines the route through which a frame travels in a network. This research concentrates on exploring the spatial parallelism in the lowest two layers: the *physical layer* and the *switching layer*.

In the *physical layer*, the state-of-the-art routers use synchronized multi-bit pipelines as buffer stages, which are similar to the latches on buses in synchronous circuits. This pipeline style simplifies the control logic but introduces significant speed overhead. The effect of the speed degradation caused by synchronization will be analysed. Some techniques will be proposed to alleviate this degradation and will be compared with the synchronized pipeline style for speed, area and power performance.

In the *switching layer*, most asynchronous on-chip networks use timing division flow control methods such as the virtual channel (VC) flow control method. The new spatial division multiplexing (SDM) flow control method proposed in this research will be compared with the virtual channel flow control method in various router implementations. Their speed performance, area consumption and power dissipation will be analysed within different working environments.

### 1.3 Research contributions

The following contributions have been made upon this research:

- In the *physical layer*

- Analysis of the speed and area overhead of synchronizing multiple lowlevel pipelines

- Channel slicing, a technique that removes the synchronization among pipelines

- A method of utilizing the *lookahead* pipeline style in normal asynchronous pipelines

- In the *switching layer*

- Overhead analysis of the virtual channel (VC) flow control method

- Overhead analysis of the *spatial division multiplexing (SDM)* flow control method

- Utilization of SDM in asynchronous routers

- Reducing the area overhead of SDM using Clos switches

- A new 2-stage Clos switch for on-chip routers

- An asynchronous dispatching algorithm and its implementation to dynamically reconfigure Clos switches

- Overall

- A novel asynchronous SDM router

- Performance comparison among various wormhole, SDM and VC routers

### 1.4 Thesis organization

The thesis is divided into three parts: Part I provides a brief background introduction of this thesis. Part II proposes several new techniques to increase spatial parallelism in asynchronous routers. Finally a router is implemented in Part III utilizing all the techniques introduced in Part II.

In the rest of Part I, Chapter 2 presents an overview of asynchronous circuits including their different delay assumptions, handshake protocols, data encoding methods and arbitration components. Chapter 3 introduces the concepts related to on-chip networks and reviews previously published asynchronous router designs.

Part II proposes several new techniques in different layers. Chapter 4 concentrates on the *physical layer*. Channel slicing is utilized to remove the synchronization among low-level pipelines and the lookahead pipeline style is used to further reduce the period. Instead of using timing division flow control methods, Chapter 5 proposes the spatial division multiplexing (SDM) flow control method and examines its advantage over the virtual channel (VC) flow control method by behavioural level simulations. The

major implementation overhead of SDM is the enlarged crossbar. Chapter 6 provides a solution to the large area overhead — replacing the crossbar with a Clos switch. However, dynamically reconfiguring a multi-stage Clos switch is complicated and has not yet been implemented asynchronously. The first asynchronous Clos scheduler is designed and implemented also in Chapter 6.

Part III combines all the techniques in Part II into one router design. Chapter 7 briefly describes the final asynchronous SDM router. The performance analyses of several router implementations are provided in Chapter 8. The thesis is finally concluded in Chapter 9.

### 1.5 Publications

The following papers have been produced during the research of this work. The chapters that are closely related to these papers are identified respectively.

Wei Song, Doug Edwards, Zhenyu Liu and Sohini Dasgupta. Routing of asynchronous Clos networks. In submission to *IET Computers & Digital Techniques*, 2011.

The hardware implementation and the performance evaluation of an asynchronous Clos scheduler in Chapter 6 come from this paper.

- Wei Song and Doug Edwards. Asynchronous spatial division multiplexing router. *Microprocessors and Microsystems*, Vol. 35. No. 2, pp. 85–97, 2011 [115]. The SDM router implementation in Chapter 5 originated from this paper.

- Wei Song and Doug Edwards. Improving the throughput of asynchronous onchip networks with SDM. In *Proc. of UK Electronics Forum*, pages 47 – 56, June 2010.

- Wei Song and Doug Edwards. An asynchronous routing algorithm for Clos networks. In *Proc. of International Conference on Application of Concurrency to System Design*, pages 67-76, June 2010 [113]. The asynchronous dispatching algorithm in Chapter 6 was first published in this paper.

- Wei Song and Doug Edwards. A low latency wormhole router for asynchronous on-chip networks. In *Proc. of Asia and South Pacific Design Automation Conference*, pages 437443, January 2010 [114].

The area and speed performance of using channel slicing and lookahead pipelines in Chapter 4 was published in this paper.

- 6. Wei Song and Doug Edwards. Channel Slicing: a way to build fast routers for asynchronous NoCs. In *Proc. of UK Asynchronous Forum*, September 2009.

- Wei Song and Doug Edwards. Building asynchronous routers with independent sub-channels. In *Proc. of International Symposium on System-on-Chip*, pages 48-51, October 2009 [112]. The channel slicing technique introduced in Chapter 4 was first proposed in this paper.

- 8. Wei Song, Doug Edwards, Jose Nunez-Yanez, and Sohini Dasgupta. Adaptive stochastic routing in fault-tolerant on-chip networks. In *Proc. of ACM/IEEE International Symposium on Networks-on-Chip*, pages 32-37, May 2009 [116].

- 9. Wei Song and Doug Edwards. A dynamic link allocation router. In *Proc. of UK Asynchronous Forum*, September 2008.

## Chapter 2

## **Asynchronous Circuits**

The asynchronous circuits in this thesis refer to the circuits where sequential components (registers and latches) are driven by handshakes rather than global clocks. The circuits using global clocks are, on the other hand, synchronous circuits. The necessary background knowledge for asynchronous circuits in asynchronous on-chip networks is introduced.

### 2.1 General description

Although asynchronous circuits have a long history of over 50 years [81], most VLSI circuits are synchronous due to the mature EDA support. Since registers and latches in synchronous circuits are synchronized by the global clock, they are the natural timing boundaries by which a circuit can be divided into paths. All these paths are driven by the same clock and operate concurrently and independently. EDA tools, especially synthesis tools, are therefore able to improve speed by optimizing these paths individually. On the other hand, the latches in asynchronous circuits are driven by handshake protocols (circuits). The operation of one latch is normally triggered by events generated from other latches. It is difficult to optimize the speed of asynchronous circuits due to the lack of clear timing boundaries to break large circuits into small analysable pieces as in synchronous circuits. Some asynchronous synthesis tools have been proposed recently, such as Petrify [29] and Balsa [43], to translate behavioural hardware descriptions into low level netlists. However, high speed asynchronous circuits are manually designed [110, 93, 105].

Shrinking transistor geometry brings opportunities for asynchronous circuits. As the number of transistors in a single die increases corresponding to the prediction of Moore's Law, the area and power overhead of synchronizing the whole chip with one global clock is unacceptable and beyond the control of current EDA tools. Future MPSoCs should be globally asynchronous and locally synchronous (GALS) designs where synchronous IP blocks talk with each other using an asynchronous communication infrastructure. 49% of the global signals will be driven by asynchronous circuits by the year 2024 [60]. Variation is another problem. The decreasing transistor size increases power density which leads to temperature and power variation [59]. Process variation worsens the situation with non-deterministic cell latencies. The worst case timing analysis in synchronous circuits generates over-pessimistic speed estimation [14]. Asynchronous circuits are tolerant to variations and provide average speed performance.

### 2.2 Delay assumptions

Delay assumptions are the assumptions made for estimating the latency of circuit components. They are used by designers to analyse, simplify and implement asynchronous circuits. Different delay assumptions lead to circuits with different speed, area and robustness.

#### 2.2.1 Delay-insensitive

Delay-insensitive (DI) assumes all the gates and wires in an asynchronous circuit have positive, undetermined and unbounded delays. With this assumption, every operation is forced to indicate its completion to allow the following operation to be processed. DI circuits are the most robust because logic function is independent to delay. However, the assumption itself constricts its usage in practical implementations. Nearly all basic gates in synchronous circuits, such as AND, OR, XOR, etc., are not delay-insensitive. Only C-elements (see Section 2.4.1 and Appendix A) and inverters can be used in delay-insensitive circuits [76].

#### 2.2.2 Quasi-delay-insensitive

Quasi-delay-insensitive (QDI) circuits relax the delay assumption of DI by allowing isochronic forks [117], the sinks of which have the same delay from their common driver. This timing assumption allows a signal to be safely sent to multiple sub-circuits

and indicated by a common acknowledge signal. QDI can be used to implement practical designs.

### 2.2.3 Speed-independent

Speed-independent (SI) assumes all wires in a circuit have zero delay while all gates have positive, undetermined and unbounded delays. This may look unrealistic as wires have positive delays, but the delay of a wire can be counted in the delay of the gate driving it. In other words, SI assumes all forks in a circuit are isochronic. Since QDI assumes some, but not all, forks are isochronic, SI is a relaxed assumption from QDI to circuit designers. As presented in [25], it is possible to synthesize behavioural circuit models described in signal transition graphs (STGs) into SI circuits.

It is not necessary in most situations for a circuit designer to differentiate the nonisochronic forks from all wires. QDI is more robust than SI but they are usually discussed without clear differentiation. In this thesis, "QDI" is used for both QDI and SI circuits.

#### 2.2.4 Relaxed QDI

DI, QDI and SI circuits assume gate delays are unbounded. As operations explicitly indicate their completion, some completion detection circuits are introduced when multiple operations are synchronized. These completion detection circuits lead to extra speed and area overhead. In addition, the delays of gates in practical circuits are bounded. Some delay relations between certain paths can be utilized to reduce the area and speed overhead introduced by synchronization. In these relations, the gate delay is still unbounded but some paths are assumed longer than other paths [131, 121, 110, 111]. When multiple paths are synchronized, only the operations through the longer paths are indicated leaving the shorter paths undetected. As long as the assumed delay relations are not violated, these circuits are still tolerant to variations as DI, QDI and SI. Currently there is no common name for these circuit styles and it is called "relaxed QDI" in this thesis.

#### 2.2.5 Self-timed

Although self-timed circuits are the superset of all asynchronous circuits, they are usually referred by their narrow meaning of circuits that assume gates and wires have

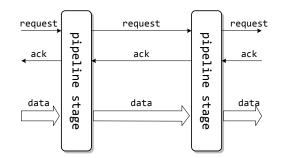

Figure 2.1: Two adjacent pipeline stages

bounded delays. Worst delay analysis and matched delay lines are used in self-timed circuits to avoid completion detection. This circuit style is area and speed efficient. However, the bounded delay assumption compromises the tolerance to delay variations; therefore, self-timed circuits require careful timing analysis and implementation to ensure that the estimated bounded delay assumption is not violated.

### 2.3 Handshake protocols

Figure 2.1 shows the abstract view of asynchronous pipeline stages. Every pipeline stage is a storage component. The data from the previous pipeline stage are ready when a valid *request* is received. When incoming data are safely captured, the previous pipeline stage is notified through the *ack* line and the old data stored in the previous stage can be released. A handshake protocol controls the transitions between two adjacent pipeline stages. Specifically, it determines the waveform and timing on *request* and *ack* lines. Two protocols are available in asynchronous circuits: 4-phase and 2-phase.

#### 2.3.1 4-phase

The 4-phase protocol (also called return-to-zero signalling or level signalling) is the most utilized handshake protocol in asynchronous circuits as all gates are level triggered. Standard cells in synchronous circuits are also level triggered. Asynchronous circuits complying with the 4-phase protocol can be implemented using synchronous standard cell libraries.

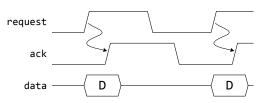

Figure 2.2 illustrates the waveform of a pipeline stage using the 4-phase protocol. Positive *request* denotes the readiness of data and positive *ack* denotes the incoming data are captured. Data are subjected to change when *request* is low. The pipeline stage is ready for new data when *ack* is low. As shown in Figure 2.2, data must remain

Figure 2.2: 4-phase handshake protocol

Figure 2.3: 2-phase handshake protocol

stable during the period between the positive edge of *request* and the positive edge of *ack*. In some implementations, data are required to remain stable until the negative edge of *request* according to different types of storage circuits.

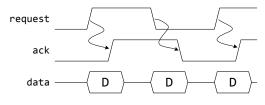

#### 2.3.2 2-phase

As described by the name, the 2-phase protocol (also called non-return-to-zero signalling or transition signalling) contains only two phases: a transition on *request* and a transition on *ack*. Figure 2.3 depicts the waveform of a 2-phase pipeline. When there is a transition on *request*, no matter positive or negative, new data are ready. In the same way, the capture of data is indicated by a transition on *ack*. Data must remain stable after the transition of *request* until the transition of *ack*. As *request* can transit immediately after *ack*, pipeline stages are always ready for new data.

Theoretically 2-phase is better than 4-phase because a set of data is delivered in two phases instead of four phases. The 2-phase protocol is fast and energy efficient. However, it has some implementation problems: The storage components in 2-phase pipeline stages are normally transistor level designs [122] which cannot be replaced with synchronous standard cells. If the combinational circuits in a 2-phase pipeline comply with the QDI delay assumption, they need to be re-designed in the same way as the storage components, which is complex and area consuming. Fault tolerance is another problem. In 4-phase pipelines, storage components are active and vulnerable to transient faults 50% of time in the worst case. On the other hand, the storage components of 2-phase pipelines are always ready for new data leading to 100% time

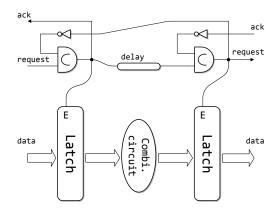

Figure 2.4: Bundled-data pipline

vulnerability. 4-phase pipelines are safer than 2-phase pipeline in the aspect of tolerance to transient faults [103].

### 2.4 Data encoding

Data are encoded in different formats, such as binary code and one-hot code, in synchronous circuits. Similarly, asynchronous circuits have various data encoding methods. Data encoding is related to different timing assumptions. It is also an important determinant to the area, speed and energy efficiency of asynchronous pipelines.

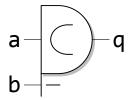

### 2.4.1 Bundled-data

Bundled-data pipelines encode data in binary code. Figure 2.4 shows a possible implementation of bundled-data pipelines.

For an *N*-bit bundled-data pipeline, the wire count of *data* is *N*. The number of available symbols is  $2^N$  and every symbol is valid. Thus the *data* bus cannot differentiate stable data from changing data. A separate control pipeline is added to identify the availability of data. In Figure 2.4, data latches are triggered by a Muller pipline. Because the control pipeline is always one bit wide, a bundled-data pipeline is also named a single-rail pipeline in some articles.

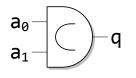

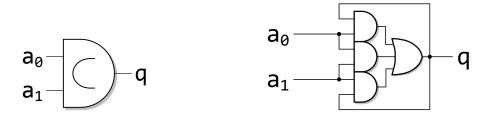

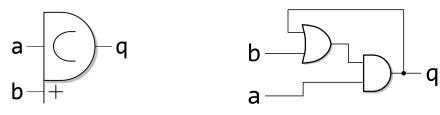

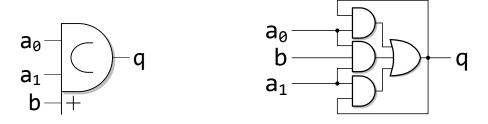

The Muller C-element is one of the most utilized primitives in asynchronous circuits. The symbol and the truth table of a 2-input C-element is shown in Figure 2.5 and Table 2.1 respectively. Its function is a combination of logical AND and latch. The output q updates when both input pins have the same value, otherwise the output value remains.

Figure 2.5: 2-input C-element

Table 2.1: Transition table of a 2-input C-element

| $a_0$ | $a_1$ | q pre | q next |

|-------|-------|-------|--------|

| 0     | 0     | _     | 0      |

| 1     | 1     | _     | 1      |

| 0     | 1     | q     | q      |

| 1     | 0     | q     | q      |

The storage components in Figure 2.4 are level triggered latches complying with the 4-phase handshake protocol. The C-elements in the control pipeline trigger data latches only when the data from the previous pipeline stage is valid (*request*+) and the next pipeline stage is ready for new data (*ack*-). The waveform of this bundled-data pipeline is already shown in Figure 2.2.

Since the control pipeline triggers latches without detecting the data bus, some delay gates are added on the *request* path to ensure that latch triggers always reach latches after data are stable. These delay gates are one of the major problems of implementing a bundled-data pipeline. To match the delay of data, the actual delay of the combinational circuit between latches is estimated and delay gates with equal delay are inserted. In other words, bundled-data pipelines assume delays are bounded, which violates the QDI delay assumption. In addition, the delay gates cannot be inserted automatically by EDA tools but are prone to be removed by them. Delay insertion introduces a heavy design burden.

It is possible to implement 2-phase bundled-data pipelines, namely a micropipeline which Ivan Sutherland first introduced [122]. A micropipeline can utilize the Muller pipeline as the trigger control logic but the data latches are double-edge triggered. As described in Section 2.3.2, these double-edge triggered latches are transistor level designs which are not available in pure standard cell design flows.

#### 2.4.2 Multi-rail

Multi-rail pipelines represent a pipeline family including several data formats. They usually comply with the QDI delay assumption.

Figure 2.6: 4-phase dual-rail pipeline

A bundled-data pipeline is not QDI for two reasons: One is that data buses cannot indicate the data availability as all symbols are valid. The other one is that the control pipeline triggers latches without detecting data. To meet with the QDI delay assumption, multi-rail pipelines use expanded symbol spaces where only a portion of symbols are valid. As long as the transform of any two valid symbols is connected by invalid symbols, data can indicate its availability and no control pipeline is needed.

#### **Dual-rail**

A dual-rail pipeline is the simplest multi-rail pipeline. Every dual-rail pipeline has two data wires:  $d_0$  and  $d_1$ . Although two digits  $\{d_1d_0\}$  provide four available symbols, only  $\{01\}$  and  $\{10\}$  are used to represent data "0" and "1" respectively. The symbol  $\{00\}$  represents idle or bubble denoting invalid data and the symbol  $\{11\}$  is illegal. In this way, the data wires denote valid data and request at the same time.

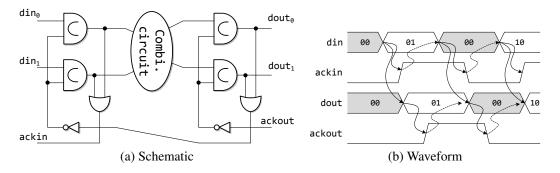

Figure 2.6 depicts a 4-phase dual-rail pipeline and its waveform. In every pipeline stage, two C-elements are used as latches triggered by *ackout*. Initially all data wires are low indicating data are not valid and *ackin* is low indicating pipeline stages are ready for new data. When a valid symbol arrives at *din*, C-elements capture this symbol and deliver it to the next pipeline stage immediately through *dout*. An OR gate is always monitoring *dout*. When the data symbol is captured, it is detected by the OR gate which sets *ackin* to high.

4-phase is also called return-to-zero because the request line is reset before another valid request. In a 4-phase dual-rail pipeline, this means every two adjacent valid symbols are intersected by an idle symbol. As shown in the waveform, when the next pipeline stage has captured the data, *ackout* (the *ackin* driving by the next stage) is driven high indicating that data can be released. When the previous pipeline stage receives an acknowledge through *ackin*, *din* is soon driven to the idle symbol {00}.

Figure 2.7: 4-bit 4-phase dual-rail pipeline

Consequently the data output *dout* of the current stage is released. The OR gate detects the idle symbol and resets *ackin* allowing the previous pipeline stage to capture new data. The idle symbol further releases the next pipeline stage which in turn resets *ackout*. A new data cycle thus starts.

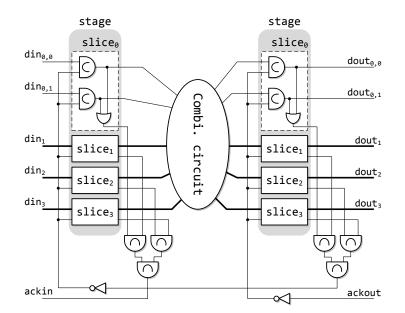

The basic dual-rail pipeline shown in Figure 2.6a delivers only one bit of data in one cycle. To form a practical pipeline that can deliver multiple data bits simultaneously, multiple dual-rail pipelines are combined and synchronized into a wide one.

Figure 2.7 demonstrates a 4-bit dual-rail pipeline built by four 1-bit dual-rail pipelines. Data on this pipeline are divided into four slices and allocated to the four bit-level pipelines in bitwise order. The four bit-level pipelines (or slices) are synchronized by the C-element tree generating a common acknowledge signal (*ackin* and *ackout*). Therefore, an acknowledge is sent only when all the four bit-level pipelines have captured valid symbols and is, vice versa, reset only when all bit-level pipelines have released their data. The C-element tree along with the OR gates in every pipeline is the completion detection circuit in wide pipelines.

#### 1-of-n

1-of-n pipelines encode data in one-hot code. A 1-of-n (n > 1) pipeline has n data wires providing  $2^n$  available symbols but only n symbols are valid. In every valid symbol, one and only one data wire is high. Table 2.2 illustrates the translation between

|   | binary | 1-of-4 |

|---|--------|--------|

| 0 | 00     | 0001   |

| 1 | 01     | 0010   |

| 2 | 10     | 0100   |

| 3 | 11     | 1000   |

|   |        |        |

Table 2.2: 1-of-4 code

1-of-4 symbols and binary symbols [3]. Because a 1-of-4 pipeline has four data wires, it provides four different data symbols and delivers two data bits in one cycle. In general, a 1-of-n pipeline delivers  $log_2n$  binary bits per cycle. The dual-rail pipeline is the smallest 1-of-n pipeline where n = 2. Similar to the 4-bit dual-rail pipeline in Figure 2.7, multiple 1-of-n pipelines can be combined into a wide pipeline.

Since the data on a 1-of-n pipeline are one-hot coded, only one data wire transits during one data cycle and the power consumption is nearly the same for different configurations of n. Increasing the number of data wires in a 1-of-n pipeline improves energy efficiency. However, a 1-of-n code is not an area efficient encoding method. Only n of  $2^n$  symbols are utilized. The total area increases proportional to n, which can be unaffordable when n is large. The number of data wires, n, in practical asynchronous on-chip networks is usually fewer than five [3, 99].

#### m-of-n

An m-of-n pipeline represents a valid data symbol by driving m of the total n wires to high. The number of valid data symbol is  $\binom{n}{m}$ . A 1-of-n pipeline can be classified as a special m-of-n pipeline where m = 1 but normally m-of-n pipelines indicate m > 1. For a pipeline with n data wires,  $\binom{n}{m}$  is larger than  $\binom{n}{1}$  when  $n \ge 4$  and n-1 > m > 1. Therefore, m-of-n pipelines can deliver more data than 1-of-n pipelines with the same wire count and they are more area efficient than 1-of-n pipelines with the same data width.

Table 2.3 shows an example of a 2-of-7 code [4]. The pipeline using this 2-of-7 code delivers four bits of data per cycle, which is equivalent to a wide pipeline built from four dual-rail pipelines or two 1-of-4 pipelines. The number of data wires used by dual-rail pipelines or 1-of-4 pipelines is eight while only seven wires are needed by the 2-of-7 pipeline. The 2-of-7 code is also promising in the aspect of power consumption. Four data wires transit per cycle in a wide dual-rail pipeline while only two data wires transit in a 2-of-7 pipeline. The total power is reduced by half.

|   | binary | 2-of-7   |    | binary | 2-of-7   |

|---|--------|----------|----|--------|----------|

| 0 | 0000   | 000-0101 | 8  | 1000   | 010-0001 |

| 1 | 0001   | 000-0110 | 9  | 1001   | 010-0010 |

| 2 | 0010   | 000-1001 | 10 | 1010   | 010-0100 |

| 3 | 0011   | 000-1010 | 11 | 1011   | 010-1000 |

| 4 | 0100   | 001-0001 | 12 | 1100   | 100-0001 |

| 5 | 0101   | 001-0010 | 13 | 1101   | 100-0010 |

| 6 | 0110   | 001-0100 | 14 | 1110   | 100-0100 |

| 7 | 0111   | 001-1000 | 15 | 1111   | 100-1000 |

Table 2.3: 2-of-7 code

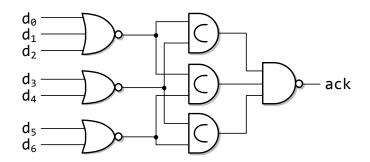

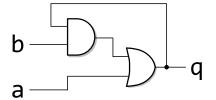

Figure 2.8: Completion detection circuit of a 2-of-7 pipeline stage

Although m-of-n pipelines are area and energy efficient, they are usually utilized to connect modules built by 1-of-n pipelines instead of to build combinational circuits directly [108]. One of the problems is the large area overhead of the completion detection circuits for m-of-n pipelines. Figure 2.8 depicts the completion detection circuit for the pipeline using the 2-of-7 code in Table 2.3. The area of this circuit is larger than that in a wide 1-of-4 pipeline with the same data width. Actually, all m-of-n codes need larger completion detection circuits than 1-of-n codes. The other problem is the area overhead of the code translation circuit. Conventional combinational circuits, especially those synchronous ones, use binary code. They can be directly transformed into circuits complying with dual-rail pipelines. Using the 1-of-4 code introduces moderate area overhead compared with dual-rail. However, it is difficult to do calculation in 2-of-7 or general m-of-n codes. Translating m-of-n to dual-rail leads to extra encoding and decoding circuits. Since the area reduction of using m-of-n codes in complex combinational circuits is normally smaller than the area overhead introduced by completion detection and code translation, m-of-n pipelines are used only in long distance communications in most circumstances.

# 2.5 Performance comparison of pipelines

In the previous sections, pipelines using different delay assumptions, handshake protocols and data encoding methods have been described. This section tries to provide a general performance comparison of all pipeline styles.

### **Pipeline delay**

Pipeline delay is the forward latency of delivering a valid data symbol from one end of an empty pipeline to the other end. It represents the delay performance of the pipelines stages. Empty multi-rail pipeline stages capture data whenever they are ready. Bundled-data pipelines insert matched delay lines in the control pipeline to ensure that latch triggers are slower than data. As a result, bundled-data pipelines normally demonstrate longer pipeline delay than multi-rail pipelines. However, it is not true when complicated combinational circuits are implemented. The multi-rail pipelines, especially the m-of-n pipelines, introduce slow combinational circuits. When the extra delay caused by these slow combinational circuits is longer than the matched delay line, bundled-data pipelines show better speed performance.

#### **Period / throughput**

Sometimes the pipelines are over-fed. Incoming data cannot be delivered as pipeline stages are busy processing old data. In this situation, the speed performance of a pipeline is determined by the period instead of the pipeline delay. The reverse of the period is the maximum throughput. It is obvious that pipeline stages may have different periods. The stage with the maximum period determines the maximum throughput because other pipeline stages are always waiting for the slowest one when the pipeline is heavily loaded. The slowest loop path is the *critical cycle* of the pipeline.

For long distance serial pipelines, 2-phase pipelines are normally faster than 4phase pipelines because no reset on request lines is needed. Bundled-data pipelines may suffer from the large data skew in long distance transmission.

For wide pipelines without complicated combinational circuits, bundled-data pipelines outperform QDI multi-rail pipelines. Although the matched delay line introduces extra latency, this overhead can be reduced if data wires are carefully routed. On the other hand, the completion detection circuits used to synchronize multiple bit-level QDI pipelines leads to significant delay. If complicated combinational circuits are implemented between pipeline stages, the delay overhead of using a multi-rail pipeline can be large. Similar to pipeline delay, bundled-data pipelines normally show better throughput thanks to their fast combinational circuits.

#### Area consumption

Multi-rail pipelines introduce significant area overhead in building data pipelines and combinational circuits due to their inefficient data encoding method. Bundled-data pipelines utilize binary coding and the combinational circuits are the same as those in synchronous circuits. Multi-rail pipelines, on the other hand, need extra data latches in pipeline stages due to the expanded symbol space, require encoders and decoders when m-of-n codes are used, and lead to large combinational circuits.

For long distance serial pipelines, m-of-n pipelines consume less area than dualrail or 1-of-n pipelines. To achieve a reasonable latency, buffers and inverters are inserted on the long wires to increase driving strength and reduce transition time. These buffers are the major area overhead. m-of-n codes reduce the wire count as well as the area. However, when complex functions are needed, the use m-of-n codes should be generally avoided because of their unaffordable area overhead in combinational circuits.

#### **Power consumption**

No clock is needed in asynchronous circuit styles therefore no dynamic power is consumed when the circuit is idle. The leakage power is proportional to the area. The key issue is the dynamic power consumed in active circuits.

Dynamic power is related to toggle rate — the number of transitions during in a certain period of time. Table 2.4 shows a simple estimation of the toggle rate of different asynchronous pipelines. In the table, D denotes the equivalent data width. The toggle rates of 4-phase QDI pipelines are two times that of 2-phase pipelines because all wires return to zero every cycle. Bundled-data pipelines represent data in binary code. On average 50% of data wires transit very cycle. Multi-rail pipelines represent data in 1-of-n or m-of-n codes. In each 4-phase multi-rail pipeline, one wire (dual-rail or 1-of-n) or m wires (m-of-n) must transit twice every cycle. All pipelines have some extra toggles introduced by the *ack* line and the *request* line (only in bundled-data pipelines).

|              | 4-phase                                                                | 2-phase                                                        |

|--------------|------------------------------------------------------------------------|----------------------------------------------------------------|

| bundled-data | $\frac{D}{2} + 4$                                                      | $\frac{D}{2} + 2$                                              |

| dual-rail    | 2D + 2                                                                 | D+1                                                            |

| 1-of-n       | $\frac{2D}{\lfloor \log_2 n \rfloor} + 2$                              | $\frac{D}{\lfloor \log_2 n \rfloor} + 1$                       |

| m-of-n       | $\frac{\frac{2mD}{\left\lfloor \log_2 \binom{n}{m} \right\rfloor} + 2$ | $\frac{mD}{\left\lfloor \log_2\binom{n}{m} \right\rfloor} + 1$ |

Table 2.4: Average toggle rate

Based on the toggle rates in Table 2.4, we can draw some simple conclusions for asynchronous pipelines without complex combinational circuits:

- 2-phase pipelines consume less dynamic power than 4-phase pipelines.

- Bundled-data pipelines consume less power than dual-rail pipelines.

- 1-of-n pipelines consume less power than dual-rail pipelines.

The power consumption comparison between m-of-n pipelines and 1-of-n pipelines is hard to evaluate. In theory, the toggle rate of m-of-n codes is smaller than 1-of-n codes. On the other hand, m-of-n pipelines require complicated completion detection circuits which cause extra power consumption.

# 2.6 Arbiter

Arbiters are an important class of combinational components in asynchronous onchip networks where arbitration occurs frequently. This section introduces the arbiters which have been used in state-of-the-art asynchronous on-chip networks.

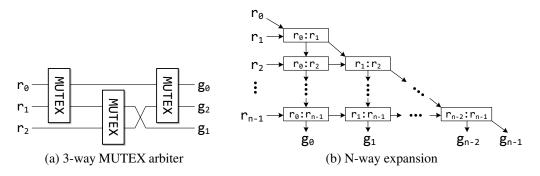

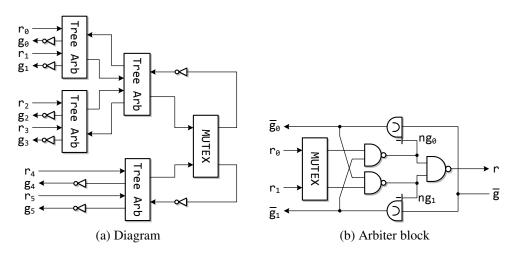

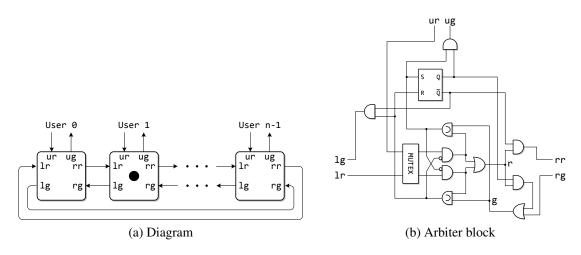

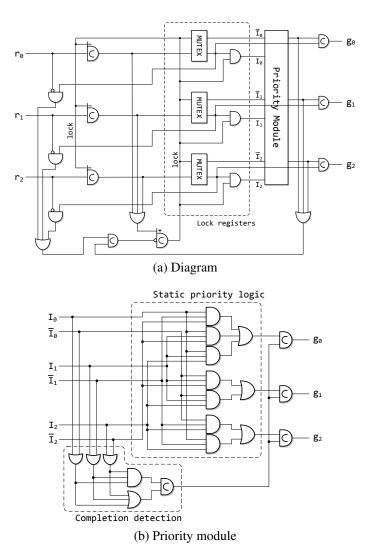

### 2.6.1 Multi-way MUTEX arbiter