# A ROUTER FOR MASSIVELY-PARALLEL NEURAL SIMULATION

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Engineering and Physical Sciences

2010

By Jian Wu School of Computer Science

# Contents

| A                             | Abstract |                                                       |           |  |

|-------------------------------|----------|-------------------------------------------------------|-----------|--|

| D                             | eclar    | ation                                                 | 12        |  |

| C                             | opyri    | ight                                                  | 13        |  |

| A                             | ckno     | wledgements                                           | 14        |  |

| 1                             | Intr     | roduction                                             | 15        |  |

|                               | 1.1      | Neural simulation                                     | 17        |  |

|                               | 1.2      | Literature review                                     | 17        |  |

|                               |          | 1.2.1 Software neural simulators                      | 18        |  |

|                               |          | 1.2.2 Neural simulations on general-purpose computers | 18        |  |

|                               |          | 1.2.3 Neurocomputers                                  | 19        |  |

|                               |          | 1.2.4 Limitations of previous neural simulators       | 21        |  |

|                               | 1.3      | Design considerations                                 | 23        |  |

|                               | 1.4      | Contributions                                         | 24        |  |

| 1.5 Dissertation organization |          | Dissertation organization                             | 25        |  |

|                               | 1.6      | Publications                                          | 25        |  |

| <b>2</b>                      | Neı      | urcomputing                                           | <b>28</b> |  |

|                               | 2.1      | Introduction                                          | 28        |  |

|                               | 2.2      | Biological neurons and neural networks                | 30        |  |

|                               | 2.3      | Mathematical neurobiology                             | 32        |  |

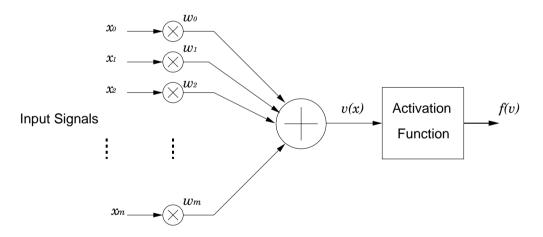

|                               |          | 2.3.1 Artificial neuron                               | 32        |  |

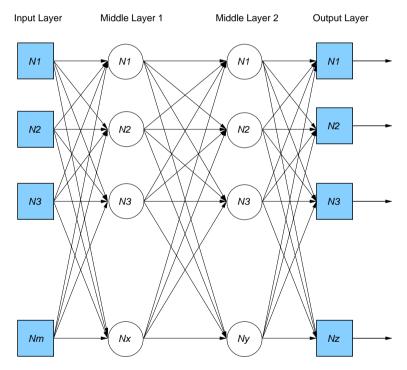

|                               |          | 2.3.2 Artificial neural networks                      | 33        |  |

|                               | 2.4      | Spiking neural network                                | 35        |  |

|                               |          | 2.4.1 Generations of spiking neural models            | 36        |  |

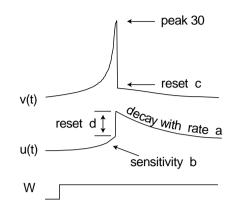

|          |                                     | 2.4.2 Izhikevich model                           | 36        |

|----------|-------------------------------------|--------------------------------------------------|-----------|

|          | 2.5                                 | Summary                                          | 37        |

| 0        | NT (                                |                                                  |           |

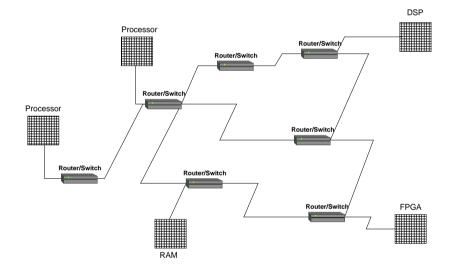

| 3        |                                     | works-on-Chip                                    | <b>39</b> |

|          | 3.1                                 | Introduction                                     | 39        |

|          | 3.2                                 | Benefits of adopting NoCs                        | 41        |

|          | 3.3                                 | NoC topologies                                   | 42        |

|          | 3.4                                 | Router architecture and switching schemes        | 45        |

|          |                                     | 3.4.1 Router architecture                        | 46        |

|          |                                     | 3.4.2 Switching schemes                          | 46        |

|          | 3.5                                 | Routing algorithms                               | 48        |

|          |                                     | 3.5.1 Source routing and distributed routing     | 48        |

|          |                                     | 3.5.2 Deterministic routing and adaptive routing | 49        |

|          | 3.6                                 | Deadlock and livelock avoidance                  | 50        |

|          | 3.7                                 | Summary                                          | 51        |

| 4        | A NoC-based neurocomputing platform |                                                  |           |

|          | 4.1                                 | Introduction                                     | 52        |

|          | 4.2                                 | Design issues                                    | 54        |

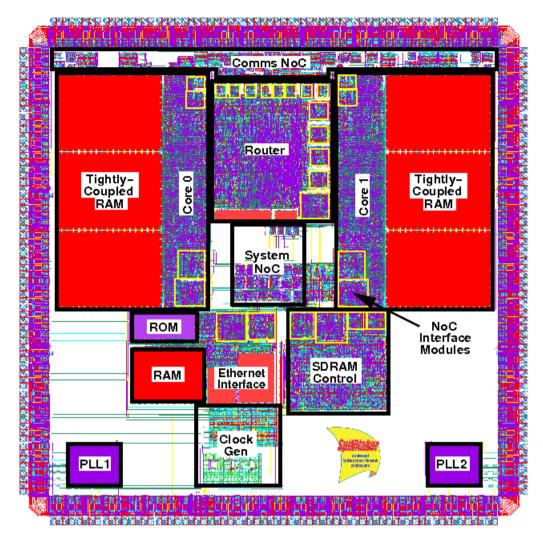

|          | 4.3                                 | Overview of SpiNNaker                            | 56        |

|          | 1.0                                 | 4.3.1 Multicasting                               | 57        |

|          |                                     | 4.3.2 Processing node                            | 60        |

|          |                                     | 4.3.3 Fault-tolerance                            | 62        |

|          | 4.4                                 | Event-driven communication                       | 62        |

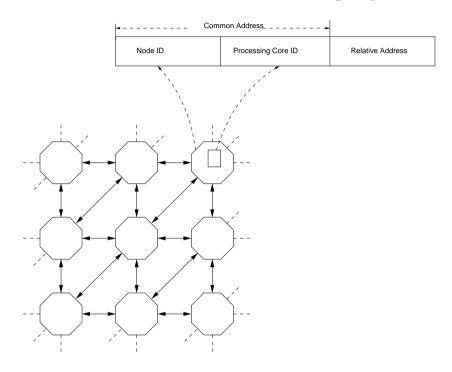

|          | 7.7                                 | 4.4.1 Address event representation               | 63        |

|          |                                     | 4.4.2 AER communication based on a router        | 64        |

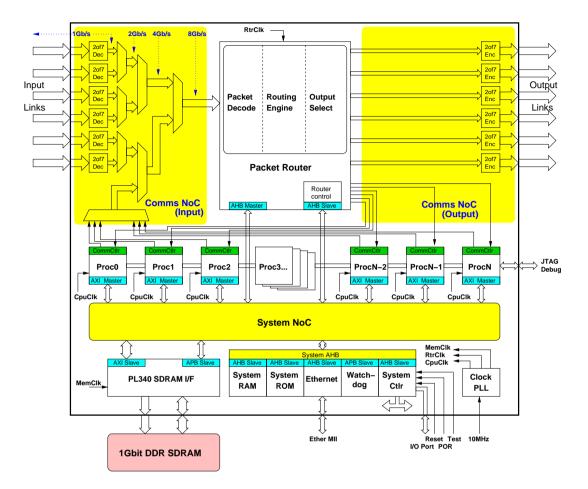

|          | 4.5                                 | Communication NoC                                | 65        |

|          | 4.0<br>4.6                          |                                                  | 66        |

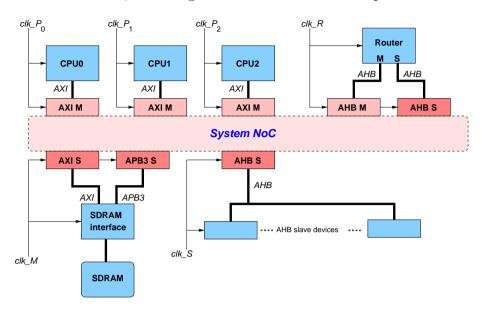

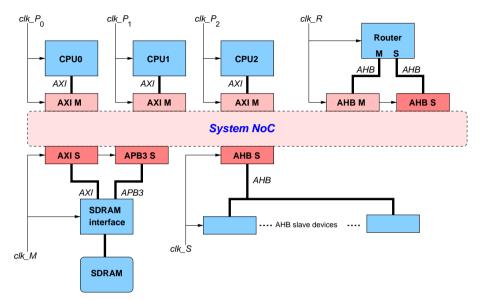

|          |                                     | System NoC                                       |           |

|          | 4.7                                 | Traffic load estimation                          | 67        |

|          | 4.8                                 | Summary                                          | 70        |

| <b>5</b> | A r                                 | outer in a neural platform                       | <b>71</b> |

|          | 5.1                                 | Introduction                                     | 71        |

|          | 5.2                                 | Routing requirements                             | 72        |

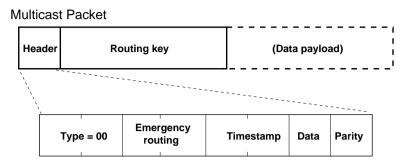

|          |                                     | 5.2.1 Multicast packets                          | 73        |

|          |                                     | 5.2.2 Point-to-point packets                     | 77        |

|   |     | 5.2.3   | Nearest-neighbour packets                                                                                                                                        |

|---|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

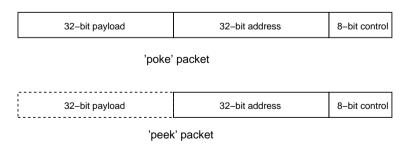

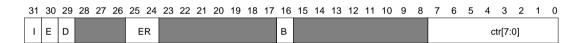

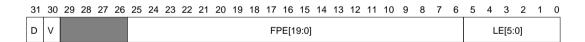

|   | 5.3 | Packet  | formats                                                                                                                                                          |

|   | 5.4 | Adapti  | ve routing $\ldots \ldots 81$                                                       |

|   | 5.5 | Router  | $configurations \dots \dots$                               |

|   |     | 5.5.1   | Routing table configuration                                                                                                                                      |

|   |     | 5.5.2   | Register configuration                                                                                                                                           |

|   |     | 5.5.3   | Programmable diagnostic counters                                                                                                                                 |

|   | 5.6 | Router  | function stage division                                                                                                                                          |

|   | 5.7 | Summa   | ary                                                                                                                                                              |

| 6 | Rou | iter im | plementation 91                                                                                                                                                  |

|   | 6.1 | Error h | $and ling \dots \dots$                                     |

|   | 6.2 | Packet  | arbitration                                                                                                                                                      |

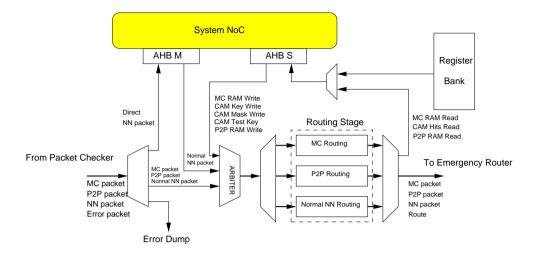

|   | 6.3 | Routin  | g stage                                                                                                                                                          |

|   |     | 6.3.1   | Multicast routing                                                                                                                                                |

|   |     | 6.3.2   | Point-to-point routing                                                                                                                                           |

|   |     | 6.3.3   | Nearest-neighbour routing $\ldots \ldots \ldots$ |

|   | 6.4 | Packet  | demultiplexing $\ldots \ldots 102$                             |

|   | 6.5 | Outgoi  | ng routing $\ldots \ldots 103$                                 |

|   |     | 6.5.1   | Adaptive routing controller                                                                                                                                      |

|   |     | 6.5.2   | Deadlock avoidance                                                                                                                                               |

|   |     | 6.5.3   | Adaptive routing timer                                                                                                                                           |

|   | 6.6 | Interfa | cing with the System NoC                                                                                                                                         |

|   |     | 6.6.1   | AHB master interface                                                                                                                                             |

|   |     | 6.6.2   | AHB slave interface                                                                                                                                              |

|   | 6.7 | Summa   | ary 109                                                                                                                                                          |

| 7 | Pip | elining | 110                                                                                                                                                              |

|   | 7.1 | Introdu | $action \dots \dots$                                       |

|   | 7.2 | The G   | ALS approach for inter-neuron communication $\ldots \ldots \ldots 111$                                                                                           |

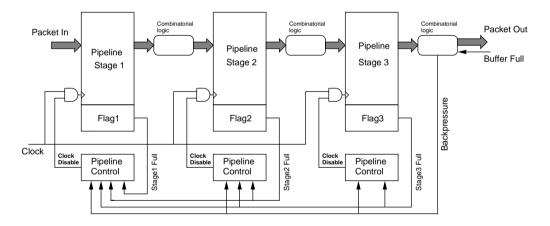

|   | 7.3 | Synchr  | onous latency-insensitive pipeline                                                                                                                               |

|   |     | 7.3.1   | Synchronous handshake pipeline                                                                                                                                   |

|   |     | 7.3.2   | Elastic buffering                                                                                                                                                |

|   |     | 7.3.3   | Flow-control                                                                                                                                                     |

|   |     | 7.3.4   | Clock gating                                                                                                                                                     |

|   | 7.4 | Input s | ynchronizing buffer                                                                                                                                              |

|   | 7.5 | Summary                                                                                                                                                       | .15 |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8 | Eva | luation 1                                                                                                                                                     | 17  |

|   | 8.1 | Functional verification                                                                                                                                       | 18  |

|   | 8.2 | Multi-chip SpiNNaker system simulation                                                                                                                        | 21  |

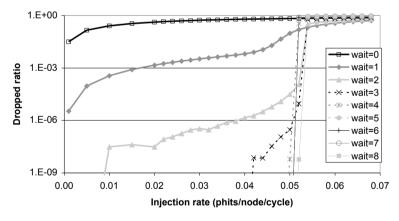

|   | 8.3 | Optimum buffer length                                                                                                                                         | 22  |

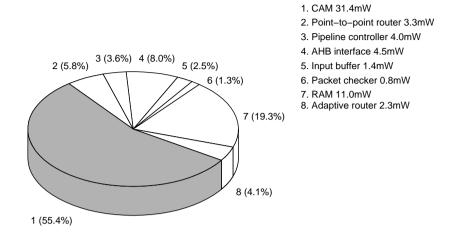

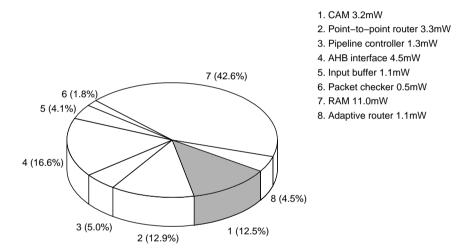

|   | 8.4 | Power measurement                                                                                                                                             | 25  |

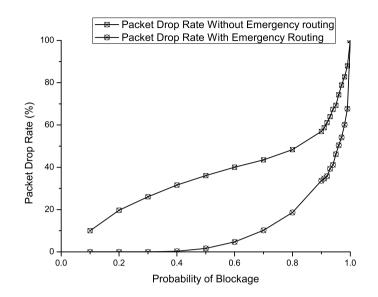

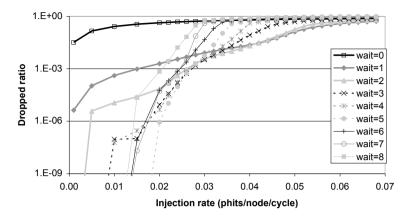

|   | 8.5 | Dropped packet ratio measurement                                                                                                                              | 28  |

|   |     | 8.5.1 Dropped packet ratio of a stand-alone router                                                                                                            | 28  |

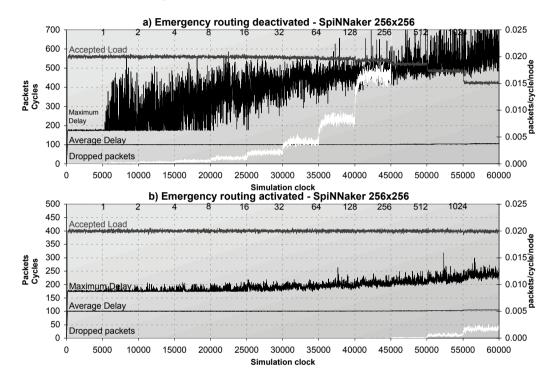

|   |     | 8.5.2 Dropped packet ratio of the SpiNNaker network 1                                                                                                         | 30  |

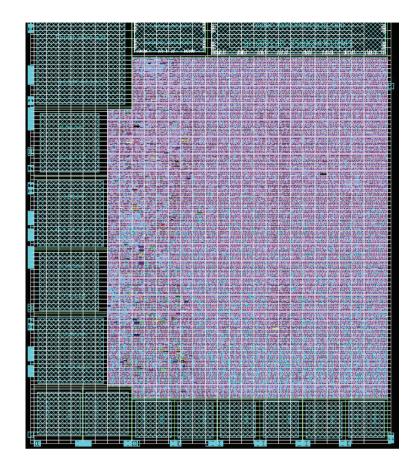

|   | 8.6 | Layout                                                                                                                                                        | 35  |

|   | 8.7 | Summary                                                                                                                                                       | 36  |

| 9 | Con | nclusion 1                                                                                                                                                    | 38  |

|   | 9.1 | Contributions and limitations                                                                                                                                 | 39  |

|   |     | 9.1.1 Efficient multicast neural event routing                                                                                                                | 39  |

|   |     | 9.1.2 Area                                                                                                                                                    | 40  |

|   |     | 9.1.3 Programmability                                                                                                                                         | 40  |

|   |     | 9.1.4 Fault-tolerance                                                                                                                                         | 41  |

|   |     | 9.1.5 Debugging                                                                                                                                               | 41  |

|   |     | 9.1.6 Power efficiency $\ldots \ldots \ldots$ | 41  |

|   |     | 9.1.7 Latency insensitivity                                                                                                                                   | 42  |

|   |     | 9.1.8 Scalability                                                                                                                                             | 42  |

|   |     | 9.1.9 Switching techniques                                                                                                                                    | 42  |

|   |     | 9.1.10 Pipelining                                                                                                                                             | 43  |

|   |     | 9.1.11 Monitoring $\ldots \ldots 1$                                                     | .43 |

|   | 9.2 | Future work                                                                                                                                                   | .43 |

|   |     | 9.2.1 Alternative implementation of the CAM                                                                                                                   | .44 |

|   |     | 9.2.2 QoS enhancements                                                                                                                                        | .44 |

|   |     | 9.2.3 Intermediate circuit test chip                                                                                                                          | 45  |

|   | 9.3 | Perspective of neurocomputing on NoCs                                                                                                                         | .46 |

| Α | Ada | aptive routing algorithm 1                                                                                                                                    | 47  |

| В | Reg | gisters definitions 1                                                                                                                                         | 50  |

|   | B.1 | Register summary                                                                                                                                              | 150 |

|   | B.2 | Register 0 (r0): control $\ldots \ldots $                                        | 50  |

| B.3  | Register 1 (r1): status $\ldots \ldots 151$                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------|

| B.4  | Register 2 (r2): error header $\ldots \ldots 152$         |

| B.5  | Register 3 (r3): error routing $\ldots \ldots 152$ |

| B.6  | Register 4 (r4): error payload $\ldots \ldots 153$                      |

| B.7  | Register 5 (r5): error status $\ldots \ldots 153$                       |

| B.8  | Register 6 (r6): dump header $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 154$                               |

| B.9  | Register 7 (r7): dump routing $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 154$                              |

| B.10 | 0 Register 8 (r8): dump payload $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 154$                            |

| B.11 | 1 Register 9 (r9): dump outputs $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 155$                            |

| B.12 | 2 Register 10 (r10): dump status $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 155$                                  |

| B.13 | 3 Register T1 (rT1): hardware test register $\ldots \ldots \ldots \ldots \ldots 156$                                                   |

| B.14 | 4 Register T2 (rT2): hardware test key $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 156$                                          |

|      |                                                                                                                                        |

#### Bibliography

# List of Tables

| 5.1 | Packet header summary 80                                                                                                                        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2 | Routing tables                                                                                                                                  |

| 5.3 | Diagnostic counter enable/reset                                                                                                                 |

| 5.4 | Diagnostic control register definition                                                                                                          |

| 6.1 | Point-to-point routing entry decoding                                                                                                           |

| 6.2 | Nearest-neighbour route decoding                                                                                                                |

| B.1 | Register summary                                                                                                                                |

| B.2 | Register 0 – router control register                                                                                                            |

| B.3 | Register 1 – router status                                                                                                                      |

| B.4 | Register 2 – error header $\ldots \ldots 152$        |

| B.5 | Register 5 – error status $\ldots \ldots 153$               |

| B.6 | Register 6 – dump header                                                                                                                        |

| B.7 | Register 9 – dump outputs                                                                                                                       |

| B.8 | Register $10 - dump$ status $\dots \dots \dots$ |

| B.9 | Register T1 – hardware test register 1                                                                                                          |

# List of Figures

| A generic neurocomputer                              | 20      |

|------------------------------------------------------|---------|

| NESPINN                                              | 21      |

| CNAPS                                                | 21      |

| SYNAPSE                                              | 22      |

| Biological neuron                                    | 31      |

| Graphical representation of an artificial neuron     | 32      |

| Layer structured neural network                      | 34      |

| Izhikevich model's voltage potential                 | 37      |

| An MPSoC based on NoC                                | 40      |

| A bus handling conflicts                             | 41      |

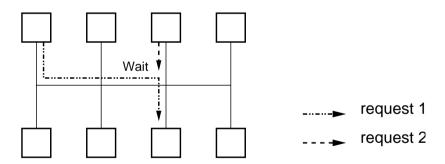

| A 3 $\times$ 3 mesh (a) and a 3 $\times$ 3 torus (b) | 43      |

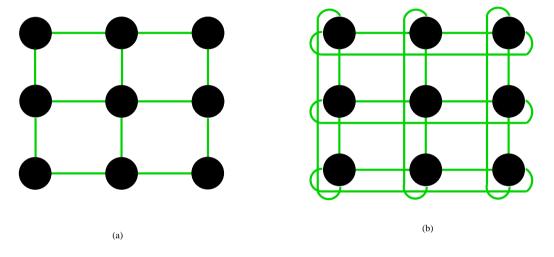

| Hypercube topology                                   | 44      |

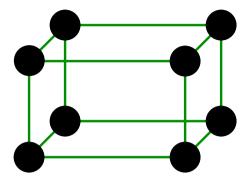

| A tree (a) and a star (b) $\ldots$                   | 44      |

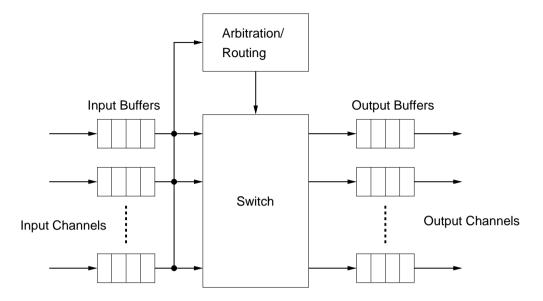

| A generic router architecture                        | 46      |

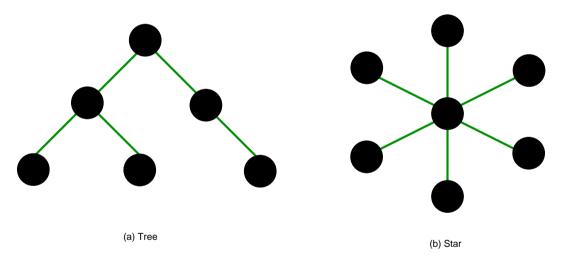

| Deadlock                                             | 50      |

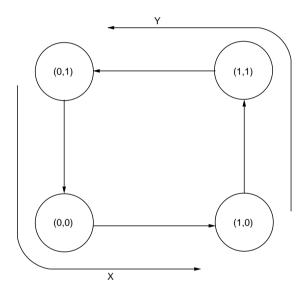

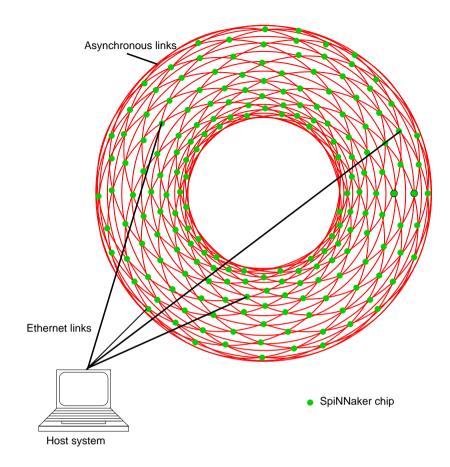

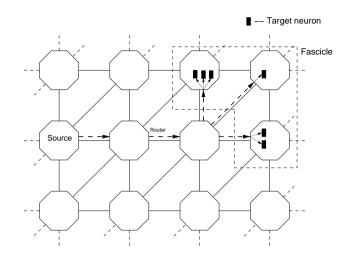

| System network topology                              | 57      |

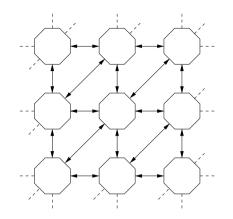

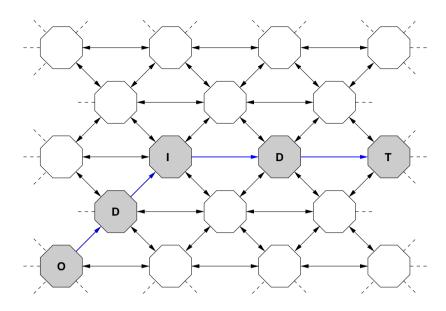

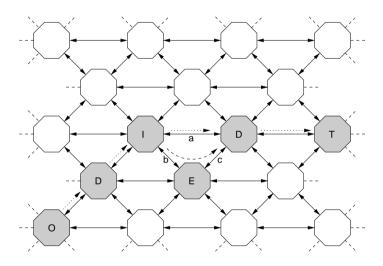

| A small array of nodes                               | 58      |

| A router for on-/inter-chip packet switching         | 59      |

| Multicasting                                         | 60      |

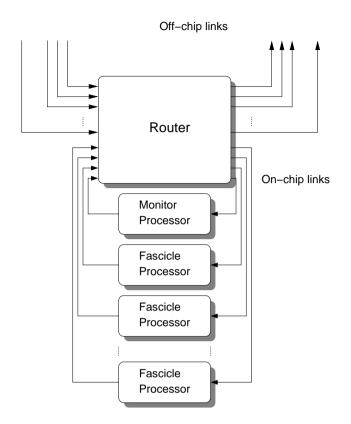

| SpiNNaker processing node                            | 61      |

| AER packet with a relative address                   | 64      |

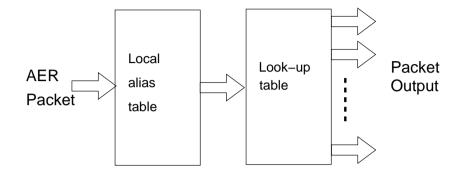

| AER-based router                                     | 65      |

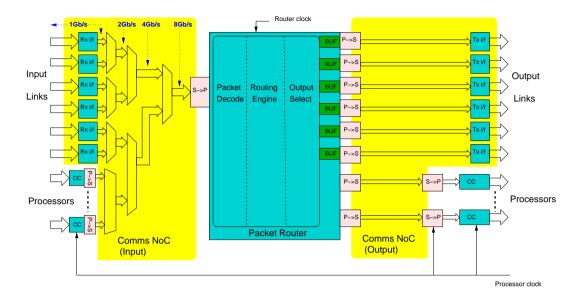

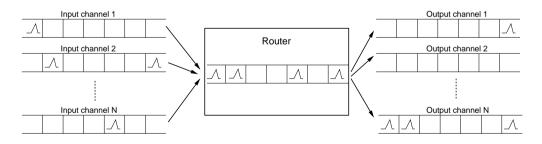

| Communication NoC                                    | 66      |

|                                                      | 67      |

| Non-uniform traffic neural traffic                   | 69      |

|                                                      | NESPINN |

| 5.1                                                                                                                             | Default routing                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

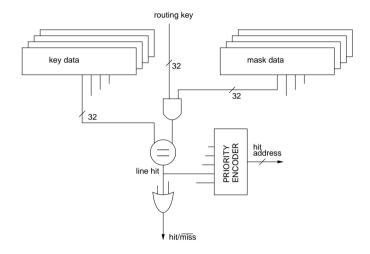

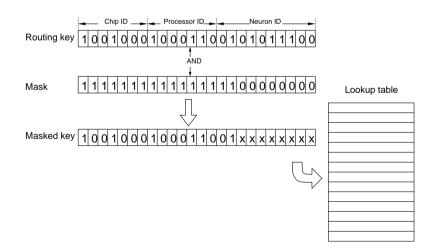

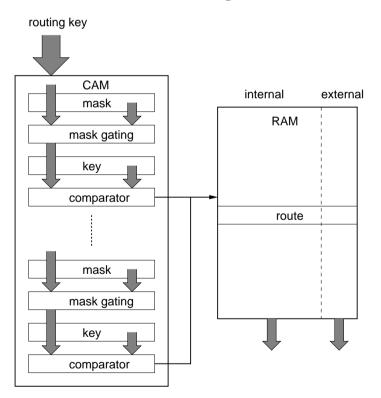

| 5.2                                                                                                                             | Masked associative memory logic                                                                                                                                                                                                                                                                                                        |

| 5.3                                                                                                                             | Multicast routing with mask                                                                                                                                                                                                                                                                                                            |

| 5.4                                                                                                                             | Packet formats                                                                                                                                                                                                                                                                                                                         |

| 5.5                                                                                                                             | An example of adaptive routing                                                                                                                                                                                                                                                                                                         |

| 5.6                                                                                                                             | Key comparison and route lookup                                                                                                                                                                                                                                                                                                        |

| 5.7                                                                                                                             | Counter filter register                                                                                                                                                                                                                                                                                                                |

| 5.8                                                                                                                             | Diagnostic control register                                                                                                                                                                                                                                                                                                            |

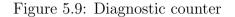

| 5.9                                                                                                                             | Diagnostic counter                                                                                                                                                                                                                                                                                                                     |

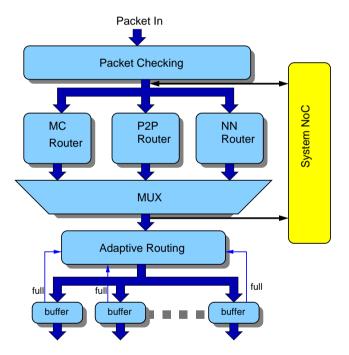

| 5.10                                                                                                                            | Router architecture                                                                                                                                                                                                                                                                                                                    |

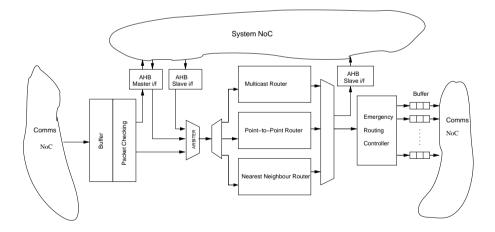

| 6.1                                                                                                                             | Router's internal structure                                                                                                                                                                                                                                                                                                            |

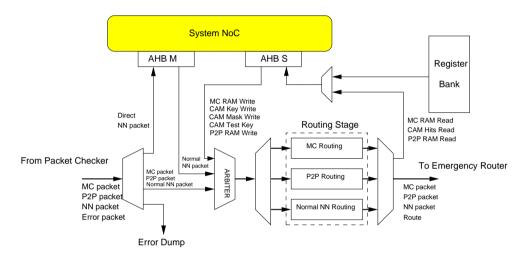

| 6.2                                                                                                                             | Packet arbitration and routing                                                                                                                                                                                                                                                                                                         |

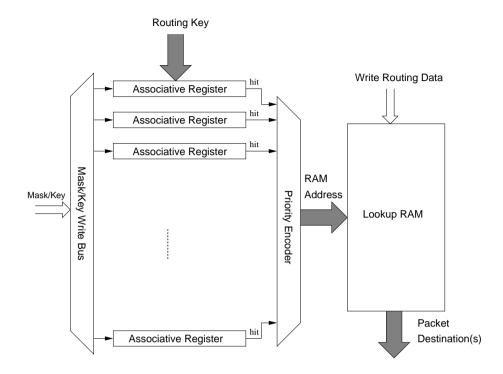

| 6.3                                                                                                                             | Content addressable memory                                                                                                                                                                                                                                                                                                             |

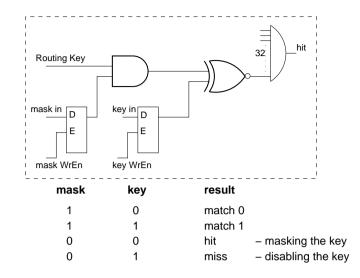

| 6.4                                                                                                                             | Associative register                                                                                                                                                                                                                                                                                                                   |

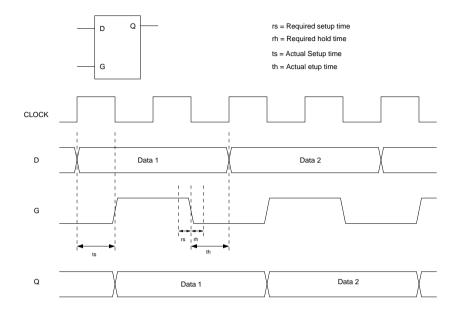

| 6.5                                                                                                                             | Timing diagram of the CAM                                                                                                                                                                                                                                                                                                              |

| 6.6                                                                                                                             | Nearest-neighbour routing algorithm                                                                                                                                                                                                                                                                                                    |

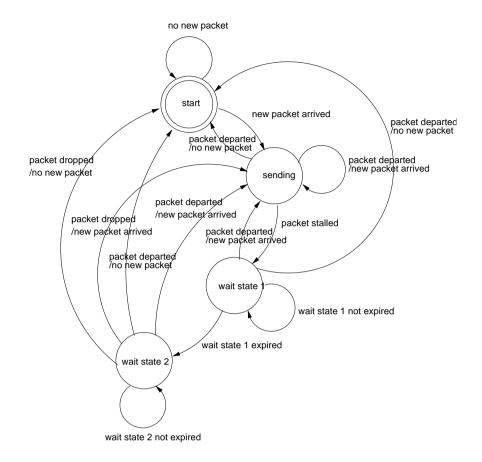

| 6.7                                                                                                                             | States of the adaptive routing controller                                                                                                                                                                                                                                                                                              |

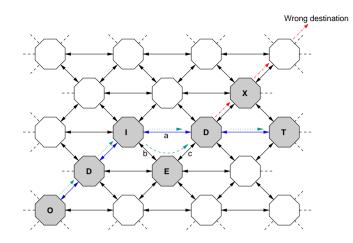

| 6.8                                                                                                                             | Redirecting an emergency routed packet back to the 'normal' route 105                                                                                                                                                                                                                                                                  |

| 6.9                                                                                                                             | System NoC organization                                                                                                                                                                                                                                                                                                                |

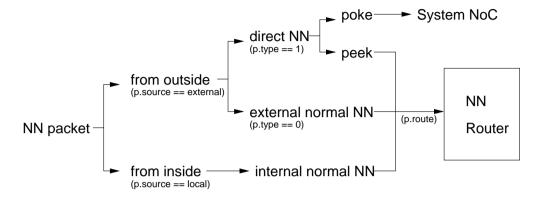

| 6.10                                                                                                                            | Direct nearest-neighbour packets                                                                                                                                                                                                                                                                                                       |

| 7.1                                                                                                                             | Global stall control                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                        |

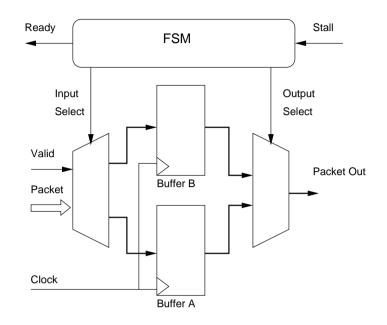

| 7.2                                                                                                                             | Data flows to the router                                                                                                                                                                                                                                                                                                               |

| $7.2 \\ 7.3$                                                                                                                    | Data flows to the router114Interchangeable buffer116                                                                                                                                                                                                                                                                                   |

|                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                        |

| 7.3                                                                                                                             | Interchangeable buffer                                                                                                                                                                                                                                                                                                                 |

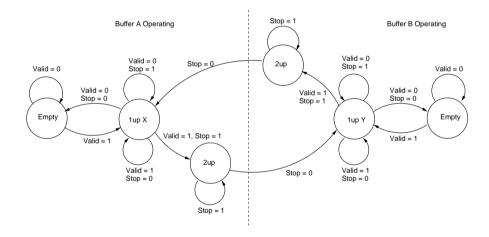

| 7.3<br>7.4                                                                                                                      | Interchangeable buffer                                                                                                                                                                                                                                                                                                                 |

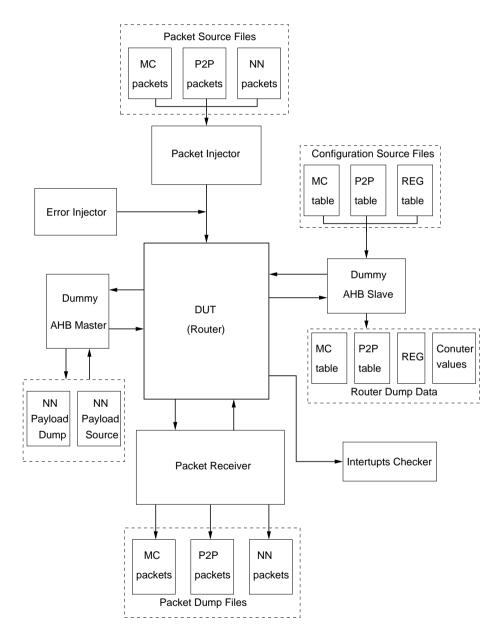

| <ol> <li>7.3</li> <li>7.4</li> <li>8.1</li> </ol>                                                                               | Interchangeable buffer       116         State machine for input buffer       116         Single router test wrapper       118                                                                                                                                                                                                         |

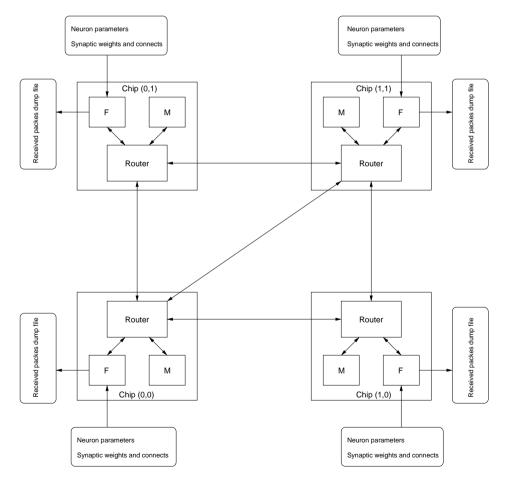

| <ol> <li>7.3</li> <li>7.4</li> <li>8.1</li> <li>8.2</li> </ol>                                                                  | Interchangeable buffer       116         State machine for input buffer       116         Single router test wrapper       118         Four-chip test wrapper       118                                                                                                                                                                |

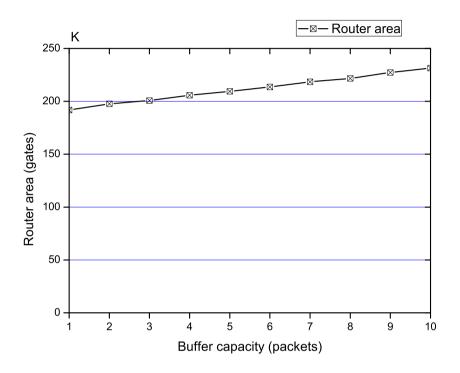

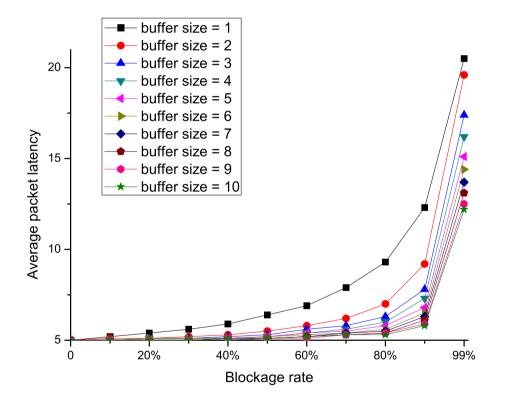

| <ol> <li>7.3</li> <li>7.4</li> <li>8.1</li> <li>8.2</li> <li>8.3</li> </ol>                                                     | Interchangeable buffer116State machine for input buffer116Single router test wrapper116Four-chip test wrapper116Router size vs buffer capacity112                                                                                                                                                                                      |

| <ol> <li>7.3</li> <li>7.4</li> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> </ol>                                        | Interchangeable buffer       116         State machine for input buffer       116         Single router test wrapper       118         Four-chip test wrapper       112         Router size vs buffer capacity       123         Router performance under different buffer lengths       124                                           |

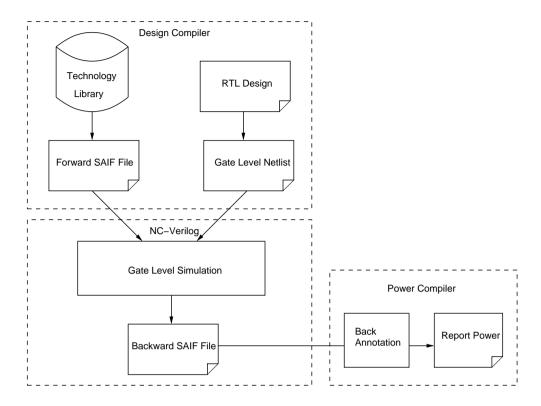

| <ol> <li>7.3</li> <li>7.4</li> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> </ol>                           | Interchangeable buffer116State machine for input buffer116Single router test wrapper118Four-chip test wrapper121Router size vs buffer capacity123Router performance under different buffer lengths124The Scenario of dynamic power estimation126                                                                                       |

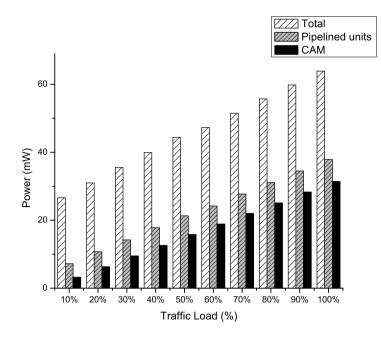

| <ol> <li>7.3</li> <li>7.4</li> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>8.6</li> </ol>              | Interchangeable buffer116State machine for input buffer116Single router test wrapper118Four-chip test wrapper121Router size vs buffer capacity123Router performance under different buffer lengths124The Scenario of dynamic power estimation126Power estimation flow through gate level simulation127                                 |

| <ol> <li>7.3</li> <li>7.4</li> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>8.6</li> <li>8.7</li> </ol> | Interchangeable buffer116State machine for input buffer116Single router test wrapper118Four-chip test wrapper121Router size vs buffer capacity123Router performance under different buffer lengths124The Scenario of dynamic power estimation126Power estimation flow through gate level simulation127Dynamic power vs traffic load128 |

| 8.11 | $256 \times 256$ in absence of failures $\ldots \ldots \ldots$ | 131   |

|------|-------------------------------------------------------------------------------------------------------------------------------|-------|

| 8.12 | $256 \times 256$ with 1 link failure                                                                                          | 132   |

| 8.13 | $256 \times 256$ with 2 link failures $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$          | 132   |

| 8.14 | $256 \times 256$ with 64 link failures $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                | 133   |

| 8.15 | Evolution of accepted packet load, maximum latency and dropped                                                                |       |

|      | packets for different system confiurations                                                                                    | 134   |

| 8.16 | Layout of the SpiNNaker router                                                                                                | 136   |

| 8.17 | A die plot of the SpiNNaker test chip                                                                                         | 137   |

| D 1  |                                                                                                                               | 1 - 1 |

| B.1  | Register 0 definition                                                                                                         | 151   |

| B.2  | Register 1 definition                                                                                                         | 151   |

| B.3  | Register 2 definition                                                                                                         | 152   |

| B.4  | Register 3 definition                                                                                                         | 153   |

| B.5  | Register 4 definition                                                                                                         | 153   |

| B.6  | Register 5 definition                                                                                                         | 153   |

| B.7  | Register 6 definition                                                                                                         | 154   |

| B.8  | Register 7 definition                                                                                                         | 154   |

| B.9  | Register 8 definition                                                                                                         | 155   |

| B.10 | Register 9 definition                                                                                                         | 155   |

| B.11 | Register 10 definition                                                                                                        | 155   |

| B.12 | Register T1 definition                                                                                                        | 156   |

| B.13 | Register T2 definition                                                                                                        | 156   |

|      |                                                                                                                               |       |

### Abstract

Spiking neural network modelling is naturally suited to massively-parallel computation because of its characteristics such as simple processing components, highly-parallel communications, and small local memory requirement. However, because the real-time modelling of large-scale spiking neural networks demands very high communications efficiency, it is hard to implement on a general-purpose computer. As the feature size of transistors shrinks, a Multi-processor Systemson-Chips (MPSoCs) with a Network-on-Chip (NoC) architecture has emerged as a promising platform for large-scale spiking neural network simulations.

This dissertation presents design methodologies for a communication router in an application-specific NoC. The router realizes neural connectivity with flexibility, power-efficiency, high throughput and fault-tolerance. Three major contributions are:

- A programable multicast routing infrastructure to realize neural network communications is first presented.

- Then a look-ahead pipeline control mechanism is implemented. It minimizes power consumption, and manages pipeline usage in a smart way, thereby maximizing the throughput.

- An adaptive routing mechanism for multicasting is investigated to achieve system-level fault-tolerance and avoid deadlocks.

The router is a sub-system of SpiNNaker – a massively-parallel multiprocessor platform for real-time simulations of large-scale neural networks. Based on this platform, experimental results show that the proposed router contributes significantly to both performance and energy/resource efficiency.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the "Copyright") and s/he has given The University of Manchester the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

- ii. Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the John Rylands University Library of Manchester. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

- iii. The ownership of any patents, designs, trade marks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and exploitation of this thesis, the Copyright and any Intellectual Property Rights and/or Reproductions described in it may take place is available from the Head of School of School of Computer Science (or the Vice-President).

### Acknowledgements

I would like to express my deep appreciation to all those who have supported me in finishing this thesis. I would like to thank first of all my supervisor, Prof. Steve Furber, for his invaluable insights, inspirations and suggestions. He has given me great supervision and guidance throughout the course of my research.

I would also like to thank my advisor, Dr. Jim Garside, who helped out tremendously on my work with his great patience. I am also grateful to Dr. Viv Woods who has helped me to improve the thesis by giving comments and proof-reading.

I would also like to extend my gratitude to the people at APT group, especially to those colleagues who have contributed to the SpiNNaker project (Luis Plana, Steve Temple, Yebin Shi, too many to list here). I had a great time working with them and they have been very helpful, giving advice and sharing knowledge with me.

Finally, and most importantly, I would like to thank my mother, Yuming Song, father, Yazhou Wu, and brother, Yang Wu, who have always been very supportive of my goals. Their encouragement was extremely important for me to complete this long journey.

### Chapter 1

## Introduction

Biological brains are capable of performing many intelligent tasks, such as face recognition, speech processing and language learning, that conventional computational systems still find difficult [Vig94][MB90][MC93]. The brain is a computing system which exploits massive parallelism, with limited elemental processing speed. Here, a huge number of slow, simple elements execute in parallel and exhibit remarkable characteristics. It is natural for scientists seeking engineered solutions to the above tasks to consider mimicking the neural networks of biological brains. However, despite much research into how neural networks work, knowledge in this area remains limited.

Simulation scale is one of the key factors of neural network modelling. The simulation of a human brain requires about 100 billion neurons and even more interconnects. Such a large-scale neural network simulation remains well beyond the reach of current computation systems, particularly in real-time. The 'real-time' concept means that the simulation finishes no later than do an equal number of biological neurons performing an equivalent task (which typically means around 1 ms per step) [JSR+97].

The emergence of massively-parallel computational systems offers an opportunity to bridge the gap between the computational requirements of large-scale neural networks and the capabilities of relevant platforms. Cluster supercomputers, commonly used by neuroscientists for neural network simulations, are the current model of conventional parallel systems. These systems are capable of distributed processing and information storage, thereby delivering high computing power, but must still overcome the huge demand for data exchange between processing nodes if a truly real-time simulation is to be achieved. As transistor feature sizes continue to shrink, Multi-Processor System-on-Chip (MPSoC) technology using Network-on-Chip (NoC) communication schemes has emerged as a promising solution for massively-parallel computing. The application of MPSoC technology to conduct research on large-scale spiking neural network simulations has attracted the attention of both computer engineers and neuroscientists. An MPSoC has many characteristics similar to those of a spiking neural network [Con97]:

- They are both parallel systems.

- They both comprise networks of processing components. The basic processing element of a neural network is the neuron, which can be described by relatively simple models, such as the Izhikevich model and the leaky integrate-and-fire model [Izh03][Tuc88]; the basic processing element of an MPSoC system is a microprocessor core, usually with a simple architecture because of energy-efficiency considerations.

- They both have highly parallel connectivity between the processing elements. A neural network uses many synapses to connect neurons; an MP-SoC uses an NoC to connect processing cores although it may multiplex several channels over each physical link.

- They are both event-driven: A spiking neural network communicates using spike events; an MPSoC communicates using discrete data packets.

The similarity between their characteristics makes the modelling of spiking neural networks naturally suited to the parallel computations on an MPSoC system, making it worthwhile to develop a dedicated MPSoC platform with special features to support neural network modelling. The platform should enable neuroscientists to achieve new insights into the operational principles of neural networks by running real-time simulations, with biologically-realistic levels of neural connectivity. The improved understanding of these natural systems will, perhaps, inspire computer engineers in their quest for ever-better high-performance computational architectures.

A neural computation system must achieve balance between its processing, storage and communication requirements [FTB06]. This dissertation focuses principally on the communication issues, and presents the design of a multicast router. The router is the core communication unit of the SpiNNaker system – a universal spiking neural network simulation platform. The design of the router has to consider both the requirements of supporting neural network communications and the feasibility of its implementation in an electronic system.

#### **1.1** Neural simulation

Neural simulation addresses the task of understanding the structure of the brain and applying it to bio-inspired information processing systems [BJ90]. It is one of the most rapidly developing research fields which attracts psychologists, neuroscientists and computer scientists seeking effective solutions to real-world problems [CW06].

Neural simulation is performed by modelling neural network topologies, which reflect information transmission between many simple functional elements – the neurons. The only information issued by a neuron is an electro-chemical impulse, indicating its firing. Information is conveyed by the firing frequency and the timing of impulses relative to other neurons. The information processing algorithms of the brain are highly related to the connectivity between neurons. A major challenge in achieving high performance neural simulation is to emulate the connectivity of a biological neural network. It is necessary to provide a communication infrastructure which models the impulses between neurons.

Wilson compared the neural simulation performance of well-connected versus loosely coupled processing elements [WGJ01]. The result indicates that communication latency is the major factor in obtaining good performance, especially in achieving real-time simulation. An infrastructure specifically supporting the massive communication of neural networks is therefore desirable for this applicationspecific platform. As the central part of this infrastructure, a router that supports efficient communication of neural impulses is one of the key issues.

#### **1.2** Literature review

Investigations into neural network modelling have been undertaken for several decades by means of theoretical studies together with experimental simulations. The research leads to two sub-questions: firstly, how can the brain's behaviour be abstracted into computable models which neuroscientists achieve by neural

network modelling; secondly, how can this computation be performed on an artificial platform. Although research into neural modelling has seen remarkable progress, the second question remains unanswered. Many research projects have been proposed in the area of developing neural simulation platforms.

#### **1.2.1** Software neural simulators

Many software simulators, such as GENESIS and NEURON, can be used to model neurons with high biophysical realism and are flexible as a result of their programmability [BB98][HC97]. They provide interfaces to conventional computers: general-purpose workstations initially and, later, commercially-available computer clusters to achieve larger simulation scales. However, software simulators are inefficient for neural modelling, especially for large-scale networks. One major reason is that spike propagation in neural networks is inherently eventdriven whereas software simulators typically employ time-driven models [Moi06].

#### **1.2.2** Neural simulations on general-purpose computers

General-purpose stand-alone workstations are the most commonly used platforms for neural simulations because they are economical, easily available and convenient to program. State-of-the-art processors have adequate computational power to support a certain scale of neural simulation in real time. For example, Boucheny presented a complete physiologically-relevant spiking cerebellum model that runs in real-time on a dual-processor computer. The model consists of 2,000 neurons and more than 50,000 synapses [BCRC05]. However, neural networks modelled on sequential computers are constrained to be very small-scale due to the limitations of the computational resource. This narrows the application range.

The pursuit of performing larger-scale neural simulations has led to investigations into hardware integration. As neural networks are inherently parallel systems, larger-scale simulations are suitable to be performed on parallel computers. Several spiking neural networks have been implemented on commercially-available parallel computers, such as the Transputer array used at Edinburgh [FRS<sup>+</sup>87], the CM-2 Connection Machine developed by Thinking Machines Corporation [Moi06].

With the advances in computational power, concurrent hardware implementations are adequate for simulating very large neural networks. A current, on-going example is the Blue Brain project conceived at IBM [Mar06]. It can simulate up to 100,000 highly complex neurons or 100 million simple neurons, which corresponds to the number of neurons in a mouse brain.

Computation power is available because the neural simulation problem is linearly scalable. A parallel computer architecture distributes computational tasks onto different processing elements to decrease the workload on an individual processor so that it fulfills the neural simulation's requirements in terms of scale and computational power. However, communication overheads in existing parallel architectures limit the overall execution speed of large-scale spiking neural simulations, which is a crucial requirement for the accomplishment of many bio-realistic tasks, such as real-time vision detection. Parallel computer architectures struggle to reach the requirements of real-time simulation (1 ms resolution) [PEM<sup>+</sup>07]. This is because existing architectures are not designed to cope with communication scalability as 'conventional' software doesn't require it. Of the above cases, only the CM-2 achieved real-time simulation of a spiking neural network, with a scale up to 512K neurons [JSR<sup>+</sup>97]. Unfortunately, a network of even several thousand neurons is still too small to satisfy the needs of many application-specific simulations and large-scale parallel computers usually have high maintenance costs.

#### **1.2.3** Neurocomputers

Because of the limitation of running a fast simulations of a large-scale spiking neural network on general-purpose high-performance computers, there is a motivation for developing dedicated digital hardware – so-called neurocomputers – which aim to achieve more cost-effective performance and faster simulation speed. They are usually custom built to distribute processing and storage, and are implemented with neurochips or a conventional computer plus neural accelerator boards that optimize the simulation algorithm.

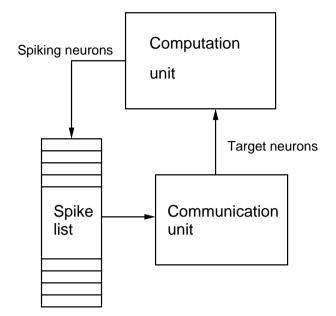

A generic neurocomputer architecture usually comprises three parts: a computing unit, a spike event list and a connection unit, a block diagram is shown is Figure 1.1. The elementary operations of neural computation are usually executed on the computing unit, usually a specific VLSI neural signal processor. It can be a single, specific processor or an array of processors located on the neurochips or the accelerator boards. When performing a simulation, the computing unit generates the addresses of spiking neurons which are stored in the spike event list. The connection unit contains connectivity information. It reads

Figure 1.1: A generic neurocomputer

the address of a neural spike from the spike event list and derives the address of target neurons [Ram92]. Well-known examples include NESPINN, CNAPS and SYNAPSE.

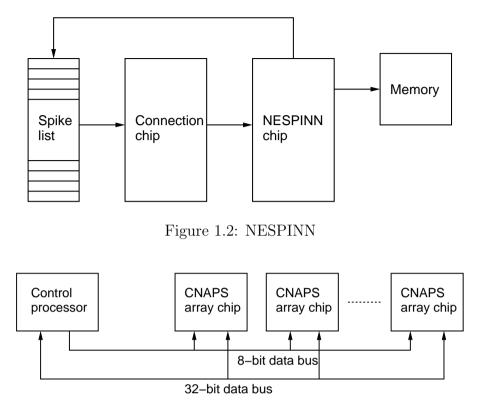

NESPINN (Neurocomputer for Spiking Neural Networks) was designed at the Institute of Microelectronics of the Technical University of Berlin [SMJK98]. Its block diagram is shown in Figure 1.2. The system was designed specifically for spiking neural networks. A NESPINN board is capable of simulating up to 512K spiking neurons with up to 10<sup>4</sup> connections. It consists of one connection chip and one processing chip. The connection chip holds the network topology. The processing chip has several processing elements, each of which executes a partition of the whole neural network. The NESPINN board achieves a good performance by using an efficient neuron parallel mapping scheme and a mixed dataflow/SIMD (Single Instruction Multiple Data) mode in the architecture. However, its has limited scalability.

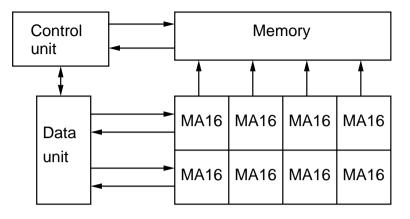

The CNAPS (Connected Network of Adaptive Processors) system, proposed at Adaptive Solutions, has shown a certain level of scalability [Ham91]. Its block diagram is shown in Figure 1.3. The elementary functional block of the CNAPS system is a neurochip, N6400, which contains 64 processing elements. A system can be expanded via a broadcast interconnection scheme, where a maximum

Figure 1.3: CNAPS

of eight chips with a total of 512 processing elements are connected by two 8bit broadcast buses in a SIMD mode. Any information exchange between the neurochips is transferred via the buses, which makes them system bottlenecks.

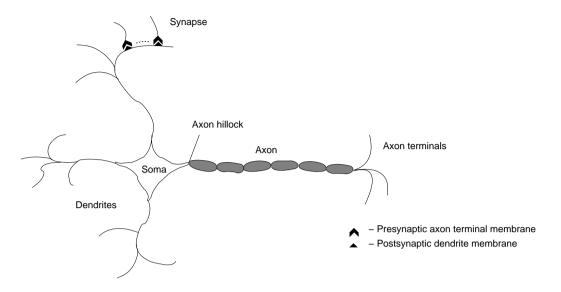

The neurocomputer SYNAPSE (Synthesis of Neural Algorithms on a Parallel Systolic Engine), developed at Siemens, also consists of eight neurochips (MA-16), connected by a systolic ring architecture [RRH+95]. Its block diagram is shown in Figure 1.4. The throughput of the communication channels is optimized by pipelining. However, the systolic ring architecture is also considered non-scalable.

#### **1.2.4** Limitations of previous neural simulators

Due to the high diversity of applications, there are many algorithms for neural networks. For example, some applications focus on real-time interactions, such as robot control, others focus on the exploration of neural modelling or brain function. It is, therefore, hard to develop a general benchmark for all neural simulations. However, one straightforward, and perhaps the simplest, way of examining the effectiveness of neural simulations is to evaluate their performance on

Figure 1.4: SYNAPSE

real-world applications. A 1 million (or more) neuron network, with about 1,000 inputs on each neuron and 100–1,000 impulses per second, would offer a good perspective on experimental research on large-scale neural simulations [Hee95].

Although the above mentioned solutions have achieved significant improvements in performance over general-purpose workstations and clusters, their capability of applying large-scale neural network topologies to complex real-world problems is still limited, and revealing the internal mechanisms of the brain is still far beyond their capability.

Software simulators have been developed to explore models close to biology. Stand-alone workstations have proved useful for small-scale experiments. General-purpose parallel computers can support a relatively large scale of simulation and are flexible for programming, but they are usually not able to run the simulations in real time. Neurocomputers have managed to achieve real-time simulations by taking advantage of the higher operating speed of VLSI circuits (nanoseconds) relative to that of neurons (milliseconds). This allows a single processor to simulate about  $10^5$  to  $10^6$  neurons in real time. However, further scaling up of the simulations while maintaining the real-time feature is difficult due to the communication overhead. One example of extending the scale is shown in the case of the CNAPS where the bus interconnect is still the system bottleneck.

New architectures and technology are thus desirable in the construction of the next generation of neural hardware, where the features of adaptivity, flexibility, scalability, higher speed and low power have to be considered. Eventually, these features will converge into one major research focus – efficient communication between neurons on massively-parallel systems. The communication issue is also

becoming one of the central topics of the trend of research on new computer paradigms, which aim to make multi-core processing on one or several chips feasible.

#### **1.3** Design considerations

Biological neurons are massively interconnected but 'compute' slowly (less than  $\sim$  1,000 Hz) and communication speed is low ( $\sim$  1 ms). Electronic components are much faster (several GHz) but interconnection is expensive. However several digital neural impulses can be multiplexed over a communication channel to provide similar connectivity to biological neurons.

An ARM968 processor is capable of simulating  $\sim 1,000$  neurons and the associated synapses connections in real time with  $\sim 50$  MB memory [JFW08]. In a system which scales to one million neurons around 1,000 microprocessors are needed, producing around one billion impulses per second. This requires an interconnection network able to handle a large number of neural impulses in real-time.

This dissertation focuses on a router as the central communication unit of the interconnection network. A set of issues were considered in designing the architecture of the router to fulfill the communication requirements of neural modelling as well as those of massively-parallel system configurations.

Three routing algorithms are defined as the basic functionalities: multicast routing for neural impulses transmission; point-to-point routing for system management and control information transmission; and nearest-neighbour routing for boot-time, flood-fill and chip debug information transmission. The multicast routing is the principal function of the router. It is more efficient for neural communication than typical unicast and broadcast routing because neurons have high fan-outs.

Some fault-tolerance features are considered for inclusion in the router. This is an emulation of biological systems which have certain abilities to identify and isolate faults.

The design is optimized to significantly reduce power and area consumption so that the router can handle a large number of neural impulses with low overhead.

#### **1.4** Contributions

This dissertation focuses on the investigation of a novel router architecture for the real-time modelling of spiking neural networks on a massively-parallel system via an on/inter-chip communication infrastructure. The router supports multiple routing algorithms which are designed specifically for efficient communication in large-scale neural networks. The major contributions include:

- Communication efficiency: Neural networks may be modelled in real time by taking advantage of the massive parallelization of the platform. This is achieved by properly balancing the system resources between computation, storage and communication. The design effort described in this dissertation focuses on deriving higher communication efficiency, principally through the multicast routing of neural packets.

- System scalability: Biological neural networks range from small-scale systems with several neurons to very large-scale systems with tremendous numbers of neurons. A platform for neural network modelling must be scalable, so that the same algorithm can be applied to various neural networks. To achieve a better scalability and speed than conventional buses, a router in a Network-on-Chip architecture is used for on-chip neural message routing and processing elements organization. In this way, the platform is formed from an array of neural chips, wrapped into a torus.

- Fault-tolerance: Fault-tolerance has become increasingly crucial in VLSI design as device variability becomes an inevitable issue in deep sub-micron technology. It is, however, present in most biological systems. The scale of the system requires an adaptive routing mechanism to enhance system-level fault-tolerance. An error handling mechanism is applied to enhance the reliability of data flows.

- Power/area efficiency: On-chip network design needs more consideration of energy and area efficiency than macro networks. These issues become even more important as a power/area-intensive associative memory circuit is required for the neural platform to store spiking neuron addresses.

- Universality: The system is intended to support multiple neural models, and can be configured 'on the fly'. This is realized by taking advantage of

the higher flexibility of programmable digital hardware. Configuration of a distributed system requires message passing between the processing nodes, which is accomplished by multiplexing the neural communication channel of the router and requires proper design of the transaction protocols.

#### 1.5 Dissertation organization

The organization of this dissertation is as follows: After discussing the basic concepts of neuron modelling in chapter 2, the thesis starts with discussing the feasibility of applying the Network-on-Chip approach to the implementation of a neurocomputing platform (chapter 3), and then particularly focuses towards the communication issues of the platform in chapter 4. Chapter 5 presents the architectural considerations of the router, which is the heart of the system's communication network. Detailed implementations of the router's routing algorithms follow in chapter 6. Chapter 7 presents router pipelining for flow control and power saving. Following that in chapter 8 the router's performance is evaluated from several perspectives, including its basic functions, its behaviours in a network environment, packet drop rate, power consumption and circuit area. Finally, in chapter 9, conclusions are drawn about how the design demonstrates the advantages and disadvantages of the proposed routing strategy for a large-scale neural platform in addition to suggesting future explorations and optimizations.

#### **1.6** Publications

The following papers have been published or submitted for publication, based on the work presented in this dissertation.

• Wu, J. and Furber, S.B.,

Delay insensitive chip-to-chip interconnect using incomplete 2-of-7 NRZ data encoding [WF06]

(18th UK Asynchronous Forum)

The paper introduces the concepts and implementations of delay-insensitive signalling protocols for a chip interface which extends the router's on-chip links into inter-chip links, followed with evaluations of the performance;

• Wu, J., Furber, S.B. and Garside, J.D.

A programmable adaptive router for a GALS parallel system [WFG09]

(15th IEEE International Symposium on Asynchronous Circuits and Systems)

The paper demonstrates the design implementation of the router in the SpiNNaker system. It proves the design feasibility and addresses the important issues desired by a neural simulation platform, such as programmability, adaptivity and scalability (see chapters 6, 7 and 8);

• Wu, J. and Furber, S.B.

A multicast routing scheme for a universal spiking neural network architecture [WF09]

(The Computer Journal)

The paper discusses the design considerations of the router from a neural simulation point of view. It addresses the importance of communication efficiency to neural network modelling, followed by evaluation results of power saving and adaptive routing showing the significance of the design (see chapter 5, 6 and 8);

Plana, L.A., Furber, S.B., Temple, S., Khan, M., Shi, Y., Wu, J. and Yang, S.

A GALS infrastructure for a massively parallel multiprocessor [PFT<sup>+</sup>07] (IEEE Design and Test of Computers)

The paper focuses on the GALS infrastructure of the SpiNNaker system and describes the router as a crucial part of the infrastructure (see chapter 4);

- Plana, L.A., Furber, S.B. Bainbridge, J., Salisbury, S., Shi, Y. and Wu, J. An on-chip and inter-chip communications network for the SpiNNaker massively-parallel neural net simulator [PFB<sup>+</sup>08] (The 2nd IEEE International Symposium on Network-on-Chip) The poster provides a perspective of the SpiNNaker system (see chapter 4);

- Lujan, M., Furber, S.B., Jin, X., Khan, M., Lester, D., Miguel-Alonsoy, J., Navaridasy, J., Painkras, E., Plana, L.A., Rast, A., Richards, D., Shi, Y., Temple, S., Wu, J. and Yang, S.

Fault-tolerance in the SpiNNaker architecture (submitted) (IEEE Transactions on Computers)

The paper addresses the fault-tolerance feature considered in the design of the SpiNNaker platform, where the router is one of the key components supporting this feature. A case study has been carried out using a 256  $\times$  256 2-dimensional triangular mesh. It shows the router's adaptive routing mechanism can significantly enhance system-level fault-tolerance and stability by decreasing the packet drop rate (see chapter 8).

### Chapter 2

### Neurcomputing

This chapter introduces the biological and mathematical background of neurcomputing. The knowledge presented here includes neurocomputing's principles, characteristics, and possible implementation methods, to explain the theoretical foundations for implementing neurocomputing through a VLSI approach. Following that spiking neural networks and one of the spiking neural models, Izhikevich model, are introduced. The feature of spiking neural networks shows that it is possible to model the networks in real-time. This brings challenges to the development of an efficient communication mechanism which will be further investigated in the following chapters.

#### 2.1 Introduction

The biological brain, which features high complexity, nonlinearity, and massive parallelism, is the central unit of the nervous system. It makes appropriate decisions in many intelligent tasks, such as speech recognition, image analysis, and adaptive control.

Research to understand the brain started from 1911 when Ramón y Cajal first introduced the concept of neurons as basic operational elements of the neural network. A brain contains a huge number of neurons. It is estimated that there are 100 million neurons in the mouse brain and 100 billion neurons in the human brain. They are massively interconnected by junctions called synapses and form a neural network. The operations of the brain are represented by the activities of the neural network, which is further represented by those of the individual neurons and their interactions. Neurons operate at a slower process speed than silicon logic gates [Hay98], however, a huge number of these slow, simple elements exhibit some remarkable characteristics by evaluating in parallel. The brain also has significantly lower power consumption ( $10^{-16}$  Joules per operation), an energy budget that the human body can afford.

In computer science, the modelling of artificial neural networks is called neurocomputing and intends to reflect complex relationships between the network's inputs and outputs. Haykin's book provides a comprehensive survey of neural network characteristics distinguishing neurocomputing from conventional computation [Hay98].

- Nonlinearity An artificial neural network can be a nonlinear system which is inherently suitable for processing certain signals with nonlinearity (e.g. speech signals).

- Input-output mapping A set of samples with unique inputs and the corresponding desired outputs can be applied to a neural network for training purposes. The network is modified in response to the examples so that it is finally trained to generate output with acceptable difference from the desired results. Thus mapping relationships between input and output signals of selected examples can be constructed within the network.

- Adaptivity A neural network is naturally adaptive to its operating environment which it achieves by the real-time modification of synaptic weights.

- Fault tolerance Brains are fault tolerant: neurons die continuously yet the brain (largely) continues to function. A hardware implementation of a neural network is potentially capable of maintaining functionality by degrading its performance to an acceptable extent rather than displaying catastrophic failure when facing damage.

- Evidential response A neural network displays a high level of confidence in pattern recognition. This means it is not only able to recognise particular patterns, but also may be used to reject ambiguous patterns.

- Contextual information A neural network is inherently capable of processing contextual information. The knowledge representation of a neural network is based on its structure and activation state.

- VLSI implementability A neural network is well suited for implementation using VLSI because of its massively-parallel nature.

- Uniformity of analysis and design Neural networks share common theories and learning algorithms. It is credible to use the same notation in all domains.

- Neurobiological analogy Research into neural networks provides an opportunity for interpreting neurobiological phenomena. The improved understanding of the natural phenomena will, in turn, inspire engineers in their quest for ever-better high-performance computational architectures.

The above-mentioned characteristics of neurocomputing suggest great engineering perspectives, but a implementation of the computation requires a profound understanding of how a neural network works. The remainder of this chapter presents the basic knowledge of neurocomputing, which starts with the biological characteristics of neural networks, followed by the mathematical modelling of neurons and neural networks, and ending up with the introduction of spiking neural networks which may be suitable for large-scale, real-time modelling on VLSI.

#### 2.2 Biological neurons and neural networks