Asynchronous System-on-Chip Interconnect

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science & Engineering

March 2000

William John Bainbridge

Department of Computer Science

# Contents

| Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                      |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                                                                                                      |

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                                                                                                      |

| Declaration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                                                                                                                     |

| Copyright                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                                     |

| The Author                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11                                                                                                                     |

| Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12                                                                                                                     |

| Chapter 1: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13                                                                                                                     |

| 1.1 Asynchronous design and its advantages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                        |

| 1.1.1 Avoidance of clock-skew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                        |

| 1.1.2 Low power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                        |

| 1.1.3 Improved electro-magnetic compatibility (EMC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                        |

| 1.1.4 Modularity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                        |

| 1.1.5 Better than worst-case performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                        |

| 1.2 Disadvantages of asynchronous design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                        |

| 1.2.1 Complexity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                        |

| 1.2.2 Deadlock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                        |

| 1.2.3 Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                        |

| 1.2.4 Testability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                        |

| 1.2.5 "It's not synchronous"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                        |

| 1.3 Thesis Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                        |

| 1.4 Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                        |

| Chapter 2: Asynchronous Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                                                                                     |

| Chapter 2: Asynchronous Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>23</b>                                                                                                              |

| Chapter 2: Asynchronous Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>23</b><br>23<br>25                                                                                                  |

| Chapter 2: Asynchronous Design<br>2.1 Introduction<br>2.2 Asynchronous design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23<br>23<br>25<br>25                                                                                                   |

| Chapter 2: Asynchronous Design<br>2.1 Introduction<br>2.2 Asynchronous design<br>2.2.1 Circuit classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>23</b><br>25<br>25<br>26                                                                                            |

| Chapter 2: Asynchronous Design<br>2.1 Introduction<br>2.2 Asynchronous design<br>2.2.1 Circuit classification<br>2.2.2 The channel<br>2.2.3 Signalling conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>23</b><br>25<br>25<br>26<br>27                                                                                      |

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.2.1 Circuit classification         2.2.2 The channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>23</b><br>25<br>25<br>26<br>27<br>29                                                                                |

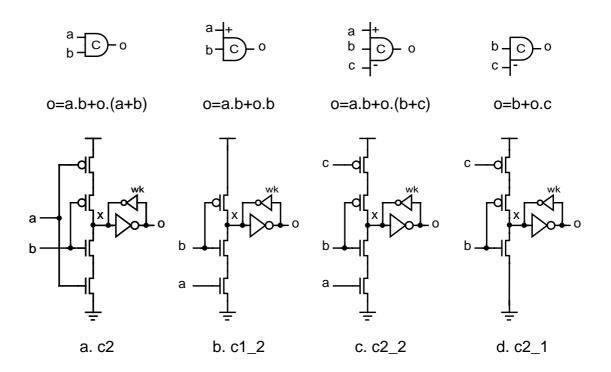

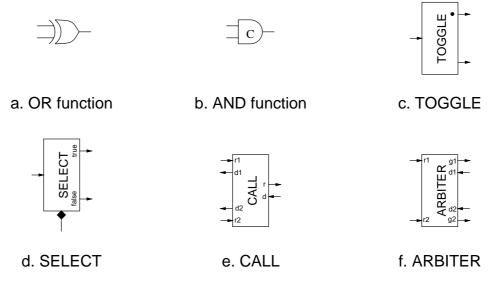

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>23</b><br>25<br>25<br>26<br>27<br>29<br>32                                                                          |

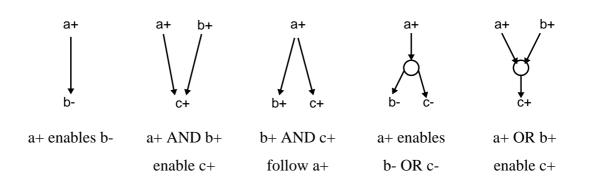

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element         2.2.6 Specifications and automated circuit synthesis                                                                                                                                                                                                                                                                                                                                                                     | <b>23</b><br>25<br>25<br>26<br>27<br>29<br>32                                                                          |

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element         2.2.6 Specifications and automated circuit synthesis         2.2.7 Metastability, arbitration and synchronisation                                                                                                                                                                                                                                                                                                        | <b>23</b><br>25<br>25<br>26<br>27<br>29<br>32<br>35                                                                    |

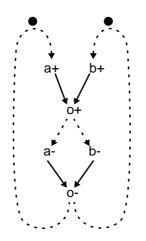

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element         2.2.6 Specifications and automated circuit synthesis         2.2.7 Metastability, arbitration and synchronisation         2.2.8 Sutherland's micropipelines                                                                                                                                                                                                                                                              | <b>23</b><br>25<br>26<br>26<br>27<br>29<br>32<br>32<br>35<br>36                                                        |

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element         2.2.6 Specifications and automated circuit synthesis         2.2.7 Metastability, arbitration and synchronisation         2.2.8 Sutherland's micropipelines         2.2.9 Large Asynchronous Circuits                                                                                                                                                                                                                    | <b>23</b><br>25<br>26<br>26<br>27<br>29<br>32<br>32<br>35<br>36<br>38                                                  |

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.1 Circuit classification         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element         2.2.6 Specifications and automated circuit synthesis         2.2.7 Metastability, arbitration and synchronisation         2.2.8 Sutherland's micropipelines         2.2.9 Large Asynchronous Circuits                                                                                                                                                                                 | <b>23</b><br>25<br>25<br>26<br>27<br>29<br>29<br>32<br>32<br>36<br>38<br>40                                            |

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element         2.2.6 Specifications and automated circuit synthesis         2.2.7 Metastability, arbitration and synchronisation         2.2.8 Sutherland's micropipelines         2.2.9 Large Asynchronous Circuits         2.3 Summary                                                                                                                                                                                                | <b>23</b><br>25<br>25<br>26<br>27<br>29<br>29<br>32<br>35<br>36<br>36<br>40<br><b>41</b>                               |

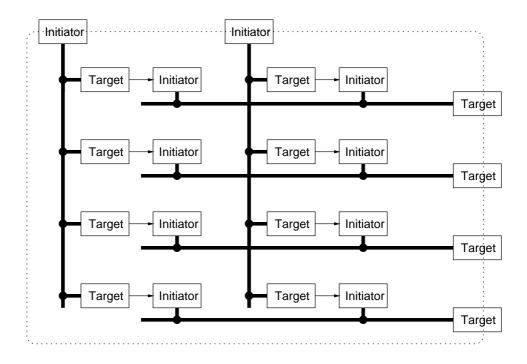

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.1 Circuit classification         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element         2.2.6 Specifications and automated circuit synthesis         2.2.7 Metastability, arbitration and synchronisation         2.2.8 Sutherland's micropipelines         2.2.9 Large Asynchronous Circuits         2.3 Summary         Chapter 3: System Level Interconnect Principles         3.1 Point-to-point communication paths                                                      | <b>23</b><br>25<br>26<br>26<br>27<br>29<br>32<br>32<br>36<br>36<br>36<br>38<br>40<br><b>41</b>                         |

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.1 Circuit classification         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element         2.2.6 Specifications and automated circuit synthesis         2.2.7 Metastability, arbitration and synchronisation         2.2.8 Sutherland's micropipelines         2.2.9 Large Asynchronous Circuits         2.3 Summary         Chapter 3: System Level Interconnect Principles         3.1 Point-to-point communication paths         3.2 Multipoint interconnect topology         | <b>23</b><br>25<br>25<br>26<br>27<br>29<br>29<br>32<br>35<br>36<br>36<br>38<br>40<br><b>41</b><br>41                   |

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element         2.2.6 Specifications and automated circuit synthesis         2.2.7 Metastability, arbitration and synchronisation         2.2.8 Sutherland's micropipelines         2.2.9 Large Asynchronous Circuits         2.3 Summary         Chapter 3: System Level Interconnect Principles         3.1 Point-to-point communication paths         3.2 Multipoint interconnect topology         3.2.1 Shared buses                 | <b>23</b><br>25<br>26<br>26<br>27<br>29<br>29<br>32<br>32<br>35<br>36<br>38<br>40<br><b>41</b><br>41<br>42<br>42       |

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.1 Circuit classification         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element         2.2.6 Specifications and automated circuit synthesis         2.2.7 Metastability, arbitration and synchronisation         2.2.8 Sutherland's micropipelines         2.2.9 Large Asynchronous Circuits         2.3 Summary         3.1 Point-to-point communication paths         3.2 Multipoint interconnect topology         3.2.1 Shared buses         3.2.2 Star and Ring Networks | <b>23</b><br>25<br>25<br>26<br>26<br>27<br>29<br>32<br>32<br>36<br>36<br>38<br>40<br><b>41</b><br>41<br>42<br>42<br>42 |

| Chapter 2: Asynchronous Design         2.1 Introduction         2.2 Asynchronous design         2.2.1 Circuit classification         2.2.2 The channel         2.2.3 Signalling conventions         2.2.4 Data representation         2.2.5 The Muller C-element         2.2.6 Specifications and automated circuit synthesis         2.2.7 Metastability, arbitration and synchronisation         2.2.8 Sutherland's micropipelines         2.2.9 Large Asynchronous Circuits         2.3 Summary         Chapter 3: System Level Interconnect Principles         3.1 Point-to-point communication paths         3.2 Multipoint interconnect topology         3.2.1 Shared buses                 | <b>23</b><br>25<br>25<br>26<br>27<br>29<br>32<br>35<br>36<br>36<br>38<br>40<br><b>41</b><br>41<br>42<br>42<br>42<br>42 |

|          | 3.3.1 Serial operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44                                                                                                                          |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

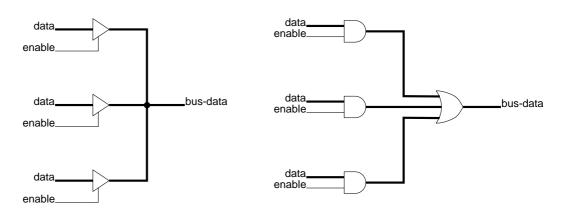

|          | 3.3.2 Multiplexed address/data lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44                                                                                                                          |

|          | 3.3.3 Separate address and data lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                             |

|          | 3.3.4 Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                          |

|          | 3.3.5 Atomic sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46                                                                                                                          |

|          | 3.3.6 Bursts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46                                                                                                                          |

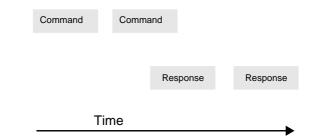

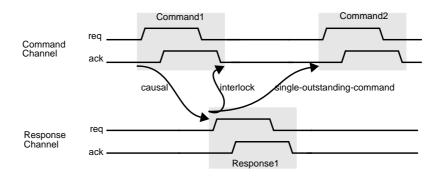

|          | 3.3.7 Interlocked or decoupled transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46                                                                                                                          |

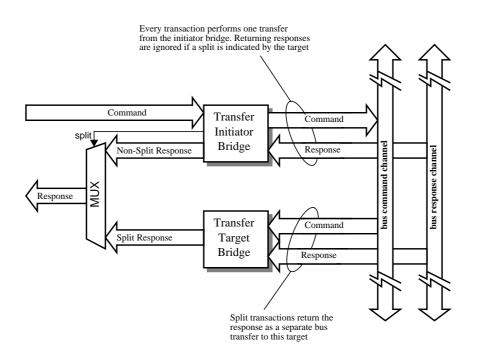

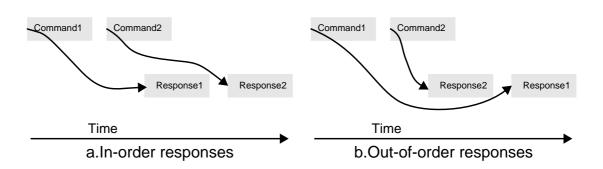

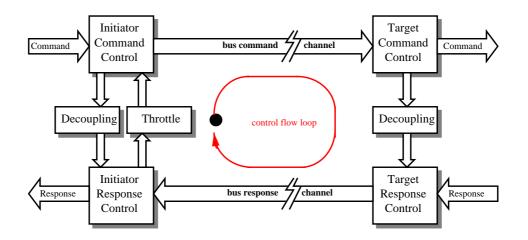

|          | 3.3.8 Split transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46                                                                                                                          |

|          | 3.4 Interconnect performance objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47                                                                                                                          |

|          | 3.5 Commercial on-chip buses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                             |

|          | 3.5.1 Peripheral Interconnect Bus (PI-Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48                                                                                                                          |

|          | 3.5.2 The Advanced Microcontroller Bus Architecture (AMBA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                             |

|          | 3.5.3 CoreConnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                             |

|          | 3.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51                                                                                                                          |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50                                                                                                                          |

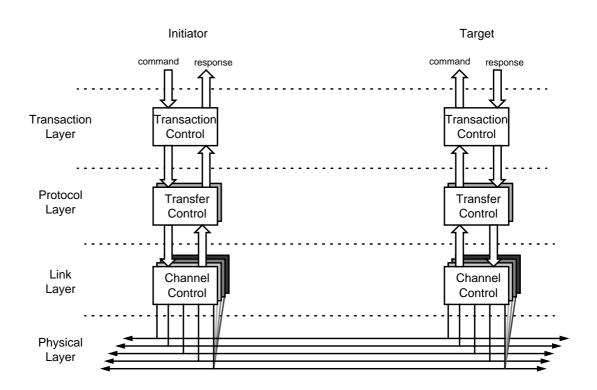

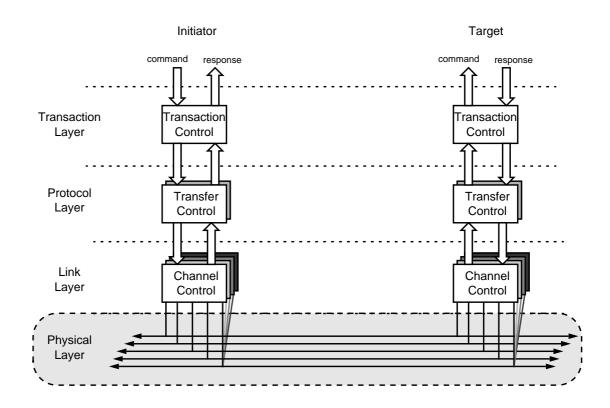

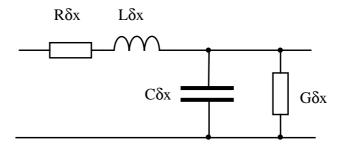

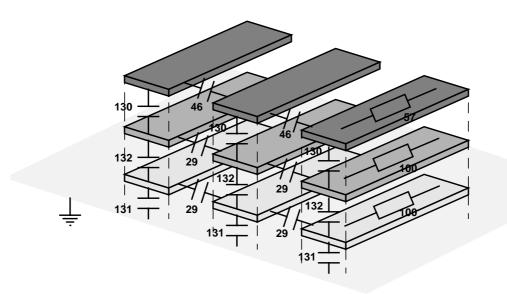

| Ch       | apter 4: The Physical (Wire) Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                             |

|          | 4.1 Wire theory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                             |

|          | 4.2 Electrical and physical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                             |

|          | 4.3 Termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                             |

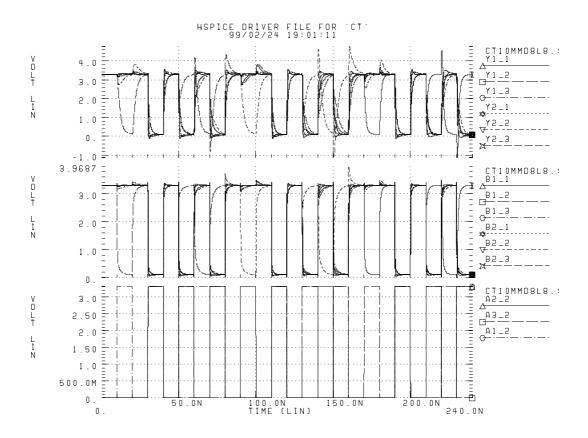

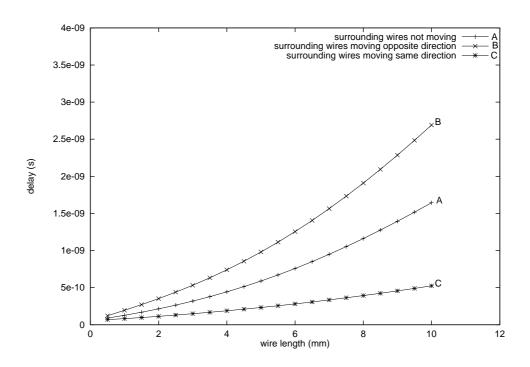

|          | 4.4 Crosstalk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                             |

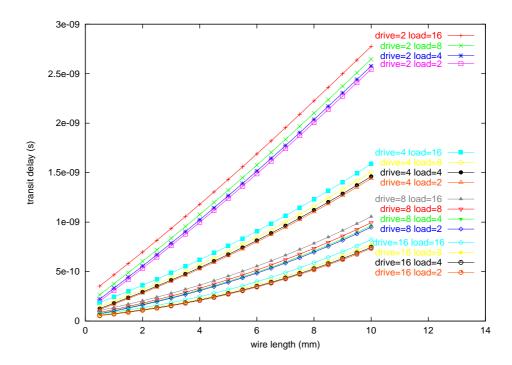

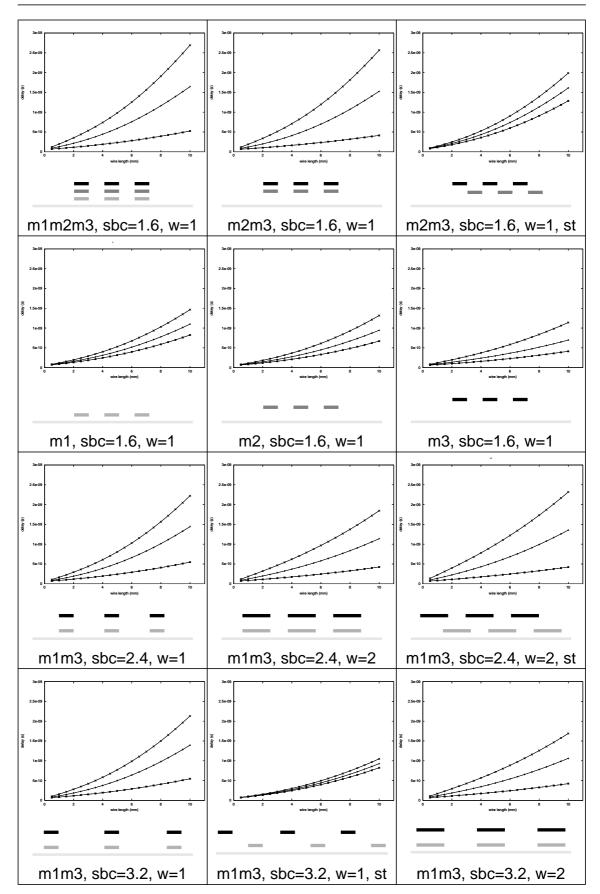

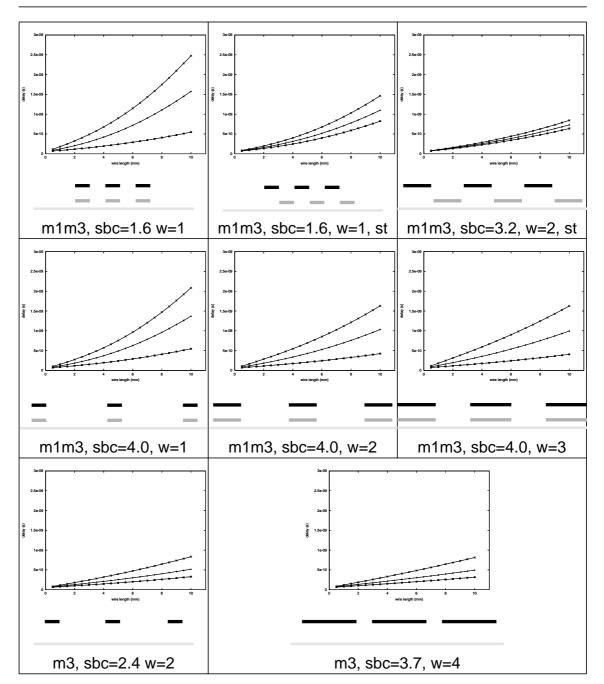

|          | 4.4.1 Propagation delay for well separated wires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                             |

|          | 4.4.2 Signal propagation delay with close-packed wires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                             |

|          | 4.4.3 Alternative wiring arrangements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                             |

|          | 4.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64                                                                                                                          |

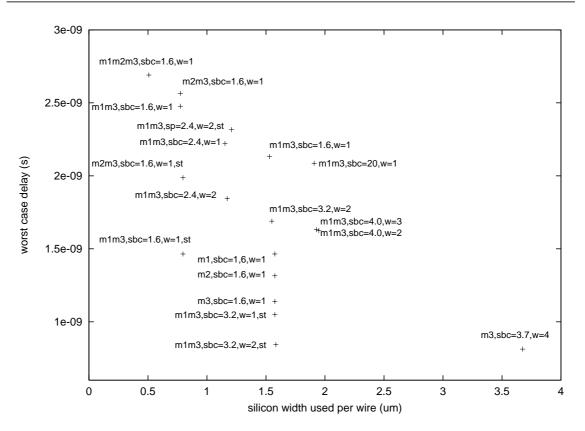

| Ch       | apter 5: The Link Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65                                                                                                                          |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                             |

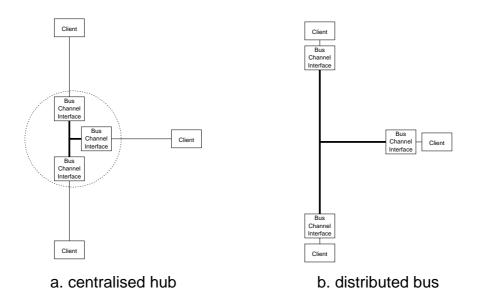

| <b>U</b> | 5.1 Centralised vs distributed interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                             |

| C II     | 5.1 Centralised vs distributed interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66                                                                                                                          |

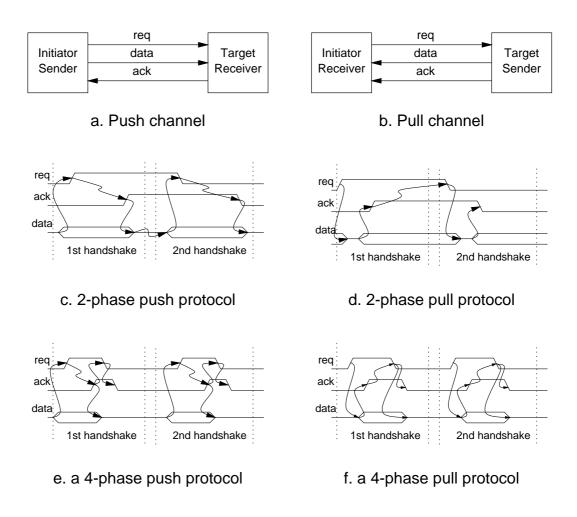

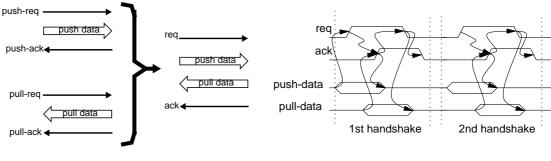

|          | <ul><li>5.1 Centralised vs distributed interfaces</li><li>5.2 Signalling Convention</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66<br>67                                                                                                                    |

|          | 5.1 Centralised vs distributed interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>67<br>67                                                                                                              |

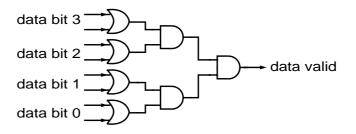

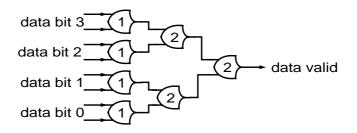

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li> <li>5.2 Signalling Convention</li> <li>5.3 Data Encoding</li> <li>5.4 Handshake sources</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>67<br>67<br>68                                                                                                        |

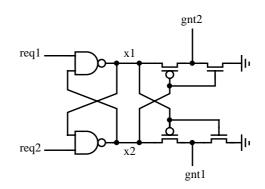

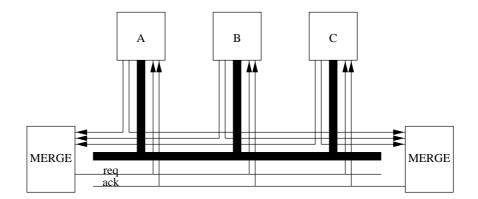

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>67<br>68<br>69                                                                                                  |

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li> <li>5.2 Signalling Convention</li> <li>5.3 Data Encoding</li> <li>5.4 Handshake sources</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>67<br>67<br>68<br>69<br>70                                                                                            |

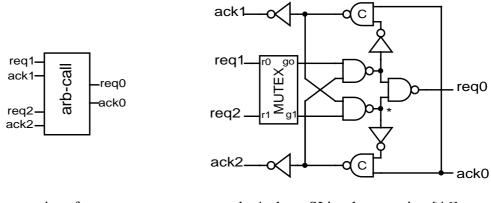

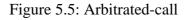

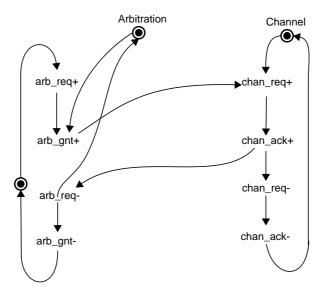

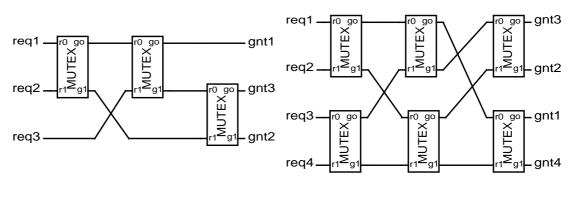

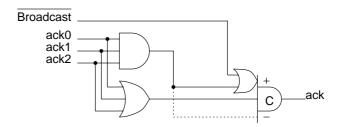

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71                                                                                            |

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77                                                                                      |

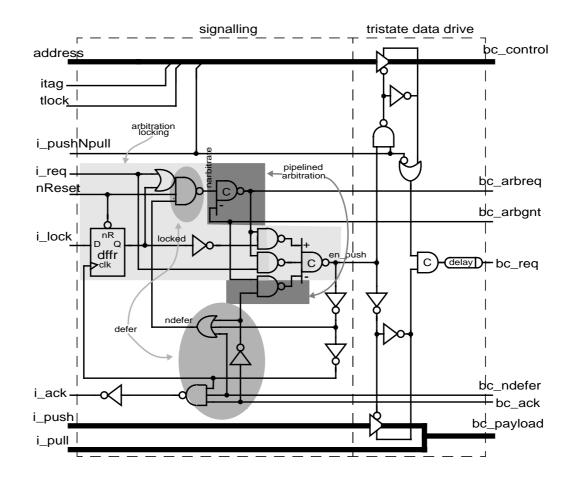

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78                                                                                |

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79                                                                          |

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>81                                                                    |

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>81<br>83                                                              |

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>81<br>83<br>83                                                        |

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>81<br>83<br>83<br>84                                                  |

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>81<br>83<br>83<br>84<br>85                                            |

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>81<br>83<br>83<br>84<br>85<br>85                                      |

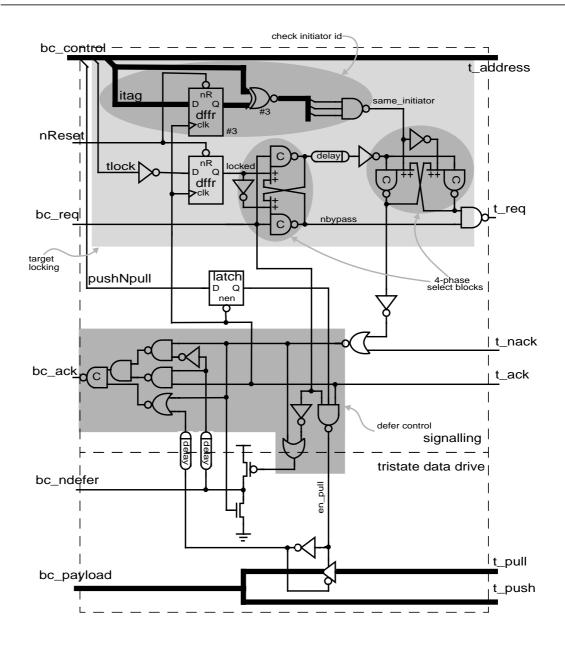

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li> <li>5.2 Signalling Convention</li> <li>5.3 Data Encoding</li> <li>5.4 Handshake sources</li> <li>5.5 Bidirectional data transfer</li> <li>5.6 Multiple initiators on one channel</li> <li>5.6.1 Arbitration</li> <li>5.6.2 Request drive and hand-over</li> <li>5.6.3 Push data drive and hand-over</li> <li>5.6.4 Transfer deferral/hardware retry</li> <li>5.6.5 Atomic transfers and locking</li> <li>5.7 Multiple Targets</li> <li>5.7.1 Acknowledge drive and hand-over</li> <li>5.7.2 Target selection</li> <li>5.7.4 Pull data drive and hand-over</li> <li>5.7.5 Defer</li> </ul> | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>81<br>83<br>83<br>84<br>85<br>85<br>86                                |

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>83<br>83<br>83<br>83<br>85<br>85<br>86<br>86                          |

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li> <li>5.2 Signalling Convention</li> <li>5.3 Data Encoding</li> <li>5.4 Handshake sources</li> <li>5.5 Bidirectional data transfer</li> <li>5.6 Multiple initiators on one channel</li> <li>5.6.1 Arbitration</li> <li>5.6.2 Request drive and hand-over</li> <li>5.6.3 Push data drive and hand-over</li> <li>5.6.4 Transfer deferral/hardware retry</li> <li>5.6.5 Atomic transfers and locking</li> <li>5.7 Multiple Targets</li> <li>5.7.1 Acknowledge drive and hand-over</li> <li>5.7.2 Target selection</li> <li>5.7.4 Pull data drive and hand-over</li> <li>5.7.5 Defer</li> </ul> | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>83<br>83<br>83<br>83<br>85<br>85<br>86<br>86<br>88                    |

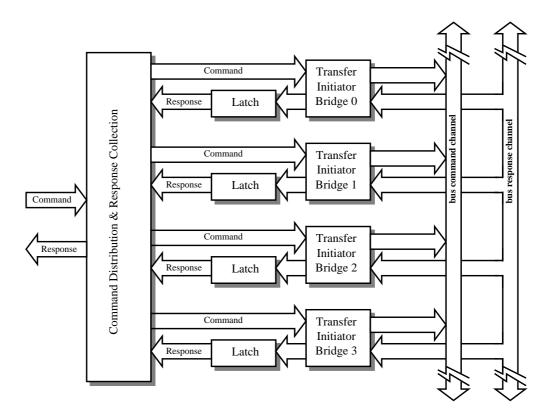

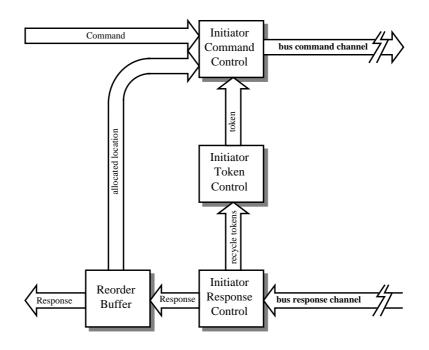

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>83<br>83<br>83<br>85<br>85<br>86<br>86<br>88<br>89              |

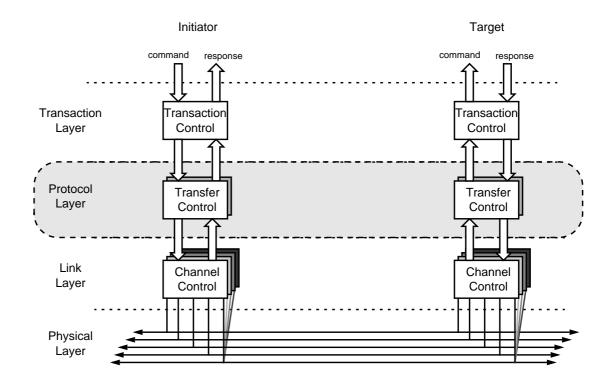

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>81<br>83<br>83<br>84<br>85<br>86<br>86<br>86<br>89<br>89<br><b>90</b> |

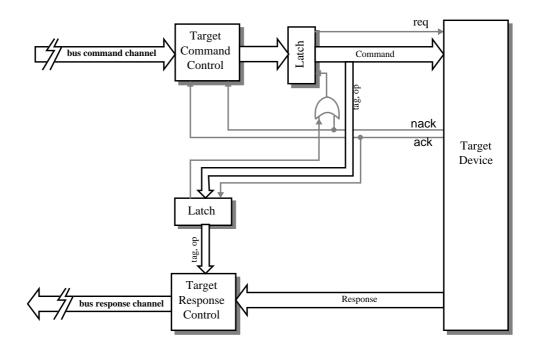

|          | <ul> <li>5.1 Centralised vs distributed interfaces</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66<br>67<br>68<br>69<br>70<br>71<br>77<br>78<br>79<br>83<br>83<br>83<br>83<br>85<br>85<br>86<br>86<br>88<br>89<br>91        |

|                                     | 6.1.2 The acknowledge phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92                                                                                                                                                                   |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | 6.1.3 The data phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 92                                                                                                                                                                   |

|                                     | 6.1.4 The response phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 92                                                                                                                                                                   |