# Processor Architectures for Power Efficiency and Asynchronous Implementation

A thesis submitted to the University of Manchester for the degree of Master of Science in the Faculty of Science

Philip Brian Endecott

Department of Computer Science

# **Contents**

| Contents.   |                                                        | 3  |

|-------------|--------------------------------------------------------|----|

| List of Fig | gures                                                  | 7  |

| _           | bles                                                   |    |

|             |                                                        |    |

| Abstract    |                                                        | 11 |

| Chapter 1   | : The Increasing Importance of High Power Efficiency   | 15 |

| 1.1         | Why Low Power?                                         | 15 |

| 1.2         | How Can Power Consumption Be Reduced?                  | 21 |

| 1.3         | Introduction to this Work                              |    |

| Chapter 2   | : Asynchronous Logic                                   | 25 |

| 2.1         | Asynchronous Logic versus Synchronous Logic            | 25 |

| 2.1.1       | The Typical-Case / Worst-Case Timing Argument          | 26 |

| 2.1.2       | Clock Skew and Ground Bounce                           | 29 |

| 2.1.3       | Ease of Design                                         |    |

| 2.2         | Micropipelines and Other Styles of Asynchronous Logic  | 33 |

| 2.3         | Asynchronous Logic and Power Efficiency                | 41 |

| 2.4         | The Disadvantages of Asynchronous Logic                |    |

| 2.5         | Conclusions                                            | 47 |

| Chapter 3   | : The Architecture of Asynchronous Processors          | 49 |

| 3.1         | Data Dependencies                                      | 50 |

| 3.2         | Order of Completion and Precise / Imprecise Exceptions | 54 |

| 3.3         | State Changing Actions                                 | 57 |

| 3.4         | Condition Codes and Conditional Instructions           |    |

| 3.5         | Branches and Flow-of-Control                           | 59 |

| 3.6         | Conclusions                                            |    |

| Chapter 4   | : Architectural Factors Influencing Power Efficiency   | 65 |

| 4.1         | Power Consumption Block-by-Block                       | 67 |

| 4.1.1       | Main Memory                                            | 67 |

| 4.1.2       | Caches                                                 |    |

| 4.1.3       | Memory Management                                      |    |

| 4.1.4       | Datapath                                               |    |

| 4.1.5       | Instruction Decoding and Sequencing                    | 72 |

| 4.2       | Summary of Factors Affecting Power Consumption            | 72     |

|-----------|-----------------------------------------------------------|--------|

| 4.3       | Code Density                                              |        |

| 4.3.1     | Defining and Measuring Code Density                       |        |

| 4.3.2     | Fixed and Variable Instruction Lengths                    |        |

| 4.3.3     | The Semantic Content of Instructions                      |        |

| 4.4       | Conclusions                                               | 80     |

| Chapter 5 | : The Potential For Increased Code Density                | 81     |

| 5.1       | Experimental Procedure                                    |        |

| 5.2       | The Sparc Architecture                                    | 82     |

| 5.3       | Unused Fields                                             | 83     |

| 5.4       | Opcode Fields                                             | 83     |

| 5.4.1     | Reducing the Number of Instructions                       | 84     |

| 5.4.2     | Variable Length Opcode Fields                             |        |

| 5.4.3     | Asynchronous Opcode Decoding                              | 88     |

| 5.5       | Immediate Fields                                          | 88     |

| 5.5.1     | Immediate Fields in Branch Instructions                   | 90     |

| 5.5.2     | Immediate Fields in Addition and Subtraction Instructions | 91     |

| 5.6       | Register Specifiers                                       | 93     |

| 5.6.1     | Number of Register Specifiers Per Instruction             | 94     |

| 5.6.2     | Number of Bits Per Register Specifier                     |        |

| 5.6.3     | Special Purpose Registers                                 |        |

| 5.7       | Features of the ARM Instruction Set                       | 99     |

| 5.8       | Conclusions                                               | 100    |

| Chapter 6 | 5 : Summary and Conclusions                               | 103    |

| 6.1       | Summary of Architectural Features                         | 103    |

| 6.2       | Quantitative Evaluation of the Proposed Architecture      | 109    |

| 6.2.1     | Power efficiency                                          | 111    |

| 6.2.2     | Performance                                               |        |

| 6.3       | Other Considerations for Architectures                    | 113    |

| 6.4       | Conclusions                                               | 113    |

| 6.5       | Future Work                                               | 114    |

| Appendix  | A: Patterns of Access to Data Operands                    | 115    |

| A.1       | Theoretical Models of Program Behaviour                   | 115    |

| A.2       | Experimental Studies of Program Behaviour                 | 116    |

| Appendix  | B : Analysis of the Code Density of the Sparc Process     | or 123 |

| B.1       | Instruction Frequencies                                   | 123    |

| B.2       | Frequency of Last Result Re-use                           | 124    |

| B.3       | The Distribution of Immediate Operands                    |        |

| B.4       | Two and Three Address Instructions       | 133 |

|-----------|------------------------------------------|-----|

| Appendix  | C : Benchmark Programs                   | 135 |

| C.1       | Programs Executed on the Shade Simulator | 135 |

| C.2       | Address Traces                           | 137 |

| Reference | ·S                                       | 139 |

# **List of Figures**

| Figure 2.1:  | Hypothetical pipeline arrangement                                       | 27 |

|--------------|-------------------------------------------------------------------------|----|

| Figure 2.2:  | Clock skew                                                              | 30 |

| Figure 2.3:  | Ground bounce                                                           | 31 |

| Figure 2.4:  | Two-phase transition signalling                                         | 33 |

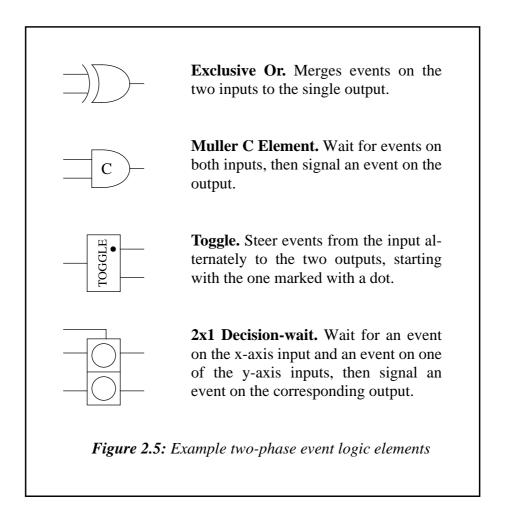

| Figure 2.5:  | Example two-phase event logic elements                                  | 34 |

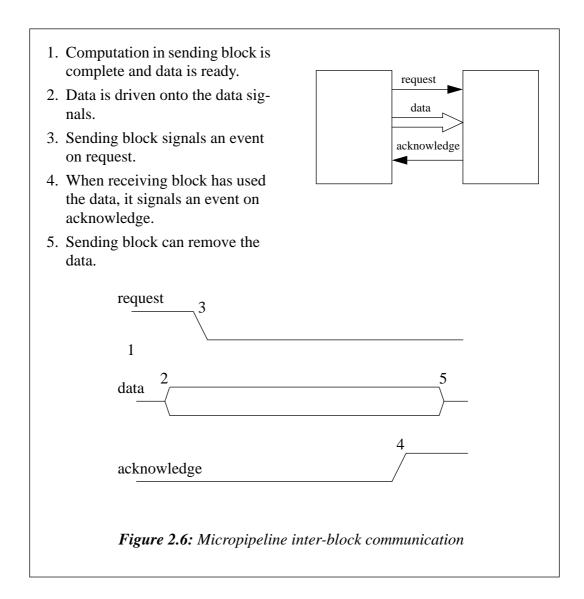

| Figure 2.6:  | Micropipeline inter-block communication                                 | 35 |

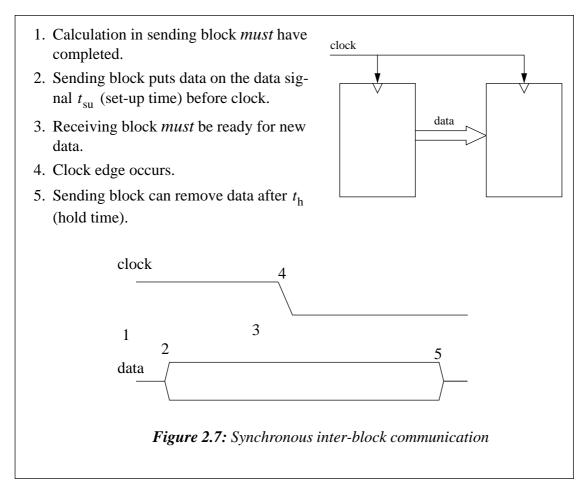

| Figure 2.7:  | Synchronous inter-block communication                                   | 36 |

| Figure 2.8:  | Four-phase transition signalling inter-block communication              | 37 |

| Figure 2.9:  | Bundled data circuit eliminated by the use of dual-rail signals         | 39 |

| Figure 2.10: | Bundled data pipelined ALUs                                             | 40 |

| Figure 2.11: | Pipelined ALUs using dual-rail encoding                                 | 41 |

| Figure 2.12: | Load on a clock signal compared to load on asynchronous control signals | 43 |

| Figure 2.13: | AMULET1 multiplier construction                                         | 46 |

| Figure 3.1:  | ARM architecture features                                               | 50 |

| Figure 3.2:  | A simple processor datapath pipeline                                    | 51 |

| Figure 3.3:  | Forwarding paths in a synchronous pipeline                              | 53 |

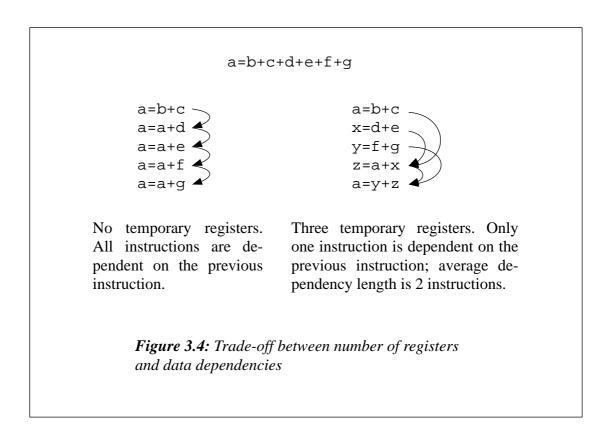

| Figure 3.4:  | Trade-off between number of registers and data dependencies             | 53 |

| Figure 3.5:  | Impact of a contended resource (condition codes) on data dependencies   | 54 |

| Figure 3.6:  | Pipeline arrangement for in-order completion                            | 55 |

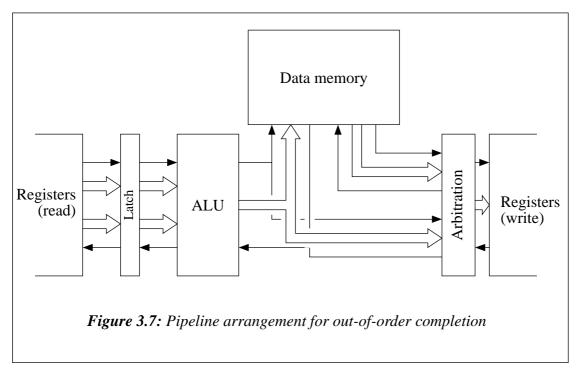

| Figure 3.7:  | Pipeline arrangement for out-of-order completion                        | 56 |

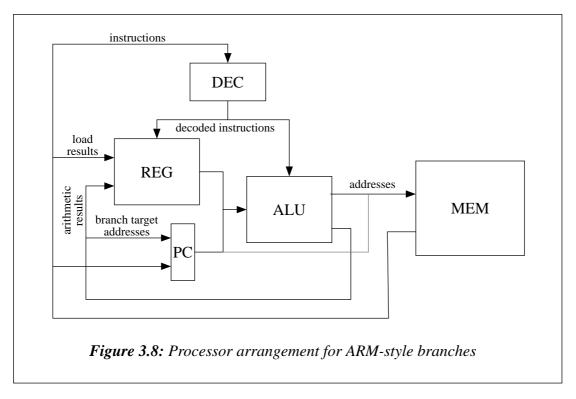

| Figure 3.8:  | Processor arrangement for ARM-style branches                            | 60 |

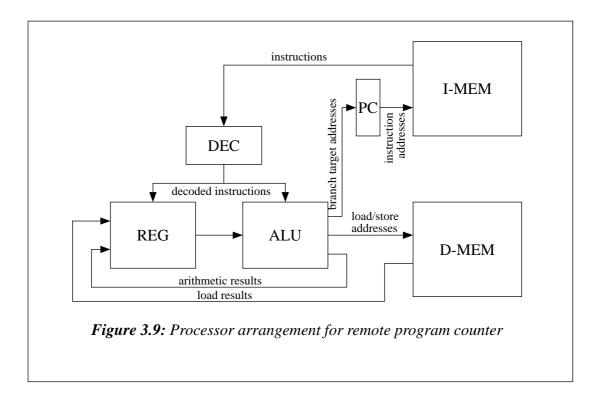

| Figure 3.9:  | Processor arrangement for remote program counter                        | 61 |

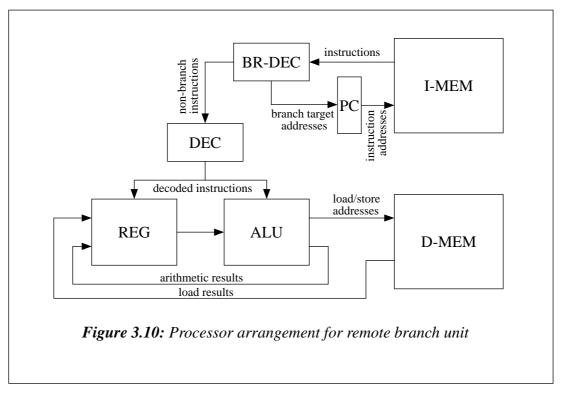

| Figure 3.10: | Processor arrangement for remote branch unit                            | 61 |

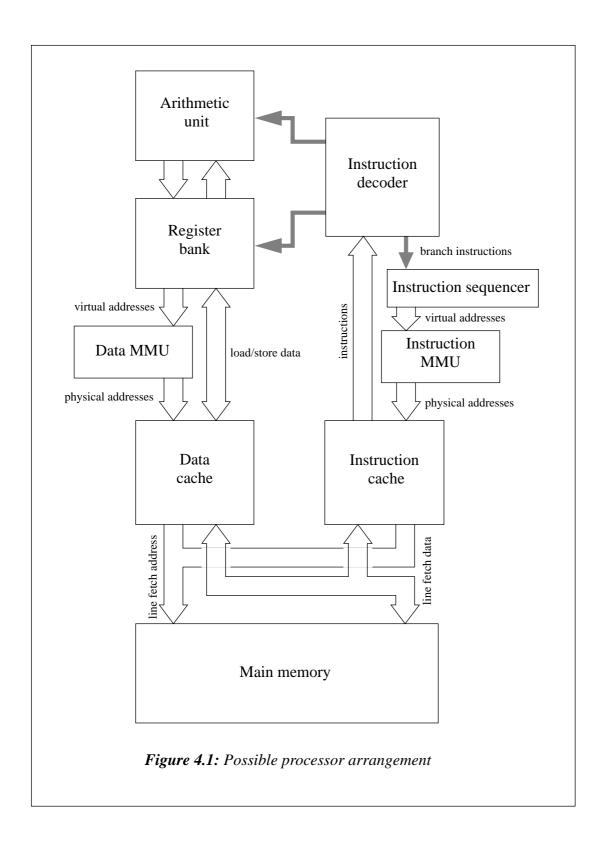

| Figure 4.1:  | Possible processor arrangement                                          | 66 |

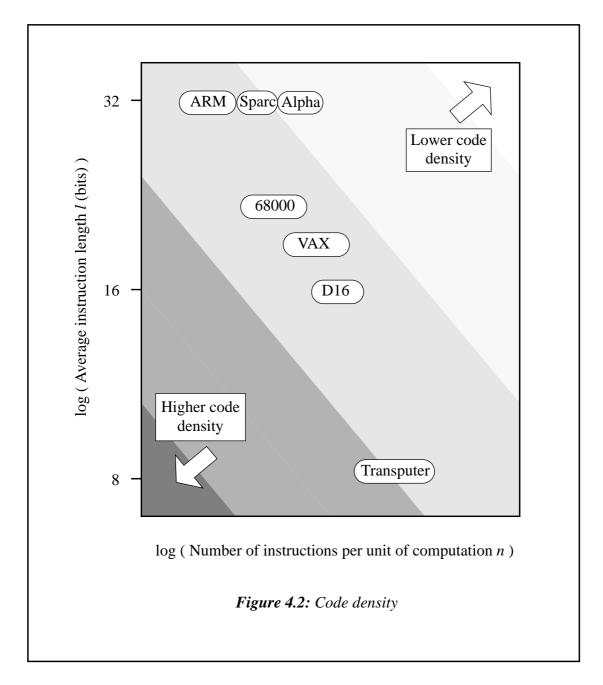

| Figure 4.2:  | Code density                                                            | 76 |

| Figure 5.1:  | Characteristics of the Sparc processor                                  | 82 |

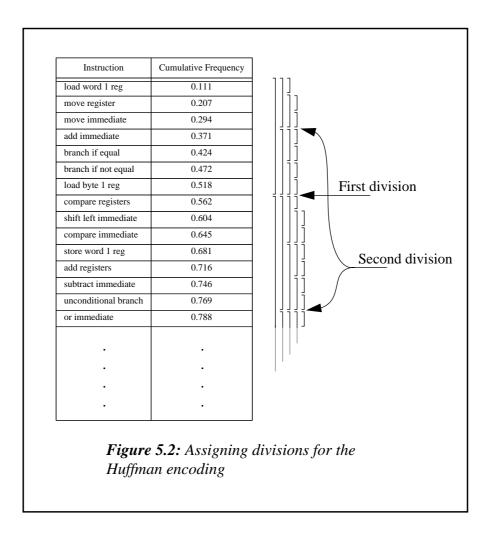

| Figure 5.2:  | Assigning divisions for the Huffman encoding                            | 87 |

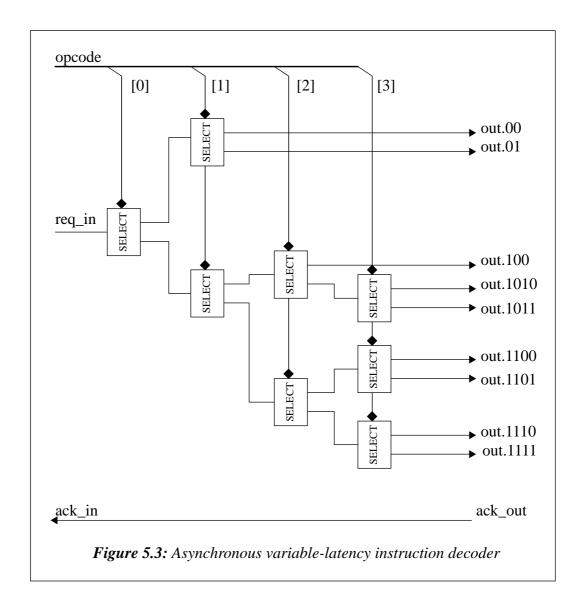

| Figure 5.3:  | Asynchronous variable-latency instruction decoder               | 89  |

|--------------|-----------------------------------------------------------------|-----|

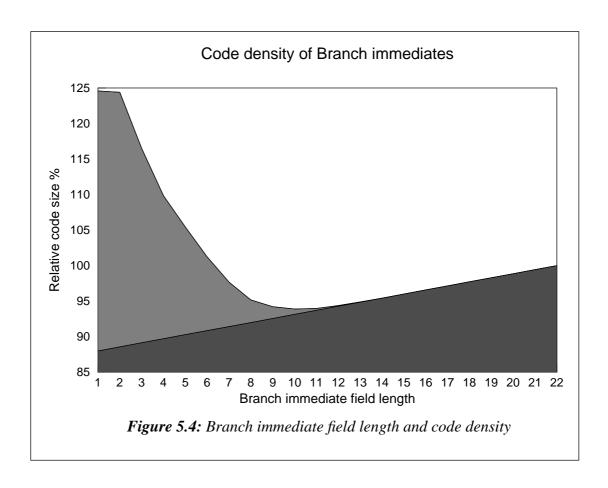

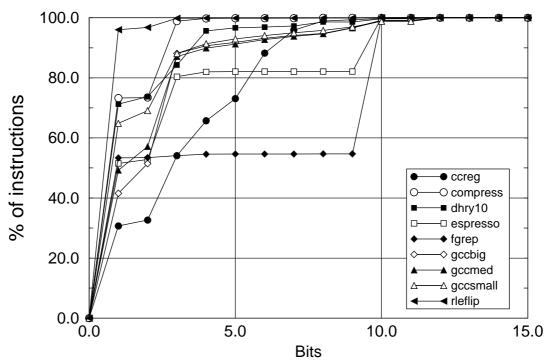

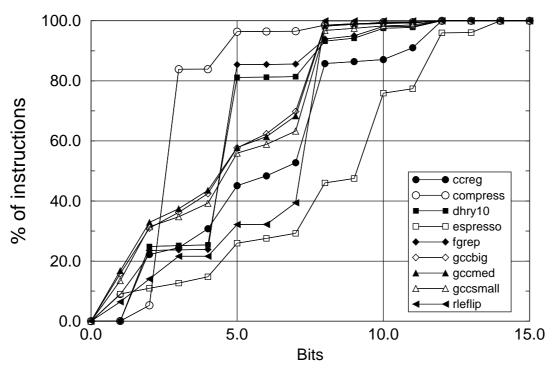

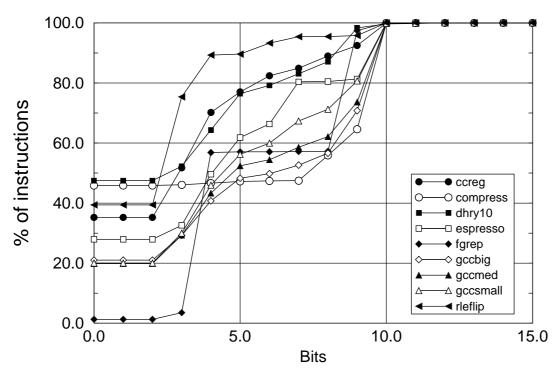

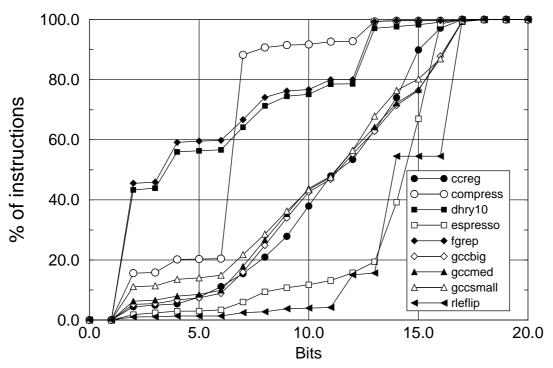

| Figure 5.4:  | Branch immediate field length and code density                  |     |

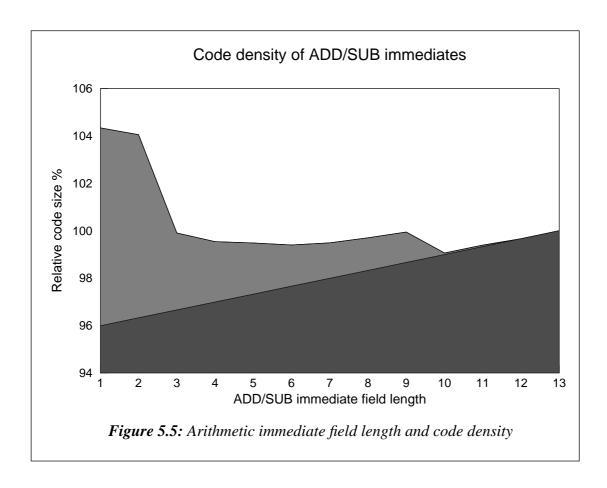

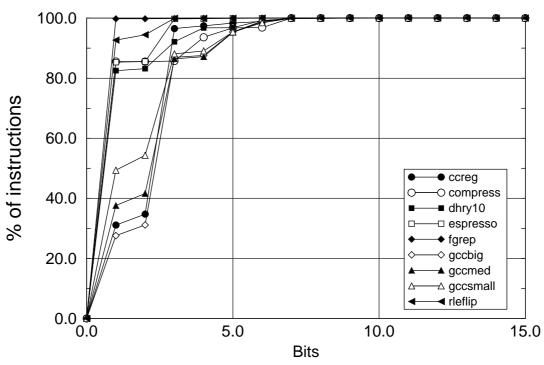

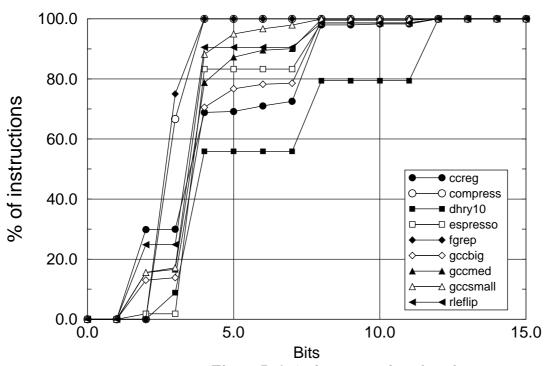

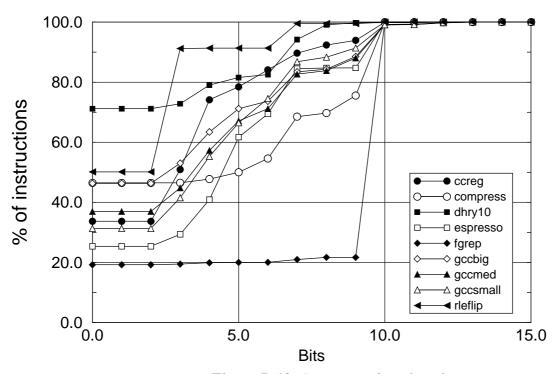

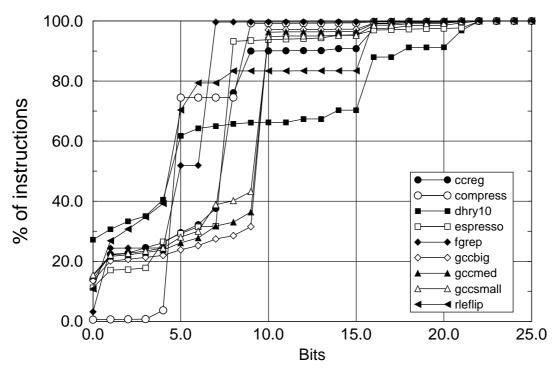

| Figure 5.5:  | Arithmetic immediate field length and code density 92           |     |

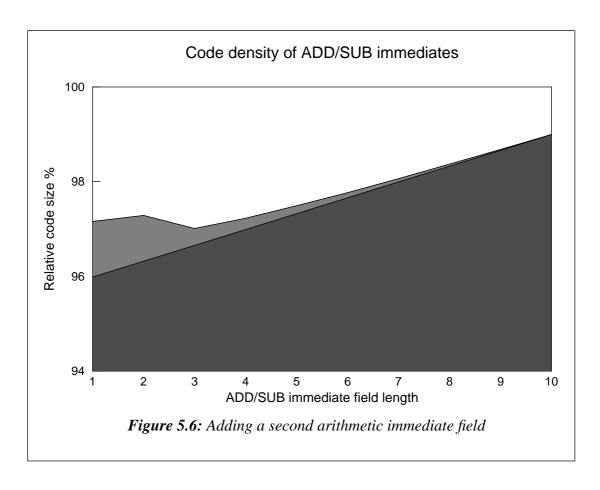

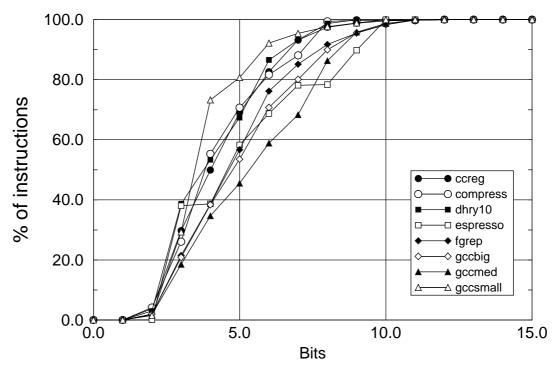

| Figure 5.6:  | Adding a second arithmetic immediate field                      | 93  |

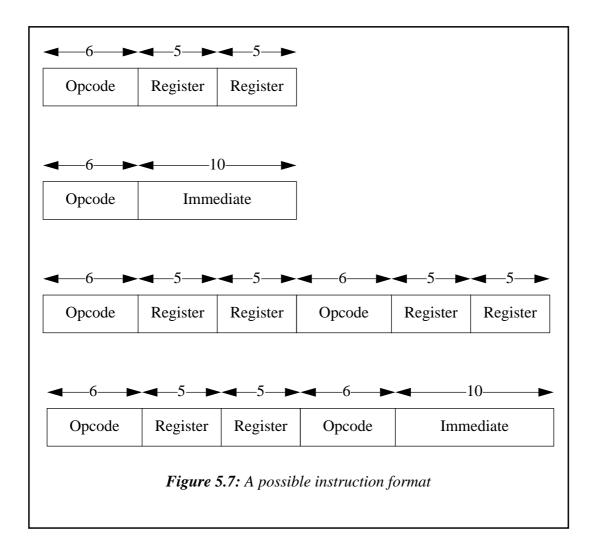

| Figure 5.7:  | A possible instruction format                                   | 102 |

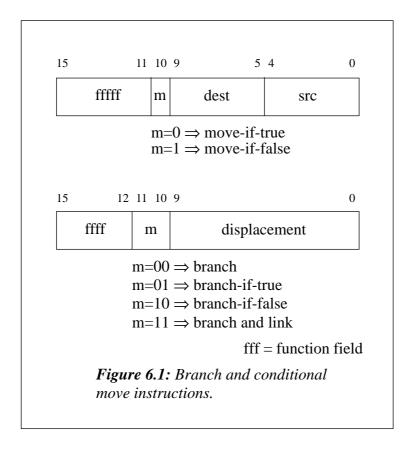

| Figure 6.1:  | Branch and conditional move instructions                        | 106 |

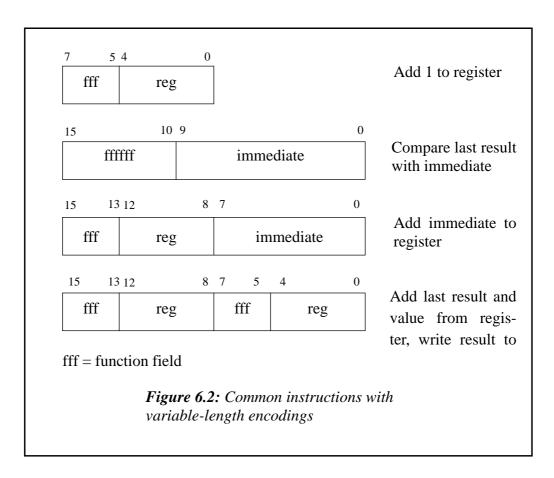

| Figure 6.2:  | Common instructions with variable-length encodings 107          |     |

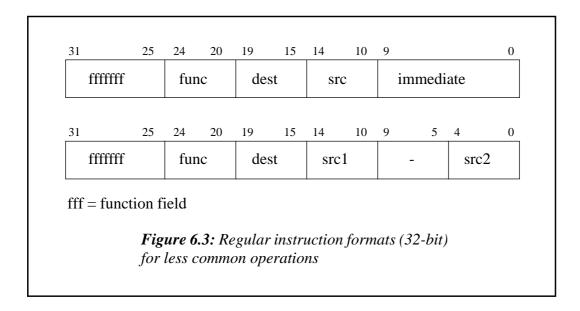

| Figure 6.3:  | Regular instruction formats (32-bit) for less common operations | 108 |

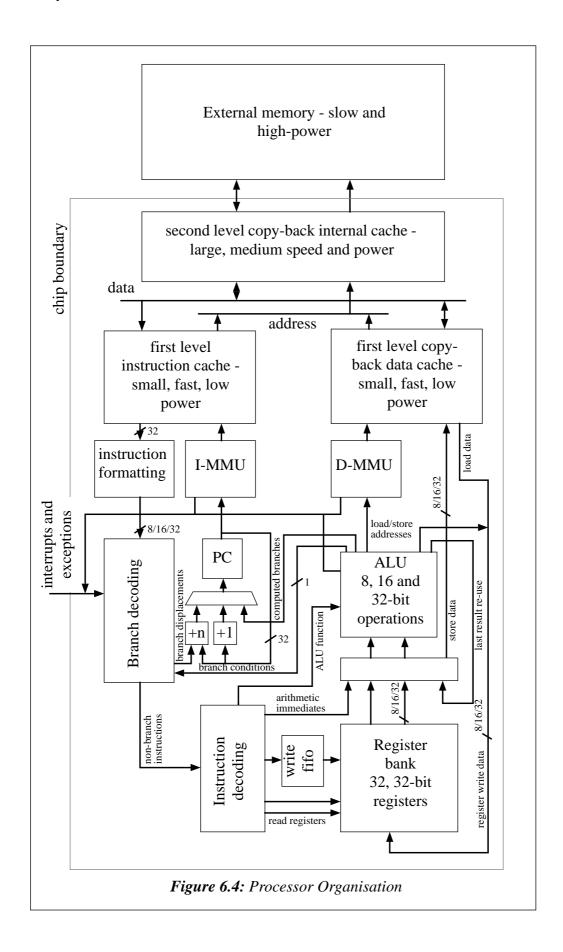

| Figure 6.4:  | Processor Organisation                                          | 110 |

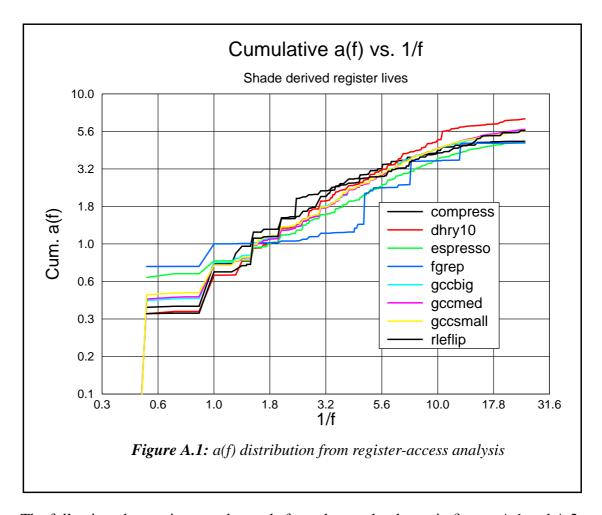

| Figure A.1:  | a(f) distribution from register-access analysis                 | 119 |

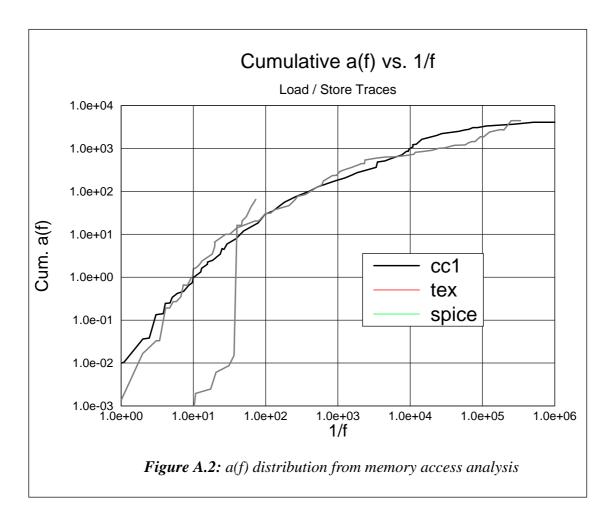

| Figure A.2:  | a(f) distribution from memory access analysis                   | 120 |

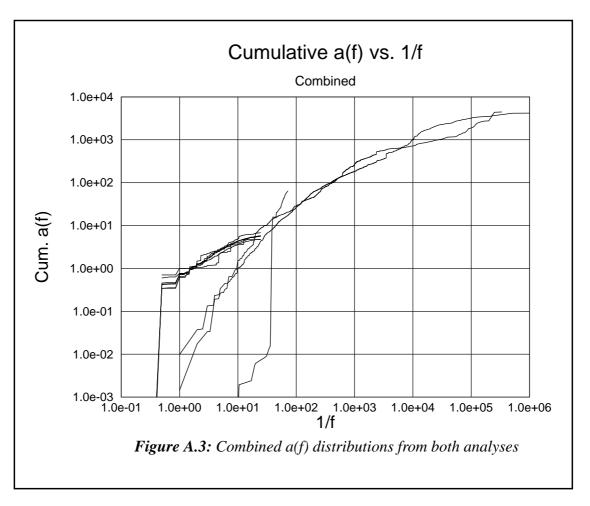

| Figure A.3:  | Combined a(f) distributions from both analyses                  | 121 |

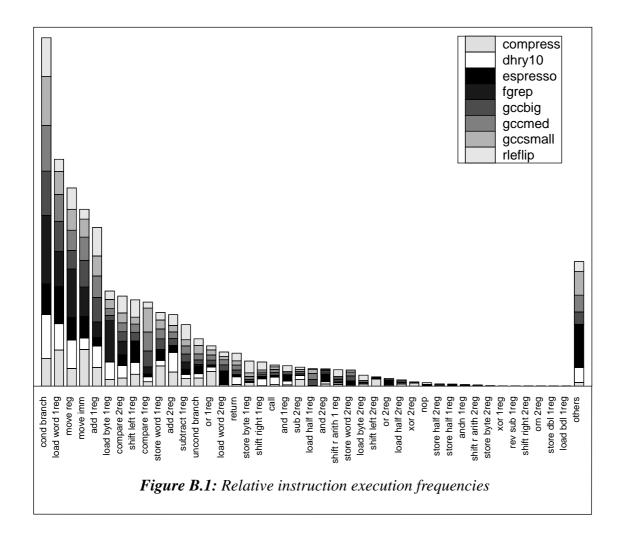

| Figure B.1:  | Relative instruction execution frequencies                      | 124 |

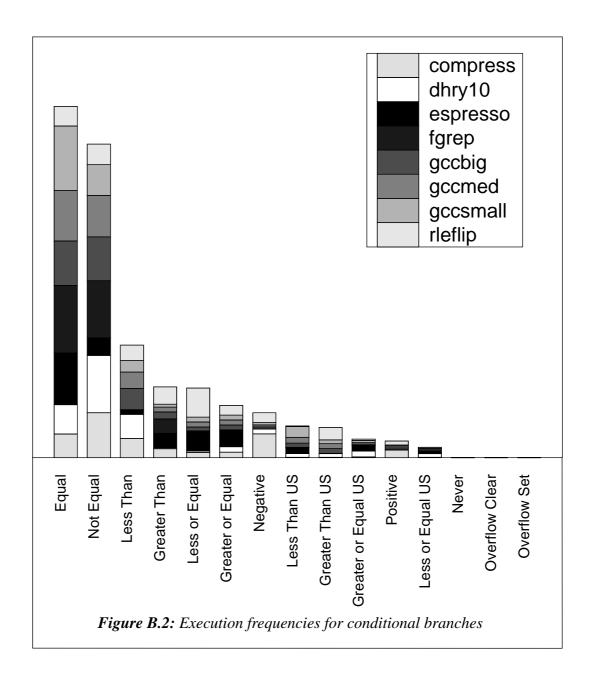

| Figure B.2:  | Execution frequencies for conditional branches                  | 125 |

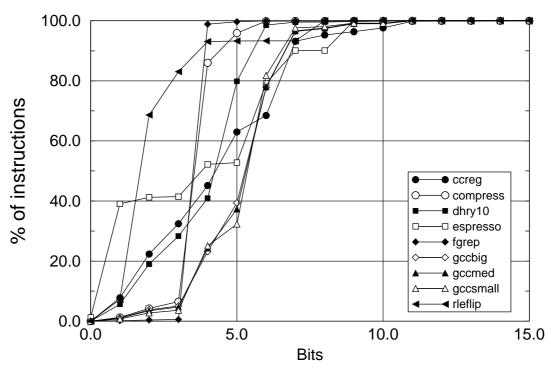

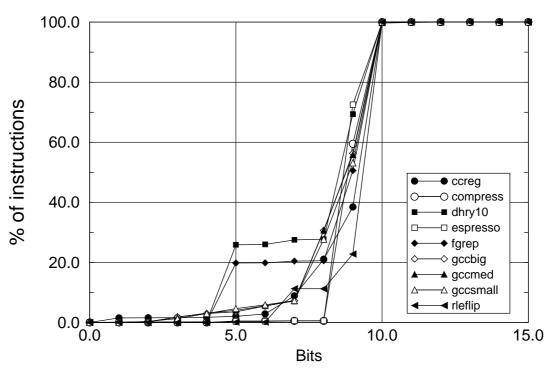

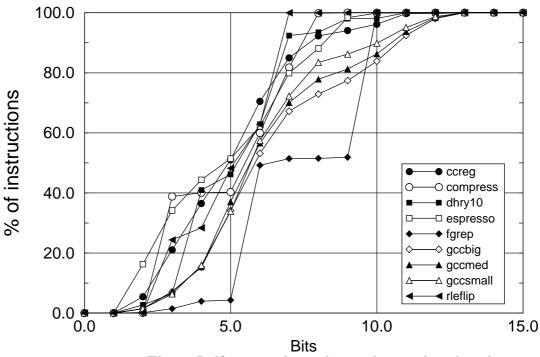

| Figure B.3:  | Add immediate lengths                                           | 127 |

| Figure B.4:  | Subtract immediate lengths                                      | 127 |

| Figure B.5:  | And immediate lengths                                           | 128 |

| Figure B.6:  | And Not immediate lengths                                       | 128 |

| Figure B.7:  | Compare immediate lengths                                       | 129 |

| Figure B.8:  | Or immediate lengths                                            | 129 |

| Figure B.9:  | Load immediate lengths                                          | 130 |

| Figure B.10: | Store immediate lengths                                         | 130 |

| Figure B.11: | Conditional Branch immediate lengths                            | 131 |

| Figure B.12: | Unconditional Branch immediate lengths                          | 131 |

| Figure B.13: | Call immediate lengths                                          | 132 |

| Figure B.14: | Move immediate lengths                                          | 132 |

# **List of Tables**

| Table 1.1: | 17                                                             | ••••• |

|------------|----------------------------------------------------------------|-------|

| Table 1.2: | Projected power consumption (approximate)                      | 18    |

| Table 2.1: | Four-phase dual-rail encoded data representation               | 38    |

| Table 2.2: | Comparison of design styles by number of transitions per cycle | 42    |

| Table 5.1: | Replacement sequences for infrequent instructions              | 85    |

| Table 5.2: | Relative density resulting from 4-bit and 5-bit opcode fields  | 86    |

| Table 5.3: | Potential for shorter immediate fields                         | 90    |

| Table 5.4: | Length of arithmetic immediates                                | 92    |

| Table 5.5: | Number of registers and code density                           | 97    |

| Table 5.6: | Summary of code density increases                              | 100   |

| Table 6.1: | Power efficiency and number of registers                       | 104   |

| Table B.1: | Last result re-use                                             | 126   |

| Table B.2: | Immediate lengths summary                                      | 133   |

| Table B.3: | Potential for 2-address instructions                           | 134   |

| Table C.1: | GCC benchmark input files                                      | 136   |

| Table C.2: | Sizes of benchmark programs                                    | 137   |

# **Abstract**

Portable battery-operated computing equipment requires high processing performance and low power consumption. Other computer systems may need low power consumption for other reasons such as overcoming the problem of heat transport away from the processor chip. This thesis investigates ways in which processor architecture can influence power efficiency.

One implementation technique which may lead to lower power consumption is the use of asynchronous logic. In particular, asynchronous logic can be more power-efficient in a system with a rapidly-changing computational load. Because of the differences between synchronous and asynchronous logic, certain architectural features are more suited to asynchronous implementation than others. This thesis proposes a number of features that are more suitable for asynchronous implementation. Important areas include the branch mechanism and the way in which data dependencies are dealt with.

Other architectural factors that influence power consumption are investigated. Increasing code density will lead to increased power efficiency because the power consumed in many parts of the computer system is proportional to the rate of instruction fetch. Code density is investigated and ways in which the density of the SPARC architecture could be increased are proposed. The most important improvements are found to result from using a Huffman encoded opcode field and reducing the length of some immediate fields. Other factors are the use of 2-address instructions, load and store multiple instructions and explicit last result re-use.

It is also noted that the power efficiency of the memory system can be increased through the use of multiple level caches and by using a copy-back write policy.

By combining these features, an architecture with a power efficiency double that of a conventional processor could be constructed.

# **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or institute of learning.

# **Acknowledgements**

Over the last year I have received a great deal of help from very many people, without which the work described in this thesis would have been impossible.

My supervisor Prof. Steve Furber has been a great source of inspiration. I would like to thank him for his constant interest in my ideas and encouragement.

The other members of the AMULET research group have provided me with a stimulating environment in which to work. I am grateful to them all for helping me to understand asynchronous logic and for listening to my ideas.

Much of my data has been collected using the SPARC simulator 'Shade' and the GNU C Compiler. These programs have been made available free of charge, and I would like to thank those people who have made this possible, including everyone at the Free Software Foundation and Bob Cmelik at Sun.

I am also grateful for help and information given by GCC users, computer architects and others through the USENET NEWS system. I am especially grateful to Jim Wilson for his assistance with GCC, and John Fitch for providing information about the DEC ECL BIPS processor.

Several people have helped by reading and commenting on drafts of this thesis. I must extend my thanks to Viv Woods for his useful comments, and to my father Richard Endecott and to Janette Taylor for proofreading.

Thanks, everyone.

# The Author

Philip Endecott obtained a B.Sc. (I) degree in Computer Science from the University of Manchester, England, in 1991. This thesis is the result of the first year of research as a member of the AMULET research group at the University of Manchester.

AMULET (Asynchronous Microprocessor Using Low Energy Techniques) comprises four projects looking at different areas where asynchronous logic techniques can be applied.

# Chapter 1: The Increasing Importance of High Power Efficiency

This thesis is about designing computer architectures whose implementations can have low power consumption. This introductory chapter examines the reasons for wanting low power consumption and the techniques that can be applied to achieve it.

The body of the work concentrates on two techniques that can be used to improve power efficiency. Firstly the idea of using asynchronous logic is considered, and secondly the influence of processor architecture on power efficiency is studied. The objective is to define a set of architectural features that permit an asynchronous power-efficient implementation.

# 1.1 Why Low Power?

The most well-known motivation for the design of power-efficient processors is for battery operated portable applications. As well as this, power efficiency is important or will become important in some applications because of the problems of thermal management and power supply. A third motivation is the issue of electricity cost and the environmental impact of power consumption.

These three issues are investigated in this section.

## **New Application Areas Need Low Power**

Increased performance from physically small computer systems has opened up a number of application areas for portable battery powered equipment. Examples include:

- Portable personal computers. It is not unusual to find portable personal computers

with processing performance, storage capacity and screen resolution closely comparable to desktop machines.

- **Personal Digital Assistants (PDAs).** This new class of portable computer demands a high-performance processor for functions such as handwriting recognition.

- Hand-held video games. Again, performance can be similar to non-portable equipment.

- Personal Digital Hi-Fi. The processing power needed to control a compact disk or digital cassette player is significant.

- **Portable Radio Telephones.** The demand to accommodate more channels within the same bandwidth for cellular telephones means that sophisticated signal compression techniques are being applied, with considerable processing requirements.

- Global Positioning by Satellite (GPS) systems. Previously used only by the military and mariners, GPS is now becoming cheap and small enough to use in cars; soon perhaps by mountaineers as well.

- **Hand-held photo and video equipment.** Successful digital photo and video cameras need good image sensors, high density storage and sufficient processing power to apply the necessary image compression algorithms.

Users of these products demand low weight and size and long operating periods between battery changes or recharging. Often, batteries make up a significant proportion of the size and weight and yet users are not satisfied with the battery life. To improve the situation, either the energy density of the battery must be increased, or the power consumption of the system must be reduced. Battery technology will improve, and in the period 1946 to 1980 battery energy density doubled approximately every ten years [2], but the growth in demand is likely to exceed the growth in battery capacity.

Approximate values for the energy density and cost of some batteries used in portable equipment are given in table 1.1 [2] [3]. Note that the battery with the highest energy density, the lithium battery, has a capacity considerably greater than the alkaline battery but the cost grows even faster. Note also that rechargeable batteries have an energy density around three times smaller than that of non-rechargeables. In order to keep the cost of the batteries needed at a reasonable level, the most advanced technology must be avoided.

The only alternative to increasing battery capacity is to reduce the power consumption of the equipment. This includes building more energy-efficient processors.

Some might expect that in the applications listed above components such as motors, speakers, RF transmitters etc. would consume far more power than the control electronics. However in practice the digital electronics actually consumes a significant proportion. For example, in a portable compact disk player approximately 50% of the power consumption is in the integrated circuits [1].

| Battery                          | $\frac{\text{Energy density}}{\text{kJ kg}^{-1}}$ | Cost pence kJ <sup>-1</sup> |  |

|----------------------------------|---------------------------------------------------|-----------------------------|--|

| Primary (non-rechargeable) cells |                                                   |                             |  |

| Zinc carbon                      | 230                                               | 2.6                         |  |

| Zinc chloride                    | 270                                               | 2.2                         |  |

| Alkaline                         | 340                                               | 3.0                         |  |

| Lithium                          | 1200                                              | 12.7                        |  |

| Secondary (rechargeable) cells   |                                                   |                             |  |

| Lead acid                        | 108                                               |                             |  |

| Nickel cadmium                   | 111                                               |                             |  |

**Table 1.1:** Batteries used in portable equipment (approximate)

#### **Thermal and Electrical Issues**

Although the obvious applications needing power-efficient processors are the battery operated ones described above, it is probable that it will soon be necessary to apply the same low-power techniques to mains-powered desktop systems.

Since the beginning of 1992, DEC has announced two processors with very high power consumption: a CMOS implementation of the Alpha architecture that consumes 30W [4], and an ECL implementation of the MIPS architecture that consumes 115W [5]. Although this power consumption is currently considered to be high, future processors will inevitably be announced with still higher power consumption.

How fast will power consumption increase? If current trends continue, the feature size used in integrated circuit fabrication will continue to decrease by about 12% per year [6]. If this decrease in feature size is not accompanied by a decrease in supply voltage (as was the case until recently when all systems used 5V supplies), it would lead to an increase in power consumption per unit area of about 45% per year<sup>1</sup>. However it seems that there is now a move to lower supply voltages as components operating at 3.3V are increasingly common. If supply voltage is scaled down linearly with the feature size there will be no increase in power consumption per unit area, although current consumption per unit area would increase by about 12% per year.

<sup>1.</sup> With constant voltage, power density increases by  $\alpha^3$  as feature sizes decreases by  $\alpha$ . So if  $100\% - \frac{1}{\alpha} = 12\%$ ,  $\alpha^3 = 1.47$ . See [6], table 4.12.

<sup>2.</sup> Assuming that operating frequency is always increased to the greatest possible value.

As integrated circuit processing techniques improve, defect density will decrease and larger devices will be feasible with economic yields. The trend in increasing device size is not as regular or as well understood as the trend in decreasing feature size; however the capacity of DRAM memory chips has typically increased by around 60% per year[7] which is about 24% more per year than is explained by the decrease in feature size. This suggests that area is increasing by about 24% per year.

If these trends apply to processors in the future, we can extrapolate the figures in table 1.2, based on the DEC 21064 Alpha in 1992 using 30W from a 3.3V supply as a starting point.

| V    | Constant voltage      | Voltage scales with feature size |                                    |

|------|-----------------------|----------------------------------|------------------------------------|

| Year | Power consumption / W | Operating voltage / V            | Power consumption / W <sup>a</sup> |

| 1992 | 30                    | 3.3                              | 30                                 |

| 1994 | 95                    | 2.6                              | 45                                 |

| 1996 | 315                   | 2.0                              | 70                                 |

| 1998 | 1015                  | 1.5                              | 110                                |

| 2000 | 3275                  | 1.2                              | 170                                |

*Table 1.2:* Projected power consumption (approximate)

Although supply voltages are likely to decline to some extent, there are three reasons why they may not decline as fast as the feature size:

- In a system it is difficult to operate different components with different supply voltages, so the system supply voltage will drop only as quickly as the slowest individual components.

- Maintaining a higher operating voltage permits operation at a higher operating frequency, and hence to higher performance. Designers will find ways to avoid scaling down supply voltage in order to maintain performance.

- Transistor threshold voltages must scale down with supply voltage. It will become increasingly difficult to make transistors with small enough thresholds.

a. Note that because the supply voltage is decreasing, supply current will grow more quickly than power consumption. It will increase 15 fold from 9A in 1992 to 140A in 2000.

Whatever happens to supply voltage, in a few years processor chips will be consuming far more power than they are now. This will face designers with problems including the following:

- The capacity of power supplies has to be increased and distribution of power on the circuit board becomes more difficult.

- Power supply from the board to the dies becomes more difficult: the number of bond wires and pins used for power and ground has to be increased. The DEC 21064 Alpha chip uses a total of 138 power and ground pins to supply its 30W requirement. The current that can be passed through a gold bond wire before it melts and the closest pitch at which they can be bonded also imposes a limit on the amount of power that can be transferred to the chip [8].

- Power distribution on the chip becomes more difficult. The DEC ECL BIPS chip has to use a layer of 25µm thick gold power distribution rails over the top of the rest of the chip for power distribution [8].

- The very high currents on the chip can cause electromigration; that is, the force of the moving electrons hitting metal atoms leads to deformations and breaks in the metal [9].

- Removing the heat from the chip becomes increasingly difficult. There is an upper limit on the amount of heat that can be carried away by a passive heat sink of a few hundred watts<sup>1</sup>. At this point, active devices such as the Peltier-effect heat pump which cools the package to below ambient temperature [13] and the heat pipe or thermosiphon (as used by the DEC ECL BIPS chip [8]) become necessary. In practice, at high power dissipations the most difficult stage is moving the heat the first millimetre or so from the die to the heat sink. A good material for this is diamond, which is an excellent thermal conductor and also an electrical insulator. Cray computers have used diamond-filled epoxy compounds to attach dies to heatsinks. A more extreme solution is to etch channels on the back of the die and pump coolant through the channels. It has been estimated that by using this technique power dissipation up to 4kW per device can be dealt with [10].

- Removing waste heat from enclosures requires larger fans and design effort has to be spent on air-flow design. The noise level from fans has to be kept low enough to reduce noise pollution.

<sup>1.</sup> This calculation is based on the thermal resistance of an infinite hemisphere of copper, which is around 0.1  $^{\circ}$ C/W when connected to a heat source of size 1cm  $\times$  1cm .

Not only are these problems difficult to overcome, but the solutions can be expensive. For example, the thermosiphon used by DEC [8] would cost \$125 in large quantities. The cost of gold power distribution rails and diamond adhesive prohibits their use in all but a few cost-insensitive applications.

To avoid problems like these, high-performance systems will need to apply similar power efficiency techniques to the ones used by battery operated equipment.

#### **Environmental Issues**

It has been estimated that 5% of the USA's non-domestic electricity consumption is used by computing equipment, and this is set to rise to 10% by the end of the decade [11]. Reasons for this increase include the increased power consumption of individual computers, the increasing number of computers, and the increasing tendency to leave equipment permanently switched on. In the US, the Environmental Protection Agency has proposed a standard for a low-power personal computer. They estimate that adoption of this standard could lead to a reduction in CO<sub>2</sub> emissions equivalent to 5 million cars.

Adoption of the low-power standard would also lead to significant financial savings on individual electricity bills. The electricity to operate a personal computer consuming 300W continuously for a year currently costs around £200 in the UK.

In the case of the personal computer, the majority of the power savings can be made in areas other than the processor; the most important areas are in the monitor and in increasing the efficiency of the power supply [12]. However the contribution made by the processor is not insignificant, and if neglected it will become more significant as the efficiency of other parts of the system increases. Processor manufacturers have started to realise this; for example Intel has recently announced that it will incorporate power-saving logic previously used only in processors for portable computers into all of its i486 processors[11].

#### **Conclusions**

It has been shown that high power efficiency is or will soon become an important factor in computer system and processor design in all types of equipment. In low-performance applications, the driving force is increased battery life for portable equipment. In medium performance applications, the cost of electricity and the environmental results of electricity use are most important. For the highest performance applications, the high thermal dissipation and power distribution may become limits.

The next section studies the approaches that exist for reducing power consumption.

# 1.2 How Can Power Consumption Be Reduced?

Power reduction techniques can be applied in many of the levels of the computer system, from underlying silicon techniques at the bottom level to compiler optimisations at the highest level.

## **Approaches Based on the Fundamental Technology**

At the lowest level, power consumption is proportional to the capacitance of the wires and transistors on the chip and the square of the supply voltage [6]. Running the chip at a reduced voltage will reduce power consumption, but it will also reduce performance as maximum operating frequency is proportional to supply voltage.

The capacitance of the wires is proportional to the feature size,  $\lambda$ . Decreasing the feature size will give a proportional reduction in power consumption. The limit on feature size is imposed by the available technology for fabrication and is constantly decreasing. This decrease in feature size will certainly lead to further increases in power efficiency.

## **Circuit Design Approaches**

In CMOS circuits, power consumption is proportional to the number of signal transitions <sup>1</sup>. Power consumption can therefore be reduced by reducing the number of signal transitions that occur. Consider for example a state machine whose state is represented by four bits, which spends 99% of its time alternating between two of these states. If these states were encoded as 0000 and 1111, there would be 4 times as much power dissipation in the state machine than if they were encoded as 0000 and 0001, because there would be four times as many signal transitions. It should be possible to incorporate this sort of optimisation into automatic logic synthesis programs, which could balance the trade-off between the most energy-efficient encoding and the encoding with the smallest or fastest implementation.

In another case, there can be a trade-off between power consumption and logic size. Sometimes pre-charge logic [6] is used, where nodes are charged to one state through a pre-charge transistor, and then possibly discharged to the other state through a transistor tree. This is in contrast to the simpler static logic approach where transistor trees are used in the pull-up and pull-down paths. The pre-charge approach saves transistors, but it means that on each cycle the output nodes make twice as many transitions<sup>2</sup>.

<sup>1.</sup> In other technologies such as ECL, power consumption is static, i.e. independent of the number of transitions. Hereafter CMOS is implied unless otherwise stated.

<sup>2.</sup> Assuming an equal probability that the bit is a zero or a one. It can be worse; in a circuit such as a content addressable memory (CAM), the 'hit lines' may be the output of pre-charge logic. All but one of the bit lines is charged and discharged, making two transitions, every cycle.

The use of asynchronous logic rather than clocked synchronous logic may also lead to improved power efficiency. This effect results from various possible factors, the most important of which is the ability of asynchronous systems to perform well in situations with varying computational load.

#### Parallelism versus Speed

In some applications it is possible to replace a circuit with another that has greater parallelism but a lower operating frequency and lower power consumption [14]. If a circuit consists of n parallel sub-circuits, all operating at frequency f and supply voltage v, its throughput is proportional to nf and its power consumption is proportional to  $nv^2f$ . If the number of sub-circuits was doubled to 2n and the operating frequency was reduced to  $\frac{1}{2}f$ , the throughput would remain nf. However since maximum operating frequency is proportional to supply voltage [6], at the reduced operating frequency the supply voltage could be reduced to  $\frac{1}{2}v$ . The power consumption would then be  $\frac{1}{4}nv^2f$ ; that is, doubling the silicon area reduces the power consumption four-fold.

Designs rarely if ever make use of parallelism with the objective of reducing power consumption. When parallelism is used in processors it is done to increase the performance that is possible at the supply voltage and operating frequency being used. Examples of this type of parallelism are multiple ALUs (superscalar processors) and multi-word wide buses between internal blocks [7].

#### **Sleep Modes**

At a higher level, systems can partially disable themselves when inactivity is detected. This feature is frequently found on portable computers. The simplest approach is to reduce the clock frequency. To obtain a further reduction in power consumption, once the clock frequency has been reduced the supply voltage can be reduced to give an even greater power saving. Reducing the supply voltage to a chip whilst it is enabled may not be a simple procedure, particularly for memory chips which may contain internal nodes that can store voltages across the change. The limit on the power efficiency improvement that can be obtained with a sleep mode depends on the workload pattern of the computer; if the computer is expected to be idle for a large proportion of the time, a sleep mode will be more beneficial than if it is almost permanently active.

## **Architectural Approaches**

Certain aspects of a processor architecture can indirectly affect power consumption, in particular the energy used to fetch instructions is inversely proportional to the code density of the instruction set. Another example of an architectural feature influencing power consumption is the width of the processor's datapath; a wide datapath wastes energy when it is used to operate on narrow data.

## **Software and Compiler Techniques**

If the algorithms used by the programs in use or the optimisations applied by the compiler to those programs can be improved so that they do the same work in fewer instructions, they will consume less energy as they are executed. These optimisations also lead to increased speed, and are constantly being improved.

#### 1.3 Introduction to this Work

All of the areas mentioned above are important, and a successful power-efficient processor will combine the best techniques from each area to obtain the optimum power consumption.

This thesis concentrates on two of these areas, namely the use of asynchronous logic and the influence of the processor architecture.

Chapter 2 introduces asynchronous logic and argues why it may have better power efficiency than traditional synchronous logic in some applications.

Chapter 3 describes why a processor using asynchronous logic can exploit different architectural features from a conventional synchronous processor. The AMULET1 processor design, which is an asynchronous implementation of an architecture originally implemented synchronously, is considered and features that an architecture needs for efficient asynchronous implementation are proposed.

Chapter 4 looks at the power consumption in a processor system and finds that it is influenced by code density and other features. The issue of code density is investigated further and the densities of various processors are compared.

Chapter 5 describes various experimental studies to find how the code density of an architecture can be increased. The code density of the Sparc architecture is examined, and various ways in which its code density could be increased are proposed.

Chapter 6 draws together the architectural features that have been proposed in chapters 3 and 5, and proposes the basis of an architecture that is suitable for a power-efficient

The Increasing Importance of High Power Efficiency

asynchronous implementation. The chapter concludes with a mention of possible future work.

There are three appendices, concerned principally with the experimental data used in Chapter 5. Appendix A studies the pattern of data accesses made by a program to its register bank and to main memory and gives a mathematical model for an aspect of this behaviour. This data is useful for evaluating the size of register banks, caches etc. Appendix B presents data relating to the frequency of occurrence of instructions in the Sparc architecture, the distribution of immediate values, and other data. Appendix C describes the benchmark programs used.

# Chapter 2: Asynchronous Logic

Currently most digital design including processor design is done using synchronous globally-clocked techniques. Synchronous design has been successful but some believe that asynchronous logic has the potential to perform better in some applications.

There are several different areas where asynchronous logic may have advantages. These include:

- Speed.

- · Power efficiency.

- Formal verification and synthesis

This chapter starts by introducing some of these the proposed advantages of asynchronous logic over synchronous logic. Secondly, it describes some of the basic asynchronous implementation techniques.

The reason why asynchronous logic is of interest in this work is its potential for improved power efficiency. The third section covers the arguments for why asynchronous logic may have better power efficiency than synchronous logic.

# 2.1 Asynchronous Logic versus Synchronous Logic

Synchronous designs make use of a global clock signal, distributed to all parts of the system, to control timing. Communication between blocks is all relative to this clock. Blocks sample their inputs on an edge of the clock signal, and arrange for their outputs to be stable on some future edge of the same signal.

In contrast, in an asynchronous design there is no such global signal. All inter-block communication occurs at a local level. When a block wishes to communicate with its neighbour, it does so by means of some form of local request-acknowledge signalling.

The types of asynchronous circuits discussed here fall into the category of being selftimed. This means that circuits generate their own timing signals by means of matched paths and delays. This is one of the weakest forms of asynchronous logic. Other asynchronous designs make use of stronger methodologies, such as delay-insensitive logic which does not rely on matched delays. [19] [20]

What advantages does the asynchronous technique have over the synchronous? There are 4 possible arguments in favour of asynchronous design:

- The speed of an asynchronous design is dependent on the time taken in the typical case, whereas for a synchronous design the speed is always limited by the worst case.

- Asynchronous circuits do not suffer from clock skew and may not suffer from ground bounce.

- Asynchronous design is easier than synchronous design.

- Asynchronous circuits consume less power than synchronous circuits.

These points are discussed in the following sections.

# 2.1.1 The Typical-Case / Worst-Case Timing Argument

The clock frequency in a synchronous system has to be slow enough to allow all blocks to propagate changes from their inputs to their outputs in one clock cycle in all conditions. The worst case will occur for:

- The slowest block.

- Its slowest operation.

- Its worst-case input data.

- Its worst operating conditions (i.e. supply voltage, fabrication speed and temperature).

In the case of an asynchronous system, the delay from data being read into a block to data being available on the output is variable and need never be longer than is necessary. It may sometimes be as slow as the synchronous clock period, but for a typical block doing a typical operation on typical data in typical conditions the delay will be smaller. So an asynchronous system will *typically* operate faster than a synchronous system.

Designers of synchronous systems go to some lengths to minimise the worst case delay. They apply techniques such as the following:

• The delays in blocks are made as close to equal as possible. This means positioning the divisions between blocks so that the numbers of levels of logic in each block are

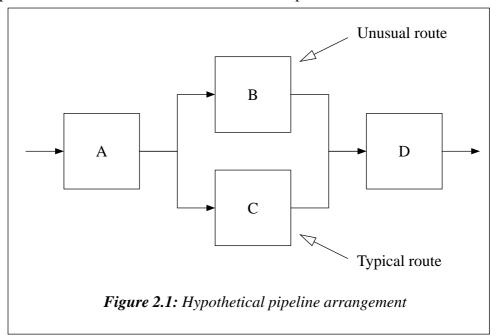

as close to equal as possible. Synchronous designers try to find the critical path in their designs and speed it up. This means that even rarely-used pieces of logic have to be analysed in detail. In asynchronous systems, the governing principle is that "the typical case must be fast, and the unusual case must be correct". For example, figure 2.1 shows a pipeline where two alternative blocks B and C can occupy the second stage. If this pipeline was for a synchronous processor, the clock would have to be as slow as the slowest of any of the four blocks. However, for an asynchronous processor, the unusual case where block B is used could be allowed to be slow, and only the typical case where block C is used needs to be optimised.

Techniques are applied to increase the speed of the logic for the worst case data input. The best example of this is for an adder unit. The simplest construction of an adder uses ripple carry, where the carry output of each adder cell is fed to the carry input of the next most significant cell. This circuit is fast for typical cases where the carry only has to propagate between a few cells, but in the rare cases where a carry ripples all the way from one end of the circuit to the other, the circuit is relatively slow. In a synchronous system, the clock speed would have to be adjusted to this worst case. To avoid this, synchronous designers devise much more complex adder circuits using techniques such as carry look-ahead, carry skip and carry select [7]. These circuits are much larger than the simple ripple-carry adder and work little if at all faster for typical operands. However they do work faster in the worst case, allowing the clock frequency to be increased. In an asynchronous system, this type of circuit is unnecessary. In [15], the asynchronous ALU used in the AMULET1 processor is described. The adder in this design has a worst-case delay that is approximately twice the typical-case delay. However, the worst-case input data occurs only about 5% of the time.

• It may seem that there is nothing that a designer can do to make his circuit work better in the worst case operating conditions. However, it is possible to redefine what the worst case operating conditions are. For a synchronous designer there is a trade-off between what he specifies as acceptable operating conditions and the maximum clock frequency that he allows. For example, the speed of a circuit decreases with increasing temperature. A designer may have a choice between specifying that his design is either "Maximum temperature 50°C, Maximum frequency 30 MHz" or "Maximum temperature 85°C, Maximum frequency 20 MHz". He has a similar choice in the case of operating voltage, and possibly also for process speed. On the other hand, the asynchronous designer can specify the widest possible margins for these parameters, on the understanding that achieved performance will be best in certain conditions.<sup>1</sup>

For many microprocessor applications, having a performance that is dependent on operating conditions is acceptable. An example is the personal computer, where users would be happy to accept improved typical performance with variation depending on operating conditions. On the other hand, there are application areas where worst case performance is the important measure. For example consider a microcontroller in an engine management system whose purpose is to collect data from various sensors and operate the spark plugs at the appropriate times. In this application, it is essential that even in the worst operating conditions the controller is able to process the input data before the time when the spark has to be generated. In applications such as this, the benefit of asynchronous logic is limited.

There may be fewer applications that fall into the same category as the engine controller than one might think. Although the specifications for most signal processing and real-time applications include maximum response times and minimum throughputs, this is just because the specification was drawn up with synchronous implementation in mind. Here are two examples:

# **Example 1: A Modem Application**

Currently modems operate at fixed data rates, e.g. 9600 bits/second. The controller inside a modem has to do a significant amount of processing to decode the output bit stream from the input analogue samples. In a synchronous design, the controller would be clocked sufficiently fast so that it could do the required processing even for the worst case input data. In an asynchronous design, at first sight it seems that the "engine controller" situation applies, and that the asynchronous controller has to keep up with the data rate even in worst case conditions. However, this is just a result of the specified fixed data rate. There is no fundamental reason why modems need to use a fixed data

<sup>1.</sup> This makes writing data sheets for asynchronous processors a challenging proposition!

rate. If the modem standard was redefined, the speed could be agreed between the sending and the receiving modems (and continuously adjusted) so that both could keep up with it.

Consider for example a modem in a battery operated portable computer. With a synchronous controller, as the battery voltage drops the controller will stop working. With an asynchronous controller, as the battery voltage drops the controller will continue to function correctly but more slowly. As it does so the communication speed will drop. Whilst the battery is fully charged (i.e. in typical conditions) the asynchronous modem will operate more quickly than the synchronous design<sup>1</sup>.

#### **Example 2: A Compact Disk Player**

Consider the data processing in a compact disk player. This is a similar problem to the modem application; the controller has to process the digital data from the disk and generate an analogue signal. The majority of the processing required is for the error detection and correction algorithms. However, unlike the modem, it is not possible for an asynchronous design to respond to reduced battery voltage or other adverse conditions by reducing the throughput, as this would slow the sound output. Instead as an alternative the controller can reduce the amount of error correction that it carries out, or it can discard some of the samples. To the user of a portable CD player, this means that as batteries run out, the synchronous design will stop functioning, whereas the asynchronous design will just lose some sound quality.

#### 2.1.2 Clock Skew and Ground Bounce

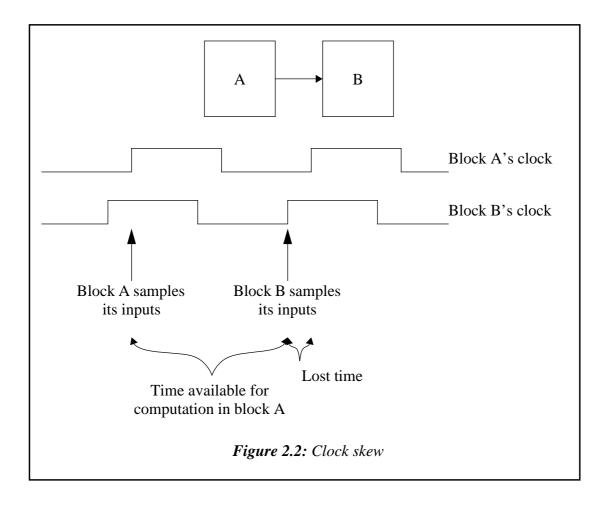

Two communicating blocks in a synchronous design may see slightly different versions of the clock signal. This is because the different blocks may place unequal loads on it and the clock distribution tracks may be longer to reach some blocks than others. This is known as clock skew. The result is that some versions of the clock will be changing before other versions. When one block communicates with another block that has a slightly earlier version of the clock, it must set up its output signals in time for that early version of the clock. This means that the actual time available for computation within a block is less than the period of the clock, as shown in figure 2.2.

<sup>1.</sup> Provided that other factors such as line bandwidth do not limit the speed.

Synchronous designers do what they can to reduce clock skew. This includes careful analysis of the load on the clock signal and careful design of the clock drivers. In the case of the DEC Alpha 21064 chip [16], the designers published a three-dimensional figure showing the simulated clock skew across the chip. This processor's clock driver uses a tree of five levels of buffers.

In asynchronous design, the absence of a global clock completely eliminates this design problem, and also removes the need for a clock driver of the type used in the Alpha implementation.

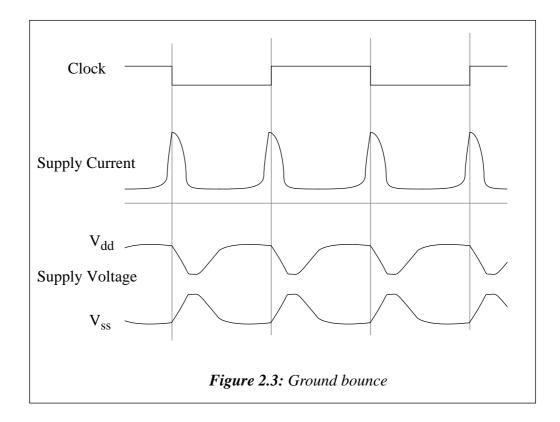

In CMOS circuits, almost all power is consumed when switching occurs. In a synchronous design, this switching occurs when the clock switches. The power consumed in a synchronous design therefore occurs mostly around the clock edges. These peaks of power consumption lead to voltage drops due to the inductance of the power supply

path. This effect is known as ground bounce, and is illustrated in figure 2.3. This variation in supply voltage can lead to malfunction if it is too extreme as signals may no longer represent valid logic levels with respect to the power supply.

Synchronous designers try to avoid the problem by reducing the inductance of the power supply and in the case of the DEC Alpha 21064 chip [16] by constructing power supply decoupling capacitors on the chip.

In asynchronous circuits, because there is no global clock signal power consumption will be randomly distributed over time, so typically the spikes shown in figure 2.3 will not occur. However there is a probability that by chance a large number of nodes will change simultaneously, and a power surge will occur<sup>1</sup>. This is particularly possible if a group of connected elements such as adjacent stages in a pipeline operate at close to the same natural frequency.

If a significant surge did occur, the resulting voltage drop may have a less severe impact on an asynchronous circuit than it would on a synchronous circuit. Provided that the

<sup>1.</sup> The probability per unit time that n nodes in a circuit of m nodes, changing at random with average frequency f, would change within time  $\delta t$  is  ${}^mC_n(f\delta t)^n$ . Because of the factorial nature of this expression, the chance of all nodes in a circuit switching simultaneously is very low (e.g. of the order of the age of the universe), but the probability of perhaps 90% of the nodes changing may be relatively high and should be allowed for. 50% of the nodes may change simultaneously very frequently.

supply voltage did not change by more than the transistor's threshold voltage, the asynchronous circuit would simply slow down briefly but it would continue to behave correctly. In a synchronous circuit this slowing down would mean that the clock may occur before the next data was ready, and the circuit would fail. In both asynchronous and synchronous cases, if the supply voltage change is too great logic levels will be miss-interpreted, causing the circuit to fail.

# 2.1.3 Ease of Design

Several points have already been mentioned that make asynchronous design easier:

- The speed of infrequently used blocks does not affect overall speed, so in these cases costly sophisticated design techniques may be avoided.

- Simpler designs may be used for blocks with data-dependent delays (e.g. the ripple-carry adder).

- Problems with clock distribution, skew and ground bounce may not exist, so the designer does not need to spend time resolving them.

The other important reason is that asynchronous design can be more modular than synchronous design.

An asynchronous designer can take a "plug-and-play" approach. Provided each block in an asynchronous design is internally correct and meets the simple timing constraints of its external interface (see section 2.2), the design will be correct in terms of timing. The designer can therefore simply replace one block by another with different characteristics, and evaluate any change in performance. The synchronous designer does not have this flexibility.

Another way of looking at this is by analogy with high-level languages. The global clock in a synchronous design is like a global variable in a program. The self-contained local timing of an asynchronous design is more like the limited scope local variable of a program. Local variables are considered "better" than global variables in high-level language programs because they help to hide information in each function from the others.

The benefit of this modularity may be most significant at the level of systems made up of large components. For smaller designs, keeping track of the timing in a synchronous system is not too difficult and the asynchronous advantage may not be significant to the designer.

Another reason why asynchronous logic leads to easier design is the potential for synthesis from high-level descriptions. Various research groups have shown that it is possi-

ble to translate from a high-level description of a system written in a CSP-like language to an asynchronous circuit. The Tangram language [29] for example is translated into so-called handshake circuits, which are four-phase asynchronous circuits. It has also been suggested that the same properties that support automatic synthesis can be used to allow the automatic verification of designs.

# 2.2 Micropipelines and Other Styles of Asynchronous Logic

This section introduces some asynchronous design techniques. Firstly the design style used in the AMULET1 asynchronous processor is explained, and then various alternatives are considered.

In reality all timing styles are instances in a multi-dimensional space; synchronous design and the style used in AMULET1 are simply points in this space. There are very many other possibilities.

The technique used in the AMULET1 processor is known as *micropipelines* [17]. It uses two fundamental ideas:

- Two-phase event signals.

- · Bundled data.

# **Two-Phase Event Signalling**

Signals in a micropipeline design can be divided into two categories: data signals and event signals. Event signals control timing, and do so by signalling events. Events are occurrences at points in time; events have no "duration".

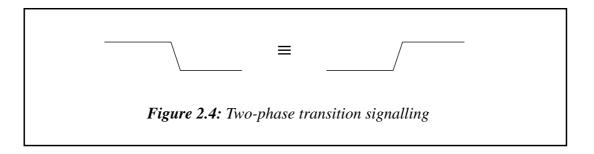

In the micropipeline design style, events are represented by two-phase transition signalling. Transition signalling means that the events are represented by a transition on the wire. In two-phase transition signalling, both low-to-high and high-to-low transitions are meaningful and equivalent (figure 2.4).

Contrast the concept of an event signal with a level-sensitive signal. A level-sensitive signal communicates the state of the driver to the receiver at all times. On the other hand, an event signal does not communicate any information except when the driver has changed state. If the receiver of an event signal is "not looking" when the event arrives, it cannot tell that it has missed the event, as levels have no absolute meaning. On the other hand, the receiver of a level-sensitive signal can tell the state of the transmitter at all times.

Various logic gates are used to build circuits that process event signals [17]. Some of these are shown in figure 2.5.

#### **Bundled Data**

Data in a micropipeline is represented using a normal binary encoding in the same way that would be used by a synchronous design (this contrasts with the alternative of dual rail encoding, discussed later). This data is 'bundled' along with event signals that indicate its validity. Normally there is one event signal in each direction. The signal from the sender to the receiver is called request and the signal from the receiver to the sender is

called acknowledge. Contrast the approaches used by the bundled data method and the synchronous method in figures 2.6 and 2.7.

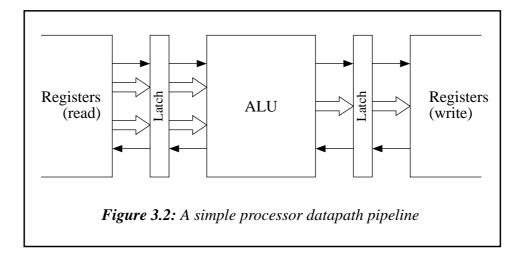

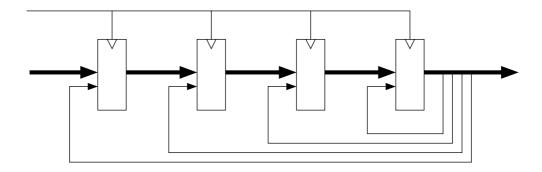

A micropipelined circuit typically consists of a number of stages each of which communicates with its two neighbours using a request-acknowledge protocol. If the problem to be solved can be represented by a sequence of units with unidirectional communication, then a micropipelined implementation is simple.

When the problem requires less structured communication, the implementation may become more difficult. In a clocked system, the progress of data between all blocks is in lockstep. In an asynchronous system, this lockstep does not occur and blocks do not know the progress of data through other blocks, so when a rendezvous is required extra control is needed. As a general rule it is therefore a good idea to avoid structures that require non-local communication.

There are various alternative asynchronous schemes apart from two-phase event signals and bundled data. These include:

- Four-phase event signalling.

- Dual-rail encoding.

These two techniques are now considered.

# **Four-Phase Signalling**

Four-phase event signalling is an alternative to two-phase signalling. Unlike two-phase signalling, the meaning of rising and falling transitions are not the same. An exchange of data using a request-acknowledge signal pair involves not two transitions but four. An example of this is shown in figure 2.8<sup>1</sup>. The reason for this apparent additional complexity in the protocol is that the control circuitry needed can be less complex and/or faster for the four-phase protocol. The elements shown in figure 2.5 have to respond to both

<sup>1.</sup> Other arrangements where the data is transferred on other edges of the request and acknowledge signals are possible.

rising and falling transitions on their inputs. Corresponding elements for four-phase signalling only need to respond to one edge, and so may be simpler.

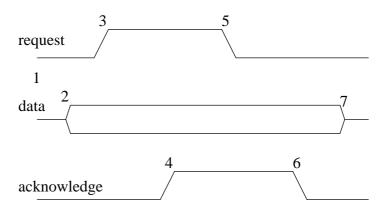

- 1. Computation in sending block is complete and data is ready.

- 2. Data is driven onto the data signals.

- 3. Sending block raises request.

- 4. Receiving block raises acknowledge.

- 5. Sending block lowers request

- 6. When receiving block has used the data, it lowers acknowledge.

- 7. Sending block can remove the data.

Figure 2.8: Four-phase transition signalling inter-block communication

### **Dual Rail Encoding**

Dual rail encoding is an alternative representation for data signals. A dual-rail encoded signal uses two wires to represent each bit of the binary value. One of the wires is used to communicate a one and the other is used to communicate a zero.

When dual-rail encoded data is used, there is no need for an external timing signal such as the clock in a synchronous system or the request signal in a bundled data system. The timing data is contained within the data itself. Furthermore, in a multi-bit signal, the different bits can become valid at different times.

There are two-phase and four-phase versions of dual-rail encoding. In the four-phase version, the two wires can be decoded to give four possible meanings, as shown in table 2.1.

| Zero | One | Meaning                   |

|------|-----|---------------------------|

| 0    | 0   | Value is not yet computed |

| 0    | 1   | Value is One              |

| 1    | 0   | Value is Zero             |

| 1    | 1   | Illegal                   |

Table 2.1: Four-phase dual-rail encoded data representation

Some sort of acknowledge mechanism is needed to allow the wires to return to the 0,0 state; this can be on a per-bit or per-signal basis.

In the two-phase version, a transition on the zero wire indicates that the value has become zero and a transition on the one wire indicates that the value has become one. An acknowledge signal is necessary to indicate to the sending block when it is free to send another value on the same wire.

There are two particular applications where dual-rail encoding has an advantage over bundled data:

- Certain control circuits, where the bundled data representation would be internally converted to dual-rail anyway.

- Datapath operations where it is advantageous to start processing before all bits have arrived.

These two cases are now considered.

#### **Dual Rail Control Circuits**

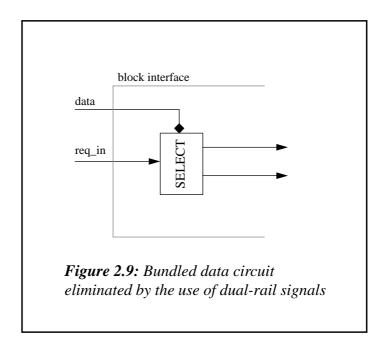

Consider the two-phase bundled data circuit shown in figure 2.9<sup>1</sup>. Here, a one-bit bundled data signal is used to produce an event on one of two output signals

<sup>1.</sup> The rectangular circuit element in figure 2.9 is a select block [17]. It steers an event on its left-hand input to one of the right-hand outputs, depending on the state of the boolean input at the top.

In this circuit, if the input was instead represented using dual rail encoding, this circuit could be entirely removed and the two dual rail wires could be connected in place of the outputs from the select block, reducing silicon area, power and delay. An example of this occurs in the AMULET1 processor where the ABORT signal enters the chip as a dual-rail encoded signal.

#### **Dual Rail Datapath Functions**

In many cases, datapath functions must wait for all the input bits to be available before acting. For example, a register write operation will always write all bits at the same time because the input data has to be synchronised with the register address. If dual rail encoded data was used in this case, a circuit would be needed to detect that all bits had arrived; that is, a dual-rail to bundled-data converter.

However there is one particular case where dual-rail encoded data demonstrates an advantage. This draws on ideas from the ALU of the superscalar SuperSparc processor [38] (which is synchronous).

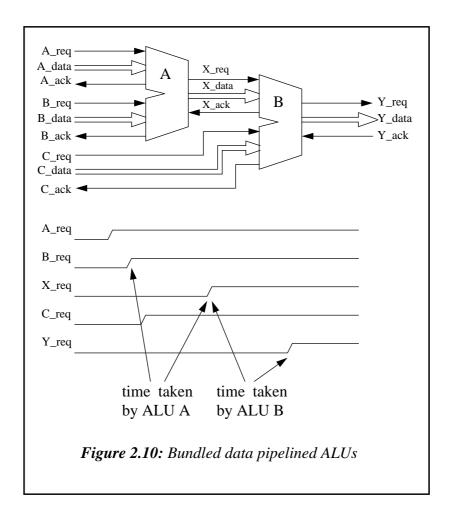

Consider a circuit that adds three operands A, B and C together in two stages. Figure 2.10 shows the timing of the bundled-data implementation of this circuit.

In the bundled-data implementation, the request output of the first ALU is connected to a request input of the second ALU, so the total time taken by the circuit is the sum of the total time taken by each of the two sub-circuits.

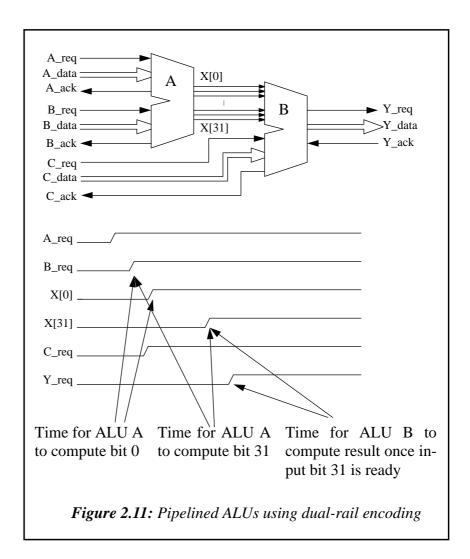

Using a dual-rail encoding for the intermediate signals between the two sub-circuits, a particular property of the adder circuit can be exploited; this is that the least significant bits are evaluated before the most significant bits. This is because of the nature of the carry signals that join the individual bit-wide adders<sup>1</sup>. Furthermore, the most significant input bits are not required until the carry signals have propagated to them. Figure 2.11 shows how this can be used. The time saving of this circuit over the one using bundled data for the intermediate value is equal to the time between the least significant bit of the output of the ALU becoming valid and the most significant bit becoming valid.

The number of cases where this technique can be applied may be fairly limited, but where it can be used it may lead to significant performance improvements.

<sup>1.</sup> This is particularly true in the case of a simple ripple-carry adder, but does also apply to other more sophisticated adders. See the description of adders for asynchronous designs on page 27.

# 2.3 Asynchronous Logic and Power Efficiency

As has been previously stated, in CMOS energy is principally used when nodes switch from one voltage level to another. Power consumption is therefore proportional to the rate of node switching. In fact the equation governing power consumption is:

$$P = \frac{1}{2}CV^2 f n$$

Where P is the power consumption, C is the average capacitance per node, V is the supply voltage, f is the switching rate in transitions per second and n is the number of nodes.

The use of asynchronous logic leads to lower power consumption because asynchronous circuits can switch fewer nodes per second with less capacitance than equivalent synchronous ones doing the same task.

The most important factor leading to this reduced power consumption is the fact that asynchronous systems can potentially have fewer "wasted" transitions than a synchronous system. This point is considered shortly. Firstly, consider the power used in the synchronous and asynchronous systems for each transaction.

#### **Transitions Per Cycle**

Consider the power used in the inter-block communication schemes outlined in figures 2.6, 2.7 and 2.8. Table 2.2 summarises the number of transitions that occur per cycle in each of the systems.

| System                  | Transitions in control signals | Transitions in data signals |

|-------------------------|--------------------------------|-----------------------------|

| Synchronous             | clock: 2                       | $\frac{n}{2}$               |

| Two-phase bundled data  | request: 1<br>acknowledge: 1   | $\frac{n}{2}$               |

| Four-phase bundled data | request: 2<br>acknowledge: 2   | $\frac{n}{2}$ a             |

| Two-phase dual-rail     | -                              | n                           |

| Four-phase dual-rail    | -                              | 2n                          |

**Table 2.2:** Comparison of design styles by number of transitions per cycle

From table 2.2, the following observations can be drawn:

- When the number of data bits n is very small, dual-rail encoding is advantageous.

- Two-phase transition signalling is more power-efficient than four-phase.

- In terms of number of transitions per cycle, no asynchronous design style does better than clocked design.

Despite the final point above, there are reasons to believe that two-phase bundled data designs can consume less power than synchronous designs:

• In a synchronous pipeline, two non-overlapping versions of the clock signal may be distributed<sup>1</sup>, doubling the effective number of transitions.

a. This assumes that on average half of the data signals change per cycle. For some situations fewer signals will change; for example if the data is the output of a counter on average 2 bits change. When a precharged logic system is used, the average value will be doubled.

<sup>1.</sup> Some recent published designs do make use of a true single-phase clock. [16] [18]

- Synchronous designs may even distribute the true and inverse of the clock signal or signals [6], doubling again the effective number of transitions per cycle<sup>1</sup>.

- Asynchronous designs can have smaller loads on control signals

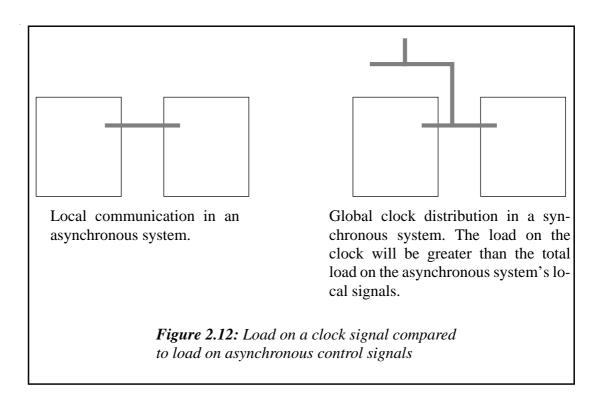

The basis for the final assertion above is that asynchronous control signals have a more local distribution than the global clock in a synchronous design. Although there are more control signals in an asynchronous design, their total capacitive load should be less than the total capacitive load on a clock signal, because they do not have the overhead of distribution from a central clock generation circuit

The clock generation circuit typically makes use of a tree of drivers to produce the final clock signal. Power is also dissipated within this tree.

## **Asynchronous Designs Have Fewer Wasted Transitions**

The most important argument for the reduced power consumption of asynchronous logic is that an asynchronous system can respond better to fluctuating levels of processing demand.

<sup>1.</sup> It should however be noted that some micropipelined units also distribute or generate locally the true and complement of the timing signals.

In all practical designs, there will be sections of the circuit that are not active at certain times. In asynchronous implementations, these circuits will see no events on their request inputs and will consume no power.

In synchronous systems, there are two approaches to this situation:

- The clock to the unused circuit can be disabled. When this is done, no power is consumed. However there are disadvantages resulting from the need to insert a gate between the global clock and the local gated clock to the block in use. This gate will introduce a delay, causing clock skew (see section 2.1.2). Adding the gate also adds to the design size and increases complexity as logic is required to control the input to the gate.

- The clock to the unused circuit can remain enabled, but a control input is used to indicate that no action should occur. In this case, the same power may be consumed as when the circuit is enabled.

In practice, the use of gated clocks is considered as something of a "black art" by many synchronous designers; for example, it is not mentioned in two of the standard textbooks [6] [19]. The natural power saving of asynchronous design is an improvement over the synchronous approach in this area.

The power saving resulting from the use of asynchronous logic can occur on any scale; from a gate-by-gate level when particular bits in a signal are not being used, to a block-by-block level when for example some of a processor's functional units are not busy, to the highest level when the processor stops and waits for an interrupt before continuing. In an asynchronous system this power-down occurs quite automatically and instantaneously, in contrast to the power-down modes of processors used in portable computers which require software intervention to enter and are generally less flexible.

# 2.4 The Disadvantages of Asynchronous Logic

There are certainly some areas in which the synchronous design style has advantages over the asynchronous. At the low level, limited experience suggests that asynchronous circuits may be larger and slower than synchronous ones. A a higher level, the non-deterministic nature of asynchronous design introduces problems such as deadlocking which are not present in synchronous design. A solution to the problem of the test of asynchronous circuits has yet to be demonstrated.

#### **Size and Speed of Control Circuits**

Experience with the AMULET1 processor suggests that the use of the micropipelined design style leads to an increase in the area taken up by the control logic compared with a synchronous implementation [23]. Possible reasons for this include:

- The asynchronous design process is less mature than the synchronous process. Synchronous designers have the advantage of design tools, standard cells and experience that has not yet evolved for asynchronous implementations.

- The two-phase event signals used need extra logic to react to both rising and falling edges, whereas a synchronous system needs to operate on one edge only. The use of four-phase event signalling can help this, but it may lead to an increase in power consumption.

The AMULET1 control circuits also have lower speed compared to clocked circuits. This can be attributed to the increase in area and complexity, and also to a more fundamental aspect of the design style; asynchronous control circuits tend to be more sequential than synchronous circuits which can be more parallel. Circuit diagrams for event logic circuits have the appearance of flow charts, where wires communicate events representing the flow-of-control within the circuit. At any time only one element is active. Introducing parallelism into an asynchronous control circuit may involve arbitration, which is also slow.

The crucial design objective must be to reduce the delay through the control circuit to no more than the delay through the datapath. Datapath design for micropipelines is very similar to datapath design for synchronous logic as both use a straightforward binary representation of the data. In the AMULET1 processor the datapath was implemented using custom cells and hand layout and the control logic used standard cells and automatic layout, yet the speed of operation is limited in most cases by the delays through the control logic.

There are two ways in which the control delay and the datapath delay can be equalised: the delay through each stage of the control logic can be reduced, or the delay through each stage of the datapath can be increased.

Possible ways in which the control logic speed can be increased include:

- The use of four-phase event signalling.

- The use of more sophisticated synthesis procedures.

- The replacement of sequential actions by parallel actions.

• The reduction of the required complexity, by implementing a different architecture.

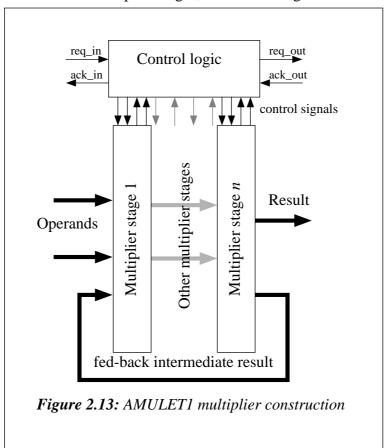

The idea of increasing the delay through the datapath logic is only sensible if it results in an increase in the functionality per stage. An example of an area where this technique has been applied is in the AMULET1's multiplier.

The AMULET1 multiplier is an asynchronous iterative multiplier. It consists of a control circuit and a number of multiplier stages, as shown in figure 2.13.

The total number of stages that the data needs to pass through is fixed by the width of the multiplication. However there is a trade-off between implementing a small number of stages and feeding back the intermediate results a large number of times to produce the final result, and implementing more stages and feeding back the data fewer times. The trade-off was chosen by implementing enough stages to match the delay through the stages implemented and the control logic. The number chosen was 3.

Adding more stages would be a waste of silicon, as it would perform no faster than the 3 stage solution. Having fewer stages would reduce the silicon area, but the critical path would then be through the control logic.

It should be possible to implement the idea used here in other areas. Two applications are immediately apparent:

- The number of pipeline stages in the datapath can be reduced, but to maintain throughput extra parallel datapaths can be added (i.e. multiple functional units).

- The rate of data transfer in, for example, the instruction fetch mechanism can be reduced, but the width of the buses can be increased to yield the same throughput.

Interestingly, the argument that speed should be reduced and parallelism should be increased was proposed in section 1.2 to allow a reduction of operating voltage and hence an increase in power efficiency. The limit on the success of this approach is determined by the amount of parallelism that can be exploited successfully.

#### **Deadlocks**

As with systems of communicating processes, micropipelined units can enter a state of deadlock where all units are waiting for some other unit to act before continuing. In the design of the AMULET1 processor, several interesting and not immediately obvious potential deadlocks were discovered. It is hoped that some mathematical formal techniques may be possible to detect or avoid the possibility of deadlock at a high level in the design process, but at present no such technique is known.

#### **Test**