# SCALP: A Superscalar Asynchronous Low-Power Processor

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science and Engineering

## **Philip Brian Endecott**

Department of Computer Science

1996

## Contents

|                                                                 | Contents                                                                                                                                                                               | 6<br>8<br>. 10<br>. 12<br>. 12<br>. 13               |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Chapter 1:<br>1.1<br>1.2<br>1.2.1                               | SCALP: A Superscalar Asynchronous Low-Power Processor<br>The Importance of Power Efficiency<br>Low Power Design Techniques<br>Low-Level Power Efficiency                               | . 15<br>. 16                                         |

|                                                                 | Process Technology.<br>Transistor Level Design<br>Charge Recovery and Adiabatic Systems<br>Logic Optimisation<br>Supply Voltage Adjustment<br>Parallelism.                             | . 16<br>. 17<br>. 17<br>. 18<br>. 18<br>. 19         |

| 1.2.2                                                           | Precomputation<br>Clocking Schemes and Asynchronous Logic<br>Higher-Level Power Efficiency: Microprocessors<br>External Memory Bandwidth<br>Cache Characteristics                      | . 19<br>. 20<br>. 20<br>. 20                         |

| 1.3<br>1.4                                                      | Datapath Arrangement          Previous Low Power Processors.          Overview of the Thesis.                                                                                          | . 21                                                 |

| Chapter 2:<br>2.1<br>2.1.1<br>2.1.2<br>2.1.3                    | Reducing TransitionsCode DensityVariable Length InstructionsRegister SpecifiersPrevious High Code Density ProcessorsD16ThumbTransputer                                                 | . 24<br>. 27<br>. 29<br>. 31<br>. 31<br>. 32<br>. 32 |

| 2.2                                                             | Datapath Activity                                                                                                                                                                      |                                                      |

| Chapter 3:<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.5.1<br>3.5.2 | ParallelismParallelism and PowerPower, Parallelism and CostParallelism in Special Purpose ProcessorsParallelism in General Purpose ProcessorsPipeliningBranch InstructionsDependencies | . 35<br>. 37<br>. 38<br>. 39<br>. 40<br>. 43         |

| 3.5.3                                                           | Different Pipeline Arrangements                                                                                                                                                        | . 48                                                 |

|            | Shorter Pipelines                                         |     |

|------------|-----------------------------------------------------------|-----|

|            | Longer Pipelines                                          |     |

| 3.6        | Superscalar Parallelism                                   |     |

| 3.6.1      | Dependencies                                              |     |

| 3.6.2      | Branch Instructions                                       | 54  |

| 3.6.3      | Observations                                              | 54  |

| 3.6.4      | Simpler forms of Multiple Functional Unit Parallelism     | 56  |

| 3.7        | Speculative Execution                                     | 57  |

| Chapter 4: | Asynchronous Logic                                        | 59  |

| 4.1        | Asynchronous Logic and Power Efficiency                   |     |

| 4.1.1      | Asynchronous Circuits can be Faster                       |     |

| 4.1.2      | Asynchronous Circuits can be Smaller                      |     |

| 4.1.3      | Asynchronous Logic in Variable Demand Systems             |     |

| 4.1.4      | Asynchronous Logic and Dynamic Supply Voltage Adjustment. |     |

| 4.1.5      | Asynchronous Logic Doesn't Waste Transitions              |     |

| 4.1.6      | Other benefits of Asynchronous Logic                      |     |

| 4.1.7      | Tangram and the Philips DCC Error Corrector               |     |

| 4.1.8      | Conclusion                                                |     |

| 4.2        | Asynchronous Pipelines                                    |     |

| 4.2.1      | Forwarding in Asynchronous Pipelines                      |     |

| 4.2.2      | Conditional Forwarding                                    |     |

| 4.2.3      | Explicit Forwarding                                       |     |

| 4.3        | Asynchronous Superscalar Parallelism.                     |     |

| 4.3.1      | Simple Superscalar Structures                             |     |

| 4.3.2      | Superscalar Forwarding                                    |     |

| 4.4        | Previous Asynchronous Processors                          |     |

| 4.4        | The Caltech Asynchronous Processor.                       |     |

|            | AMULET1 and AMULET2                                       |     |

|            | NSR                                                       |     |

|            |                                                           |     |

|            | Fred                                                      |     |

|            |                                                           | 00  |

|            | fluces                                                    |     |

|            | ECSTAC                                                    |     |

|            | TITAC                                                     |     |

|            | ST_RISC                                                   |     |

|            | FAM                                                       |     |

| 4 4 1      | STRiP                                                     |     |

| 4.4.1      | Observations                                              | 85  |

| Chapter 5: | The SCALP Architecture                                    |     |

| 5.1        | Explicit Forwarding and Non-Global Registers              |     |

| 5.2        | Deadlocks and Determinism                                 |     |

| 5.3        | Other SCALP Features                                      |     |

| 5.4        | A SCALP Instruction Set                                   | 100 |

| 5.5        | The SCALP Programming Model                               | 104 |

| 5.6        | Interrupts and Exceptions                                 |     |

| 5.7        | Related Work                                              | 117 |

| 5.7.1      | Stack Processors                                          | 117 |

| 5.7.2      | Architectural Queues                                      | 117 |

| 5.7.3        | Explicit Forwarding                          | . 118 |

|--------------|----------------------------------------------|-------|

| Chapter 6:   | Implementation                               | . 120 |

| 6.1          | Asynchronous Design Styles                   | . 120 |

| 6.1.1        | Timing Models for Control Circuits           |       |

| 6.1.2        | Timing Models for Datapaths                  | . 122 |

| 6.1.3        | Asynchronous Signalling Protocols            |       |

| 6.2          | Implementation Methodology                   |       |

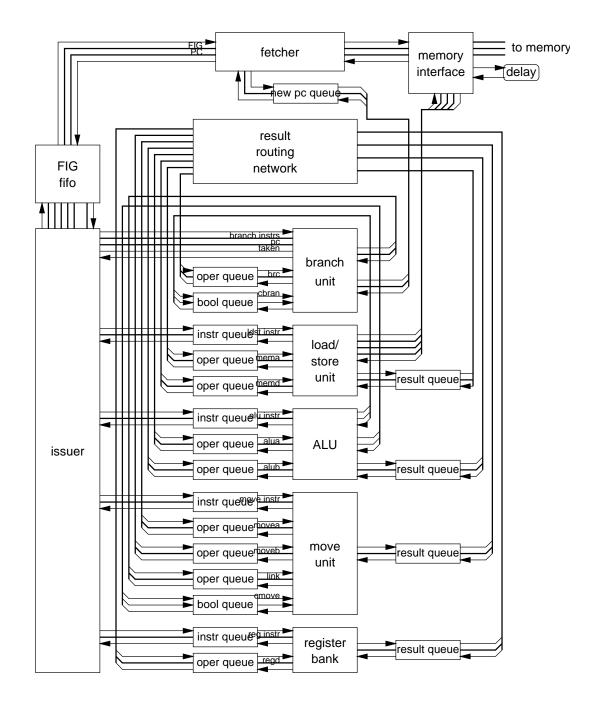

| 6.3          | Overview of the Design                       |       |

|              | Memory Interface                             |       |

|              | Fetcher.                                     |       |

|              | FIG Fifo                                     |       |

|              | Issuer                                       |       |

|              | Instruction Queues.                          |       |

|              | Operand Queues                               |       |

|              | Branch Unit                                  |       |

|              | ALU.                                         |       |

|              | Load/Store Unit                              |       |

|              | Move Unit                                    |       |

|              | Register Bank                                |       |

|              | 0                                            |       |

|              | Result Queues                                |       |

| 6.4          | Result Routing Network                       |       |

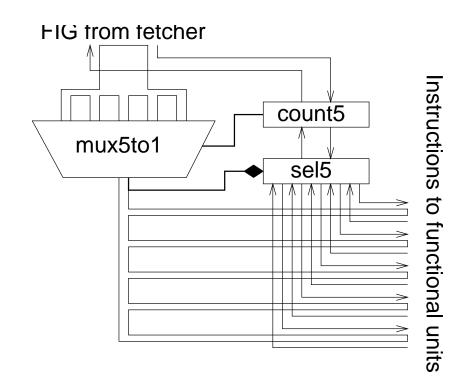

| 6.4<br>6.4.1 | Implementation of the Instruction Issuer     |       |

|              | The Need for Parallelism                     |       |

| 6.4.2        | The Proposed Solution                        |       |

| 6.4.3        | The Implementation                           |       |

|              | Token Block                                  |       |

|              | Decode Block                                 |       |

|              | Sequence Block                               |       |

| 6.4.4        | Adding Branch Instructions                   |       |

| 6.4.5        | Adding Variable Length Instructions          |       |

| 6.4.6        | Performance of the Instruction Issuer        |       |

|              | Architectural Performance                    |       |

|              | Implementation Performance                   |       |

| 6.5          | Implementation of the Result Routing Network |       |

|              | Arbitration                                  |       |

|              | Other Organisations.                         |       |

| 6.6          | Functional Units                             |       |

| 6.7          | Size of the Implementation                   | . 158 |

| Chapter 7:   | Evaluation                                   | 162   |

| 7.1          | Evaluation Procedure                         |       |

| 7.1.1        | Test Stimuli.                                |       |

| /.1.1        |                                              |       |

|              | Instruction Sequences                        |       |

| 710          | Example Programs                             |       |

| 7.1.2        | Evaluation Programs.                         |       |

|              | Pipeline Visualisation                       |       |

|              | Resource Utilisation                         |       |

| - 1          | Instruction Rate                             |       |

| 7.1.3        | Use of the Geometric Mean                    | . 16/ |

| 7.2         | Code Density                                     | 169 |

|-------------|--------------------------------------------------|-----|

| 7.3         | Pipeline Performance                             | 171 |

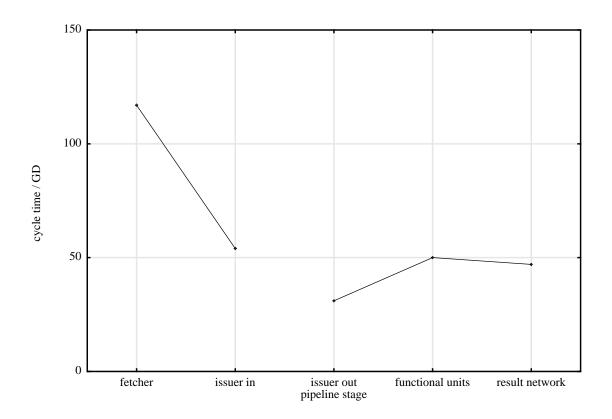

| 7.3.1       | Performance of Isolated Stages                   | 171 |

|             | FIG Fetch.                                       | 171 |

|             | Instruction Issue                                | 172 |

|             | Functional Units                                 | 173 |

|             | Result Network                                   | 174 |

| 7.3.2       | Overall Performance                              | 175 |

|             | Starvation and Blocking                          | 177 |

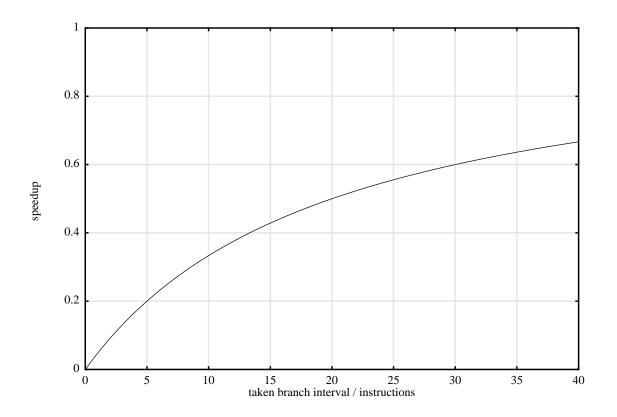

|             | Pipeline Performance with Branches               | 179 |

| 7.3.3       | Measured Performance                             |     |

|             | Instruction Sequences                            |     |

|             | Example Programs                                 |     |

| 7.3.4       | Conclusion                                       |     |

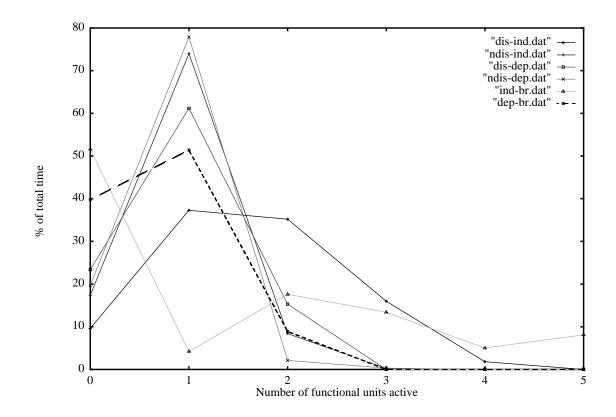

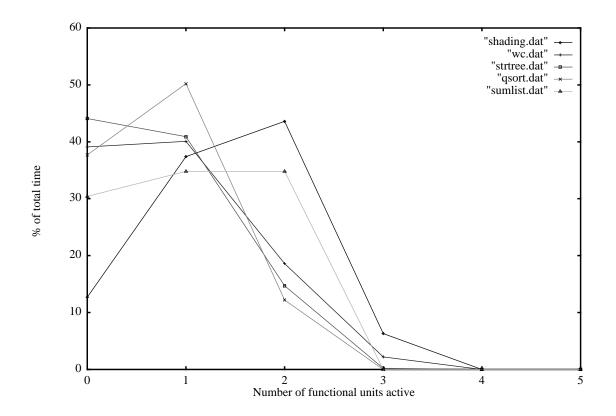

| 7.4         | Functional Unit Parallelism                      |     |

| 7.5         | Comparative Performance                          |     |

| 7.6         | Evaluating the performance of Asynchronous Logic |     |

| 7.7         | Power                                            |     |

| 7.7.1       | High code density                                |     |

| 7.7.2       | Parallelism                                      |     |

| 7.7.3       | Asynchronous Implementation                      |     |

| 7.7.4       | Variable width datapath operations               |     |

| 7.7.5       | Summary                                          |     |

| 7.8         | Evaluating the SCALP Programming Model           | 193 |

| Chapter 8:  | Conclusions.                                     |     |

| 8.1         | Summary                                          | 196 |

|             | Motivation                                       | 196 |

|             | Architecture                                     | 198 |

|             | Implementation                                   | 198 |

| 8.2         | Improving the SCALP Architecture                 | 199 |

| 8.3         | Improving the SCALP Implementation               |     |

| 8.3.1       | Branch Prediction                                |     |

| 8.3.2       | Faster Asynchronous Logic                        |     |

| 8.3.3       | Variable Length Instructions                     |     |

| 8.3.4       | Functional Unit Pipelining                       |     |

| 8.4         | The Future of SCALP                              |     |

| 8.5         | SCALP and Conventional Architectures             |     |

| 8.6         | Conclusions                                      | 207 |

| Appendix A: | Benchmarks                                       | 208 |

|             | References                                       |     |

## List of Figures

| 2.1        | Decoding Fixed Length Instructions                         | . 28 |

|------------|------------------------------------------------------------|------|

| 2.2        | Decoding Variable Length Instructions                      | . 28 |

| 2.3        | More Efficient Variable Length Instruction Decoding        | . 28 |

| 2.4        | Variable Length Instruction Decoding with a Control Field  | . 29 |

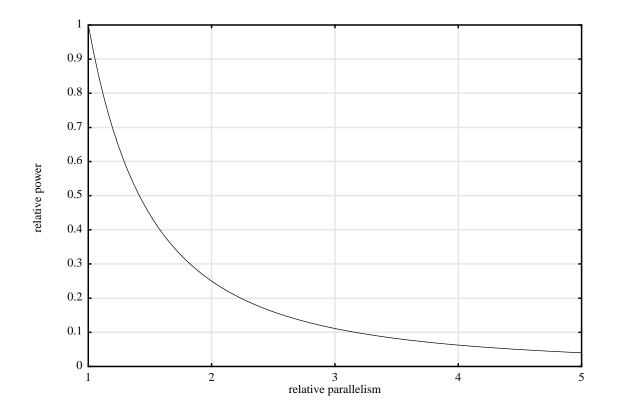

| 3.1        | The Relationship between Parallelism and Power Efficiency  | . 37 |

| 3.2        | A 6-Stage Pipeline                                         | . 42 |

| 3.3        | Timing of a 6-Stage Pipeline                               | . 42 |

| 3.4        | Branches in a 6-Stage Pipeline                             | . 43 |

| 3.5        | Timing of Branches in a 6-Stage Pipeline                   | . 43 |

| 3.6        | A Pipeline with a dedicated branch adder                   |      |

| 3.7        | Timing of Branches with a dedicated branch adder           |      |

| 3.8        | A 6-stage Pipeline with Forwarding                         | . 46 |

| 3.9        | Control for Forwarding                                     |      |

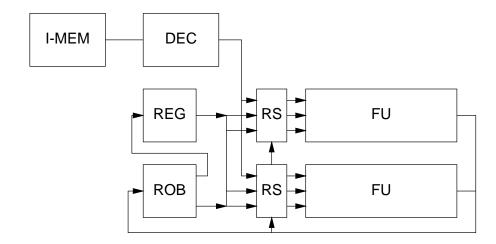

| 3.10       | Symmetric 2-way superscalar processor                      |      |

| 3.11       | Forwarding in a Superscalar Processor.                     |      |

| 3.12       | Superscalar Processor with Out of Order Issue and Register |      |

|            | Renaming                                                   | . 54 |

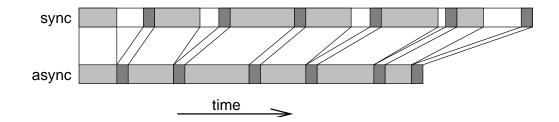

| 4.1        | Speed of Synchronous and Asynchronous Circuits             |      |

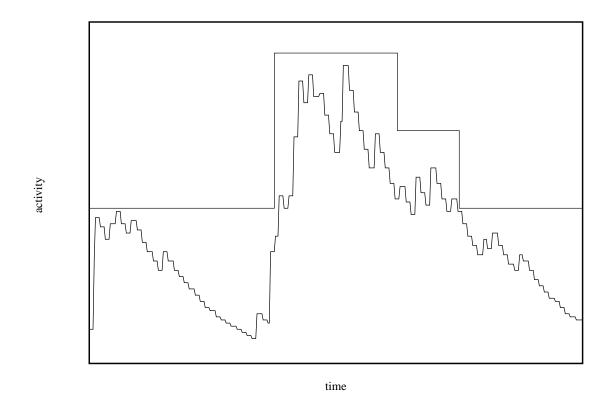

| 4.2        | Power Saving in Variable Demand Systems                    |      |

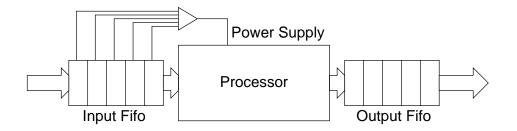

| 4.3        | Dynamic Supply Voltage Adjustment controlled by Fifo       |      |

|            | Occupancy                                                  | . 64 |

| 4.4        | Dynamic Supply Voltage Adjustment controlled by a HALT     |      |

|            | instruction                                                | . 64 |

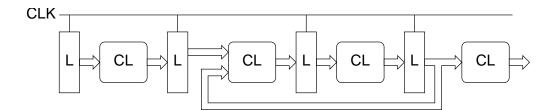

| 4.5        | A Simple Synchronous Pipeline                              |      |

| 4.6        | A Simple Asynchronous Pipeline with Matched Delays         |      |

| 4.7        | A Simple Asynchronous Pipeline with Completion Detection . |      |

| 4.8        | A Synchronous Pipeline with Forwarding                     |      |

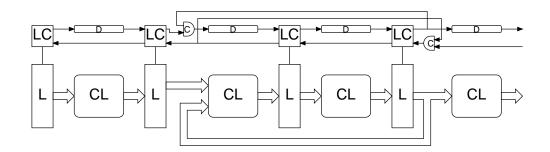

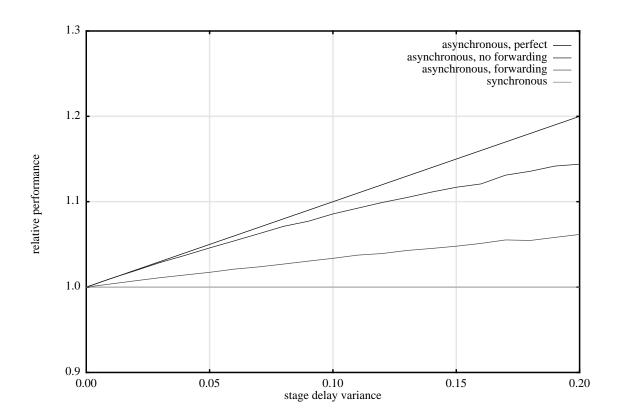

| 4.9        | An Asynchronous Pipeline with Forwarding                   |      |

| 4.10       | Performance of Synchronous and Asynchronous Pipelines with |      |

|            | and without Forwarding                                     |      |

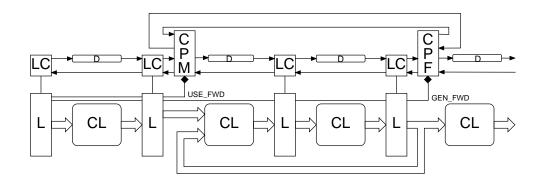

| 4.11       | An Asynchronous Pipeline with Conditional Forwarding       |      |

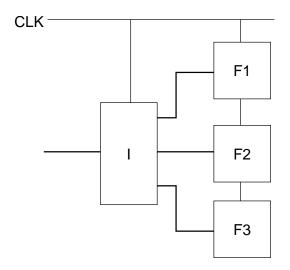

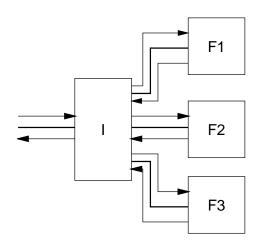

| 4.12       | Synchronous Parallel Functional Units                      |      |

| 4.13       | Asynchronous Parallel Functional Units                     |      |

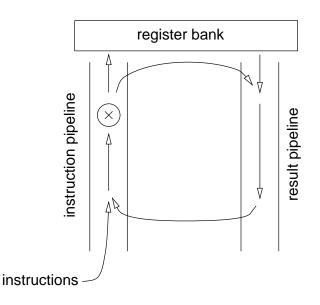

| 4.14       | Counterflow Pipeline Processor                             |      |

| 5.1        | SCALP Processor Organisation                               |      |

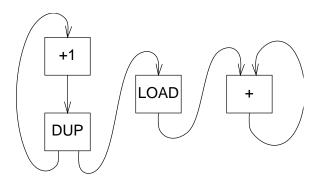

| 5.2        | Scalp Program Dataflow Representation                      |      |

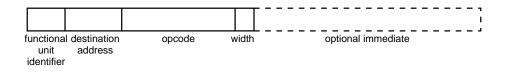

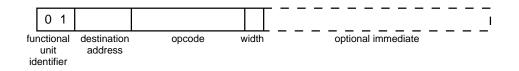

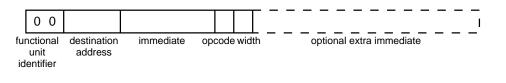

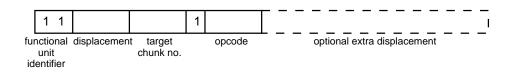

| 5.3        | SCALP Instruction Format                                   |      |

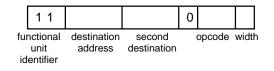

| 5.4        | Move unit instruction format                               |      |

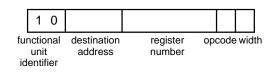

| 5.5        | Register bank instruction formats                          |      |

| 5.6        | ALU instruction format                                     |      |

| 5.7        | Load/Store instruction format                              |      |

| 5.8        | Branch instruction format.                                 |      |

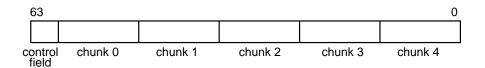

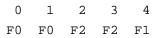

| 5.8<br>5.9 | Five Instruction Group (FIG) format                        |      |

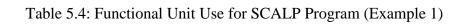

| 5.10       | The division of responsibilities between hardware and the  | 102  |

| 5.10       | compiler (from [HOOG94])                                   | 110  |

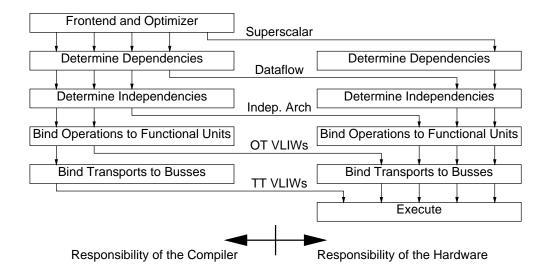

| 6.1        | Four Phase Asynchronous Signalling.                        |      |

| 0.1        | rour r hase Asynchionous Signannig                         | 124  |

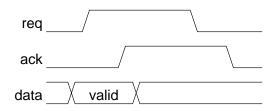

| 6.2  | Two Phase Asynchronous Signalling                           | 125 |

|------|-------------------------------------------------------------|-----|

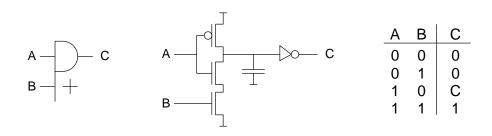

| 6.3  | An Example Muller C Gate                                    |     |

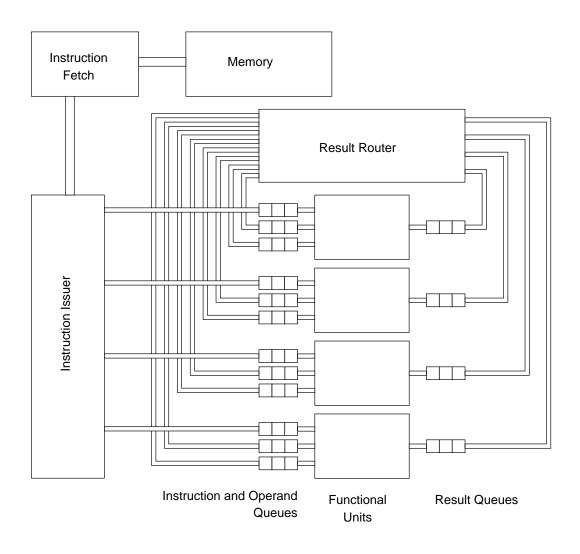

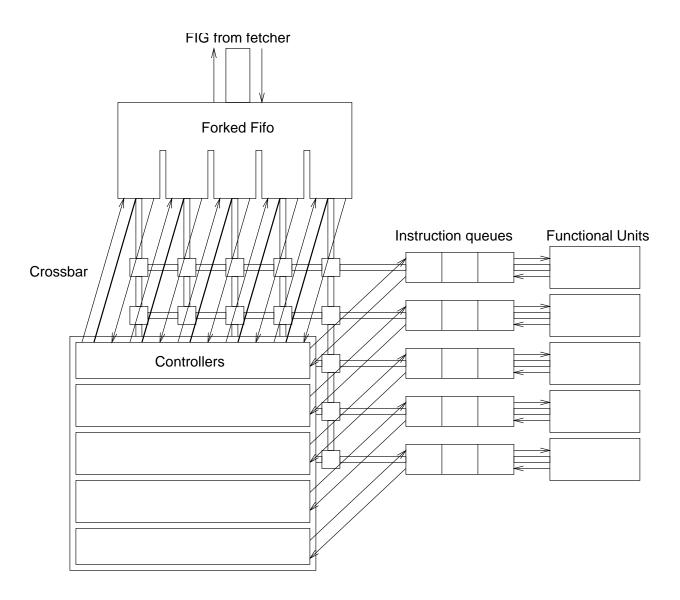

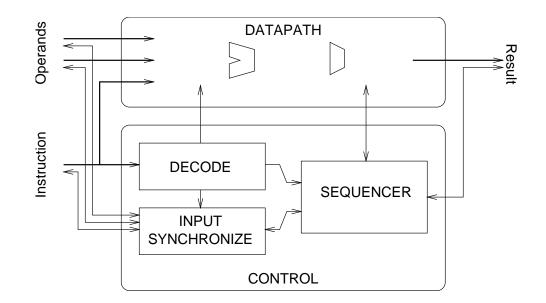

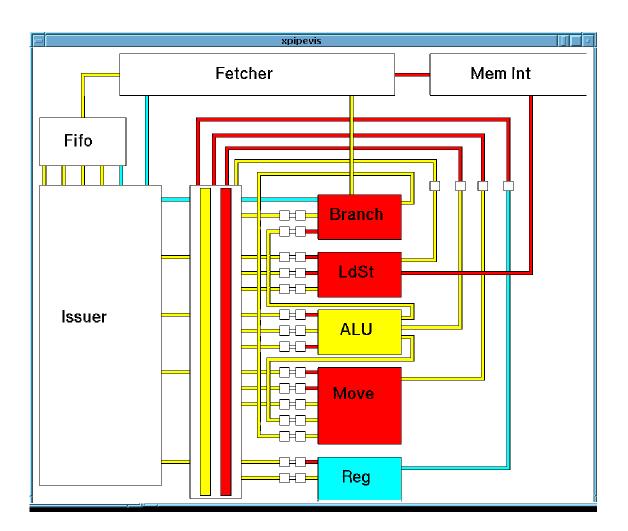

| 6.4  | SCALP Implementation Overview                               | 130 |

| 6.5  | An Unsatisfactory Issuer Architecture                       |     |

| 6.6  | Instruction Issuer Architecture                             |     |

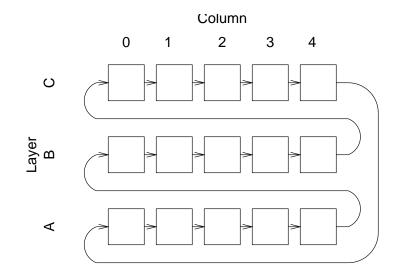

| 6.7  | Issuer Token Path                                           | 141 |

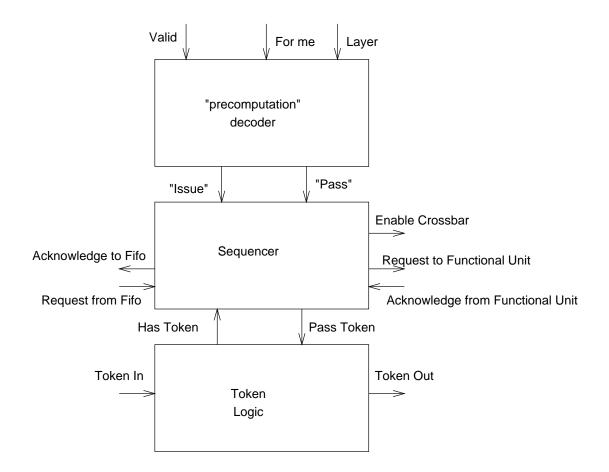

| 6.8  | Issuer Cell Internal Organisation                           | 142 |

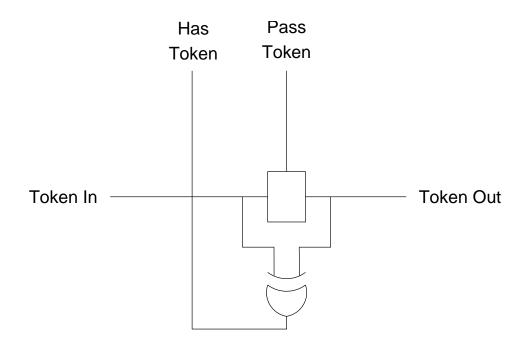

| 6.9  | Token Block Implementation                                  | 143 |

| 6.10 | Decode Block Implementation                                 | 144 |

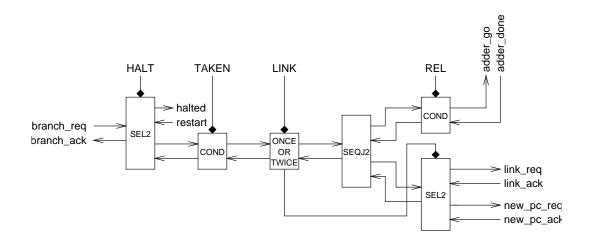

| 6.11 | Sequence Block Implementation                               | 145 |

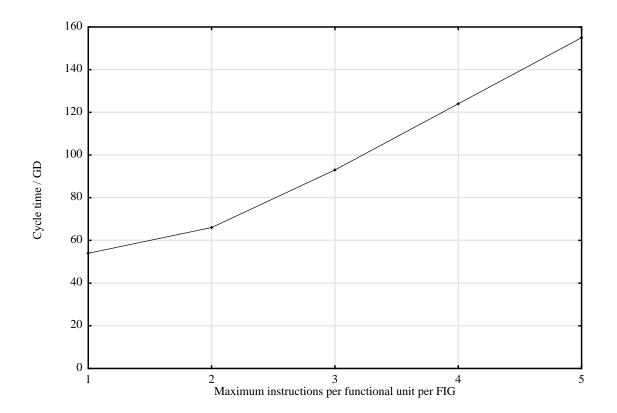

| 6.12 | Instruction Issuer Architectural Performance                | 150 |

| 6.13 | Single Bus Network                                          | 152 |

| 6.14 | Fully Populated Crossbar Network                            |     |

| 6.15 | Two Bus Network                                             |     |

| 6.16 | Four way mutual exclusion circuit built from two way mutual |     |

|      | exclusion elements                                          | 153 |

| 6.17 | Arbiter for Result Network                                  | 154 |

| 6.18 | An Asymmetric Result Network                                | 155 |

| 6.19 | Function Units General Structure                            | 156 |

| 6.20 | Branch Unit Sequencer                                       | 156 |

| 6.21 | SCALP Block Sizes                                           | 161 |

| 7.1  | Pipeline Visualisation                                      | 167 |

| 7.2  | Instruction Issuer Performance                              | 173 |

| 7.3  | Performance of Isolated Pipeline Stages                     | 176 |

| 7.4  | Performance and Branch Interval                             |     |

| 7.5  | Instruction Sequence Functional Unit Parallelism            | 184 |

| 7.6  | Example Program Functional Unit Parallelism                 | 185 |

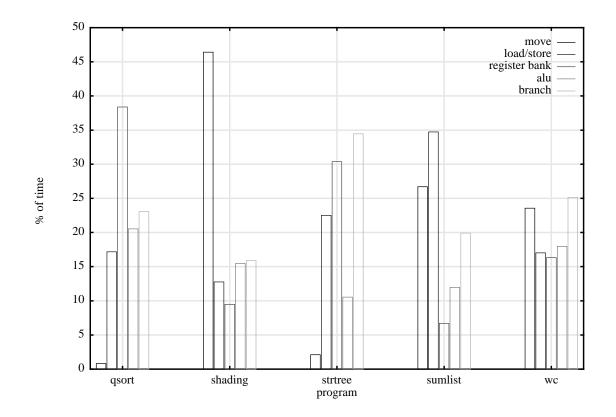

| 7.7  | Functional Unit Use for Example Programs                    | 186 |

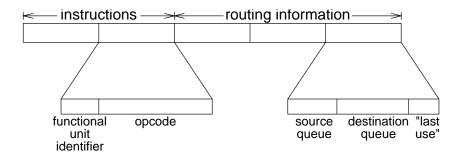

| 8.1  | Instruction Encoding with Separate Instructions and Result  |     |

|      | Routing                                                     | 200 |

## **List of Tables**

| 2.1  | Improvement in SPARC code density resulting from             |      |

|------|--------------------------------------------------------------|------|

|      | instruction set changes                                      | . 26 |

| 2.2  | Frequency of 2-address instructions in SPARC code            | . 30 |

| 2.3  | Frequency of Last Result Re-use                              | . 30 |

| 3.1  | Video Decompression Circuits from [RABA94]                   | . 39 |

| 3.2  | Programmer-visibility of parallelism                         | . 40 |

| 3.3  | Effective parallelism in a 6 stage pipeline                  | . 47 |

| 3.4  | Instruction Mix                                              | . 48 |

| 3.5  | Performance Advantage of Major Processor Features (from      |      |

|      | [JOHN91])                                                    | . 55 |

| 3.6  | Branch Prediction and Power Efficiency                       | . 58 |

| 4.1  | Performance Of Synchronous and Asynchronous Pipelines        | . 69 |

| 4.2  | Performance Of Synchronous and Asynchronous Superscalar      |      |

|      | Processors                                                   | . 75 |

| 4.3  | Recent Asynchronous Microprocessors                          | . 78 |

| 4.4  | Characteristics of the AMULET1 compared with ARM6;           |      |

|      | slow-slow silicon                                            | . 80 |

| 5.1  | Number of times each instruction result is subsequently used |      |

|      | (from[ENDE93])                                               | . 93 |

| 5.2  | Instruction Set Summary                                      | 103  |

| 5.3  | Functional Unit Use for Conventional Program (Example 1)     | 111  |

| 5.4  | Functional Unit Use for SCALP Program (Example 1)            | 112  |

| 5.5  | Functional Unit Use for Conventional Program (Example 2)     | 114  |

| 5.6  | Functional Unit Use for SCALP Program (Example 2)            | 115  |

| 6.1  | Macromodules used in the SCALP implementation                | 128  |

| 6.2  | Issuer Decode Block Function                                 | 144  |

| 6.3  | Instruction Issuer Architectural Performance                 | 149  |

| 6.4  | Total Gate Counts                                            | 158  |

| 6.5  | Gates per Block.                                             | 160  |

| 6.6  | SCALP, AMULET and ARM sizes                                  | 161  |

| 7.1  | Illustrating the use of the Geometric Mean                   | 168  |

| 7.2  | Static Code Size / bytes                                     | 169  |

| 7.3  | Dynamic Code Size / bytes                                    | 169  |

| 7.4  | Register Bank and Move Unit Instructions per Useful          |      |

|      | Instruction                                                  |      |

| 7.5  | FIG fetch performance, no branches                           |      |

| 7.6  | Instruction issuer performance                               |      |

| 7.7  | Functional Unit Performance                                  |      |

| 7.8  | Network Performance                                          |      |

| 7.9  | Performance of Isolated Pipeline Stages                      |      |

| 7.10 | Pipeline Decoupling Queue Lengths                            |      |

| 7.11 | Ideal and Actual Queue Lengths.                              |      |

| 7.12 | Branch Latency                                               |      |

| 7.13 | Instruction Sequence Throughput                              |      |

| 7.14 | Example Program Throughput                                   | 182  |

| 7.15 | Maximum Potential Functional Unit Parallelism for Example |  |

|------|-----------------------------------------------------------|--|

|      | Programs                                                  |  |

| 7.16 | Average Functional Unit Parallelism 187                   |  |

| 7.17 | Example Program Performance 188                           |  |

| 7.18 | Power Saving due to Inactive Functional Units 192         |  |

| 8.1  | Example Program Code Sizes for SCALP with Separate        |  |

|      | Result Routing 201                                        |  |

| A.1  | Benchmark Programs 208                                    |  |

### Abstract

The design of low power microprocessors is an important research area because of the increasing demand for high-performance portable computers with long battery life. Most previous low power microprocessor designs have been constrained by the need to maintain compatibility with existing instruction sets and so have been able to apply power efficiency techniques only at the implementation level and below. Furthermore conventional design approaches have prevented processor implementations from exploiting the power saving potential of asynchronous logic. This thesis describes a processor, SCALP, whose architectural design and implementation are free from these constraints.

SCALP is motivated by three objectives: high code density, highly parallel operation, and asynchronous implementation. These three objectives should all lead to increased power efficiency and also dictate the nature of the architecture.

Conventional instruction sets indicate the flow of data between instructions by means of register numbers; each instruction gives register numbers for its operands and result. This technique leads to complexity in pipelined superscalar implementations: register numbers from many instructions must be compared to identify dependencies and activate appropriate forwarding paths. In asynchronous systems these forwarding paths cause further inefficiency due to the additional synchronisation that they impose. Furthermore the register specifier bits in a typical instruction set take up around half of the total instruction, making them crucial to code density.

SCALP's main architectural innovation is its use of "explicit forwarding". SCALP does not use a global register bank but rather indicates for each instruction to where the result should be sent. This takes the form of a destination queue identifier. One such queue is associated with each operand required by each functional unit. Using this scheme the need for many register specifier comparators is eliminated. The arrangement also suits asynchronous implementation and increases code density.

SCALP has other features aimed at increased code density or other ways of increasing power efficiency: it has variable length instructions and operations need only activate part of the datapath for byte operations.

After describing the background to and features of the proposed architecture the implementation is described. SCALP is the first known asynchronous implementation of a superscalar architecture. It operates using the four-phase bundled data protocol like the AMULET2 processor. Much of the design uses a "macromodule" design approach, and the total size of the design is around 9,500 components. The design of some of the more interesting parts of the implementation, such as the parallel asynchronous instruction issuer, are described in detail.

The implementation has been taken to gate level using the hardware description language VHDL. The implementation is extensively evaluated in comparison with a conventional instruction set and conclusions about its effectiveness are drawn.

### **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning, except as indicated in section 2.1.

## **Copyright and Intellectual Property Rights**

- (1) Copyright in the text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made only in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

- (2) The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of Department of the Department of Computer Science.

## Acknowledgements

During my three years as a postgraduate student in Manchester I have received a great deal of support and encouragement from many students and staff in the Department of Computer Science. I would like to thank everyone for their help.

I am especially grateful to my supervisor Prof. Steve Furber who has encouraged my creativity, and to the other members of the AMULET research group.

Thanks are also due to those people who have helped by proof reading and commenting on this thesis, in particular Richard York and David Gilbert.

### **The Author**

Philip Endecott obtained a B.Sc. (I) degree in Computer Science from the University of Manchester in 1991. After a year employed by Advanced RISC Machines Ltd in Cambridge he returned to Manchester as a postgraduate student. In 1993 his M.Sc. thesis entitled "Processor Architectures for Power Efficiency and Asynchronous Implementation" was submitted. This thesis represents the result of a further two years work in this area.

## Chapter 1: SCALP: A Superscalar Asynchronous Low-Power Processor

To design a superscalar microprocessor is a complex and challenging task. To do so using asynchronous logic - the subject of this thesis - makes it doubly difficult. So what is it that makes such a processor desirable? The answer is that superscalar and asynchronous operation, along with a number of other factors, should help to make SCALP a highly power efficient processor.

Power efficiency is becoming an increasingly important factor in digital design, particularly as a result of the proliferation of portable battery-operated applications. Proposed design techniques for low power systems are discussed later in this chapter. These techniques have been applied with particular success in special purpose signal processing applications such as the Philips Digital Compact Cassette Player [BERK95] and the Berkeley InfoPad [CHAN94]. In the case of general purpose processors however designers have been less adventurous.

Many constraints influence the designer of a general purpose microprocessor. Often it is necessary to maintain code compatibility with a previous design. If absolute code compatibility is not necessary then the processor is expected to follow a model that assembly language programmers and compiler code generators are used to. At the very least an execution model that is a suitable target for common high level languages is needed. Other constraints limit the choice of implementation technology. Compatibility with existing memory and interface circuits requires that the processor operates in a conventional synchronous fashion at a fixed standard supply voltage. All these restrictions limit the designer's ability to apply novel and radical ideas that may have benefits in terms of power efficiency or other factors.

This work has suffered no such impediment. SCALP, the processor described here, deviates significantly from the conventional idea of a microprocessor in order to try architectural and implementation ideas that may contribute towards increased power efficiency.

This first chapter starts by providing a background explaining why power efficiency is becoming increasingly important. Proposed techniques for improving power efficiency are reviewed, and finally an overview of the remainder of the thesis is presented.

### **1.1 The Importance of Power Efficiency**

There are several reasons why power efficiency is becoming increasingly important. Most importantly portable systems powered by batteries are performing tasks requiring increasing computational performance. At the same time these systems are becoming physically smaller and battery weight is becoming more significant. Users demand longer battery life and this can only be obtained by increasing the capacity of the battery or by increasing the efficiency of the logic. The rate of progress in battery technology is slow, so the onus is on the digital designer to improve efficiency.

There are other reasons why power is becoming important. As the heat output of chips increases it becomes more difficult and expensive to provide sufficient cooling in the form of special packages, heat sinks and fans. Furthermore increased temperatures lead to greater stress on the component and reduced reliability.

Electrical issues are also important. Providing a supply of sufficient capacity requires a large number of bond wires between the chip and the package, and a large proportion of the potential signal routing space is occupied by power distribution. High current densities can lead to electromigration. At the system level, increased power demands larger and more expensive power supplies.

Even the cost of the electricity used can be important. It is estimated that at the end of the decade 10 % of U.S. non-domestic electricity consumption will be by personal computers. Reducing this contribution would have significant economic and environmental benefits.

These factors, and others described in [ENDE93], combine to make power efficiency an increasingly important factor in the design of digital systems.

#### 1.2 Low Power Design Techniques

This section reviews techniques that have been suggested for improving power efficiency. These techniques apply at a number of levels from transistors through to high level design. The savings obtained at each of these levels tend to combine multiplicatively, so a successful low power system must employ techniques at all levels.

The descriptions in the following sections apply to CMOS logic unless otherwise indicated.

#### 1.2.1 Low-Level Power Efficiency

#### Process Technology

The ever-diminishing feature size possible with successive generations of fabrication processes is greatly beneficial to power efficiency. As feature sizes shrink capacitances

are reduced and gates become faster. As a first approximation the energy per gate transition is proportional to the cube of the feature size and the gate delay is directly proportional to the feature size if the supply voltage is scaled with the feature size [WEST93].

As feature sizes continue to scale interconnect delays become increasingly significant. Interconnect delays do not scale with feature size or with supply voltage and so eventually limit the available performance.

Improving process technology also allows for the construction of increasingly large circuits on single chips. Inter-chip connections are far more power consuming and slower than on chip connections, so as the number of inter-chip connections necessary is reduced the power efficiency of the system is improved.

#### Transistor Level Design

The size of the transistors used to build basic logic gates affects their speed and power consumption. One objective is to obtain fast output changes as short-circuit current flows in the driven gate at intermediate voltages during the transition. On the other hand it is desirable to minimise transistor sizes in order to reduce capacitances. Recent work [FARN95] has investigated the ideal transistor sizes for greatest power efficiency.

In some cases asymmetric gates can be constructed; some input to output paths are faster and are used for critical paths while others are more power efficient and are used for less critical paths. The scope is greatest in the case of complex gates where the order of the transistors can be chosen based on known input transition orders and probabilities [GLEB95].

#### Charge Recovery and Adiabatic Systems

Conventional circuits charge nodes that must become high by connecting them to the positive supply and discharge nodes that must become low by connecting them to the

negative supply. This mode of operation leads to the conventional CMOS power consumption equation:

$$P \propto C V_{\text{supply}}^2$$

Other schemes use different techniques. Adiabatic systems [SOLO94] use inductors, capacitors and sinusoidal clock / power signals to charge nodes in a more efficient fashion such that

$$P \propto V_{\text{supply}} V_{\text{threshold}}$$

More readily implementable schemes use charge sharing between signals; signals that are high and wanting to become low are connected to signals that are low and wanting to become high, moving all nodes to an intermediate level. Subsequently the power supply is used to complete charging or discharging the nodes [KHOO95].

#### Logic Optimisation

For conventional CMOS the majority of the power consumption is dynamic; that is power is consumed only when signals change. Power efficiency can therefore be improved by reducing the probability that signals will change.

In many cases the most common mode of operation of a block is known, for example a typical sequence of states for a state machine or a typical set of inputs for a combinational block. Low power consumption in this mode can be an objective of the design process. Algorithms have been proposed that provide state encodings and implementations for optimum power efficiency for state machines based on typical state sequences [OLSO94].

#### Supply Voltage Adjustment

Optimum power efficiency occurs when a circuit is powered from the lowest supply voltage at which it can provide the necessary performance. Recent work [USAM95] has suggested providing multiple supply voltages to a system. Gates on the circuit's critical

path are operated from the higher voltage and those not on the critical path are operated from the lower voltage. Other work [NIEL94] [KESS95] proposes that the power supply to the whole circuit is dynamically adjusted in response to the varying workload (see section 4.1.4).

#### Parallelism

Increasing the parallelism in the system permits individual gates to operate more slowly while maintaining the same overall throughput. Slower operation may be performed at a lower supply voltage, increasing power efficiency [CHAN94] (see chapter 3).

#### Precomputation

Precomputation may be used to prevent unnecessary operations from being performed; for example in a comparator it is possible to initially compare only a few of the bits. Only if these bits match need the remaining bits be compared. In the case where the first comparison gives a false result power has been saved [ALID94].

#### Clocking Schemes and Asynchronous Logic

In synchronous systems significant power is consumed by the clock signal, its driver and the driven latches. Clock gating may be employed to disconnect the clock from parts of the circuit that are inactive at a particular time [BENI95].

A more radical approach is to eliminate the global clock altogether. In asynchronous systems, local timing signals control communication between blocks which occurs only when useful work has to be performed (see chapter 4).

#### **1.2.2 Higher-Level Power Efficiency: Microprocessors**

At higher levels of abstraction methods of increasing power efficiency are dependent on the particular application. In the case of microprocessors, this means the architectural properties of the processor and its instruction set.

Previous work by the author identified three particularly important architectural features: external memory bandwidth, cache characteristics, and datapath arrangement [ENDE93].

#### External Memory Bandwidth

The power consumed operating an external signal is substantially larger than the power used by an internal transition; consequently it is important to minimise number and size of external memory accesses. This can be effected by:

- Increasing the code density; a processor with a higher code density will require fewer or smaller instructions to be fetched for a given workload.

- Reducing the frequency of load and store operations. This may be achieved by for example incorporating a larger register bank.

- Improving the on-chip cache characteristics. A higher cache hit rate will reduce the frequency of external memory accesses. Cache write policy is also important; write-through caches will cause more external memory accesses than copy-back caches.

#### **Cache Characteristics**

Because the cache is a large regular structure its power efficiency properties are both important and easy to study. Larger caches will consume more power than smaller ones; this must be traded off against the corresponding reduction in external memory access frequency mentioned above.

Greater power efficiency can be obtained with multiple levels of on-chip cache. In this case the power consumption should be determined by the small size of the more frequently used first level cache, whereas overall performance should be determined by the large size of the second or further levels.

#### **Datapath Arrangement**

Typical RISC processors have a 32-bit datapath which is used for all operations. Many of those operations will be operating on smaller quantities such as characters or small loop counters that could be processed using a small fraction of the datapath width. Power efficiency will be improved if the instruction set provides datapath operations of various widths.

#### **1.3 Previous Low Power Processors**

Most previous low power microprocessors make use of only low level power efficiency techniques in order to maintain code compatibility with previous high power versions of the processors. This section describes the low power techniques used by these conventional processors.

The ARM processor [FURB89] is considered to be one of the most power efficient microprocessors available [ARM95]. Its power efficiency is due primarily to its simplicity and consequent small size. The processor was designed for simplicity in order to reduce both design complexity and cost; the resulting low power consumption was a bonus. While most microprocessors are available only as single integrated circuits the ARM is available as a VLSI macrocell which can be incorporated into a larger chip. In this way the number of off chip interconnections required is reduced, increasing power efficiency.

Other processors that are inherently more complex must apply other mechanisms to increase their power efficiency. The most common approach is to introduce a number of

power saving modes in which parts of the processor are disabled. Typically there would be several modes such as "standby", "sleep", "hibernate" etc. As deeper levels are entered the number of active blocks reduces. Generally these modes are controlled by operating system software. As one example the NEC 4100 processor [TURL95b] has standby, suspend, and hibernate modes that reduce power consumption to 10 %, 5 %, and virtually zero respectively. This processor is targeted at the portable "personal digital assistant" market. Another example is the Hitachi SH7708 processor [TURL95a] which allows the clock frequency to be dynamically changed to 1, 2, or 4 times the input frequency.

Some processor designs have made use of transistor sizing to minimise power consumption. The PowerPC 400 series processors [CORR95] have been designed using a large library of basic gates with many different combinations of transistor sizes. The choice of which gate to use is made by a synthesis tool; the result is that relatively few gates on critical paths use large transistors for high speed and the majority use smaller transistors for low power consumption.

Some other processors do incorporate architectural features that benefit power efficiency, though often these features were not incorporated with power efficiency in mind. Specifically section 2.1.3 considers a number of processors with high code density. Generally though no current microprocessors make high-level architectural choices such as changing the underlying execution model in order to improve power efficiency.

#### 1.4 Overview of the Thesis

Whereas the previous work described above has considered primarily the low level power efficiency techniques, this work concentrates primarily on three of the higher level techniques described in section 1.2, namely parallelism, asynchronous logic and high code density.

The thesis is arranged as follows:

Chapters 2 to 4 consider each of the areas of interest in turn. Chapter 2 considers how the number of transitions required to execute a program can be reduced by increasing code density and reducing the datapath activity. Chapter 3 considers parallelism, particularly how parallelism is obtained in pipelined and superscalar processors. Chapter 4 considers asynchronous logic, investigating how its use can improve power efficiency and considering how the parallel structures described in chapter 3 can be implemented asynchronously.

Chapter 5 describes the SCALP architecture and explains how its novel organisation helps several of the objectives identified in the previous chapters. Chapter 6 gives an introduction to asynchronous design styles before describing the implementation of SCALP as a gate level VHDL model. It gives an overview of the design and then concentrates on some of the more interesting blocks. Chapter 7 presents an evaluation of the processor and studies how well it meets its objectives, identifying strengths and weaknesses.

Chapter 8 gives a summary of the work and then considers ways in which the architecture and implementation could be improved. Ways in which the successful SCALP techniques could be applied to more conventional processors are also considered.

## Chapter 2: Reducing Transitions

One way in which power efficiency can be increased is to reduce the amount of circuit activity required to carry out a computation. This chapter considers two particular ways in which the number of signal transitions that occur while executing a program can be reduced.

The first section is concerned with increasing code density. If code density can be increased then the number of signal transitions in the instruction memory and instruction fetch logic is reduced. The second section considers how datapath activity can be reduced and proposes that when operands are smaller than the whole width of the datapath only the required part of the datapath should be activated.

#### 2.1 Code Density

Code density is a measure of the compactness of encoding of a processor's instruction set. In this section the relationship between code density and power efficiency is shown, and ways in which code density can be altered through changes to the instruction set architecture are investigated. Much of this section is based on previous work by the author in [ENDE93].

The code density of a processor can be defined as the reciprocal of the amount of program code required to perform some standard benchmark task. There are two variants of this measure:

- Static code density measures the total amount of memory required to store the code for the benchmark program.

- Dynamic code density measures the total amount of processor memory code communication required for the execution of the benchmark program.

Static code density and dynamic code density tend to be correlated, but factors such as compiler optimisation can lead to differences. For example, if the compiler unrolls loops in the program the static code density will decrease but the dynamic code density will increase.

Static code density is important when questions such as the size of cache memories are considered; a processor with a higher static code density can obtain equivalent performance with a smaller cache. For questions related to power efficiency it is generally the dynamic code density that is most important.

As a first approximation power consumption in the memory and related parts of the system is inversely proportional to the dynamic code density. If dynamic code density could be doubled then the activity in the memory would be halved, and consequently its power consumption would be halved. The power consumption associated with the main memory system is particularly important as the main memory is typically on a different chip from the processor itself and inter-chip communication is less power efficient than on-chip communication.

Compared with previous generations, modern RISC processors have a relatively low code density. This has occurred for a number of reasons:

In order to minimise the complexity and increase the speed of the processor's instruction decoding logic, the instruction encoding is simple and hence redundant.

Older designs used a microcode ROM for decoding which made more arbitrary encodings possible.

- All instructions are the same length, and the length is determined by the longest required instruction. Other instructions have unused bits. Previous designs used variable length instructions.

- RISC processors have a large number of registers. Typically five bits are used to specify one of 32 registers, and instructions may specify three registers, requiring a total of 15 bits. In earlier systems compilers were unable to make use of so many registers and fewer were provided.

Previous work [ENDE93] measured the potential improvement in code density that could be achieved for a SPARC processor by changing certain aspects of its instruction set architecture. Please refer to appendix A for details of the benchmark programs used. The possible improvements are summarised in table 2.1; following sections interpret many of the values in this table. It can be seen that there is no single way in which the code density can be dramatically improved, though taken together a combination of these changes could have a substantial effect.

|    | Change                                      | Relative code density |

|----|---------------------------------------------|-----------------------|

| 1  | Remove unused bit fields                    | 1.03                  |

| 2  | Fixed length 5-bit opcode field             | 1.08                  |

| 3  | Huffman encoded variable-length opcodes     | 1.25                  |

| 4  | 10-bit branch displacements                 | 1.07                  |

| 5  | 1, 3 and 10-bit add and subtract immediates | 1.04                  |

| 6  | 2- and 3-address instructions               | 1.05                  |

| 7  | Explicit use of last result                 | 1.05                  |

| 8  | Explicit generation and use of last result  | 1.08                  |

| 9  | 16 registers                                | 1.01                  |

| 10 | Workspace pointer register                  | 1.03                  |

| 11 | Load and store multiple                     | 1.11                  |

This section investigates two of these areas where SCALP makes improvements over conventional architectures. These areas are the use of variable length instructions and the code density of register specifiers. The final subsection describes a number of other processor designs that have higher than usual code density.

#### 2.1.1 Variable Length Instructions

There are two ways in which the use of variable length instructions can improve code density:

- Opcodes can be encoded with longer codes for less common operations and shorter codes for more frequent operations. Line 3 of table 2.1 above shows that this technique can increase SPARC code density by 25 %; however to achieve this increase it is necessary to allow opcodes to be any number of bits in length. Realistic variable length instruction formats will allow only a small number of instructions lengths, reducing the benefit of this approach.

- The lengths of immediate fields can be varied. Lines 4 and 5 of table 2.1 shows that if a branch instruction with an immediate field of 10 bits and arithmetic operations with immediate fields of 1, 3 and 10 bits are added SPARC code density can be increased by 11 %.

The reason why RISC processors avoid variable length instructions is that they are more difficult to decode than fixed length instructions. This is especially true when a superscalar processor needs to decode more than one instruction at once.

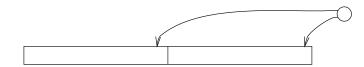

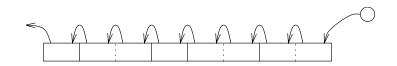

Figure 2.1 shows how two fixed length instructions can be decoded in parallel. In contrast figure 2.2 shows how five variable length instructions in the same total number of bits must be decoded (the solid lines indicate instruction boundaries, the dotted lines indicate boundaries between parts of the same instruction). Because it cannot tell in advance where the boundaries between instructions lie the decoder must consider the instruction parts serially, making the operation significantly slower.

Figure 2.1: Decoding Fixed Length Instructions

Figure 2.2: Decoding Variable Length Instructions

There are ways in which decoding variable length instructions can be made easier. The simplest modification is to ensure that the first part of each instruction contains all of the control information to indicate the total length of the instruction. In this case the decoder can operate more quickly as shown in figure 2.3.

Figure 2.3: More Efficient Variable Length Instruction Decoding

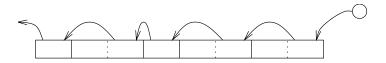

A more radical approach is indicated in figure 2.4. Here a "control field" is associated with each group of instructions. The control field is decoded first and indicates the layout of the instructions within the group to the decoder. The decoder is therefore able to decode all instructions in parallel once the control field has been decoded, making the decoding process nearly as fast as the fixed length instruction decoding. This is the technique used by SCALP.

Figure 2.4: Variable Length Instruction Decoding with a Control Field

#### 2.1.2 Register Specifiers

RISC processors typically use up to about half of the bits in their instructions to represent register numbers. When other techniques such as less redundant opcode encodings and variable length instructions are used this fraction grows more significant. It is important to be able to reduce this factor in order to increase overall code density.

Simply reducing the number of registers is not a solution. Compilers are able to use 32 registers effectively and if the number is reduced the number of load and store instructions is increased.

Reducing the number of register specifiers per instruction is a strong possibility. It is common to find that the destination register is the same as one of the source registers; this was quantified in [ENDE93] (see appendix A) and is summarised in table 2.2. This form of encoding is known as a 2-address encoding rather than a 3-address encoding. Table 2.2 shows that in around one third of instructions one register specifier can be eliminated and a 2-address instruction used. Line 6 of table 2.1 indicates that this can lead to a 5 % code density increase.

Using 2-address instructions is a way of exploiting the locality of register specifiers: if a particular register is given by one register specifier in an instruction then there is an increased chance that it is given by another register specifier in the same instruction. This idea of locality can be taken further. It can be observed that if a register is used in one instruction it has an increased chance of being used by preceding or following instructions.

| Instruction category                   | Example        | % of instructions |

|----------------------------------------|----------------|-------------------|

| No register specifiers                 | Branch         | 19.7              |

| One register specifier                 | Move immediate | 12.0              |

| Two register specifiers, equal         | ADD R1,R1,#1   | 25.6              |

| Two register specifiers, not equal     | ADD R1,R2,#1   | 32.4              |

| Three register specifiers, two equal   | ADD R1,R1,R2   | 5.8               |

| Three register specifiers, not equal   | ADD R1,R2,R3   | 4.4               |

| Total potential 2-address instructions |                | 31.4              |

Table 2.2: Frequency of 2-address instructions in SPARC code

It is very common for the result that has been computed by one instruction to be used by the immediately following instruction. By referring to "the result of the last instruction" in shorthand rather than by giving its register number a significant code density increase can be obtained. Table 2.3 summarises measurements of this property made in [ENDE93] (see appendix A).

|    | Instruction category                                                                       | % of instructions |

|----|--------------------------------------------------------------------------------------------|-------------------|

| A: | Use the result of the previous instruction                                                 | 43.8              |

| B: | As A, but excluding branch instructions that use the boolean result of a preceding compare | 29.4              |

| C: | As B, and the value used is not used by any subsequent instructions                        | 20.6              |

Table 2.3: Frequency of Last Result Re-use

Line 7 of table 2.1 indicates that code density can be increased by 5 % by using an instruction encoding which indicates last result reuse in shorthand.

Line C of table 2.3 suggests how this idea can be taken further. Many instructions use the result of the previous instruction and that result is subsequently never used again. In this case it is not necessary for either instruction to provided a register specifier to refer to this

value; both may use shorthand. Line 8 of table 2.1 indicates that both forms of shorthand together provide an 8 % code density increase.

It is possible to go further and to allow instructions to refer to the results of other preceding instructions, leading to further code density improvements. This idea forms the basis of the "explicit forwarding" mechanism used by SCALP which is described in chapter 5.

#### 2.1.3 Previous High Code Density Processors

Conventional RISC processors have relatively poor code density due to their regular fixed length instruction format. In comparison the preceding generations of CISC processors made use of a more dense variable length instruction encoding.

In addition to the CISC processors a number of other architectures have increased code density. This section considers three processor designs; D16 and Thumb use 16-bit RISC-like instructions whereas the transputer uses a variable length stack based instruction set.

#### D16

[BUND94] proposes a 16-bit RISC-like instruction set called D16. This is based on DLXe which is in turn very similar to the MIPS architecture. Comparisons are made between the code density and power efficiency of D16 and DLXe.

D16's instruction set is relatively simple with only five instruction formats. The instructions specify at most two register specifiers and can access 16 registers.

The dynamic code density of D16 is found to be around 70 % higher than that of DLXe. However as the 16 bit instruction set contains less redundancy than the conventional instruction set, more bits on the instruction fetch bus change per cycle. For D16 on average 3.88 bits change per byte of instruction; for DLXe 2.85 bits change. This means that the 70 % code density increase leads to a power efficiency increase on the instruction fetch bus of only around 30 %.

#### Thumb

Thumb [ARM95] is an extension to the ARM architecture that extends the instruction set to include a set of 16-bit instructions. These 16 bit instructions are dynamically translated to ARM 32 bit instructions during decoding.

The Thumb instruction set is complex with 19 different instruction formats. Most operations use a two address format and can access 8 registers. The standard 32 bit ARM instruction set is available when necessary; for example the Thumb instruction set contains no floating point instructions.

The motivation for Thumb is to increase code density so that ROMs in embedded applications may be smaller, and so that performance can be increased when the processor is connected to a byte or 16 bit wide instruction fetch bus. The reduced instruction fetch requirement also leads to increased power efficiency. Thumb's code density is around 50 % higher than the standard ARM processor.

#### Transputer

The transputer [MITC90] is an unusual processor with two key features that lead to increased code density.

Firstly the execution model is based on a stack rather than a register bank. Most instructions receive their operands from and write their results to a three entry stack. Other data must be stored in memory, though a small memory is integrated with the processor making this relatively efficient. Memory accesses may be relative to a workspace pointer.

Secondly short variable length instructions are used. Instructions are multiples of one byte long. The most common instructions using only implicit stack addressing without

immediate values are encoded in a single byte; less common instructions and immediate values are encoded using "prefix instructions".

#### 2.2 Datapath Activity

Conventional RISC processors normally have a 32 or 64 bit wide datapath consisting of register bank, ALU, shifter, multiplexors, latches etc. This datapath works efficiently when it is processing quantities of this full width such as addresses but many of the values dealt with by a program are significantly narrower than this. Examples include characters which are encoded by only 8 bits and booleans which require only one. When a 32 bit datapath is used to operate on these smaller quantities much of the power used is wasted.

The solution is to add operations to the instruction set that operate on small quantities. When executing these instructions the processor need only activate a part of the datapath.

The power benefit of the reduced datapath activity must be balanced against the reduced code density resulting from the additional width information in the instructions. SCALP chooses the simplest possible scheme with each instruction using a single bit to indicate whether it operates on byte or word quantities.

Many earlier CISC processor architectures included datapath operations of more than one width. In some cases these features lead to complications when advanced implementations of these architectures were considered. Consider the following example:

- An early instruction writes a 32-bit value into a register.

- A later instruction starts execution and will write an 8-bit value into the same register.

- The immediately following instruction wishes to read a 32-bit value from this register.

In a pipelined implementation, a forwarding path would be used to send the result of the second instruction to the third. However the value that the third instruction should receive should contain 8 bits from the second instruction and 24 from the first instruction. It is therefore necessary for the third instruction to get part of the value from the forwarding path and part of it from the register bank. This is complex and undesirable.

This problem has recently been reported in the Intel P6 processor which is a superscalar implementation of the old 8086 architecture [GWEN95].

To avoid this type of problem SCALP defines the most significant bits of a value to be undefined when an instruction has operated on only the least significant byte.

## Chapter 3: Parallelism

This chapter investigates the idea that increased parallelism can be beneficial for power efficiency, and then describes forms of parallelism that can be used in microprocessors and other systems. Firstly the relationship between power, computational throughput, parallelism, and supply voltage is established.

#### 3.1 Parallelism and Power

Let

*V* be the supply voltage

- *P* be the power consumption

- *S* be the speed at which gates operate

- *N* be the extent of parallelism

- and *T* be the computational throughput

For CMOS circuits, over a reasonable range of supply voltages the gate speed depends directly on the supply voltage [WEST93]:

$$S \propto V$$

(1)

If the potential parallelism is fully utilised, the throughput depends on the gate speed and the parallelism:

$$T \propto SN$$

(2)

If there is no overhead associated with the parallelism, for conventional CMOS power consumption depends on the square of the supply voltage and the throughput [WEST93]:

$$P \propto TV^2$$

(3)

Let us derive the relationship between P and N for constant T and variable V:

Substituting from (1) and (2) into (3):

$$P \propto T \left(\frac{T}{N}\right)^2 \tag{4}$$

Since T is constant, from (4)

$$P \propto \frac{1}{N^2} \tag{5}$$

So power decreases with the square of the parallelism. For example, if a processor with no parallelism is replaced by another with parallelism of two, the power consumption is reduced by a factor of four if the supply voltage is adjusted to maintain the same throughput. The overhead of the parallelism will eat in to this advantage to some extent; the additional control logic will consume power, and the utilisation of the parallelism may be incomplete. Although these effects may be quite significant in some cases they are unlikely to exceed the factor of four mentioned here.

Figure 3.1 plots the relationship derived above for parallelism between 1 and 5.

Figure 3.1: The Relationship between Parallelism and Power Efficiency

# 3.2 Power, Parallelism and Cost

One practical disadvantage of an increase in parallelism is the resulting increase in cost, particularly as many power-sensitive embedded applications are also cost sensitive.

For most forms of parallelism circuit area increases at least linearly with the degree of parallelism (the important exception is pipelining which is discussed later). Cost depends on area, and as area increases yield decreases further multiplying the cost.

In most cases the question of what additional cost can be sustained for a particular increase in power efficiency is a matter of marketing. In some cases however a quantitative argument can be made.

Consider a system comprising a processor and a battery. If the power efficiency of the processor can be increased then a cheaper lower capacity battery could be used with the same overall system performance. If

$C_{p1}$  is the cost of the non-parallel processor

and  $C_{b1}$  is the cost of the battery for the non-parallel processor

then the optimum degree of parallelism,  $N_{opt}$ , to minimise total cost is given by

$$N_{\rm opt} = \sqrt[3]{\frac{2C_{b1}}{C_{p1}}}$$

(6)

This result is unappealing because it suggests that in this case even two-way parallelism is attractive only when  $C_{b1} = 4C_{p1}$ . Other factors for desiring low power, such as increased battery life or reduced battery weight, are less quantifiable but may be more compelling.

# 3.3 Parallelism in Special Purpose Processors

The use of increased parallelism to reduce power consumption has been applied in a number of digital signal processing applications with good results.

An excellent example is the Berkeley InfoPad work [CHAN94] [RABA94] which has implemented a number of signal processing functions for a portable multimedia terminal including video decompression. These circuits incorporate substantial parallelism, allowing them to operate at reduced supply voltages and hence with increased power efficiency. Table 3.1 compares two implementations of a video decompression circuit.

These results show that in this special purpose processing application the use of parallelism and reduced supply voltage can lead to very great power savings. It would be a great success to achieve the same sort of savings in general purpose processors.

| Design Style    | Clock Fre-<br>quency / MHz | Supply<br>Voltage / V | Power / mW | Area / mm^2 |

|-----------------|----------------------------|-----------------------|------------|-------------|

| Uni-processor   | 8.3                        | 3.3                   | 10.8       | 72          |

| Multi-processor | 1.04                       | 1.1                   | 0.25       | 112         |

Table 3.1: Video Decompression Circuits from [RABA94]

# 3.4 Parallelism in General Purpose Processors

In the past parallelism has not been applied to general purpose processors with the objective of improving power efficiency, but it has been extensively used to improve performance and exactly the same techniques may be applied. These techniques and their applicability to low power processors are described in the remaining sections of this chapter.

Parallelism in processors may be divided into two categories:

- Parallelism that is explicitly visible to the programmer, for example the multiple communicating processors of a transputer network.

- Parallelism that is not visible to the programmer, for example using pipelining to overlap the execution of several instructions.

Making parallelism visible places the duty of exploitation on the programmer rather than the processor designer. In the case of a transputer network the hardware overhead is low; the only requirement is for a number of communication channels between the processors. On the other hand the programmer's overhead is large: he must re-write his algorithms to use message-passing parallelism.

When parallelism is invisible to the programmer, code that has been written for a conventional processor can be executed unchanged on the parallel machine. The hardware

takes responsibility for detecting and exploiting the available parallelism; consequently the processor design is more complex.

Some examples of programmer-visible and invisible parallelism are show in table 3.2.

| Fully Visible                        | Visible only to compiler | Invisible              |

|--------------------------------------|--------------------------|------------------------|

| Message passing multi-<br>processors | Vector processors        | Pipelined processors   |

| Shared memory multiproc-<br>essors   | VLIW processors          | Superscalar processors |

Table 3.2: Programmer-visibility of parallelism

With all of these approaches the potential for increased power efficiency is determined in the same way by the degree of parallelism achieved, as explained in section 3.1. SCALP uses parallelism that is generally invisible to the programmer and so this chapter focuses on pipelining and superscalar execution.

The following two sections describe the implementation of conventional pipelined and superscalar processors, and it will be seen that particularly in the case of superscalar processors the implementation complexity is high. SCALP finds a compromise that can maintain the programming simplicity of programmer-invisible parallelism and bring some of the hardware simplicity of programmer-visible parallelism.

# 3.5 Pipelining

Pipelining is a particularly attractive form of parallelism because it does not carry the same area overhead that other forms do. This section seeks to find out what degree of pipeline parallelism can be obtained reasonably in a microprocessor and what cost is associated with its implementation.

The degree of parallelism depends on two factors:

- The number of pipeline stages.

- The extent of utilisation of the stages.

Pipelining is possible in RISC microprocessors as a result of their regular instruction sets. In these processors all instructions follow virtually the same sequence of microoperations<sup>1</sup>:

- Generate the address of the instruction.

- Fetch the instruction from the memory.

- Decode the instruction.

- Read the source registers.

- Perform the ALU operation.

- For load and store instructions, access the memory.

- Write the result to the destination register.

There are a number of ways in which these operations can be organised into pipeline stages. The particular organisation chosen will depend on the relative speeds of each of the operations. Here we consider a six-stage organisation where each of these operations is carried out in a separate pipeline stage, with the exception of instruction decode and register read which can be carried out together<sup>2</sup>; other pipeline organisations are considered later.

<sup>1.</sup> branch instructions excepted.

<sup>2.</sup> The positions of the source register specifiers in a RISC instruction are fixed so these registers can be read while the rest of the instruction is decoded.

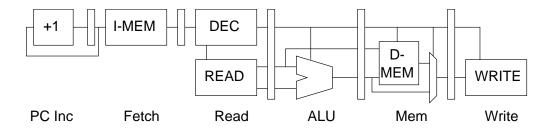

The structure and timing of this pipeline are shown in figures 3.2 and 3.3. In figure 3.3 each column represents a clock period and each row a pipeline stage; the numbers indicate which instruction is active in each stage at each time. It would appear that this organisation offers 6 fold parallelism which has a potential 36 fold power saving. In fact a non pipelined processor would not have to execute exactly 6 times as many cycles as the pipelined processor because many instructions do not need to perform every operation; only loads and stores access the memory, compares and stores do not write a result to the register bank, branch instructions do not access the register bank etc.

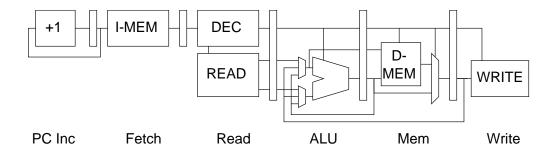

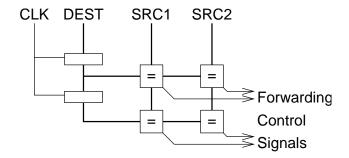

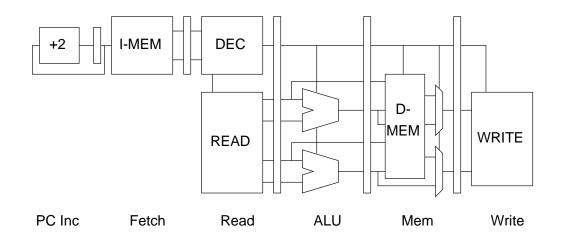

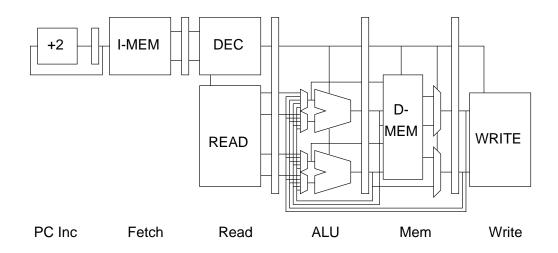

Figure 3.2: A 6-Stage Pipeline

| New PC 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | ] |

|----------|---|---|---|---|---|---|---|---|---|

| Fetch    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | ] |

| Read     |   | 1 | 2 | 3 | 4 | 5 | 6 | 7 | ] |

| ALU      |   |   | 1 | 2 | 3 | 4 | 5 | 6 | ] |

| Mem      |   |   |   | 1 | 2 | 3 | 4 | 5 | ] |

| Write    |   |   |   |   | 1 | 2 | 3 | 4 | ] |

Figure 3.3: Timing of a 6-Stage Pipeline

Furthermore there are two particular problems that could reduce the performance of the pipelined processor: branches and dependencies. The following sections explain these problems and the mechanisms used to mitigate their effects; afterwards table 3.3 quantifies the parallelism that is obtainable.

#### 3.5.1 Branch Instructions

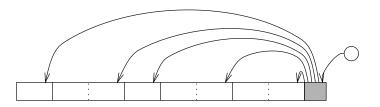

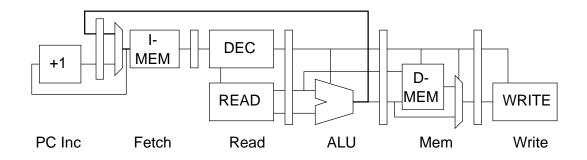

Branch instructions do not work well in simple pipelines because until they have computed their target address instructions from the target address cannot be fetched and begin execution. In a processor with a single adder branch target addresses take the path highlighted in figure 3.4. The timing of this organisation is shown in figure 3.5; instruction 3 is a branch to instruction 10. Two instructions (shaded) must be discarded after the branch is fetched.

Figure 3.4: Branches in a 6-Stage Pipeline

| New PC | 1 | 2 | 3 | 4 | 5 | 10 | 11 | 12 | 13 |  |

|--------|---|---|---|---|---|----|----|----|----|--|

| Fetch  |   | 1 | 2 | 3 | 4 | 5  | 10 | 11 | 12 |  |

| Read   |   |   | 1 | 2 | 3 | 4  | 5  | 10 | 11 |  |

| ALU    |   |   |   | 1 | 2 | 3  | 4  | 5  | 10 |  |

| Mem    |   |   |   |   | 1 | 2  | 3  | 4  | 5  |  |

| Write  |   |   |   |   |   | 1  | 2  | 3  | 4  |  |

Figure 3.5: Timing of Branches in a 6-Stage Pipeline

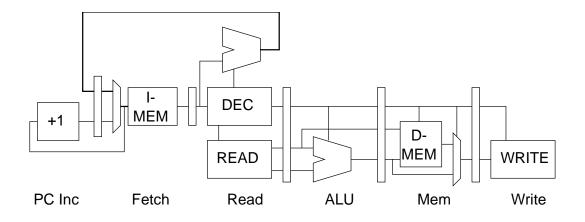

If a dedicated adder is available for branch target computation and branch instructions can be decoded quickly the approach shown in figures 3.6 and 3.7 can be used. In this case only one cycle is lost.

Figure 3.6: A Pipeline with a dedicated branch adder

| New PC | 1 | 2 | 3 | 4 | 10 | 11 | 12 | 13 | 14 |  |

|--------|---|---|---|---|----|----|----|----|----|--|

| Fetch  |   | 1 | 2 | 3 | 4  | 10 | 11 | 12 | 13 |  |

| Read   |   |   | 1 | 2 | 3  | 4  | 10 | 11 | 12 |  |

| ALU    |   |   |   | 1 | 2  | 3  | 4  | 10 | 11 |  |

| Mem    |   |   |   |   | 1  | 2  | 3  | 4  | 10 |  |

| Write  |   |   |   |   |    | 1  | 2  | 3  | 4  |  |

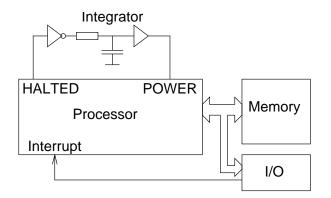

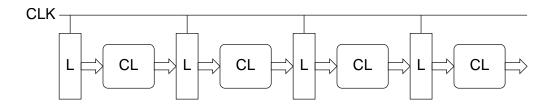

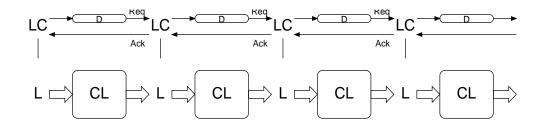

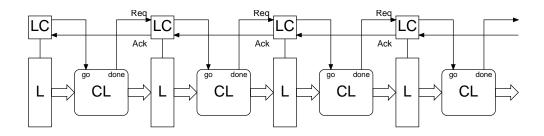

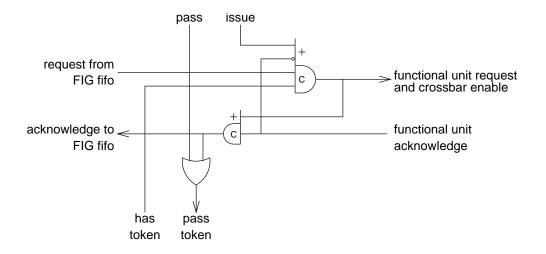

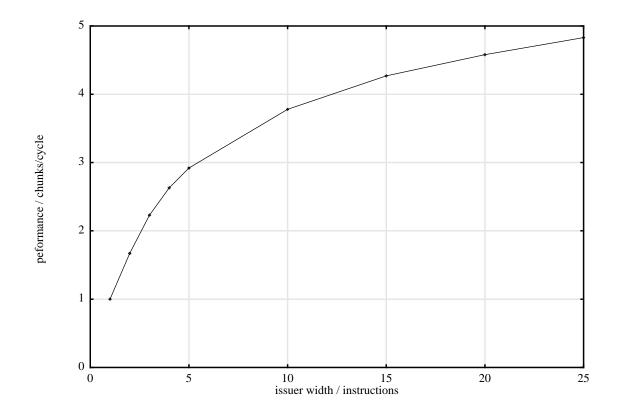

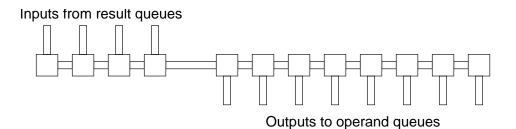

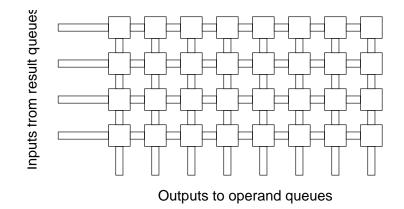

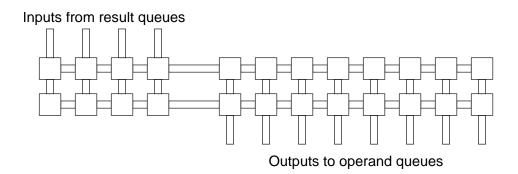

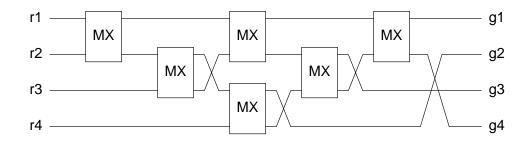

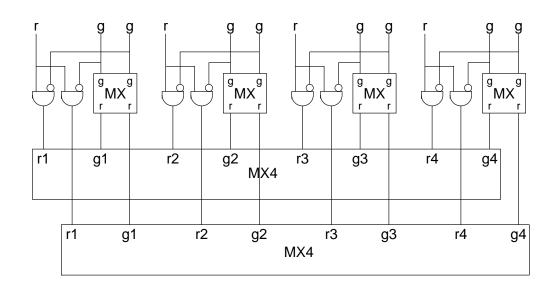

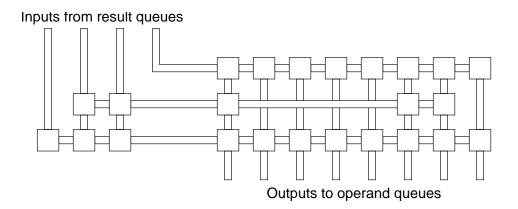

Figure 3.7: Timing of Branches with a dedicated branch adder