# Boosting Single Thread Performance in Mobile Processors using Reconfigurable Acceleration

# Geoffrey Ndu

School of Computer Science

University of Manchester

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Engineering and Physical Sciences 2012

# Contents

| Co  | ontent  | 'S                                      | 2  |

|-----|---------|-----------------------------------------|----|

| Lis | st of F | Figures                                 | 7  |

| Lis | st of 7 | Tables                                  | 9  |

| Lis | stings  |                                         | 10 |

| Ab  | ostrac  | t                                       | 12 |

| De  | eclara  | tion                                    | 13 |

| Co  | pyrig   | ht                                      | 14 |

| De  | edicat  | ion                                     | 15 |

| 1   | Intro   | oduction                                | 16 |

|     | 1.1     | Improving Single Thread Performance     | 19 |

|     | 1.2     | The Need for Dynamically Generated Code | 21 |

|     | 1.3     | Contributions                           | 23 |

|     | 1.4     | Overview                                | 24 |

|     | 1.5     | Publications                            | 24 |

| Ac  | know    | vledgement                              | 16 |

| 2   | Reco    | onfigurable Computing                   | 26 |

|     | 2.1     | Reconfigurable Computing Advantages     | 26 |

|     | 2.2     | Reconfigurable Hardware                 | 27 |

|     |         | 2.2.1 Granularity                       |    |

|     |         | 2.2.2 Reconfiguration Model             | 30 |

|     |         | 2.2.3 System Architecture               | 30 |

|     | 2.3     | Reconfigurable Architecture Programming | 32 |

|     | 2.4     | Warp                                    | 34 |

|     | 2.5     | Configurable Compute Array              | 35 |

#### CONTENTS

|   | 2.6 | Dynam      | ic Instruc | tion Merging .   | • • •   |         |       |     | ••• | ••• | ••• | • | 37 |

|---|-----|------------|------------|------------------|---------|---------|-------|-----|-----|-----|-----|---|----|

|   | 2.7 | RHU ar     | nd RIG co  | ores             | • • •   |         |       |     |     |     |     |   | 38 |

|   | 2.8 | Summar     | ry         |                  | • • •   |         | •••   | ••• | ••  |     | ••• | • | 39 |

| 3 | App | lication A | Analysis   |                  |         |         |       |     |     |     |     |   | 40 |

|   | 3.1 | Introdu    | ction      |                  | • • •   |         | • • • |     | ••• |     |     | • | 40 |

|   | 3.2 | Applica    | tion/Kerr  | el Pool          | • • •   |         | • • • |     | ••• |     |     | • | 40 |

|   | 3.3 | Applica    | tion Cha   | racterisation    | • • •   | • • • • |       |     |     |     | ••• | • | 43 |

|   |     | 3.3.1      | Dynamic    | Instruction Mix  | ζ       |         |       |     | ••• |     | • • | • | 43 |

|   |     |            | 3.3.1.1    | Observations .   | • • •   |         |       |     | ••• |     | • • | • | 44 |

|   |     | 3.3.2      | Kernel Pr  | ofiling          | • • •   |         |       |     |     |     |     |   | 47 |

|   |     |            | 3.3.2.1    | Observations .   | • • •   |         |       |     | ••• |     | • • | • | 48 |

|   |     | 3.3.3      | Instructio | n Level Parallel | ism     |         |       |     |     | ••• |     | • | 48 |

|   |     |            | 3.3.3.1    | Observations .   | • • •   |         |       |     |     |     |     |   | 49 |

|   |     | 3.3.4      | Branch P   | redictability    | • • •   |         |       |     |     |     |     |   | 49 |

|   |     |            | 3.3.4.1    | Observations .   | • • •   |         |       |     |     |     |     |   | 49 |

|   |     | 3.3.5      | Memory     | Reuse Distances  | 5       |         |       |     |     |     |     |   | 52 |

|   |     |            | 3.3.5.1    | Observations .   | • • •   |         |       |     |     | ••• |     | • | 53 |

|   |     | 3.3.6      | Memory     | footprint        | • • •   |         |       |     |     |     |     |   | 53 |

|   |     |            | 3.3.6.1    | Observations .   | • • •   |         |       |     |     |     |     |   | 55 |

|   |     | 3.3.7      | Parallel S | peedup           | • • •   |         |       |     |     |     |     | • | 55 |

|   |     |            | 3.3.7.1    | Observations .   | • • •   |         |       |     |     |     |     |   | 55 |

|   |     | 3.3.8      | Key Char   | acteristics      |         |         |       |     |     |     |     |   | 55 |

|   | 3.4 | Impact     | on Recon   | figurable Accele | erator  | Design  |       |     |     |     |     | • | 56 |

|   | 3.5 | Summar     | ry         |                  | • • •   |         | •••   | ••• | ••• |     | ••• | • | 57 |

| 4 | VIR | EMENT      | Hardwar    | e Architecture   |         |         |       |     |     |     |     |   | 58 |

|   | 4.1 | Introdu    | ction      |                  | • • •   |         |       |     |     |     |     |   | 58 |

|   | 4.2 | VIREM      | 1ENT Ov    | erview           | • • •   |         |       |     |     |     |     |   | 58 |

|   | 4.3 | Microa     | rchitectur | e                | • • •   |         |       |     |     |     |     |   | 60 |

|   |     | 4.3.1      | CPU        |                  |         |         |       |     |     |     |     |   | 60 |

|   | 4.4 |            |            | d Integration .  |         |         |       |     |     |     |     |   | 62 |

|   |     | 4.4.1      | VIREME     | NT Reconfigura   | able Da | atapath |       |     |     |     |     |   | 63 |

|   |     |            |            |                  |         |         |       |     |     |     |     |   |    |

#### CONTENTS

|   |      | 4.4.1.1 ALU                                    | 55 |

|---|------|------------------------------------------------|----|

|   |      | 4.4.1.2 Interconnect                           | 66 |

|   |      | 4.4.1.3 VRD Dimensions                         | 58 |

|   |      | 4.4.1.4 Depth                                  | 59 |

|   |      | 4.4.1.5 Width                                  | 59 |

|   |      | 4.4.1.6 VRD Size                               | 70 |

|   |      | 4.4.1.7 Data Memory Interface                  | 70 |

|   |      | 4.4.2 VIREMENT Control Unit                    | 71 |

|   |      | 4.4.2.1 Reconfiguration Cache                  | 72 |

|   |      | 4.4.2.2 Execution Engine                       | 72 |

|   | 4.5  | Summary                                        | 75 |

| 5 | Dyna | amic Compilation Engine 7                      | 76 |

|   | 5.1  | Overview                                       | 76 |

|   | 5.2  | DCE's Structure                                | 77 |

|   |      | 5.2.1 Runtime Code Generation Process          | 78 |

|   | 5.3  | Reconfigurable Instruction Generation          | 30 |

|   |      | 5.3.1 Translation                              | 30 |

|   |      | 5.3.2 Optimisation                             | 32 |

|   |      | 5.3.3 Placement and Routing                    | 32 |

|   |      | 5.3.3.1 Example P&R                            | 33 |

|   |      | 5.3.3.2 Handling Register False Dependencies 8 | 34 |

|   |      | 5.3.3.3 Handling False Memory Dependencies 8   | 86 |

|   | 5.4  | Summary                                        | 37 |

| 6 | Eva  | luation Methodology 8                          | 39 |

|   | 6.1  | Evaluating Reconfigurable Processors           | 39 |

|   |      | 6.1.1 Functional Simulation                    | 90 |

|   |      | 6.1.2 Execution-Based Co-simulation            | 90 |

|   | 6.2  | VIREMENT Evaluation Framework                  | 91 |

|   |      | 6.2.1 Major Framework Components               | 91 |

|   |      | 6.2.2 Gate-Level Model                         | 92 |

|   |      | 6.2.3 Architecture Model and Simulator 9       | 92 |

|   |      |                                                |    |

#### CONTENTS

|   |      |          | 6.2.3.1 CPU Objects                                 | 93  |

|---|------|----------|-----------------------------------------------------|-----|

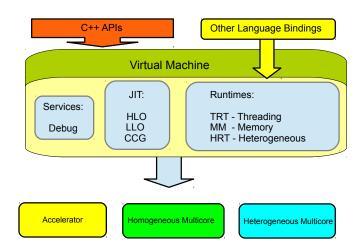

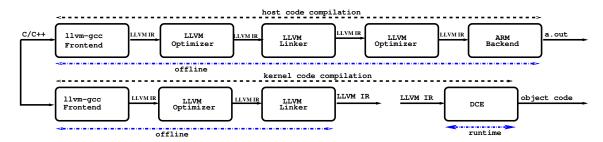

|   |      | 6.2.4    | Compilation and Execution Model                     | 93  |

|   |      |          | 6.2.4.1 A Forward-Scaling Programming Environment . | 93  |

|   |      |          | 6.2.4.2 Compilation on the Framework                | 95  |

|   | 6.3  | Summ     | ary                                                 | 96  |

| 7 | Resi | ilts and | Analysis                                            | 97  |

|   | 7.1  |          | uction                                              | 97  |

|   | 7.2  |          |                                                     |     |

|   | 7.3  |          | • • • • • • • • • • • • • • • • • • • •             |     |

|   | 7.4  |          | mance                                               |     |

|   | 7.5  |          | and Power Efficiency                                |     |

|   | 7.6  |          | Budget Designs                                      |     |

|   |      | 7.6.1    | Models for VIREMENT_16                              | 107 |

|   |      | 7.6.2    | Models for BC                                       |     |

|   |      | 7.6.3    | Models for $BC_{het}$                               | 110 |

|   |      | 7.6.4    | Power Equivalent Models                             | 110 |

|   |      | 7.6.5    | Comparing designs                                   | 111 |

|   | 7.7  | Evalua   | ating DCE                                           | 116 |

|   |      | 7.7.1    | Memory Requirements                                 | 116 |

|   |      | 7.7.2    | Translation Overheads                               | 117 |

|   | 7.8  | Summ     | ary                                                 | 119 |

| 8 | Con  | clusion  | S                                                   | 120 |

|   | 8.1  |          | sis                                                 | 120 |

|   |      |          | ving VIREMENT and DCE                               |     |

|   |      | 8.2.1    | Floating Point PEs                                  |     |

|   |      | 8.2.2    | Split compilation                                   |     |

|   |      | 8.2.3    | Beyond Basic Blocks                                 |     |

|   |      | 8.2.4    | Superscalar Processors                              |     |

|   | 8.3  | Impro    | ving the Evaluation Framework                       |     |

|   |      | 8.3.1    | Energy Estimation                                   |     |

|   |      | 8.3.2    | Area Estimates                                      |     |

|   |      |          |                                                     |     |

| 8.4     | Summary of Contributions |     |  |  |  |  |  |

|---------|--------------------------|-----|--|--|--|--|--|

| 8.5     | Conclusion               | 125 |  |  |  |  |  |

| Acronyr | ns                       | 127 |  |  |  |  |  |

| Referen | ces 1                    | 132 |  |  |  |  |  |

Thesis Word Count: 39397

# List of Figures

| Intel (desktop) vs. ARM (mobile)                     |

|------------------------------------------------------|

| Microprocessor trends: past and future               |

| A state-of-the-art mobile SoC                        |

| Architecture flexibility and performance trade-off   |

| Comparing bit-reversal on ARM9Erev2 and FPGA         |

| Simplified depiction of an LE 29                     |

| Types of RFU coupling                                |

| Architecture of Warp processors                      |

| A block diagram of a depth 7 CCA                     |

| Architecture of DIM 37                               |

| Datapath of a RIG-core 39                            |

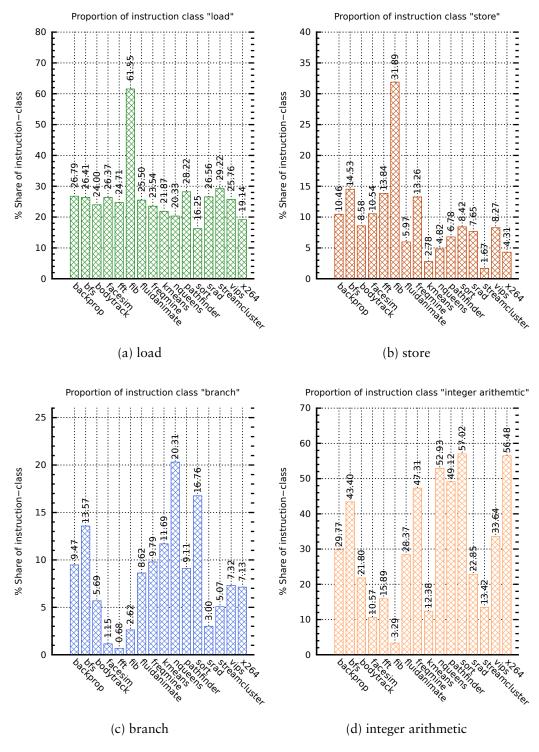

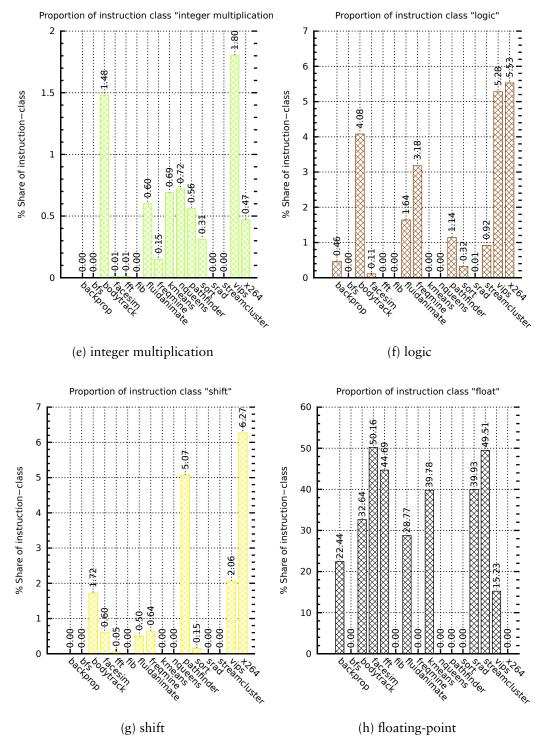

| Dynamic instruction mix per application              |

| Dynamic instruction mix for each individual class 45 |

| Dynamic instruction mix by class (cont.)             |

| Dynamic instruction mix by class (cont.)             |

| Function breakdown based on execution time 48        |

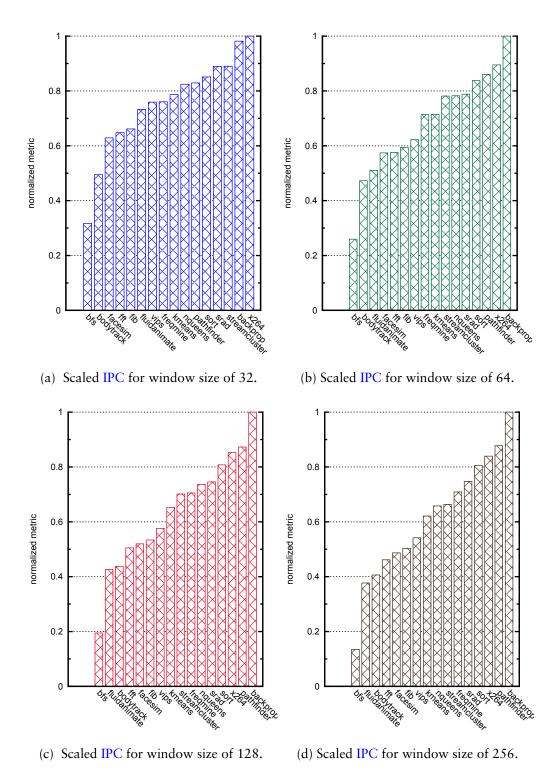

| IPC for window size 32, 64, 128, 256                 |

| The accuracy of branch prediction                    |

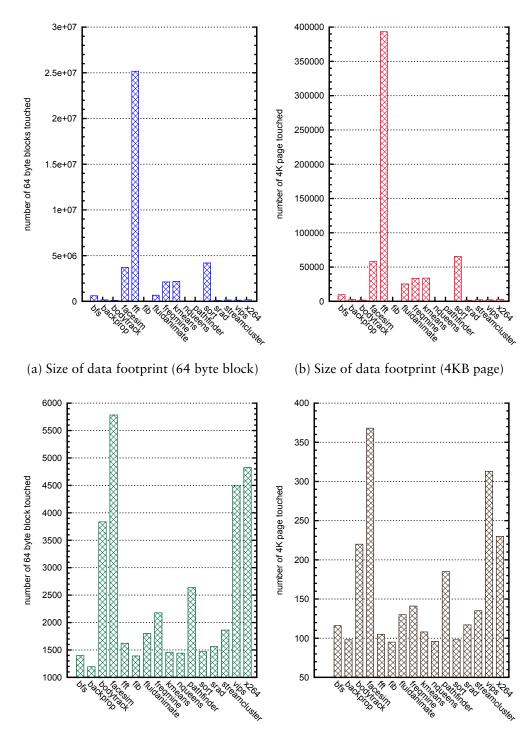

| Size of Memory Footprint 54                          |

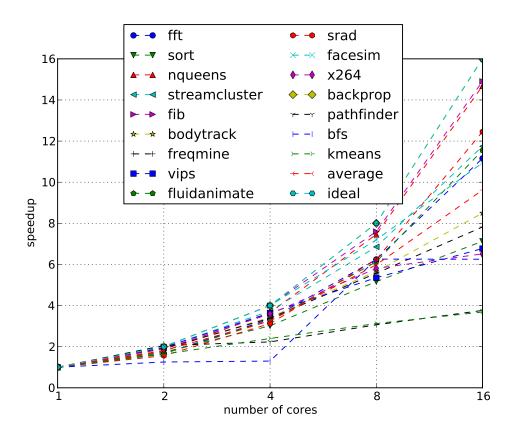

| Speedup for 1, 2, 4, 8 and 16 cores                  |

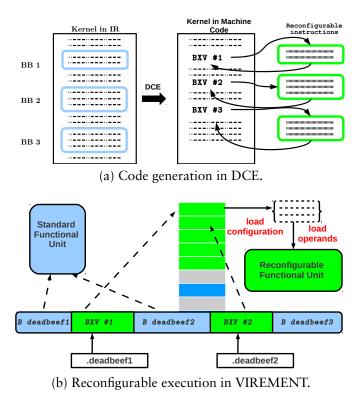

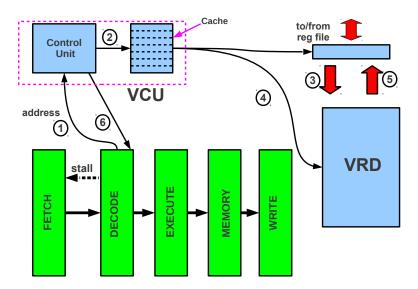

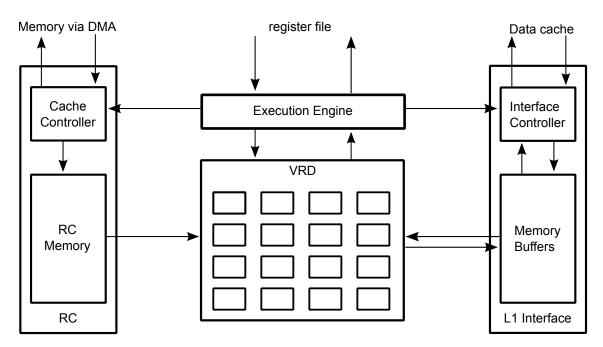

| Overview of compilation and execution in VIREMENT 59 |

| 4-core VIREMENT processor block diagram 61           |

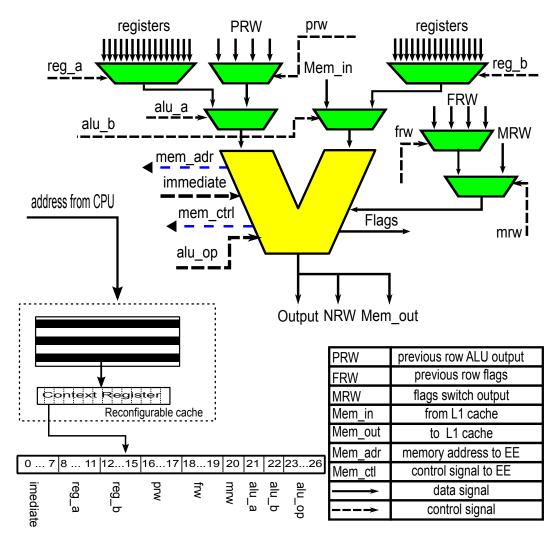

| BXV binary encoding                                  |

| Instruction execution on VRFU 63                     |

| VRD ALU interconnection                              |

| Interconnect on a $2X2$ VRD                          |

| ALU's result forwarding multiplexers                 |

| Basic block processing in LLVMOOPE                   |

| PE control signals                                   |

|                                                      |

| 4.10 Exact controls bits                                                                                                                              | 3 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 4.11 VRFU Block diagram                                                                                                                               | 4 |

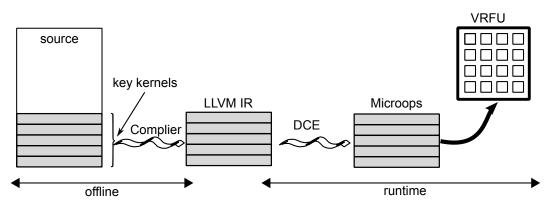

| 5.1 Compilation in DCE                                                                                                                                | 5 |

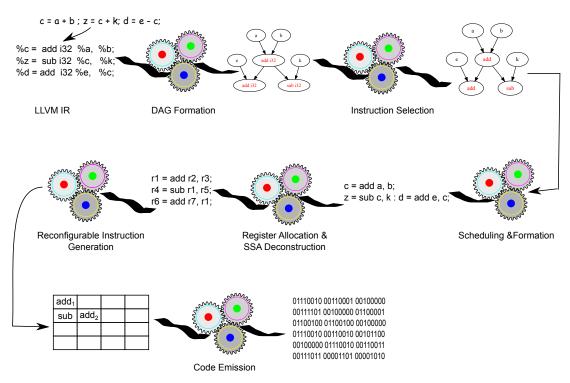

| 5.2 A pictogram of DCE's compiler stages                                                                                                              | 8 |

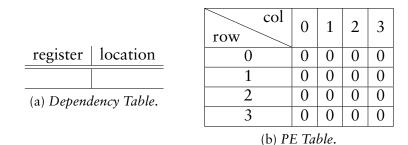

| 5.3 Tables before first P&R                                                                                                                           | 3 |

| 5.4 Tables after first P&R                                                                                                                            | 4 |

| 5.5 Tables after second P&R                                                                                                                           | 4 |

| 5.6 Tables after third P&R                                                                                                                            | 5 |

| 5.7 Tables after fourth P&R 83                                                                                                                        | 5 |

| 5.8 Tables after placing line 1                                                                                                                       | 5 |

| 5.9 Tables after placing line 2                                                                                                                       | 5 |

| 5.10 Tables after placing line 3                                                                                                                      | 7 |

| 5.11 Tables after placing line 4                                                                                                                      | 7 |

| 6.1 ArBB Virtual Machine                                                                                                                              | 4 |

| 6.2 Framework's compilation system                                                                                                                    | 5 |

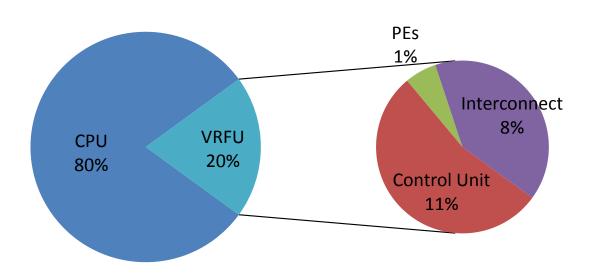

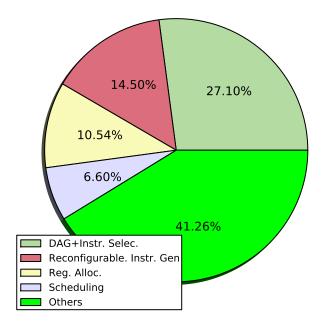

| 7.1 VIREMENT's resource usage                                                                                                                         | 8 |

| 7.2 VIREMENT power cost breakdown                                                                                                                     | 0 |

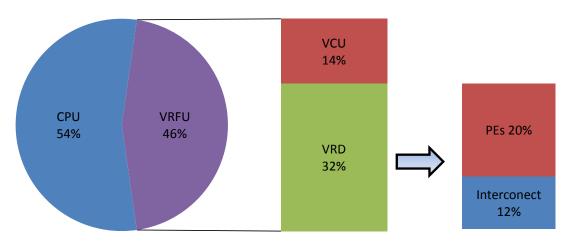

| 7.3 CMP design styles                                                                                                                                 | 7 |

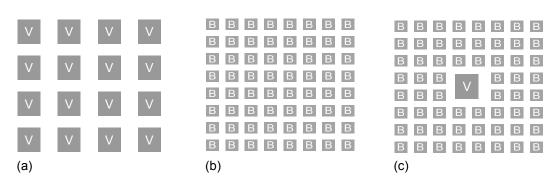

| 7.4 Number of cores for each power budget                                                                                                             | 1 |

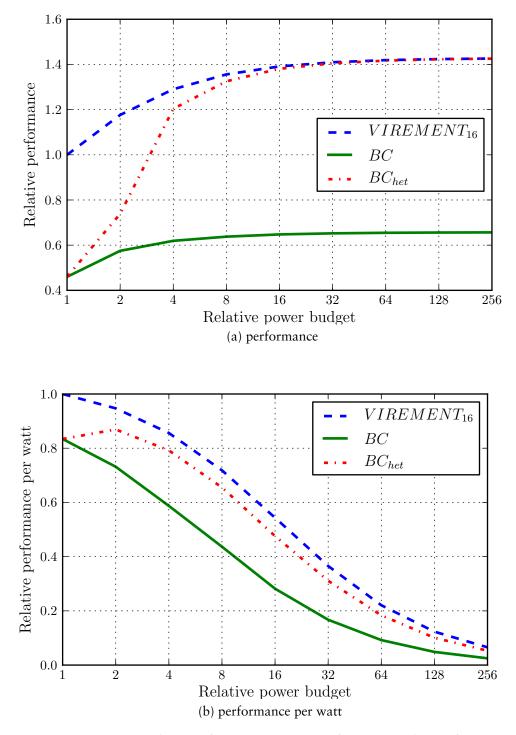

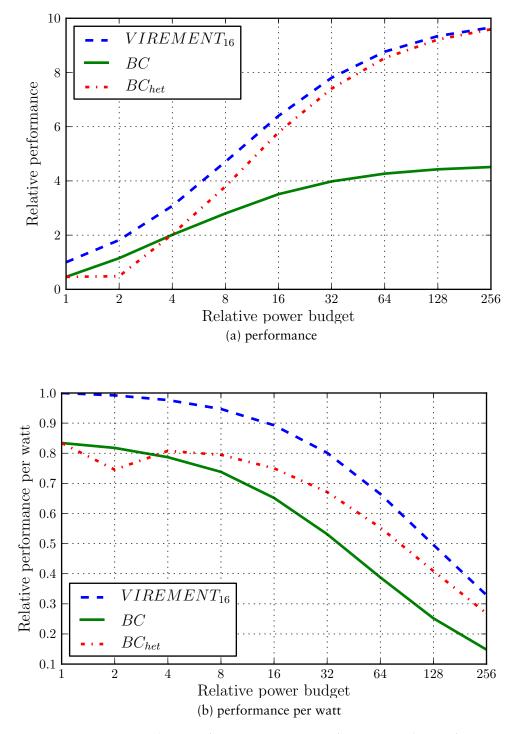

| 7.5 Comparing designs for $f = 0.3 \dots \dots$ | 2 |

| 7.5 Comparing designs for $f = 0.3 \dots \dots$ | 3 |

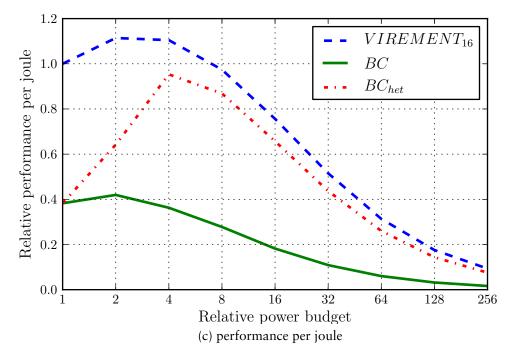

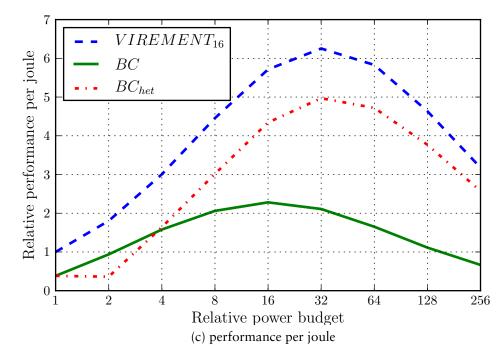

| 7.6 Comparing designs for $f = 0.9 \dots \dots$ | 4 |

| 7.6 Comparing designs for $f = 0.9 \dots \dots$ | 5 |

| 7.7 Time cost DCE                                                                                                                                     | 9 |

# List of Tables

| 1.1  | Supercomputer vs Mobile Phone                                        |

|------|----------------------------------------------------------------------|

| 2.1  | Comparing integration techniques doinside                            |

| 3.1  | Application Pool                                                     |

| 3.2  | Memory reuse distance statistics                                     |

| 4.1  | Supported data operations                                            |

| 4.2  | Cumulative percentage of schedule matrices with varying depths $.70$ |

| 4.3  | Matrix utilization of schedule matrices                              |

| 7.1  | VIREMENT area cost                                                   |

| 7.2  | Dynamic instruction count across kernels                             |

| 7.3  | VIREMENT_16 speedup                                                  |

| 7.4  | VIREMENT_4 speedup 103                                               |

| 7.5  | caption                                                              |

| 7.6  | VIREMENT_32 speedup 104                                              |

| 7.7  | Instructions per configuration                                       |

| 7.8  | VIREMENT_16 area efficiency                                          |

| 7.9  | Extra power to match VIREMENT_16                                     |

| 7.10 | DCE memory consumption                                               |

| 7.11 | Execution time break down                                            |

| 7.12 | Execution time break down                                            |

# Listings

| 5.1 | Translation: CPU Instrs          | 81 |

|-----|----------------------------------|----|

| 5.2 | Translation: Microops            | 81 |

| 5.3 | Microops with false dependencies | 85 |

### Abstract

Boosting Single Thread Performance in Mobile Processors using Reconfigurable Acceleration Geoffrey Ndu A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy, 2012.

Mobile processors, a subclass of embedded processors, are increasingly employing CMP (Chip Multi-Processor) designs to improve performance. Single-thread performance in CMP suffers as vendors move to fewer per core resources to enable them to instantiate more cores on a die. Single thread performance is still important according to Amdahl's law. The traditional technique for efficiently boosting serial performance in embedded processors, dedicated hardware acceleration, is unsuitable for modern mobile processors because of the heterogeneity and the diversity of applications they run. This thesis investigates the possibility and potential benefits of using a general purpose accelerator (placed within the datapath of a CPU), reconfigured on an application-by-application basis, as a means of efficiently increasing single-thread performance. Configurations for the accelerator are generated at runtime, via a JIT compiler, which allows it to accelerate dynamically generated code. This is important as dynamic code generation is now prevalent on mobile processors.

# Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http: //documents.manchester.ac.uk/DocuInfo.aspx?DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http:// www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses

I would like to dedicate this thesis to my loving family.

# Acknowledgements

Thanks to Dr. James (Jim) Garside, my supervisor, and to the whole APT group for their help and encouragement. A big thank you to Dr. Andrew Bardsely and Dr. Plana Cabrera, my proof readers, for their fast turn-around times.

Special thanks to Imepras for donating software tools used in this project.

# Introduction

Mobile processors, a subclass of embedded processors, are General Purpose Processors (GPPs) designed primarily for small, fan-less, battery powered, mobile computing devices such as smart-phones. They are characterised by high performance, low energy consumption, small area and low cost. Mobile processors began as processors tuned for particular classes of applications, Application Specific Instruction-set Processor (ASIP). For instance, early mobile phones had baseband processors (e.g. Philips KISS-16-V2 [1]). Simple scalar processors augmented with Application Specific Integrated Circuits (ASICs) for processing speech and radio signals in real-time. Baseband processors also run the user interface on phones but at a lower priority. The dedicated hardware accelerators on these processors improved performance and reduced energy consumption in a cost and area effective manner [1].

Mobile processors have evolved from ASIPs to full blown GPPs as mobile computing moved from embedded devices, with few functionalities, into portable, connected, general purpose computers. A typical Android [2] smart-phone can install and run about 500 000 [3] diverse applications, often called 'apps', ranging from Linpack [4], a library for numerical linear algebra, to Visidon AppLock [5], a face recognition tool for protecting applications. Relying on dedicated accelerators, as in the early days of mobile phones, to boost performance is no longer practical as apps are diverse and not known at design time. Further, mobile processors are increasingly being used outside portable devices such as in microservers. Micro-servers are servers built using a large number of relatively slow

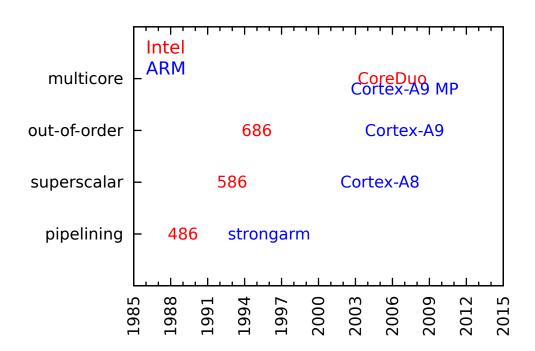

Figure 1.1: Intel (desktop) vs. ARM (mobile).

but cheap and power efficient mobile processors [6]. Therefore, a modern mobile processor is more like a conventional (desktop) processor, see figure 1.1, making it a challenge to manage the contradictory constraints of power/energy, area, flexibility and cost.

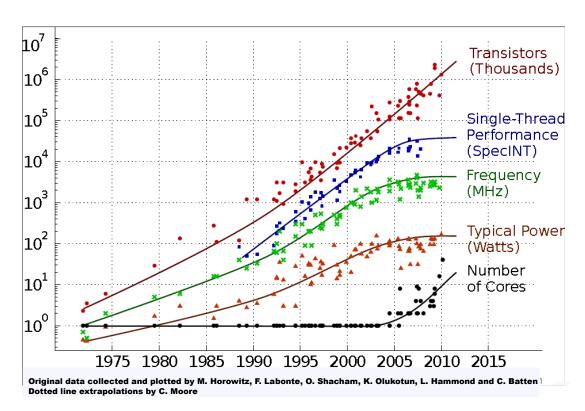

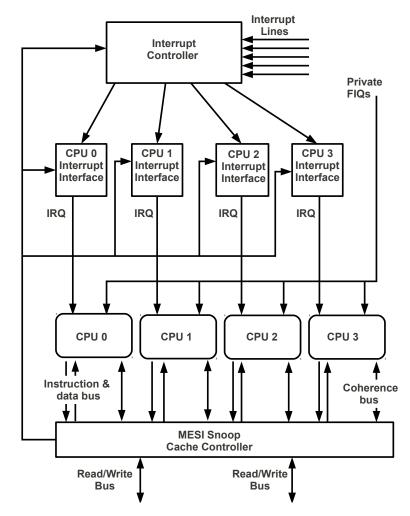

Mobile processor vendors are increasingly employing Chip-MultiProcessor (CMP) designs, multiple 'simple' Central Processing Units (CPUs) (often called 'cores') on the same integrated circuit die, to improve the performance and energy efficiency instead of more powerful single processors. Single processors are no longer scaling in performance (see Figure 1.2 for past and future trends in microprocessor technology), because technology scaling no longer provides consequent clock frequency improvements. Furthermore, it costs less to exploit the ever increasing number of transistors provided by process technology by simply instantiating more copies of the relatively simpler (and relatively easier to design) CPU in each successive chip generation instead of designing and debugging a new large single processor each time. A mobile CMP is actually part of a System-on-Chip (SoC) that enables a typical mobile device such as a smart-phone

1. Introduction

Figure 1.2: Microprocessor trends: past and future [7].

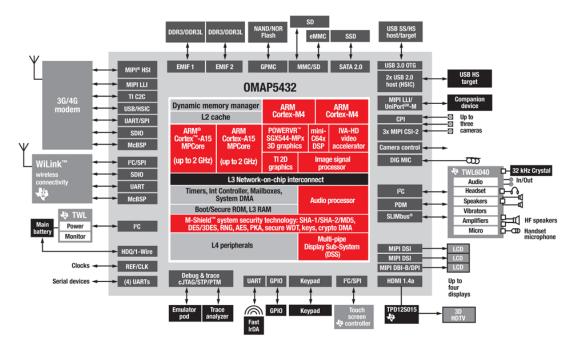

to provide more processing power than was available to supercomputers of the 1970s at  $4 \times 10^{-11}$  of the cost; see Table 1.1. For instance, the Texas Instrument<sup>®</sup> OMAP5432 SoC has up to 12 processors in a 14 mm × 14 mm package that runs within the maximum system power limitation of 2.5–3.0 W for mobile devices while costing less than \$50. These processors range from a 2-core 2 GHz mobile processor to a 16-core General Purpose Graphics Processing Unit (GPGPU), see Figure 1.3, all running off a 1000–1500 mAh battery.

CMPs, also called multi-core microprocessors, improve performance and reduce power consumption by handling more work in parallel on simpler, more energy efficient CPUs compared to single processors. They exploit Thread-Level Parallelism (TLP) [8], distributing execution processes/threads across cores [8, 9]. Performance improvements depend on the fraction of the application that is parallelised. Performance is compromised for lowly threaded applications as CMPs tend to have limited single thread capabilities (because of fewer per core resources). Single thread performance is still important as some key applications have limited TLP. According to Amdahl's law [10], serial sections within a parallel application are performance constraints. Current and future challenge for mobile processor vendors is how to increase single thread performance in these resourceconstrained, general purpose cores efficiently. Most traditional methods employed by conventional cores are unsuitable for mobile processors because of energy, area and cost issues.

| Feature                  | Cray-1                     | HTC HD2                  |

|--------------------------|----------------------------|--------------------------|

| Year                     | 1976 [ <mark>11</mark> ]   | 2009 [12]                |

| Number of processors     | 1 [11]                     | 1 [ <mark>12</mark> ]    |

| Frequency(MHz)           | 80 [11]                    | 1000 [ <mark>12</mark> ] |

| MFLOPS(Linpack 100)      | 3.4 [ <mark>13</mark> ]    | 74 [ <mark>14</mark> ]   |

| Volume(mm <sup>2</sup> ) | $\approx 196846795$ [11]   | 88 845 [ <b>12</b> ]     |

| Power(W)                 | 115000 [ <mark>11</mark> ] | 3 [12]                   |

| Cooling                  | Freon [11]                 | none [12]                |

| Weight(kg)               | 4762 [11]                  | 0.2 [ <mark>12</mark> ]  |

| Price(\$ Million 2009)   | 20-36 [15]                 | 0.0008                   |

| Main Memory(MB)          | 8 [15]                     | 512 [ <mark>12</mark> ]  |

Table 1.1: Supercomputer Cray-1 vs Mobile Phone HTC HD2.

# 1.1 Improving Single Thread Performance

Improvements in single thread performance, at the architectural level, have largely come from superscalar processing and pipelining. Superscalar processing [16] exploits Instruction Level Parallelism (ILP) [17, 18] by dynamically increasing the number of instructions issued simultaneously to functional units on the processor. Pipelining [19] breaks down a single instruction into a sequence of small steps and performs the steps of adjacent instructions in parallel, allowing the clock rate to be increased more than suggested by Moore's 'law' [20]. Unfortunately, extracting

ILP from an instruction stream is power-hungry as the complexity of the additional logic needed for dynamic discovery of ILP is approximately proportional to the square of the number of instructions that can be issued simultaneously [9]. Cost and power issues mean that mobile processors do not employ 'aggressive' superscalar processing. Further, the degree of parallelism in a typical instruction stream is limited [21], so using transistors to build even more complex superscalar processors achieves very little additional benefit for most applications.

## TI OMAP5432 SoC

Figure 1.3: A state-of-the-art mobile SoC. Courtesy of Texas Instruments.

Similarly, increasing performance via deeper pipelines is expensive as more transistors are needed for adding pipeline registers and bypass path multiplexers, increasing power consumption further. This, and performance losses from pipeline flushes, primarily caused by branches, combine to make very deep pipelining unsuitable for mobile processors.

The time-tested approach of accelerating compute-intensive parts of application using dedicated hardware is not suitable for mobile processors because of the heterogeneity and diversity of applications they run. The next best alternative is having 'general purpose' Reconfigurable Hardware (RH), which can be reconfigured on an application by application basis to implement frequently occurring functions. This approach, reconfigurable computing, is less efficient in terms of area, cost and power than fixed hardware but allows a GPP to be *specialised based on the application it's currently running*. GPPs augmented with RH are known as Reconfigurable Processors (RPs). RH has been used successfully to accelerate single thread performance in experimental and commercial processors [22, 23, 24, 25, 26]; the challenge is *how to map dynamically generated code onto the reconfigurable hardware efficiently*.

### 1.2 The Need for Dynamically Generated Code

Software cost is now significant, up to 80% of the development cost for mobile computers [27]. This, and the short development cycles of mobile computing devices makes it inconceivable to rewrite millions of lines of code for each processor generation. Some mobile 'ecosystems', such as Google's Android [2], require all but low-level system code to be written in platform independent Intermediate Representation (IR) which is compiled to binary 'just-before-use' via a Virtual Machine (VM). Mobile processors are designed to be binary compatible across generations and, at most, a simple recompilation is all that is required to port software to a new generation of processor may degrade performance as the application may be very sensitive to hardware parameters such as core count or inter-core latencies, that vary from one generation to another. Consequently, mobile software development is gradually moving to programming systems that support forward-scaling [28].

Forward-scaling is the ability of parallel application performance to scale with new core counts and cope with constant evolution of the Instruction Set Architecture (ISA) with little or no rewriting and compilation i.e. binary and performance portability [28]. For example, the data width of vector extensions increase with each new generation of chip causing difficulties in terms of binary compatibility. Forward-scaling systems such as Array Building Blocks (ArBB) [28] generate vector instructions at runtime to match the width on the processor even though the programmer can't know what they might be when the program was created.

One of the key enablers of forward-scaling in programming systems is dynamic compilation [29, 30]—the runtime compilation of platform independent IR to native code—which allows applications to adapt to particular architectural characteristics at runtime. Most state-of-the-art parallel programming systems now support dynamic compilation. This, potentially, allows applications to take advantage of the latest hardware and software features without the need for recompilation at the cost of runtime overheads.

Dynamic software compilation is now so common on mobile processors that vendors provide hardware to speed it up. For instance ARM processors have ThumbEE and Jazelle [31]. Most state-of-the-art Placement and Routing (P&R) only support off-line mapping on the RH which is inadequate for mobile computers where compilation is now largely dynamic. They need the compiler or programmer to identify suitable section(s) for acceleration and to synthesize configurations for them off-line. The dynamic generation of configuration, dynamic mapping, is particularly difficult for RPs as time consuming tasks such as P&R now need to be performed at runtime. Recent studies [22, 23, 24, 32, 33] have investigated dynamic mapping to RH using Dynamic Binary Translation (DBT) [34]. A dynamic binary translator, which could be software, hardware or a software/hardware hybrid, is used to map sequences of machine code to the RH. DBT for RH has the advantage of low overheads since the semantic gap between microprocessor machine code and RH configurations is small compared to translating from a high-level language. Binaries, however, lack the high-level semantic information required for efficient mapping to the RH requiring binary translators to decompile binaries to recover such information [23]. The sophistication of decompilation differs from design to design. Decompilation is expensive and does not always recover enough high level information. Furthermore, DBT introduces additional overheads reducing performance and increasing energy consumption. Even without the drawbacks of DBT, present DBT-based dynamic mappers are still unsuitable for mobile CMPs because of area, cost, resource (e.g. memory footprint) or power issues.

This thesis advocates dynamic mapping based on compilation from IR instead of DBT. RH dynamic compilers can be integrated into VMs already present on the CMP eliminating the need for an extra, distinct translation layer. Furthermore, IRs usually contain enough high level information to remove the need for decompilation. The translation overheads, however, are high compared to DBT. This thesis explores a hardware/software co-design approach to reducing the overheads of dynamic compilation on RH.

#### **1.3 Contributions**

This thesis explores the possibilities and potential benefits of an architecture that uses RH to accelerate single thread execution of dynamically generated code on mobile CMPs. Its main contribution is the co-design of a mobile CMP (augmented with RH) and associated RH dynamic compiler the Just-In-Time (JIT) variant capable of accelerating single threads in the code produced at run-time. It specifically targets forward-scaling programming systems such as the Array Building Blocks where kernel (critical) code is dynamically generated.

Specifically, the key contributions include:

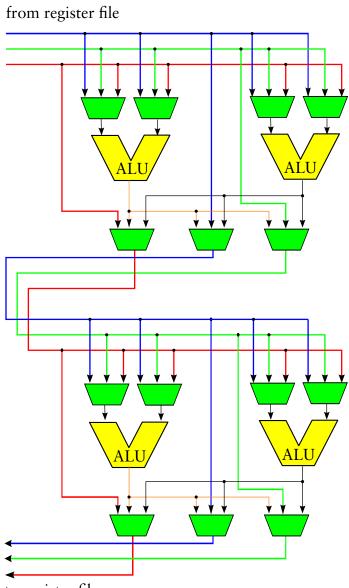

VIrtual REconfigurable Micro-ENgine for Translation (VIREMENT), a mobile CMP architecture where each CPU has reconfigurable hardware integrated as a functional unit. The architecture is restrictive which reduces mapping overhead enabling the run time generation of configurations. The reconfigurable hardware speeds up single threads by exploiting the 'small' ILP within a typical basic block. As such, it consists of a two-dimensional array of interconnected simple, programmable, word-sized functional units with data routed using multiplexers.

Since CMPs have stringent cost constraints (e.g. chip size), the design aims to keep the reconfigurable extension to the CPU small by using a reconfigurable array of modest size.

• Dynamic Compilation Engine (DCE), a JIT compiler for VIREMENT which dynamically translates IR into configurations for the RH. The DCE design

aims to be a back end JIT complier for the numerous VMs available on various mobile software platforms but the primary targets are VMs of forwardscaling programming systems. Like hardware, mobile software platforms have stringent cost constraints (e.g. memory footprint) as such DCE design places emphasis on being lean and fast. The JIT is intended for the translation of kernels (critical sections of an application) to enhance the chances of amortization of overheads.

P&R in the DCE is with a novel, single pass algorithm suitable for resource constrained mobile platforms. The algorithm was developed as part of this thesis.

#### 1.4 Overview

The rest of this thesis is divided into seven chapters:

Chapter 2 reviews reconfigurable processing in general with emphasis on the challenges of dynamic translation. It also discusses related work.

Chapter 3 presents a quantitative characterization of the targeted application and how that impacts the design of VIREMENT.

Chapter 4 discusses the design of VIREMENT.

Chapter 5 discusses the design of DCE and illustrates its operation with some examples.

Chapter 6 presents the proposed evaluation methodology and framework for VIREMENT and DCE.

Chapter 7 is an evaluation of the VIREMENT architecture using the the methodology and framework proposed in chapter 6.

Chapter 8 concludes the thesis with a summary, a list of achievements, and an outline of potential improvements to VIREMENT.

#### 1.5 Publications

The following articles, based on the work presented in this thesis, have been published or accepted for publication:

- Geoffrey Ndu, Jim Garside: Boosting Single Thread Performance in Mobile Processors via Reconfigurable Acceleration. 8th International Symposium on Applied Reconfigurable Computing (ARC 2012): 114-125

- 2. Geoffrey Ndu, Jim Garside: Architecture for Runtime Hardware Compilation. 5th HiPEAC Workshop on Reconfigurable Computing 2011, and also as: HiPEAC Technical Report, TR-HiPEAC-0014, January 2011

- 3. Geoffrey Ndu, Jim Garside: A Co-designed Dynamic Compilation Framework for Reconfigurable Processors (Abstract). Sixteenth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS 2011), March 2011.

2

# Reconfigurable Computing

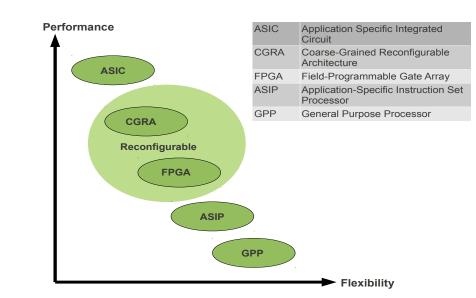

Reconfigurable computing employs some form of post-fabrication programmable hardware potentially allowing the same hardware to be specialised to fit any application. A Reconfigurable Hardware (RH) combines post-fabrication programmability with the spatial (parallel) computation style of ASICs, unlike the less efficient temporal (sequential) computation style of Von Neuman processors [35]. Reconfigurable computing offers a good balance between the contradictory design aims of implementation efficiency and flexibility. This trade-off is depicted in Figure 2.1 for common processing architectures. From the figure, flexibility improves at the expense of efficiency. Augmenting a General Purpose Processor (GPP) core with RH potentially improves efficiency at the cost of reduced flexibility.

### 2.1 Reconfigurable Computing Advantages

Implementing a section of an application using RH may speed up performance significantly compared to software on a microprocessor, especially if the section is highly parallel e.g. extensive bit-level manipulation.

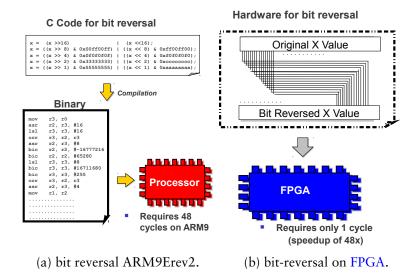

The efficiency of bit-level operations can be improved significantly by using an Field-Programmable Gate Array (FPGA), a type of RH, instead of a microprocessor. Bit-level operations are inefficient on microprocessors as they typically require a separate instruction or several instructions. Figure 2.2 compares bit reversal on an FPGA to a microprocessor. Figure 2.2a is an efficient software implementation of a bit reversal [36] that requires approximately 38 instructions and 48 cycles

Figure 2.1: Flexibility and performance trade-off for various processing architectures

to reverse a 32-bit integer on ARM9Erev2 . However, the same operation can be performed in a single cycle on an FPGA, by simply reversing the connections betweens two buffers as shown in figure 2.2b, achieving a speedup of  $48\times$  (assuming equal cycle lengths). In this example, an instruction to achieve the same effect has been added to later implementations of ARM which illustrates that efficiency in 'rarely' used operations may be important. However, adding many specific instructions to a GPP is not practical because of the limited hardware budget and cost.

## 2.2 Reconfigurable Hardware

#### 2.2.1 Granularity

The RH design space is extensive and can be broadly classified into two segments fine-grained and coarse-grained—based on the data width of the smallest Processing Element (PE). Fine-grained reconfigurable hardware, like an FPGA, employ PEs of data width 1 i.e. bit-level programmable. Conversely, coarse-grained hardware

Figure 2.2: Comparing bit-reversal on ARM9Erev2 and FPGA.

employs PEs working at word level. Fine-grained hardware is very flexible and can implement arbitrary digital logic. However, its flexibility leads to performance, area and power inefficiencies as will be explained shortly. Therefore, a typical FPGA compared to standard cell ASIC requires approximately 20 to 35 times more area with a speed roughly 3 to 4 times slower and consumes roughly 10 times as much dynamic power [37]. The huge difference in efficiency is better understood by looking at the architecture of a typical FPGA, the Altera Cyclone II [38].

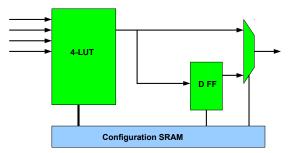

At the heart of the Cyclone II PE is the Lookup Table (LUT). This is a highspeed  $16 \times 1$  Static Random-Access Memory (SRAM). The PE is programmed by loading a function's truth table. Therefore, any logic function with one output and up to four inputs can be implemented on the LUT. More complicated functions can be implemented by aggregating several LUTs.

The LUT and other logic such as flip-flops make up a Logical Element (LE) and 10 of them form a Logic Array Block (LAB). Figure 2.3 shows a simplified LE. Cyclone II devices range in capacity from 4,608 to 68,416 LEs interconnected in a two-dimensional row and column-based architecture. Generally, routing is unsegmented but each wiring segment spans only one LAB before terminating in a switch box. Consequently, an FPGA requires a lot switches, typically 200–400 per

Figure 2.3: Simplified depiction of an LE [40].

4-LUT resulting in an inefficient implementation, especially when used to compose operators for wide datapaths. FPGAs also require large configuration memories because of the high number of configuration points. Partial reconfiguration reprogramming a portion of the FPGA while the rest is still operating—could be used to reduce/hide reconfiguration times at the cost of increased hardware and software complexity.

Some of the disadvantages of FPGAs, lack of forward compatibility and long reconfiguration times, can be tackled with Pipeline Reconfigurable FPGAs (PipeRench architecture) [39]. PipeRench breaks large, single static configurations into pieces that correspond to pipeline stages in the application. These small configurations are swapped in and out automatically at run-time allowing a circuit that would otherwise be too large to fit on the available hardware. Configurations compiled for one instance of PipeRench can used for a larger (or smaller) instance of PipeRench with a corresponding increase (or decrease) in performance.

In summary; fine-grained hardware trades area, speed, and power for flexibility. As such, they are unsuitable for designs where power efficiency is of primary importance, and with their long configuration time it would be slow to implement an execution model which relies of a rapid change of configuration.

In contrast to fine-grained hardware, the PEs in a coarse-grained hardware are complex logic blocks ranging from Arithmetic and Logic Units (ALUs) to small Reduced Instruction Set Computer (RISC) type programmable cores often arranged as a 2D array. The use of complex logic blocks allows for an efficient implementation of complex operators in silicon rather than having to compose such operators from LUTs. Coarse-grained hardware also has fewer configuration points leading to a significant reduction in configuration data and time. However, they are potentially inefficient for bit-level processing. There are also unable to leverage optimizations in the size of operands as the size of each logic block is static. For instance, configuring a 64-bit ALU for 8-bit operations leads to a high degree of inefficiency.

#### 2.2.2 Reconfiguration Model

The reconfiguration model is largely determined by when a new configuration can be loaded into the reconfigurable hardware. Traditionally, a new configuration is only loaded at the beginning of execution and remains unchanged for the duration of the application. This is referred to as static reconfiguration and requires the system to be halted while the reconfiguration is in progress.

Dynamic reconfiguration allows concurrent reconfiguration and execution. This is achieved by grouping configurations into contexts allowing the device to quickly switch between different planes, or context to be swapped as needed. Code that may not have been able to implement completely onto the reconfigurable can be partitioned and swapped as needed.

The dynamic reconfiguration model enables implementation which are otherwise too large for the RH. Reconfiguration overhead, however, becomes significant if not carefully managed [41].

#### 2.2.3 System Architecture

It is often impractical to implement the entirety of an application on a RH. Most applications have large number of sections that are executed relatively infrequently, and attempting to implement all of these sections on the RH would be non-viable (a section needs to be executed sufficiently frequently on the RH to recover configuration overhead). In practice, RH is used to accelerate only the most critical sections (kernels). As such, the RH is usually coupled to a host processor(s) that executes the non-critical control sections. However, some reconfigurable systems [42, 43] are without host microprocessors.

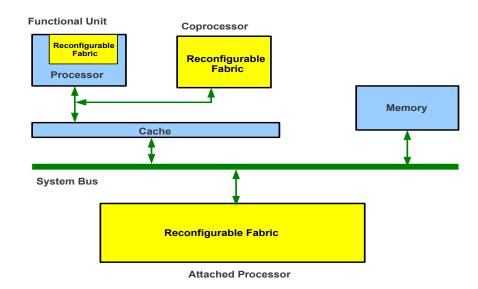

The RH and its host can be integrated in a number of ways as shown in figure 2.4. In some systems [44, 45, 46], the RH is a separate device attached to the

Figure 2.4: Types of RFU coupling

host processor through the system bus. The host processor simply offloads kernels to the hardware for processing. However, the overheads of communicating over the system bus makes this approach suitable only for computations requiring little communication between the RH and the host. For example: graphics processing, where the RH may only need the source and destination addresses from the host to process a large chunk of pixels. Systems employ SRAM-based data buffers (which consumes a significant amount of power), analogous to a data cache, between the reconfigurable hardware and the memory to service applications with data.

An attached processor system is easy to construct and does not require any modification to the host or its compiler. However, the cost of communicating over the system bus limits it to applications where the communication to computation ratio of an application is low.

The reconfigurable hardware can also be coupled to the host processor as a coprocessor [23, 47, 48, 49, 50]. This reduces communications overhead compared to an attached processor as data is exchanged using protocols similar to those used in floating point coprocessors. The host processor requires little or no modification but the communication overhead can still be significant if the communication to computation ratio is high. In such a situation, employing the RH as a extra functional unit in the host processor's data path is more suitable

[50, 51, 52]. This reduces the communication overhead to a minimum as the RH has direct access to the host processor's register file and the decoder issues 'special' instruction to the RH to perform processing just like any other functional unit. However in this case, the host processor needs to be modified to integrate the RH, often called the Reconfigurable Functional Unit (RFU). Such designs are often termed Reconfigurable Instruction Set Processorss (RISPs) [53]. The merits of these different approaches to integration are summarised in table 2.1

| Coupling        | Power <sup>a</sup> | Speed <sup>b</sup> | Bottleneck                                     | Application <sup>c</sup>                                                |

|-----------------|--------------------|--------------------|------------------------------------------------|-------------------------------------------------------------------------|

| Attached        | high               | slow               | 0                                              | large data set, low<br>communication to<br>computation ratio            |

| Coprocessor     | low                | fast               | limited coproces-<br>sor register file<br>size |                                                                         |

| Functional unit | low                | very fast          | limited processor<br>register file size        | small data set,<br>very high com-<br>munication to<br>computation ratio |

<sup>a</sup> power consumed by data-storage elements used for communication.

<sup>b</sup> communication speed between RH and host.

<sup>c</sup> characteristics of application best suited for.

Table 2.1: Comparing RH integration techniques.

### 2.3 Reconfigurable Architecture Programming

**RPs** are not yet widespread—despite significant performance improvements reported by academic and commercial projects—because they are significantly more difficult to program compared to conventional processors.

Programming a RP often involves first choosing a target processor and then writing high-level application code for it, almost always in C/C++. Coarse-grain parallelism is often required to be written in a particular style to exploit the capabilities of the architecture. The application is then optimised for the specific

architecture by identifying parts of the application that can benefit from hardware acceleration, and replacing them with RH configuration(s). Compilation tools are now able to generate the RH configurations—with little or no help from the programmer—and interface them with the rest of the code. Designers, however, still prefer hand-mapping as automatic compilation remains significantly less efficient [54].

Reconfigurable computing is a volatile and fragmented field, new architectures are introduced and previous architectures retired within a short time by different vendors. These architectures do not have common hardware architecture, even those from the same vendor, thus requiring the programmer to re-program substantially each time the application is moved to a new device. This makes reconfigurable processing uncompetitive against standard microprocessors where different hardware architecture implementations are hidden behind a standardised ISA.

Dynamic mapping avoids these problems by translating code to run on RH automatically at runtime. The most common technique is translating executing microprocessor binary onto a restrictive RH (a form of DBT [34]). Restricting the flexibility of the RH drastically reduces the time and resources required to perform tasks such as P&R. Translating from binaries instead of source code keeps overheads small but requires expensive, and not always effective, decompilation to recover high-level constructs such as loops, arrays and functions which are critical to efficient mapping [23].

Mapping without decompilation might result in slower and bigger circuits— Vahid et alia [55] reported an average slowdown of  $4\times$ —while mapping with very limited decompilation lead to implementations that are only slightly faster than software [23, 55]. Therefore, decompilation is a prerequisite for effective binarybased dynamic mapping. As an example, consider that for many applications, compilation exposes parallelism by unrolling loops. Without recovering enough information about loop structures and bounds from binary, the parallelism visible to a binary translator is very limited.

The main problem with decompilation is that the representation of data and instructions in the Von Neumann architecture are indistinguishable. Data is often located in between instructions e.g. indexed jump tables. Furthermore, programmers often write self-modifying code. As such, it is hard and expensive to decompile a software binary [56]. The successes of the reconfigurable architectures that employ extensive decompilation, such as Warp [23, 55] (discussed later), is that they operate in the embedded and DSP domains, where applications tend to be written using constructs that are ideal for decompilation [57].

A Directly Interpretable Representation (DIR) [58], an IR with a simple syntax and a relatively small set of simple operators, such as Lower Level Virtual Machine (LLVM) [59], is a middle ground between the need for high level information and minimising translation overheads. It is portable across RPs and has relatively little run-time translation overhead. A DIR retains enough semantic information to allow more aggressive program transformations than are easily attainable with binary (even with decompilation).

Architectures that employ dynamic mapping are discussed next with emphasis on their suitability for mobile processors.

#### 2.4 Warp

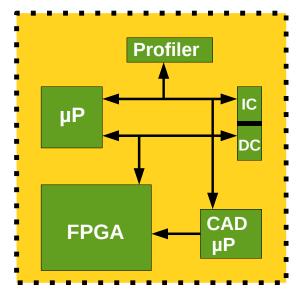

Warp [23] is a family of processors that automatically extracts and compiles critical software kernels to FPGA. A typical Warp processor (see figure 2.5) is an SoC with a main processor for executing application, a less powerful CAD processor on which a lean FPGA compiler—Riverside On-Chip CAD (ROCCAD)—runs, a profiler and an FPGA.

Execution starts on the main processor. A hardware profiler monitors the executing application and determines the critical kernels defined as loops that account for 10% or more of total application execution time. The profiling result is then passed to ROCCAD which first analyses the profiling results to determine the candidates for implementation on the FPGA. The selected kernels are first decompiled to an IR and then synthesised for the FPGA. The hardware configuration generated by ROCCAD is then loaded onto the FPGA. Finally, the executing binary is patched so that the next time the kernels are encountered they are processed on the FPGA instead of the main processor.

Despite the significant reduction in execution times and energy consumption for applications, Warp still suffers from the disadvantages of FPGA-based sys-

Figure 2.5: Architecture of Warp processors

tems (see subsection 2.2.2). Furthermoremore, decompilation, used to convert the executing binary to a format suitable for synthesis, is expensive and does not always recover enough high level information to generate efficient hardware. Finally, the significant on-die memory requirements of ROCCAD and the large memory footprint (which makes them unsuitable for mobile processors) for storing FPGA configurations limits Warp to only applications where a few inner loops dominate.

#### 2.5 Configurable Compute Array

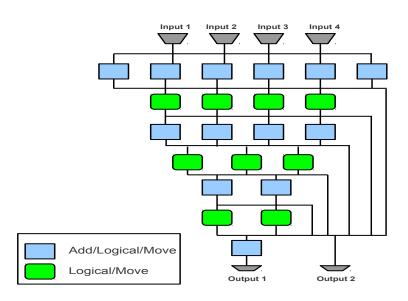

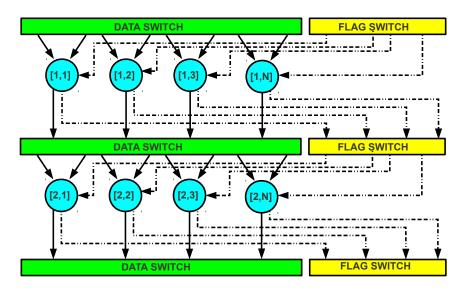

The Configurable Compute Array (CCA) [22, 60] is a matrix of simple, heterogeneous functional units, coupled to a host processor as a functional unit. The CCA, depicted in figure 2.6, is configured with hardware primitives ,'microops', similar to microcode. Data flows from top to bottom with the outputs of functional units fully connected to the inputs of the units in the next row.

Accelerating applications on the CCA involves two steps: the discovery and delineation of critical subgraphs, subsets of an application's Directed Flow Graph (DFG), suitable for the CCA and the replacement of such subgraphs with microops that configure the CCA. Static and dynamic approaches for generating microops

Figure 2.6: A block diagram of a depth 7 CCA.

have been presented [22, 60].

The dynamic approach uses an offline compiler to identify and delineate critical subgraphs that can be mapped onto the RH. However, mapping itself is performed at runtime by a hardware engine which generates the RH configurations necessary to execute the subgraphs. This involves initially executing critical subgraphs without the RH, constructing traces of retiring instructions using a trace cache [61] (a special instruction cache which captures dynamic instruction sequences) and feeding the traces to the mapping engine.

The dynamic mapping approach is completely transparent but requires a trace cache which is rare in a mobile processor because of area, cost and energy issues. Furthermoremore, the mapping engine, based on rePlay [62], uses a very complex graph analysis technique which leads to huge resource overhead. The static approach is similar to the dynamic one but is completely offline.

As implied by figure 2.6, suitable subgraphs are restricted to those having at most four inputs and two outputs which may be limit performance [24]. Furthermore, subgraphs must not contain memory or shift instructions, which constitute a significant proportion of operations (see chapter 3), as they are not supported on the CCA.

Figure 2.7: Architecture of DIM.

## 2.6 Dynamic Instruction Merging

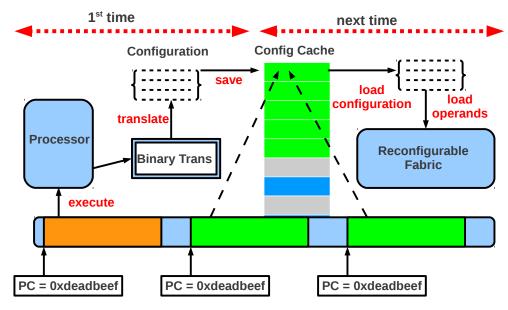

Dynamic Instruction Merging (DIM) [24] (see figure 2.7) dynamically translates executing instructions onto a 2D reconfigurable array of functional units attached to a host processor as an extra functional unit. The translation algorithm, implemented in hardware, detects and transforms instruction groups into microops for execution on the RH.

Translations occur as soon as instructions are fetched and the result is stored in a dedicated configuration cache indexed by the Program Counter (PC). The next time the processor starts fetching the same sequence of instructions the processor loads the previously stored configuration from the cache and the operands from the register bank, then it activates the RFU. The RH now performs the processing and updates the PC, to the end of the sequence, for execution to continue with standard instructions.

DIM makes the RH transparent to executing binaries and can handle dynamically generated code. However, DIM takes up a very significant amount of die area. Furthermore, the binary translation algorithm is simple and fast (as it is implemented in hardware) but misses opportunities for optimising the microops produced. It has been shown that decomposing instructions into microops produces suboptimal internal code sequences [63]. Optimising the internal code sequence is non-trivial and best performed in software instead of hardware [64]. Furthermore, energy is spent translating instruction sequences that contribute little to performance as DIM attempts to translate all instructions.

Custom Reconfigurable Arrays for Multiprocessor System (CReAMS) [33] is the multiprocessor variant of DIM but has a 4-stage pipelined translation unit termed Dynamic Detection Hardware (DDH). As with DIM, the DDH is responsible for detecting and translating instructions. The DDH and its configuration memory are tightly coupled to a 5-stage processor. The host CPU, the RH and the DDH together form the Dynamic Adaptive Processor (DAP). Multiple DAPs were coupled together to form a CMP. CReAMS, like DIM, suffers from high area overhead.

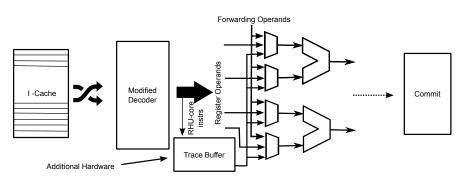

## 2.7 RHU and RIG cores

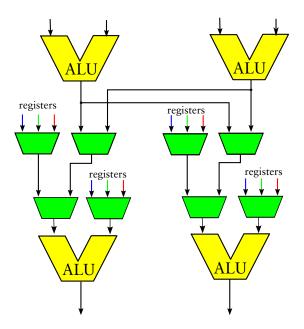

Another project [25, 32] is based on a heterogeneous multiprocessor where each core is either a Reconfigurable Hardware Unit (RHU) or a Reconfiguration Instruction Generation (RIG). A RHU is a superscalar processor augmented with RH. The RIG is based on the same processor as the RHU but with dedicated hardware for reconfigurable configuration generation and without the RH (see figure 2.8). Each RIG services a number of RHUs.

Each RHU collects traces of committed instructions which are dispatched to a RIG for translation. A trace starts whenever a backward branch instruction commits. When a configuration is received from the RIG it is stored at the executing thread address space. When the start of a translated trace is detected it is processed using the RH instead of the standard datapath. Standard execution continues from the original instruction after the end of the translated trace. The RH is a 2D array of functional units that only handles integer ALU and simple memory operations.

A RIG generates a configuration using a combination of hardware and software. Analysis is in hardware with code generation in software that is part of the Operating System (OS).

Figure 2.8: Datapath of a RIG-core.

A 4-core model, a single RIG servicing three RHU, improved per-core performance by an average of 23% [32]. However, the architecture may be too 'complex' for a mobile processor as it uses trace caches which are rare in mobile processors because of area, cost and energy issues.

## 2.8 Summary

This chapter introduced the concept of reconfigurable computing and discussed its advantages and potential issues. Difficulty of programming and diminished binary portability were identified as major barriers to the widespread adoption of RPs. Then, architectures that use dynamic mapping to overcome these drawbacks were reviewed. The merits and demerits of each architecture were discussed. The next chapter is on the quantitative characterization of applications targeting mobile processors with the aim of using the results to guide the design of VIREMENT.

# **3** Application Analysis

## 3.1 Introduction

Application characterisation, the quantitative understanding of workload characteristics, is important to the design of processors. This often involves instrumenting and executing reference applications to generate records and summaries of the time cost of subroutines, algorithms, number of calls etc. The output of application characterisation guides architecture and microarchiecture design.

This chapter is about the characterisation of reference applications, assembled from the Parsec [65], Rodinia [66] and Bots [67] benchmark suites. These applications are described in section 3.2 and summarised in table 3.1. The emphasis is on emerging applications such data mining. Section 3.4 describes how the insights gathered influences the design of VIREMENT.

## 3.2 Application/Kernel Pool

**backprop** Back Propagation [69] is a machine-learning algorithm, implemented in OpenMP, that trains the weights of connecting nodes on a layered neural network. backprop's domain is pattern recognition and is included in this pool because of the increasing importance of pattern recognition applications—such as handwriting recognition—in mobile computing devices.

| A 1° .°       | C       | D '                 | ידין 1 ד    |

|---------------|---------|---------------------|-------------|

| Application   | Suite   | Domain              | Thread Imp. |

| backprop      | Rodinia | Pattern Recognition | OpenMP      |

| bfs           | Rodinia | Graph Algorithms    | OpenMP      |

| bodytrack     | Parsec  | Computer Vision     | Pthreads    |

| facesim       | Parsec  | Physics Simulation  | Pthreads    |

| fib           | Bots    | Integer             | OpenMP      |

| fft           | Bots    | Spectral Transforms | OpenMP      |

| fluidanimate  | Parsec  | Physics Simulation  | TBB         |

| freqmine      | Parsec  | Data Mining         | OpenMp      |

| kmeans        | Rodinia | Data Mining         | OpenMP      |

| nqueens       | Bots    | Search              | OpenMP      |

| pathfinder    | Rodinia | Grid Traversal      | OpenMP      |

| sort          | Bots    | Integer Sorting     | OpenMP      |

| srad          | Rodinia | Image Processing    | OpenMP      |

| streamcluster | Parsec  | Data Mining         | TBB         |

| vips          | Parsec  | Media Processing    | Pthreads    |

| x264          | Parsec  | Media Processing    | Pthreads    |

Table 3.1: Application Pool (TBB refers to Intel Threading Building Blocks [68]).

- **bfs** Breadth-First Search transverses a graph beginning at the root node and then exploring all the neighbouring nodes. Breadth-First Search is used in solving many problems in graph theory.

- bodytrack tracks a human body with multiple cameras through an image sequence. The increasing significance of computer vision algorithms on mobile computing devices, where it is used in character animation and computer interfaces, leads to the inclusion of bodytrack.

- facesim computes a visually realistic animation of a modelled face by simulating the underlying physics [70]. Computer animations increasingly employ physical simulation to create more realistic effects.

- fft computes the one-dimensional Fast Fourier Transform of a vector of n complex values using the divide and conquer Cooley-Tukey [71] algorithm. It was included to represent DSP applications.

fib computes the nth Fibonacci number using recursive paralellization [67]. It

was included to represent recursive algorithms that need to exploit irregular parallelism.

- fluidanimate employs an extension of the Smoothed Particle Hydrodynamics method to simulate an incompressible fluid for interactive animation purposes [72]. It was included in the application pool because of the increasing use of physics simulations for animations.

- freqmine identifies sets of items that often occur together in a given database using the Frequent Pattern-growth method [73]. It was included because of the emerging field of data mining in resource-constrained mobile computing environments [74].

- kmeans k-means is a clustering algorithm used in data mining that aims to partition n observations into k clusters. Each observation belongs to the cluster with the nearest mean. It is used in mobile phone gesture recognition systems [75]

- nqueens computes all solutions of the n-queens problem (finding a placement for n queens on an  $n \times n$  chessboard such that none of the queens attack any other) using a backtracking search algorithm.

- **pathfinder** uses dynamic programming to find a path on a two-dimensional grid from the bottom row to the top row with the smallest accumulated weights i.e. finds the shortest path. It is included because of the importance of mapping applications that find directions between physical locations by finding the shortest path.

- sort is a parallel variation of mergesort [76]. It sorts a random permutation of n 32-bit numbers and was included because sorting is a computational building block of fundamental importance.

- srad Speckle Reducing Anisotropic Diffusion (SRAD) is an algorithm based on partial differential equations for removing the speckles in ultrasound images without sacrificing important image features [77]. It is included in the pool because of the emergence of inexpensive mobile ultrasound using an ultrasound probe connected to a mobile phone [78].

- streamcluster is a kernel that finds a pre-determined number of medians in data streams so that each point is assigned to its nearest centre as it is streamed in [65]. It is part of the application pool because of the increasing importance of data mining algorithms on mobile devices.

- vips is designed for processing images larger than the amount of RAM available on a device [79]. Photo editing applications on mobile-devices are becoming more prevalent.

- x264 is an application for encoding video streams into the H.264/MPEG-4 AVC format [80]. H.264, a standard for video compression, is one of the most commonly used formats for the recording, compression and distribution of high definition video.

## 3.3 Application Characterisation

The applications described in section 3.2 are characterised using a combination of publicly available tools (Intel Software Development Emulator [81], Microarchitecture-Independent Characterization of Applications (MICA) [82]) and custom Pin [83] based tools running on an x86 platform. Pin is a dynamic instrumentation tool for programs. It allows the injection of C or C++ code at arbitrary places in the executable. All instrumentations occur at runtime obviating the need to rewrite binaries.

A major pitfall of application characterisation is that processor microarchitecture could hide underlying, inherent program behaviour [82], hence only microarchitectureindependent application characteristics are measured. The results are presented in sections 3.3.1 to 3.3.6.

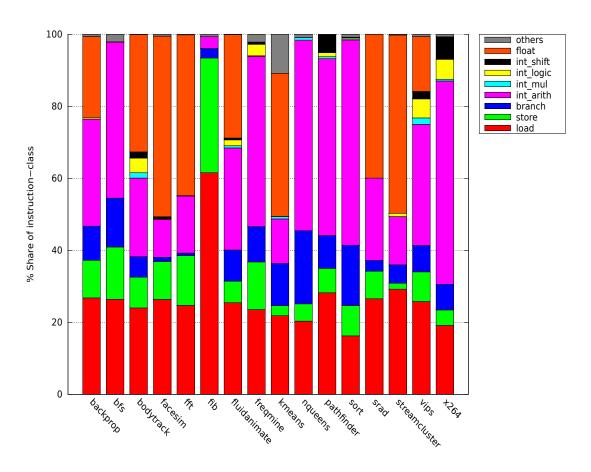

## 3.3.1 Dynamic Instruction Mix

The dynamic instruction mix characterises applications according to the frequency of the different instruction types encountered during execution and serves as a guide to the type of operations to support on the RH. Instructions are classified functionally into 9 groups: load, store, branch, integer arithmetic,

Figure 3.1: Dynamic instruction mix per application.

integer multiplication, logic, shift, floating-point arithmetic and others.

The dynamic instruction mix depends on the application, the compiler, and the processor's instruction set, but not on architectural/hardware parameters of the processor such as the number of execution units, cache sizes, etc.

Figure 3.1 depicts the distribution of the instruction classes while figures 3.2a to 3.2i, on pages 45 to 47, show dynamic instruction mix in more detail by displaying the frequencies for each instruction class individually.

#### 3.3.1.1 Observations

The analysis of the dynamic instruction mix leads to a number of observations. First, 7 of the 16 applications do not have floating-point operations. The rest have

Figure 3.2: Dynamic instruction mix for each individual class.

Figure 3.2: Dynamic instruction mix by class (cont.).

(i) others

Figure 3.2: Dynamic instruction mix by class (cont.).

a significant number of floating point operations with facesim having 50% of its instructions involving floating-point operands.

Another is that the individual share of integer multiplication, logic and shift classes are quite small. The combination of load, store and integer arithmetic/floating-point arithmetic tend to dominate in almost every application.

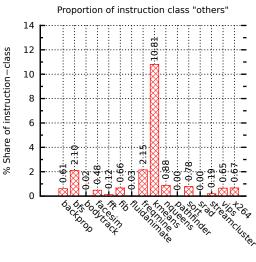

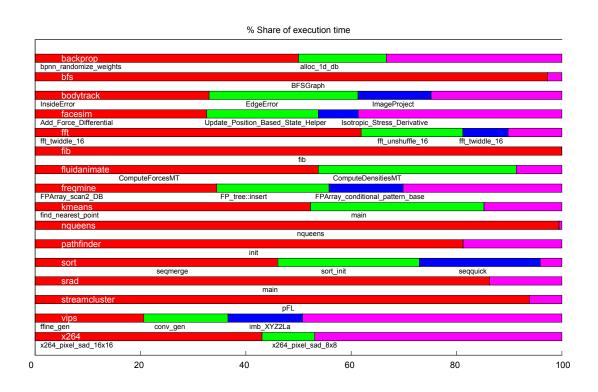

#### 3.3.2 Kernel Profiling

Kernel profiling involves locating the kernels of an application that take most of the execution time. A function breakdown facilitates the identification of kernels in an application. A function breakdown lists all functions of an application together with the relative contribution of each to execution time. Figure 3.3 on page 48 is the function breakdown for the applications in table 3.1. The segments in each bar represent the dominant functions for the application except the rightmost segment which represents the merged shares of all remaining functions. For instance, in vips the dominant functions are fine\_gen, conv\_gen and imb\_XYZ2La with 20.64%, 15.98% and 14.14% of execution time. The rest of the functions represented by the last segment are only 49.24% of execution time.

Figure 3.3: Function breakdown based on execution time.

## 3.3.2.1 Observations

Most applications spend a majority of their execution time inside at most two functions. There are applications, such as fib, where one function dominates. However, even in cases without clear dominant functions (e.g. vips), the two most referenced functions still account for a significant proportion of execution time.

## 3.3.3 Instruction Level Parallelism

ILP refers to the number of individual 'machine' operations executable in parallel. High ILP is important for applications targeting highly-parallel RH.

To characterize the degree of ILP within each application, an idealised outof-order processor model is considered. Architectural features are idealised and unlimited (perfect caches, perfect branch prediction, infinite number of functional units, etc.) except for the instruction window size. ILP is measured in terms of Instructions Per Cycle (IPC). Figure 3.4, on page 50, shows the IPCs at window size of 32, 64, 128 and 256 in-flight instructions.

#### 3.3.3.1 Observations

As expected, streaming (e.g. x264) and related applications (e.g. streamcluster) characterised by compute-intensive numerical code—tend to have relatively high ILP. Common and important computer science algorithms such sorting (in sort) tend to have relatively low ILP.

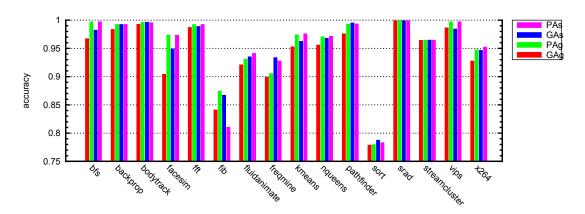

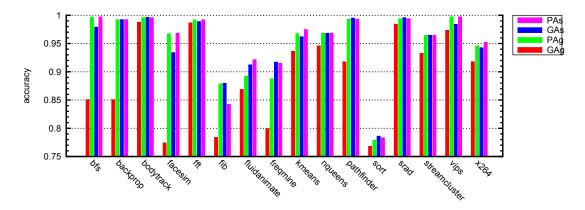

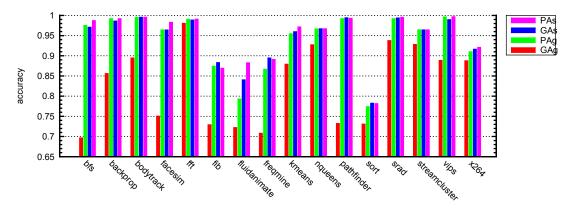

## 3.3.4 Branch Predictability

Branch predictability refers to how accurately future branch behaviour can be foreseen. This is important as the amount of ILP within a basic block is usually not enough to keep typical RH fully utilized. Hence, an increasing number of reconfigurable systems [24] speculate across branches. The predictability of branches determines how accurate and efficient speculation as an execution strategy will be.

The predictor used here is the Prediction by Partial Matching (PPM) predictor [84]. This allows the capture of branch predictability in a microarchitectureindependent manner as a PPM predictor can be viewed as a theoretical basis for branch prediction rather than an actual hardware predictor [82]. Four variations of the PPM predictor are considered: *GAg*, *PAg*, *GAs* and *PAs*. 'G' is global branch history, 'P' is per-address or local branch history, 'g' is one global predictor table for all branches and 's' is separate tables per branch. The accuracy of the 4 variations of the PPM using different history lengths are given in figure 3.5 on page 51.

#### 3.3.4.1 Observations

The branch behaviour of most applications is predictable (over 90% of the predictions are correct), with a variety of prediction schemes. However, there are a few exceptions such as sort with accuracy level of less than 80% across all prediction schemes used. The GAg scheme accuracy level tends always to lag the

Figure 3.4: Scaled IPC for idealised processor window sizes 32, 64, 128, 256.

(a) Branch prediction accuracy using predictors with 12 bits history.

(b) Branch prediction accuracy using predictors with 8 bits history.

(c) Branch prediction accuracy using predictors with 4 bits history.

Figure 3.5: Accuracy for the 4 variations of the PPM with history lengths (12, 8, 4).

other 3 schemes and there is little difference in terms of accuracy among the other 3 schemes.

#### 3.3.5 Memory Reuse Distances

Caching frequently used data in smaller, local buffers near the RH is essential as it reduces the access time to data [50]. The efficacy of caching depends on the principle of locality of reference. The locality of reference in any application can be quantified using the memory reuse distance. Quantifying the locality of references enables the determination of the appropriate size for the local buffers.

Memory reuse distance is the number of distinct data element references between two references to the same data element. It allows the quantitative comparison of the locality of applications that is not tied to any particular buffer design.

Address traces are obtained using MICA [82]. In MICA, reuse distances are limited to memory reads and are evaluated as follows. The address space is divided into 64-byte memory blocks. For each memory read, the corresponding 64-byte memory block is determined. Reuse distance is the number of distinct 64-byte memory blocks referenced between two references to the same block. The reuse distances for all memory reads are then sorted into 19 buckets. Each bucket captures distances within  $[2^n, 2^{(n+1)}]$  64-byte block with *n* ranging from 0 to 18. The first captures reuse distances of [1, 2] while the last actually captures  $[2^{18}, \infty]$ . For example, the fourth bucket corresponds to accesses with reuse distance between  $2^3$  and  $2^4$  blocks.

Table 3.2 on page 53 shows the probability of reads to the same address having a particular reuse distance. For instance, the probability of two memory reads to the same data element in backprop having a reuse distance between  $2^0$  and  $2^1$  is 0.50. Note that the probabilities in the table do not add up to 1 as cold references (data elements referenced only once) are not shown in the table. Furthermore, some of the probabilities are so small that they are shown as 0.00. Columns where all rows are 0.00 are not shown in the table.

| Buckets      |        |        |        |        |        |        |        |        |          |               |

|--------------|--------|--------|--------|--------|--------|--------|--------|--------|----------|---------------|

| Benchmark    | [0, 1[ | [1, 2[ | [2, 3[ | [3, 4[ | [4, 5[ | [5, 6[ | [6, 7[ | [7, 8[ | [11, 12[ | $[18,\infty[$ |

| backprop     | 0.50   | 0.09   | 0.04   | 0.13   | 0.17   | 0.02   | 0.00   | 0.00   | 0.00     |               |

| bfs          | 0.56   | 0.09   | 0.11   | 0.05   | 0.06   | 0.06   | 0.07   | 0.00   |          |               |

| bodytrack    | 0.66   | 0.11   | 0.11   | 0.05   | 0.03   | 0.01   | 0.01   | 0.00   |          |               |

| facesim      | 0.68   | 0.07   | 0.08   | 0.07   | 0.03   | 0.02   | 0.02   | 0.01   | 0.00     |               |

| fib          | 0.58   | 0.08   | 0.11   | 0.09   | 0.03   | 0.04   | 0.04   | 0.01   | 0.00     |               |

| fluidanimate | 0.58   | 0.13   | 0.15   | 0.04   | 0.04   | 0.03   | 0.02   | 0.00   | 0.00     |               |