# DATA CENTRIC AND ADAPTIVE SOURCE CHANGING TRANSACTIONAL MEMORY WITH EXIT FUNCTIONALITY

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2012

By Herath Mudiyanselage Isuru Prasenajith Herath School of Computer Science

## Contents

| Al | bstrac | et       |                                      | 12 |

|----|--------|----------|--------------------------------------|----|

| De | eclara | tion     |                                      | 13 |

| Co | opyri  | ght      |                                      | 14 |

| Ac | cknov  | vledgen  | ients                                | 15 |

| 1  | Intr   | oductio  | 'n                                   | 17 |

|    | 1.1    | Contri   | butions                              | 22 |

|    | 1.2    | Thesis   | Structure                            | 23 |

|    | 1.3    | Public   | ations                               | 25 |

| 2  | Tra    | nsaction | nal Memory                           | 26 |

|    | 2.1    | Introd   | uction                               | 26 |

|    | 2.2    | TM D     | esign Considerations                 | 28 |

|    |        | 2.2.1    | Concurrency Control                  | 28 |

|    |        | 2.2.2    | Version Management                   | 29 |

|    |        | 2.2.3    | Conflict Detection                   | 29 |

|    | 2.3    | TM Se    | emantics                             | 30 |

|    |        | 2.3.1    | Serializability                      | 30 |

|    |        | 2.3.2    | Strict Serializability               | 31 |

|    |        | 2.3.3    | Linearizability                      | 31 |

|    |        | 2.3.4    | Weak Isolation                       | 31 |

|    |        | 2.3.5    | Strong Isolation                     | 31 |

|    |        | 2.3.6    | Single Lock Atomicity                | 32 |

|    |        | 2.3.7    | Disjoint Lock Atomicity              | 32 |

|    |        | 2.3.8    | Transactional Sequential Consistency | 32 |

|        |                                                           | 2.3.9                                                                                                | Nested Transactions                                                                                                                                                                                                                                                                                            | 33                                                                                 |

|--------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|        |                                                           |                                                                                                      | 2.3.9.1 Flattened Nesting                                                                                                                                                                                                                                                                                      | 33                                                                                 |

|        |                                                           |                                                                                                      | 2.3.9.2 Closed Nesting                                                                                                                                                                                                                                                                                         | 33                                                                                 |

|        |                                                           |                                                                                                      | 2.3.9.3 Open Nesting                                                                                                                                                                                                                                                                                           | 33                                                                                 |

|        | 2.4                                                       | TM Pe                                                                                                | rformance Considerations                                                                                                                                                                                                                                                                                       | 34                                                                                 |

|        |                                                           | 2.4.1                                                                                                | Non-blocking Synchronization                                                                                                                                                                                                                                                                                   | 34                                                                                 |

|        |                                                           | 2.4.2                                                                                                | Contention Management                                                                                                                                                                                                                                                                                          | 34                                                                                 |

|        |                                                           | 2.4.3                                                                                                | Early Release                                                                                                                                                                                                                                                                                                  | 35                                                                                 |

|        | 2.5                                                       | Progra                                                                                               | mming with TM $\ldots$                                                                                                                                                                                                                                                                                         | 35                                                                                 |

|        |                                                           | 2.5.1                                                                                                | Composability                                                                                                                                                                                                                                                                                                  | 35                                                                                 |

|        |                                                           | 2.5.2                                                                                                | Conditional Synchronization                                                                                                                                                                                                                                                                                    | 36                                                                                 |

|        |                                                           | 2.5.3                                                                                                | Memory Allocation                                                                                                                                                                                                                                                                                              | 36                                                                                 |

|        |                                                           | 2.5.4                                                                                                | Transactions Everywhere                                                                                                                                                                                                                                                                                        | 37                                                                                 |

|        | 2.6                                                       | Hardw                                                                                                | are Transactional Memory                                                                                                                                                                                                                                                                                       | 38                                                                                 |

|        | 2.7                                                       | Softwa                                                                                               | re Transactional Memory                                                                                                                                                                                                                                                                                        | 46                                                                                 |

|        | 2.8                                                       | Hybrid                                                                                               | I Transactional Memory                                                                                                                                                                                                                                                                                         | 48                                                                                 |

|        | 2.0                                                       | Cumana                                                                                               | ary                                                                                                                                                                                                                                                                                                            | 49                                                                                 |

|        | 2.9                                                       | Summa                                                                                                |                                                                                                                                                                                                                                                                                                                | 17                                                                                 |

|        | 2.9                                                       | Summa                                                                                                |                                                                                                                                                                                                                                                                                                                | 12                                                                                 |

| T      |                                                           |                                                                                                      |                                                                                                                                                                                                                                                                                                                | -                                                                                  |

| Ι      |                                                           |                                                                                                      | Data Centric Transactional Memory                                                                                                                                                                                                                                                                              | 50                                                                                 |

| I<br>3 | Da                                                        | CTM:                                                                                                 |                                                                                                                                                                                                                                                                                                                | 50                                                                                 |

|        | Da                                                        | CTM:<br>CTM: Da                                                                                      | Data Centric Transactional Memory                                                                                                                                                                                                                                                                              | 50<br>51                                                                           |

|        | Da<br>DaC                                                 | <b>CTM:</b><br>C <b>TM: D</b> a<br>Introdu                                                           | Data Centric Transactional Memory<br>ata Centric Transactional Memory                                                                                                                                                                                                                                          | <b>50</b><br><b>51</b><br>51                                                       |

|        | <b>Da</b><br><b>Da</b><br>3.1                             | <b>CTM:</b><br><b>CTM: D:</b><br>Introdu<br>Motiva                                                   | Data Centric Transactional Memory         ata Centric Transactional Memory         action                                                                                                                                                                                                                      | <b>50</b><br><b>51</b><br>51<br>53                                                 |

|        | <b>Da</b><br><b>Da</b><br>3.1<br>3.2                      | <b>CTM:</b><br><b>CTM: D:</b><br>Introdu<br>Motiva                                                   | Data Centric Transactional Memory         ata Centric Transactional Memory         action         ation                                                                                                                                                                                                        | <b>50</b><br><b>51</b><br>51<br>53                                                 |

|        | <b>Da</b><br><b>Da</b><br>3.1<br>3.2                      | <b>CTM:</b><br><b>DATE:</b><br>TM: Da<br>Introdu<br>Motiva<br>DaCTM                                  | Data Centric Transactional Memory         ata Centric Transactional Memory         action         ation         M Concept                                                                                                                                                                                      | <b>50</b><br><b>51</b><br>51<br>53<br>57                                           |

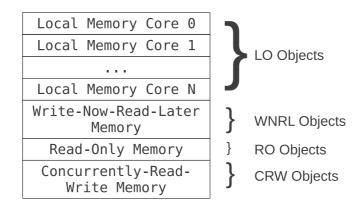

|        | <b>Da</b><br><b>Da</b><br>3.1<br>3.2                      | CTM: Da<br>TM: Da<br>Introdu<br>Motiva<br>DaCTN<br>3.3.1                                             | Data Centric Transactional Memory         ata Centric Transactional Memory         action                                                                                                                                                                                                                      | <b>50</b><br><b>51</b><br>51<br>53<br>57<br>57<br>58                               |

|        | <b>Da</b><br><b>Da</b><br>3.1<br>3.2                      | CTM: Da<br>Introdu<br>Motiva<br>DaCTN<br>3.3.1<br>3.3.2                                              | Data Centric Transactional Memory         ata Centric Transactional Memory         action                                                                                                                                                                                                                      | <b>50</b><br><b>51</b><br>51<br>53<br>57<br>57<br>58<br>58                         |

|        | <b>Da</b><br><b>Da</b><br>3.1<br>3.2                      | <b>CTM: Da</b><br>Introdu<br>Motiva<br>DaCTN<br>3.3.1<br>3.3.2<br>3.3.3                              | Data Centric Transactional Memory         ata Centric Transactional Memory         action         ation         M Concept         Local (LO)         Read Only (RO)         Concurrently Read and Write (CRW)                                                                                                  | <b>50</b><br><b>51</b><br>51<br>53<br>57<br>57<br>58<br>58                         |

|        | <b>Da</b><br><b>Da</b><br>3.1<br>3.2                      | CTM: Da<br>Introdu<br>Motiva<br>DaCTN<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5                   | Data Centric Transactional Memory         ata Centric Transactional Memory         action         ation         M Concept         Local (LO)         Read Only (RO)         Concurrently Read and Write (CRW)         Write Now Read Later (WNRL)                                                              | <b>50</b><br><b>51</b><br>53<br>57<br>57<br>58<br>58<br>59<br>61                   |

|        | <b>Da</b> (<br><b>Da</b> (<br>3.1<br>3.2<br>3.3           | CTM: Da<br>Introdu<br>Motiva<br>DaCTN<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>DaCTN          | Data Centric Transactional Memory         ata Centric Transactional Memory         action                                                                                                                                                                                                                      | <b>50</b><br><b>51</b><br>51<br>53<br>57<br>57<br>58<br>58<br>58                   |

|        | <b>Da</b><br><b>Da</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | CTM: Da<br>Introdu<br>Motiva<br>DaCTN<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>DaCTN<br>Summa | Data Centric Transactional Memory         ata Centric Transactional Memory         action         ation         M Concept         Local (LO)         Read Only (RO)         Concurrently Read and Write (CRW)         Write Now Read Later (WNRL)         Object Operation         M Special Cases             | <b>50</b><br><b>51</b><br>51<br>53<br>57<br>57<br>58<br>58<br>59<br>61<br>67<br>70 |

| 3      | <b>Da</b><br><b>Da</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | CTM: Da<br>Introdu<br>Motiva<br>DaCTN<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>DaCTN<br>Summa | Data Centric Transactional Memory         ata Centric Transactional Memory         action         ation         M Concept         Local (LO)         Read Only (RO)         Concurrently Read and Write (CRW)         Write Now Read Later (WNRL)         Object Operation         M Special Cases         ary | <b>50</b><br><b>51</b><br>53<br>57<br>57<br>58<br>58<br>59<br>61<br>67             |

|   |     | 4.2.1   | LO Memory                                                 | 73  |

|---|-----|---------|-----------------------------------------------------------|-----|

|   |     | 4.2.2   | RO, WNRL and CRW Memory                                   | 74  |

|   |     | 4.2.3   | Region Information Table                                  | 74  |

|   |     | 4.2.4   | Modifed Translation Lookaside Buffer                      | 75  |

|   | 4.3 | DaCTI   | M support for Transactional Memory                        | 75  |

|   |     | 4.3.1   | Basic TM System                                           | 75  |

|   |     | 4.3.2   | DaCTM                                                     | 78  |

|   |     | 4.3.3   | Hardware Signatures in DaCTM                              | 79  |

|   | 4.4 | Incorp  | orating Memory Regions with Transactional Memory in DaCTM | 80  |

|   | 4.5 | DaCTI   | M-CS                                                      | 82  |

|   | 4.6 | DaCTI   | M-U                                                       | 84  |

|   | 4.7 | Summ    | ary                                                       | 85  |

| 5 | DaC | TM Ev   | aluation                                                  | 86  |

|   | 5.1 |         | tion Environment                                          | 86  |

|   | 5.2 |         | marks Tested                                              | 87  |

|   |     | 5.2.1   | Genome                                                    | 87  |

|   |     | 5.2.2   | Intruder                                                  | 87  |

|   |     | 5.2.3   | Kmeans                                                    | 88  |

|   |     | 5.2.4   | Labyrinth                                                 | 88  |

|   |     | 5.2.5   | Ssca2                                                     | 88  |

|   |     | 5.2.6   | Vacation                                                  | 88  |

|   |     | 5.2.7   | Lee-TM                                                    | 89  |

|   | 5.3 | Evalua  | tion Setup                                                | 89  |

|   |     | 5.3.1   | Building Complete System                                  | 90  |

|   |     | 5.3.2   | Building Transactional Memory Support                     | 90  |

|   |     | 5.3.3   | Support for Memory Regions                                | 91  |

|   |     | 5.3.4   | Evaluation Procedure                                      | 92  |

|   | 5.4 | Perform | mance                                                     | 92  |

|   | 5.5 | Charac  | cterization of DaCTM                                      | 97  |

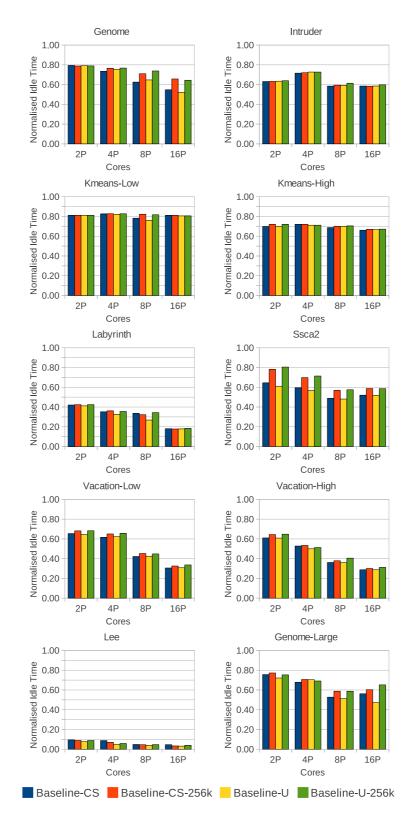

|   |     | 5.5.1   | Idle Time                                                 | 98  |

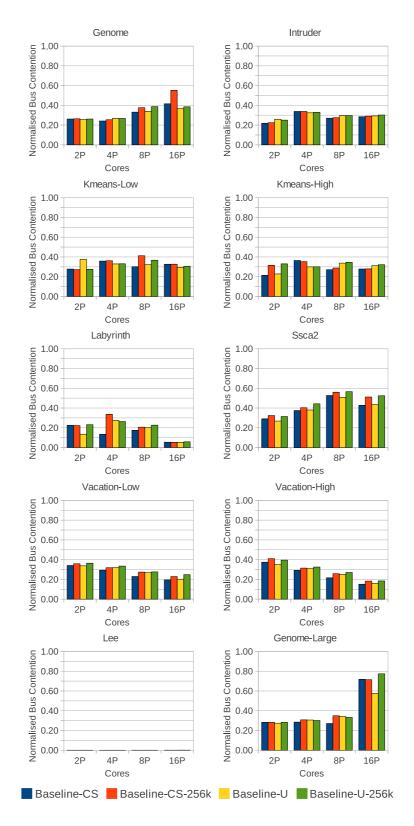

|   |     | 5.5.2   | Bus Contention                                            | 100 |

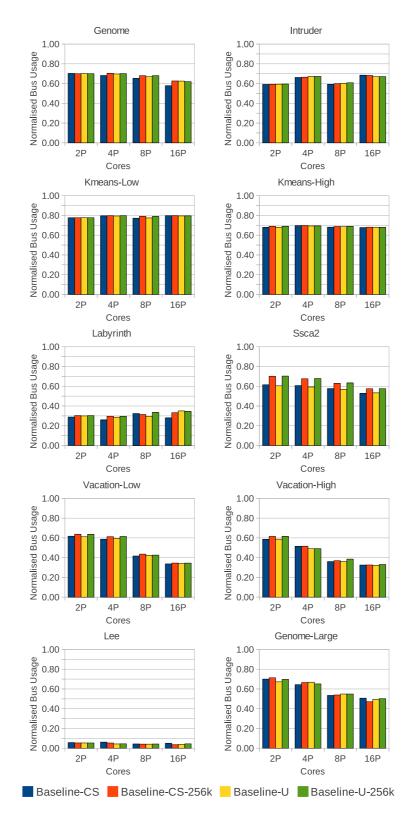

|   |     | 5.5.3   | Bus Usage                                                 | 102 |

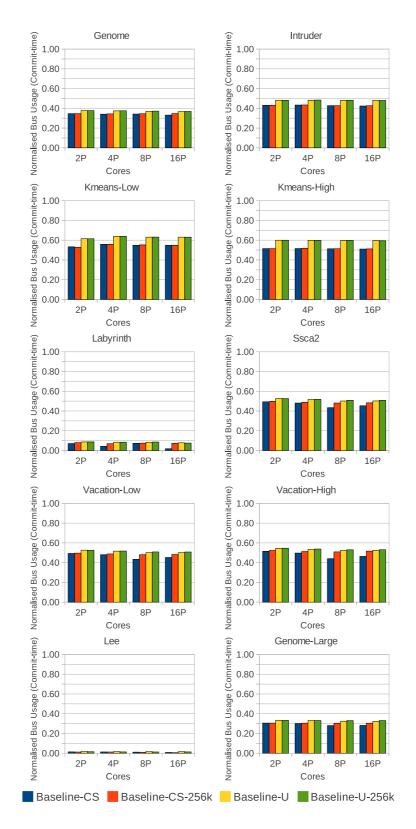

|   |     | 5.5.4   | Commit Phase Bus Usage                                    | 104 |

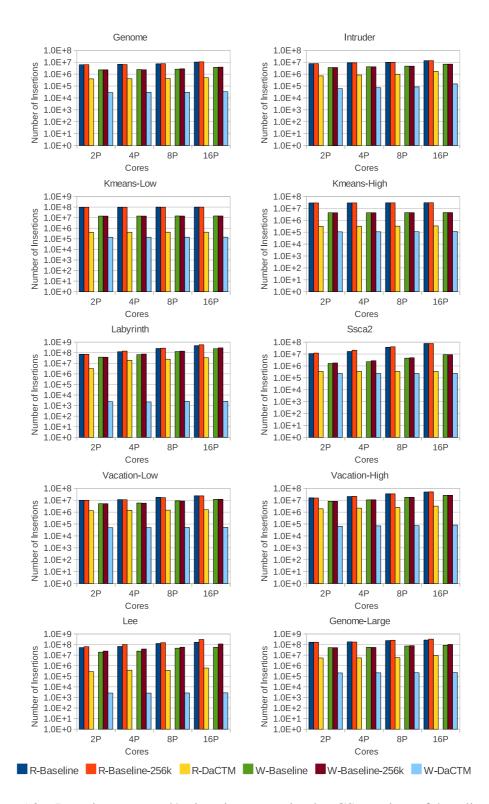

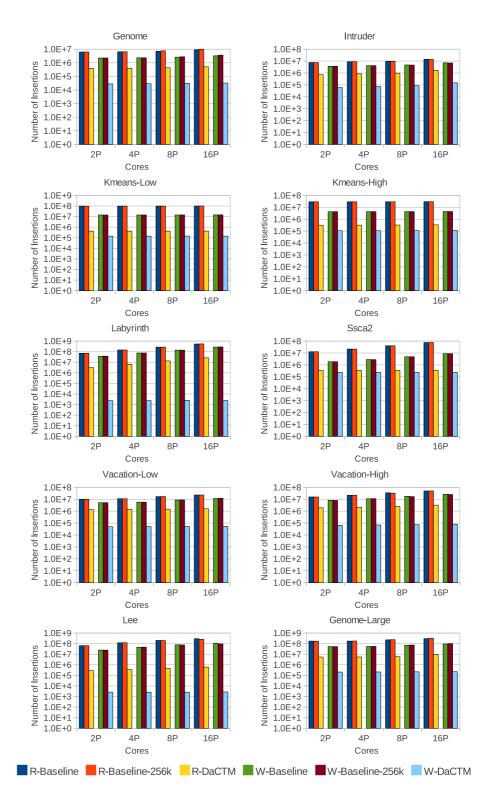

|   |     | 5.5.5   | Signature Insertions                                      | 106 |

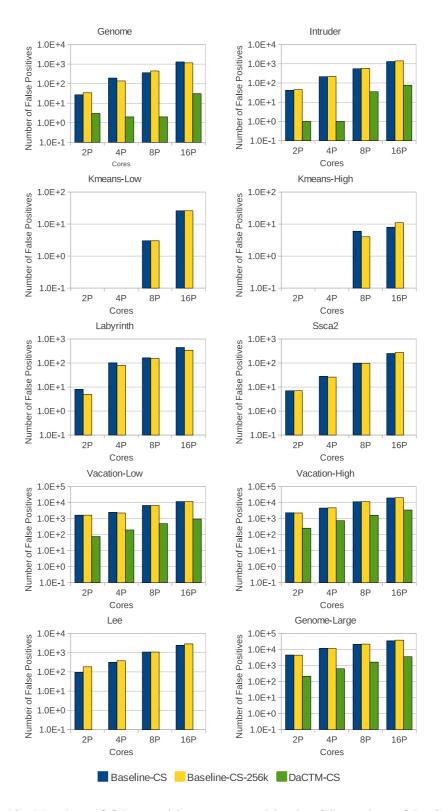

|   |     | 5.5.6   | False Positives                                           | 109 |

|         | 5.6  | Summary                                                                                          | 113 |

|---------|------|--------------------------------------------------------------------------------------------------|-----|

| 6       | Rela | ated Work on DaCTM                                                                               | 114 |

|         | 6.1  | Data Centric Synchronization                                                                     | 114 |

|         | 6.2  | Cache Coherence                                                                                  | 116 |

|         | 6.3  | Memory Consistency                                                                               | 120 |

|         | 6.4  | Data Separation in Transactional Memory                                                          | 122 |

|         | 6.5  | Memory Management                                                                                | 125 |

| II<br>C |      | nCTM: Reducing False Transaction Aborts by Adaptively<br>ging the Source of Conflict Detection 1 | 27  |

| 7       | SnC  | <b>CTM: Adaptive Sources for Conflict Detection</b>                                              | 128 |

|         | 7.1  | Introduction                                                                                     | 128 |

|         | 7.2  | Motivation                                                                                       | 130 |

|         | 7.3  | Related Work on Hardware Signatures                                                              | 133 |

|         | 7.4  | SnCTM Concept                                                                                    | 138 |

|         | 7.5  | Summary                                                                                          | 140 |

| 8       | SnC  | CTM Implementation and Evaluation                                                                | 141 |

|         | 8.1  | SnCTM Architecture                                                                               | 141 |

|         |      | 8.1.1 Baseline Architecture                                                                      | 141 |

|         |      | 8.1.2 SnCTM Design                                                                               | 144 |

|         | 8.2  | Evaluation                                                                                       | 145 |

|         |      | 8.2.1 Evaluation Setup                                                                           | 146 |

|         |      | 8.2.2 Performance                                                                                | 148 |

|         |      | 8.2.3 Characterization of SnCTM                                                                  | 150 |

|         |      | 8.2.4 Sensitivity Analysis                                                                       | 156 |

|         | 8.3  | Summary                                                                                          | 161 |

|         | _    |                                                                                                  |     |

# IIITM\_EXIT: Exiting a Transaction In the Context of Hard-<br/>ware Transactional Memory162

| 9 | TM_EXIT: A Case for Exiting a Transaction |                           |     |  |

|---|-------------------------------------------|---------------------------|-----|--|

|   | 9.1                                       | Introduction              | 163 |  |

|   | 9.2                                       | Motivation for TM_RESTART | 165 |  |

|    | 9.3  | Motivation for TM_EXIT                                    | 166 |

|----|------|-----------------------------------------------------------|-----|

|    |      | 9.3.1 Lee-TM [108]                                        | 167 |

|    |      | 9.3.2 Red-Black Tree                                      | 168 |

|    |      | 9.3.3 Java Exceptions                                     | 169 |

|    | 9.4  | Performance Impact                                        | 170 |

|    | 9.5  | Defining and Using TM_EXIT                                | 171 |

|    |      | 9.5.1 Integrating TM_EXIT to Existing Applications        | 171 |

|    |      | 9.5.2 Implicit Control Transfer with TM_EXIT              | 173 |

|    |      | 9.5.3 Incorrect Usage of TM_EXIT                          | 174 |

|    |      | 9.5.4 Increasing Expressiveness With TM_EXIT              | 175 |

|    | 9.6  | Summary                                                   | 176 |

| 10 | Impl | lementation and Evaluation of TM_EXIT                     | 177 |

|    | -    | Architectural support for TM_EXIT                         | 177 |

|    |      | 10.1.1 Requirements for TM_EXIT                           | 178 |

|    |      |                                                           | 179 |

|    |      | 10.1.3 Baseline-2: TM-U                                   | 180 |

|    | 10.2 | Evaluation                                                | 181 |

|    |      | 10.2.1 Evaluation Setup                                   | 181 |

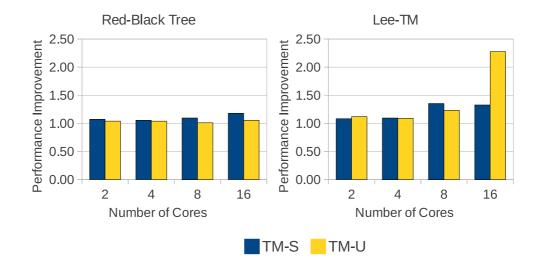

|    |      | 10.2.2 Performance                                        | 182 |

|    |      | 10.2.3 Characterisation of TM_EXIT                        | 182 |

|    |      | 10.2.4 Performance Evaluation of Increased Expressiveness | 186 |

|    | 10.3 | Summary                                                   | 189 |

| 11 | Rela | ted Work on TM_EXIT                                       | 190 |

|    |      | Software Approaches                                       | 190 |

|    |      | Hardware Approaches                                       | 192 |

|    |      | Applicability of TM_EXIT on other TM Systems              | 194 |

|    |      | Summary                                                   | 195 |

|    |      |                                                           |     |

| 12 |      | clusions and Future Work                                  | 196 |

|    |      | Data Centric Transactional Memory                         | 196 |

|    |      | Adaptive Sources for Conflict Detection                   | 198 |

|    | 12.3 | Exiting a Transaction without Committing                  | 200 |

#### Bibliography

202

Word Count: 57081

## **List of Tables**

| 3.1  | Determining the <i>type</i> of a method when operating on mix of data              | 63  |

|------|------------------------------------------------------------------------------------|-----|

| 3.2  | Operations to perform for each data type                                           | 63  |

| 4.1  | Instructions to be used in a naive DaCTM design                                    | 72  |

| 5.1  | Benchmark applications and their inputs used for evaluating DaCTM .                | 89  |

| 5.2  | Components and features of the DaCTM evaluation environment                        | 90  |

| 8.1  | Components and features of the SnCTM evaluation environment                        | 147 |

| 8.2  | Benchmark applications and their inputs used for evaluating SnCTM .                | 147 |

| 8.3  | Average performance improvement of SnCTM over baseline                             | 150 |

| 9.1  | Non-useful commits                                                                 | 170 |

| 10.1 | Components and features of the $\texttt{TM}\_\texttt{EXIT}$ evaluation environment | 182 |

| 10.2 | Usage of TM_EXIT as a percentage of total commits                                  | 183 |

| 10.3 | Bytes committed per transaction                                                    | 184 |

| 10.4 | Threshold configurations for Linked-list                                           | 186 |

| 10.5 | Number of times the overflow area is accessed in the Linked-list ap-               |     |

|      | plication that uses TM_EXIT                                                        | 189 |

|      |                                                                                    |     |

## **List of Figures**

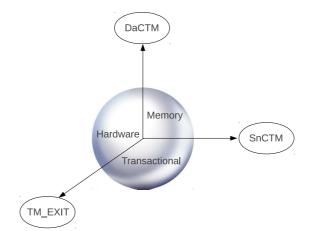

| 1.1  | Contributions of the Thesis                                           | 23 |

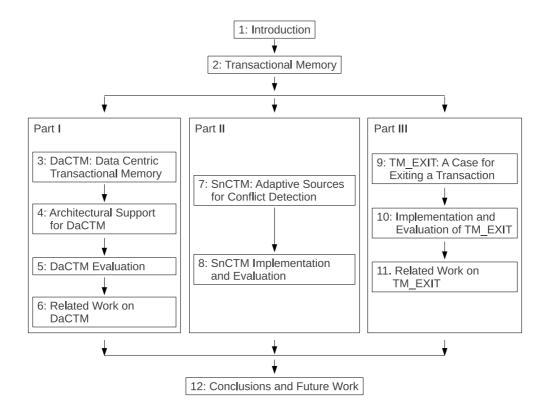

|------|-----------------------------------------------------------------------|----|

| 1.2  | Suggested reading structure of the Thesis                             | 25 |

| 3.1  | Example use of the <i>private</i> keyword in OpenMP                   | 54 |

| 3.2  | Example use of the <i>final</i> keyword in Java                       | 55 |

| 3.3  | Example use of the <i>synchronized</i> keyword in Java                | 56 |

| 3.4  | A pseudocode of a Producer-Consumer application                       | 56 |

| 3.5  | A memory allocation request that can be considered as LO              | 58 |

| 3.6  | A memory allocation request that can be considered as RO              | 58 |

| 3.7  | A memory allocation request that can be considered as CRW             | 59 |

| 3.8  | A memory allocation request that can be considered as WNRL            | 60 |

| 3.9  | DaCTM memory regions                                                  | 62 |

| 3.10 | Proposed memory allocation function in DaCTM                          | 62 |

| 3.11 | Working with explicitly defined transactions in DaCTM                 | 64 |

| 3.12 | A Chain of functions taken from Barnes application of SPLASH [109]    | 64 |

| 3.13 | Nested transactions for chain functions in DaCTM                      | 65 |

| 3.14 | Committing before starting another function when operating with chain |    |

|      | functions in DaCTM                                                    | 66 |

| 3.15 | Pseudocode of the Lee-TM [108] application                            | 67 |

| 3.16 | DaCTM approach to avoid the violation of TM semantics                 | 68 |

| 3.17 | A library function used in copying vectors                            | 69 |

| 3.18 | DaCTM approach to allocate memory inside a library function           | 69 |

| 4.1  | A code segment for totalling an array                                 | 72 |

| 4.2  | DaCTM memory hierarchy and mapping of memory regions                  | 74 |

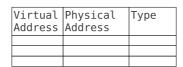

| 4.3  | Proposed Region Information Table (RIT) in DaCTM                      | 75 |

| 4.4  | Modified TLB used in DaCTM                                            | 75 |

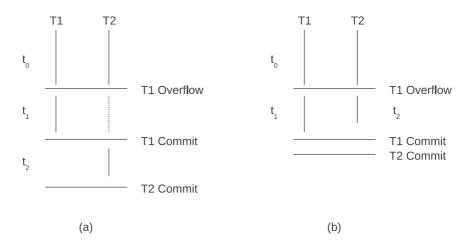

| 4.5  | Difference between the original TCC and the improved TCC (which is    |     |

|------|-----------------------------------------------------------------------|-----|

|      | used as baseline)                                                     | 77  |

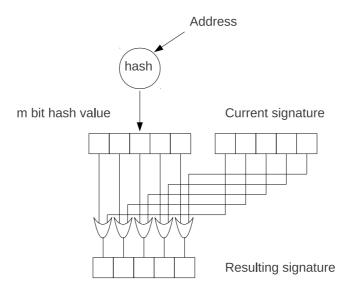

| 4.6  | Inserting an address to a signature                                   | 79  |

| 4.7  | Signature operations used in DaCTM                                    | 80  |

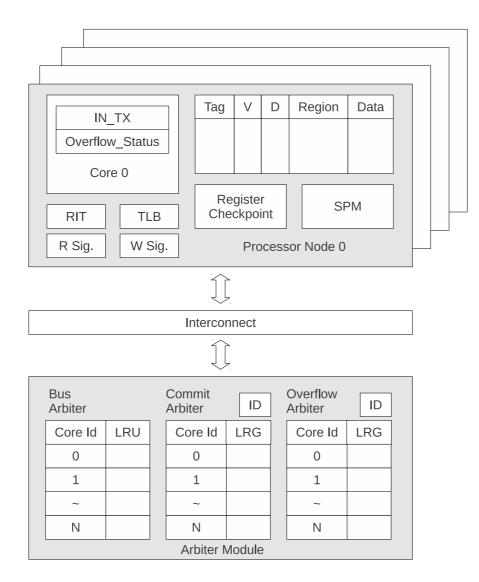

| 4.8  | A complete DaCTM-CS system                                            | 82  |

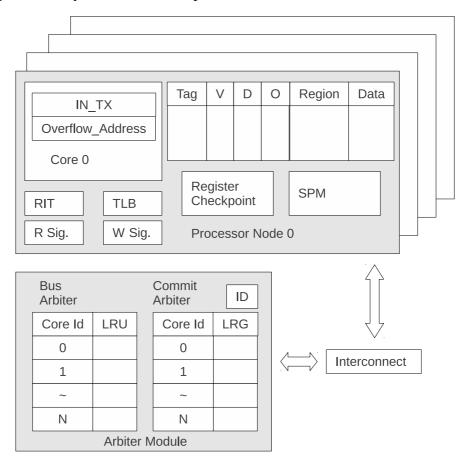

| 4.9  | A complete DaCTM-U system                                             | 84  |

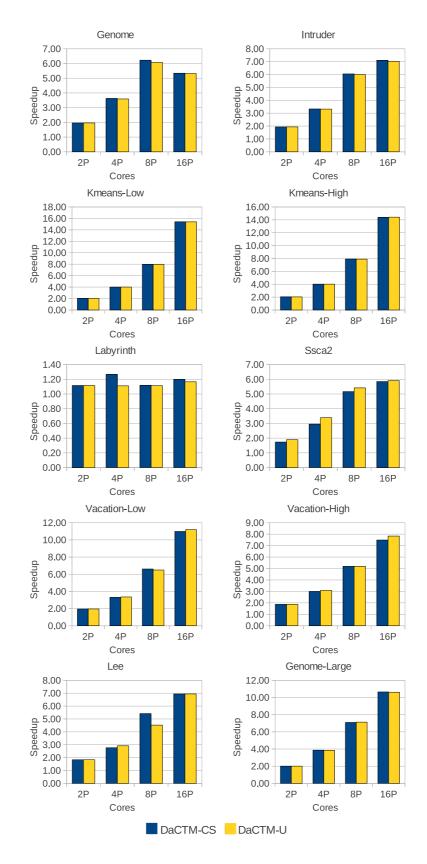

| 5.1  | Scalability of DaCTM                                                  | 93  |

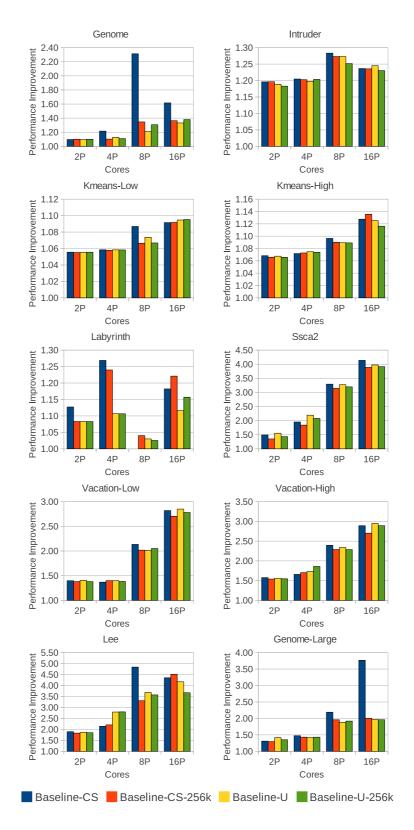

| 5.2  | Performance improvement of DaCTM over baseline architectures          | 95  |

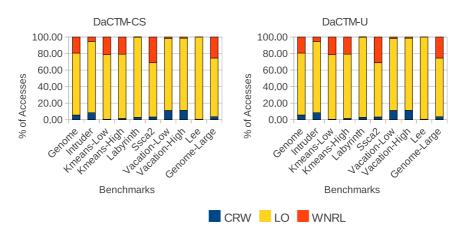

| 5.3  | Percentage of LO, WNRL and CRW data types in both DaCTM archi-        |     |

|      | tectures                                                              | 97  |

| 5.4  | DaCTM idle time normalised to baseline                                | 99  |

| 5.5  | DaCTM bus contention normalised to baseline                           | 101 |

| 5.6  | DaCTM bus usage normalised to baseline                                | 103 |

| 5.7  | DaCTM commit phase bus usage normalised to baseline                   | 105 |

| 5.8  | Insertions to read/write signatures in the CS version of baseline and |     |

|      | DaCTM                                                                 | 107 |

| 5.9  | Insertions to read/write signatures in the U version of baseline and  |     |

|      | DaCTM                                                                 | 108 |

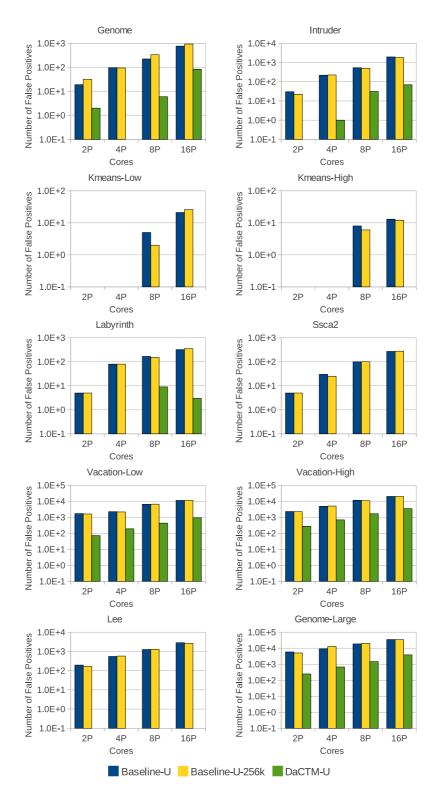

| 5.10 | Number of false positives presented in the CS version of DaCTM and    |     |

|      | baselines                                                             | 110 |

| 5.11 | Number of false positives presented in the U version of DaCTM and     |     |

|      | baselines                                                             | 111 |

| 6.1  | An example of using data centric approach for synchronization (taken  |     |

|      | from [106])                                                           | 115 |

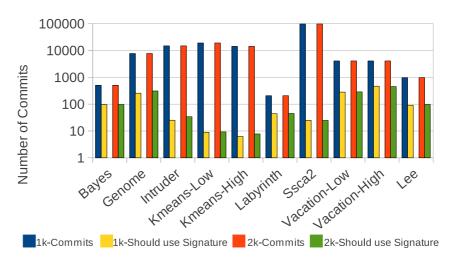

| 7.1  | Signature requirement for transactions committed                      | 131 |

| 7.2  | False aborts that could have been avoided                             | 132 |

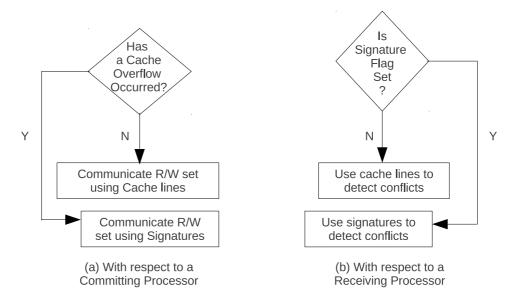

| 7.3  | The concept of SnCTM                                                  | 139 |

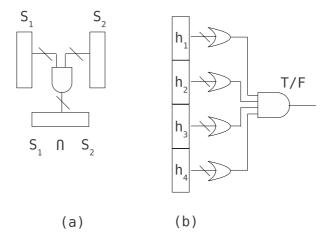

| 8.1  | Signature operations used in SnCTM                                    | 142 |

| 8.2  | A complete SnCTM system                                               | 144 |

| 8.3  | Adaptively checking for conflicts in a SnCTM processor                | 146 |

| 8.4  | Performance improvement of SnCTM over the baseline                    | 149 |

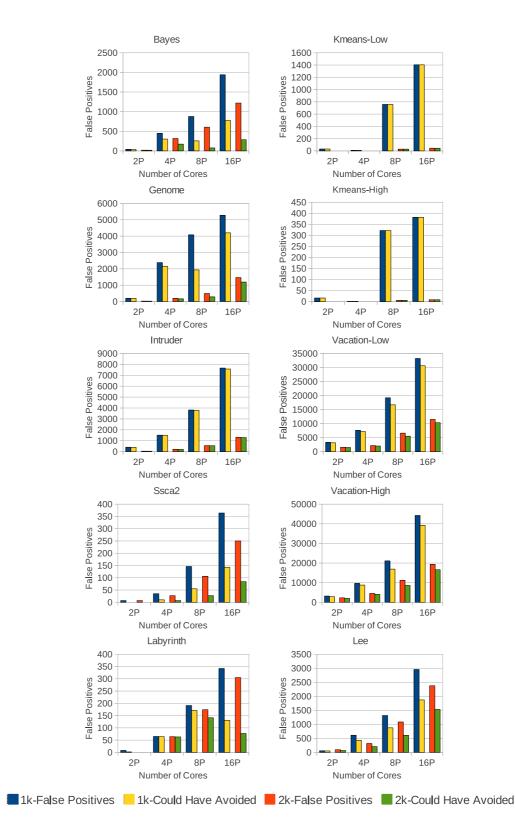

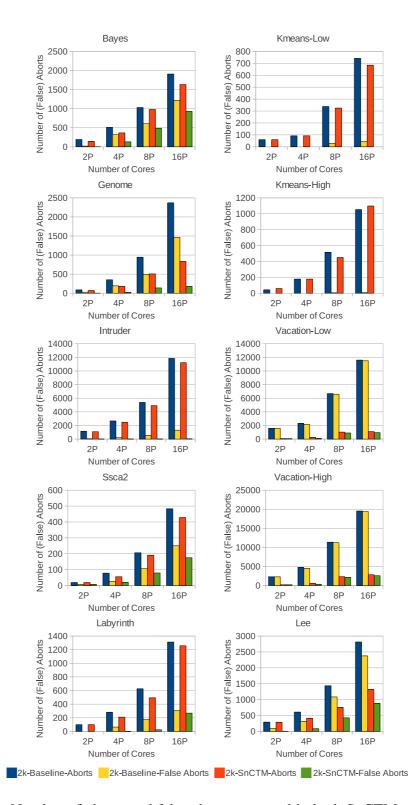

| 8.5  | Number of aborts and false aborts occurred in both SnCTM and baseline |     |

|      | with a 1024 bit signature                                             | 152 |

| 8.6        | Number of aborts and false aborts occurred in both SnCTM and baseline                    |            |

|------------|------------------------------------------------------------------------------------------|------------|

|            | with a 2048 bit signature                                                                | 153        |

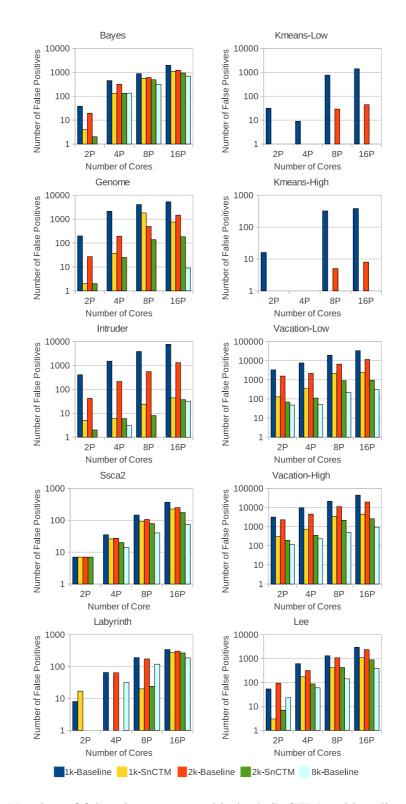

| 8.7        | Number of false aborts occurred in both SnCTM and baseline with 1k,                      |            |

|            | 2k and a perfect (8k) signature                                                          | 155        |

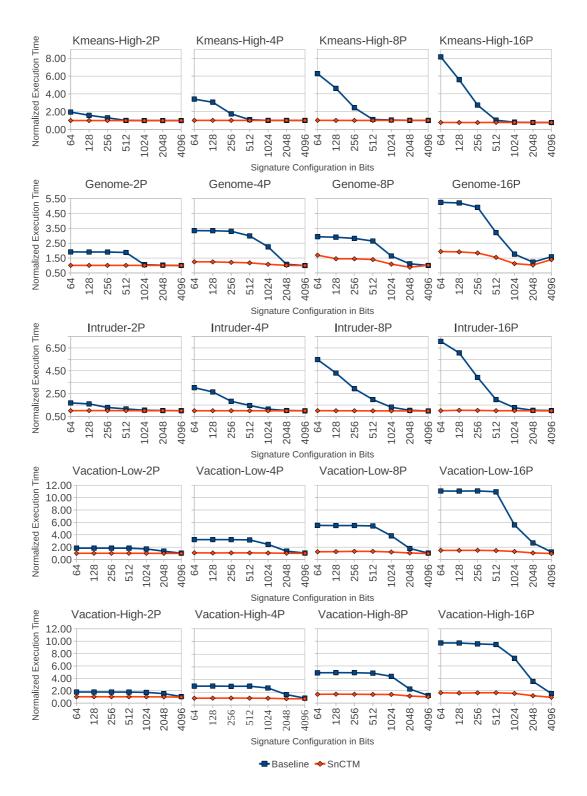

| 8.8        | Signature sensitivity of baseline and SnCTM - Part I (execution time is                  |            |

|            | normalised to the perfect signature)                                                     | 157        |

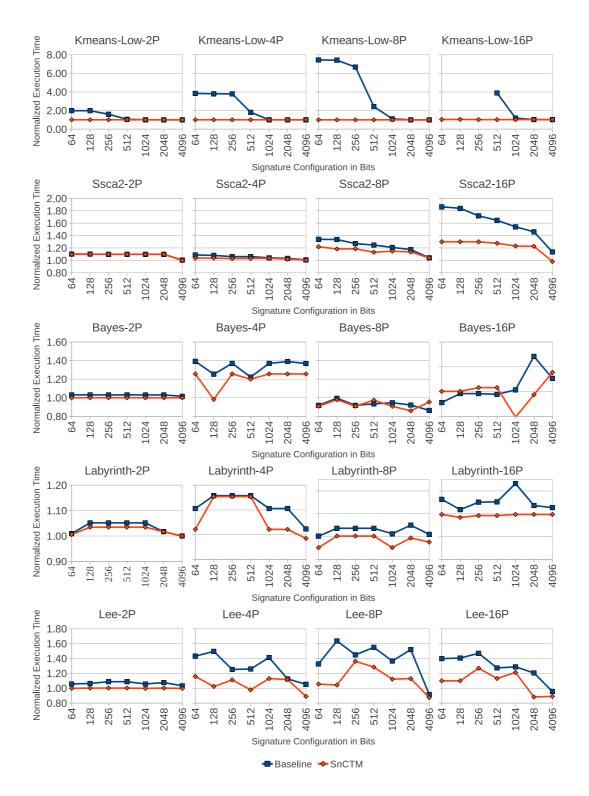

| 8.9        | Signature sensitivity of baseline and SnCTM - Part II (execution time is                 |            |

|            | normalised to the perfect signature)                                                     | 158        |

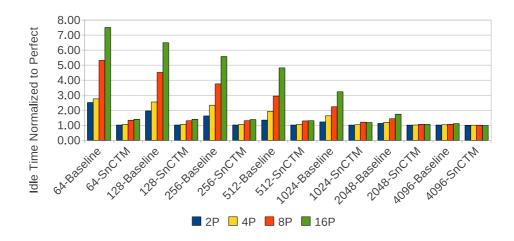

| 8.10       | Idle time of SnCTM and baseline normalised to perfect                                    | 160        |

| 9.1        | TM_RESTART function used in Vacation application                                         | 165        |

| 9.2        | TM_RESTART function used in Labyrinth application                                        | 165        |

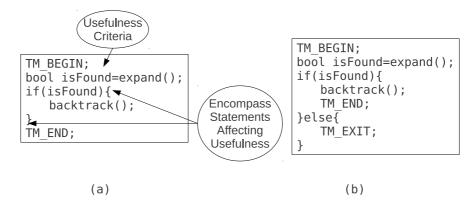

| 9.3        | Lee-TM pseudocode                                                                        | 167        |

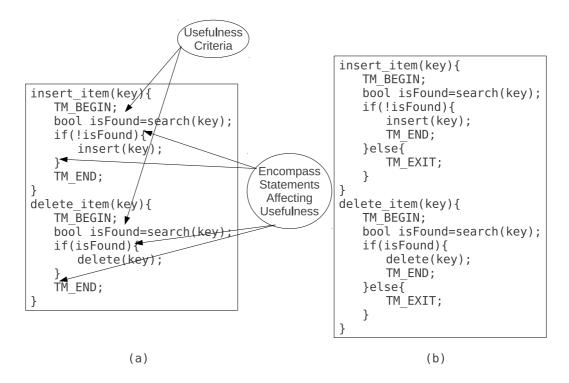

| 9.3<br>9.4 | Red-Black Tree TM pseudocode                                                             | 169        |

| 9.4<br>9.5 | Java TM code with exceptions                                                             | 169        |

| 9.5<br>9.6 |                                                                                          | 109        |

| 9.0<br>9.7 | Modifying Lee-TM pseudocode to use TM_EXIT                                               | 172        |

| 9.7<br>9.8 | Modifying Red-Black Tree TM pseudocode to use TM_EXIT Modified Java code to used TM_EXIT | 173        |

| 9.8<br>9.9 |                                                                                          | 175<br>174 |

|            | Implicit control transfer in Lee-TM pseudocode                                           | 174<br>174 |

| 9.10       | Incorrect usage of TM_EXIT                                                               |            |

|            | Pseudocode showing the conventional approach                                             | 175        |

| 9.12       | Pseudocode of revised reverse method using TM_EXIT                                       | 176        |

| 10.1       | Performance improvement when using TM_EXIT over baseline                                 | 183        |

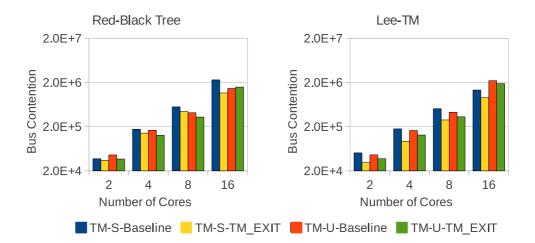

| 10.2       | Effect on bus contention when using TM_EXIT                                              | 185        |

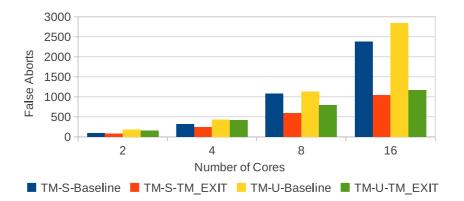

| 10.3       | Number of false positives occurred in Lee-TM for both baselines and                      |            |

|            | architectures supporting TM_EXIT                                                         | 185        |

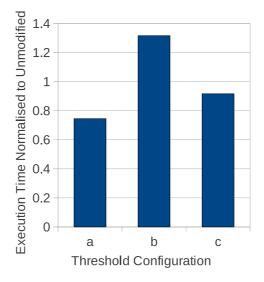

| 10.4       | Execution time of modified Linked-list normalised to the original                        | 187        |

| 10.5       | Memory accesses of both modified and unmodified Linked-list applic-                      |            |

|            | ations                                                                                   | 188        |

### Abstract

#### DATA CENTRIC AND ADAPTIVE SOURCE CHANGING TRANSACTIONAL MEMORY WITH EXIT FUNCTIONALITY Herath Mudiyanselage Isuru Prasenajith Herath A thesis submitted to The University of Manchester for the degree of Doctor of Philosophy, 5th December 2012

Multi-core computing is becoming ubiquitous due to the scaling limitations of single-core computing. It is inevitable that parallel programming will become the mainstream for such processors. In this paradigm shift, the concept of abstraction should not be compromised. A programming model serves as an abstraction of how programs are executed. Transactional Memory (TM) is a technique proposed to maintain lock free synchronization. Due to the simplicity of the abstraction provided by it, TM can also be used as a way of distributing parallel work, maintaining coherence and consistency. Motivated by this, at a higher level, the thesis makes three contributions and all are centred around Hardware Transactional Memory (HTM).

As the first contribution, a transaction-only architecture is coupled with a "data centric" approach, to address the scalability issues of the former whilst maintaining its simplicity. This is achieved by grouping together memory locations having similar access patterns and maintaining coherence and consistency according to the group each memory location belongs to. As the second contribution a novel technique is proposed to reduce the number of false transaction aborts which occur in a signature based HTM. The idea is to adaptively switch between cache lines and signatures to detect conflicts. That is, when a transaction fits in the L1 cache, cache line information is used to detect conflicts and signatures are used otherwise. As the third contribution, the thesis makes a case for having an exit functionality in an HTM. The objective of the proposed functionality, TM\_EXIT, is to terminate a transaction without restarting or committing.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx? DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester. ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses

### Acknowledgements

I would like to thank Prof. Ian Watson, my supervisor, for accepting me as a PhD student to the APT group. He not only accepted me as a student, but also provided me with a scholarship that covered my tuition fees and living expenses. The whole PhD was funded by an Overseas Research Studentship (ORS) and a School of Computer Science studentship from the University of Manchester. I am very grateful to them, none of this would have been possible if I was not able to secure that scholarship. Prof. Watson did more than supervising, he helped me a lot in debugging and improving my writing. He gave me enough freedom to explore new ideas, listened well and always proposed a solution/suggestion when I was stuck in the dark. Dr. Mikel Luján, my co-supervisor, helped me in numerous ways throughout my PhD.

When I started my PhD, four years ago, I knew nothing about research. Adapting to the research environment was painful. The APT group (Jamaicans) was very helpful. Dr. Jeremy Singer (now a lecturer at Glasgow) and Dr. Ian Rogers (now at Google), as the research associates of the group at that time, helped me a lot in getting familiar with the lab and the research environment. Dr. Preethi Sam (now at ARM), Dr. Christos Kotselidis (now at Intel Labs), Dr. Behram Khan (now a research associate at Manchester) and Dr. Mohammad Ansari (now a lecturer at Umm Al-Qura University), as the senior PhD students of the group at that time, gave good insights about how to get on with the PhD. I would also like to extend my thankfulness to Dr. Daniel Goodman, for volunteering to present my paper at the Transact 2012 workshop, when I was unable to participate due to visa issues.

I would also like to extend my heartiest gratitude to the Disability Support Office (DSO) of the university and to the Environs officer of the Computer Science school, Mr. Eamon Griffin, for supporting me in every possible way they can for my health problems.

Friends are part of our lives. During my stay at Manchester, I have made good friends with whom I have shared moments of joy, sadness, frustration, anger (the list

can go on and on). Paraskevas (Paris) Yiapanis always had something to talk about. He is one of the best social beings I have ever known. Demian Rosas, my research partner, is a good listener. I have wasted lots of his useful hours with my "fantastic" ideas. The three of us used to have one to two hours of "lunch hours" discussing non-CS issues like world politics, economy (again the list can go on). I will always remember those nice times.

I would also like to thank my former supervisors Dr. Manjula Sandirigama, Dr. Swarnalatha Radhakrishnan and Dr. Roshan G. Ragel from the University of Peradeniya, for supporting and encouraging me to embark on a research career. Dr. Ragel was like a friend to me. He checked my applications, helped to improve research proposals, even let me use his credit card to pay the application fee.

My father, Mr. Dhanapal Herath, always valued education. He tried to give the best possible education to his kids. If I needed something for my studies (books, exam papers or anything), he made sure that I would have it by the time I needed it. He told me the importance of higher education and convinced me to read for a PhD. The unconditional love of my mother, Mrs. Wimala Dhanapala, was a magnificent source of inspiration to me. I thank my parents and my sister for being so loving and present even from a distance.

It is the Sri Lankan culture that everybody belongs to big family. All my aunts, uncles, brothers and sisters (I don't know how many, its that big!) sent me well wishes whenever they can. I never felt alone. My lovely in-laws were in touch with me all the time, energizing me with Sri Lankan sweets.

Finally, and certainly not least, a great debt of gratitude is owed to Sashila, my wife, for her understanding and love. You were with me in every single step of this journey. You tried your best to make it comfortable for me. I love you.

## **Chapter 1**

## Introduction

Technology enables the doubling of transistors every 18-24 months (known as Moore's law [76]). This has allowed designers to increase complexity, by including more functional units in a processor, in search for higher performance. The objective of increasing the functional units is to allow a computation to proceed without waiting for resources. Having more resources facilitates instructions to be executed in parallel, which is therefore known as Instruction Level Parallelism (ILP). However there exists a limit to the number of instructions that can be executed in parallel [107]. In addition to this, the scaling limitations of single-core computing (power consumption and heat dissipation) [81] urges the hardware designers to investigate other directions.

In an attempt to address these issues, hardware manufacturers consider developing a processor with more than a single core on the same die, which is called a chipmultiprocessor or a multi-core processor. In this multi-core design, the speed of each individual core is less than the speed of a modern single core processor. As this multicore processor comprises many of those average speed cores, an application which is executed on them is expected to complete in less amount of time than in a single core processor, or at least in theory that is what should happen.

Just because a processor has higher number of cores, does not guarantee that any application runs on it will deliver higher performance. A best case scenario would be, executing an application which comprises several independent work units which can execute on their own. In such a situation, each work unit can be scheduled in one core and the output can be produced in considerably less amount of time than running each work unit sequentially in a single core processor. However, this is not the case for most of the applications. In order to gain the advantage of all the cores in this multi-core processor, first an application needs to be divided into several work units. As the

execution of this application progresses, some work units may need to communicate with each other. Sometimes they may try to access the same set of variables at the same time. Therefore a considerable effort is required when transforming a single core application to take the advantage of a multi-core processor. Changing the direction of processor design from single-core to multi-core has introduced several issues and the most significant and most relevant of them to the scope of this thesis is summarised hereafter.

The data transfer rate between the processor and the memory is much slower compared to the speed of a modern processor. This creates a processor-memory gap, which is called the Von Neumann bottleneck. A small but faster storage called cache is attached to the processor to address this, by storing frequently used data in cache and servicing memory requests with them. Even though this was a promising way of achieving its objective, in a multi-core environment this can lead to a situation where more than one processor has different values in their caches for the same memory location. This is possible because now the memory is being accessed/modified by more than one processor and the cache of one processor may not be aware of the changes made by another processor. Therefore a mechanism is required to communicate the state of a cache line in one core, to the rest of the cores. As the issue is related to maintaining a coherent view of caches, the associated communication is called cache coherence protocol. Quite a number of protocols each having different performance characteristics have been proposed. All these protocols require a data structure to be maintained in hardware (a modified cache) to store the state (modified, invalid or identical to memory copy) of cached entries and a messaging mechanism to communicate the state of the cache lines concerned.

In a single core processor, instructions are issued by a single entity. Therefore the order the effects of these instructions appear, is the same as the order they have been issued. Simply, a read operation to a memory location should return the last value written to that location. The definition of "last" is trivial in a single core processor as there exists only a single program order. Also having a single order allows certain compiler optimizations such as reordering of instructions and so on. However in an environment where multiple entities are issuing instructions, firstly, the ordering is not trivial. Secondly, some of the compiler optimizations may not match the behaviour expected by the application developer. Therefore a mechanism is required to ensure that the memory operations issued by all the processors correspond to some order and this order should match the behaviour expected by a programmer. Memory consistency

models are introduced to address this issue.

In the multi-core computing era, software applications need to be modified to utilise the extra cores available in a processor. The workload needs to be distributed to available cores when executing these applications. Therefore it is inevitable that parallel programming becoming the mainstream programming practise. In an application that is written to execute in parallel, the parallelism can exist either at task level or method level or thread level. (The discussion is made at the context of thread level parallelism, but the issues remain the same for other levels as well). When a program is executing in parallel, different threads may access/modify the same memory location. Programmers need to identify those situations and special mechanisms (locks, barriers) need to be introduced to the program to produce the correct result. This is the synchronisation issue in parallel programming. In order to ensure mutual exclusiveness is maintained among those concurrent accesses made to these memory locations, conventionally, locks are used. To execute a code region protected by locks, first the lock is acquired. It is released when the execution is completed. In order to acquire a lock, at the hardware level it is required to first check whether it is available. The acquire operation happens afterwards. Essentially this involves a read and a write operation. If the process of acquiring a lock is done using conventional read and write operations, in a multi-core environment it is possible for two processors to acquire the same lock at the same time. Therefore atomic instructions like Test-And-Set which allows to atomically read and modify a memory location are used to implement locks. The instruction pair Load-Linked/Store-Conditional (LL/SC) is similar to other atomic instructions, but comprises two instructions. This allows it to have intermediate operations between the load and the store operations. This feature makes LL/SC a good candidate for constructing other atomic instructions. For example a new atomic increment instruction can be constructed using this LL/SC instruction.

The simplest form of lock based programming is to have a single program-wide lock and each thread acquires it before entering the critical region and releases it, once it has finished executing the critical region. This approach is quite simple and easy to explain. However this kind of approach is not advisable as there can be groups of critical regions where these groups have no relation to each other. Therefore despite its simplicity, this kind of coarse grained locking approach can harm the performance of a parallel application. The other alternative is to associate a smaller lock with each significant computation inside the critical region. In this manner if all the associated locks are available, a thread can complete the computation enclosed in the critical region. Also in this case, non-availability of a lock means that the computation can not be performed in parallel. Even though this kind of finer grained locking seems promising in delivering better performance, writing applications with this approach is a difficult task. A programmer has to ensure that the program does not end up in a situation where two or more threads are waiting for each other to release a lock. This kind of situation is known as a *dead lock* and it can occur in any lock based program, if the locks are not managed properly.

Observing how optimistic concurrency is exploited in databases [37], Herlihy and Moss proposed a lock free synchronisation mechanism called Transactional Memory (TM) [50]. In the TM approach, instead of waiting for a lock to be available, all the threads enter the critical region as if the lock is available. In order to ensure the consistency and the correctness is not compromised, all the operations performed in this critical region are made speculatively and kept in isolation from other threads. Under TM, a critical region becomes a transaction and each transaction appear to rest of the system, as if it happened atomically. This is achieved by operating speculatively within the critical region and keeping those operations in isolation. This requires a mechanism to keep two versions (speculative and original) of memory locations that are accessed within a transaction. If more than one thread has accessed the same memory location and one of them has modified it, a conflict has occurred. In order to check conflicts, each thread is required to maintain a set of locations it has read and written in the current transaction. Based on how this versioning and conflict detection is performed several flavours of TM systems exist. Also all these TM related operations can be performed in hardware, software or using a combination of both (hybrid).

Having described the issues of multi-core computing related to this thesis, the discussion is now aimed to determine the root cause of these problems. Starting with a very general approach, a computer consists of large number of transistors, wires and so on. In order to make use of this equipment an application program needs to be developed. In order to facilitate the job of an application program developer, an abstraction of the underlying system is defined. Programmers write their programs according to the abstraction provided and this comes in the form of a programming model. In single-core computing this could simply be the Von Neumann model, since it comprises only one processor and one memory. Therefore programmers can only specify "what" operations need to be done with the memory and not how to do it. Due to its simplicity, programmers would still favour this kind of abstraction, even in the multi-core era. A problem occurs when ensuring a Von-Neumann like abstraction in a multi-core processor, because the memory can now be modified by more than one processor. In order to provide this simple abstraction, at the architectural level, it is required that each processor has the same view of the shared memory. In this thesis, the term "global view requirement" is used to represent this. The simplest form of providing this is to ask each processor to issue instructions in an order, one after the other and the effects of each instruction becomes visible to the others before the next instruction is issued. In this regard, a cache coherence protocol can be used to propagate the effects of the execution of an instruction and a memory consistency model defines when this propagation should be done.

This kind of approach will certainly be able to provide a Von-Neumann like abstraction for a multi-core processor. However, it will restrict the optimizations like instruction reordering and bypassing and also incurs quite a lot of communication. Analysing this issue from a high level programming language perspective, it is clear that not all the threads are interested in the modifications made to all the memory locations by other threads. In terms of a coherence protocol this translates to, a propagation not being required for all the cache lines that get modified. The same observation, in terms of a memory consistency model can be interpreted as, based on the access pattern certain memory locations can be reordered or bypassed even without the programmer intervention. Even though the latter is provided in certain relaxed memory consistency models, a programmer is required to categorise memory locations to relax the ordering. Based on these observations one part of this thesis presents an architecture that relaxes coherence and consistency of memory locations based on their access patterns.

Going back to the discussion of abstraction, when providing synchronisation using locks, programmers have to define not only "what" data needs be synchronised but also "how" to provide it. It becomes the responsibility of a programmer to acquire and release locks in a way that the program does not end up in a *dead lock* state. This clearly breaks the much believed concept of abstraction in computing. The TM approach to maintaining synchronisation, is able to provide the same abstraction as it only requires the definition of the critical section and the underlying TM mechanism takes care of how the mutual exclusiveness is maintained among accesses to that critical section. Since TM relies on speculation, aborts can happen due to mispeculation. Also aborts can happen due the lack of clarity in the mechanism used to detect conflicts (false aborts). Another part of this thesis proposes a novel technique to reduce these false aborts.

It is the job of a programmer to mark the critical sections in a TM application and

the underlying TM system guarantees that all these critical sections will be executed speculatively and committed at the end. Committing requires communicating the speculative modifications to others. If there is a condition inside a critical section, in some cases it possible that all the prior computation becomes non-useful if this condition is not met. As the underlying TM mechanism is not aware of any such condition, a commit phase will always take place as it is the only way to complete the transaction. Another part of this thesis recognizes that, in those circumstances, there is a need to exit from a transaction without committing it, hence such a functionality is proposed.

#### **1.1 Contributions**

At a high level, this thesis makes three major contributions. The first contribution is the Data Centric Transactional Memory (DaCTM) in which the region based coherency and consistency is introduced. The basic idea of DaCTM is to group together memory locations of similar access patterns and to allocate them to different memory regions. The required level of coherence and consistency for each memory region is defined according to the access pattern of the locations it holds. The key idea is that, a location itself defines the required level of coherence and consistency for that location, which is the basis of the "data centric" concept. DaCTM is inspired by the "Transactions Everywhere" [60] approach and Transactional Memory Coherence and Consistency (TCC) [39] which suggest the development of an application entirely from transactions. The attractive component from those proposals is that transactions can be considered as the basic unit of parallel work, maintaining coherence and consistency, therefore provides a simple abstraction. However this simplicity comes at the cost of a higher bandwidth requirement which is not desirable in a multi-core environment. This is addressed in DaCTM by coupling this sort of "transactions-only" approach with the data centric concept. Using this approach, DaCTM is able to provide the same simplicity as "Transactions Everywhere" [60] and TCC [39] without saturating the communication network.

The second contribution of the thesis is SnCTM, a novel way of reducing false transaction aborts in a hardware TM system. The key idea is to use either cache lines or signatures to detect conflicts in a TM system, depending on the situation. SnCTM is motivated by two facts: (1)signatures produce false aborts; (2)signatures are only required when a transaction cannot fit in the cache. Therefore the proposal of SnCTM is to use cache lines to detect conflicts when a transaction is able to fit in the cache,

signatures are used otherwise. By adaptively changing between these two sources, SnCTM is able to reduce false transaction aborts in a hardware TM system. Also SnCTM is able to reduce the size of a signature without comprising the performance.

As the third contribution, the thesis makes a case for having an exit functionality in a hardware TM system. The objective of the proposed functionality (TM\_EXIT) is to exit from a transaction without committing it. Once exited, the program control is transferred to the line immediately following the transaction. The proposal is motivated by the fact that when there is a condition inside a transaction, the whole computation can be non-useful when this condition is not met. However, regardless of the fact that the condition is met or not, a commit phase takes place. If there is a mechanism to notify that the commit is not useful, it could skip that step and go to the line immediately following the atomic block. The exit functionality proposed in the thesis fits well for this purpose. By avoiding these unnecessary commits, the network utilization can be reduced. In addition to making the case for this functionality, ways to improve expressiveness using this approach are also discussed in the thesis.

#### **1.2 Thesis Structure**

The contributions made in this thesis are centred around hardware transactional memory and each of them is independent of the others (as shown in Figure 1.1). Therefore the thesis is organized in to three parts.

Figure 1.1: Contributions of the Thesis

Part I presents the Data Centric Transactional Memory (DaCTM) and comprises

Chapters 3, 4, 5 and 6. The concept of DaCTM is presented in Chapter 3. The architectural extensions required to support the DaCTM concept are described in Chapter 4. The performance evaluation of DaCTM is presented in Chapter 5. The other related work of DaCTM, except TM, is presented in Chapter 6. The detailed contributions related to DaCTM are described in the first chapter of Part I.

The SnCTM approach to reduce false transaction aborts is presented in Part II which comprises Chapters 7 and 8. The motivation and the concept of using adaptive sources to reduce false aborts is presented in Chapter 7. The same chapter also summarises related work on hardware signatures. The architectural design of SnCTM and its evaluation is presented in Chapter 8. A list of contributions made with the SnCTM approach is presented in the first chapter of Part II. The text in Part II is mostly based on [45].

Part III which comprises Chapters 9, 10 and 11, makes a case for having an exit functionality in an HTM. The motivation for the proposed functionality, TM\_EXIT, is presented in Chapter 9. The same chapter formally defines the TM\_EXIT function and describes how to use it in TM programming. Even though increasing performance is not the prime objective of TM\_EXIT, the effect of it towards the execution time is presented in Chapter 10. Related hardware and software TM approaches that could either deliver or one would think is able to deliver the same functionality as TM\_EXIT are discussed in Chapter 11. All the contributions made by introducing TM\_EXIT are described in the first chapter of Part III. The text in Part III is mostly based on [44].

In addition to these three parts, Chapter 2 describes the background of Transactional Memory (TM). It focuses on conceptual aspects such as concurrency control, versioning and conflict detection; theoretical aspects such as syntax and semantics of TM; and implementation aspects such as hardware TM, software TM and Hybrid TM. As the thesis is centred around hardware TM, a significant portion of the chapter is dedicated to describe some of the key HTM proposals. The conclusions of the contributions made in the thesis is presented in Chapter 12. The same chapter also discusses the possible future research directions of each high level contribution.

Figure 1.2 shows the suggested reading order for the thesis. As each part is independent, the reader can only read the relevant chapters of an interested part and jump directly to the conclusions chapter. Also if the reader is experienced in the area of Transactional Memory, Chapter 2 can be skipped as each part has a separate chapter-/section describing most of the related work to the contributions made in that part.

Figure 1.2: Suggested reading structure of the Thesis

#### **1.3 Publications**

The work presented in thesis has resulted in following publications.

- Isuru Herath, Demian Rosas-Ham, Mikel Luján, and Ian Watson. SnCTM: Reducing False Transaction Aborts by Adaptively Changing the Source of Conict Detection. In Proceedings of the 9<sup>th</sup> Conference on Computing Frontiers, CF '12, pages 65-74, New York, NY, USA, 2012. ACM.

- Isuru Herath, Demian Rosas-Ham, Daniel Goodman, Mikel Luján, and Ian Watson. A case for Exiting a Transaction in the Context of Hardware Transactional Memory. In TRANSACT '12: 7<sup>th</sup> ACM SIGPLAN Workshop on Transactional Computing, February 2012.

### **Chapter 2**

### **Transactional Memory**

The contributions made in this thesis are centred around Hardware Transactional Memory (HTM). In order to facilitate the reader to understand the contributions, to compare and contrast them with the existing proposals, this chapter provides a comprehensive summary of hardware transactional memory. It also gives an overview of software and hybrid transactional memory systems. The chapter starts the discussion by elaborating on theoretical and semantical aspects of Transactional Memory (TM) in Sections 2.2 and 2.3 respectively. Design considerations that could affect the performance of a TM system are discussed in Section 2.4. Advantages, issues and models for programming with TM are discussed in Section 2.5. A comprehensive summary of HTM based on the most influential existing proposals is presented in Section 2.6. Brief overviews of software and hybrid TM systems are provided in Sections 2.7 and 2.8. Finally, Section 2.9 summarises the chapter.

#### 2.1 Introduction

When writing parallel programs mutually exclusive accesses are required in certain cases. Conventionally, a programmer may use locks to ensure that the mutually exclusive execution is guaranteed. In order to acquire a lock, at the hardware level it is required to first check whether it is available. The acquire operation happens afterwards. Essentially this involves a read and a write operation. If the process of acquiring a lock is done using conventional read and write operations, in a multicore environment it is possible for two processors to acquire the same lock at the same time. Therefore atomic instructions like Test-And-Set which allow to atomically read and modify a memory location are being used to implement locks. The instruction

Load-Linked/Store-Conditional (LL/SC) is similar to other atomic instructions, but it also gives the possibility to construct other atomic instructions. For example a new atomic increment instruction can be constructed using this LL/SC instruction. However the atomicity is still maintained only for a single memory location.

Herlihy and Moss [50] propose to generalise this LL/SC instruction in order to provide atomicity to more than a single memory location. Their approach is called Transactional Memory (TM) which is based on the concept of database transactions [37]. They also inherited the concept of *atomic* blocks proposed by Lomet [69] as a notion of structuring a program. The initial TM proposal of Herlihy and Moss introduced a new multi-core architecture that is capable of providing lock-free synchronization. A programmer is expected to mark any number of instructions that need to be executed atomically. The atomic execution on multiple memory locations is made possible with speculation. When the end of the atomic region is reached, these modifications are communicated to other processors. The idea of executing code blocks and checking conflicts at commit points has also been expressed by Knight [57]. In the architecture proposed by Knight, all the modified cache entries are kept in a second cache called a *confirm* cache. Once a block has completed its execution, entries in the *confirm* cache are written back to the main memory. During this process, any other processor which has accessed these locations gets aborted.

Transactional Memory and database transactions have certain similarities. For example, some of the properties that a database system needs to maintain, are also required to be maintained in a TM system. These are known as ACI (Atomicity, Consistency and Isolation) properties. A transaction in TM context encompasses one or more memory operations. *Atomicity* requires a transaction to either complete all its memory operations or to leave the system as if none of those took place. If a transaction is successful, it commits all its speculative operations thereby making them visible to the rest of the system. If a transaction is not successful, it aborts thereby abandoning all its speculative modifications and leaving the system unmodified. *Consistency* requires a system to be transferred from one consistent state to another consistent state. In other words it ensures no transaction leaves the system in a half-finished state. Finally the *Isolation* property requires all the modifications made within an atomic region to be kept in isolation until the commit point. Modifications made by one processor are not visible to others until they are committed.

#### 2.2 TM Design Considerations

When executing transactions, *conflicts* occur when more than one processor accesses the same memory location and one of them is a write. These conflicts then need to be *detected* and *resolved*. The detection and resolution of conflicts can be performed at the time the conflict occurs or they can be deferred until later in the execution. The concurrency control of a TM system defines how these events are handled.

#### 2.2.1 Concurrency Control

Currently there are two basic approaches to concurrency control. In the first approach, known as *pessimistic concurrency*, all three events happens at the same time. That is when a transaction is about to access a memory location, it tries to get the exclusive ownership of the location. If another transaction has already accessed this location a conflict is detected and, depending on the conflict resolution policy, one of the transactions is aborted immediately.

In the second approach, known as *optimistic concurrency*, these events can happen at different times. For example multiple transactions can modify the same memory location. Even though this results in a conflict, it is not detected until one of the transactions decides to commit. When the committing transaction publishes the locations it has accessed, the TM system detects conflicts and resolves them.

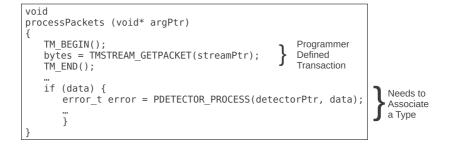

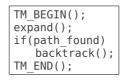

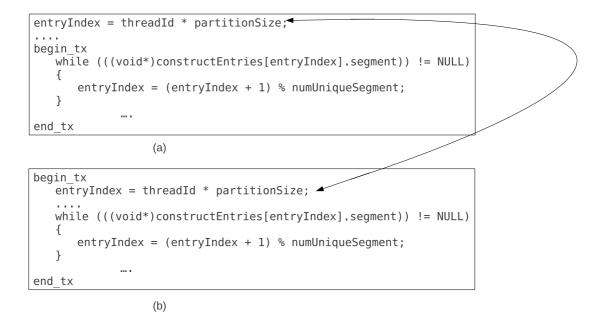

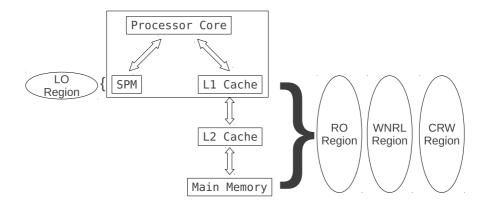

It is hard to advocate which form of concurrency is better because it depends on the nature of the application. If the application has high contention, it tends to produce more aborts. For such situations *pessimistic concurrency* becomes useful because it help to reduce the wasted work. However it requires exclusive ownership before accessing a memory location. This could lead to a live-lock situation, which affects the forward progress of the execution. On the other hand *optimistic concurrency* does not require such ownership, allowing any number of speculatively modified entries to exist for the same memory location. Therefore it does not introduce any live-lock and it guarantees at least a single thread will progress.