# Simulation and Visualisation for Debugging Large Scale Asynchronous Handshake Circuits

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science & Engineering

2004

Lilian Janin

Department of Computer Science

## Contents

| Contents2                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures                                                                                                                                                                                                                                                                                                                                                                |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                 |

| Abstract9                                                                                                                                                                                                                                                                                                                                                                      |

| Declaration10                                                                                                                                                                                                                                                                                                                                                                  |

| Copyright10                                                                                                                                                                                                                                                                                                                                                                    |

| Acknowledgements11                                                                                                                                                                                                                                                                                                                                                             |

| Chapter 1: Introduction12                                                                                                                                                                                                                                                                                                                                                      |

| 1.1 Large Scale Asynchronous Handshake Circuits12                                                                                                                                                                                                                                                                                                                              |

| 1.2 Automated Circuit Synthesis14                                                                                                                                                                                                                                                                                                                                              |

| 1.3 Motivations and Objectives15                                                                                                                                                                                                                                                                                                                                               |

| 1.4 Contributions made by this work16                                                                                                                                                                                                                                                                                                                                          |

| 1.5 Thesis Overview17                                                                                                                                                                                                                                                                                                                                                          |

| 1.6 Publications18                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 2: Background19                                                                                                                                                                                                                                                                                                                                                        |

| Chapter 2: Background    19      2.1 Asynchronous Design    19                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                |

| 2.1 Asynchronous Design                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>2.1 Asynchronous Design</li></ul>                                                                                                                                                                                                                                                                                                                                     |

| 2.1 Asynchronous Design                                                                                                                                                                                                                                                                                                                                                        |

| 2.1 Asynchronous Design       19         2.1.1 Handshake Signalling Protocols       21         2.1.2 Delay Models       22         2.1.3 Data Encodings       24                                                                                                                                                                                                               |

| 2.1 Asynchronous Design       19         2.1.1 Handshake Signalling Protocols       21         2.1.2 Delay Models       22         2.1.3 Data Encodings       24         2.1.4 Asynchronous Difficulties       26                                                                                                                                                              |

| 2.1 Asynchronous Design       .19         2.1.1 Handshake Signalling Protocols       .21         2.1.2 Delay Models       .22         2.1.3 Data Encodings       .24         2.1.4 Asynchronous Difficulties       .26         2.2 Asynchronous Specification Techniques       .28                                                                                             |

| 2.1 Asynchronous Design       .19         2.1.1 Handshake Signalling Protocols       .21         2.1.2 Delay Models       .22         2.1.3 Data Encodings       .24         2.1.4 Asynchronous Difficulties       .26         2.2 Asynchronous Specification Techniques       .28         2.2.1 Event-Based Specification       .28                                           |

| 2.1 Asynchronous Design       19         2.1.1 Handshake Signalling Protocols       21         2.1.2 Delay Models       22         2.1.3 Data Encodings       24         2.1.4 Asynchronous Difficulties       26         2.2 Asynchronous Specification Techniques       28         2.2.1 Event-Based Specification       28         2.2.2 State-Based Specification       30 |

| 2.1 Asynchronous Design192.1.1 Handshake Signalling Protocols212.1.2 Delay Models222.1.3 Data Encodings242.1.4 Asynchronous Difficulties262.2 Asynchronous Specification Techniques282.2.1 Event-Based Specification282.2.2 State-Based Specification302.2.3 Communicating Sequential Processes30                                                                              |

| 2.1 Asynchronous Design192.1.1 Handshake Signalling Protocols212.1.2 Delay Models222.1.3 Data Encodings242.1.4 Asynchronous Difficulties262.2 Asynchronous Specification Techniques282.2.1 Event-Based Specification282.2.2 State-Based Specification302.2.3 Communicating Sequential Processes302.2.4 Macromodules and DI Interconnect31                                      |

| 2.1 Asynchronous Design192.1.1 Handshake Signalling Protocols212.1.2 Delay Models222.1.3 Data Encodings242.1.4 Asynchronous Difficulties262.2 Asynchronous Specification Techniques282.2.1 Event-Based Specification282.2.2 State-Based Specification302.2.3 Communicating Sequential Processes302.2.4 Macromodules and DI Interconnect312.3 Balsa32                           |

| 2.1 Asynchronous Design192.1.1 Handshake Signalling Protocols212.1.2 Delay Models222.1.3 Data Encodings242.1.4 Asynchronous Difficulties262.2 Asynchronous Specification Techniques282.2.1 Event-Based Specification282.2.2 State-Based Specification302.2.3 Communicating Sequential Processes302.2.4 Macromodules and DI Interconnect312.3 Balsa322.3.1 Balsa Framework33    |

| Chapter 3: Related Work41                                  |

|------------------------------------------------------------|

| 3.1 Handshake Circuit Simulation41                         |

| 3.2 Debugging Asynchronous-Specific Problems43             |

| 3.3 Visualisation Oriented Towards Program Comprehension44 |

| 3.3.1 Knowledge Organisation by Merging Multiple Sources45 |

| 3.3.2 Dynamic Visualisation47                              |

| 3.3.3 Information Exploration with Coordinated Views       |

| 3.4 Unified IDE for Large Scale Asynchronous Circuits      |

| 3.5 Summary                                                |

| Chapter 4: Theory of Handshake Circuit Debugging53         |

| 4.1 The Handshake Circuit Model53                          |

| 4.1.1 Static Model53                                       |

| 4.1.2 Dynamic Model54                                      |

| 4.2 Deadlocks                                              |

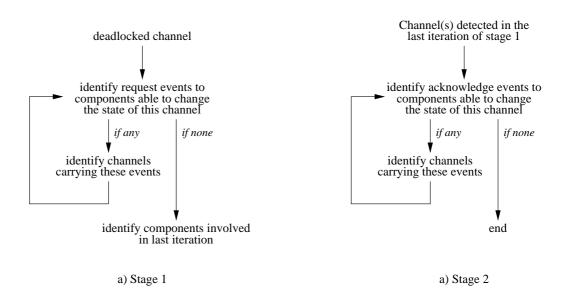

| 4.2.1 Handshake Circuit Deadlock Detection57               |

| 4.2.2 Handshake Circuit Deadlock Analysis59                |

| 4.3 Non-determinism                                        |

| 4.3.1 Metastability63                                      |

| 4.3.2 Modelling Delays With Errors64                       |

| 4.3.3 Exhaustive Simulation64                              |

| 4.4 Activity Pattern Analysis65                            |

| 4.4.1 Visual Analysis65                                    |

| 4.4.2 Automated Analysis66                                 |

| 4.5 Circuit Optimisation – Profiling67                     |

| 4.6 Summary67                                              |

| Chapter 5: High-Performance Simulation                     |

| 5.1 Preamble                                               |

| 5.1.1 Choice of the Simulation Level69                     |

| 5.1.2 Choice of the Handshake Protocol70                   |

| 5.1.3 Preliminary Statistics71                             |

| 5.2 Scheduler                                              |

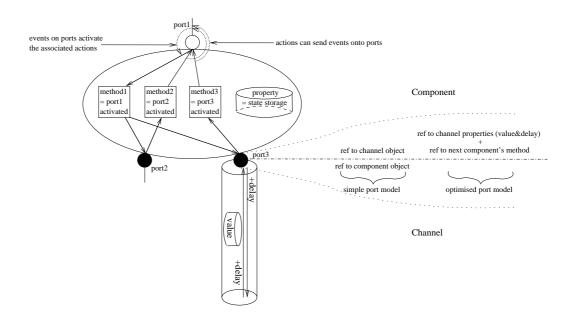

| 5.2.1 A Software Model for Simulating Handshake Circuits72 |

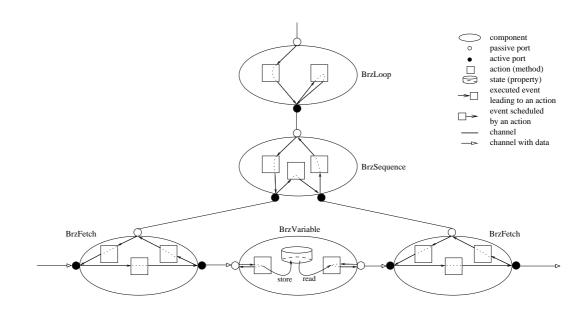

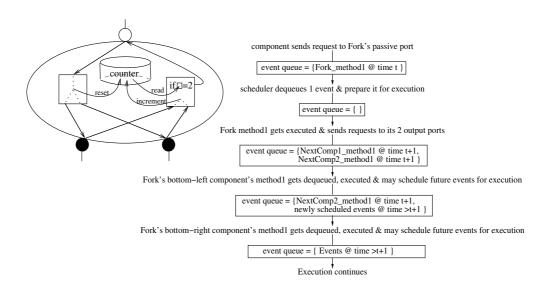

| 5.2.2 Standard Event-Driven Scheduler74                    |

| 5.2.3 Out-of-Order Scheduler76                             |

| 5.2.4 Reordering Arbitration Inconsistencies                | 83  |

|-------------------------------------------------------------|-----|

| 5.3 Modelling Handshake Circuits for Speed                  | 84  |

| 5.3.1 Channel Data Value Implementation                     | 84  |

| 5.3.2 Premature Channel Data Storage                        | 85  |

| 5.3.3 Data Sharing Between Components                       | 85  |

| 5.4 Test Harnesses                                          | 86  |

| 5.5 Summary                                                 | 87  |

| Chapter 6: Analysis-Oriented Simulation                     | 88  |

| 6.1 Timing Analysis                                         |     |

| 6.1.1 Determining and Adjusting Delays                      |     |

| 6.1.2 Simulating Delays with Errors                         | 90  |

| 6.1.3 Delays in Test Harnesses                              | 91  |

| 6.2 Power Analysis                                          | 91  |

| 6.3 Source Code Position Annotation                         | 92  |

| 6.4 Simulation Tracing for Offline Analysis                 | 93  |

| 6.4.1 Standard Trace                                        | 94  |

| 6.4.2 Out-of-Order Trace                                    | 95  |

| 6.4.3 Pattern Analysis and Compressed Out-of-Order Trace    | 95  |

| 6.5 Summary                                                 | 97  |

| Chapter 7: Visualisation                                    | 98  |

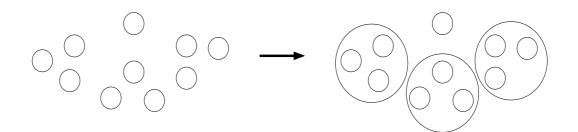

| 7.1 Information Clustering                                  | 98  |

| 7.1.1 Functional Grouping                                   | 99  |

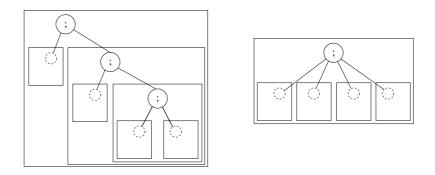

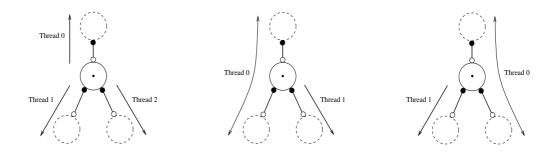

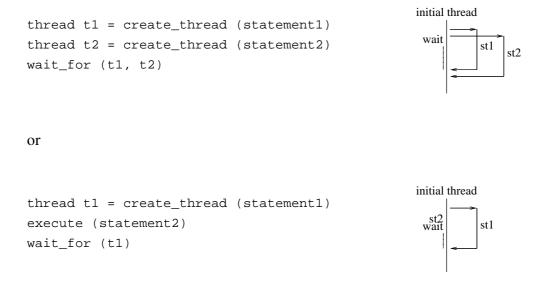

| 7.1.2 Control Threads                                       | 102 |

| 7.1.3 Data Flow                                             | 104 |

| 7.1.4 Test Harnesses                                        | 107 |

| 7.2 Multi-Source Graph View                                 | 108 |

| 7.2.1 Static Multiscale Structure                           | 108 |

| 7.2.2 Dynamic Colour-Based Animation                        | 109 |

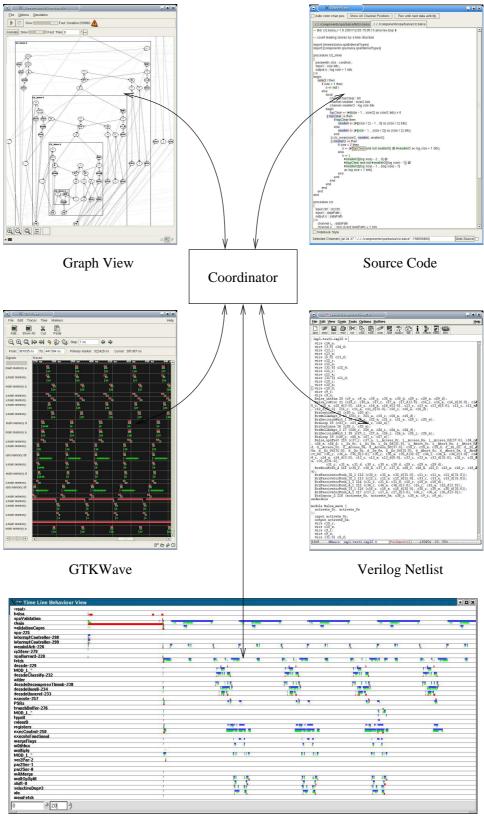

| 7.3 Coordinated/Collaborative Views                         | 110 |

| 7.3.1 Views                                                 | 111 |

| 7.3.2 Multiple Views: Linking the Different Representations | 113 |

| 7.4 Additional techniques                                   | 116 |

| 7.4.1 Dot Layout                                            | 116 |

| 7.4.2 Tracking Structural Changes during Design Iterations  | 117 |

| 7.5 Summary1                                                      | 19  |  |

|-------------------------------------------------------------------|-----|--|

| Chapter 8: Integration1                                           | 20  |  |

| 8.1 Balsa Compiler and Breeze Format1                             | 21  |  |

| 8.2 Simulation Trace1                                             | 22  |  |

| 8.3 Visualisation Control Links1                                  | 22  |  |

| 8.4 Summary1                                                      | 23  |  |

| Chapter 9: Results and Discussion1                                | 24  |  |

| 9.1 Simulation: Boosted Compilation and Simulation Speeds1        | 25  |  |

| 9.2 Debugging Demonstrator: The Simple Corridor Problem1          | 31  |  |

| 9.2.1 Deadlock Handling1                                          | 32  |  |

| 9.2.2 Livelock Handling1                                          | 34  |  |

| 9.2.3 Non-Determinism Handling1                                   | 35  |  |

| 9.2.4 Further Pattern Analysis and Trace Compression1             | 36  |  |

| 9.2.5 Discussion1                                                 | 39  |  |

| 9.3 Visualisation Demonstrator: The Huge SPA Microprocessor Core1 | 39  |  |

| 9.3.1 Merging Sources for Multiscale Graph Visualisation1         | 40  |  |

| 9.3.2 Animated Graph1                                             | 45  |  |

| 9.3.3 Coordinated/Collaborative Views1                            | 46  |  |

| 9.3.4 Discussion1                                                 | 48  |  |

| 9.4 Unified Debugging Environment1                                | 49  |  |

| Chapter 10: Conclusions1                                          | 150 |  |

| 10.1 Summary1                                                     | 50  |  |

| 10.2 Summary of Contributions1                                    | 51  |  |

| 10.3 Limitations1                                                 | 52  |  |

| 10.4 Suggestions for Future Work1                                 | 52  |  |

| Appendix A: Balsa Example Circuits with Statistics154             |     |  |

| Appendix B: Breeze Handshake Components159                        |     |  |

| References1                                                       | 171 |  |

## List of Figures

| 1.1        | Synchronous and asynchronous mechanisms                                                                      | 13       |

|------------|--------------------------------------------------------------------------------------------------------------|----------|

| 2.1        | Push and pull channel notations                                                                              | 20       |

| 2.2        | Channel signalling protocols                                                                                 | 22       |

| 2.3        | 4-phase push data validity schemes                                                                           | 23       |

| 2.4<br>2.5 | STG notation<br>STG specification for a 2 input Muller C-element                                             | 29<br>29 |

| 2.3<br>2.6 | Balsa design flow                                                                                            | 29<br>34 |

| 2.7        | Balsa language features (modulo-10 counter example)                                                          | 35       |

| 2.8        | Breeze handshake circuit graph (modulo-10 counter example)                                                   | 37       |

| 2.9        | Breeze handshake circuit netlist (modulo-10 counter example)                                                 | 39       |

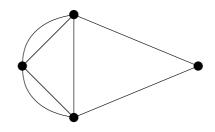

| 2.10       | Network graph                                                                                                | 40       |

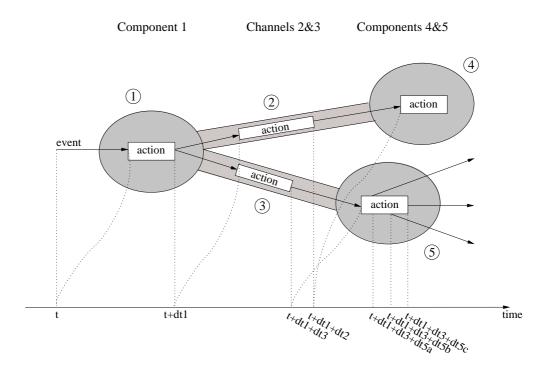

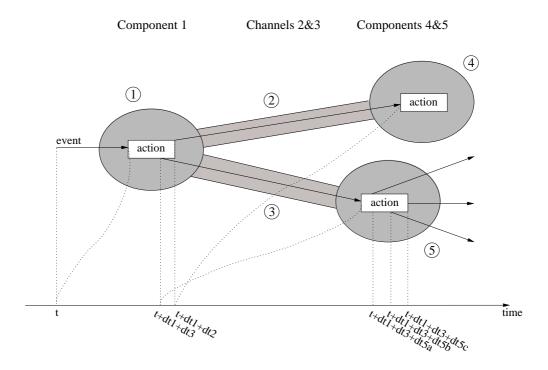

| 4.1        | Time model of the execution of a handshake circuit                                                           | 54       |

| 4.2        | Simplified time model of the execution of a handshake circuit                                                | 55       |

| 4.3        | Elements involved in a handshake circuit deadlock                                                            | 59       |

| 4.4        | Deadlock analysis algorithm                                                                                  | 60       |

| 5.1        | Object-oriented view of handshake component and channel                                                      | 73       |

| 5.2        | Object-oriented view of a handshake circuit                                                                  | 75       |

| 5.3        | Fork component model and scheduler's event queue                                                             | 75       |

| 5.4        | Pseudo handshake circuit for the equation                                                                    | 77       |

| 5.5<br>5.6 | Execution order of the handshake components in figure 5.4<br>Arbitrated circuit                              | 79<br>81 |

| 5.7        | Starvation due to out-of-order arbitration                                                                   | 82       |

| 5.8        | Three stage buffer circuit                                                                                   | 86       |

| 6.1        | Interleaved and sequential traces of threads of events                                                       | 96       |

| 7.1        | Abstracted functional grouping                                                                               | 100      |

| 7.2        | Unoptimised and optimised representations of a sequence of 4 actions                                         | 102      |

| 7.3        | Three control thread sets possible with a Fork component                                                     | 103      |

| 7.4        | The data Transferrer component                                                                               | 105      |

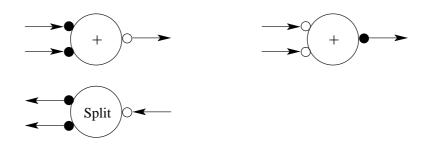

| 7.5        | Pull and push Add (BinaryFunc) and Split components                                                          | 106      |

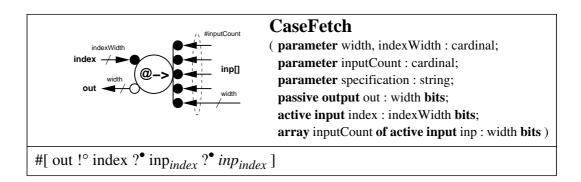

| 7.6        | CaseFetch component                                                                                          | 106      |

| 7.7        | Coordinated/collaborative views                                                                              | 112      |

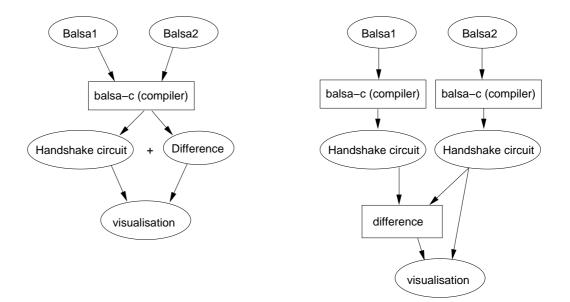

| 7.8        | Circuit reconfiguration strategies                                                                           | 118      |

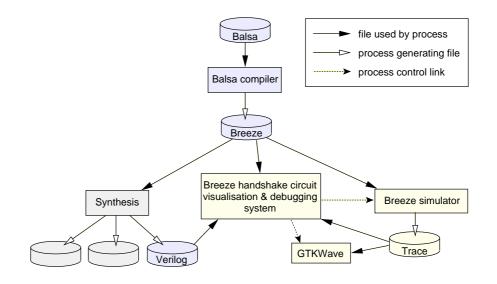

| 8.1        | New Balsa simulation and visualisation flow                                                                  | 120      |

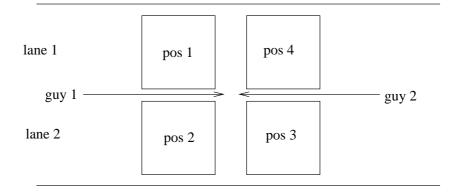

| 9.1        | Implementation model for the corridor problem                                                                | 132      |

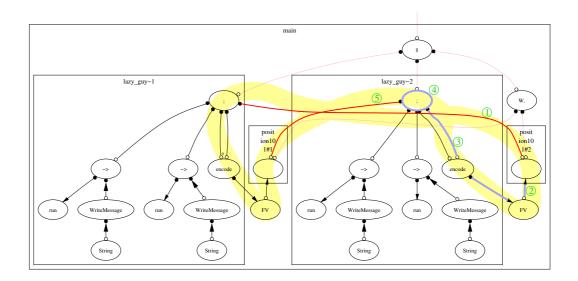

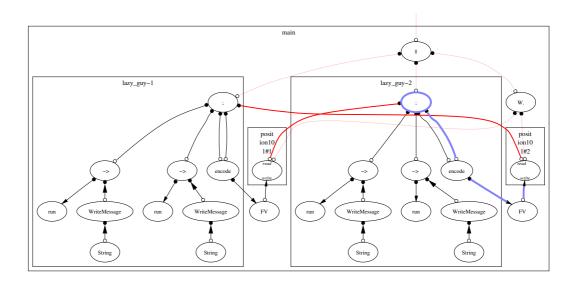

| 9.2        | Deadlock with two lazy_guys in the corridor example                                                          | 133      |

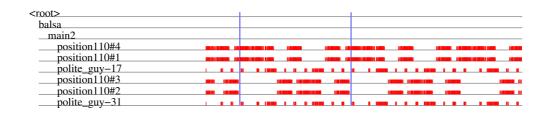

| 9.3        | Livelock with two polite_guys in the corridor example                                                        | 134      |

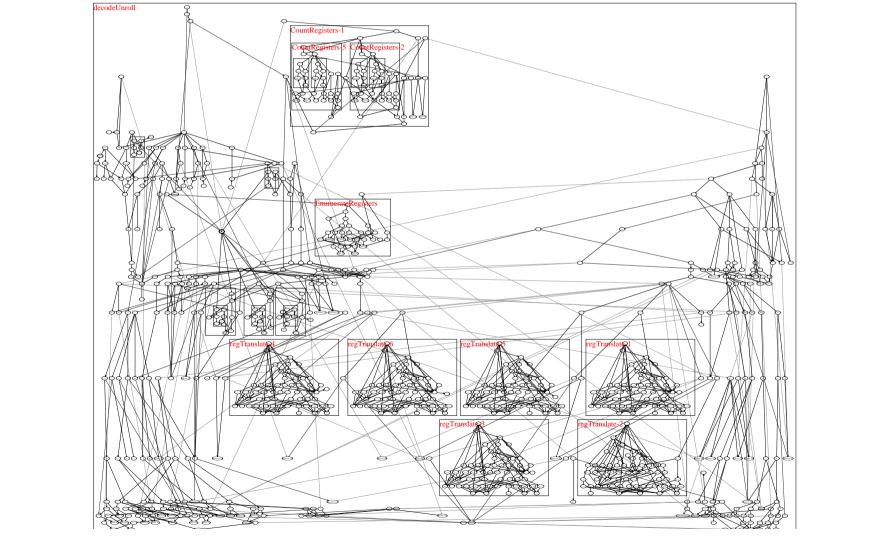

| 9.4<br>9.5 | Handshake circuit of the one-place buffer example with its environment<br>Huge graph layout: SPA - Zoom 100% | 137      |

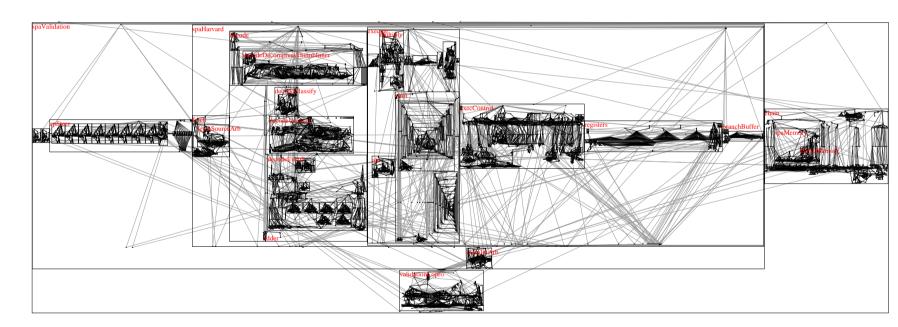

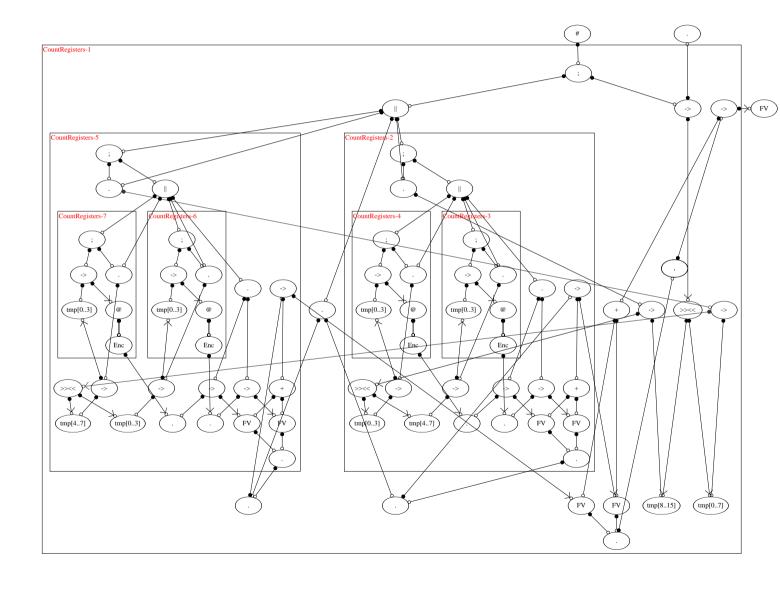

| 9.5<br>9.6 | Huge graph layout: SPA - Zoom 100%<br>Huge graph layout: SPA - Zoom 250%                                     | 141      |

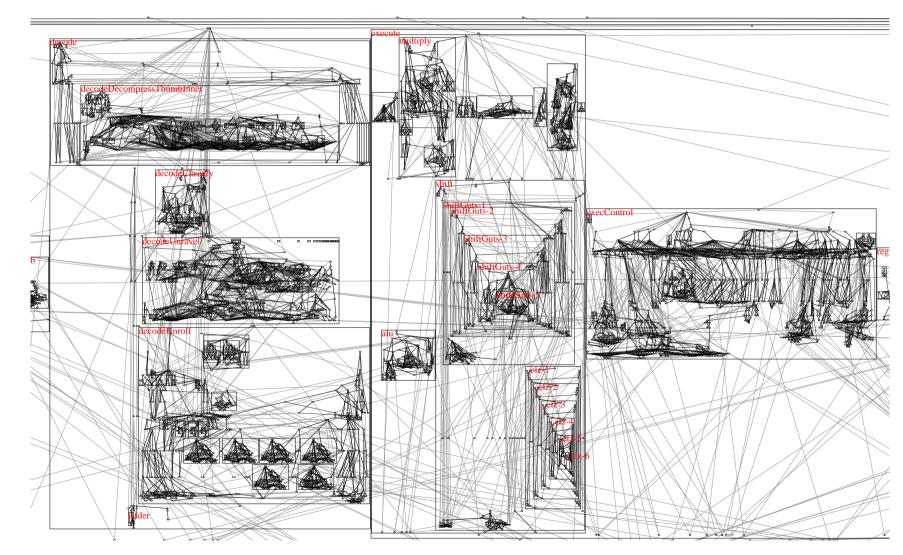

| 9.7        | Huge graph layout: SPA - Zoom 900%                                                                           | 143      |

| 9.8        | Huge graph layout: SPA - Zoom 4500%                                                                          | 144      |

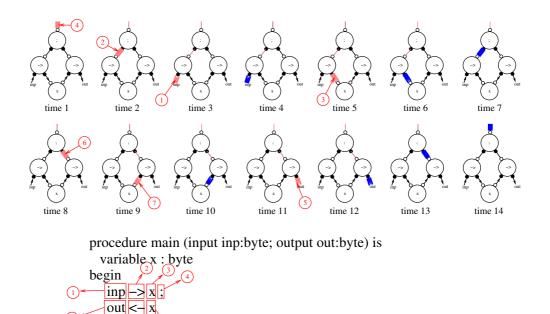

| 9.9        | Step by step animation of a 1-place buffer                                                                   | 146      |

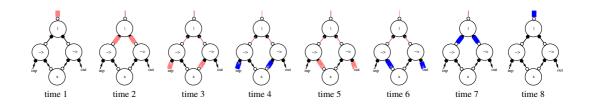

|              | Step by step animation of a hypothetical parallel circuit     | 146 |

|--------------|---------------------------------------------------------------|-----|

| 9.11         | High level SPA animation snapshot with bars in groups         | 147 |

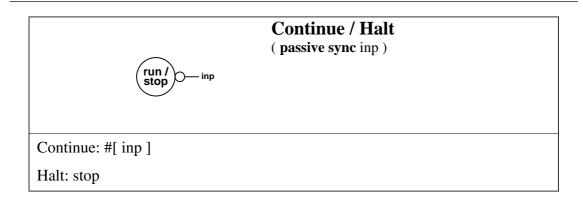

| <b>B</b> .1  | Continue and Halt handshake components                        | 160 |

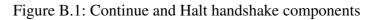

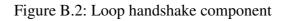

| B.2          | Loop handshake component                                      | 160 |

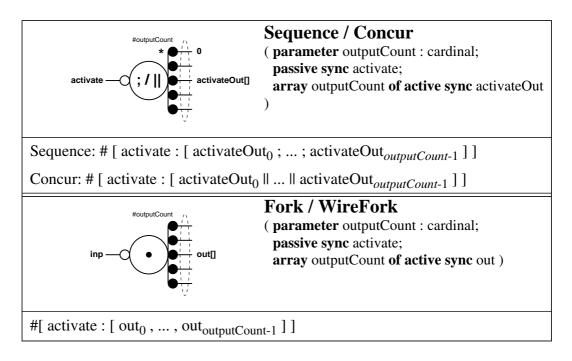

| B.3          | Sequence, Concur, Fork and WireFork handshake components      | 160 |

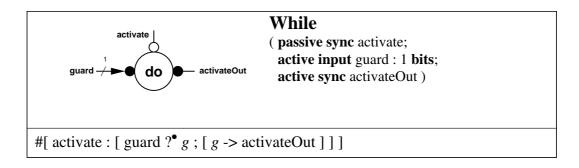

| <b>B.</b> 4  | While handshake component                                     | 161 |

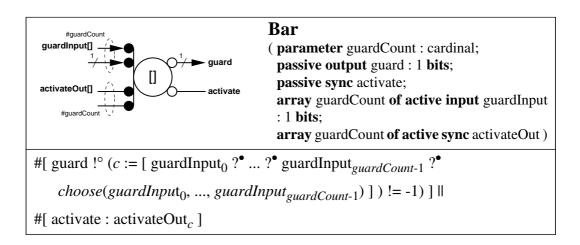

| B.5          | Bar handshake component                                       | 161 |

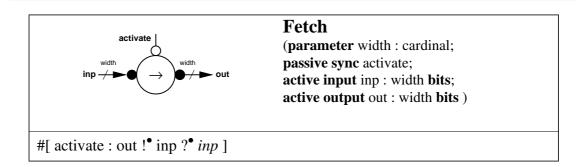

| B.6          | Fetch handshake component                                     | 162 |

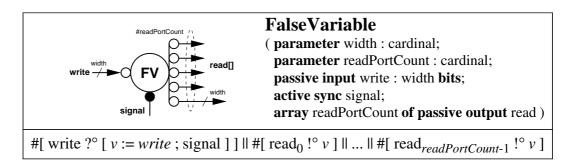

| B.7          | FalseVariable handshake component                             | 162 |

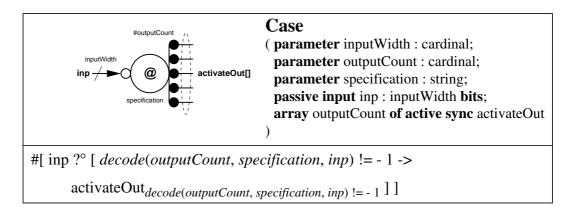

| B.8          | Case handshake component                                      | 162 |

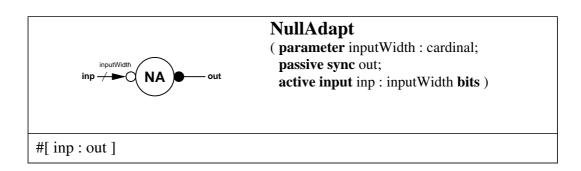

| B.9          | NullAdapt handshake component                                 | 162 |

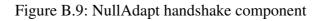

| B.10         | Encode handshake component                                    | 163 |

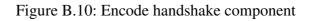

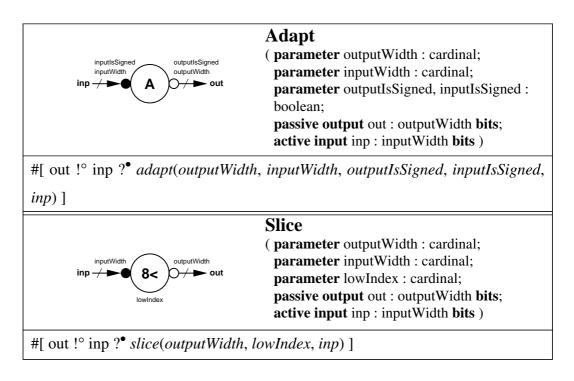

| <b>B</b> .11 | Adapt and Slice handshake components                          | 163 |

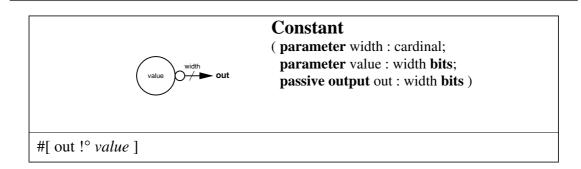

| B.12         | Constant handshake component                                  | 164 |

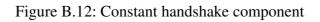

| B.13         | Combine and CombineEqual handshake components                 | 164 |

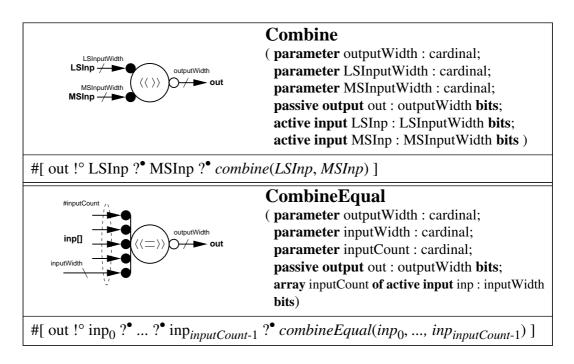

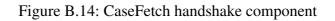

| B.14         | CaseFetch handshake component                                 | 164 |

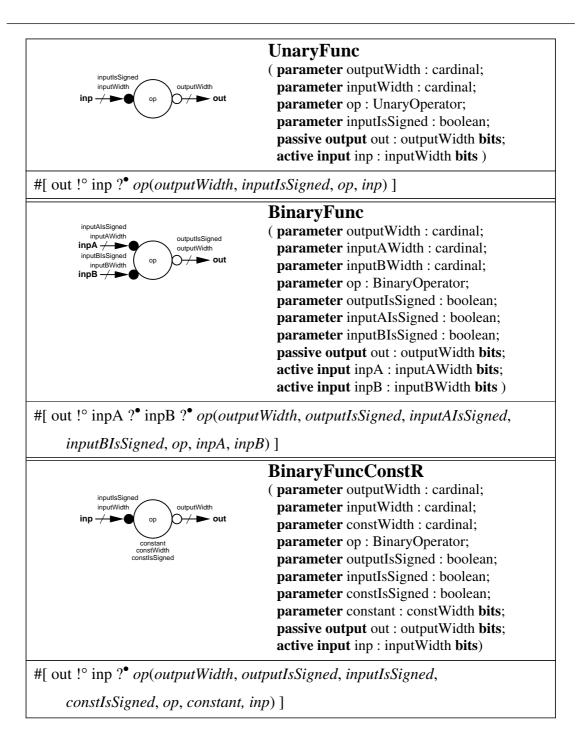

| B.15         | UnaryFunc, BinaryFunc and BinaryFuncCont handshake components | 165 |

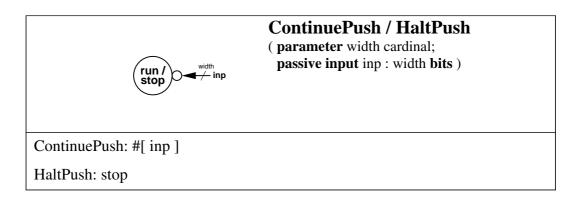

| B.16         | ContinuePush and HaltPush handshake components                | 166 |

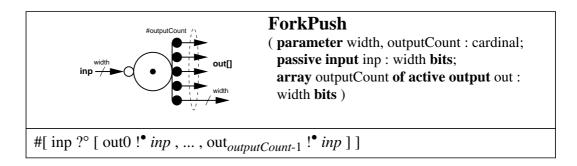

| B.17         | ForkPush handshake component                                  | 166 |

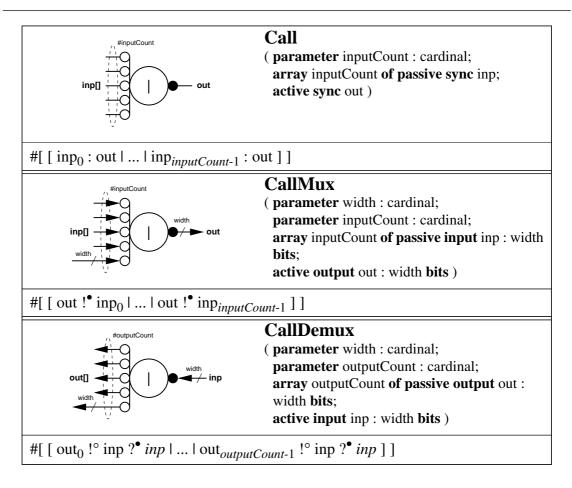

| B.18         | Call, CallMux and CallDemux handshake components              | 167 |

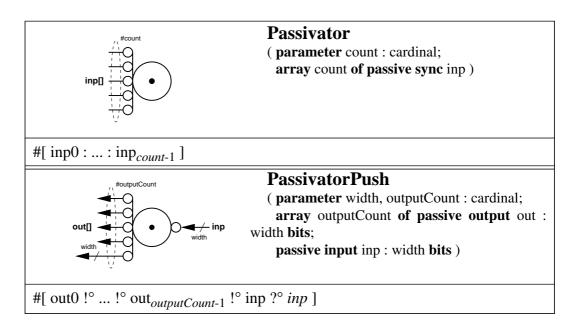

| B.19         | Passivator and PassivatorPush handshake components            | 167 |

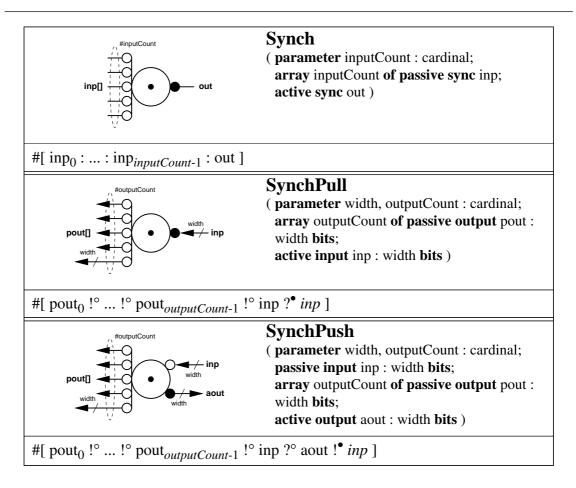

| B.20         | Synch, SynchPull and SynchPush handshake components           | 168 |

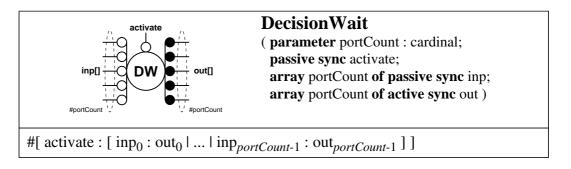

| B.21         | DecisionWait handshake component                              | 168 |

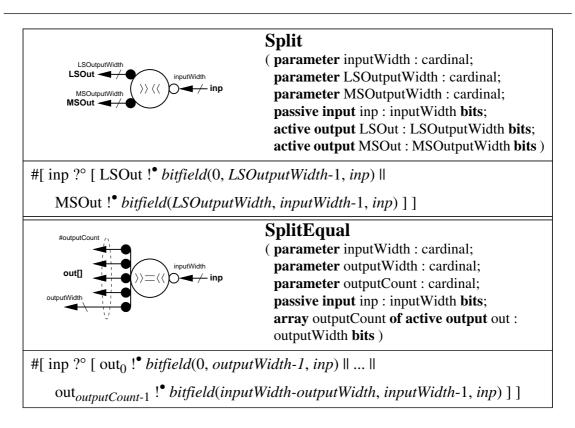

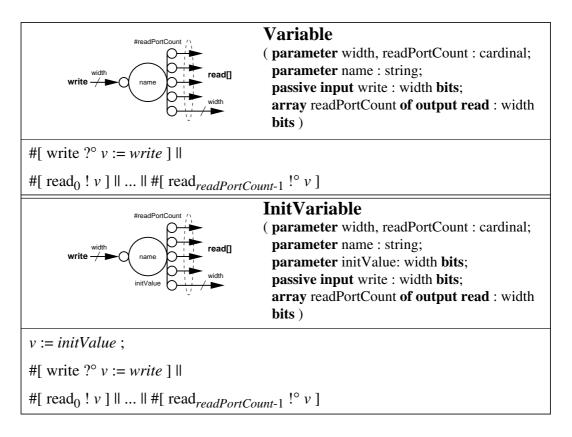

| B.22         | Split and SplitEqual handshake components                     | 169 |

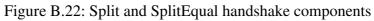

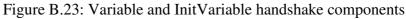

| B.23         | Variable and InitVariable handshake components                | 169 |

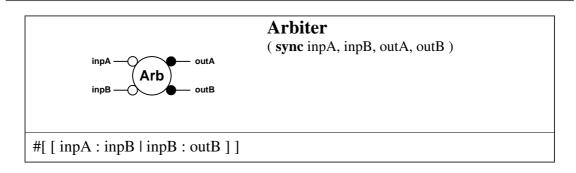

| B.24         | Arbiter handshake component                                   | 170 |

## List of Tables

|     | Visualised elements per view<br>Visualised elements per source | 114<br>114 |

|-----|----------------------------------------------------------------|------------|

| 9.1 | Evolution of the compilation speed                             | 127        |

| 9.2 | Evolution of the simulation speed                              | 128        |

| 9.3 | Comparison of Breeze and Verilog simulators                    | 130        |

| 9.4 | Design iteration speedup                                       | 130        |

| 9.5 | Trace compression results                                      | 138        |

| A.1 | Size of Balsa circuits examples                                | 154        |

## Abstract

Recent advances in automated synthesis tools for asynchronous circuits have made possible the design of large self-timed circuits. However, these new tools are still weak in their behavioural simulation and debugging capabilities because asynchronous circuits pose different challenges and opportunities in these areas from conventional clocked circuits. Balsa is such a tool intended for the synthesis of large asynchronous circuits by using handshake circuits as an intermediate representation.

This thesis addresses new simulation and visualisation techniques for debugging large scale asynchronous circuits at the handshake circuit level. It is based on extensive behavioural simulation and large scale visualisation of handshake circuits.

A set of optimisation techniques applicable to the simulation of handshake circuits leads to a simulator four orders of magnitude faster than the previous Balsa simulator on large circuits. A visualisation system targeting program comprehension by efficiently tracking control flows is presented. It is based on two techniques: First, a graph-based view of the handshake circuit merges multiple sources of information to generate a graph viewable at any level of detail, with dynamic simulation results rendered atop it. Then, a collaborative scheme between multiple views allows the tracking of elements between views for efficient navigation.

The framework is evaluated on the largest circuit described with Balsa so far, an ARMcompatible asynchronous microprocessor.

## Declaration

Most of the figures and descriptions contained in Appendix B were originally described by Bardsley [5]. They have been reproduced here and updated with the permission of the author.

No other portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- (1) Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

- (2) The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without permission of the University, which will prescribe the terms and conditions of any such agreement.

- (3) Further information on the conditions under which disclosures and exploitation may take place is available from the Head of the Department of Computer Science.

## Acknowledgements

It is a pleasure to thank the many people who have contributed to my happiness during these last four years and made this thesis possible.

I would like to thank first my supervisor, Dr. Doug Edwards, for his kindness, for the freedom he gave me and for always being there at the right time to guide me.

Thanks to Dr. Andrew Bardsley for the many explanations and advice about Balsa, and thanks to everybody in the APT group for their friendship.

Special thanks to my local proofreaders: Peter Riocreux, Dr. Andrew Bardsley, Dr. John Bainbridge, Dr. Luis Plana and Sam Taylor for fixing my French style as much as they possibly could, and also for being such nice colleagues and friends. I could never thank Andrew enough for reading the whole of my thesis so quickly, nor Peter for reading it twice even more quickly, saving me from the deadline.

Another set of proofreading thanks goes to my French friends: Fred Lapin Lacombe, Régis Décamps, Alexandre Klimowicz, Franck Bettinger and Nicolas Gaborit. They have been extremely helpful.

Thanks to all my friends: Franck, Nicolas, Fabrice, Vivek, Bruno, Racoon, Alexandre, Régis, Jérôme, Laurent, Arnaud, Aymeric, Nathanaël and all the others for enjoying some time with me. And a giant thank you to Lapin, who was there for me in critical times.

Finally I'd like to thank Yin Jin, my brothers and sister Florent, Marion and Jean, and my parents for their love.

## Chapter 1: Introduction

This thesis is concerned with techniques to support the debugging of large asynchronous handshake circuits by using extensive simulation and large scale visualisation methods. These techniques are applied to the Balsa asynchronous circuit synthesis framework.

## 1.1 Large Scale Asynchronous Handshake Circuits

Very Large Scale Integration (VLSI) is the current level of computer microchip miniaturisation and refers to electronic circuits on a chip containing more than hundreds of thousands of transistors. A computer microprocessor is an example of VLSI chip.

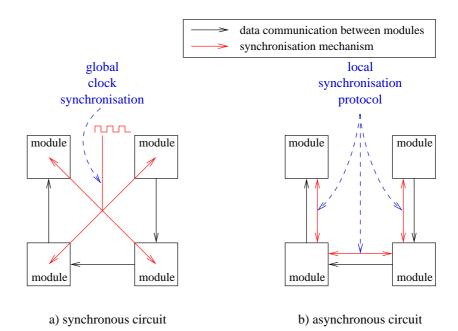

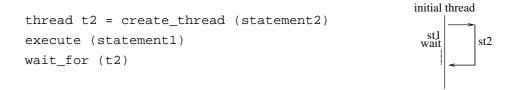

VLSI designs can be divided into two major classes: synchronous and asynchronous circuits. Synchronous circuits use a periodic signal called a *clock* to synchronise every part of the circuit. The clock signal is distributed throughout all parts (or *modules*) of a system to ensure correct timing and to synchronise the data processing mechanisms. Asynchronous circuits contain no global clock. The synchronisation required for data transfers between two modules is controlled by locally generated signals (Figure 1.1). One major class of asynchronous circuits uses a synchronisation method between modules called *handshaking*. Handshaking is used to synchronise two independent asynchronous modules for data transfer by observing the following scheme:

- 1. The sender places the data onto the data wires.

- The sender notifies the receiver by changing the value of a specific wire meaning:

"The data on the data wires is valid, you can read it".

- 3. The receiver receives the message and processes the data.

- 4. The receiver notifies the sender by changing the value of a specific wire meaning:"I have finished using the data".

- 5. The sender receives the message and continues its processing.

Figure 1.1: Synchronous and asynchronous mechanisms

Unfortunately, the complexity added by the local handshake protocols required in every asynchronous module makes asynchronous circuits more difficult and expensive to build in terms of circuit area and power consumption. For this reason, they have stayed a niche research area restricted to universities for many years, while synchronous methodologies and tools were developed at a high pace by companies. However, with the development of million-transistor chips, new difficulties have appeared with synchronous circuits which are more easily overcome by the asynchronous design style. The most important of these problems are:

- *Clock skew*: As the size of a chip and the number of modules increase, the clock network required to distribute the clock signal all over the chip becomes more complex. This leads to tiny differences in propagation delay known as clock skew, which can affect the correct synchronisation of the modules.

- *Non-adaptation to environmental conditions*: As environmental conditions (such as temperature, voltage, etc.) change, the propagation delays of the signals inside parts of the chip can become slower or faster. This further increases the effects of clock skew problems.

- *Electromagnetic interference*: In a synchronous circuit, all the modules get synchronised by the same clock events. This generates peaks of activity at every clock tick leading to electromagnetic interferences. In an asynchronous circuit, modules are only synchronised to their close neighbours. This tends to distribute electromagnetic emissions over time and therefore avoid the interference peaks.

- Power management: When a synchronous circuit has nothing to do, it can either let

its clock circuitry work, thus consuming energy, or it can stop the clock in order to

save this energy. Unfortunately, restarting stopped clock circuitry takes some time

before stabilisation. This makes power management in synchronous chips complex.

In asynchronous chips, when no processing is to be done, no activity happens at all,

and thus no energy is consumed without the need for any special power

management.

Noting the increasingly important qualities of asynchronous technology, a growing interest from the industry in asynchronous circuits is now stimulating research in design methodologies and the development of design tools which can be used to develop efficient asynchronous VLSI designs.

## 1.2 Automated Circuit Synthesis

Circuit synthesis refers to the process of transforming a problem description (usually in the form of a program) into a hardware circuit. Each step of the synthesis process can be made either manually or automated by using Computer Aided Design (CAD) tools. In the past, asynchronous CAD tools were limited to the design of individual small controllers [26, 41, 116], and thus were only useful for small portions of the final circuit. Some large scale asynchronous systems have been designed manually, allowing aggressive, hand-made optimisations, but at the expense of requiring a cumbersome, slow and error-prone design process. For example, the Amulet3 processor [46] took 20 man-years to complete and the Intel asynchronous instruction-length decoder chip [88] took 9 man-years, using a combination of manual techniques and academic synthesis tools for designing individual controllers. Synchronous hardware description languages (HDLs) and tools were able to handle parts of the design process, but could not tackle asynchronous specific problems such as fine-grained parallelism, deadlocks and non-determinism (see §2.1.4).

Nowadays, a few all-encompassing design methodologies and CAD tools able to handle the overall synthesis flow of asynchronous systems have emerged. The most scalable ones are syntax-directed tools [17] and can be used for VLSI designs. Other asynchronous complete CAD flows have been developed and used for large circuits such as the Caltech design methodology [115] and the NCL design flow [95, 109]. The syntax-directed model starts from a high-level abstraction, such as a concurrent program, and produces a circuit by translating each individual program construct into a corresponding sub-circuit. The proprietary Philips' *Tangram* tool [82], developed by van Berkel et al., and *Balsa* [4], developed at the University of Manchester follow this model. The work in this thesis is based on the Balsa system.

Balsa and Tangram have proven their ability to synthesise full VLSI circuits [6, 43]. However, these high-level asynchronous CAD tools suffer major deficiencies:

- lack of aggressive automatic optimisations [21, 99]

- lack of debugging capabilities.

The research work presented in this thesis deals with the last point.

## **1.3 Motivations and Objectives**

The long-term aim of this work is to provide the Balsa CAD tool suite with a debugging system able to handle the peculiarities of asynchronous circuits.

The short-term motivation for this work was to help with the ongoing development of SPA, a synthesised ARM-compatible processor core designed at the University of Manchester and intended for use in third generation smartcards [84]. It is described entirely in Balsa, and the two last years of the SPA project overlapped with the two first years of this thesis. SPA is currently the largest circuit synthesised with Balsa, and is composed of about ten thousand asynchronous components, a huge number to deal with. (Making a comparison with the field of graph manipulations, graphs over a thousand nodes are considered huge). A part of the work presented here is the result of extending the capabilities of the Balsa suite with tools which are appropriate for the final validation

of SPA. In return, SPA has been used as a test case to evaluate the different aspects of this work.

The validation checks that the SPA processor passes all the 76 programs constituting the ARM architecture validation suite. In the execution of this validation suite, the most important aspect was simulation speed. The original simulation time of almost two weeks per test needed to be improved considerably. Moreover, decent simulation speed is the basis for a good debugging system as debugging information is collected during the simulation process. A fast simulator also allows repetitive tests on complex designs to be processed for design iterations and design-space exploration.

The design of a fast simulator led to the need for a tool able to trace back and pinpoint the causes of incorrect behaviour during simulation. A handshake circuit debugger was thus developed. The debugger was then extended for fixing not only problems with the simulator, but also the simulated Balsa descriptions. For this reason, the debugger was developed to recognise and treat special asynchronous failure modes such as deadlocks and non-determinism. The simulator was extended to report the information necessary for this analysis. Finally, as the size of Balsa circuits was becoming larger, a visualisation system appeared to be useful. It needed to display graphically all the information needed for the comprehension and debugging of the handshake circuit, linking all the different aspects of the circuit together: the pre-compilation Balsa code, the post-compilation handshake circuit, the dynamic simulation events, and the various results of simulation analysis such as control and data flows.

## 1.4 Contributions made by this work

This work commenced with the idea of simulating Balsa directly at the handshake circuit level. Although this idea cannot be considered as a contribution by itself, it led to the following discoveries and achievements:

- Four orders of magnitude Balsa simulation speedup

- Ideas for debugging asynchronous-specific problems at the handshake circuit level identifying:

- deadlocks

- non-determinism

- Pattern analysis of the out-of-order simulation trace, with direct applications to:

- debugging of livelocks

- compression of simulation traces

- clustering for better visualisation

- Following the execution of a circuit for program comprehension:

- Merging complementary sources of information together to generate a graph viewable at any level of detail

- Colour-based graph animation to highlight handshake circuit control flows

- Coordinating this graph view and the various views "well-known to the designer" together for an efficient element tracking and easy navigation

- The first published debugging environment for large scale asynchronous circuits.

## 1.5 Thesis Overview

Chapter 2 describes the fundamentals of asynchronous design and graph theory used in the rest of the thesis. Nomenclature and notations are introduced there. Balsa, the language and framework on which this research is based, is described.

Chapter 3 addresses other research works similar to that presented in this thesis, and exposes their differences, strengths and weaknesses.

Chapter 4 investigates the theoretical requirements for debugging asynchronous handshake circuits. Classical asynchronous problems of deadlocks, non-determinism and metastability are studied and applied to handshake circuits. Problems specific to large scale debugging are also examined, with some solutions proposed to solve the problem of the huge amount of data generated by the simulation of such systems.

Chapters 5 and 6 explore the design of a handshake circuit simulator, first by targeting high performance, then by taking into account the various requirements for gathering data for off-line analysis, visualisation and circuit debugging.

Chapter 7 examines the requirements for a visualisation system able to represent effectively the large amount of data, the fine-grained concurrency and the different steps of the synthesis process together.

Chapter 8 describes the integration of the debugging, simulation and visualisation aspects into a unified framework.

Chapter 9 presents an evaluation of the framework developed after the ideas uncovered by this thesis. It shows how the framework can be successfully employed on real-life examples.

Finally, Chapter 10 concludes the thesis by summarising the contributions and their deficiencies. Some guidelines for future possible work are suggested.

## 1.6 Publications

The following papers have been presented at conferences:

- Debugging Tools for Asynchronous Design [58]

(10th UK Asynchronous Forum, no peer review)

- A Visualisation System for Balsa Simulations [59]

(12th UK Asynchronous Forum, no peer review)

The following journal paper has been published:

Simulation and Visualisation of Asynchronous Circuits [60] (International Journal of Simulation: Systems, Science & Technology).

## Chapter 2: Background

This chapter provides an introduction to asynchronous design. The information presented here is intended to set the context for the description of the simulation system developed in the subsequent chapters.

First, the terminology and the major styles of asynchronous design are introduced. Then, the difficulties of metastability and deadlocks specific to asynchronous circuits are presented. The main asynchronous specification techniques are then described, concluding with a description of Balsa and handshake circuits, which form the basis of this work. Finally, graphs are introduced as a way to represent and manipulate handshake circuits.

## 2.1 Asynchronous Design

In asynchronous circuits, data is passed between modules using groups of wires, known as *channels*. These channels are unidirectional, point-to-point connections. Over the years, a number of different asynchronous channel implementations have been defined. In such channels, the data typically flows in one direction between two modules:

- The *sender* is the module that delivers data onto the channel.

- The *receiver* is the module that accepts data from the channel.

Orthogonal to this classification is the concept of *control flow*, determined by which end caused the transfer to occur:

- The *initiator* is the module that caused the transfer to begin.

- The *target* is the module that responds to the initiator.

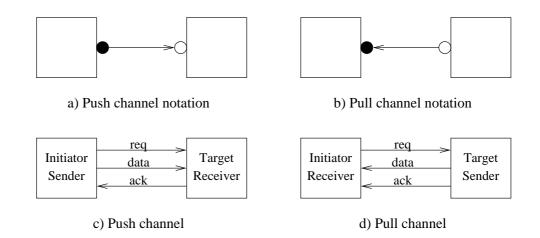

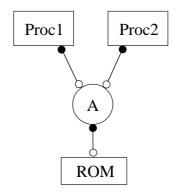

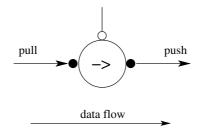

A channel is connected to a module via a *port*. A port connected to an initiator is an *active* port while a port connected to a target is a *passive* port. As illustrated in Figure 2.1a and 2.1b, the graphical notation used to represent channels uses the filled and empty circles to denote the active and the passive partners in the handshake procedure respectively.

The relative direction of the data flow compared to the control flow determines whether the channel is classified as a *push* channel (where the sender is the initiator of the communication) or a *pull* channel (where the receiver is the initiator of the communication). These two types of channel are illustrated in figures 2.1c and 2.1d. Designers often speak of pushing or pulling data, thus implying the protocol used. A channel which does not transmit any data, and has therefore only a control part, is called a *sync* (or *nonput*) channel.

Figure 2.1: Push and pull channel notations

Which module performs which function on a channel is determined by the protocol and the transfer direction.

Most of the popular asynchronous handshaking approaches can be classified using the following three criteria, explained below:

- signalling protocol,

- delay model,

- data encoding.

## 2.1.1 Handshake Signalling Protocols

The transfer of information between two computation blocks across a channel is negotiated using a signalling protocol. Every transfer features a request action (req) where the initiator starts a transfer, and an acknowledge action (ack) allowing the target to respond. These may occur on dedicated signalling wires, or may be implicit in the data encoding used (as described below), but in either case, one event indicates data validity, and the other signals its acceptance and the readiness of the receiver to accept further data. These control signals carry all the necessary timing information to provide for proper data communication and can also be used as a mechanism for synchronising two modules without the explicit transfer of data (e.g. to implement token passing schemes or control shared resources).

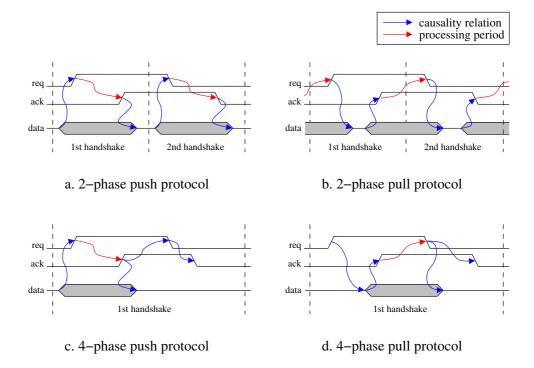

The request and acknowledge may be passed using one of the two popular protocols described below: either a 2-phase transition signalling protocol (a non return-to-zero scheme) or a 4-phase level signalling protocol (a return-to-zero scheme). Conversion between the different protocols is possible [66].

#### 2-phase (transition) signalling

In the 2-phase signalling scheme, transitions on wires are interpreted as signalling events. The level of the signal is not used and a transition carries information with rising edges being equivalent to falling edges. A push channel using the 2-phase signalling protocol thus passes data using a request signal transition, and acknowledges its receipt with an acknowledge signal transition. Figures 2.2a and 2.2b illustrate the push and pull data validity schemes for the 2-phase signalling protocol. Arrows indicate causality between events.

Proponents of the 2-phase design style try to use the lack of a return-to-zero phase to achieve higher performance and lower power circuits.

#### 4-phase (level) signalling

The 4-phase signalling protocol uses the level of the signalling wires to indicate the validity of data and its acceptance by the receiver. When this signalling scheme is used to pass the request and acknowledge timing information on a channel, a return-to-zero phase

Figure 2.2: Channel signalling protocols

is necessary so that the channel signalling system ends up in the same state after a transfer as it was in before the transfer. This scheme therefore uses twice as many signalling edges per transfer than its 2-phase counterpart. Push and pull variants of the 4-phase signalling protocol are shown in figures 2.2c and 2.2d.

4-phase control circuits are often simpler than those of the equivalent 2-phase system because the signalling lines can be used to drive level-controlled latches, and the like, directly.

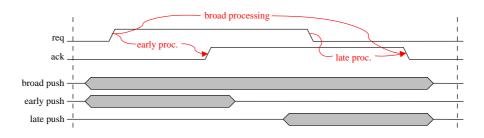

Data validity in 4-phase handshakes can be signalled in a number of ways, the most common of which (*broad*, *early* and *late* data validity) are illustrated with push channels in Figure 2.3.

### 2.1.2 Delay Models

Delays in digital circuits are associated with wires and gates. The effects of delays on systems are often characterised using a *delay model*. Delay models can be divided into

Figure 2.3: 4-phase push data validity schemes

three categories: fixed, bounded and unbounded delay models. In the fixed delay model, delays are assumed to have fixed values. In the bounded delay model, delays may have any value in a given interval. In the unbounded delay model, delays can have any finite value.

The fixed delay model is rarely used for the construction of asynchronous circuits since small variations in fixed delays could lead to significant differences in switching activity and break the model. The bounded delay model was commonly used in the early days of asynchronous design and is still used in some interconnection schemes such as the SCSI bus [94] where part of the protocol is based upon known, fixed delays allowing small variations. It is also commonly used for datapath components, where it can lead to smaller implementations.Delay variations are estimated by considering factors such as data dependence, statistical process variation, temperature and supply voltage variation. Current asynchronous VLSI designs and research efforts mostly use the unbounded delay model for the implementation of state-machines and controllers since it leads to circuits that will always operate correctly whatever the distribution of delays. This model separates delay management from the correctness issue, allowing the functionality of the circuit to be more easily verified.

Within the unbounded delay model, various design styles are commonly used, each with its own merits and problems. In order of increasing number of timing assumptions the major ones are:

#### **Delay-insensitive (DI) circuits**

A circuit whose operation is independent of the delays in both circuit elements (gates) and wires is said to be delay-insensitive. DI circuits require no timing constraints or assumptions to be preserved for circuit functionality to be guaranteed. Unfortunately, at the gate level, few interesting circuits conform to the delay-insensitive ideal [69]. For this reason, delay-insensitivity is most often applied to larger, more coarsely grained units, constructed using other timing regimes in order to make them easier to compose. This is the case with the handshake circuits used throughout this thesis.

#### Quasi delay-insensitive (QDI) circuits

If the difference between signal propagation delays in the branches of a set of interconnecting wires is negligible compared to the delays of the gates connected to these branches then the wires are said to form an isochronic fork [10]. Circuits created using the DI design style, augmented with the isochronic fork assumption, are said to be quasi delay-insensitive (QDI).

#### Speed-independent (SI) circuits

If wire delays in a circuit are assumed to be zero (or, in practice, less than the minimum gate delay), and the circuit exhibits correct operation regardless of the delays in any circuit elements, then the circuit is said to be speed-independent. The assumption of zero wire delay is valid for small circuits.

In general, SI circuits and QDI circuits are regarded as equivalent from the modelling point of view.

### 2.1.3 Data Encodings

A further dimension in asynchronous design is the choice of encoding scheme used for data representation where the designer must choose between a single-rail, dual-rail, or other more complex N-of-M schemes (any other encoding is possible, but these ones are the most popular ones). These alternatives are discussed in the following paragraphs.

#### **Single-rail encoding**

Single-rail encoding [82] uses one wire for each bit of information. The logical level of the signal represents either a logic 1 or a logic 0. This encoding is the same as that conventionally used in synchronous designs. Timing information is passed on separate request and acknowledge lines which allow the sender to indicate the availability of data and the receiver to indicate its readiness to accept more new data. This scheme is also known as the *bundled-data* approach. All single-rail encoding schemes contain inherent timing assumptions in that the delay in the signal line indicating data readiness must be no less than the delay in the corresponding data path.

Single-rail design is popular, mainly because its area requirements are similar to those of synchronous design, as is the construction of any arithmetic components using this scheme.

#### **Dual-rail encoding**

Dual-rail circuits [81] use two wires to represent each bit of information. Each transfer involves activity on only one of the two wires for each bit. A dual-rail circuit thus uses  $2 \times n$  signals to represent *n* bits of information. Timing information is implicit in the code, in that it is possible to determine when the entire data word is valid by detecting a level (for 4-phase signalling) or an event (for 2-phase signalling) on one of the two rails for every bit in the word. A separate signalling wire to convey data readiness is thus not necessary. The standard level-sensitive dual-rail data encoding technique uses the following four states for each bit of information:

- 00 initial state, data is not valid

- 10 transmission of a logical zero

- 01 transmission of a logical one

- 11 illegal state.

Once the data has been transmitted the wires must be returned to their initial state. And so, the presence of new data is indicated by a transition on one of the propagation wires. The illegal state is not used in dual-rail data encoding.

The major disadvantage of using dual-rail data representation compared to single-rail data encoding, where each wire represents one bit of binary information, is that its implementation requires twice as many wires and, as a consequence, leads to larger and more power-hungry circuits. Area overhead also comes from the large fan-in networks required to detect an event on each pair of wires in order to determine when the word is complete before being able to begin the next stage of processing.

#### **N-of-M encoding**

N-of-M encodings are using groups of M wires to encode data values by considering a data valid as soon as N wires are activated.

Dual-rail encoding is an example of an N-of-M encoding scheme where N=1 and M=2. Coded data systems using an N-of-M code operate correctly regardless of the distribution of delay in the wires or gates, and are thus delay-insensitive [111].

1-of-M codes are mostly used [3]. More complex codes, where N>1, use actions on more than one wire in a group to indicate one of a set of possible codes. These offer better utilisation of the available wires (for example a 2-of-7 code can transmit 4-bits of information over 7 wires in a delay-insensitive manner), but result in larger arithmetic circuits and conversion between the coded form and a single-rail scheme is more expensive than for the 1-of-M codes.

### 2.1.4 Asynchronous Difficulties

#### **Metastability and Arbitration**

Some asynchronous modules require their inputs to be mutually exclusive. For this, a special component is usually designed to provide *arbitration* between two contending asynchronous inputs. The basic circuit needed to deal with such situations is a mutual exclusion element (mutex) with two inputs and two outputs [91]. The role of the mutex is to pass the signals received on its two inputs to the corresponding outputs in such a way that at most one output is activated at any given time. If only one of the two inputs is activated, the mutex activates the corresponding output. If an input gets activated while the first input is already activated and its output selected, then the second input waits. A problem arises when both inputs are activated at the same time, or within a small time

window. The mutex' internal signals hover for an unbounded amount of time before reaching a stable state and selecting one of the outputs [27]. This problem is known as *metastability*, and the act of determining which event came first is called *arbitration*.

The condition for a mutex to go metastable is to have its two inputs activated within a small time window  $\Delta$ . The size of this time window can be determined by experiments or simulations, and a representative value for good circuit designs implemented with a 0.25µm fabrication process is  $\Delta = 30$ ps [96].

Once the mutex is in a metastable state, the probability of still being metastable at a given time *t* is:

$$P(met_t | met_{t=0}) = e^{-\frac{t}{\tau}}$$

where  $\tau$  expresses the ability of the mutex to exit the metastable state spontaneously, and  $P(met_t)$  is the probability of being metastable at time *t*. In the same conditions as for the time window, a representative value of  $\tau$  is  $\tau = 25 ps$ .

The notions of non-determinism and race condition can also be defined. *Non-determinism* is when the next action of a system is not fully determined by its current state. This happens when a mutex arbitrarily chooses one of its outputs rather than the other. A *race condition* happens when two or more system entities potentially may be competing for resources (an arbiter component) at some time during execution.

#### Deadlocks

A set of processes (which will be the handshake components of this thesis) is said to be *deadlocked* if each process in the set is waiting for an event that only another process in the set can cause.

A typical high-level example of an asynchronous processor system deadlock is as follow [96]:

1. A (non-sequential) data transfer needs access to a particular RAM block.

- 2. This is prevented because an instruction fetch is already using the RAM array.

- 3. The instruction fetch cannot complete because the instruction decoder is still busy.

- 4. The processor pipeline is full and is blocked by the data fetch.

- 5. Deadlock.

In contrast with synchronous circuits, working through deadlock problems during the design of asynchronous systems is very common. Without implicit global clock control, the control logic in an asynchronous design is more complex than in a synchronous equivalent design since each module of the design requires hardware to perform synchronisation, to wait for data, and to trigger other modules when it has produced its data. The use of explicit communications between modules increases the risk of introducing deadlocks. This problem can be introduced by design errors. Ideally, deadlocks should be detected and then avoided at a very early stage in the design process. Unfortunately, current formal validation techniques [7] cannot cope with large designs. Instead, designers use extensive simulation to give good confidence in design functionality.

## 2.2 Asynchronous Specification Techniques

A number of specification techniques are available to the asynchronous designer. Those for which an automated synthesis route (automated translation from specification to hardware) is currently available are summarised here. For small-scale asynchronous designs, two classes of specification are commonly used: state-based and event-based. As these techniques do not scale well, they are usually used for the construction of small modules, which are then assembled together to create larger designs.

### 2.2.1 Event-Based Specification

Petri nets [83] can be used to describe and study the behaviour of systems in terms of sequences of events, incorporating the concurrency and causality between the events.

Based upon the foundations laid by Rosenblum and Yakovlev [87], current event-based asynchronous circuit synthesis methodologies use interpreted Petri nets as the input specification with the transitions labelled with signal names [26]. These graphs are known

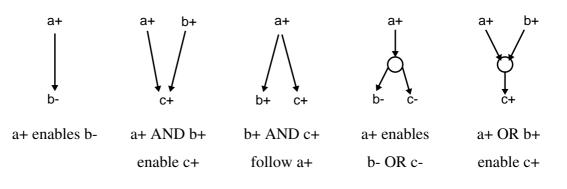

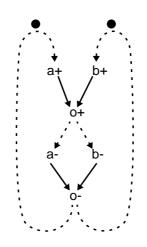

as Signal Transition Graphs (STG). In the STG notation, transitions describe signal activity and can model a rising signal, a falling signal or a change in level. Dependencies and causalities are represented in the STG using the notations shown in Figure 2.4. As an example of the STG specification style, Figure 2.5 shows the specification of a two input Muller C-element (which is a AND function for events, defined as follow: A transition will occur on the output only when there has been a transition on both inputs) with inputs *a* and *b* and output *o*. The dotted arcs show the behaviour of the circuit's environment, and the solid arcs show the behaviour of the circuit (the Muller C-element in this case). The use of Petri nets in circuit design makes it easy to describe systems which are concurrent at a very fine level. This kind of concurrent operation can be more difficult to express in state diagrams without drawing multiple diagrams or resorting to expanding the Cartesian product of the states of all the concurrent portions of a design.

Figure 2.4: STG notation

Figure 2.5: STG specification for a 2 input Muller C-element

Petri nets and state graphs also use different semantics of concurrency. The true concurrency semantics, used in Petri nets and their unfoldings, models concurrency by partial order of events, avoiding combinatorial explosion. However, the interleaving approach used in state graphs, models concurrency indirectly, or "sequentially", i.e. by means of all possible interleavings.

### 2.2.2 State-Based Specification

Huffman state machines [54] are the classical asynchronous finite state machines. They follow the fundamental mode assumption in which the environment must wait long enough for the output data to stabilize on the circuit outputs (a bounded delay model), and the condition of only one input changing at a time. Burst-mode machines, as introduced by Stevens [98] and formalised by Nowick [79], and extended burst mode machines are a relaxation of the single input change. A design approach to building burst-mode finite state machines was proposed by Nowick et al. [80]. According to this approach:

- Each state transition can occur under a certain set of input changes (so called an input burst) so that no burst from a particular state can be a subset of another burst from the same state.

- Any state must be entered with the same set of input values.

The proposed timing mechanism allows the burst-mode finite state machine to be moved to a new state whenever the output associated with the previous state has changed, enabling the input signals to be changed. A burst-mode oriented backend for the Balsa synthesis system using the MINIMALIST tool [41] was proposed by Chelcea et al. [21].

## 2.2.3 Communicating Sequential Processes

Communicating Sequential Processes (CSP) is a model developed by Hoare to describe concurrency by using parallel composition of processes communicating through channels [52].

Martin first suggested a synthesis method to manually compile a CSP description into DI circuits [68], where each process was synthesised as an asynchronous module, and where communications were following a handshake protocol. This work set the basis for a series

of macromodular synthesis methods, of which Balsa is an example. They are described in the following section.

### 2.2.4 Macromodules and DI Interconnect

*Macromodular* methodologies make use of pre-built modules connected together by handshaking channels to construct circuits [101]. This allows the use of a delay-insensitive style of interconnect between the modules, which is difficult to achieve at the gate level. The modules can have their own internal timing constraints (they can even be clock-driven modules) without affecting the high-level DI properties of the circuit. Other non-DI interconnection styles (e.g. single-rail protocols) can also be used in order to reduce the number of wires, but at the expense of extra-complexity in layout timing validation to ensure that bundling constraints are met.

Macromodular design styles exist for hand construction of circuits and for automated circuit synthesis. *Macromodules* were first developed by Clark at Washington University [24] during the late 1960s as a system for constructing large digital circuits which were composed of pre-built blocks of asynchronously communicating functional units: the macromodules. In his 1988 Turing Award lecture, Ivan Sutherland described an elegant approach to building elastic asynchronous pipelines called *micropipelines* [103], where the control structures were similar to those of macromodules. Micropipelines are an important design style similar to handshake circuits, but limited to the control part of the circuits. In 1989, Brunvand introduced his macromodular synthesis system [16, 17], making use of the channel-based, CSP-like programming language Occam [57, 106] to describe circuits. Descriptions are automatically synthesised into compositions of control, variable read/write and datapath macrocells implemented with 2-phase signalling with bundled data. Following this lead, *handshake circuits* were introduced by Van Berkel for use in the Tangram tool developed inside Philips [11]. The same scheme was later used with Balsa, developed at the University of Manchester by Bardsley [4].

Handshake circuits are macromodular circuits made of *handshake components* connected together via point-to-point asynchronous communication channels. Unlike micropipelines, which are only implementing control components, handshake circuits are composed of both control and data handshake components. In Balsa, these handshake

components are chosen from a cell library of about 45 predefined components parameterisable to a limited degree. Handshake circuits and components are described in the next section with the Balsa framework, and used extensively throughout this thesis.

## 2.3 Balsa

*Balsa* refers to both a framework for synthesising asynchronous circuits and the language for describing such circuits.

The Balsa system uses the *handshake circuits* macromodule-based design paradigm as an intermediate representation for synthesising Balsa designs. Handshake circuits are compiled from specifications in the Balsa language by a syntax-directed compilation scheme. The advantage of this approach is that of a transparent compilation: There is a one-to-one mapping between the language constructs in the specification and the handshake circuits that are produced. It is relatively easy for an experienced user to deduce the arrangement of the circuit that results from the original description. Moreover, incremental changes made at the language level result in predictable changes at the circuit implementation level. This is important if optimisations and design trade-offs are to be made easily at the source level and contrasts with, for example, a VHDL description in which small changes in the specification may make radical alterations to the resulting circuit.

The description of Balsa presented in this section is intended to set the context for the handshake circuit simulation-visualisation-debugging system developed in the rest of the thesis. For this reason, this description is mainly focused on the handshake circuits, which are currently used as an intermediate format in the Balsa synthesis flow. This section starts with an overview of the complete Balsa framework and design flow, followed by a presentation of the main characteristics of the Balsa language. Handshake circuits are then described. The set of macromodules (the handshake components) specific to Balsa, very useful for a deeper understanding of the contents of this thesis, is described in detail in Appendix B.

For further information on the other aspects of Balsa, a complete explanation of Balsa synthesis, including the compilation from specification to handshake circuit and the

transformation from handshake circuit to hardware, can be found in [4, 5]. A more complete description of the Balsa language can be found in the Balsa User Manual [32].

### 2.3.1 Balsa Framework

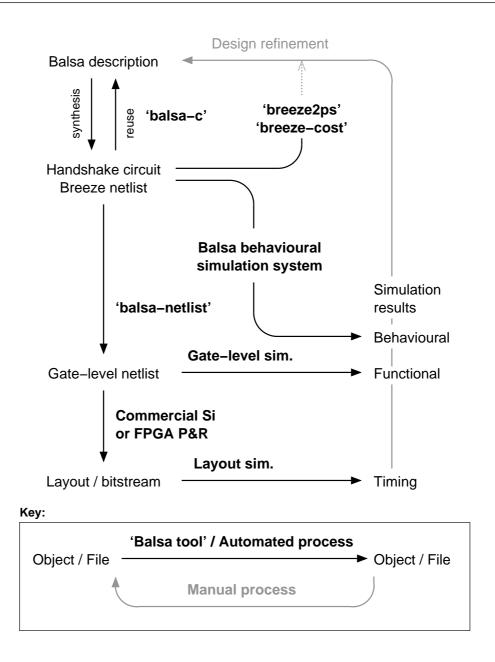

The Balsa framework is a set of tools designed for the synthesis of a Balsa language description into an asynchronous hardware circuit, with an intermediate representation using handshake circuits. As shown in Figure 2.6, the Balsa description is first compiled into a handshake circuit by the Balsa compiler 'balsa-c'. This handshake circuit can then be transformed into a gate-level netlist by the 'balsa-netlist' tool. The same handshake circuit can also be used as a source for the 'breeze2ps' and 'breeze-cost' tools, and for the simulation system. The two tools generate a PostScript file of the handshake circuit graph and an area cost estimate of the circuit respectively, which can be seen as a static analysis of the handshake circuit.

Three design loops are shown in the design flow. These design loops use behavioural, gate level (functional) and final layout (timing accurate) simulation tools respectively to allow simulation to be performed at different points in the design flow. In a typical design, all three levels of simulation complexity are used as the design approaches its final version.

## 2.3.2 Balsa Language

The Balsa language was created as a source language for compiling handshake circuits, with the ambition of satisfying the *directness* property. *Directness* is the ability to map constructs of the input description to modules of the hardware implementation on a one-to-one basis. It allows the user to deduce the arrangement of the final circuit at the time of writing the original source description.

The Balsa language (following the Tangram model [9]) was designed as an imperative, channel-oriented language based on CSP (i.e. with parallel composition and channels). Its transparent syntax-directed compilation to handshake circuits satisfies directness.

Directness is preserved at every step of the synthesis process, so that the final hardware circuit has a one-to-one mapping with the original description's structure. In the Balsa synthesis flow, the compilation process consists of two stages: A Balsa specification is

Figure 2.6: Balsa design flow

compiled into a handshake circuit, which is then transformed into an asynchronous hardware circuit. This second stage of the synthesis, as described in [4], is direct, as each macromodule making the handshake circuit is mapped to a specific piece of hardware. The only threat to directness happens during optimisation of the resulting circuit, but the Balsa tools also try to preserve directness for this operation by only using keyhole optimisations [29].

The modulo-10 counter example shown in Figure 2.7 illustrates most of the Balsa features embedded in the language:

```

import [balsa.types.basic] -- 1

type C size is nibble -- 2

constant max_count = 9

procedure mod10 (sync aclk; output count: C_size) is -- 3

local -- 4

variable count_reg : C_size

variable tmp : C_size

begin

loop -- 5

select aclk then -- 6

if count_reg /= max_count then -- 7

tmp := (count_reg + 1 as C_size) -- 8

else

tmp := 0

end ; -- 9

count <- count_reg ; -- 10</pre>

count_reg := tmp

end

end

end

```

Figure 2.7: Balsa language features (modulo-10 counter example)

1. Pre-compiled module inclusion. In this case [balsa.types.basic] defines some common types: byte, nibble, etc.

- **2.** Type and constant declarations.

- 3. Procedure declaration with sync and output ports.

- 4. Local variables/latches.

- 5. Infinite repetition with loop ... end. Once activated a loop never terminates.

6. Passive input enclosure using select. The commands inside the select are enclosed in the handshake on aclk, aclk is effectively the activation for these commands.

7. if  $\ldots$  then  $\ldots$  else  $\ldots$  end statements.

8. Assignment, expressions and type casting.

9. Sequential composition with ';'. In the same manner, ' $\parallel$ ' specifies parallel composition

at a very fine-grained level.

**10.** Output synchronising communication. The notation for input communications is the other way around: channel -> variable.

A few other important features of Balsa not illustrated in this example are:

- *Structural iterations: for* loop constructs can be used for repeating a block's implementation.

- *Parameterised procedures*: Procedures can be declared with parameters evaluated during compilation.

- *Conditional ports and declarations*: Instantiation of procedure ports and declarations can depend on parameters evaluated during compilation.

- *Recursive procedures*: Recursive calls to parameterised procedures can be used to describe scalable circuits.

- *Shared procedures*: Procedures can be declared to be implemented as a unique circuit and be treated as a resource shared by callers.

- *Nested procedures*: Local procedures can be declared inside procedures.

## 2.3.3 Breeze Handshake Circuit

One of the major contributions of the Tangram project (which Balsa originates from) was the development of handshake circuits, an intermediate representation which both:

- abstracts low-level technology-specific details, and

- supports an elegant translation to asynchronous hardware.

A handshake circuit is built by composing a set of primitive handshake components to form a graph. Handshake circuits combine macromodular design style with delayinsensitive communications to produce a design methodology in which entire designs are described using macromodules connected together by asynchronous communication channels. Each handshake circuit instance is taken from a macromodule library cell and may be parameterised to a limited degree. There are only a small number of such cells defined in a particular handshake component set. Balsa is made of a similar set of handshake components to Tangram. Balsa's handshake components are called *Breeze components*, and circuits made of these components are referred to as *Breeze handshake circuits*.

A handshake component is the abstraction of an electronic circuit able to perform a specific computation. Depending on the level of abstraction desired, the component's internals can either be shadowed as in a black box or revealed to the user. In this work, the handshake components' internals are hidden from the outside world, and only the behavioural and timing characteristics are exposed.

Important note: See Appendix B for handshake component descriptions.

#### Handshake Circuit Graph

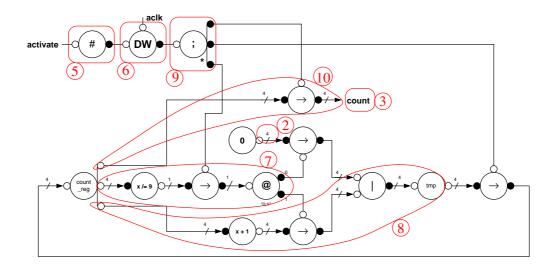

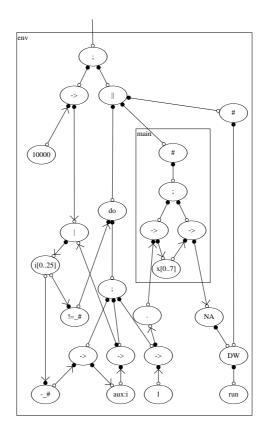

Figure 2.8 shows (in black) the graph of a simple Breeze handshake circuit composed of handshake components linked by channels. This handshake circuit was obtained by compilation of the "modulo-10 counter" example shown in Figure 2.7. Some of the Balsa features enumerated in the previous section (the red numbers match the numbered comments in Figure 2.7) and illustrated at the language level are highlighted here on the graph of the handshake circuit (in red). This illustrates the directness of the compilation.

Figure 2.8: Breeze handshake circuit graph (modulo-10 counter example)

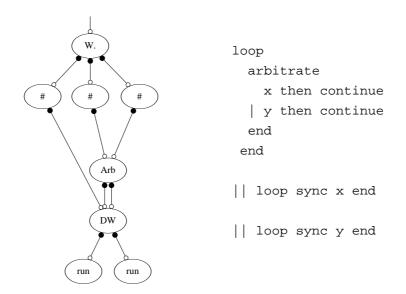

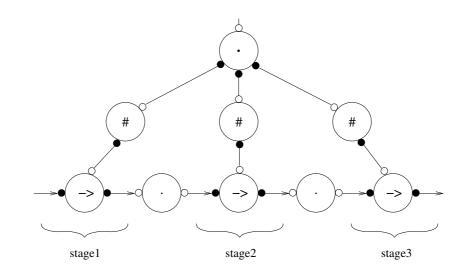

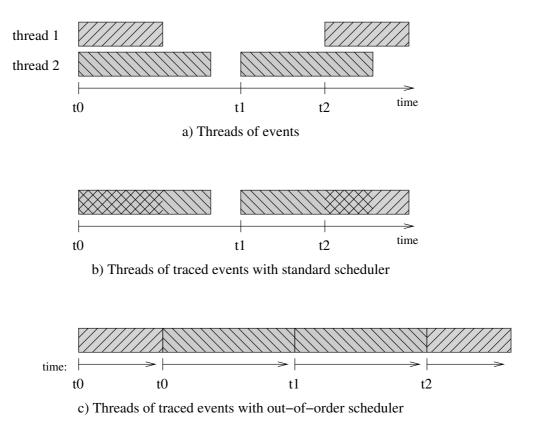

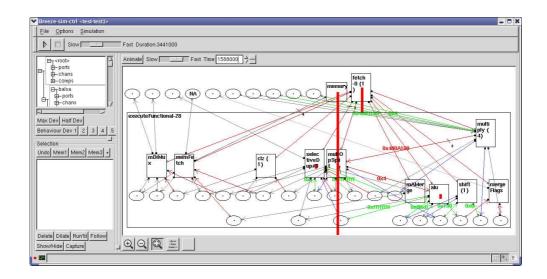

The circuit is first activated by a request signal on the *activate* channel (implicitely declared in every Balsa procedure), at the top left of the figure. This signal activates the Loop component, whose abbreviation on the graph is '#' (see the list of abbreviations at the end of Appendix B) and whose behaviour is to endlessly activate the next component it is connected to. Notice that this behaviour corresponds to the *loop* construct in the original source program. The next component is a DecisionWait, which corresponds to the next line in the Balsa source code: waiting for *aclk* before continuing. The rest of the circuit continues in the same obvious translation scheme with a Sequence component and others.