# RUN-TIME OBJECT CODE COMPILATION TO HARDWARE

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2008

By Ian Jason School of Computer Science

# Contents

| Al | Abstract    |         |                                        |    |  |

|----|-------------|---------|----------------------------------------|----|--|

| D  | Declaration |         |                                        |    |  |

| Co | opyri       | ght     |                                        | 13 |  |

| A  | cknov       | wledge  | ments                                  | 14 |  |

| 1  | Intr        | oductio | on                                     | 15 |  |

|    | 1.1         | Resea   | rch goals                              | 17 |  |

|    | 1.2         | Simul   | ator and benchmark details             | 18 |  |

|    | 1.3         | Thesis  | soutline                               | 19 |  |

| 2  | Rec         | onfigur | cable hardware and dynamic compilation | 20 |  |

|    | 2.1         | Recon   | figurable computing                    | 20 |  |

|    |             | 2.1.1   | Field programmable gate arrays         | 22 |  |

|    |             | 2.1.2   | Granularity                            | 22 |  |

|    |             | 2.1.3   | Coupling with host processor           | 24 |  |

|    |             | 2.1.4   | Configuring the hardware               | 25 |  |

|    |             | 2.1.5   | Hardware/software partitioning         | 27 |  |

|    | 2.2         | Dynai   | mic optimisation                       | 28 |  |

|    |             | 2.2.1   | Dynamic optimisation in software       | 29 |  |

|    |             | 2.2.2   | Hardware dynamic optimisation          | 30 |  |

|    |             | 2.2.3   | Detecting hot spots                    | 33 |  |

|   | 2.3  | Sumn    | nary                                              | 35 |

|---|------|---------|---------------------------------------------------|----|

| 3 | Hot  | spot d  | etection                                          | 36 |

|   | 3.1  | Progr   | am behaviour                                      | 36 |

|   |      | 3.1.1   | Dynamic basic blocks                              | 37 |

|   |      | 3.1.2   | Dynamic analysis of executed basic blocks         | 39 |

|   |      | 3.1.3   | Hot spots                                         | 40 |

|   |      | 3.1.4   | Phased behaviour                                  | 41 |

|   | 3.2  | Chain   | ns of basic blocks                                | 43 |

|   |      | 3.2.1   | Handling unexpected branch decisions              | 45 |

|   |      | 3.2.2   | Change of branch behaviour                        | 47 |

|   |      | 3.2.3   | Increase in block size                            | 48 |

|   | 3.3  | Profili | ing                                               | 48 |

|   |      | 3.3.1   | Static profiling                                  | 48 |

|   |      | 3.3.2   | Dynamic profiling                                 | 50 |

|   | 3.4  | Opera   | ation of hot spot detector                        | 52 |

|   |      | 3.4.1   | Determining which blocks to compile               | 53 |

|   |      | 3.4.2   | Sensitivity of the hot spot detector              | 54 |

|   |      | 3.4.3   | Constructing Block Chains                         | 59 |

|   | 3.5  | Block   | Profile Table                                     | 60 |

|   |      | 3.5.1   | Size of block profile table                       | 62 |

|   | 3.6  | Hardy   | ware Configuration Table                          | 63 |

|   |      | 3.6.1   | Storage of hardware configuration data            | 65 |

|   |      | 3.6.2   | Number of entries in hardware configuration table | 66 |

|   | 3.7  | Sumn    | nary                                              | 69 |

| 4 | Bloo | ck opti | misation and compilation                          | 70 |

|   | 4.1  | Optin   | nisations on single basic blocks                  | 70 |

|   |      | 4.1.1   | Temporary values                                  | 70 |

|   |      | 4.1.2   | Increasing parallelism                            | 73 |

|   | 4.2  | Optin   | nisations on chains of basic blocks                 | 76  |

|---|------|---------|-----------------------------------------------------|-----|

|   |      | 4.2.1   | Increased number of temporary values                | 76  |

|   |      | 4.2.2   | Increase parallelism                                | 78  |

|   |      | 4.2.3   | Memory aliasing                                     | 82  |

|   |      | 4.2.4   | Reducing stack operations                           | 83  |

|   | 4.3  | Block   | compilation process                                 | 85  |

|   | 4.4  | Perfor  | ming the compilation process                        | 93  |

|   | 4.5  | Summ    | nary                                                | 94  |

| 5 | Rec  | onfigur | able hardware structure                             | 96  |

|   | 5.1  | Adva    | ntages of executing in reconfigurable hardware      | 96  |

|   | 5.2  | Desig   | n aspects of the hardware execution engine          | 99  |

|   |      | 5.2.1   | Interface with microprocessor                       | 99  |

|   |      | 5.2.2   | Parallelism                                         | 100 |

|   |      | 5.2.3   | Memory and register interface                       | 104 |

|   |      | 5.2.4   | Word size of functional units                       | 109 |

|   |      | 5.2.5   | Size of compiled block definitions                  | 111 |

|   |      | 5.2.6   | Implementation of reconfigurable hardware structure | 113 |

|   | 5.3  | Struct  | ure description                                     | 115 |

|   |      | 5.3.1   | Memory interface                                    | 116 |

|   |      | 5.3.2   | Interface with architectural registers              | 125 |

|   |      | 5.3.3   | Functional units                                    | 126 |

|   |      | 5.3.4   | Immediate operands                                  | 127 |

|   |      | 5.3.5   | Control of block execution                          | 130 |

|   | 5.4  | Block   | mapping algorithm                                   | 133 |

|   | 5.5  | Summ    | nary                                                | 135 |

| 6 | Syst | em An   | alysis                                              | 137 |

|   | 6.1  | Evalu   | ation method                                        | 137 |

|   | 6.2  | Perfor  | mance                                               | 138 |

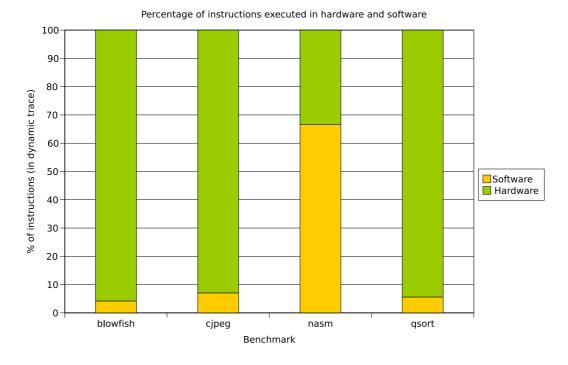

|        | 6.2.1   | Amount of code executed in hardware        | 138 |

|--------|---------|--------------------------------------------|-----|

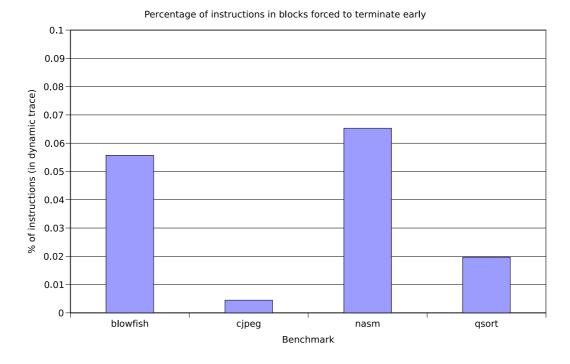

|        | 6.2.2   | Effect of block breakouts                  | 139 |

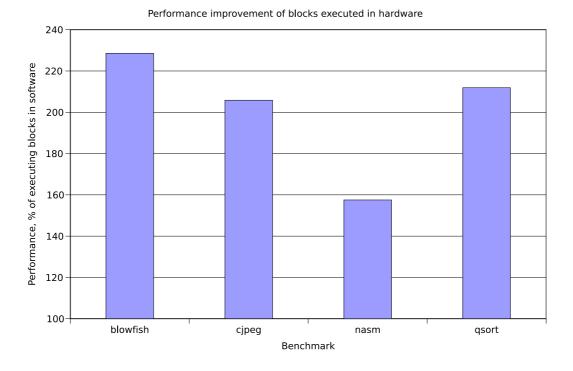

|        | 6.2.3   | Performance of blocks executed in hardware | 140 |

|        | 6.2.4   | Performance impact of run-time compilation | 143 |

|        | 6.2.5   | Performance analysis                       | 143 |

| 6.3    | Energ   | y consumption                              | 144 |

|        | 6.3.1   | Parallelising instructions                 | 145 |

|        | 6.3.2   | Reduced register bank access               | 146 |

|        | 6.3.3   | Fetch and decode                           | 149 |

|        | 6.3.4   | Hot spot detector and compilation process  | 150 |

| 6.4    | Sumn    | nary                                       | 150 |

| 7 Co   | nclusio | ns                                         | 151 |

| 7.1    | Limit   | ations                                     | 155 |

| 7.2    | Futur   | e work                                     | 155 |

|        | 7.2.1   | Energy consumption evaluation              | 156 |

|        | 7.2.2   | Looping within compiled blocks             | 156 |

|        | 7.2.3   | Multiple paths through compiled blocks     | 157 |

|        | 7.2.4   | Compilation and scheduling algorithms      | 157 |

| 7.3    | Sumn    | nary                                       | 158 |

| Refere | nces    |                                            | 159 |

# **List of Figures**

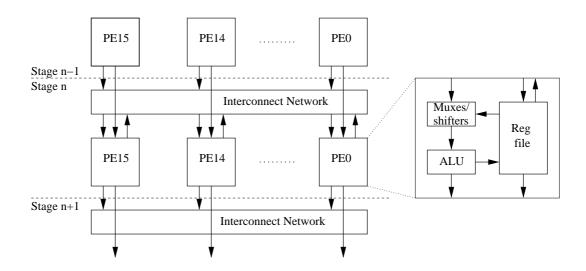

| 2.1 | PipeRench reconfigurable datapath [GSM+99]                         | 23 |

|-----|--------------------------------------------------------------------|----|

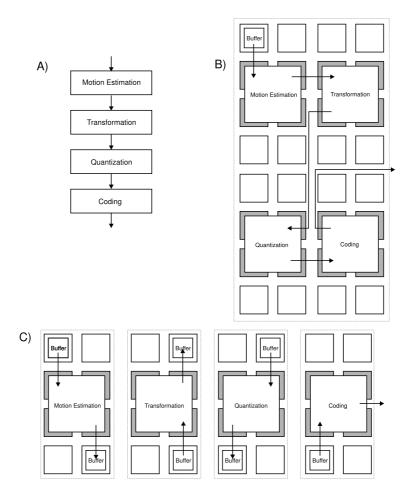

| 2.2 | SCORE reconfigurable hardware virtualisation. A) Stages in         |    |

|     | video processing algorithm. B) Compute pages loaded simulta-       |    |

|     | neously into large hardware structure. C) Compute pages time-      |    |

|     | multiplexed into smaller hardware structure. [CCH+00]              | 26 |

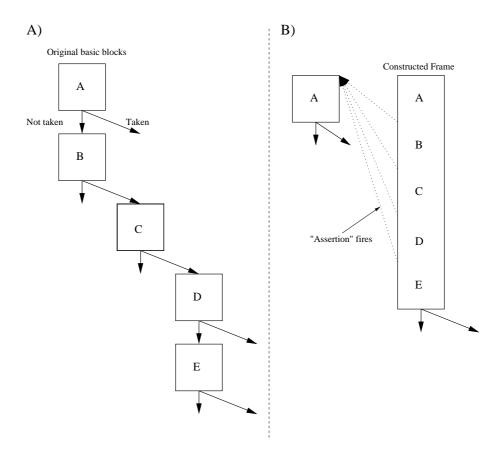

| 2.3 | RePLay frame construction. A) Original basic blocks. B) RePLay     |    |

|     | frame, with conditional branches replaced by assertions. [PL01]    | 32 |

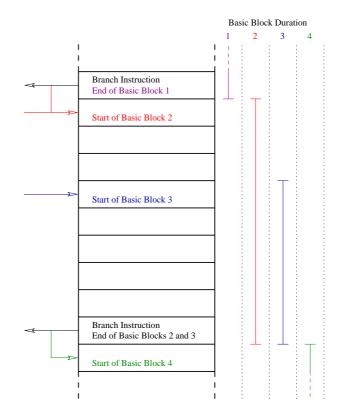

| 3.1 | Layout of dynamic basic blocks in memory                           | 38 |

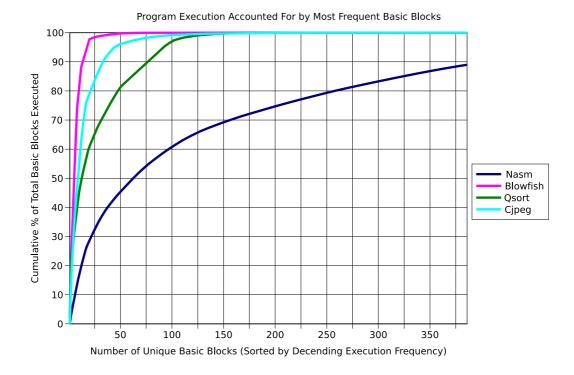

| 3.2 | Cumulative percentage of total basic blocks executed by the        |    |

|     | most frequently executed unique basic blocks                       | 40 |

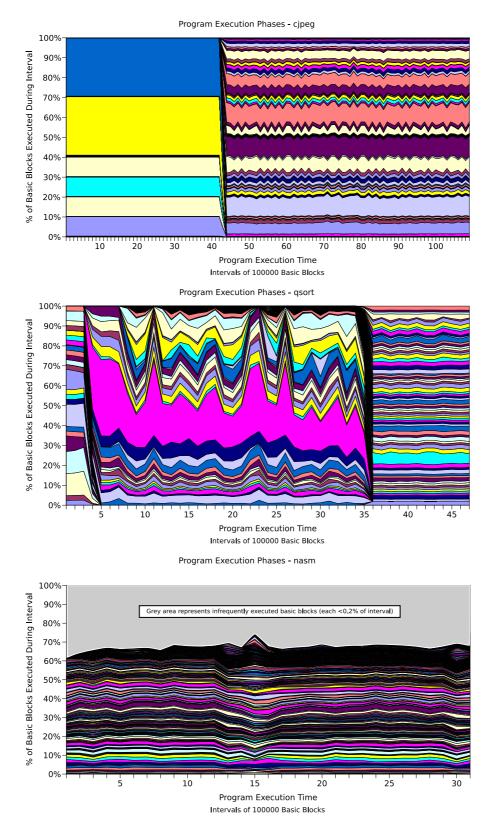

| 3.3 | Phases during program execution: each horizontal slice shows       |    |

|     | the execution frequency of a unique basic block as a percentage    |    |

|     | of the total basic blocks executed during each time interval       | 42 |

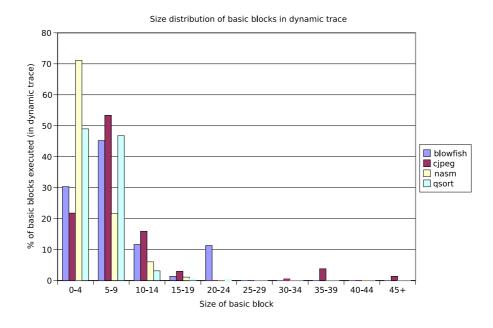

| 3.4 | Distribution of basic blocks in dynamic trace by number of         |    |

|     | instructions                                                       | 44 |

| 3.5 | Basic block size vs. chained block size                            | 49 |

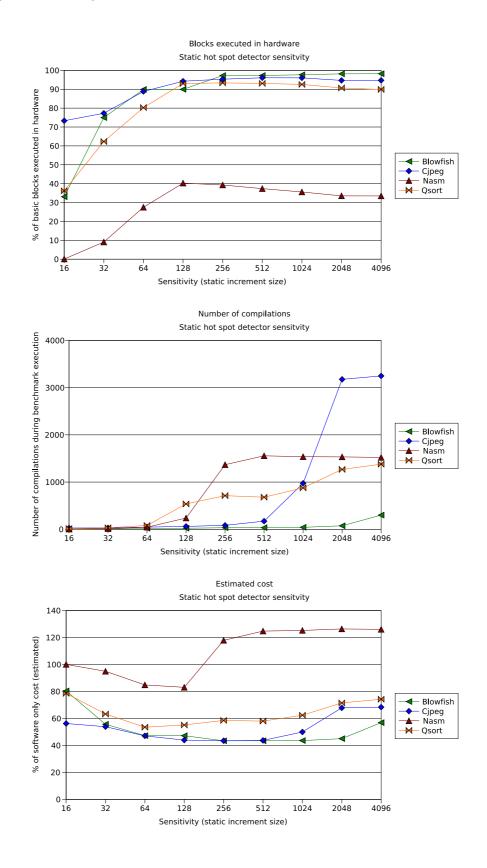

| 3.6 | Number of blocks executed in hardware, number of compila-          |    |

|     | tions and estimated cost with static hot spot detector sensitivity | 56 |

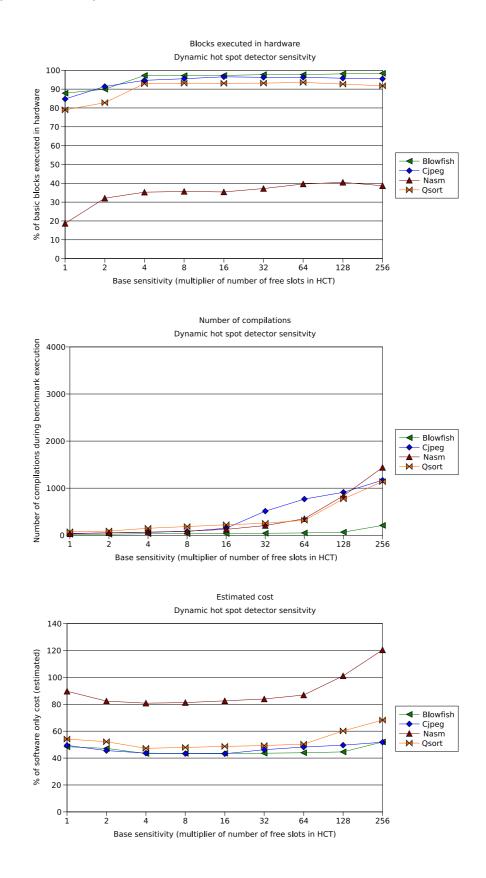

| 3.7 | Number of blocks executed in hardware, number of compi-            |    |

|     | lations and estimated cost with dynamic hot spot detector          |    |

|     | sensitivity                                                        | 58 |

| 3.8 | Block profile table                                                | 61 |

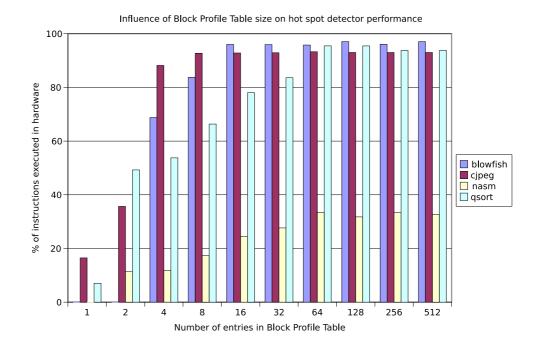

| , | 3.9  | Influence of Block Profile Table size on number of instructions    |     |

|---|------|--------------------------------------------------------------------|-----|

|   |      | executed in hardware                                               | 63  |

| , | 3.10 | Hardware Configuration Table                                       | 65  |

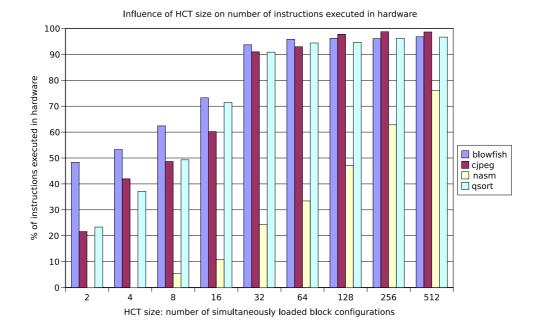

| , | 3.11 | Influence of Hardware Configuration Table size on number of        |     |

|   |      | instructions executed in hardware                                  | 68  |

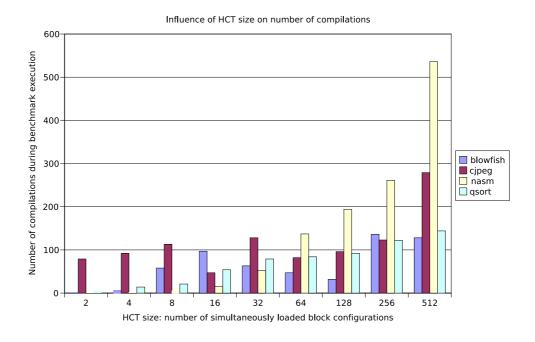

|   | 3.12 | Influence of Hardware Configuration Table size on number of        |     |

|   |      | compilations                                                       | 68  |

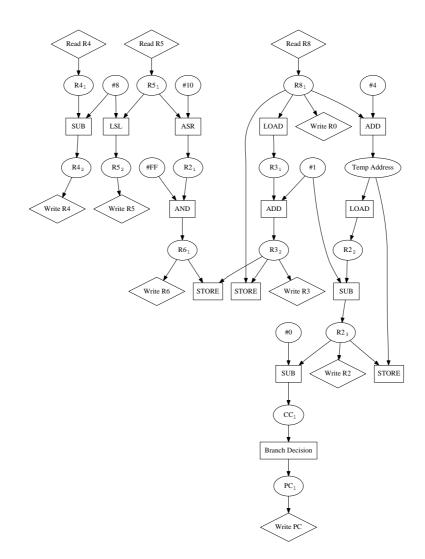

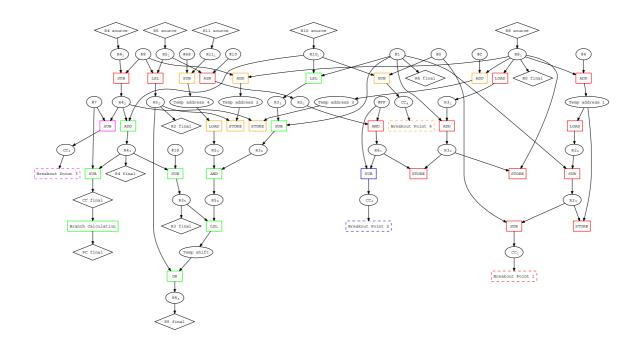

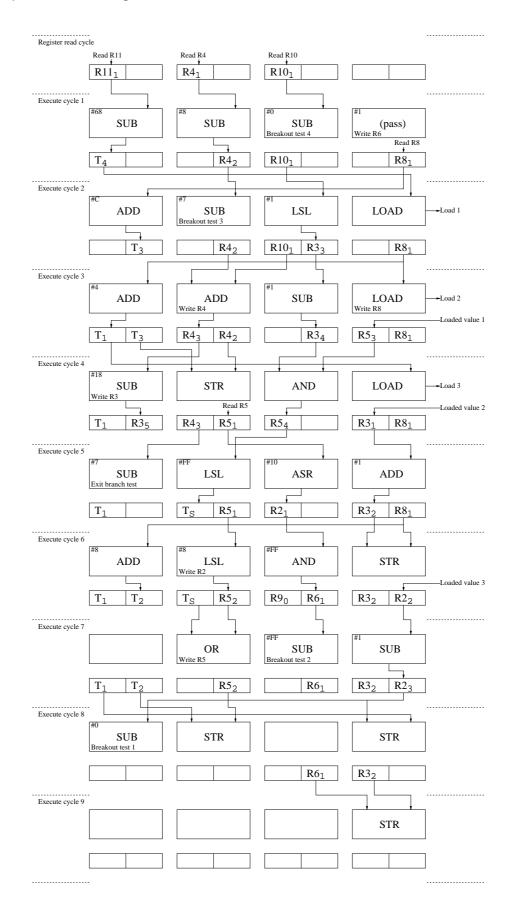

|   | 4.1  | Data flow graph of single basic block                              | 74  |

|   | 4.2  | Data flow graph of basic block with three-way constrained          |     |

|   |      | parallelism, single load per cycle and a single-cycle load delay . | 75  |

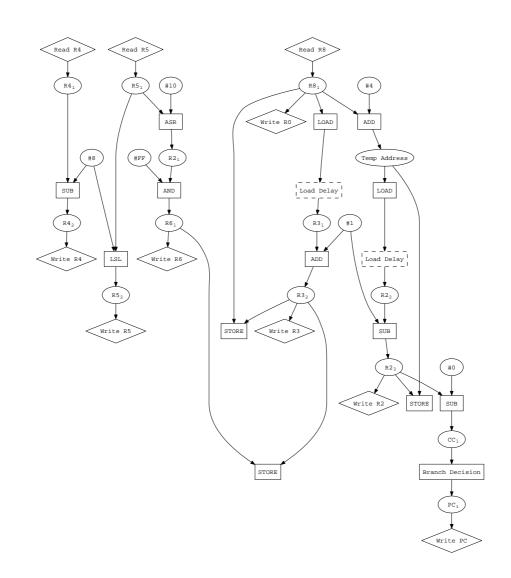

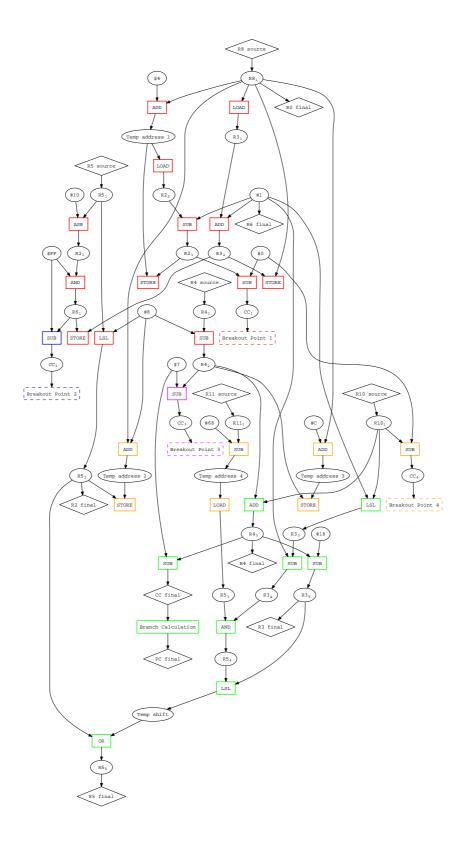

|   | 4.3  | Data flow graph of chained block with control dependencies         |     |

|   |      | between basic blocks                                               | 79  |

|   | 4.4  | Data flow graph of chained block with control dependencies         |     |

|   |      | removed                                                            | 80  |

|   | 4.5  | Data flow graph of chained block with four-way constrained         |     |

|   |      | parallelism, single load operation per cycle and a single-cycle    |     |

|   |      | load delay                                                         | 81  |

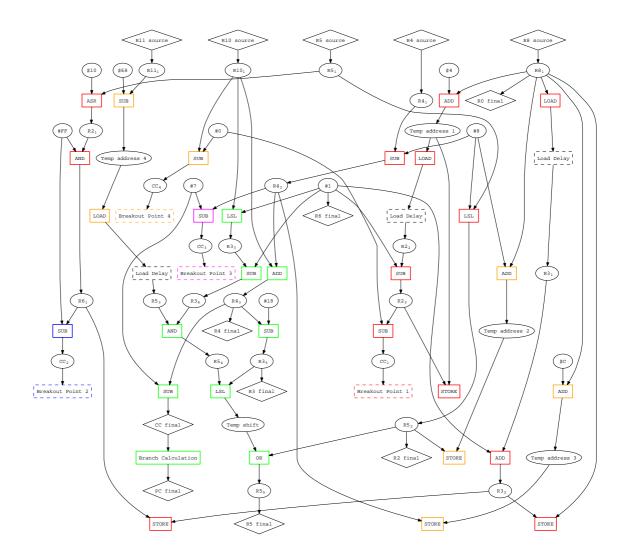

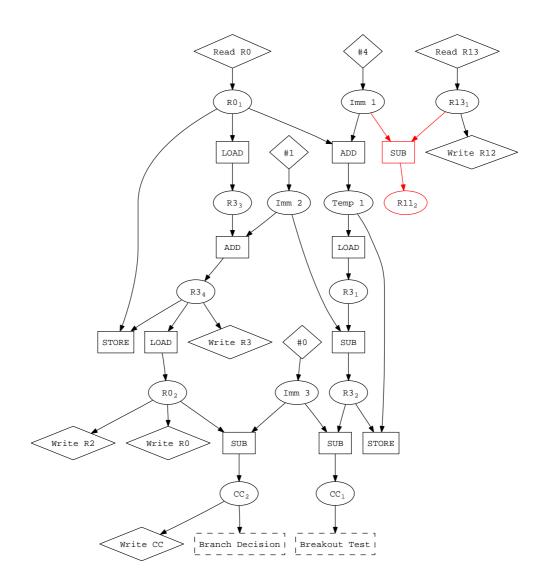

|   | 4.6  | Data flow graph of example block, with redundant operations        |     |

|   |      | in red                                                             | 91  |

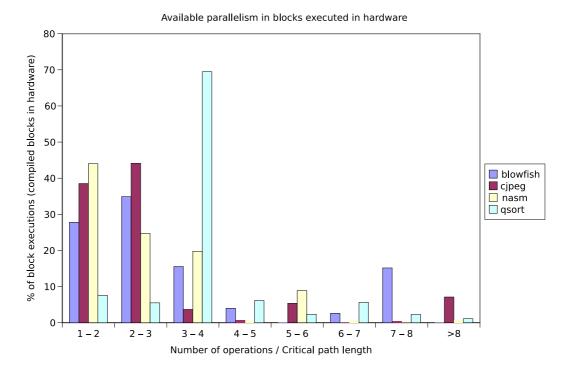

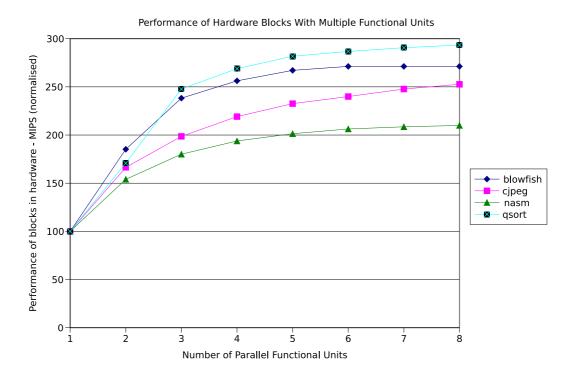

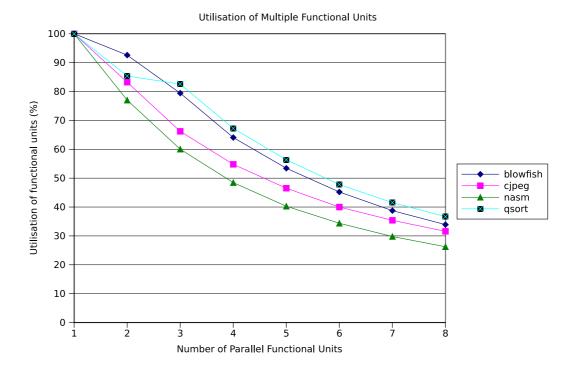

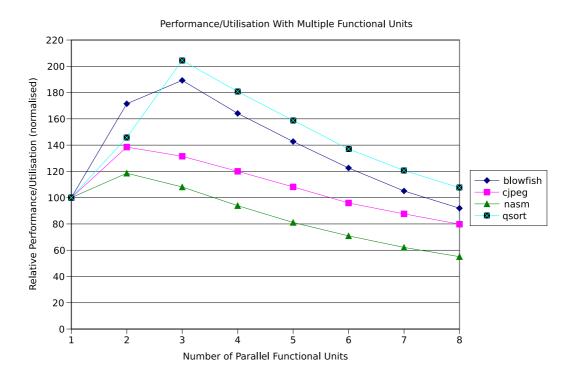

| , | 5.1  | Average parallelism in executed hardware blocks                    | 101 |

| , | 5.2  | Performance of hardware blocks with increasing numbers of          |     |

|   |      | parallel functional units                                          | 102 |

| , | 5.3  | Utilisation of hardware structure with multiple parallel func-     |     |

|   |      | tional units                                                       | 103 |

| , | 5.4  | Relative performance over utilisation of hardware structure        |     |

|   |      | with multiple parallel functional units                            | 103 |

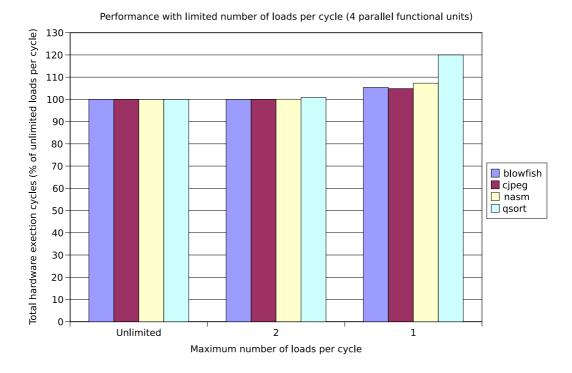

| , | 5.5  | Performance of hardware blocks with limited numbers of loads       |     |

|   |      | per execution cycle                                                | 106 |

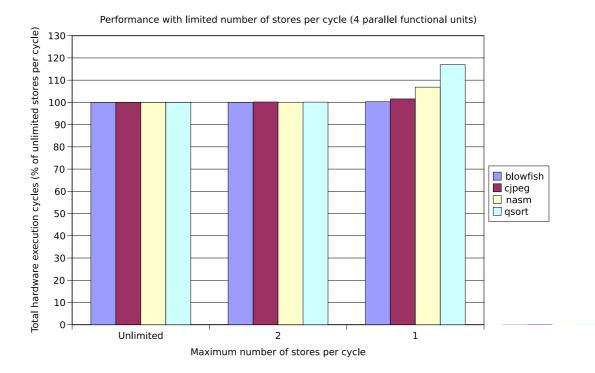

| 5.6  | Performance of hardware blocks with limited numbers of stores     |     |

|------|-------------------------------------------------------------------|-----|

|      | per execution cycle                                               | 108 |

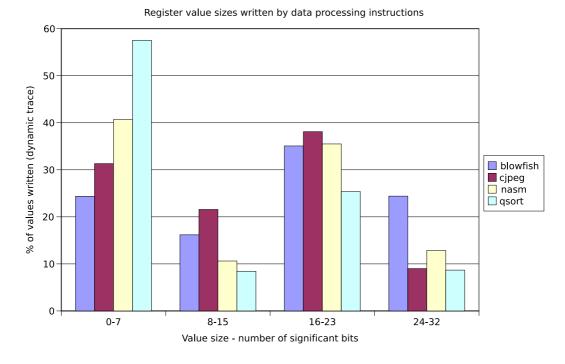

| 5.7  | Size of values (position of most significant bit) written by data |     |

|      | instructions                                                      | 109 |

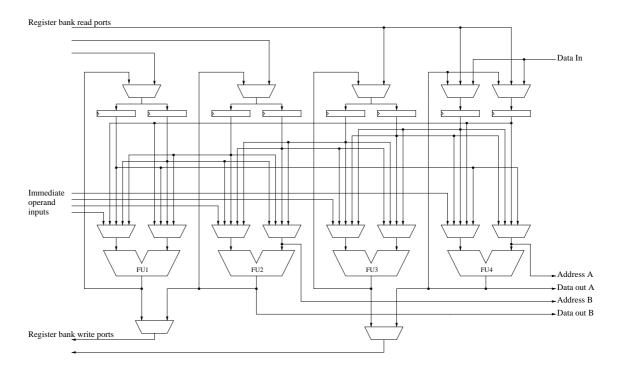

| 5.8  | Hardware structure internal interconnect                          | 116 |

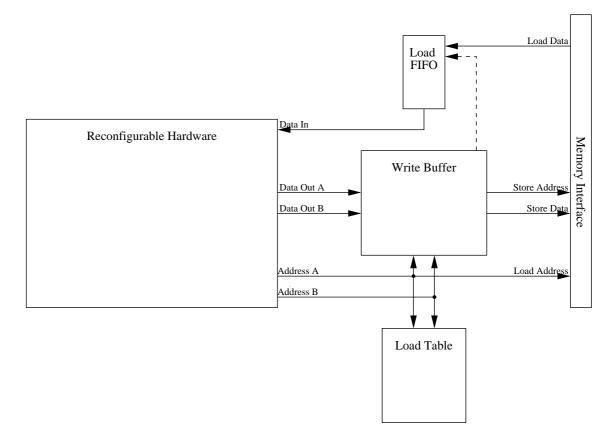

| 5.9  | Memory interface block diagram                                    | 117 |

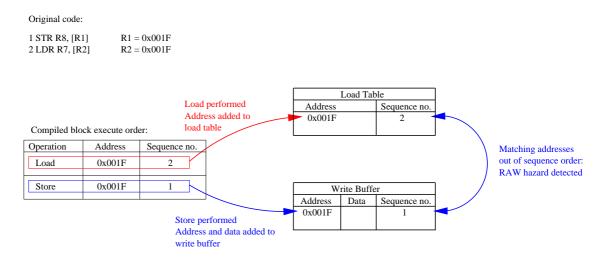

| 5.10 | Read-after-write memory alias detection                           | 120 |

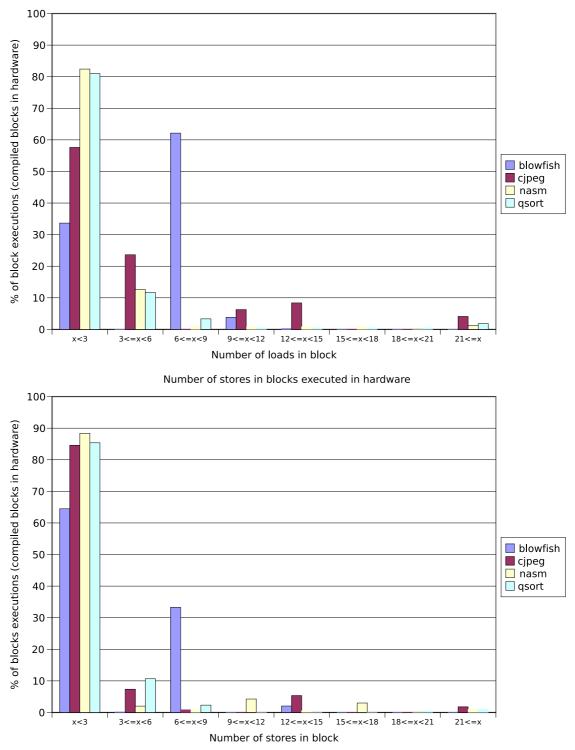

| 5.11 | Number of loads and stores in executed hardware blocks $\ldots$   | 121 |

| 5.12 | Write buffer                                                      | 123 |

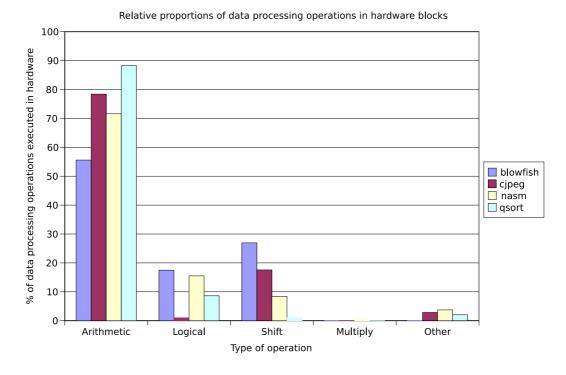

| 5.13 | Proportion of data processing operation types in executed         |     |

|      | hardware blocks                                                   | 127 |

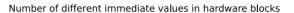

| 5.14 | Number of different immediate values in each executed hard-       |     |

|      | ware block                                                        | 131 |

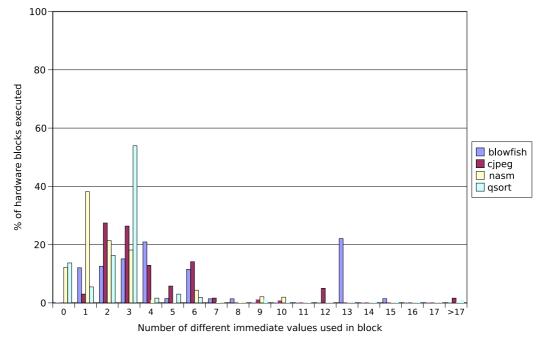

| 5.15 | Number of different immediate values in each executed hard-       |     |

|      | ware block, excluding most common values (0, 1, 2, 3, 4, 8, 10    |     |

|      | and FF)                                                           | 131 |

| 5.16 | Example mapping of block on page 77 into hardware structure .     | 134 |

| 6.1  | Percentage of instructions executed in hardware and software      |     |

| 0.1  | during benchmark execution                                        | 139 |

| 6.2  | Percentage of instructions re-executed due to hardware blocks     | 157 |

| 0.2  | terminating early (upper bound, assuming all instructions in a    |     |

|      | block are executed twice if it terminates early)                  |     |

| 6.3  | Performance improvement of blocks compiled into hardware,         | 140 |

| 0.5  | weighted mean based on dynamic frequency of execution             | 141 |

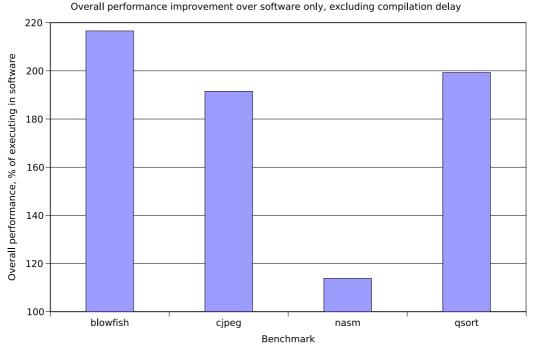

| 6.4  | Overall performance improvement of benchmark, excluding           | 141 |

| 0.4  |                                                                   | 142 |

| 65   | performance penalties due to compilation process                  |     |

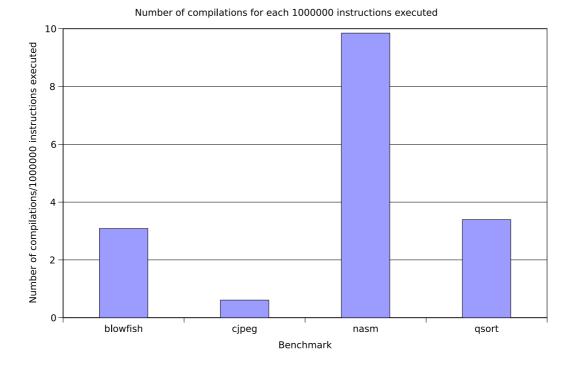

| 6.5  | Number of compilations per million instructions executed          | 144 |

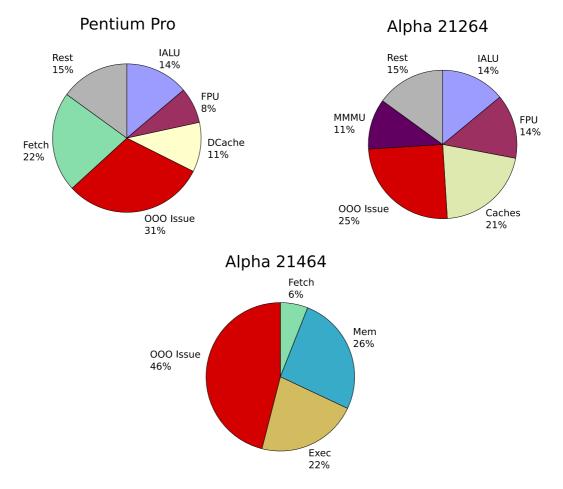

| 6.6  | Power breakdown of superscalar processors [Val05]                 |     |

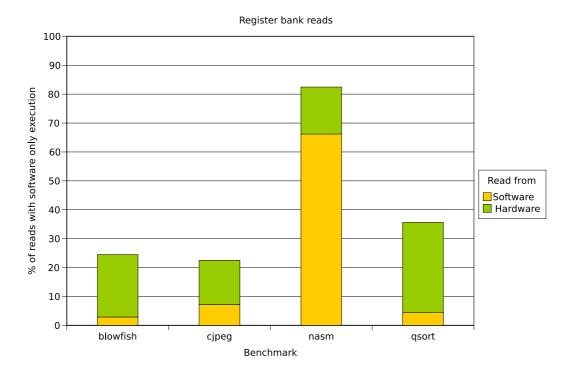

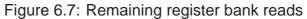

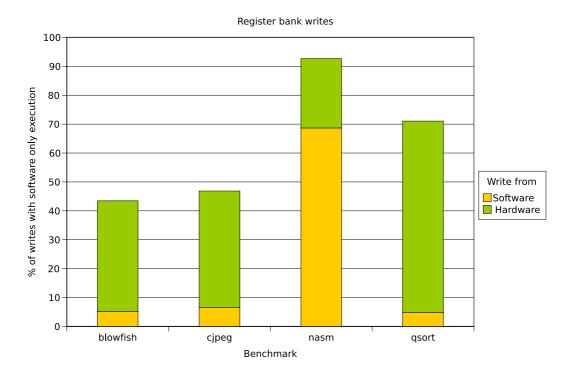

| 6.7  | Remaining register bank reads                                     | 147 |

| 6.8 | Remaining register bank writes | S | 147 |

|-----|--------------------------------|---|-----|

|-----|--------------------------------|---|-----|

# **List of Tables**

| 3.1 | Unique basic blocks and total number of basic blocks executed,  |     |

|-----|-----------------------------------------------------------------|-----|

|     | dynamic trace                                                   | 39  |

| 4.1 | Frequency of occurrence of read-after-write memory hazards      |     |

|     | that are not statically determinable                            | 83  |

| 4.2 | Temporary stores to the stack within a block as a proportion of |     |

|     | total stores (in executed hardware blocks)                      | 84  |

| 4.3 | List of operations in example block, in execution order         | 87  |

| 4.4 | List of operations in example block with individual values      |     |

|     | labelled and internal control operations removed                | 90  |

| 5.1 | Most frequent immediate values, sorted by percentage of total   |     |

|     | immediates within hardware blocks                               | 128 |

| 5.2 | Number of different immediate values in blocks stored in HCT    |     |

|     | (maximum at one time)                                           | 129 |

## Abstract

Reconfigurable hardware systems offer great potential for improving performance over software through increased parallelism and reduced control overhead. However, the configuration of the hardware is performed statically, restricting the system's ability to adapt to the run-time environment. This thesis explores the possibility of compiling from object code into a reconfigurable hardware structure at run-time to allow the hardware configuration to benefit from the behaviour of the currently executing code.

A mechanism for detecting hot spots at run-time is presented; this minimises compilation overheads by only compiling the most frequently executed sections of code. A dynamic detection threshold allows the hot spot detector to adapt to radically different code and to react quickly to changes in program behaviour. A hardware structure suitable for executing these hot spots is proposed, consisting of a sequenced execution engine containing four parallel functional units and a configurable interconnect.

# **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institution of learning.

# Copyright

Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of the School of Computer Science.

## Acknowledgements

Firstly I would like to thank my supervisor Dr. Jim Garside for his advice, insight and patience over the last four years.

Thanks must also go to all my friends in the APT group for keeping me sane, especially Sam (for his inspirational research methodology), Andrew and Matt.

Special thanks are due to my parents for their encouragement, support and tolerance.

Finally, I would like to thank Sonja for inspiring me to finish this thesis.

## **Chapter 1**

## Introduction

Today's consumers demand an increasingly diverse set of features in portable electronic devices. Modern mobile phones, for example, are capable not only of making and receiving calls but also playing music and video, taking photographs and browsing the Internet. These features require considerable computing resources; in the past the significant data processing tasks performed in such devices, such as voice processing, were executed in dedicated hardware processors. Dedicated hardware can perform a task much more quickly and efficiently than a microprocessor executing software by both increasing parallelism and by reducing the control overhead required by executing an algorithm in software.

Developing custom hardware has a number of disadvantages however: systems are expensive and time-consuming to develop, and once such a system is produced it is not possible to modify it if required, for example in the event of a defect being discovered or additional features being required. The increasing diversity in the processing requirements of portable devices means that it is not feasible to develop custom hardware for them all; instead a more general purpose processing unit is required.

Reconfigurable hardware provides performance similar to fixed-function hardware while maintaining flexibility close to that of a microprocessor. Initial reconfigurable systems were based on standalone Field Programmable Gate Arrays (FPGAs) intended as a soft-programmable replacement for fixedfunction hardware; more recent systems are hybrid architectures, consisting of a microprocessor with a reconfigurable coprocessor. These allow the core algorithms to be accelerated by the reconfigurable hardware and the less frequently executed parts of a program to execute in software, reducing the amount of reconfigurable hardware required.

Selecting the sections of code to compile into the reconfigurable hardware is typically performed at compile-time using static profile information. However, a program's behaviour is not always easily predictable at compile-time: it may depend, for example, on the data being processed or options selected by the user. Additionally, during execution a program's behaviour may not be constant as it may consist of a number of phases when different sections of code are executed.

Backward compatibility is an additional disadvantage of reconfigurable architectures as special programming methods and tools are required to create configurations for the reconfigurable hardware. Incompatibility with the existing code base provides a significant barrier to adoption, as evidenced by the continued prevalence of Intel's x86 instruction set architecture despite the development of more efficient alternatives.

One possible solution to these problems is to translate the code at runtime. This is used in dynamic binary translation systems to allow legacy code to execute on new architectures. Similar techniques are used in dynamic optimisation systems, which transform instructions at run-time into a more efficient internal representation to improve performance.

However, performing the optimisation at run-time is an expensive process and may incur significant overheads if performed for an entire program. These overheads can be reduced by only selecting the most frequently executed parts of a program for optimisation. This can be achieved by using *dynamic*  *profiling* mechanisms; these monitor the executing program to locate the most frequently executed sections of code, or *hot spots*, which are then optimised.

## 1.1 Research goals

This thesis explores the feasibility and potential benefits of compiling existing object code into reconfigurable hardware at run-time. By profiling the currently executing program, hot spots are detected which are then compiled into a reconfigurable execution engine. Key contributions include:

- The development of architectural techniques to allow object code to be compiled at run-time into reconfigurable hardware.

- Analysis of program execution, leading to a proposed mechanism for detecting program hot spots at run-time, including a method of dynamically altering the threshold of the hot spot detector to quickly adapt to variations in program behaviour.

- The use of information gathered dynamically by the hot spot detector to detect highly biased branches and to use this to speculatively combine multiple basic blocks into a single atomic entity with a single entry and exit point. An analysis of optimisations that can be performed within these blocks is given, and mechanisms for handling incorrect speculation are proposed.

- The development of a reconfigurable parallel execution engine capable of processing detected hot spots. Methods for overcoming difficulties of executing hardware configurations created from object code, such as supplying immediate operands and detecting memory aliasing, are explored.

• An evaluation of the potential performance improvements that can be gained by dynamic compilation into hardware using the techniques described in this thesis.

## 1.2 Simulator and benchmark details

The system described in this thesis is evaluated by modifying a software model of an ARM [JS00] microprocessor. The ARM architecture is chosen as it is commonly used in real-world embedded systems that the techniques in this thesis are intended for, and tools (such as simulators and compilers) are widely available. The simulator models the architecture at the instruction level: detailed simulation of low-level architectural structures such as pipeline stage interaction is not performed.

Four benchmarks are used to evaluate the system<sup>1</sup>. These were selected to give a varied set of different program behaviours:

- **Blowfish** is an encryption algorithm [Sch93]. The input data is a 100KB file, causing the benchmark to execute 15 million instructions. *Blowfish* contains a very small set of basic blocks which make up the majority of the dynamic trace of the program; this property allows it to perform well in this system.

- **Cjpeg** is an open-source implementation of the jpeg image compression standard [cjp]. This benchmark runs for 134 million instructions when compressing a 1.4MB TGA file using default settings. Like *blowfish* this benchmark contains a number of very frequently executed hot spots; however, unlike *blowfish* distinct phases of operation are present, causing a change in the working set of basic blocks about a third of the way through the program's execution.

<sup>&</sup>lt;sup>1</sup>Contact author at ianjason(at)gmx.at to request input data used with benchmarks.

- **Nasm** is an x86 assembler [nas]. 14 million ARM instructions are required to assemble the 500 line program used as test data. This benchmark is provided as a contrast to the other benchmarks as it performs a larger, diverse set of operations on a relatively small input. This program contains no hot spots that dominate program execution time and so performs poorly in this system compared to the other benchmarks.

- **Qsort** is a program to sort words in an input text file into alphabetical order. The input data to be sorted contains 13000 words, and the benchmark runs for 25 million instructions. Like *cjpeg*, *qsort* contains distinct phases of execution, but program behaviour fluctuates significantly within these phases.

All benchmarks are compiled with GCC 3.4.3 [gcc] using level two optimisations.

## 1.3 Thesis outline

The next chapter outlines developments in reconfigurable computing and dynamic optimisation systems. Chapter 3 describes the process of monitoring code and detecting hot spots. Optimisations that can be performed on detected hot spots are discussed in chapter 4. A suitable reconfigurable execution engine for processing these hot spots is outlined in chapter 5. Chapter 6 combines the techniques described in the preceding chapters to analyse the performance of such a system. Finally, chapter 7 draws conclusions on the work presented in this thesis, identifies limitations and outlines directions for future work.

## **Chapter 2**

# Reconfigurable hardware and dynamic compilation

This chapter presents an overview of reconfigurable hardware and dynamic compilation techniques. The concept of reconfigurable hardware is outlined and compared with fixed-function hardware and general-purpose microprocessors. A description of different types of reconfigurable hardware and methods of use is given. A number of examples of architectures utilising reconfigurable hardware are described briefly.

The second part of this chapter deals with dynamic compilation and optimisation techniques; their use in translation for binary compatibility and dynamic optimisation to enhance performance is described. A number of example systems are outlined, both hardware and software based.

## 2.1 Reconfigurable computing

In traditional computing systems two primary methods are used to execute algorithms. One is to encode the algorithm into a series of software instructions which are used to control a microprocessor. Microprocessors are very flexible: changing the algorithm to be processed merely involves changing the software. However, this limits performance as the algorithm is executed sequentially, and decoding the stream of instructions incurs overheads due to extra instructions other than those used to process data being required to load data into the hardware and control the execution of the algorithm.

These overheads can be removed by creating a piece of hardware specifically tailored to process the algorithm required. The algorithm can be processed in parallel as the requirement for it to be encoded as a sequence of instructions is removed. No instructions must be fetched and decoded as the function of the algorithm is encoded into the structure of the hardware itself. Executing an algorithm in custom hardware can therefore be significantly faster and more power efficient than the same algorithm executing in a microprocessor. Custom hardware is therefore used when high performance or low power consumption is required and the algorithm is inherently parallel; for example processing video, routing network packets or processing voice data in a mobile phone. However, a specific custom-designed piece of hardware can only process one algorithm; should a different algorithm be required a new hardware design must be produced at significant cost.

Reconfigurable hardware offers a compromise between these two methods. The structure of a reconfigurable hardware system is not fixed: it can be softconfigured to process different algorithms. Once configured, reconfigurable hardware can be used to process an algorithm in a similar way to custom hardware, with no need to continually fetch and decode instructions. Data can pass directly between execution units, and any inherent parallelism in the algorithm can be more easily exploited as there is no need to follow a linear sequence of instructions.

These factors should allow reconfigurable hardware to achieve significantly higher performance than a microprocessor while maintaining greater flexibility than hardware.

#### 2.1.1 Field programmable gate arrays

Field programmable gate arrays (FPGAs) [BR96] are an example of a reconfigurable hardware structure. FPGAs consist of a grid of *logic blocks* and a two-dimensional programmable interconnect. Logic blocks typically consist of look-up tables (LUTs), which can produce any function of a number of inputs allowing general logic functions to be computed. Fixed-function logic blocks containing commonly used structures, such as adders, can be included to improve performance at the cost of some flexibility. The interconnect provides much of the flexibility of an FPGA as it consists of a hierarchical grid of horizontal and vertical connections allowing signals to be routed almost anywhere in the array.

FPGAs were originally intended for low product volumes where producing custom hardware would be uneconomical, or for rapidly prototyping hardware designs. However, it has been shown that FPGAs can be used as an alternative computing paradigm and have been demonstrated to show significantly improved performance in some applications traditionally employing software [Gos96][EP00][GHK<sup>+</sup>91].

Reconfigurable hardware is not limited to FPGAs however. Different logic block sizes and interconnect structures can be used to tailor the reconfigurable fabric for the intended application. Many systems have demonstrated the effectiveness of combining reconfigurable structures with a traditional microprocessor (see section 2.1.3).

#### 2.1.2 Granularity

The *granularity* of a reconfigurable hardware structure refers to the size of configurable logic blocks in the structure. A *fine-grained* structure contains small logic blocks that are configurable at the bit-level, usually consisting of small look-up tables. These have a very high flexibility and are suited to

Figure 2.1: PipeRench reconfigurable datapath [GSM+99]

algorithms that manipulate individual bits, such as encryption. The hardware can also be easily tailored to match the width of the data being processed. In addition, fine granularity is required for random logic and state machines, hence the use of fine-grained reconfigurable structures such as FPGAs for prototyping hardware designs.

*Coarse-grained* reconfigurable hardware contains larger, fixed-function logic blocks such as adders, shifters and multipliers [Har01]. These are less flexible than fine-grained architectures as individual bits cannot be configured. However, a large fixed function logic block is faster and more power efficient than a series of interconnected look-up tables and so performance is greater when executing algorithms that process fixed word-size data using the functions available in the logic blocks. The Pleiades architecture [ZPG<sup>+</sup>00] is very coarse-grained, consisting of a number of heterogeneous processing units optimised for different tasks in a reconfigurable interconnect structure. PipeRench [GSM<sup>+</sup>99] is a coarse-grained reconfigurable pipeline architecture; each pipeline stage consists of sixteen configurable 8-bit ALUs, or Processing Elements (PEs), and a reconfigurable interconnect (see figure 2.1).

The amount of configuration data in a coarse-grained structure is less than an equivalent fine-grained structure. This is due to commonality in the operations performed, requiring the configuration of fewer, larger logic blocks. This commonality is extended to the interconnect, which routes data in bundles as opposed to individual bits.

The granularity of a reconfigurable hardware structure is therefore a trade-off between performance, flexibility and configuration effort. The reconfigurable architecture proposed in chapter 5 of this thesis is coarse grained, consisting of word-width functional units within a reconfigurable interconnect.

#### 2.1.3 Coupling with host processor

Reconfigurable hardware can stand alone without a microprocessor; this is usually the case if the reconfigurable hardware is replacing a custom hardware unit in a system. Many algorithms that are designed to run in software cannot be mapped entirely into a block of reconfigurable hardware due to limited space. A solution to this is to map the frequently executed core parts of an algorithm into the reconfigurable hardware and have the remaining infrequently executed code execute in software.

#### **Reconfigurable coprocessors**

One way to achieve this is to have a microprocessor with a reconfigurable coprocessor. This provides a trade off between accelerating the performance of a program and keeping the size of the required reconfigurable fabric low. Garp [HW97] is an example of this type of architecture. Garp incorporates an FPGA-like reconfigurable structure with a MIPS processor. The reconfigurable hardware is loaded with configurations for executing the core algorithms of an application and acts as a coprocessor to the MIPS core, which executes the remaining parts of the code. Configuration of the Garp array is done statically:

configurations are created at compile time and then are loaded at run-time under microprocessor control. Only one configuration can be active at any one time; rapid switching between configurations is facilitated by caching multiple sets of configuration data. Many other examples of reconfigurable coprocessor architectures exist [Pag94][MO99][RLG<sup>+</sup>98][SLL<sup>+</sup>00].

#### **Reconfigurable functional units**

Another method is to use reconfigurable functional units within the microprocessor core itself [RS94][HFHK97][WH95][WC96]. Reconfigurable functional units are either used to provide custom complex instructions to accelerate a frequent sequence of operations within an application, or used to alter the number of parallel functional units of a certain type within a superscalar processor to match the distribution of operations in the executing program [NZ04].

#### 2.1.4 Configuring the hardware

A significant drawback of FPGAs is that configuration data are only compatible with a specific device. This means configurations created for one generation of FPGAs will need to be recreated to work on the next generation of larger, faster devices. A number of architectures have attempted to solve this problem by virtualising the physical hardware.

PipeRench [GSM<sup>+</sup>99] divides a configuration up into virtual pipeline stages; these are then mapped into a physical reconfigurable hardware pipeline. If insufficient physical stages are available multiple configurations can be swapped in and out, effectively allowing an unlimited number of virtual stages. Performance is improved by having a greater number of physical stages, allowing it to scale with improvements in technology.

SCORE [CCH<sup>+</sup>00] uses a similar method of virtualisation. A hardware representation of an algorithm is divided up into virtual *compute pages* which

Figure 2.2: SCORE reconfigurable hardware virtualisation. A) Stages in video processing algorithm. B) Compute pages loaded simultaneously into large hardware structure. C) Compute pages time-multiplexed into smaller hardware structure. [CCH<sup>+</sup>00]

interface in a data flow manner. These are mapped onto physical FPGAlike compute pages; if there are insufficient physical pages they can be timemultiplexed by swapping configurations in and out of the hardware (see figure 2.2). Data is buffered in on-chip memories between compute pages.

SCORE and PipeRench are both heavily pipelined and need to be supplied with a constant stream of data to perform well. They are therefore targeted towards algorithms that access data in predictable patterns such as those found in streaming media applications and DSPs, limiting their use. They also require special programming methods and tools to create the hardware configurations.

This thesis proposes a reconfigurable architecture configured by translating native code at run-time into hardware configurations; these are then stored onchip and loaded on demand into the reconfigurable hardware.

#### 2.1.5 Hardware/software partitioning

In systems that contain both a microprocessor and a reconfigurable structure the application must be partitioned into software and hardware sections. Selecting the procedures or loops to be executed in hardware is usually performed manually by the programmer. Static profiling can be used to help select the appropriate sections of code. However, this requires program behaviour at run-time to match that at the time of simulation, which may not be the case with different input data or user options.

Creating the hardware configurations typically requires special design processes and tools, and requires a different programming model for the hardware and software sections of the program. The executable is divided into two parts: one contains the software instructions that execute on the microprocessor and the other contains configuration data for the hardware. These data are loaded into the reconfigurable hardware by special instructions in the software.

HASTE [Lev05] differs by using a single programming model and executable for both the sequential processor and the reconfigurable hardware. The instruction set architecture is designed to be easily translatable to reconfigurable hardware while remaining efficiently executable in a microprocessor. During execution, core loops of a program are translated into the reconfigurable fabric by a dedicated hardware unit while the first iteration of the loop is executed on the sequential processor. The remaining iterations of the loop are then executed in the reconfigurable hardware. However, these core loops must be selected statically at compile time.

Reconfigurable systems have been shown to achieve significant benefits over traditional microprocessors [CH02]. The core algorithms that are compiled into the hardware are selected manually or using static profiling techniques; if program behaviour differs at run-time from during profiling, for example if it is dependent on input data, then the compiled hot spots may not match the hot spots executed at run-time. Additionally, different programming models are required to create hardware configurations and so these systems are not compatible with existing object code or tool-chains.

The system proposed in this thesis attempts to use reconfigurable hardware to improve performance by using *dynamic optimisation* to translate frequently executed sections of the code into a reconfigurable hardware structure at runtime. This requires additional hardware to detect hot spots at run-time, but means that only sections of code which are frequently executed during the current invocation of the program will be translated. This also allows the use of existing compiled code, removing the requirement for new programming methods and tools and maintaining backwards compatibility with legacy code.

## 2.2 Dynamic optimisation

Dynamic optimisation is the process of monitoring code behaviour as it executes and then using this information to perform optimisations on the executing program. Optimising at run-time can bring a number of benefits over performing optimisations at compile-time. Profile information can be used to target optimisations at regions of code that can gain the greatest improvement. This can include optimisations that may only give benefits in certain circumstances, such as loop unrolling and data prefetching. Profiling and optimising at run-time incurs an overhead; this must be overcome by the optimisations performed. The profile information can be used to direct optimisations towards code sections that execute most frequently; these are known as *hot spots*. Code sections that execute infrequently can be left unoptimised, thus reducing the overhead of the optimisation process.

Dynamic optimisation can also be used in conjunction with a binary translator to allow executables compiled for one instruction set to be executed transparently on an incompatible microprocessor. Optimisations are performed on translated sequences of instructions to ameliorate the performance overheads of translation. Dynamic translation is typically used to allow incompatible legacy code to run on current microprocessors; however, it can also be used to improve performance of existing binaries by allowing them to execute on a more efficient microprocessor architecture [DGB+03][EA97].

#### 2.2.1 Dynamic optimisation in software

Dynamic optimisation may be performed by software, hardware or a combination of the two. Dynamo [BDB00] is an example of a software-only dynamic optimisation system. Initially code is interpreted and likely hot spot start points such as backward branch targets (which are likely to be loop entry points) are monitored. Once a monitored point's execution count exceeds a threshold value, a trace is recorded as the instructions executed after this point are interpreted. Trace construction ends when a backward branch or a branch into an already constructed trace is encountered. Optimisations that can not be, or are not usually, performed statically, such as loop unrolling and function inlining from dynamically linked libraries, are then performed on the trace. Optimised fragments of code are then stored in a software fragment cache and executed natively on the processor (instead of being interpreted) the next time they are reached. Dynamo operates on native code: no translation is performed. However, similar techniques are used in dynamic translation systems. Some interpret and monitor code until hot spots are detected and only translate frequently executed sections to native instructions [CH97]; others, such as DAISY [EA97] and Transmeta's Crusoe [Kla00] architecture translate code as it is encountered and cache translated traces for future re-use [HKZ<sup>+</sup>06][DGB<sup>+</sup>03][EA97]. Dynamic optimisation is also used to improve the performance of Java virtual machines [BH03][AFG<sup>+</sup>00].

These systems must either interpret the code in software or translate all of the code to native instructions: this impacts on performance as interpretation is slow, and translating is a time consuming process which, if performed on large sections of code that execute infrequently, will have a large performance overhead. The dynamic optimisation system proposed in this thesis differs from these software-based dynamic optimisation systems by adding hardware to perform profiling. This allows the unoptimised code to execute in the microprocessor as opposed to being interpreted while still providing profiling support, so that only frequently executed sections of code are optimised.

#### 2.2.2 Hardware dynamic optimisation

Many hardware based dynamic optimisation techniques work by optimising instructions in a *trace cache*. A trace cache is an instruction cache that stores traces of instructions that represent the order in which they are executed dynamically as opposed to how they are arranged in memory [RBS96]. Trace caches, when combined with branch prediction techniques, allow multiple basic blocks to be fetched simultaneously thereby improving fetch bandwidth for superscalar microprocessors. Traces are constructed by a hardware unit which, in its simplest form, is a buffer that accumulates a trace of instructions as they complete and then writes this trace into the cache. Traces do not need to match the representation of instructions in memory, allowing optimisations to be performed. For example, Intel's NetBurst architecture [HSU<sup>+</sup>01] does not store the original x86 CISC instructions in the trace cache; instead, instructions are partially decoded into a RISC-like representation before being cached. This allows the execution core to be a fast, simple RISC processor, allowing improved performance.

Trace cache fill units can be used as an alternative to a superscalar engine as a method of extracting parallelism from a stream of sequential instructions [FS94]. The DIF machine [NH97] translates traces of instructions to execute in an internal VLIW parallel processor. The first time a trace is encountered it is executed in a scalar microprocessor and simultaneously scheduled and translated into a VLIW representation. Scheduled traces are then cached for future execution, removing the need to determine parallelism each time they are executed as in a superscalar microprocessor.

RePLay [PL01] extends the trace cache model by constructing regions of code containing no control instructions, called frames. The increased predictability gained from reducing the number of control instructions increases the efficiency of the fetch unit and reduces the need for fast branch predictor units. Frames are constructed by building long single-entry singleexit instruction streams consisting of many basic blocks, linked by highly biased branches. Initially code is executed as normal, and retired instructions are sent to the frame constructor. The frame constructor looks at the recent history of branches; once a branch has targeted the same address consecutively a certain number of times it is promoted to an assertion instruction. The basic blocks linked by this assertion are chained together into an instruction trace. Once this trace reaches a given size it is optimised and built into a frame. The created assertion instructions replace the conditional branches in the original instruction stream. Assertions check the conditions of the original branch, and fire if the expected conditions are not true. If an assertion fires, architectural

state is rolled back and control returns to the original, unoptimised basic block at the start of the frame (see figure 2.3).

Other systems perform more complex optimisations on the instructions in the trace cache. An Instruction Path Coprocessor (I-COP) [CS00] is an on-chip coprocessor that can be programmed to perform optimisations on instructions as they are added to the trace cache. The advantage of the I-COP is its programmability: a single simple piece of hardware can perform many different types of optimisation, and the optimisations performed can be customised for different applications.

Dynamic profiling can also be used to adapt the hardware for more efficient execution of the current program. By monitoring the relative frequency

of operations in the trace cache, reconfigurable functional units within a superscalar processor can be adapted to provide more functional units able to execute the most frequent operations [NZ04].

Many of the above systems optimise or translate all code as it is encountered. Optimised sequences are stored, for example in a trace cache, for future re-use; any overheads due to performing optimisations will usually be overcome by repeated re-execution of optimised code. However, in many programs only a small portion of code is executed very frequently; typically 90% of instructions executed dynamically come from 5-10% of the code [HP]. Many sequences are only executed infrequently; therefore optimising these sequences may incur a greater overhead than the optimisations gain. The system proposed in this thesis reduces the optimisation overhead by performing *hot spot detection* in hardware to detect the most frequently executing sections of code and only optimise those, leaving the infrequently executed remainder of the code unoptimised.

#### 2.2.3 Detecting hot spots

By monitoring a program as it executes a profile can be constructed; this can be used to determine which sections of code are worth optimising. Many profiling systems work by monitoring each branch in an executing program to give an accurate picture of how frequently sections of code have executed [CPMC96][CMH96][CLCG00]. The problem with this, from a dynamic optimisation viewpoint, is that it does not take into account how recently sections of code have executed; it merely gives an average of execution patterns in the program so far. This may cause changes in a program's behaviour to go undetected for a significant length of time. Code sections that execute very frequently for a short period of time may not be detected and optimised. An effective hot spot detector must be able to react quickly to changes in program behaviour and predict which sections of code will be executed frequently. An accurate profile of the entire program's execution is not required as execution in the near future is likely to follow recent program behaviour. In addition, only frequently executed branches need to be profiled to detect hot spots. Duesterwald et.al. demonstrate that gathering accurate dynamic profile information is not necessary to effectively predict hot paths [DB00].

One method proposed by the IMPACT group is to use a modified branch target buffer (BTB) to monitor execution frequencies of branches [MTG<sup>+</sup>99]. When a branch execute count exceeds a threshold a *candidate* bit is set. This table is cleared periodically of non-candidate branches leaving only branches which have executed frequently in that period. Candidate branches are then monitored; if a high enough proportion of the set of recently executed branches are candidate branches then the set of candidate branches is determined to be a hot spot. This hot spot is then laid out in the most frequently executed order in a region of memory called a *code cache*, and loop unrolling and other optimisations are performed [MTN<sup>+</sup>00]. The traces generated are longer than in a standard trace cache and contain sequences of instructions that are more frequently executed in sequence as they have been ordered according to profile information, providing better performance.

The system described in this thesis proposes a hot spot detection mechanism, described in Chapter 3, based on monitoring the execution of basic blocks. A dynamic hot spot detection threshold, based on the number of currently active previously detected and optimised hot spots, allows the hot spot detector to vary its sensitivity based on the current behaviour of the program and react quickly to changes in that behaviour. The detector also monitors branch bias to allow the hot spots produced to consist of a chain of basic blocks linked with highly biased branches that has a single entry and exit point. This produces smaller hot spots than other systems such as the IMPACT system, but effectively removes control information from the hot spot, increasing the scope over which optimisations can be performed (see section 4.2). Detected hot spots are optimised and translated to execute in a parallel hardware execution engine.

## 2.3 Summary

Significant performance improvements can be gained by executing core algorithms of a program in reconfigurable hardware. These core algorithms are typically selected manually or by static profiling. As program behaviour may differ with different inputs these statically selected core algorithms may not match the most frequently executed code sections at run-time. Dynamic profiling techniques allow hot spots to be detected at run-time and therefore match the current program behaviour. This thesis explores the possibility of configuring hardware at run-time from object code by using dynamic profiling to select program hot spots.

## **Chapter 3**

## Hot spot detection

The architecture described in this thesis contains a reconfigurable hardware execution engine as part of a standard microprocessor. The most frequently executed sections of code, or *hot spots*, are executed in the reconfigurable hardware and the remainder of the code is executed by the microprocessor. This chapter describes the process of profiling the code to detect these hot spots.

### 3.1 Program behaviour

To justify attempting to exploit hot spots to improve performance it is first essential to analyse the run-time behaviour of example programs and determine the properties of any contained hot spots. Such properties include the number of hot spots, their size, how frequently they execute, what proportion of the program is executed within each and the lifetime of a hot spot within the duration of a program's execution. This can be performed by analysing a *dynamic trace* of a benchmark program. A dynamic trace is a listing of the order in which instructions are executed during the execution of a program. It differs from a static listing of a program in that instructions are listed each time they are executed and so instructions can appear multiple times; instructions that are never executed do not appear in the dynamic trace.

A dynamic trace is useful for analysing program behaviour as it contains information on how frequently sections of code are used and at what points during a program they are executed. This analysis can be simplified by looking at logical blocks of code instead of individual instructions; a suitable block of code is the *dynamic basic block*.

#### 3.1.1 Dynamic basic blocks

A dynamic basic block is defined in this thesis as a maximal linear section of code with single entry and exit points and no internal control flow instructions such as branches or subroutine returns. They are dynamic entities: each instruction fetched immediately following a control flow instruction marks the entry point of a dynamic basic block; the exit point will be the next control flow instruction fetched. Dynamic basic blocks may overlap; overlapping dynamic basic blocks may have different entry points but will all end at the same control flow instruction. This can occur when a branch targets an instruction contained within an existing dynamic basic block: a second dynamic basic block exists at this entry point which overlaps the dynamic basic block containing the entry point (see figure 3.1). Note that using the standard static definition of a basic block here would result in two non-overlapping basic blocks divided at the point of the entering branch target. Using dynamic basic blocks simplifies runtime detection of entry and exit points because dynamically it is difficult to determine whether an instruction is targeted by a branch. For the remainder of this thesis dynamic basic blocks will be referred to simply as basic blocks for brevity.

Basic blocks are attractive from a code analysis and optimisation point of view for a number of reasons:

Figure 3.1: Layout of dynamic basic blocks in memory

- Atomic nature As a basic block contains no control flow instructions each instruction within is executed precisely once each time the block is executed (ignoring conditional execution of instructions found in some instruction sets, for example ARM); the reverse is not true as an instruction can be contained in more than one overlapping basic block. This simplifies analysis of code execution as fewer points need to be monitored to obtain an accurate dynamic trace of a program.

- **Simple dynamic detection** Basic block entries are straightforward to determine dynamically as a basic block entry point always follows the execution of a control flow instruction. A list of all targets of control flow instructions is equal to a list of all basic blocks.

- **Linear control flow** The linear flow of instruction execution through the block enables simple determination of data dependencies when code is being

| Benchmark                        | blowfish | cjpeg    | nasm    | qsort   |

|----------------------------------|----------|----------|---------|---------|

| Unique Basic Blocks              | 344      | 1155     | 2620    | 488     |

| Total Basic Blocks Executed      | 1922283  | 12946104 | 3340064 | 4967372 |

| Mean Executions per Unique Block | 5588     | 11209    | 1275    | 10179   |

Table 3.1: Unique basic blocks and total number of basic blocks executed, dynamic trace

optimised. The operations performed by a basic block can be described by a linear data flow graph which can be used to optimise or parallelise the code within the basic block.

#### 3.1.2 Dynamic analysis of executed basic blocks

A program contains many basic blocks; some of these will execute only once during the lifetime of the program whereas some will execute many times. A *unique basic block* is defined here as a basic block at a particular address that is executed at least once. The number of unique basic blocks and the total number of blocks executed during a run of some benchmarks is shown in table 3.1.

The size of the set of unique basic blocks varies considerably between benchmarks: during the execution of *blowfish* and *qsort* under 500 unique basic blocks execute whereas *nasm* has over 5 times this number. This corresponds to the algorithms involved: *blowfish* and *qsort* are performing a repeated small set of operations whereas *nasm*, an x86 assembler, performs a much wider variety of operations. The total number of basic blocks executed, and therefore the mean executions per block, also vary widely between the benchmarks, however these values depend on the size of the input. A larger volume of input will cause the number of basic blocks executed in these benchmarks to increase, with little or no increase in the number of unique basic blocks executed.

Figure 3.2: Cumulative percentage of total basic blocks executed by the most frequently executed unique basic blocks

#### 3.1.3 Hot spots

A hot spot is a section of code that executes frequently enough to take up a significant proportion of the total execution time. To determine whether hot spots exist, the number of times each unique basic block executes in a dynamic trace must be counted. The proportion of the blocks executed that is accounted for by the most frequently executed unique basic blocks can be used to show the presence of hot spots, as is shown in figure 3.2.

From this it can be seen that a small number of unique basic blocks accounts for a large proportion of the total dynamically executed blocks. The most frequent 16 blocks in *blowfish* account for 95% of the total blocks executed. *Blowfish* is an encryption algorithm and so performs a relatively small linear set of operations repeatedly on an input file, accounting for the small working set of basic blocks. Compared to *blowfish* the most frequent blocks in *cjpeg* and *qsort* account for a smaller percentage of the total blocks. This is partly due to the more complex algorithms involved (requiring more basic blocks within the main program loops) and partly because these programs exhibit *phased behaviour* (see next section). *Nasm,* an x86 assembler, performs very differently having a large working set of basic blocks, few of which execute very frequently. Over 60 of the most frequent blocks are required to account for 50% of the total blocks executed. This is because an assembler performs a large variety of operations on a relatively small set of input data. These results confirm a well known observation that often a large proportion of the executed time is spent within a small portion of the code [HP].

#### 3.1.4 Phased behaviour

Many programs go through a number of stages, or *phases*, during execution. These phases correspond to different stages in the program. For example a program to encrypt a file first goes through an initialisation phase where memory is allocated, command line arguments are processed and files are opened, then enters a phase to generate the keys to be used to encrypt the file and finally, performs the encryption of the file itself. These phases typically involve differing program behaviour and each will require a different set of basic blocks containing different hot spots. The initialisation phase in the encryption program will likely be short and perform a variety of tasks, so will therefore contain few significant hot spots. The file encryption stage, however, will perform a very repetitive set of operations and therefore will contain a small set of very frequently executed basic blocks.

This behaviour can be seen in figure 3.3. The frequency for each unique basic block is shown, recorded for each 100000 basic blocks executed. Each horizontal slice represents a unique basic block. Different phases of execution are clearly visible in *cjpeg* and *qsort*. The working set of frequent blocks can be seen to change about two fifths of the way through the execution of *cjpeg*. Almost 60% of the total basic block executions in the first phases are from two

Figure 3.3: Phases during program execution: each horizontal slice shows the execution frequency of a unique basic block as a percentage of the total basic blocks executed during each time interval

basic blocks; most of the remaining 40% are from only four more. These blocks make up a significant hot spot in this first phase. *Qsort* has three phases: reading in the unsorted file, performing the sort itself and then outputting the sorted data. Unlike these two benchmarks, *nasm* does not show distinct phase changes, although there are slight changes in behaviour about half way through and towards the end of the program. No horizontal slice on this graph is significantly thicker than the rest, indicating that there are no significant hot spots in this benchmark. The working set of basic blocks in this benchmark is much larger than in the other benchmarks; the grey area at the top of the graph represents unique basic blocks that are too infrequent to show (unique blocks that make up less than 0.2% of the total blocks during an interval).

The presence of phased behaviour suggests that for this system to take full advantage of the hardware execution engine it should be able to adapt to the current program behaviour. This requires the currently running program to be monitored at run-time to determine the current hot spots and to detect when these hot spots change. Section 3.4 proposes a mechanism to achieve this.

# 3.2 Chains of basic blocks

So far it has been assumed that hot spots would consist of single basic blocks. However basic blocks are typically small, averaging about seven instructions in length (see figure 3.4). Compiling these into hardware does not give much scope for optimisation and parallelism within the blocks and the short length of blocks will increase the frequency and therefore the cost of switching between hardware and software.

Blocks to be compiled into hardware can be increased in size by chaining together several that are usually executed in sequence. If the branch (or other control flow instruction) at the end of a basic block is taken in the same direction a high proportion of the time then it is determined to be a *highly*

Figure 3.4: Distribution of basic blocks in dynamic trace by number of instructions

*biased* branch. Basic blocks linked by highly biased branches can be linked together to form a larger block of instructions or *block chain*. Block chains can be constructed by repeating this process until a block is found with a branch that is not highly biased, a branch is found that loops back into the chain or the chain becomes too large. Similar methods are used in the DIF [NH97] and RePLay [PL01] mechanisms to improve optimisation scope.

The chain of blocks can be treated as a single basic block as it is compiled: all contained branches are removed and the basic blocks become a single linear block of instructions containing no control flow. During execution the situation may arise where a highly biased branch is taken against its bias; this is treated as a special case and is discussed in section 3.2.1.

Increasing the size of the compiled blocks brings a number of benefits:

**Improved optimisation scope.** A greater number of instructions within the chain increases the scope for optimisations to be applied. Removing branches between the blocks removes control dependencies, increasing

the number of independent operations and therefore increasing available parallelism. Some operations may be redundant due to not-taken branches and can be removed, and some operations for control flow (for example branch calculations and procedure call stack operations) can also be removed from the block. Section 4.2 discusses these advantages in more detail.

- **Reduced switching between hardware and software.** Larger blocks will run for a longer period of time and, as there are fewer of them to cover a given amount of code, they are less frequently entered reducing any overhead from switching between hardware and software execution. In addition the number of temporary values within the block will be increased thus reducing register bank accesses (see section 4.1.1).

- **Reduced number of hardware compilations.** Fewer individual compilations will reduce the number of compiled block definitions that must be cached and reduces the overhead of maintaining this cache (for example deciding which compilation to reject upon a new entry being added). The number of compilations performed will be reduced, although the compilation time will increase with larger, more complex blocks.

#### 3.2.1 Handling unexpected branch decisions

When block chains are executed in hardware they are treated as a linear block of instructions containing no internal branches. Chaining together blocks linked by unconditional and deterministic branches is straightforward: the branch will always be taken and so it can simply be removed. If, however, the branch is conditional the condition must be tested. The majority of the time the result of the condition test will match that observed during profiling and the block chain will complete as expected although the case may arise when the test would cause a branch out of the chain of blocks. This case must be handled to ensure the program executes correctly. It is expected that these *breakouts* are infrequent due to the highly biased nature of the branches and so handling them can be slow without significantly affecting the overall performance of the system. Chain breakouts could be handled in the following ways:

- **Continue executing in software from breakout point.** Upon detecting that a breakout has occurred the hardware structure transfers results generated before the breakout point to the microprocessor and execution continues in software. This requires the hardware structure to be able to hand control back to the software after each basic block, requiring values in each architectural register to be synchronised at the end of each basic block in the chain. This reduces the ability for operations to be scheduled independently of their original basic block, reducing the scope for parallelisation. Alternatively, register values can be preserved for each possible breakout point using register renaming [NH97], increasing the number of registers required, and operations in basic blocks before a possible exit point must be executed before the breakout can occur.

- **Restore state to before chain began executing.** If a chain must be broken out of, all results generated in the reconfigurable hardware are discarded and architectural state is restored to the point before the chain began executing. Control is handed to the microprocessor and the chain executes from the start in software. This requires the state before the chain began executing to be preserved until it is known that the block will complete. Values can only be committed to memory and registers after it is known no breakout can occur.

The latter is expensive when a breakout occurs as results generated so far have to be discarded, but this is very infrequent (see section 6.2.2) and so overall this cost is expected to be small. Therefore, this method is used, as control dependencies between operations in different basic blocks can be removed, allowing them to be scheduled in parallel if no data dependencies exist (see section 4.2.2). Additional hardware is required to preserve architectural state while the chain executes. Values in registers can be preserved by, for example, using register renaming [Kel75]: two copies of each architectural register exist, one which preserves the value at the start of the chain and one which is written to by the hardware structure. These are switched to the original values if the chain is broken out of; if it completes fully the values written by the block executing in hardware are used. A similar mechanism exists in Transmeta's Crusoe microprocessor [DGB+03]: speculatively executed operations write to a working copy of a register whilst the original value in the register is shadowed in an additional register. These shadow values can be copied into the working registers if one of the assumptions speculated upon proves to be incorrect, restoring the original state.

A write buffer [MTL95] can be used to hold stores to memory while the block is executing; this can be flushed back to memory once it is known that the block will complete. Section 5.3.1 describes this hardware support in more detail.

#### 3.2.2 Change of branch behaviour

The situation may arise when the behaviour of a branch changes during the course of a program's execution. A branch that was previously highly biased may lose this bias or it may be reversed. If this branch has been compiled into a block chain this will cause the chain to break out frequently, adversely affecting performance. This is resolved by counting the number of times a chain is broken out of; if this count exceeds a threshold then the compiled chain can be discarded, possibly allowing the hot spot detector to re-detect and recompile it with the new branch biases. Section 3.6 details how branch bias change is detected.

#### 3.2.3 Increase in block size

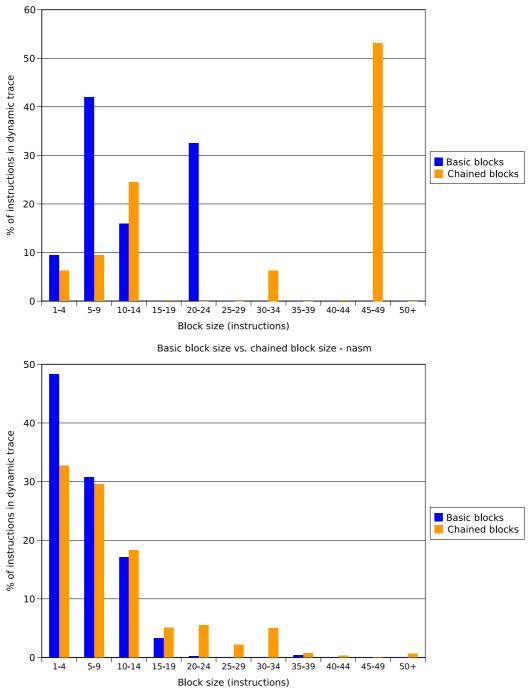

Figure 3.5 shows the proportion of instructions (in a dynamic trace) contained within different block sizes and compares basic blocks and chained blocks for *blowfish* and *nasm*. Blocks were chained together if the branch bias was  $\geq$ 99% in one direction. In *blowfish* the block chaining process more than doubles the size of the blocks in hot spots. The increase in *nasm* is less significant, although chaining does reduce the number of instructions that execute in blocks fewer than 5 instructions in size by about a third. This suggests that there are few highly-biased branches in *nasm* compared to *blowfish*; this supports other observations made that indicate the behaviour of *nasm* is not as predictable as the other benchmarks.

# 3.3 Profiling

For frequently executed basic blocks to be compiled into hardware they must be detected to be part of a hot spot. To detect hot spots the code must be *profiled*. Profiling is either *static*, when it is performed in advance, or *dynamic* when it occurs at run-time.

#### 3.3.1 Static profiling

Static profiling is performed in advance of the program being executed, usually during the compilation process of the program. The program is executed in a simulator with a sample set of data and a trace is produced. This trace is used to determine the most frequently executed code sections within the program which are then optimised and compiled into reconfigurable hardware configurations. These configurations are then distributed with the software binary, where they are loaded into the reconfigurable hardware at the appropriate time.

Basic block size vs. chained block size - blowfish

Figure 3.5: Basic block size vs. chained block size

The primary advantage of static profiling is that all the processing involved with profiling, optimisation and compilation is performed at compile-time and so there is no overhead at run-time.

However static profiling has significant disadvantages: the sample set of data used to generate the profile can differ from the data used at run-time. This can cause the program to behave differently from the static profile. Different options or program environments can also change its behaviour. This can change the hot spots in the program causing the hardware configurations generated by the static profile to no longer be valid.

With a static profile, configurations can either be loaded at the start of the program or swapped in and out of the hardware by specially inserted instructions. The latter requires phase changes to correspond to a particular point in the code. This may not be the case if behaviour changes are caused by changes in the data being processed, and so configurations must be available throughout the program even if they are not currently in use. This increases the storage required to hold configurations, possibly limiting the number of hot spots that can be compiled.

Another disadvantage of static profiling is that compilations must be distributed along with the program binary; this is not a problem for new code but legacy binaries must be profiled if they are to gain any benefit from the reconfigurable hardware.

#### 3.3.2 Dynamic profiling

Dynamic profiling is performed at run-time: the code is monitored as it executes and sections that execute frequently enough to pass a threshold are compiled into hardware. Dynamic profiling looks at the currently executing instance of the program, therefore detected hot spots are correct for the current input data and program options. Changes in program behaviour during runtime (such as entering a new phase of execution) will be detected by the dynamic profiler and a new set of hardware configurations will be generated. The set of compiled hot spots can adapt to the current program behaviour, so the need to have configurations for hot spots in all phases to be available at all times is removed. This reduces the space required to store configurations, reducing the size of the hardware or allowing a greater number of currently active hot spots to execute in hardware.

To perform dynamic profiling a method of monitoring a program at runtime is required. One of the following methods can be used:

- **Use a software interpreter.** The program is interpreted and profiled until hot spots are detected. Once detected, hot spots are executed in hardware and the remainder of the program continues to be interpreted. This requires no modifications to the code or the hardware; however, interpreting code is much slower than executing it on a microprocessor so any improvements from optimisation will have to overcome this overhead for a resulting net gain.

- **Inserting monitoring instructions.** The program can be run on a standard microprocessor with no additional hardware. Code modifications to insert monitoring instructions to update a counter table in memory are performed before the program executes. These additional instructions, plus the need to periodically break out of the program to look for hot spots, will add delay to the executing program. Instructions must be added to each basic block to construct an accurate profile. If only an estimated profile is required then the number of added instructions can be reduced by only instrumenting blocks in strategic places (for example loop or procedure call entry points); however, the ability to profile individual branch bias would be lost.

This method requires altering the program binary before execution begins by inserting instructions and altering internal addresses such as branch offsets or instructions that load constants from the code space. This method is difficult with dynamically linked libraries: they would either need to be altered in a similar fashion (requiring a copy to be created if a loaded library is shared between multiple programs) or ignored and not profiled.