# **Arithmetic and Control Components for an Asynchronous System**

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

IN THE FACULTY OF SCIENCE AND ENGINEERING

1997

Jianwei Liu

Department of Computer Science

# **Table of Contents**

| 1 | Int | rodu    | ction                                    | <b>17</b> |

|---|-----|---------|------------------------------------------|-----------|

| 2 | Ba  | ckgro   | ound                                     | 24        |

|   | 2.1 | Introd  | uction                                   | 24        |

|   | 2.2 | Basic   | concepts                                 | 26        |

|   |     | 2.2.1   | Delay models                             | 26        |

|   |     | 2.2.2   | Circuit classification                   | 26        |

|   |     | 2.2.3   | Hazards and races                        | 27        |

|   |     | 2.2.4   | Metastability and arbitration            | 27        |

|   |     | 2.2.5   | Circuit specifications                   | 28        |

|   |     | 2.2.6   | Signalling protocols                     | 29        |

|   |     | 2.2.7   | Data representation                      | 30        |

|   |     | 2.2.8   | Synthesis                                | 30        |

|   | 2.3 | Suther  | land's micropipelines                    | 31        |

|   |     | 2.3.1   | Event control modules                    | 31        |

|   |     | 2.3.2   | Event-controlled storage element         | 33        |

|   |     | 2.3.3   | Micropipeline FIFO                       | 34        |

|   |     | 2.3.4   | Micropipelines with processing           | 35        |

|   | 2.4 | The A   | MULET project                            | 35        |

|   |     | 2.4.1   | AMULET1 chip                             | 36        |

|   |     | 2.4.2   | AMULET2e chip                            | 37        |

|   |     | 2.4.3   | AMULET3i                                 | 38        |

| 3 | Ad  | der d   | lesign                                   | 39        |

|   | 3.1 | Introd  | uction                                   | 39        |

|   | 3.2 | Carry   | arbitration                              | 40        |

|   |     | 3.2.1   | Two-way carry arbiter                    |           |

|   |     | 3.2.2   | Three-way carry arbiter                  | 44        |

|   |     | 3.2.3   | Carry arbiters with more than three ways | 46        |

|   | 3.3 | Paralle | el prefix computation                    | 47        |

|   | 3.4 | Imple   | mentation                                | 49        |

|   | 3.5 | Refine  | ement of the Manchester carry chain      | 53        |

|   | 3.6 |         | ification of carry select adders         |           |

|   | 3.7  | Adder   | design for AMULET3i                       | 57 |

|---|------|---------|-------------------------------------------|----|

|   | 3.8  | Circuit | design                                    | 58 |

|   | 3.9  | Layout  | design                                    | 61 |

|   | 3.10 | Evalua  | tion                                      | 62 |

|   |      | 3.10.1  | Performance                               | 62 |

|   |      | 3.10.2  | Power consumption                         | 62 |

|   |      | 3.10.3  | Silicon area                              | 62 |

|   | 3.11 | Summa   | ary                                       | 64 |

| 4 | Mu   | ltipli  | er design                                 | 66 |

|   | 4.1  | Introdu | action                                    | 66 |

|   |      | 4.1.1   | Making each addition faster               | 68 |

|   |      | 4.1.2   | Reducing the number of additions required | 70 |

|   | 4.2  | AMUL    | ET2e multiplier                           | 72 |

|   | 4.3  | Multip  | ly support for AMULET3i                   | 75 |

|   |      | 4.3.1   | Normal multiply                           | 75 |

|   |      | 4.3.2   | Long multiply                             | 75 |

|   | 4.4  | Multip  | lier organization                         | 76 |

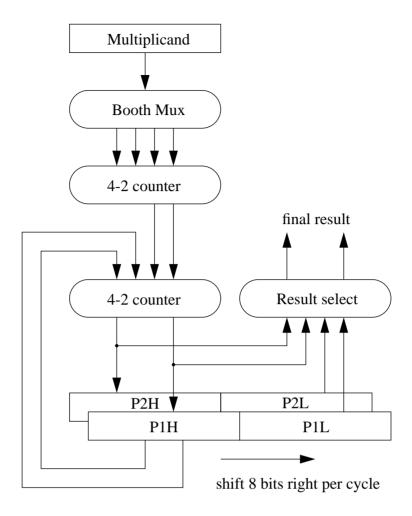

|   |      | 4.4.1   | First design iteration                    | 76 |

|   |      | 4.4.2   | Encoding technique                        | 77 |

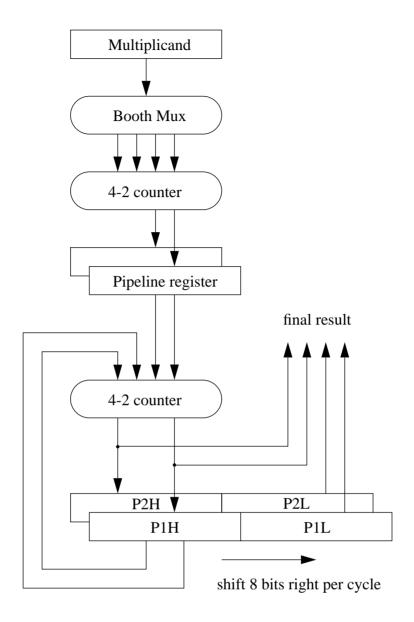

|   |      | 4.4.3   | Second design iteration                   | 79 |

|   |      | 4.4.4   | Sign extension                            | 81 |

|   | 4.5  | Circuit | design                                    | 82 |

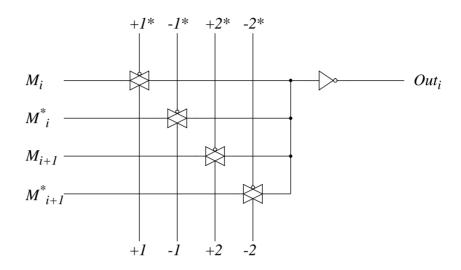

|   |      | 4.5.1   | Booth mux cell design                     | 82 |

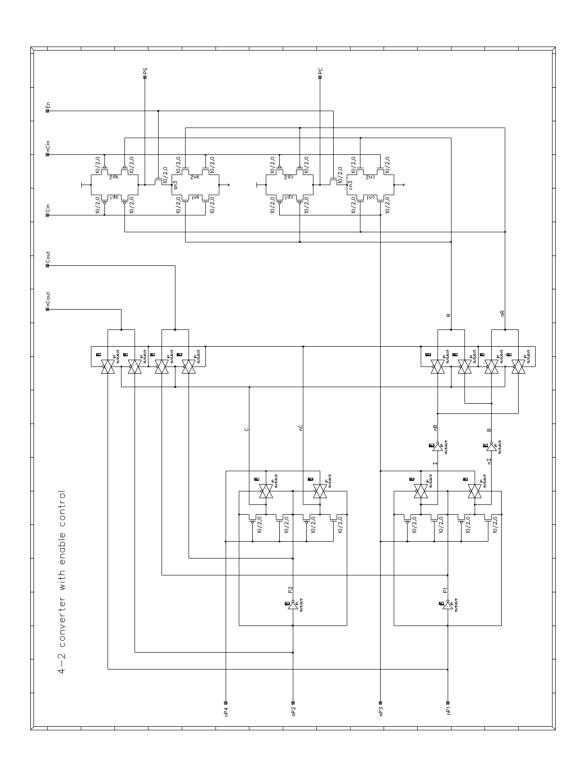

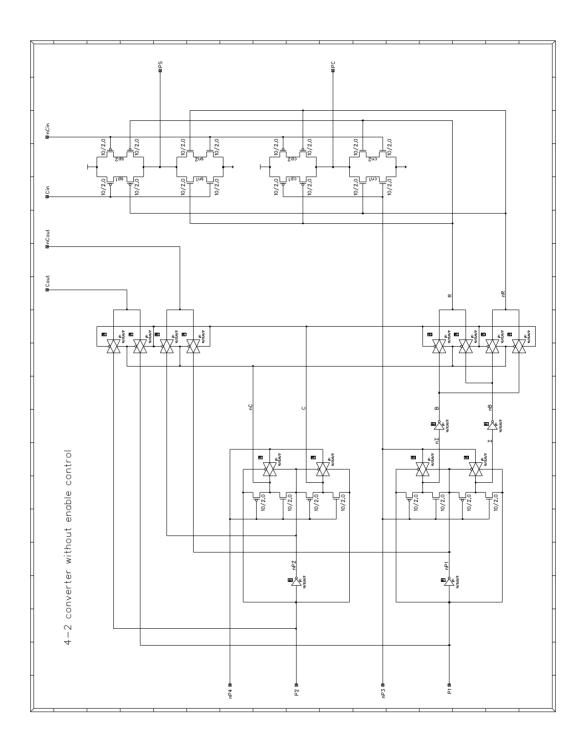

|   |      | 4.5.2   | 4-2 Counter design                        | 84 |

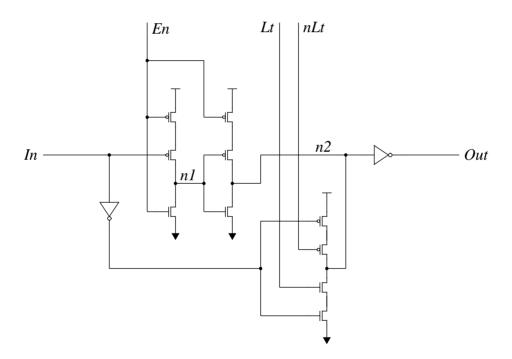

|   |      | 4.5.3   | Pipeline register design                  | 88 |

|   |      | 4.5.4   | Partial product register design           | 90 |

|   |      | 4.5.5   | Low power design                          | 91 |

|   | 4.6  | Layout  | design                                    | 93 |

|   | 4.7  | Evalua  | tion                                      | 93 |

|   |      | 4.7.1   | Performance                               | 94 |

|   |      | 4.7.2   | Power consumption                         | 94 |

|   |      | 4.7.3   | Silicon area                              | 94 |

|   | 4.8  | Summa   | ary                                       | 96 |

| 5 | For  | ır-ph   | ase pipeline control                      | 97 |

|   | 5.1  | Introdu | action                                    | 97 |

|   | 5.2  | Data-v  | alidity scheme                            | 98 |

|   | 5.3  | Logic activation configuration       | 100 |

|---|------|--------------------------------------|-----|

|   | 5.4  | Decoupling degree                    | 101 |

|   | 5.5  | ERU latch control circuit            | 102 |

|   | 5.6  | ERS latch control circuit            | 103 |

|   | 5.7  | ERF latch control circuit            | 106 |

|   | 5.8  | BRU latch control circuit            | 107 |

|   | 5.9  | BRS latch control circuit            | 108 |

|   | 5.10 | BRF latch control circuit            | 109 |

|   | 5.11 | BAS & BAF latch control circuits     | 111 |

|   | 5.12 | Interfacing                          | 114 |

|   | 5.13 | Low-power design using dynamic logic | 115 |

|   | 5.14 | Simulation results                   | 117 |

|   | 5.15 | Discussion                           | 118 |

|   | 5.16 | Summary                              | 120 |

| 6 | Fou  | r-phase control modules              | 121 |

|   | 6.1  | Introduction                         | 121 |

|   | 6.2  | CALL modules                         | 123 |

|   |      | 6.2.1 pCALL module                   | 123 |

|   |      | 6.2.2 dCALL module                   | 124 |

|   |      | 6.2.3 bCALL module                   | 126 |

|   | 6.3  | ARBITER modules                      | 127 |

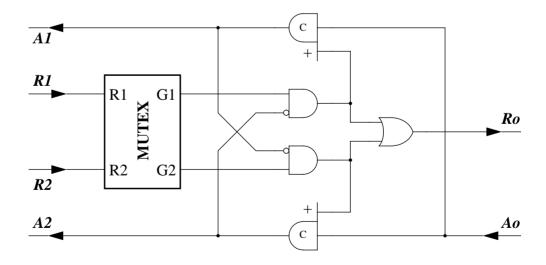

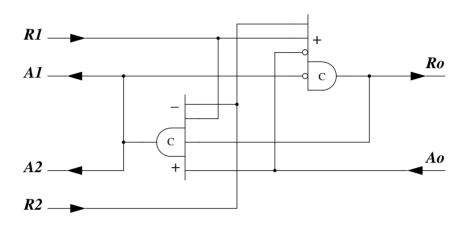

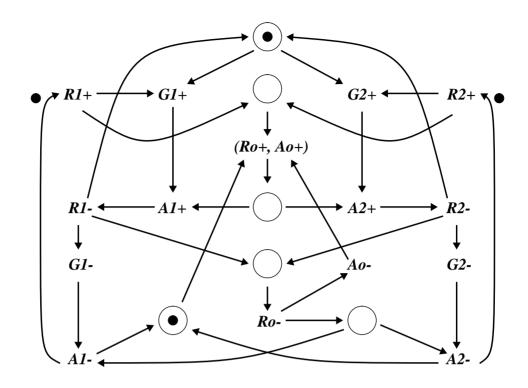

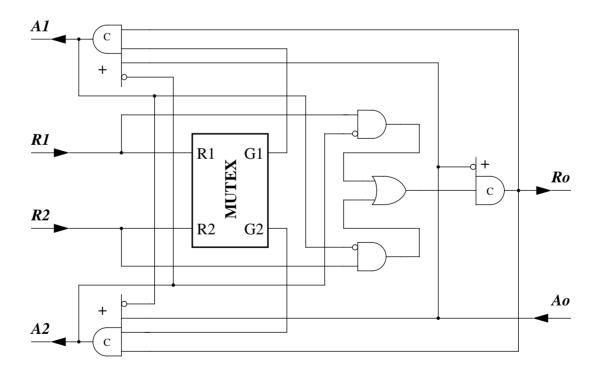

|   |      | 6.3.1 pARBITER module                | 128 |

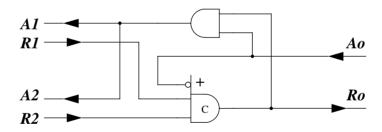

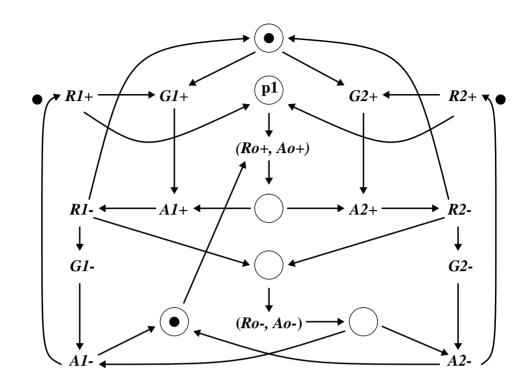

|   |      | 6.3.2 dARBITER module                | 130 |

|   |      | 6.3.3 bARBITER module                | 131 |

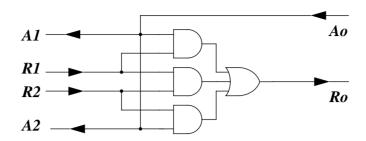

|   | 6.4  | JOIN modules                         | 133 |

|   |      | 6.4.1 pJOIN module                   | 133 |

|   |      | 6.4.2 dJOIN module                   | 133 |

|   |      | 6.4.3 bJOIN module                   | 134 |

|   | 6.5  | FORK modules                         | 135 |

|   |      | 6.5.1 pFORK module                   | 135 |

|   |      | 6.5.2 dFORK module                   | 135 |

|   |      | 6.5.3 bFORK module                   | 136 |

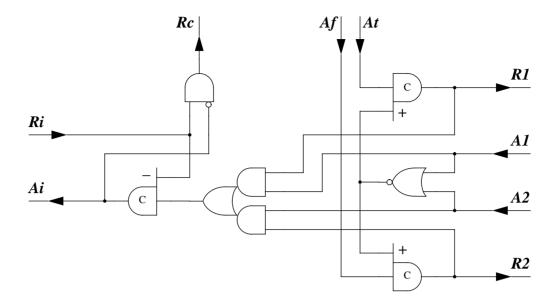

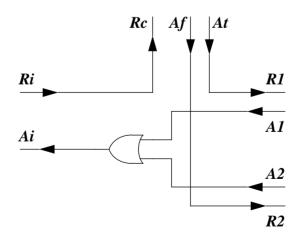

|   | 6.6  | SELA modules                         | 137 |

|   |      | 6.6.1 pSELA module                   | 137 |

|   |      | 6.6.2 dSELA module                   | 138 |

|   |      | 6.6.3 bSELA module                   | 138 |

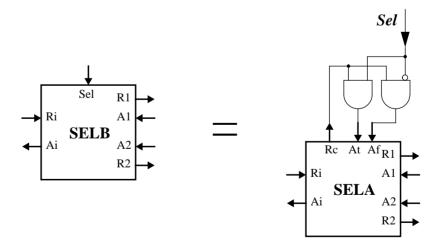

|     | 6.7                    | SELB modules                      | 140 |

|-----|------------------------|-----------------------------------|-----|

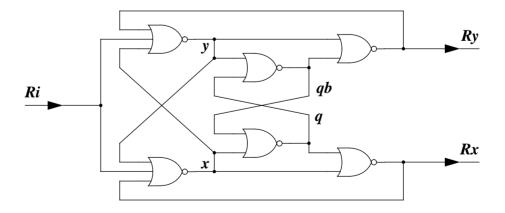

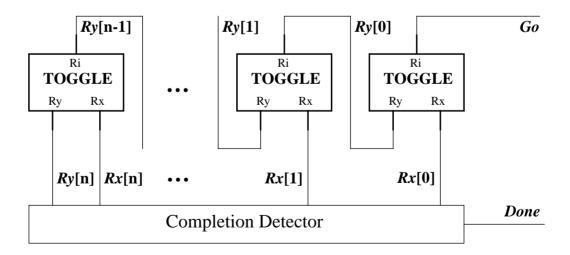

|     | 6.8                    | TOGGLE module                     | 141 |

|     | 6.9                    | An example: a counter             | 142 |

|     | 6.10                   | Arbiter modules revisited         | 143 |

|     |                        | 6.10.1 eARBITER module            | 143 |

|     |                        | 6.10.2 fARBITER module            | 143 |

|     | 6.11                   | Modules with multiple input links | 146 |

|     | 6.12                   | Summary                           | 148 |

| 7   | $\mathbf{A}\mathbf{M}$ | IULET3i                           | 149 |

|     | 7.1                    | Introduction                      | 149 |

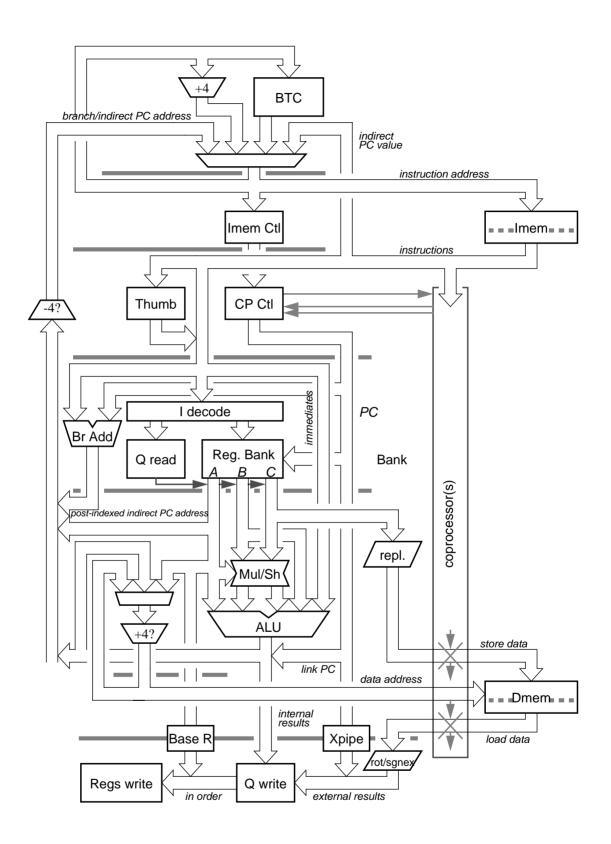

|     | 7.2                    | AMULET3i                          | 150 |

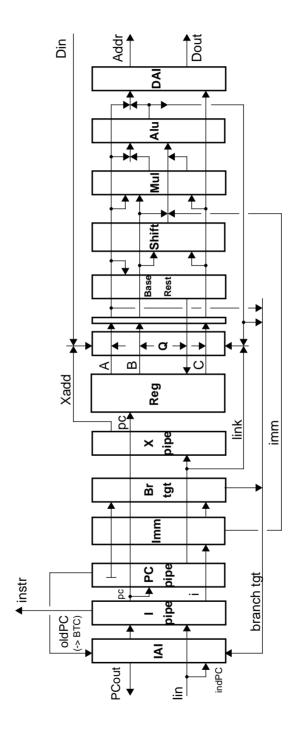

|     | 7.3                    | AMULET3                           | 151 |

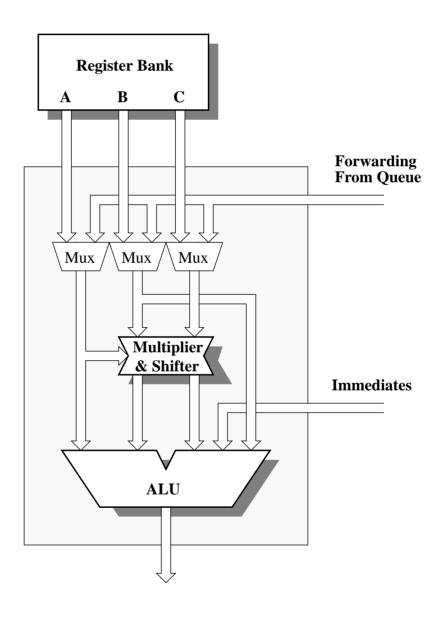

|     | 7.4                    | Execution unit                    | 154 |

|     | 7.5                    | Implementation                    | 155 |

|     | 7.6                    | Summary                           | 156 |

| 8   | Coı                    | nclusions                         | 157 |

|     | 8.1                    | Contributions                     | 157 |

|     | 8.2                    | Future work                       | 159 |

|     |                        | 8.2.1 Low power market            | 159 |

|     |                        | 8.2.2 Mobile communication market | 160 |

|     | 8.3                    | Asynchronous prospects            | 161 |

| Bil | bliog                  | raphy                             | 162 |

| A   | Ado                    | der schematics                    | 170 |

| В   | 4 .1.                  | der layouts                       | 176 |

|     | Au                     | aci layouts                       | 170 |

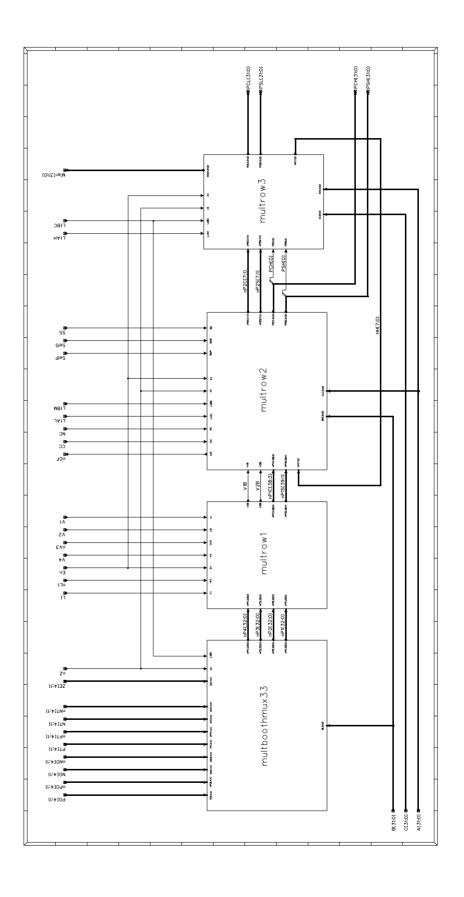

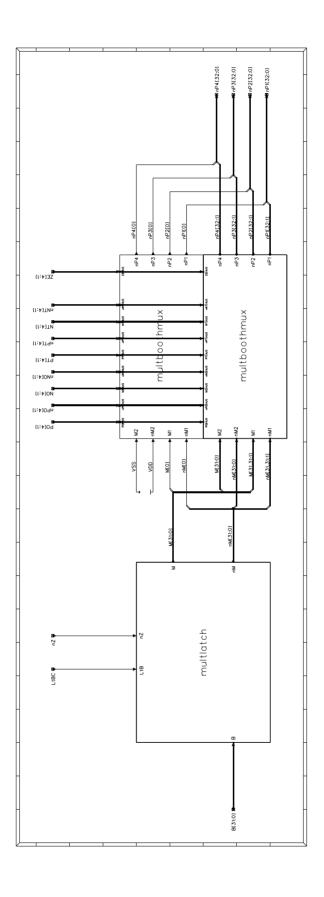

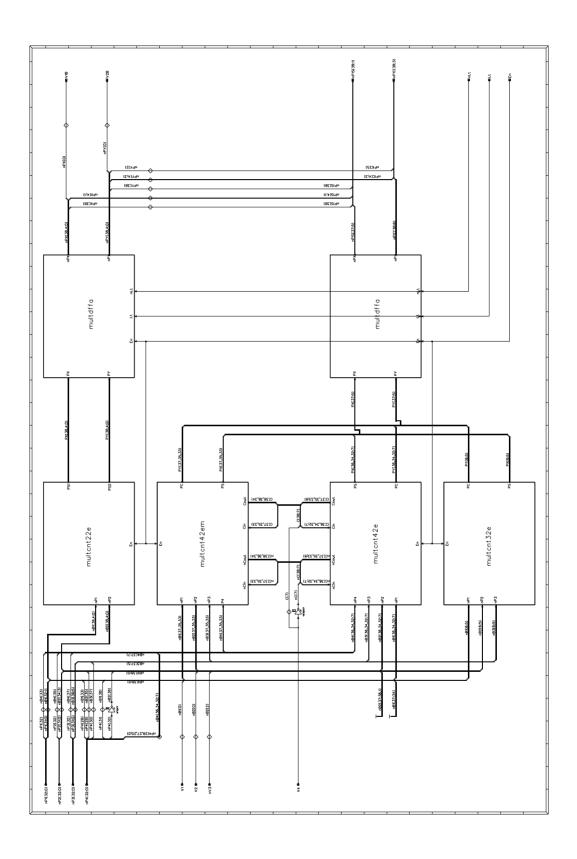

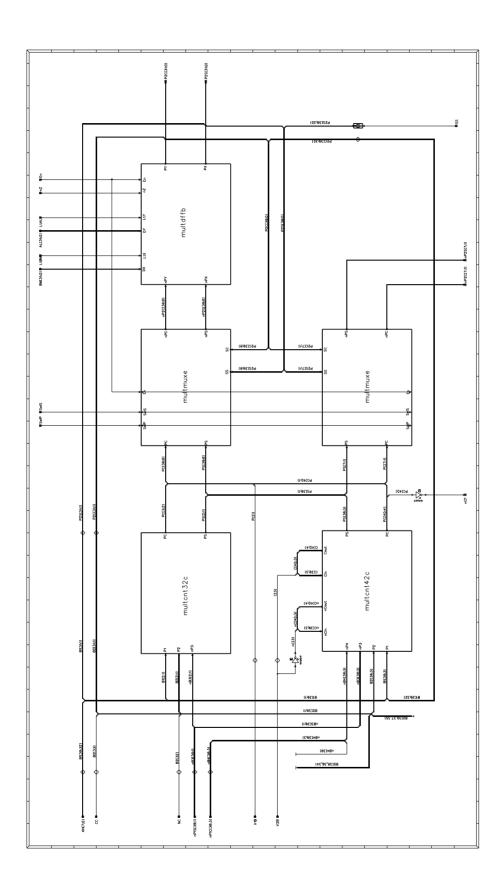

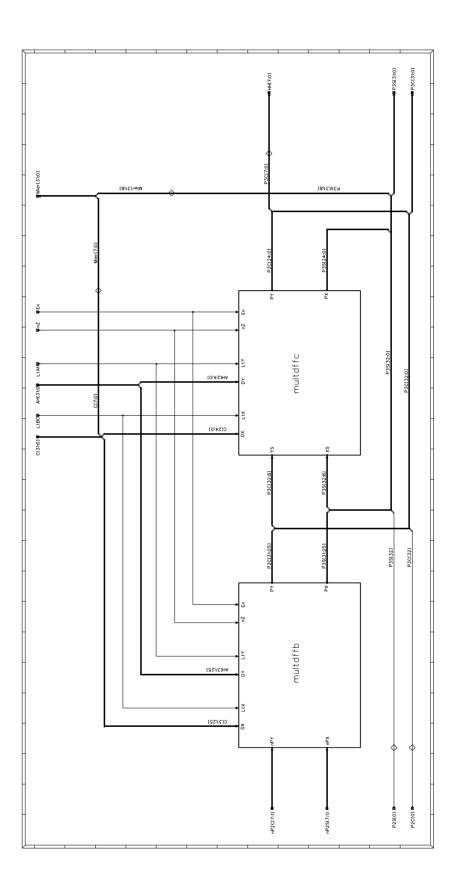

| C   |                        | ltiplier schematics               | 181 |

# **List of Figures**

| 2-1  | A bundled data interface                                            | 31 |

|------|---------------------------------------------------------------------|----|

| 2-2  | Micropipeline event logic modules                                   | 32 |

| 2-3  | Event-controlled storage element                                    | 33 |

| 2-4  | Micropipeline FIFO                                                  | 34 |

| 2-5  | Basic micropipeline structure                                       | 36 |

| 3-1  | Two-way carry arbiter                                               | 41 |

| 3-2  | 4-bit carry computation                                             | 42 |

| 3-3  | Three-way carry arbiter                                             | 45 |

| 3-4  | 9-bit carry computation                                             | 46 |

| 3-5  | Static implementation of a two-way carry arbiter                    | 50 |

| 3-6  | Pass-transistor based implementation                                | 50 |

| 3-7  | Direct implementation of a three-way carry arbiter                  | 51 |

| 3-8  | Modified implementation of a three-way carry arbiter                | 52 |

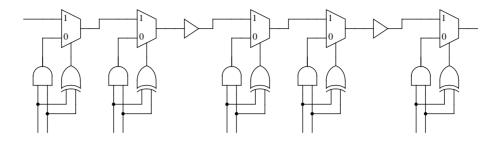

| 3-9  | Manchester carry chain with buffers                                 | 54 |

| 3-10 | Manchester carry chain without buffers                              | 54 |

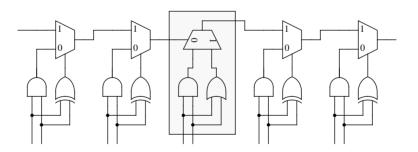

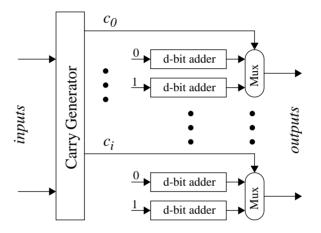

| 3-11 | Carry select adder                                                  | 55 |

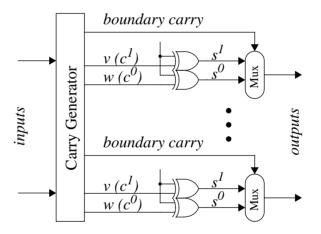

| 3-12 | New carry select adder                                              | 56 |

| 3-13 | AMULET3i adder block diagram                                        | 57 |

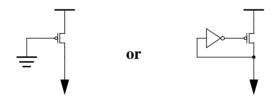

| 3-14 | Devices for dynamic circuits                                        | 58 |

| 3-15 | Static Implementation of a three-way carry arbiter                  | 59 |

| 3-16 | New Implementation of a three-way carry arbiter                     | 60 |

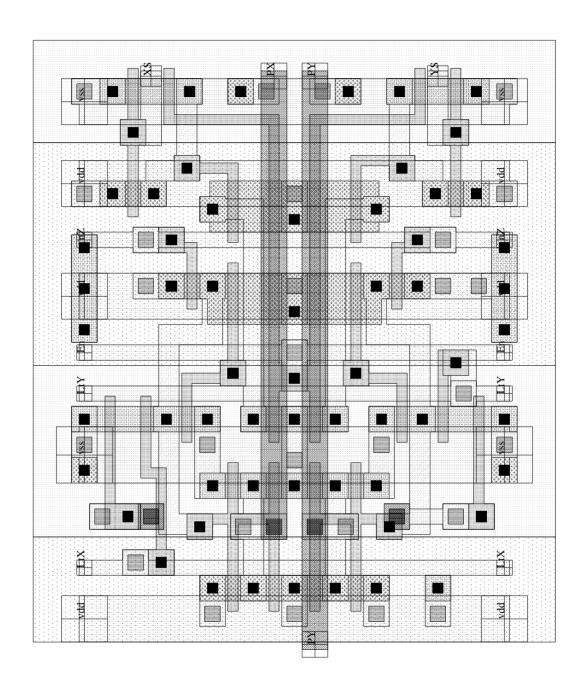

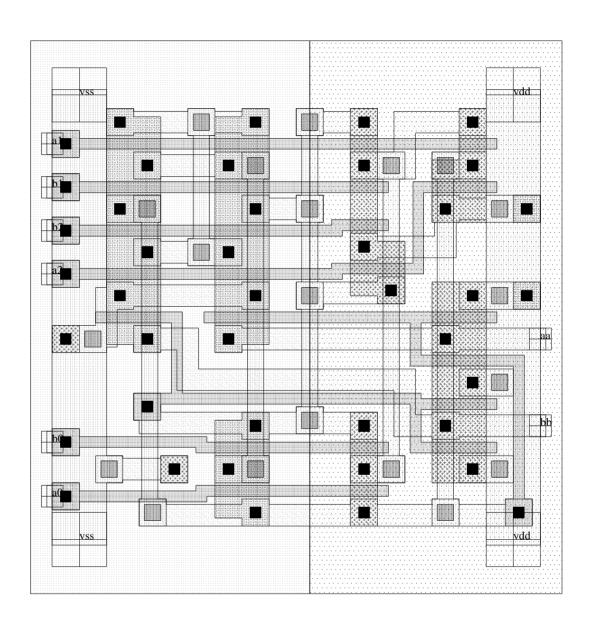

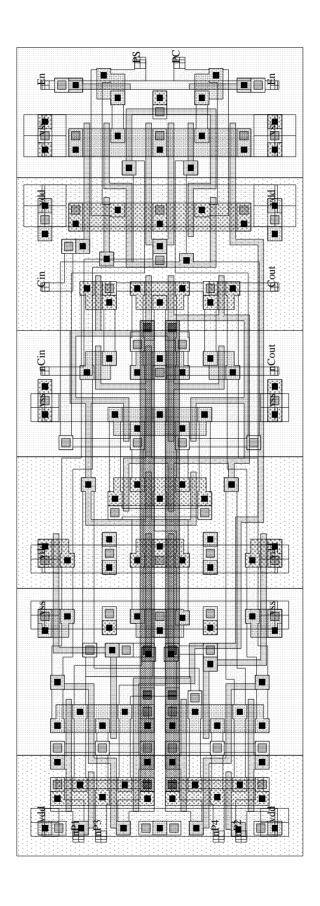

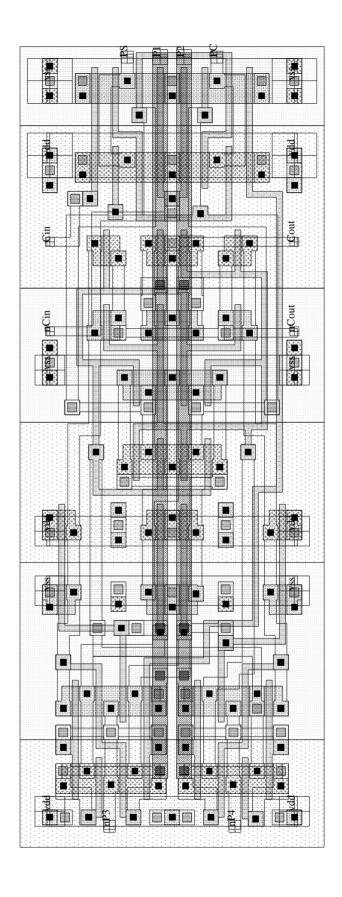

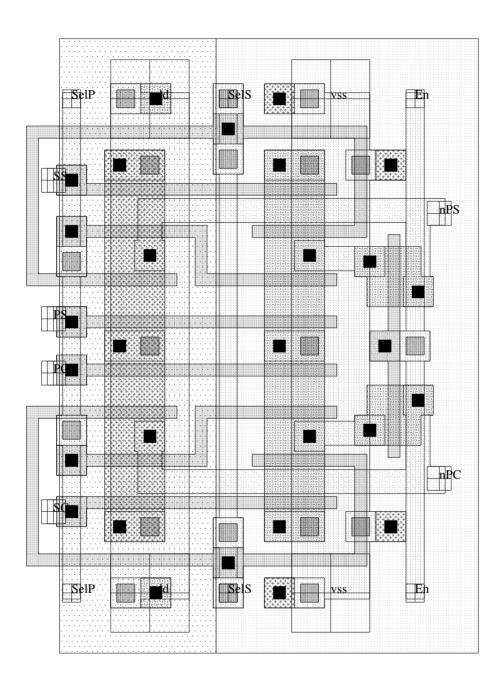

| 3-17 | Physical layout of the adder datapath                               | 63 |

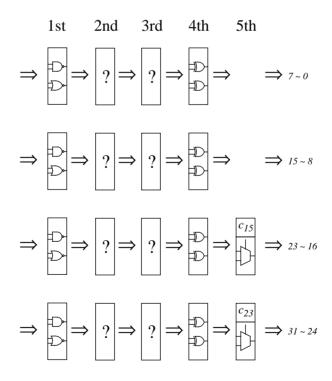

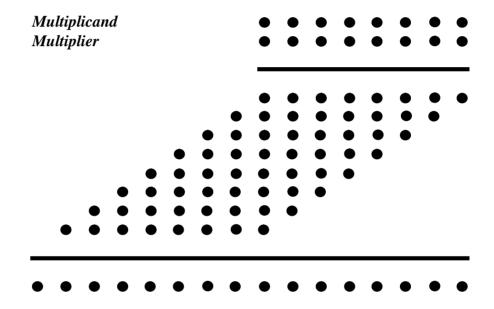

| 4-1  | Dot representation of $8 \times 8$ bit add and shift multiplication | 67 |

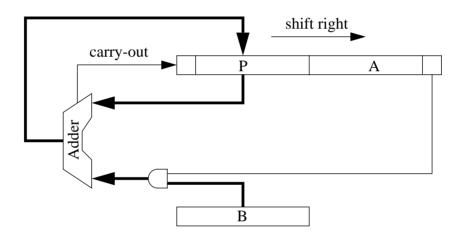

| 4-2  | A simple multiplier                                                 | 68 |

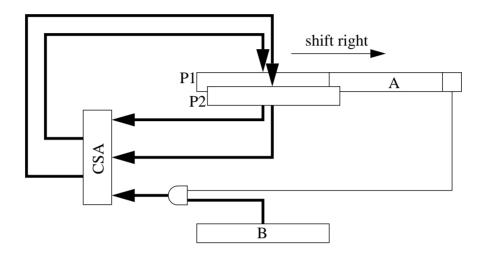

| 4-3  | A carry-save multiplier                                             | 69 |

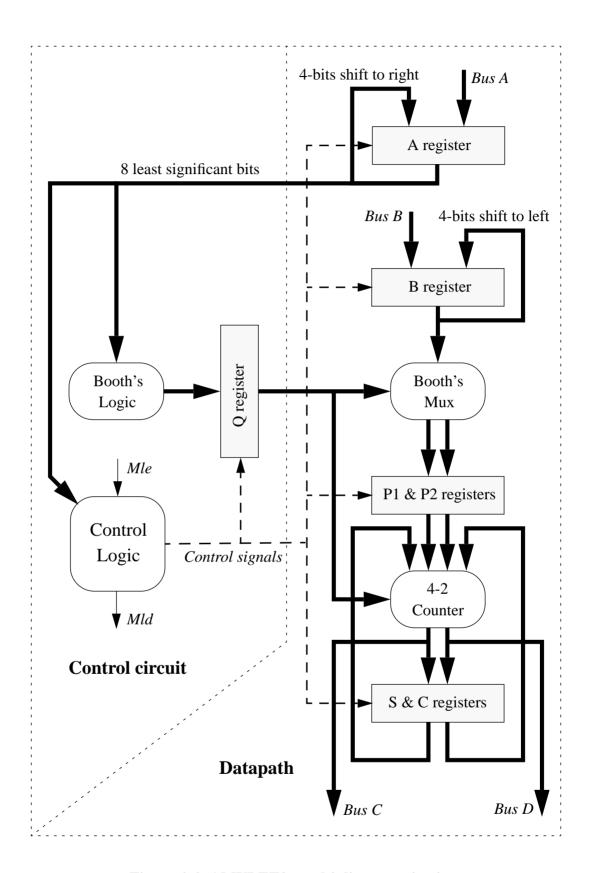

| 4-4  | AMULET2e multiplier organization                                    | 73 |

| 4-5  | First version                                                       | 78 |

| 4-6  | Second version                               | 80  |

|------|----------------------------------------------|-----|

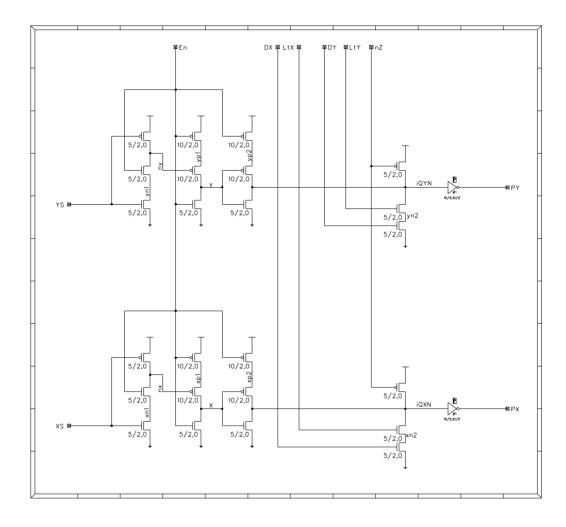

| 4-7  | Booth mux cell                               | 83  |

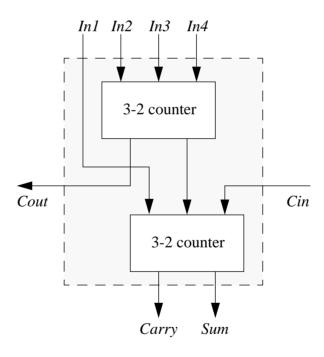

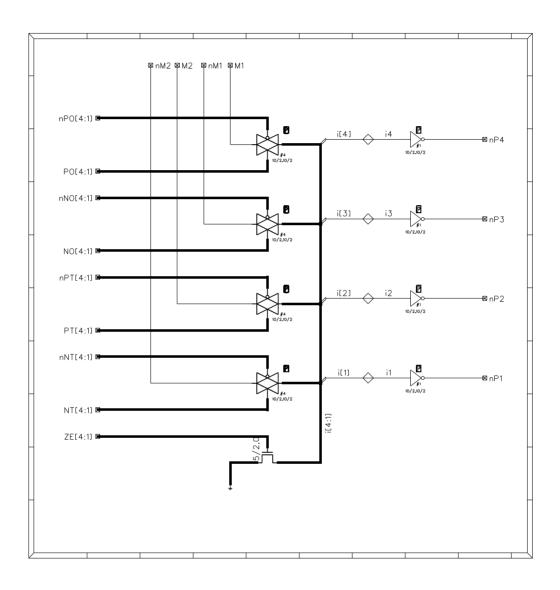

| 4-8  | 4-2 Counter structure                        | 84  |

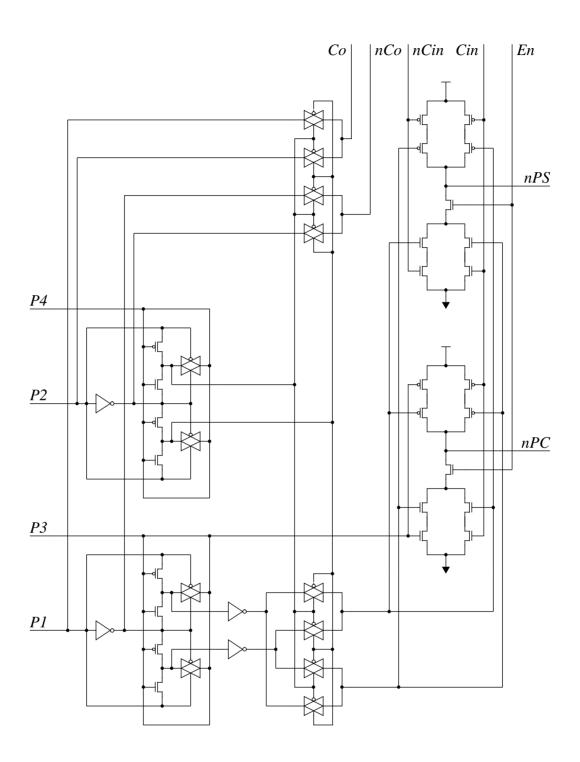

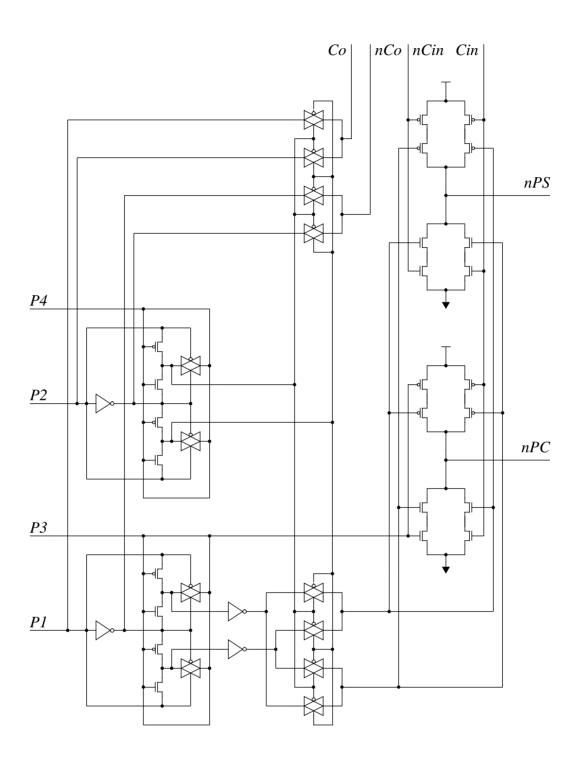

| 4-9  | 4-2 Counter with enable control              | 86  |

| 4-10 | 4-2 Counter without enable control           | 87  |

| 4-11 | Pipeline register                            | 89  |

| 4-12 | Partial product register                     | 91  |

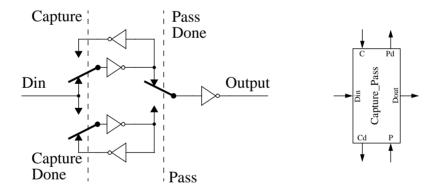

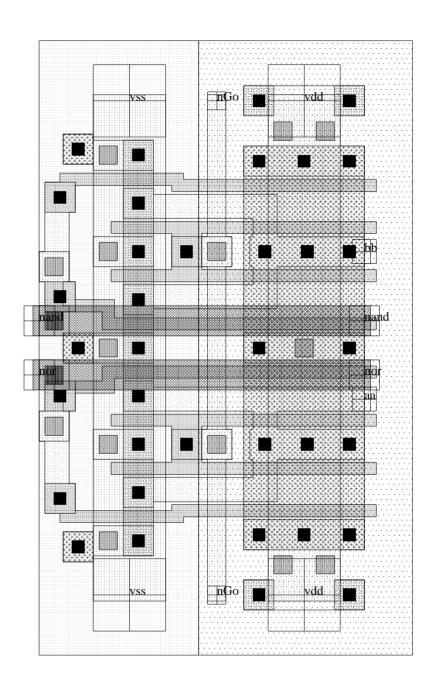

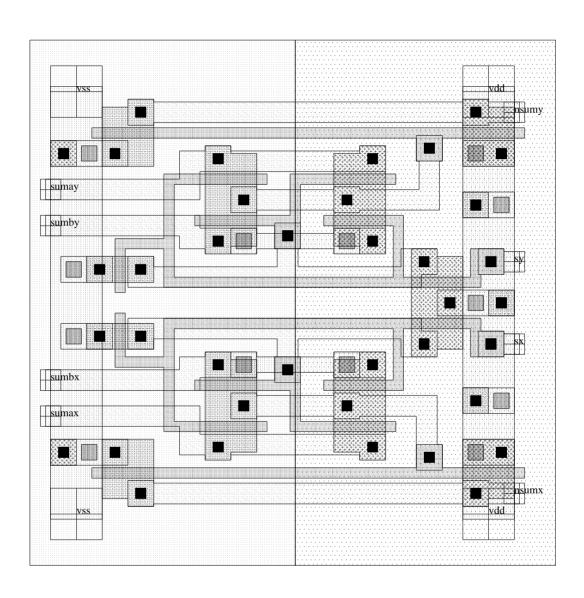

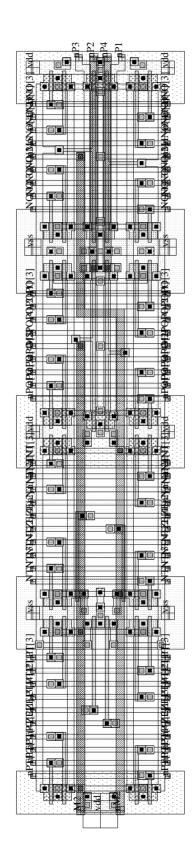

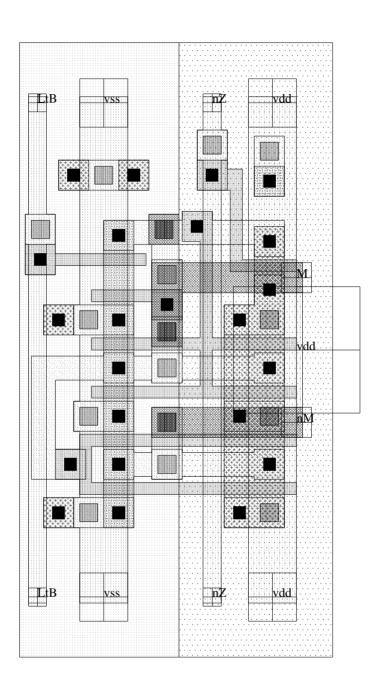

| 4-13 | Physical layout of the multiplier datapath   | 95  |

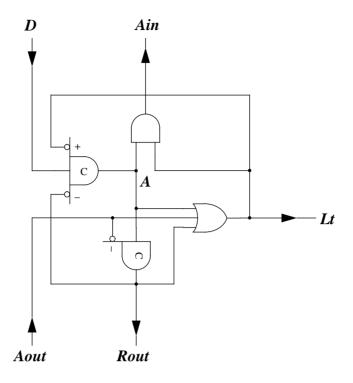

| 5-1  | Micropipeline stage structure                | 98  |

| 5-2  | Three data-validity schemes                  | 99  |

| 5-3  | "Request-activate" configuration             | 100 |

| 5-4  | "Acknowledge-activate" configuration         | 101 |

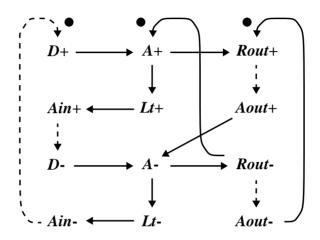

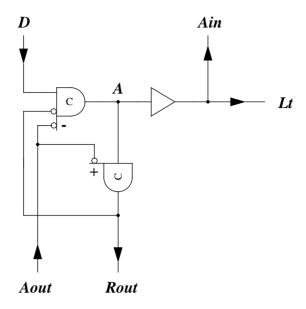

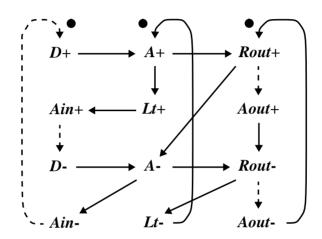

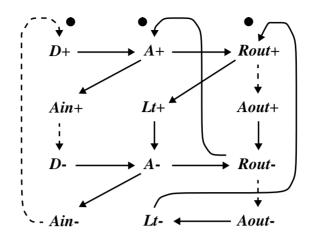

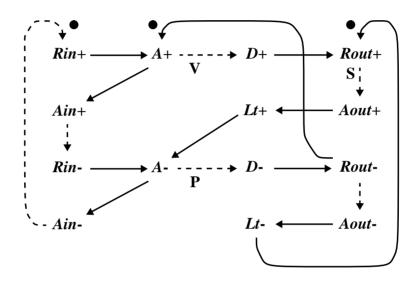

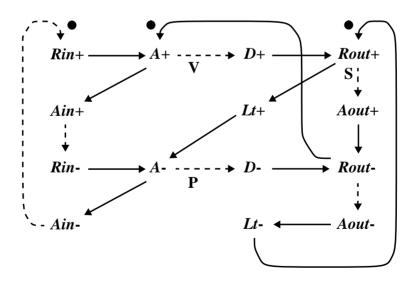

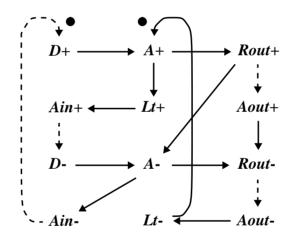

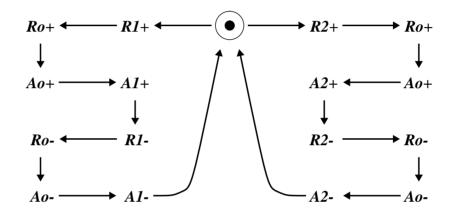

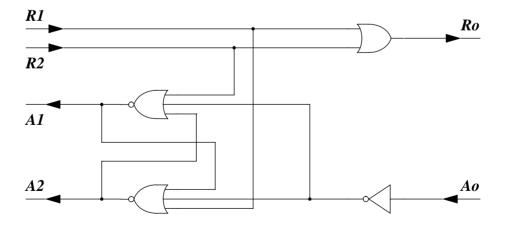

| 5-5  | STG of the ERU latch control circuit         | 102 |

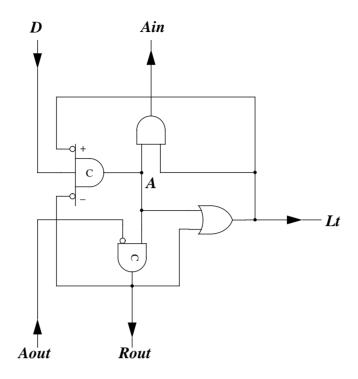

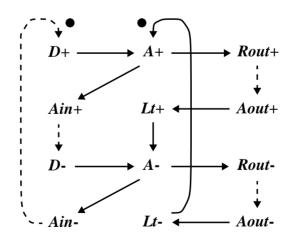

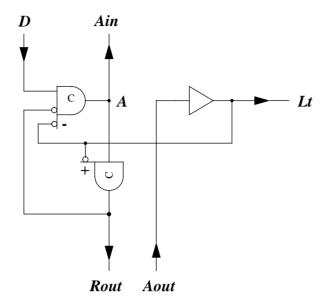

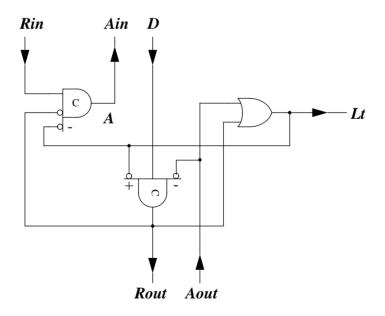

| 5-6  | ERU latch control circuit                    | 103 |

| 5-7  | STG of the ERS latch control circuit         | 104 |

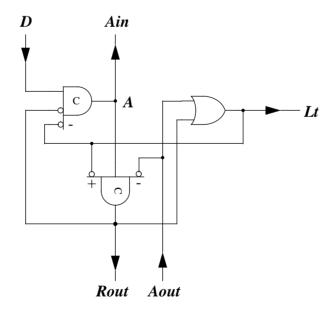

| 5-8  | ERS latch control circuit                    | 105 |

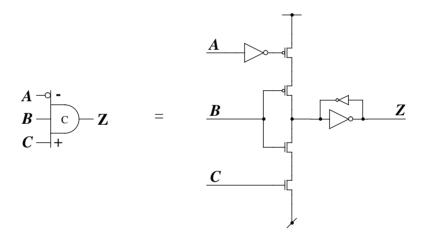

| 5-9  | Asymmetric C-gate notation                   | 105 |

| 5-10 | STG of the ERF latch control circuit         | 106 |

| 5-11 | ERF latch control circuit                    | 107 |

| 5-12 | STG of the BRU latch control circuit         | 107 |

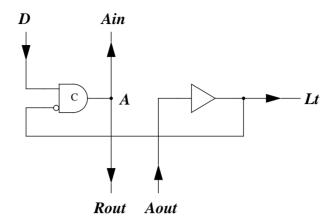

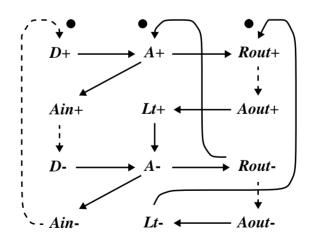

| 5-13 | BRU latch control circuit                    | 108 |

| 5-14 | STG of the BRS latch control circuit         | 108 |

| 5-15 | BRS latch control circuit                    | 109 |

| 5-16 | STG of the BRF latch control circuit         | 110 |

| 5-17 | BRF latch control circuit                    | 110 |

| 5-18 | Another "Acknowledge-activate" configuration | 111 |

| 5-19 | STG of the BAS latch control circuit         | 112 |

| 5-20 | STG of the BAF latch control circuit         | 112 |

| 5-21 | BAS latch control circuit                    | 113 |

| 5-22 | BAF latch control circuit                    | 113 |

| 5-23 | STG of the Converter                         | 114 |

| 5-24 | Converter circuit                            | 115 |

| 5-25 | Test circuit                       | 118 |

|------|------------------------------------|-----|

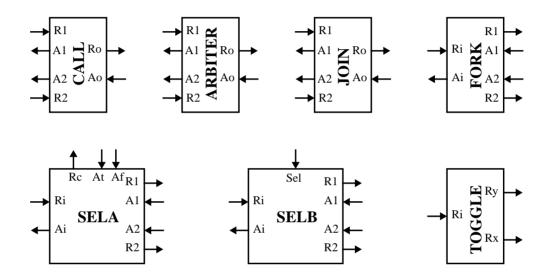

| 6-1  | Four-phase control modules         | 122 |

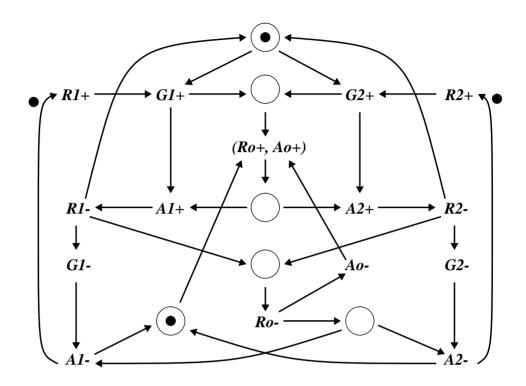

| 6-2  | PN of the pCALL module             | 124 |

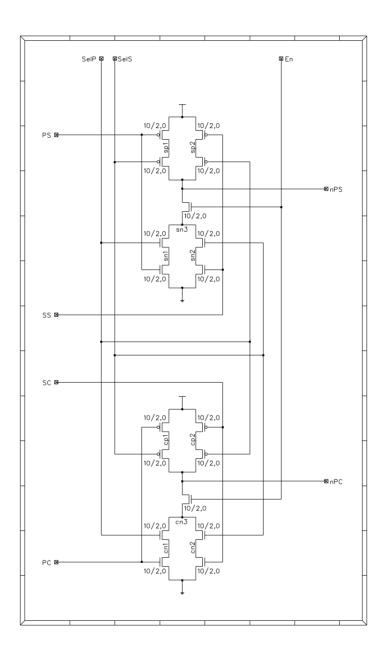

| 6-3  | pCALL circuit implementation       | 124 |

| 6-4  | PN of the dCALL module             | 125 |

| 6-5  | dCALL circuit implementation       | 125 |

| 6-6  | PN of the sCALL module             | 126 |

| 6-7  | sCALL circuit implementation       | 126 |

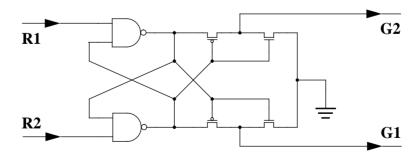

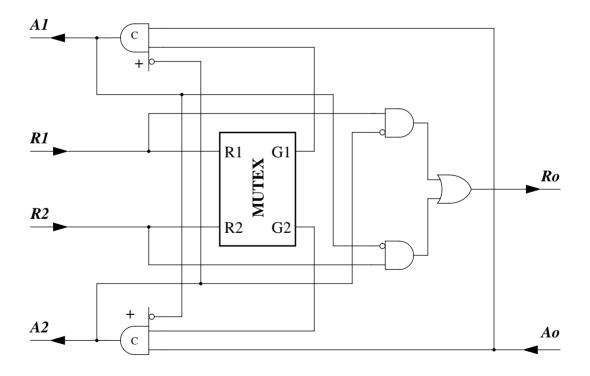

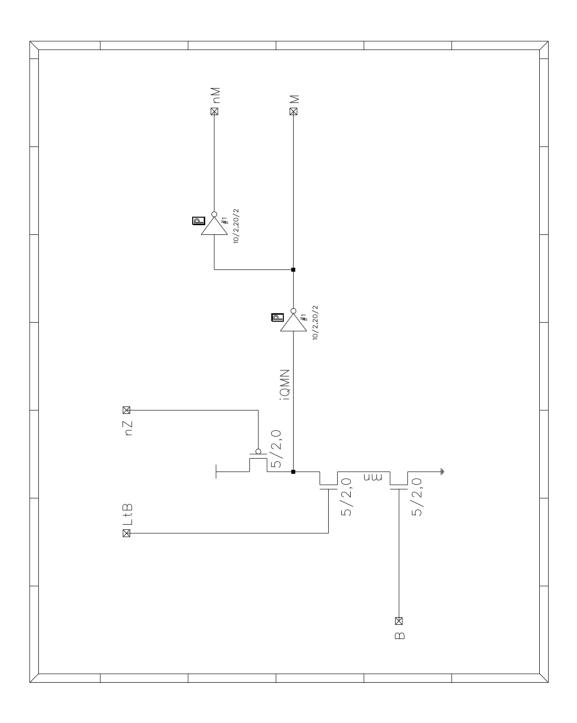

| 6-8  | MUTEX circuit                      | 127 |

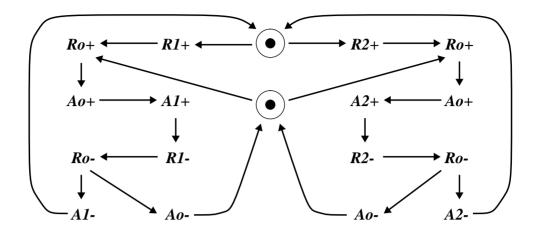

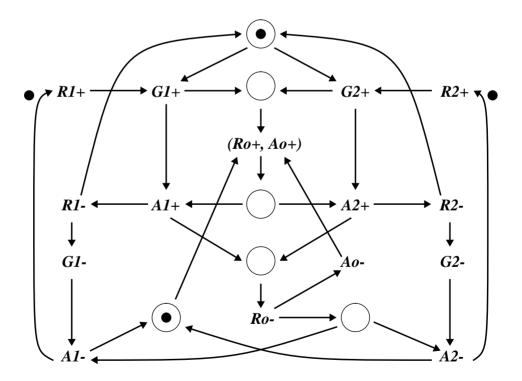

| 6-9  | PN of the pARBITER module          | 129 |

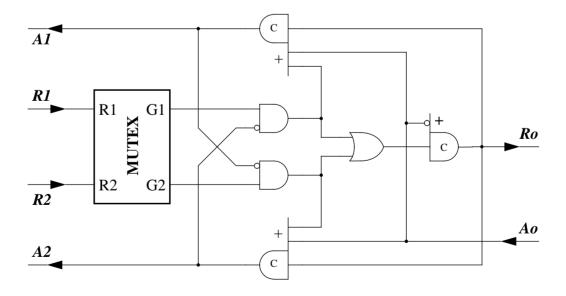

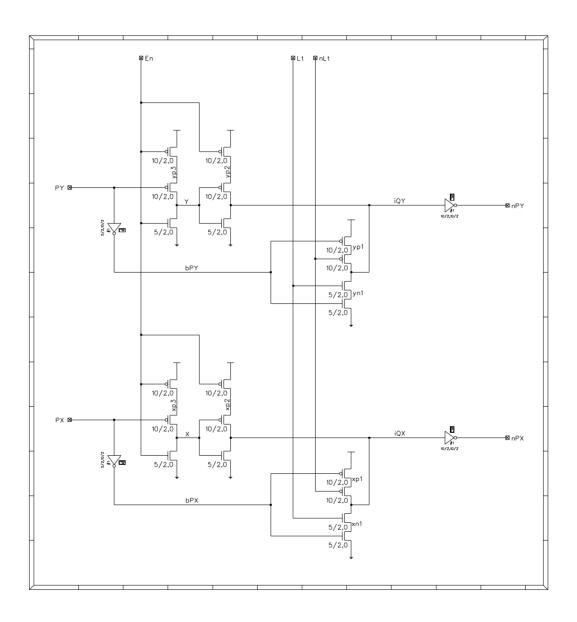

| 6-10 | pARBITER circuit implementation    | 129 |

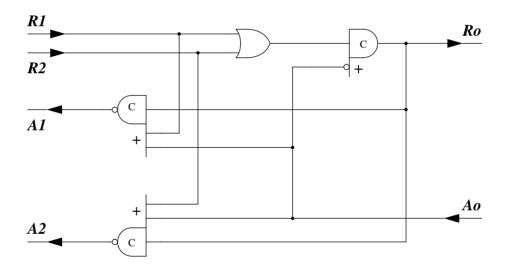

| 6-11 | PN of the dARBITER module          | 130 |

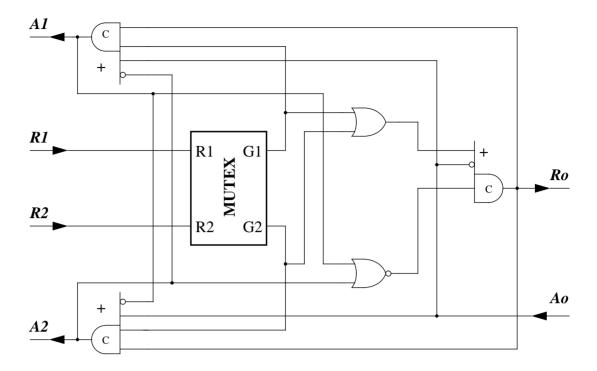

| 6-12 | dARBITER circuit implementation    | 131 |

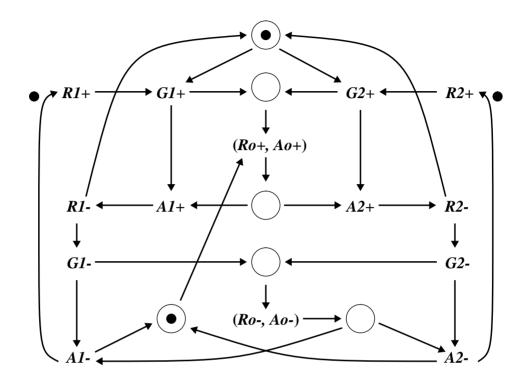

| 6-13 | PN of the bARBITER                 | 132 |

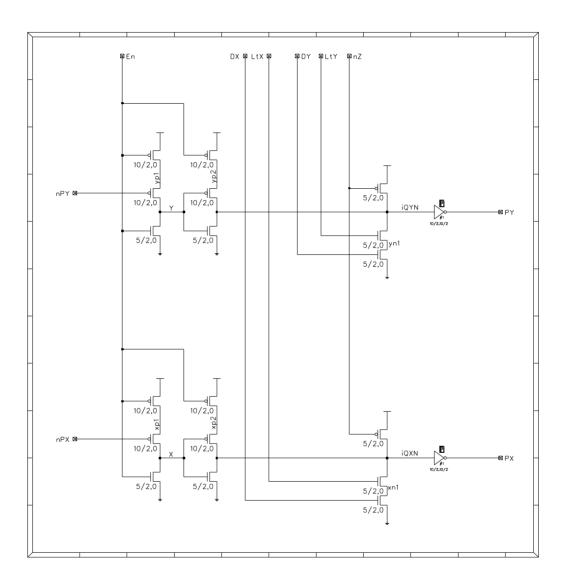

| 6-14 | bARBITER circuit implementation    | 132 |

| 6-15 | pJOIN circuit implementation       | 133 |

| 6-16 | dJOIN circuit implementation       | 134 |

| 6-17 | bJOIN circuit implementation       | 135 |

| 6-18 | pFORK circuit implementation       | 136 |

| 6-19 | dFORK circuit implementation       | 136 |

| 6-20 | bFORK circuit implementation       | 137 |

| 6-21 | pSELA circuit implementation       | 138 |

| 6-22 | dSELA circuit implementation       | 139 |

| 6-23 | bSELA circuit implementation       | 139 |

| 6-24 | Implementation of the SELB modules | 140 |

| 6-25 | TOGGLE circuit implementation      | 141 |

| 6-26 | Speed-independent incrementer      | 142 |

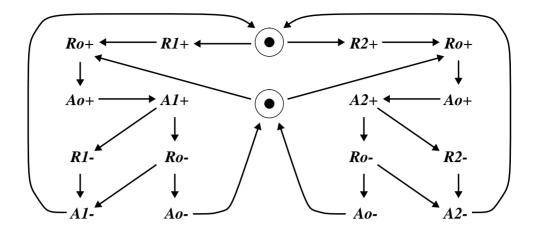

| 6-27 | PN of the eARBITER module          | 144 |

| 6-28 | eARBITER circuit implementation    | 144 |

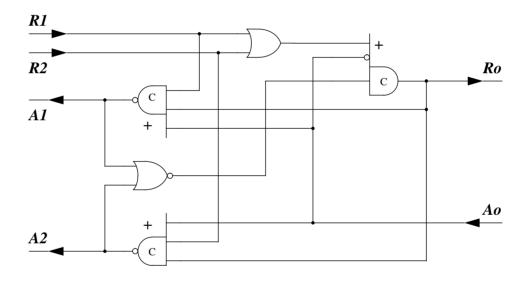

| 6-29 | PN of the fARBITER module          | 145 |

| 6-30 | fARBITER circuit implementation    | 145 |

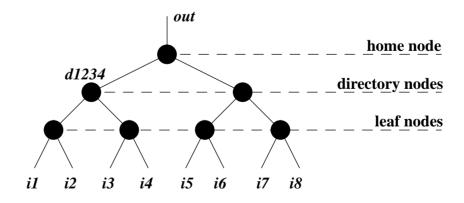

| 6-31 | Tree arbiter                       | 146 |

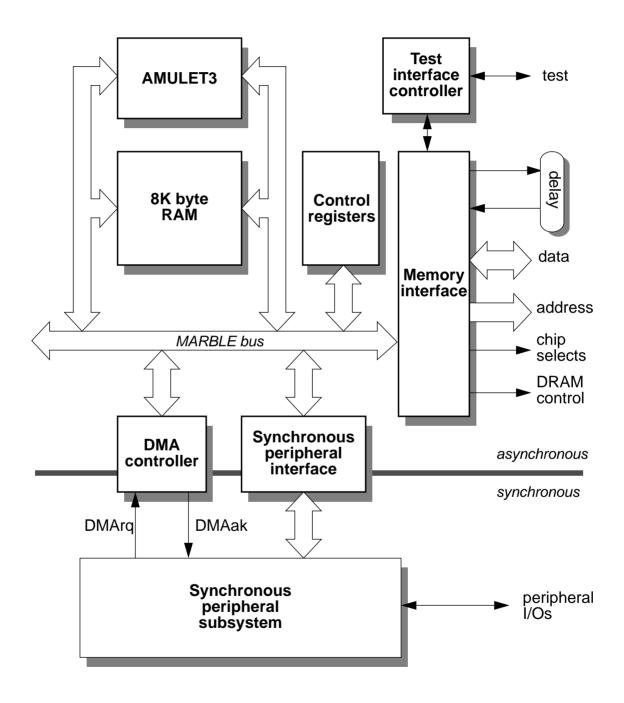

| 7-1 | AMULET3i block diagram          | 150 |

|-----|---------------------------------|-----|

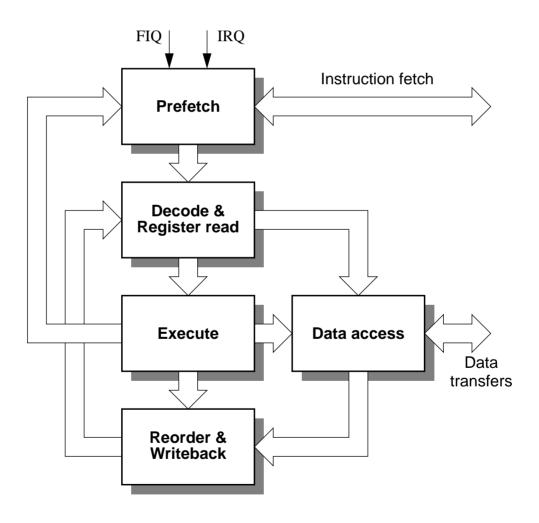

| 7-2 | AMULET3 block diagram           | 151 |

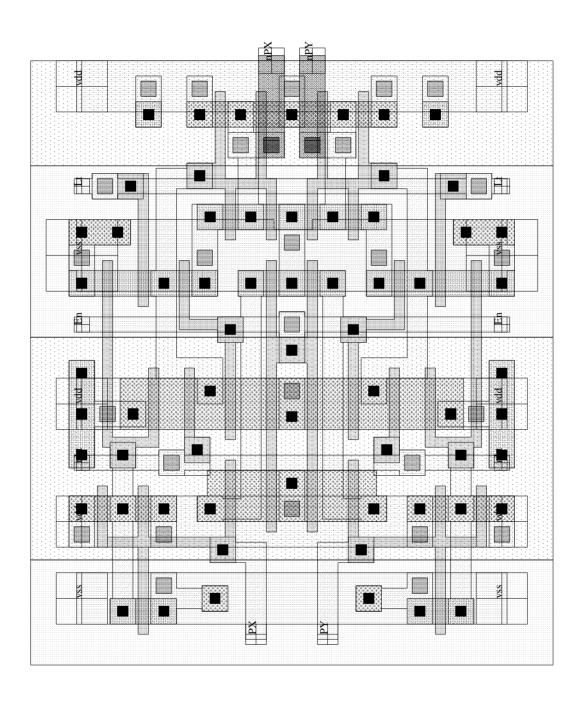

| 7-3 | AMULET3 organisation            | 153 |

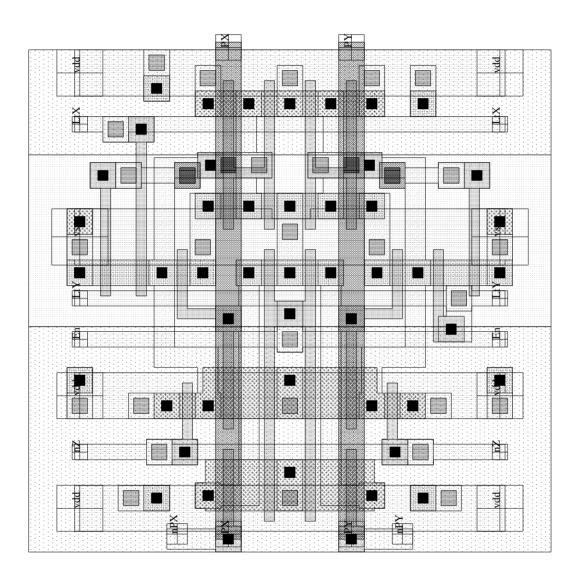

| 7-4 | Execution pipeline organization | 154 |

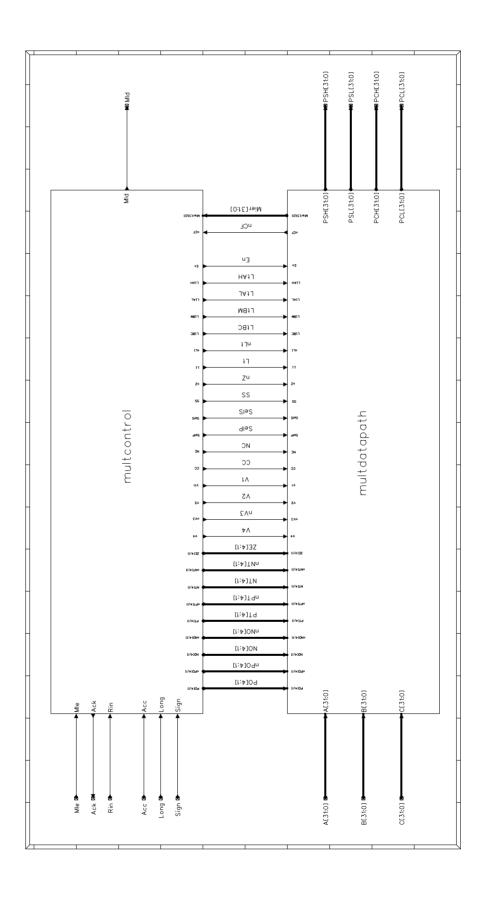

| 7-5 | AMULET3 datapath structure      | 155 |

# **List of Tables**

| 2-1 | Characteristics of AMULET1                                   | 37  |

|-----|--------------------------------------------------------------|-----|

| 2-2 | Characteristics of AMULET2e                                  | 38  |

| 3-1 | Carry request                                                | 40  |

| 3-2 | Two-way carry requests                                       | 41  |

| 3-3 | Dual-rail code                                               | 42  |

| 3-4 | (g, p) carry requests                                        | 43  |

| 3-5 | The Brent and Kung carry code                                | 44  |

| 3-6 | Three-way carry requests                                     | 45  |

| 3-7 | Simulation results of the three-way carry arbiter            | 61  |

| 4-1 | Modified Booth algorithm                                     | 72  |

| 4-2 | Simulation results on the Booth mux cell                     | 83  |

| 4-3 | Truth table for 4-2 Counters                                 | 85  |

| 4-4 | Simulation results on the 4-2 Counter with enable control    | 88  |

| 4-5 | Simulation results on the 4-2 Counter without enable control | 88  |

| 4-6 | Simulation results on the pipeline register                  | 90  |

| 4-7 | Simulation results on the partial product register           | 91  |

| 5-1 | HSPICE simulation results                                    | 117 |

## **Abstract**

This thesis describes arithmetic components (an adder and a multiplier) and control components which have been designed and implemented for AMULET3i, a commercial asynchronous embedded system chip incorporating the third generation asynchronous ARM processor (AMULET3).

A novel carry arbitration scheme is proposed (and has been patented) for parallel adder circuits. This new scheme provides an efficient encoding in which the carry is generated by arbitrating several input carry requests, exploiting the associativity of the carry computation. Post-layout simulation, in a 0.35 micron triple metal CMOS technology, shows that the adder for AMULET3i takes 1.8 ns to complete the computation of a 32-bit addition.

The multiplier design uses the modified Booth's algorithm integrated with a new encoding technique for adjusting the product result of an unsigned number multiplication. An adjustment value is made on the least significant 32-bit positions. Post-layout simulation, in a 0.35 micron triple metal CMOS technology, shows that the multiplier for AMULET3i takes 11.2 ns (2.8 ns × 4 cycles) to complete the computation of a 32-bit long multiplication in the worst case.

Organizing these arithmetic components efficiently into a four-phase asynchronous pipeline is investigated and a set of speed-independent latch control circuits is then proposed. Additionally, a set of control modules for four-phase micropipelines is presented. These two sets of control components can be used to construct complex and powerful asynchronous systems.

# **Declaration**

No portion of the work referred to in the thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institution of learning.

# Copyright and the Ownership of Intellectual Property Rights

- (1) Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

- (2) The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of Department of Computer Science.

## The Author

The author was awarded the degrees of B.Sc and M.Sc, both in Electrical and Electronic Engineering, at Shenyang Institute of Technology and Harbin Institute of Technology, China, in 1984 and 1987, respectively. Significant experience was gained from involvement in 16-bit and 32-bit microprocessor, FPGA and ASIC chip designs at the Northeast Microelectronics Institute, China, from 1987 to 1993. He became interested in asynchronous design, VHDL design and formal approaches to hardware design when at the Technical University of Denmark, as a visiting scholar, from 1993 to 1994. He obtained an M.Sc degree in Computer Science from the University of Manchester in 1995. This thesis reports the results of the work undertaken during the AMULET project at the Computer Science Department of the University of Manchester.

# Acknowledgements

First and foremost, I am grateful to my supervisor, Steve Furber, who has been an invaluable source of inspiration and continuous support in every aspect of this work. I could not hope for a better supervisor.

During my PhD study, I have also been with the Cogency Technology, Inc., as a VLSI design engineer. Thanks are due to Nigel Paver, Paul Day, Craig Farnsworth, Dave Jackson and Warren Lien for their support. Again, special thanks go to Nigel Paver for his commenting on the thesis structure and continuous support.

Thanks are due also to my adviser, Doug Edwards, for his encouragement and support, and to Steve Temple, Jim Garside, Dave Gilbert, Phil Endecott, Oleg Petlin and Julian Skidmore for their kind help. Thanks also to David Lloyd for his commenting on a draft of this thesis, to John Bainbridge and Suck-Heui Chung for discussions on the PETRIFY tool, and to Sun-Yen Tan for interesting conversations in Chinese. The other members of the AMULET group are acknowledged for their contributions at the regular Monday afternoon meetings.

I would also like to acknowledge with gratitude the grants from ORS and URS.

Last, but not least, I owe much gratitude to Jørgen Staunstrup, who brought me into the world of asynchronous design when I stayed at the Technical University of Denmark as a visiting scholar from 1993 to 1994.

# **Dedication**

To

My parents — Pengqi Liu and Shuhua Zhang

My wife — Li He

And my sons — Dan Liu and Ying Liu

# 献给:

我的父母 -- 刘鹏起 和 张淑华

我的妻子 -- 何莉

我的儿子 -- 刘丹 和 刘英

Introduction

The real world is asynchronous by nature. It is, thus, logical to build digital systems in an asynchronous way, exploiting the potential advantages of this inherent property of asynchrony to their fullest. However, synchronous design styles have been preferred and have dominated digital systems for the last three decades. This is not surprising for two reasons. Firstly, synchronous design is easier to understand and easier to implement, which are attractive characteristics. Secondly, asynchronous design was usually considered less disciplined and more anarchic, which frightens most designers away.

With the rapid development of synchronous digital systems, however, there is evidence that we are beginning to hit some of the fundamental limitations of synchrony. It is becoming ever more difficult to establish global synchrony within today's chips, let alone from chip to chip. It is becoming unacceptable for global synchrony to burn increasing power, especially for power-sensitive applications where short battery life is the bane of the users. It is becoming a huge task for a digital system to be maintained and for its components to be replaced or reused. High noise emission and Electro-Magnetic Interference (EMI) are also increasingly becoming concerns in mobile communication applications.

Asynchronous design [1] has made a come-back in recent years, showing a number of advantages [2,3] over synchronous design. There are no clock related problems because global synchrony has been removed. Performance can be better as it is based on the average case rather than the worst case. Power consumption can be lower since power is only consumed when needed. Large digital systems can easily be maintained due to the high modularity and composability as each block can be designed without knowledge of the timing characteristics of any of the other blocks. Also, the low noise emission and good Electro-Magnetic Compatibility (EMC) of asynchronous systems are of potential use in mobile communication applications since increasingly rigorous EMI compliance specifications and testing can be more easily satisfied.

With asynchronous design becoming widely recognized after a world-wide resurgence of interest, it seems that it is expanding beyond its initial area of interest (which was primarily in academic research) into industry. However, there is still confusion surrounding the claimed advantages as there are very few demonstrable chips available to assess and therefore to endorse the asynchronous design methodology. The outcomes for most claims are still to be answered, though some are obvious.

The AMULET (Asynchronous Microprocessor Using Low Energy Techniques) group was established late in 1990, led by Professor Steve Furber, to investigate the claimed advantages and the feasibility of designing large asynchronous systems. The objective is to realize asynchronous microprocessors with lower power consumption and higher performance than is currently available using synchronous design techniques. Rather than adding to the theoretical work, an engineering approach was adopted and this has contributed to the growing pool of asynchronous knowledge during the last seven years.

The first milestone was AMULET1 [4-8] in 1994, an asynchronous implementation of the ARM 32-bit RISC microprocessor [9,10]. It demonstrated the feasibility of building an asynchronous system at the levels of complexity of current synchronous digital systems with the resources and tools readily available to synchronous designers.

The second milestone was AMULET2e [11] in 1996, an asynchronous embedded system chip which includes a significantly enhanced version of AMULET1. Its performance and power efficiency are competitive with the industry leading synchronous ARM designs. The AMULET2e work established a path to the commercial exploitation of asynchronous design.

AMULET3i, a commercial asynchronous embedded system chip for communication applications, is currently under development. This will be a significant milestone: the first fully asynchronous embedded system going into a commercially viable product.

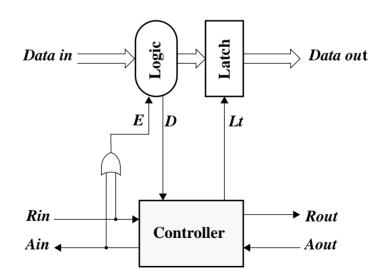

The main objective of the work described in this thesis is to design high performance and low power arithmetic components (an adder and a multiplier) and control components for AMULET3i. An adder and a multiplier have been designed and implemented down to the layout level; these are two basic arithmetic blocks which are critical to the performance of the processor core. A set of control components for four-phase micropipelines, namely the pipeline latch control circuits, have been proposed, which can be used to organize arithmetic components efficiently into a micropipeline. Additionally, another set of control components, namely four-phase control modules, is also presented as basic building blocks. These two set of control components can be used to construct complex and powerful asynchronous systems.

#### Thesis overview

Due to the engineering nature of my PhD work, there is considerable detail which could easily blur the picture of the basic ideas. Instead, only the key ideas and relevant information are given here. Some engineering detail can be found in the circuit schematics and layout, presented in the appendices. Background information for asynchronous design is provided in chapter 2. The body of the work is divided into two main parts. The first part includes the arithmetic components, the AMULET3i adder in chapter 3 and the AMULET3i multiplier in chapter 4. The other part deals with the control components, a set of four-phase micropipeline latch control circuits in chapter 5 and a set of four-phase control modules in chapter 6. Each chapter is self-contained.

Addition is one of the most important arithmetic operations performed frequently within both general purpose and digital signal processing systems and an adder is therefore an important arithmetic component. A novel carry arbitration scheme is proposed (and has been patented [12]) for parallel adder circuits in chapter 3. This scheme provides an efficient encoding in which the carry is generated by arbitrating several input carry requests, exploiting the associativity of the carry computation. The new coding is a logically redundant superset of the conventional carry process. Departing from this general coding, certain modifications which reduce the redundancy can easily be made where this simplifies the implementation. The proposed carry arbitration scheme not only leads to high speed adders due to the reduction in the required layers of logic, but also offers a regular and compact layout and uniform fan-in and fan-out loadings. To demonstrate the feasibility and effectiveness of the new scheme, a 32-bit adder for AMULET3i has been designed and implemented down to the layout level.

Multiplication is another of the most common arithmetic operations. In chapter 4, the multiplier design for AMULET3i is presented, in which attention is focused on CMOS circuit design techniques. The AMULET3i multiplier can process two classes of multiply instructions: a normal 32-bit result and a long 64-bit result; both types of multiply instruction can also optionally perform an accumulate operation. A new encoding technique has been employed to adjust the final result of an unsigned number multiply operation. The design uses the modified Booth's algorithm [13,14] and eight bits are scanned at a time. A new 4-2 Counter with an enable control has been proposed. High speed circuit design techniques including the "true single-phase clocking registers" [15] are used. Some of this chapter is based on previous work by the author described in his M.Sc thesis [16].

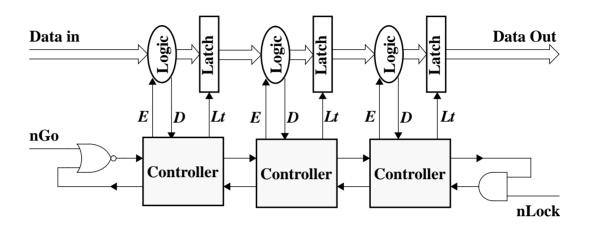

As the four-phase micropipeline design style [17-19] was adopted for AMULET3i, the design of arithmetic components, the adder and the multiplier, are similar to clocked designs in some ways. However there are some subtle differences between the two; this is obvious in the multiplier design where the asynchronous nature has been exploited. The fundamental difference lies in the control mechanisms, which are described in chapter 5 and chapter 6.

The AMULET designs are based on Sutherland's micropipelines [20]. Although micropipelines were originally conceived with two-phase control, most recent work uses four-phase control mainly for performance reasons. The change from two-phase control to four-phase control leaves many choices open regarding the organization of the asynchronous pipelines. Chapter 5 explores these control schemes for asynchronous pipelines and presents a set of pipeline latch control circuits. All of the proposed pipeline

latch control circuits are speed-independent, which is verified using the FORCAGE tool [21]. Low power considerations and the use of dynamic logic are also discussed in this chapter.

To ease the design of asynchronous systems based on four-phase micropipelines, a set of basic control modules is required. Such a set is proposed in chapter 6. Arbiters, which are non-trivial and tricky to implement, are also included. The specifications of these four-phase control modules are carried out using Petri Nets [22]. These basic control modules, together with the pipeline latch control circuits, can construct complex and powerful asynchronous systems including forking or joining multiple pipelines. All of the proposed control modules are speed-independent, which is verified using the PETRIFY tool [23-26].

A brief description of AMULET3i is given in chapter 7 in the hope of providing the big picture into which the components described in the previous chapters can be placed.

Conclusions are finally made in chapter 8.

## **Contributions**

The main contributions made in this thesis are:

In chapter 3, a high performance, low power asynchronous 32-bit adder for AMULET3i has been designed and implemented down to the layout level. The design uses a novel carry arbitration scheme (which has been patented) exploiting the associativity of the carry computation.

| In chapter 4, a high performance, low power asynchronous 32-bit multiplier for        |

|---------------------------------------------------------------------------------------|

| AMULET3i has been designed and implemented down to the layout level. The design       |

| employs the modified Booth's algorithm integrated with a new encoding technique for   |

| adjusting the product result of an unsigned number multiply operation.                |

|                                                                                       |

| In chapter 5, a set of speed-independent latch control circuits has been proposed     |

| for asynchronous pipelines. These pipeline latch control circuits provide a framework |

| within which arithmetic components can be efficiently organized.                      |

|                                                                                       |

| In chapter 6, a set of speed-independent control modules has been proposed. These     |

| control modules provide basic building blocks which can be used to construct complex  |

| and powerful asynchronous systems.                                                    |

Background

In this chapter, we highlight some aspects of asynchronous design. Asynchronous design here refers to the design of digital circuits which operate correctly without relying on global clocks for synchronization. It is not possible to offer a comprehensive overview here; instead a brief introduction to the basic concepts is provided. The micropipeline design style and the AMULET project are then overviewed, which are of interest here because they form the background for the rest of the work described in this thesis. A full treatment of other asynchronous design styles can be founded elsewhere [2,3].

### 2.1 Introduction

A binary digital circuit uses two distinct values, 0 and 1. This is an ideal model. In reality, there are no true digital circuits, but only analog circuits which approximate to digital behaviours. No matter how *quick* the transitions the digital signals make, there are not only 0's and 1's but also undefined values between 0 and 1. These undefined values, when they occur, may not be recognized or may be interpreted in different ways by a digital circuit. As a result the digital circuit may behave unexpectedly. The period of this time uncertainty of a transition can be interpreted as "delay", and unexpected phenomena in a digital circuit due to the existence of delays are called "hazards'. To

avoid such hazards, we must wait and evaluate digital signals only at well-defined reference points. Generally, digital design methodologies fall into two categories according to how these reference points are defined. The synchronous design methodology uses global clock signals as reference points, whereas the asynchronous design methodology employs the elapse of time or local control signals as reference points.

Historically, most early asynchronous designs used the elapse of time as reference points, based on some *real* delay assumptions on circuit elements or wires. The design process is much the same as synchronous design. It postulates many local clock signals based on the elapse of time between the changes of circuit signals. These postulated local clock signals are used to define reference points, which can be variable and controlled by adjusting delays in circuit elements or wires. Though much effort has been expended during the last three decades on this design approach, there are some fundamental problems that are hard to deal with. As a result, this design style is viewed as less disciplined and more anarchic than synchronous design, and this view has frightened most designers away in the past and still generates an adverse reaction.

However, most current asynchronous designs have abandoned the old ad hoc method based on *real* delay assumptions on circuit elements or wires. Instead, they use unbounded delay assumptions, which means a circuit always operates correctly under any distribution of circuit element delays or wire delays. Though this seems very pessimistic, it resolves all the delay-related problems that would otherwise arise. At the same time, the performance of a circuit is not compromised and even may be improved since concurrent operations can easily be exploited. Another benefit is that the circuit

correctness issue is separated from delays and as a result circuit verification becomes easy, which is increasingly important for a complex system. Current asynchronous design is very systematic and well disciplined.

## 2.2 Basic concepts

A few key concepts and a taxonomy of asynchronous design are introduced and defined informally here; these are fundamental to the understanding of asynchronous design. Formal definitions are beyond the scope of this thesis and can be found elsewhere.

#### 2.2.1 Delay models

The <u>bounded delay</u> model assumes that there is an upper bound on the delay of a circuit element or a wire.

The <u>unbounded delay</u> model assumes that there is no upper bound on the delay of a circuit element or a wire.

#### 2.2.2 Circuit classification

<u>Timed circuits</u> are circuits whose correct operation is dependent on the delays in circuit elements and wires.

<u>Speed-independent circuits</u> are circuits whose correct operation is independent of the delays in circuit elements, and wire delays are assumed to be zero.

<u>Delay-insensitive circuits</u> are circuits whose correct operation is independent of the delays in both circuit elements and wires.

*Quasi-delay-insensitive circuits* are delay-insensitive circuits augmented with isochronic forks.

(*Isochronic forks* are sets of interconnecting wires where the delay difference between the branches is zero or negligible compared to the circuit element delays.)

#### 2.2.3 Hazards and races

A <u>static hazard</u> is a single transition of a signal which should remain constant.

A <u>dynamic hazard</u> is a multiple transition of a signal which should change only once.

A *function hazard* is inherent in the specification of the logic function.

A <u>logic hazard</u> depends on the particular implementation of the logic function.

An *essential hazard* is inherent in the specification of the finite state machine.

A <u>non-essential hazard</u> (also called a <u>race</u>) depends on the particular state encoding.

A noncritical race is where all transient states settle to the same final state.

A *critical race* is where different transient states may lead to the different final states.

#### 2.2.4 Metastability and arbitration

The *metastability* problem [27] is the phenomenon of the unusually long delay in the logic decision time between two values 0 and 1 for bistable systems such as flip-flops. When two asynchronous inputs to a bistable system arrive at very nearly the same time, a discrete decision must be made from a continuous range of input possibilities. It is fundamentally impossible to make this decision reliably within a bounded time. The delay may theoretically be an indefinite amount of time [28-30]. *Arbitration* is the mechanisms whereby a bistable system responds to either one input or the other.

Though metastability is an inevitable problem, the resulting metastable states can be resolved internally to maintain valid logic levels at the circuit interface using analog circuit techniques. The *mutual exclusion circuit* (MUTEX) [31] has this property and is used for making a non-deterministic decision between asynchronous calling requests.

It is worth noting here that the probability of failure of synchronous designs can never be zero and it must be accepted that whenever an asynchronous signal is input there is some chance of failure, though the probability can be made small with careful design techniques. However, this is not the case in asynchronous designs; an asynchronous circuit can be designed always to operate correctly, though it will require an unbounded time to resolve in the worst case.

#### 2.2.5 Circuit specifications

Generally speaking, there are two broad classes of asynchronous design specification styles: state-based and event-based approaches.

Asynchronous finite state specifications are Huffman state machines [32,33] or extended Huffman state machines such as Burst Mode state machine [34,35]. Huf fman circuits operate in fundamental mode, which assumes that only one input can change at a time, and succeeding input changes must not occur until the entire circuit settles into be a stable state. Relaxing the condition of only one input change in fundamental mode, burst-mode circuits allow multiple input changes as a burst. Another operation mode is called the input/output mode [36], which assumes that further external input changes can be applied as soon as the expected outputs have responded the current inputs. Total state specifications [37,38] are referred to as Muller state graphs, from which the semantics of

event-based models are derived. <u>Trace theory</u> [39,40] is an abstract and formal description of a Muller state graph.

<u>Event specifications</u> are referred to as Petri Net [22] specifications, and include I-nets [41], Signal Transition Graphs (STG) [42,43], and Change Diagrams (CD) [21,44]. <u>Petri Net</u> specifications are a mathematical formalism to describe the behaviour of systems with concurrency, causality and conflicts between events.

<u>I-nets</u> are restricted Petri Nets in which interface signal names are assigned to transitions. <u>Signal Transition Graphs</u> are interpreted Petri Nets whose transitions are labelled as signal value changes. Similar to STGs, <u>Change diagrams</u> are interpreted Petri Nets, but allow OR-type signal transitions and disengageable arcs for nonrepeating signal transitions.

#### 2.2.6 Signalling protocols

A <u>handshake</u> is a procedure where one signal (the request signal) makes a transition and a second signal (the acknowledge signal) makes a transition as a response.

<u>Links</u> are sets of request and acknowledgement wires used for communications through handshaking between different blocks.

The <u>two-phase</u> [20] protocol uses one handshake along a link for one transaction between two blocks. As a result, rising and falling signal transitions are equivalent,

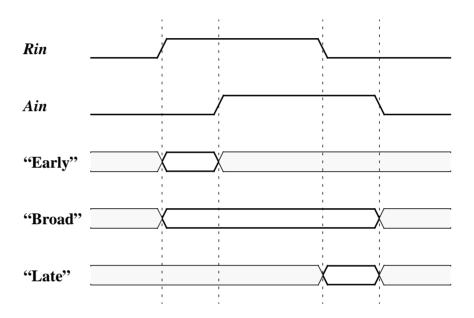

The <u>four-phase</u> [17-19] protocol uses two handshakes along a link for one transaction between two blocks. There are variant schemes (see chapter 5) based on this protocol.

#### 2.2.7 Data representation

<u>Bundled data</u> [20] comprises a set of data wires and an associated control signal that indicates the validity of the data. The data wires and the control wire are constructed such that stable data are available at the receiver before the control signal makes an indication of valid data. The relationship between the data and control delays required to ensure correct operation is referred to as the <u>bundling constraint</u>.

<u>Coded data</u> systems hide timing information in the data itself. There are many ways to encode data [45]. One well-known method is the <u>dual-rail</u> code [46] that requires two wires to encode a single bit of data. A transition can occur on either one wire or the other and not on both wires.

#### 2.2.8 Synthesis

The type of specification usually determines the style of synthesis which can be used to generate the asynchronous circuit. State-based and event-based specifications have corresponding synthesis approaches: state-based and event-based synthesis. These two synthesis approaches are often used to design controllable asynchronous modules. Once a set of asynchronous modules is at hand, large asynchronous systems can be built up from these modules. Syntax directed program translations for specifications using CSP like programming languages [47] such as Tangram [48] are examples of this approach to building circuits from a library of modules. Although state-based or event-based design techniques can be applied directly to large asynchronous systems, they have not been very successful and practical for VLSI applications. Note that some designs are combinations of state-based and event-based design approaches.

## 2.3 Sutherland's micropipelines

Micropipelines were introduced by Ivan Sutherland in his 1988 Turing Award lecture [20], and are a framework for building asynchronous pipelines. Micropipelines are composed of a bounded delay datapath operated by an unbounded delay two-phase control circuit.

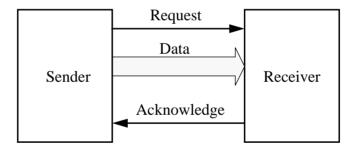

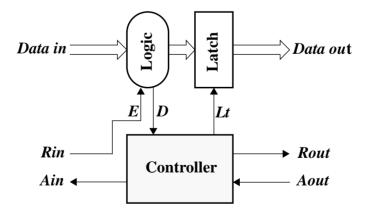

Data passes on a bus from sender to receiver and is associated with a *Request* wire indicating when the data is valid. There is an *Acknowledge* wire from the receiver to the sender which indicates whether the data has been received. (see figure 2-1). The data wires and the request signalling wire must be treated as a bundle; the data must reach the receiver prior to the request event. Rising and falling transitions of request and acknowledge wires are equivalent, carrying the same information.

Figure 2-1: A bundled data interface

#### 2.3.1 Event control modules

Figure 2-2 illustrates a basic set of event control blocks proposed by Sutherland which can be "programmed" to build complex and powerful asynchronous systems. These basic building blocks were designed using I-nets [41].

Figure 2-2: Micropipeline event logic modules

The **XOR** gate acts as the OR function for events. A transition on either input results in a transition on its output. For correct operation events must not arrive simultaneously on both inputs. XOR modules are often called **MERGE** elements because they merge two event streams into one.

The **Muller C-gate** acts as the AND function for events. A transition will occur at the output only when there have been transitions at both of the inputs. Muller C-gates are often called **RENDEZVOUS** elements because they make events at the output wait until events have been received on both inputs.

The **TOGGLE** module steers incoming events to its outputs alternately; the first event to arrive is issued to the output marked with a dot, the second to the unmarked output, and so on.

The **SELECT** module steers incoming events to one of two outputs according to the Boolean value of its diamond input. The Boolean value must be set up before the incoming event that it steers, a requirement similar to the bundling constraint.

The **CALL** module allows two processes to share a common resource, similar to a procedure call in software. The calling processes must be mutually exclusive; if they are not, they must access the call block through an arbiter.

The **ARBITER** module is used to control the interaction between two asynchronous event streams. As the two streams can issue requests at any time, the arbitration logic is inherently prone to metastability. The metastable states must be resolved internally to maintain valid logic levels at the interface of the module.

#### 2.3.2 Event-controlled storage element

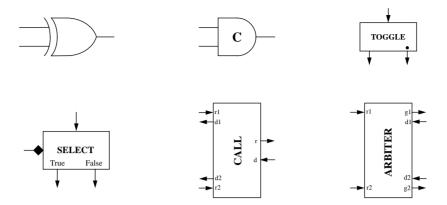

Event-controlled storage elements are needed to build a complete micropipeline circuit. Figure 2-3 shows an implementation of an event-controlled storage element and the symbol used to denote it.

Figure 2-3: Event-controlled storage element

The input is initially connected to the output; it is transparent when empty and does not behave as a storage element at all. An event on the "capture" wire flips the two switches, and as a result a loop is formed containing two inverters, causing the data to be latched. This loop is still connected to the output, which therefore carries the previously latched

value and does not follow subsequent input changes. An event on the "capture done" wire is issued after the switches have flipped. An event on the "pass" wire flips the other switch and as a result the element is returned to the transparent state and ready for the next coming transaction. Similarly, an event on the "pass done" wire is issued after the switch has flipped.

#### 2.3.3 Micropipeline FIFO

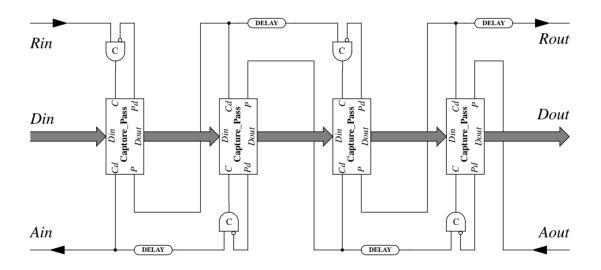

A micropipeline with no processing in it, which is simply a FIFO, can be built as shown in figure 2-4. A data value can be entered into the FIFO from the left by signalling an event on the *Rin* wire, whereupon it will ripple down the FIFO and eventually will be fed out through the wire *Rout*.

Figure 2-4: Micropipeline FIFO

One of the elegant features of a micropipeline FIFO is its elasticity. Data can be inserted into or removed from a FIFO at any rate bounded from zero to a maximum defined by the throughput parameter. The maximum insertion rate at the input end and the

maximum removal rate at the output end can be achieved at the same time. However, in this condition, the percentage occupancy of the FIFO remains unchanged, and is determined by how fast the request signal passes forward and the acknowledge signal returns backward. If the request signal and acknowledge signal travel at the same rate, which is the most common case for a micropipeline FIFO, the percentage occupancy is only 50%.

Therefore, if we want to sustain high throughput for a long time, more FIFO stages should be used than might be expected. This is why an asynchronous micropipeline FIFO is often deeper than its synchronous counterpart for the same application.

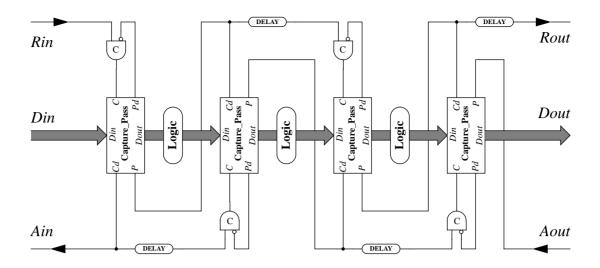

#### 2.3.4 Micropipelines with processing

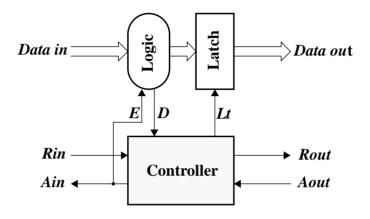

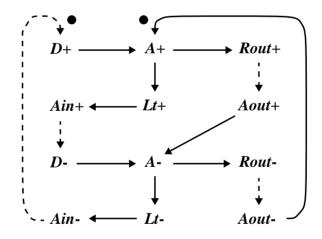

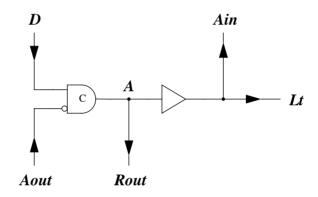

The simple micropipeline FIFO can be extended to interpose processing logic between micropipeline FIFO stages, as shown in figure 2-5. The operation of this micropipeline with processing operates in a similar manner to the micropipeline FIFOs. The delay in the request event path must match the logic processing delay in order to preserve the data bundling convention.

More complex structures including forking and merging multiple pipelines can be built with the aid of other event control modules.

## 2.4 The AMULET project

It is our belief that asynchronous designs should be justified not only on a theoretical significance but also by their practical implications. This is also the motivation behind the AMULET project.

Figure 2-5: Basic micropipeline structure

#### 2.4.1 AMULET1 chip

In 1994 Professor Steve Furber's AMULET group at the University of Manchester took delivery of the AMULET1 processor, the first asynchronous implementation of a commercial processor architecture. The AMULET1 chips are code compatible with the ARM 32-bit RISC processor.

The design used the two-phase micropipeline style and includes several novel features such as the register locking mechanism [49], the instruction prefetching with its "colour" management of non-determinism and the data dependent ALU operations [50]. The chips were fabricated on two CMOS processes: a 1  $\mu$ m process at ES2 and a 0.7  $\mu$ m process at GEC Plessey Semiconductors.

Table 2-1 shows a summary of the characteristics of the AMULET1 chips with those of ARM6 for comparison. The chips demonstrate robustness to variations in temperature and voltage supply. The AMULET1 chip demonstrated the feasibility of building an

asynchronous digital system at the levels of complexity of current synchronous digital systems.

**Table 2-1: Characteristics of AMULET1 [4]**

|                         | AMULET1 (a)   | AMULET1 (b)      | ARM6             |

|-------------------------|---------------|------------------|------------------|

| Process                 | 1 μm          | 0.7 μm           | 1 μm             |

| Area (mm <sup>2</sup> ) | 5.5 × 4.1     | $3.9 \times 2.9$ | $4.1 \times 2.7$ |

| Transistors             | 58,374        | 58,374           | 33,494           |

| Performance             | 20.5 kDhry.   | 40 kDhry.        | 31 kDhry         |

| Power                   | 152 mW        | N/A              | 148 mW           |

| MIPS/W                  | 77            | N/A              | 120              |

| Conditions              | 5 volt, 20 °C | 5 volt, 20 °C    | 5 volt, 20 MHz   |

### 2.4.2 AMULET2e chip

Two years later, the AMULET group took delivery of the AMULET2e embedded system chip. AMULET2e is aimed at the embedded control market, and includes AMULET2 (a significantly enhanced version of AMULET1), 4 Kbytes of RAM which can also be configured to operate as a cache, a counter-timer for real-time reference, a flexible memory interface and various configuration and control registers. The design includes several novel features such as the load and register forwarding, branch target prediction, and the "halt" mode. The design uses the four-phase micropipeline design style. The chips were fabricated in a 0.5 µm triple metal CMOS technology.

Table 2-2 shows a summary of the characteristics of AMULET2e with those of ARM710 and ARM810 for comparison. AMULET2e is the first asynchronous processor whose performance and power-efficiency are competitive with the industry-leading clocked

ARM designs. One remarkable feature of AMULET2e is that the power consumption drops to nearly zero with the "halt" function enabled.

Table 2-2: Characteristics of AMULET2e [11]

|                         | ARM710           | AMULET2e        | ARM810           |

|-------------------------|------------------|-----------------|------------------|

| Process                 | 0.6 μm 2LM       | 0.5 μm 3LM      | 0.5 μm 3LM       |

| Area (mm <sup>2</sup> ) | 32               | 41              | 76               |

| Transistors             | 570,295          | 454,000         | 836,022          |

| Cache                   | 8 K 4-way        | 4K 64-way       | 8K 64-way        |

| MIPS                    | 23               | 40              | 86               |

| Power                   | 120 mW           | 150 mW          | 500 mW           |

| MIPS/W                  | 192              | 250             | 172              |

| Conditions              | 3.3 volt, 25 MHz | 3.3 volt, 20 °C | 3.3 volt, 72 MHz |

#### **2.4.3 AMULET3**i

AMULET3i, an asynchronous embedded system chip which incorporates the third generation asynchronous ARM processor (AMULET3), is currently under development. Different from its predecessors, AMULET1 and AMULET2e, AMULET3i is aimed to be a commercially viable product for communication applications. This will be a significant step (see chapter 7).

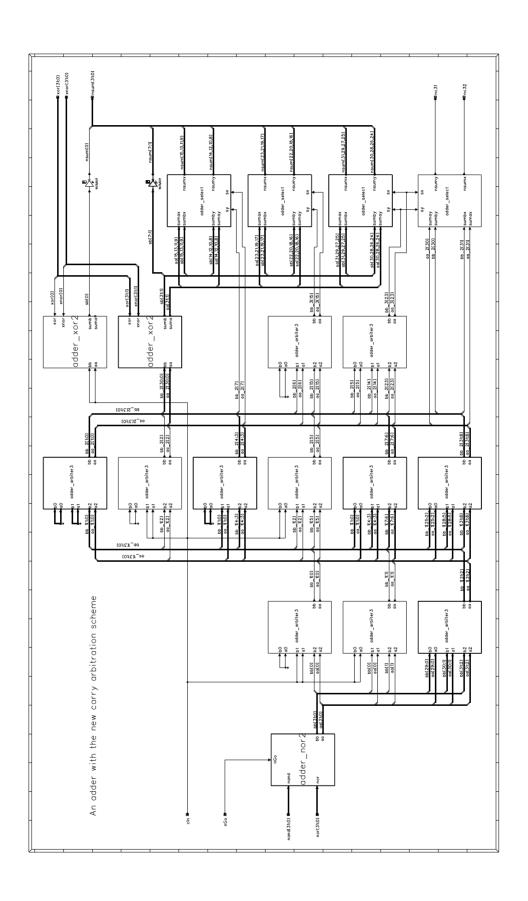

Adder design 3

In this chapter a novel carry arbitration scheme is proposed (and has been patented) for parallel adder circuits. The proposed scheme provides an efficient encoding in which the carry is generated by arbitrating several input carry requests, exploiting the associativity of the carry computation. The new scheme not only leads to high speed adders due to a reduction in the required layers of logic, but also offers a regular and compact layout and uniform fan-in and fan-out loadings. To demonstrate the feasibility and effectiveness of the proposed scheme, a 32-bit adder for AMULET3i has been designed. Post-layout simulation, in a 0.35 micron triple metal CMOS technology, shows that it takes 1.8 ns to complete the computation of a 32-bit addition.

### 3.1 Introduction

Addition is one of the most important arithmetic operations performed frequently within both general purpose and digital signal processing systems. A problem with designing high speed adder circuits is that the most significant bits of the result are logically and physically dependent upon the carry output values from the least significant bits. The consequence of this sequential dependency is that addition operations tend to be relatively slow. This has been widely recognized, and adder design has been studied

extensively for decades. Generally, the basis of adder designs is still either carry generation and carry propagation [51-55] or carry selection based on all possible results being available [56,57]. In recent years carry free additions achieved by employing redundant number systems have received considerable attention [58,59]. In an effort to develop adder circuits that are capable of operating at high speed a carry arbitration scheme for parallel adders is proposed. The new scheme provides an efficient encoding in which the carry is generated by arbitrating several input carry requests, exploiting the associativity of the carry computation.

# 3.2 Carry arbitration

The interesting and difficult task in an adder circuit is the computation of the carry bits. For an addition of two 1-bit numbers  $a_i$  and  $b_i$ , the carry  $c_i$  can be evaluated as shown in table 3-1. There are two general cases defined by the values of  $a_i$  and  $b_i$ . The first case, where there is a carry request, arises when both operand bits are equal. A 1-carry request occurs if both inputs are 1, whereas a 0-carry request occurs if both inputs are 0. The second case, where there is no carry request, arises when the operand bits have different values. The letter u indicates there is no carry request. Carry computation is similar to the logic behaviour when connecting wires  $a_i$  and  $b_i$  together. If they have the same value, then the result follows. If they are different, the result is undefined.

Table 3-1: Carry request

| $a_i, b_i$ | $c_i$ |

|------------|-------|

| 0 0        | 0     |

| 11         | 1     |

| 0 1        | u     |

| 10         | u     |

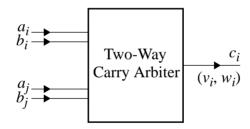

#### 3.2.1 Two-way carry arbiter

One input pair may or may not make a carry request. If two input pairs  $(a_i, b_i)$  and  $(a_j, b_j)$  are considered together, they may issue carry requests at the same time. Therefore, there is a need to arbitrate these two carry requests. Figure 3-1 shows a two-way carry arbiter. The input pair  $(a_i, b_i)$  can make a *non-maskable* carry request, where *non-maskable* means that a carry request from the input pair  $(a_i, b_i)$  must always be granted service to the output  $c_i$ . The input pair  $(a_j, b_j)$  can make *maskable* carry requests, where *maskable* means that a carry request from the input pair  $(a_j, b_j)$  may be masked by the input pair  $(a_i, b_i)$ . Only when there is no non-maskable carry request from the input pair  $(a_i, b_i)$  granted service to the output  $c_i$ . The truth table required to implement two-way carry arbiters is illustrated in table 3-2.

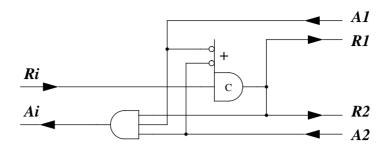

Figure 3-1: Two-way carry arbiter

Table 3-2: Two-way carry requests

| $a_i, b_i$   | $a_j, b_j$   | $c_i$ |

|--------------|--------------|-------|

| 0 0          |              | 0     |

| 11           |              | 1     |

| 0 1 (or 1 0) | 0 0          | 0     |

| 0 1 (or 1 0) | 11           | 1     |

| 0 1 (or 1 0) | 0 1 (or 1 0) | u     |

The output carry  $c_i$  can be encoded using two wires  $(v_i, w_i)$  as shown in table 3-3. Equations EQ-1 and EQ-2 satisfy table 3-2 and table 3-3.

Table 3-3: Dual-rail code

| $c_i$ | $v_i, w_i$   |

|-------|--------------|

| 0     | 0 0          |

| 1     | 11           |

| u     | 0 1 (or 1 0) |

$$v_i = a_i b_i + (a_i + b_i) a_j \tag{EQ-1}$$

$$w_i = a_i b_i + (a_i + b_i) b_i \tag{EQ-2}$$

Figure 3-2 shows a 4-bit carry computation using two-way carry arbiters. The solid dots represent two-way carry arbiters. The carry output values of the high order bits is generated by arbitrating carry requests from their low order bits. High order bit carry requests have priority over low order bit carry requests. For any carry output bits, there must exist a path to every low order input operand bits, which reflects the fact that the carries shall propagate across all the way of the word length of the operands.

Figure 3-2: 4-bit carry computation

The proposed scheme is similar to but different from the scheme proposed by Brent and Kung [52]. Firstly, the computation logic needed for carry generate  $g_i$  and carry propagate  $p_i$  in the Brent and Kung adders is not necessary in our scheme. This leads to a reduction of the required layers of logic and hence high speed carry generation. Secondly, only single-rail signals need to be routed instead of dual-rail signals if the signals  $v_i$  and  $w_i$  are predicted to be equal (which indicates that the carry has been generated, either a 1-carry request or a 0-carry request). This results in a reduction of chip area, especially in the final row of the carry computation where more room is needed to accommodate signals crossing from the least significant bits to the most significant bits. Finally and more importantly, group adders in a carry select adder can be eliminated using the modified implementation of carry arbiters as we will see later.

In fact, the Brent and Kung scheme can be viewed as a special encoding of our scheme as shown in table 3-4. The two signal pairs  $(g_i, p_i)$  and  $(g_j, p_j)$  generated from the input pairs  $(a_i, b_i)$  and  $(a_j, b_j)$  can be seen as new input pairs. The new input pair  $(g_i, p_i)$  issues a 0-carry request when they are both 0, a 1-carry request when  $g_i$  is 1, and no carry request when  $p_i$  is 1. Note that  $g_i$  and  $p_i$  are mutually exclusive. In other words, the case of  $(g_i, p_i)$  with the value (1, 1) is removed by the Brent and Kung encoding.

Table 3-4: (g, p) carry requests

| $g_i, p_i (a_i, b_i)$ | $g_j, p_j(a_j, b_j)$ | $c_i$ |

|-----------------------|----------------------|-------|

| 0 0 (0 0)             | ()                   | 0     |

| 10(11)                | ()                   | 1     |

| 0 1 (0 1 or 1 0)      | 0 0 (0 0)            | 0     |

| 0 1 (0 1 or 1 0)      | 10(11)               | 1     |

| 0 1 (0 1 or 1 0)      | 0 1 (0 1 or 1 0)     | u     |

The carry request output  $c_i$  is encoded here as shown in table 3-5. Equations EQ-3 and EQ-4 give the behaviour defined by table 3-4 and table 3-5.

Table 3-5: The Brent and Kung carry code

| $c_i$ | $v_i, w_i$ |

|-------|------------|

| 0     | 0 0        |

| 1     | 1 1        |

| u     | 0 1        |

$$v_i = g_i + p_i g_j \tag{EQ-3}$$

$$w_i = p_i p_i \tag{EQ-4}$$

Equations EQ-3 and EQ-4 are the key ideas of the well known Brent and Kung adders. It is clear that the computation logic for carry generate  $g_i$  and carry propagate  $p_i$  is wasteful except for understanding how the carries are generated and propagated. By encoding the input pair  $a_i$  and  $b_i$  to the carry generate  $g_i$  and propagate  $p_i$ , the advantage in our scheme of some signals being routed in single-rail form is lost because the dual-rail signals  $g_i$  and  $p_i$  are always required in the Brent and Kung scheme.

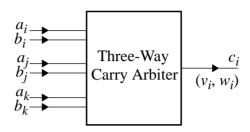

### 3.2.2 Three-way carry arbiter

A three-way carry arbiter is shown in figure 3-3. As before, the input pair  $(a_i, b_i)$  can issue a non-maskable carry request. The input pairs  $(a_j, b_j)$  and  $(a_k, b_k)$  can both make maskable carry requests at any time, possibly at the same time. However, the input pair  $(a_j, b_j)$  has priority over the input pair  $(a_k, b_k)$ . Only when there is no non-maskable carry request from the input pair  $(a_i, b_i)$  is a maskable carry request from the input pair  $(a_j, b_j)$  granted service to the output  $c_j$ . Only when there is no non-maskable carry request from

the input pair  $(a_i, b_i)$  and no maskable carry request from the input pair  $(a_j, b_j)$  is a maskable carry request from the input pair  $(a_k, b_k)$  granted service to the output  $c_i$ .

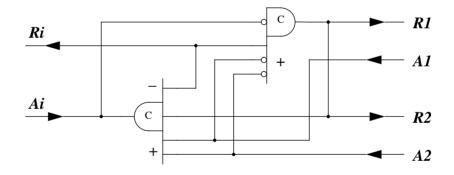

Figure 3-3: Three-way carry arbiter

The truth table required to implement three-way carry arbiters is shown in table 3-6. Equations EQ-5 and EQ-6 give the behaviour defined by table 3-3 and table 3-6.

**Table 3-6: Three-way carry requests**

| $a_i, b_i$   | $a_j, b_j$   | $a_k, b_k$   | $c_i$ |

|--------------|--------------|--------------|-------|

| 0 0          |              |              | 0     |

| 11           |              |              | 1     |

| 0 1 (or 1 0) | 0 0          |              | 0     |

| 0 1 (or 1 0) | 11           |              | 1     |

| 0 1 (or 1 0) | 0 1 (or 1 0) | 0 0          | 0     |

| 0 1 (or 1 0) | 0 1 (or 1 0) | 11           | 1     |

| 0 1 (or 1 0) | 0 1 (or 1 0) | 0 1 (or 1 0) | u     |

$$v_i = a_i b_i + (a_i + b_i)(a_j b_j + (a_j + b_j)a_k)$$

(EQ-5)

$$w_i = a_i b_i + (a_i + b_i)(a_j b_j + (a_j + b_j)b_k)$$

(EQ-6)

Figure 4 shows a 9-bit carry computation using three-way carry arbiters. The addition of an n-bit binary number using three-way carry arbiters can be performed in a time proportional to  $O(log_3n)$ , and therefore is more efficient than using two-way carry

arbiters where the computation time is  $O(log_2n)$ . It is worth noting here that there is a difference in complexity between two-way and three-way carry arbiters, which should be taken into account when comparing them.

Figure 3-4: 9-bit carry computation

The algorithm as shown in the above diagram is very elegant, and follows a very simple rule:

$$t = 3$$

; while  $(c_i = u) \{c_i = c_{i-t}; t = 3t;\}$

Here *t* is the number of input pairs of carry arbiters used, and is three for this case. In the bottom line, the carries are computed just by looking at the three bits and hold either *u* or the correct carries. In the top line, the carry computation covers more bits and reach the point where all of the bit positions have been examined, therefore all of the carries are generated.

#### 3.2.3 Carry arbiters with more than three ways

Using the same approach, carry arbiters with any number of pairs of input signals can be derived. Theoretically, it will be appreciated that a single carry arbitration circuit could

be responsive to n pairs of input signals (n > 3). However, carry arbiters with more than four ways are not usually of practical interest. Firstly, too many series transistors are needed to implement these arbiters, which leads to inefficient CMOS designs. Secondly, the arbiter cell layout can easily become too large for the bit pitch of a datapath.

The circuit which implements a 9-bit carry computation as shown in figure 3-4 can be, in fact, considered as a nine-way carry arbiter, which is built up using three-way carry arbiters.

Now it may be questioned why the new term "carry arbitration" has been introduced to describe a circuit whose function is purely combinational. The introduction of this new term serves to explain the idea, since it is difficult to use the conventional terms "generate", "kill" and "propagate" to describe the new coding.

In a sense, the new coding is a logically-redundant superset of the conventional carry process. Departing from this general coding, certain modifications (which reduce the redundancy) can easily be made where this simplifies the implementation as we will see later in section 3.4.

# 3.3 Parallel prefix computation

In this section the verification of the adder design using the proposed scheme is carried out formally by taking an n-bit addition using two-way carry arbiters as an example. Let  $(a_n, a_{n-1}, ..., a_1)$  and  $(b_n, b_{n-1}, ..., b_1)$  be n-bit binary input operands with output carries  $(c_n, c_{n-1}, ..., c_1)$ , and let  $c_0$  be the initial input carry bit. We define an operator "o" [60] here as follows:

$$(a, b)o(a', b') = (ab + (a + b)b', ab + (a + b)b')$$

Lemma 1: Let

$$(v_i, w_i) = \begin{cases} (c_1, c_1) & \text{if } i = 1 \\ (a_i, b_i) o(v_{i-1}, w_{i-1}) & \text{if } 2 \le i \le n \end{cases}$$

where  $c_1 = a_1 b_1 + (a_1 + b_1) c_0$ .

Then

$$c_i = v_i = w_i$$

for  $i = 1, 2, ..., n$ .

*Proof*: We prove the lemma by induction on i.

It is obvious that the above equation holds true for i = 1.

If

$$i > 1$$

and  $c_{i-1} = v_{i-1} = w_{i-1}$ , then

$$(v_i, w_i) = (a_i, b_i)o(v_{i-1}, w_{i-1})$$

$$= (a_i, b_i)o(c_{i-1}, c_{i-1})$$

$$= (a_ib_i + (a_i + b_i)c_{i-1}, a_ib_i + (a_i + b_i)c_{i-1})$$

$$= (c_i, c_i)$$

Thus, the equation holds true by induction.

Lemma 2: The operator "o" is associative.

Proof: For any three

$$(a_3, b_3)$$

,  $(a_2, b_2)$  and  $(a_1, b_1)$ ,

$$[(a_3, b_3)o(a_2, b_2)]o(a_1, b_1) =$$

$$[(a_3b_3 + (a_3 + b_3)a_2), (a_3b_3 + (a_3 + b_3)b_2)]o(a_1, b_1) =$$

$$(((a_3b_3 + (a_3 + b_3)a_2)(a_3b_3 + (a_3 + b_3)b_2) +$$

$$((a_3b_3 + (a_3 + b_3)a_2) + (a_3b_3 + (a_3 + b_3)b_2))a_1),$$

$$((a_3b_3 + (a_3 + b_3)a_2)(a_3b_3 + (a_3 + b_3)b_2) +$$

$$((a_3b_3 + (a_3 + b_3)a_2) + (a_3b_3 + (a_3 + b_3)b_2))b_1)) =$$

$$(((a_3b_3 + (a_3 + b_3)a_2b_2) + (a_3b_3 + (a_3 + b_3)(a_2 + b_2))a_1),$$

$$((a_3b_3 + (a_3 + b_3)a_2b_2) + (a_3b_3 + (a_3 + b_3)(a_2 + b_2))b_1)) =$$

$$((a_3b_3 + (a_3 + b_3)(a_2b_2 + (a_2 + b_2)a_1)),$$

$$(a_3b_3 + (a_3 + b_3)(a_2b_2 + (a_2 + b_2)b_1)) =$$

$$(a_3, b_3)o(a_2b_2 + (a_2 + b_2)a_1, a_2b_2 + (a_2 + b_2)b_1) =$$

$$(a_3, b_3)o[(a_2, b_2)o(a_1, b_1)]$$

Thus, the operator "o" is associative.

This lemma provides the foundation for using tree structures to generate carries since the signals  $v_i$  and  $w_i$  can be computed in any order from the given input values. This is the key idea for the proposed scheme.

Lemma 3: The operator "o" is not commutative.

This can easily be proved by inspection that  $(1, 1)o(0, 0) \neq (0, 0)o(1, 1)$ . This lemma implies that carry arbitration should perform in a prioritized way.

### 3.4 Implementation

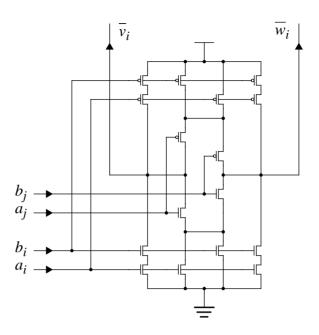

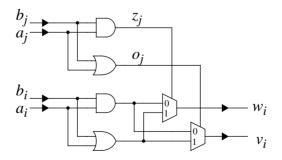

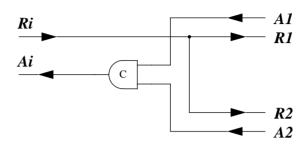

Figure 3-5 shows a static CMOS implementation of a two-way carry arbiter. Note that the outputs  $v_i$  and  $w_i$  are complemented signals. However, the arbiter is quite symmetrical and implementing the next stage in inverse logic is straightforward. The signals through two arbiters are naturally positive true, so no inverters are needed.

Figure 3-6 shows a pass-transistor based implementation of a two-way carry arbiter. This implementation has an additional feature. The output  $v_i$  is zero if and only if the output  $w_i$  is zero, and the output  $w_i$  is one if and only if the output  $v_i$  is one. This provides another view of the arbiter. When the outputs  $v_i$  and  $w_i$  are different this means that there

Figure 3-5: Static implementation of a two-way carry arbiter

are no carry requests from the inputs as described previously. Furthermore we can view the output  $v_i$  as the carry out generated with a one carry-in and the output  $w_i$  as the carry out generated with a zero carry-in. The implementation in figure 3-5 does not distinguish which is the carry out generated with a one carry-in and which with a zero carry-in, since each output can be zero or one independent of the other output. The AND and OR gates in figure 3-6 serve as an input conversion from  $(0\ 1)$  to  $(1\ 0)$ . The signals after these two gates, e.g.,  $(o_j, z_j)$ , take one of the three values  $(0\ 0)$ ,  $(1\ 1)$  and  $(1\ 0)$ .

Figure 3-6: Pass-transistor based implementation

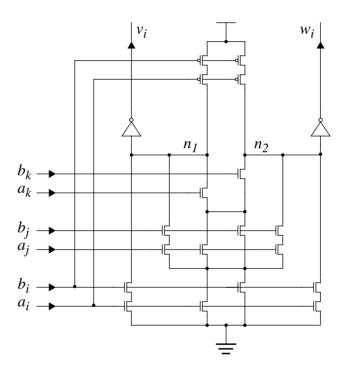

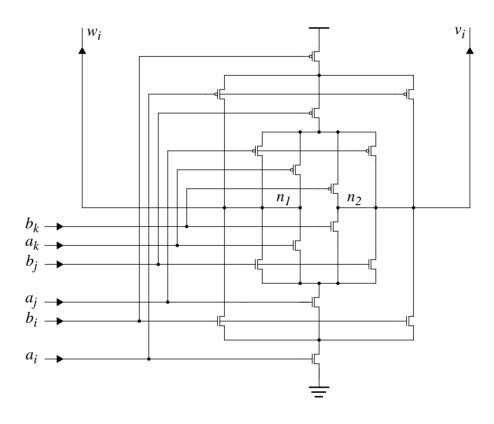

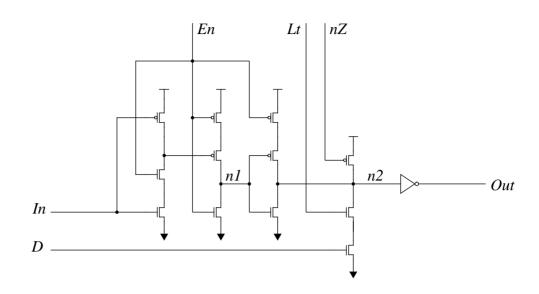

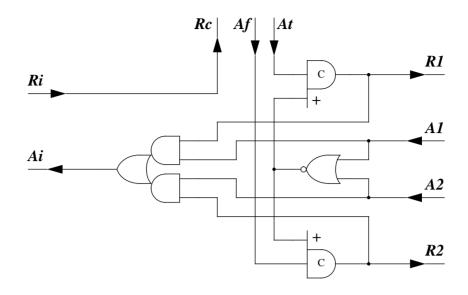

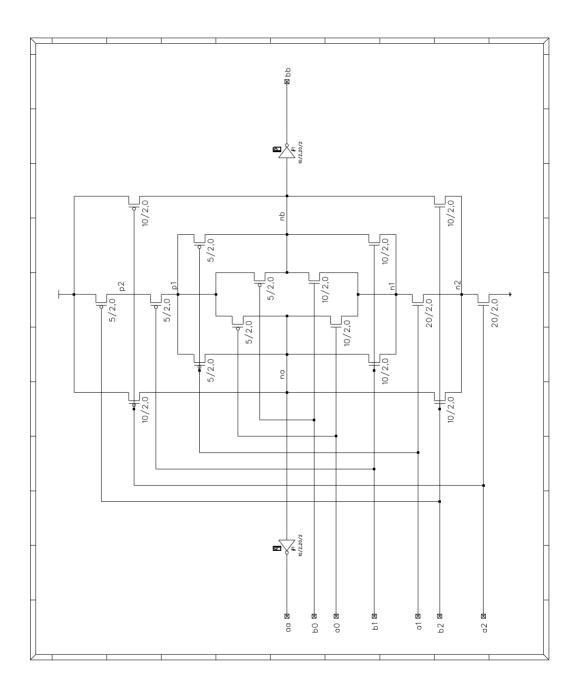

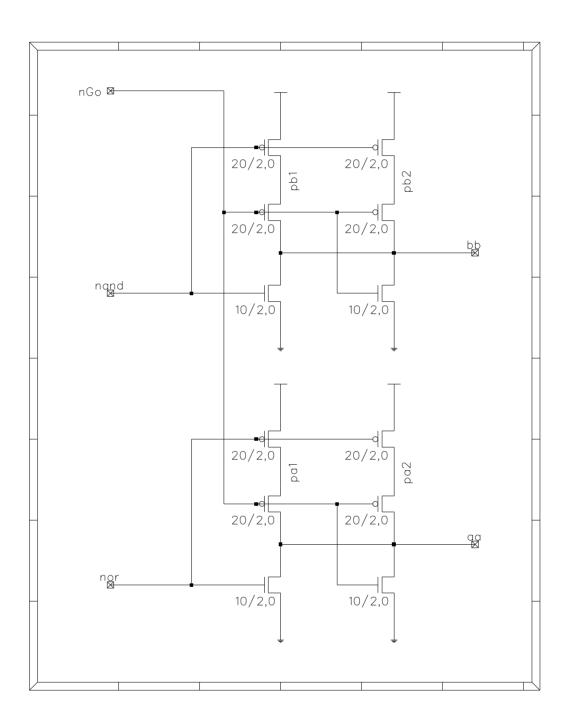

Three-way carry arbiters and four-way carry arbiters may be advantageous if dynamic CMOS techniques are used. Figure 3-7 shows a direct dynamic CMOS implementation [61-63] of a three-way carry arbiter. Instead of using a global precharge control signal, local incoming input signals are used for this purpose. The operation of the circuit is such that the nodes n1 and n2 are precharged high when the inputs  $a_i$  and  $b_i$  are low during the reset phase of the control handshake and will conditionally discharge during the evaluation phase in a self-timed design. The inverters are required for the next stage and also served to maintain proper drive strength.

Figure 3-7: Direct implementation of a three-way carry arbiter

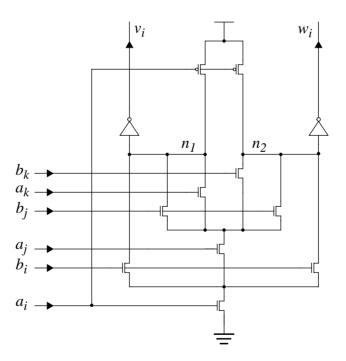

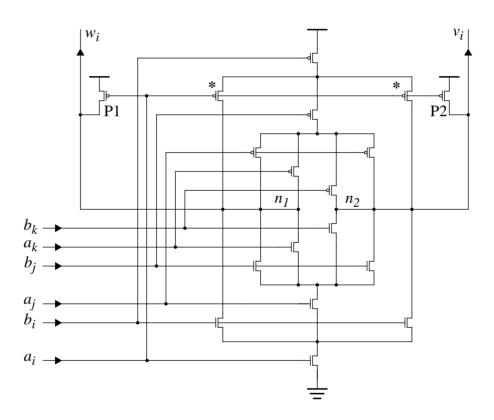

Figure 3-8 gives a modified version of the three-way carry arbiter by reducing the redundancy of the new coding. We assume here that every input pair takes one of the three values (0 0), (1 1) and (1 0), and (0 1) has already been transformed to (1 0) as described previously. The output  $v_i$  is the carry out generated with a one carry-in and the

output  $w_i$  is the carry out generated with a zero carry-in if no carry requests issue from input signals. This results in the elimination of group adders in a carry select adder (see section 3.6) and is the main feature of our scheme.

However, the use of the modified implementation needs the input conversion from (0 1) to (1 0). Fortunately this causes no problem; the conversion is simple. It consists of one 2-input NAND and one 2-input NOR gate per bit. For practical reasons, gates are normally necessary anyway to isolate the signals from the main input buses. The difference here is that NAND and NOR gates are used instead of inverters. If the two input buses are designed using a precharged structure, the outputs from the NAND and NOR gates are naturally low (as required in the dynamic implementation) when the buses are precharged high. Furthermore, these NAND and NOR gates can be reused for logic operations in an ALU design.

Figure 3-8: Modified implementation of a three-way carry

It could be questioned here whether there is a real difference between this new scheme eliminating the value (0 1) compared with the Brent and Kung scheme which does not use the value (1 1). How can we claim that the new arrangement without the formation of generate and propagate terms has an advantage after adding initial NAND and NOR gates? The answer lies in observing that the constraint of not using the value (1 1) is inherent in the Brent and Kung scheme and therefore an initial formation of the generate and propagate terms is required, whereas the constraint of not using the value (0 1) in the modified implementation of the carry arbitration scheme is introduced as an optimization rather than enforced. The optimization leads to the benefit of eliminating group adders in a carry select adder (see section 3.6) and also results directly in a simplified circuit.

### 3.5 Refinement of the Manchester carry chain

One simple application of the new scheme is given in this section, where it is used to refine the Manchester carry chain. In the next section, another application is given, which is to simplify the design of carry select adders.

A wide variety of addition schemes and their implementations are available to serve different performance/cost requirements. One of them is the well known Manchester carry chain [31], which is often found in custom datapaths combined with the carry skip scheme. However a problem with the Manchester carry chain is that too many pass transistors are in series along the carry chain, which degrades the performance especially in CMOS designs with a low supply voltage. To avoid this problem, buffers are usually used to divide the carry chain into several sets of series pass transistors as shown in figure 3-9.

Figure 3-9: Manchester carry chain with buffers

Instead of using buffers to limit the number of pass transistors in series, the carry chain can be rearranged using the part of the circuit in figure 3-6 based on the concept of carry arbitration. Figure 3-10 shows a new carry chain in which the output of one set of series pass transistors is connected to the control gate of the next stage. By so doing, we avoid the series connection of pass transistors without any overhead. It is worth noting that a double pass-transistor logic design style [64] should be used in order to exploit this new carry chain fully.

Figure 3-10: Manchester carry chain without buffers

Obviously, this new implementation of the Manchester carry chain can be derived directly from the truth table without any knowledge of the carry arbitration scheme. The new implementation was found during the development of the carry arbitration scheme.

### 3.6 Simplification of carry select adders

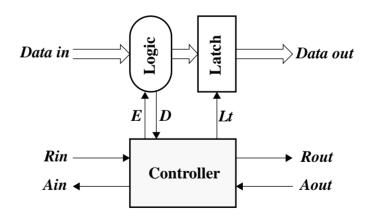

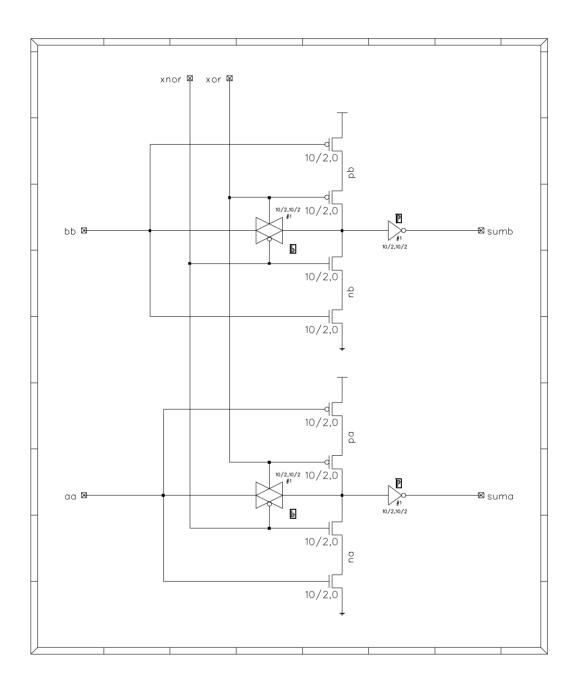

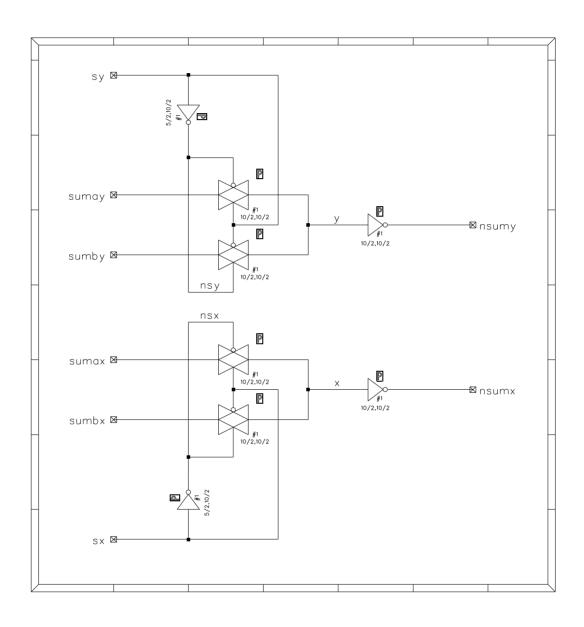

Figure 3-11 shows an adder design using the conventional carry select scheme [57]. The inputs are divided into d-bit (or possibly variable width) groups. Two d-bit adders are needed per group. One is an adder with a zero carry-in and the other with a one carry-in. The carry generator is responsible for generating the boundary carries for all groups, which are then used to select the appropriate sum using a multiplexer.

Figure 3-11: Carry select adder