# Asynchronous Design Aspects of High-Performance Logic

Architectural Modelling of a Bipolar

Asynchronous Microprocessor

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF MASTER OF SCIENCE IN THE FACULTY OF SCIENCE

> Robert Kelly Department of Computer Science 1995

### **Table of Contents**

| Table  | of Contents                                | 2    |

|--------|--------------------------------------------|------|

| List o | f Figures                                  | 5    |

| 1. In  | troduction                                 | 11   |

| 2. As  | ynchronous Logic                           | 14   |

| 2.1    | Delay Modelling                            |      |

| 2.2    | Signalling Protocols                       |      |

| 2.2.1  | Two-Phase Signalling                       |      |

| 2.2.2  | Four-Phase Signalling                      |      |

| 2.2.3  | Data Communications                        |      |

| 2.2.4  | Bundled-Data Interface                     |      |

| 3. M   | icropipelines                              | 25   |

| 3.1    | Control Circuit Elements                   | . 28 |

| 3.1.1  | XOR (Merge)                                | . 28 |

| 3.1.2  | Muller-C (Join)                            | . 28 |

| 3.1.3  | Select                                     | . 29 |

| 3.1.4  | Toggle                                     | . 29 |

| 3.1.5  | Decision-Wait                              | . 30 |

| 3.1.6  | Arbiter                                    | . 30 |

| 3.1.7  | Call                                       | . 31 |

| 3.1.8  | Capture-Pass Latch                         | . 32 |

| 3.2    | Control Circuit Examples                   | . 32 |

| 3.2.1  | Event Register                             | . 32 |

| 3.2.2  | Design Example: PARITY FUNCTION            | . 34 |

| 4. Ve  | erilog HDL                                 | 36   |

| 4.1    | Introduction to HDLs                       | . 36 |

| 4.2    | Introduction to Verilog                    | . 37 |

| 4.3    | Modules                                    | . 37 |

| 4.4    | Structural Modelling                       | . 38 |

| 4.4.1  | Design Example: RS Flip-Flop               | . 39 |

| 4.5    | Behavioural Modelling                      | . 40 |

| 4.5.1  | Compound Statements                        | 41   |

| 4.5.2  | Process Control                            | . 42 |

| 4.5.3  | Timing Control                             | . 42 |

| 4.5.4  | Design Example: Behavioural Representation | . 44 |

| 4.5.5  | Programmable Logic Arrays                  | . 45 |

| 4.6    | Verilog Simulator                          | . 46 |

| 5. Multi-Level Differential Current Mode Logic 48 |                                                      |      |  |  |

|---------------------------------------------------|------------------------------------------------------|------|--|--|

| 5.1                                               | Introduction to Logic Families                       | . 48 |  |  |

| 5.2                                               | Multi-Level Differential Current Mode Logic          | . 50 |  |  |

| 6. Ve                                             | erilog Modelling of MDCML                            | 55   |  |  |

| 6.1                                               | Requirement for Accurate Model of System             | . 55 |  |  |

| 6.2                                               | Determination of Electrical Characteristics of MDCML |      |  |  |

| 6.2.1                                             | Output Loading Effects                               | . 58 |  |  |

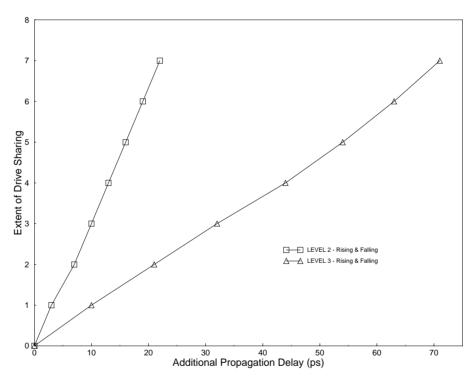

| 6.2.2                                             | Input Drive Effects                                  | . 59 |  |  |

| 6.3                                               | Production of Verilog Model                          | . 61 |  |  |

| 6.3.1                                             | Accuracy Comparison                                  | . 63 |  |  |

| 6.3.2                                             | Continuous Assignment                                | . 66 |  |  |

| 6.3.3                                             | Net Delays                                           | . 67 |  |  |

| 7. M                                              | DCML Asynchronous ARM                                | 69   |  |  |

| 7.1                                               | ARM Architecture                                     | . 69 |  |  |

| 7.1.1                                             | Overview                                             |      |  |  |

| 7.1.2                                             | Instruction Set                                      | . 71 |  |  |

| 7.2                                               | MDCML Asynchronous ARM                               | . 72 |  |  |

| 7.2.1                                             | Overview                                             |      |  |  |

| 7.2.2                                             | Register Bank                                        | . 76 |  |  |

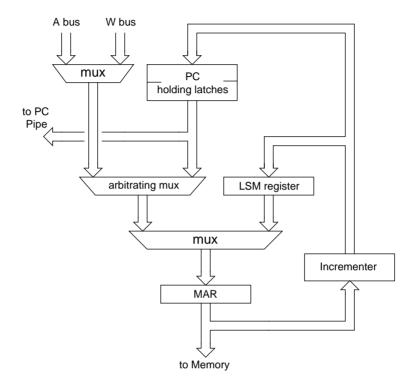

| 7.2.3                                             | Memory Interface                                     | . 83 |  |  |

| 7.2.4                                             | Address Interface                                    | . 83 |  |  |

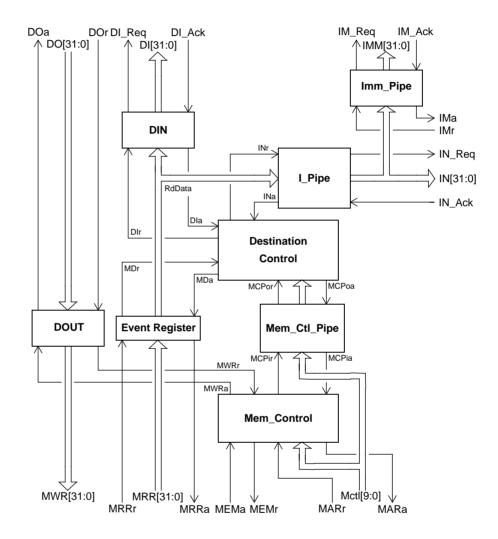

| 7.2.5                                             | Data Interface                                       | . 93 |  |  |

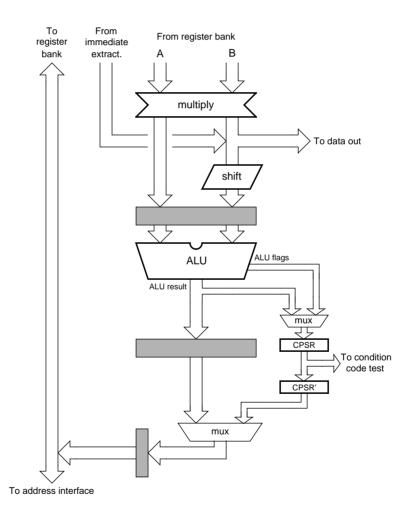

| 7.2.6                                             | Execution Unit                                       |      |  |  |

| 7.2.7                                             | Comments on the MDCML Asynchronous ARM Design        | 106  |  |  |

| 8. Aı                                             | chitectural Modelling 1                              | 107  |  |  |

| 8.1                                               | Introduction                                         | 107  |  |  |

| 8.2                                               | Modelling                                            | 107  |  |  |

| 8.3                                               | Features                                             | 113  |  |  |

| 8.3.1                                             | Instantiation Parameters                             | 113  |  |  |

| 8.3.2                                             | Test Vector Generation                               | 114  |  |  |

| 8.4                                               | Code Execution                                       | 117  |  |  |

| 8.4.1                                             | Compilation Method                                   | 117  |  |  |

| 8.4.2                                             | Validation Suite                                     | 117  |  |  |

| 8.4.3                                             | Dhrystone Benchmark                                  | 118  |  |  |

| 8.5                                               | Usage                                                | 120  |  |  |

| 8.5.1                                             | Instrumentation                                      | 120  |  |  |

| 8.5.2                                             | Graphical Output                                     | 122  |  |  |

| 8.5.3                                             | Detecting Incorrect Operation                        |      |  |  |

| 8.6                                               | Performance analysis                                 |      |  |  |

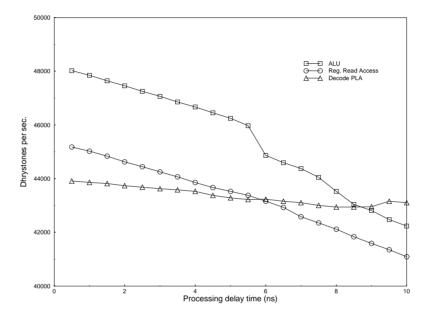

| 8.6.1                                             | Subsystem Processing Performance                     | 126  |  |  |

| 8.6.2                     | Non-symmetrical Propagation Delays            | 128 |  |

|---------------------------|-----------------------------------------------|-----|--|

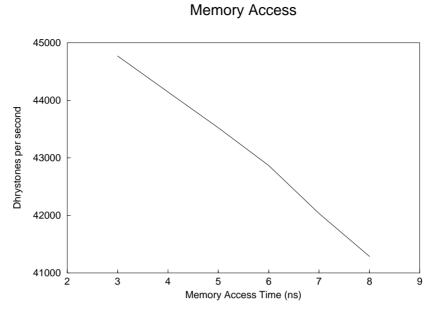

| 8.6.3                     | Processor-Memory Interaction                  | 129 |  |

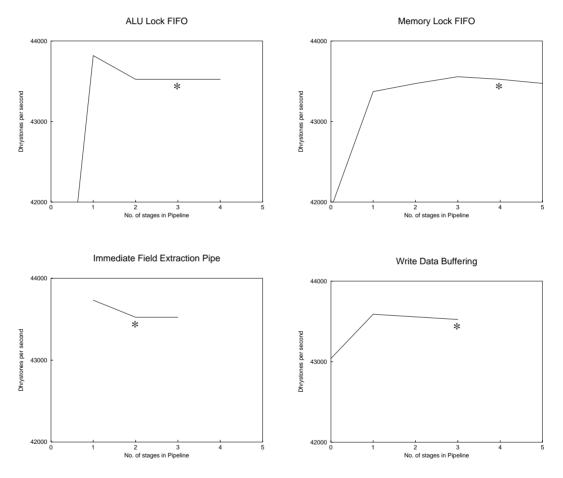

| 8.6.4                     | Internal Pipeline Efficiency                  | 130 |  |

| 8.6.5                     | Comments on the Performance Analysis          | 133 |  |

| 9. Conclusions 134        |                                               |     |  |

| 9.1                       | Production of the System Model                | 134 |  |

| 9.2                       | Current State of the Project                  | 135 |  |

| 9.3                       | Comments on the Verilog Modelling Environment | 135 |  |

| 9.4                       | Future Research                               | 137 |  |

| 9.4.1                     | Technology Migration                          | 137 |  |

| 9.4.2                     | Architectural Design Alternatives             | 137 |  |

| References                |                                               |     |  |

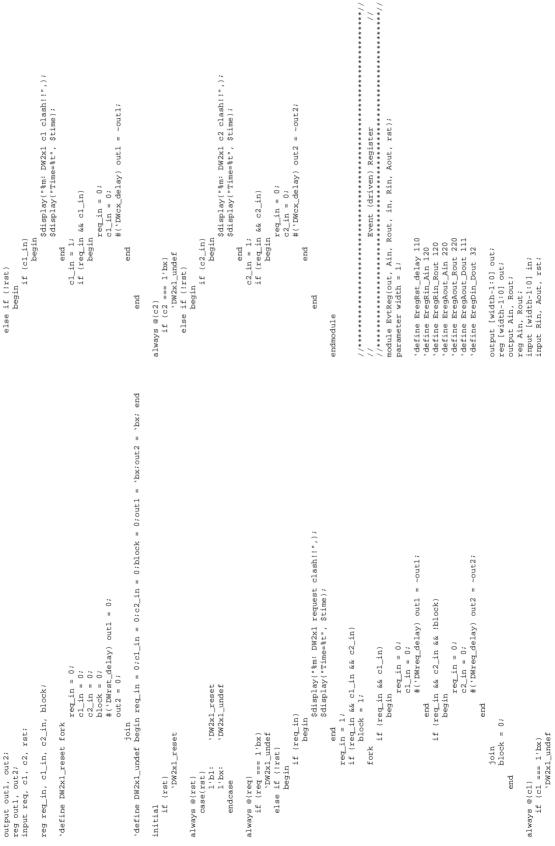

| Appendix A: Verilog Model |                                               |     |  |

### **List of Figures**

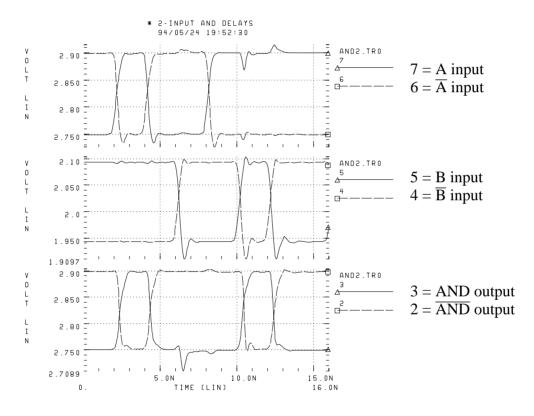

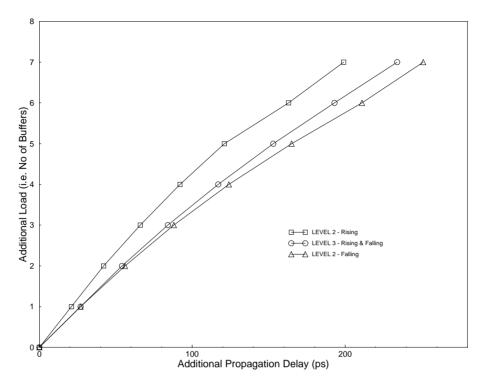

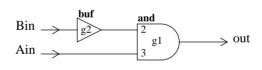

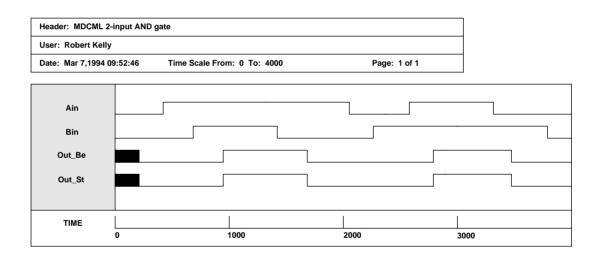

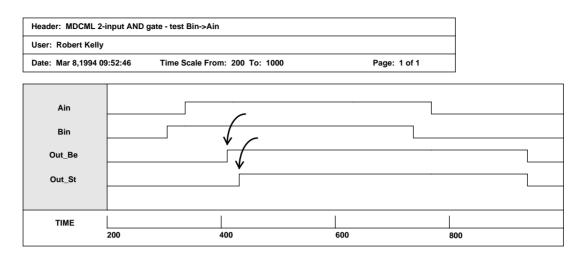

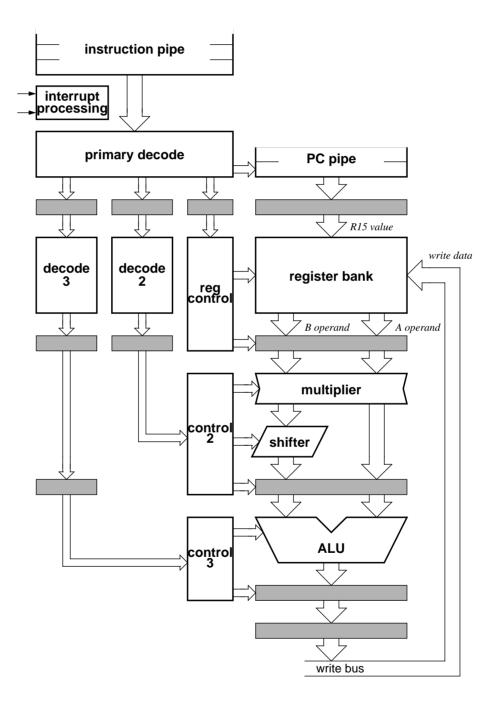

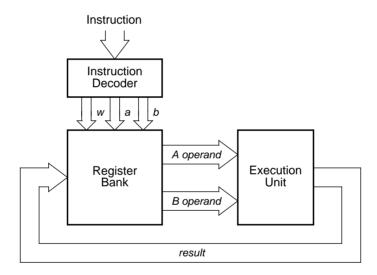

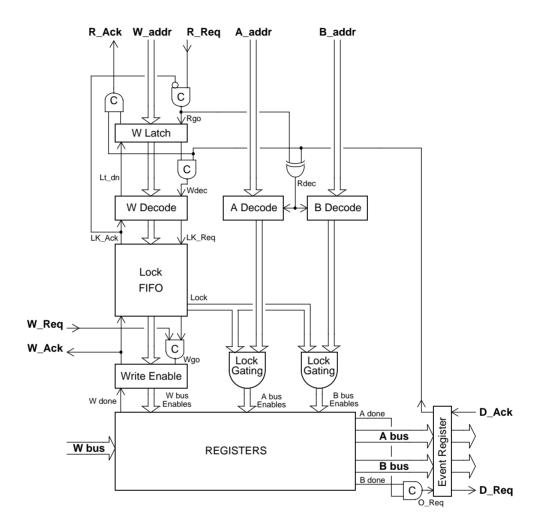

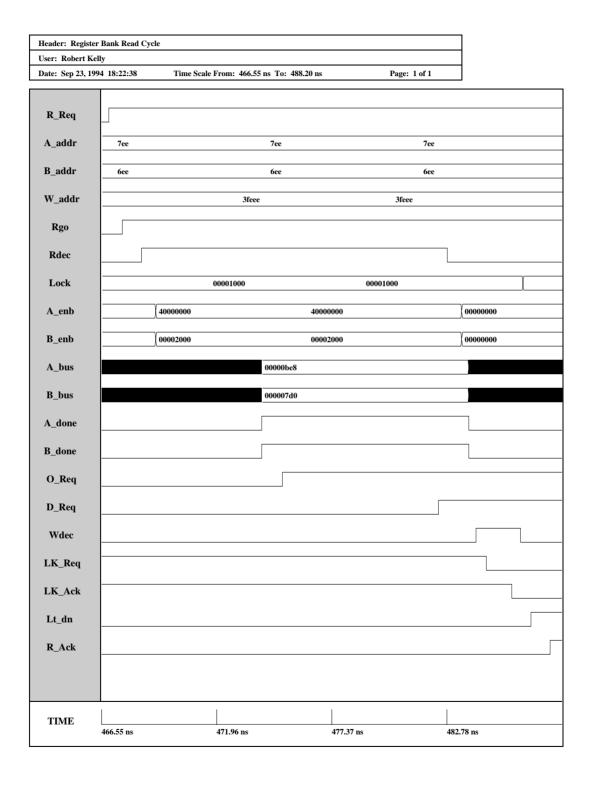

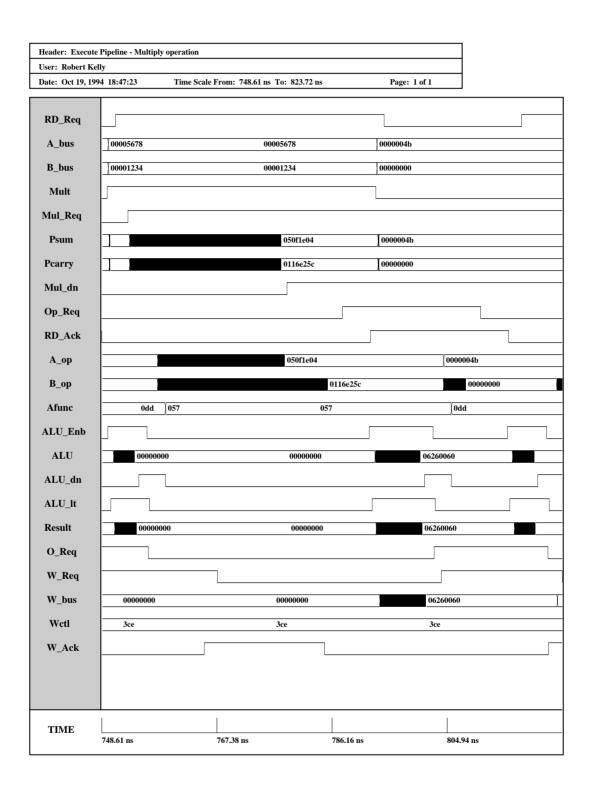

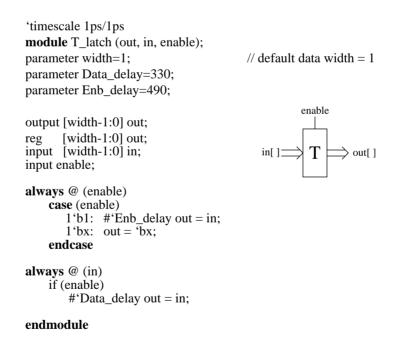

Two-phase (transition) Signalling. 19 Four-phase Signalling (incorrect operation). 20 Four-phase Signalling (correct operation). 21 Bundled Data Interface. 23 Data Value Constraints. 24 Event Register. 33 Micropipeline Control Block Implementation of Parity Function. 35 Possible Implementation of RS Flip-Flop. 39 Dynamic Power Dissipation. 49 MDCML 3-Input AND Gate. 51 4:1 Multiplexer. 52 Transparent Latch with Reset. 53 2-input AND gate. 56 SPICE model of AND2. 56 2-input AND gate SPICE waveforms. 57 Graphs of Additional Load vs Additional Delay. 59 Graphs of Additional Delay vs Extent of Drive Sharing. 60 Ain after Bin SPICE waveforms. 65 ARM6 Block Diagram. 70 Internal Processor Organisation. 73 Micropipelined Structure of the Execution Pipeline. 75 Register Bank Operation. 76 Asynchronous Register Bank Design. 78 Register Bank Read Cycle Waveform. 80 Register Bank Stalled Read Waveform. 81 Register Bank Write Cycle Waveform. 82 Address Interface Structure. 84 Address Interface Instruction Prefetching Waveform. 89 Address Interface Data Transfer Waveform. 90 Address Interface Block Data Transfer Waveform. 91 Address Interface Branch Waveform. 92 Data Interface Structure. 93 Data Interface Byte Read Waveform. 97 Data Interface Byte Write Waveform. 98 Data Interface Instruction Read Waveform. 99 Execution Unit Structure. 100

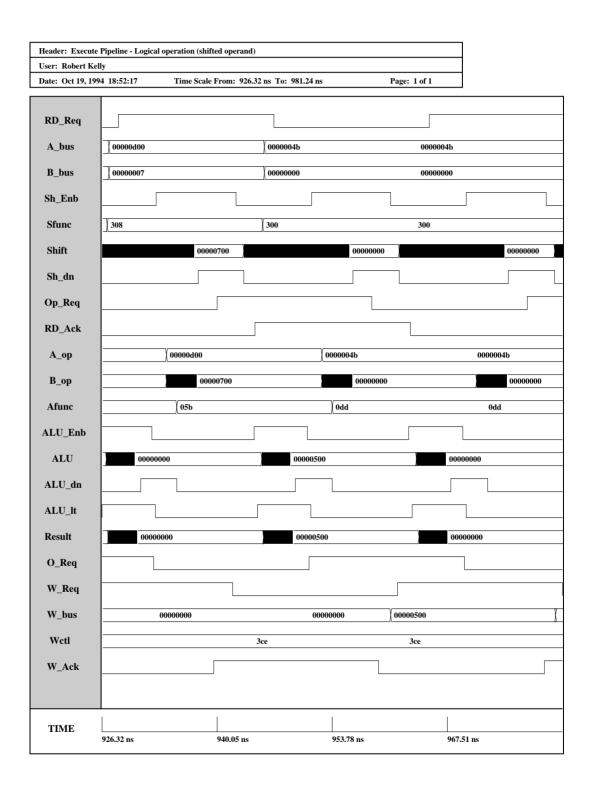

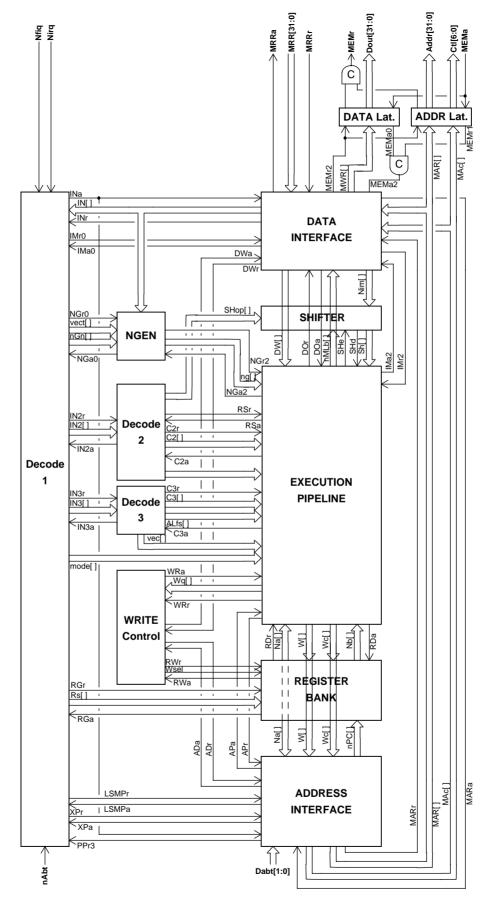

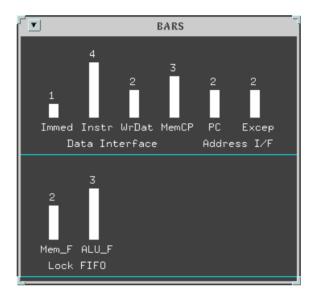

Execution Unit Multiply Waveform. 104 Execution Unit Shifted ALU Operand Waveform. 105 MDCML Asynchronous ARM Processor Diagram. 111 MDCML Asynchronous ARM 'Top-Level' Verilog Model. 112 Register Bank Display using Verilog gr\_regs() system task. 123 Pipeline Occupancy using Verilog gr\_bars() system task. 124 Graph of Block Processing Time vs Dhrystone performance. 127 Effect of Non-Symmetrical Propagation Delays. 129 Effect of Memory Speed on Processor Performance. 130 Pipeline Occupancy during Benchmark Execution. 131 Effect of Pipeline Length on Processor Performance. 132

## Abstract

As VLSI process technologies develop and feature sizes shrink, the global clocking schemes currently employed in synchronous systems are beginning to experience difficulties in a number of areas. Asynchronous circuits have a potentially higher performance than synchronous circuits since an asynchronous circuit exhibits average-case performance, in contrast to synchronous systems, which must be specifically designed to accommodate worst-case conditions. However, asynchronous design techniques are not widely understood or developed, particularly in the context of a large, complex system.

Recently, an asynchronous design methodology, namely Micropipelines, has been presented which has proved useful in developing an asynchronous CMOS implementation of an existing commercial RISC architecture. A subsequent project has been initiated to develop architectural modelling and implementation tools for an asynchronous highperformance bipolar implementation of the same target architecture.

This thesis presents the issues involved in asynchronous logic design, the details of the particular asynchronous design methodology employed and an introduction to the architectural modelling environment used in the development of the bipolar asynchronous implementation. The development of the system model is illustrated, with reference to the underlying primitive components and the hierarchical composition of the complete design from asynchronous sub-functions communicating via a well-defined signalling protocol. A demonstration of how the architectural model can be used to generate information regarding the internal operation of the system, which is then used to improve the complete design is given. The suitability of modelling asynchronous systems with the modelling environment employed is discussed.

### **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification at this or any other university or institute of learning.

Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of Department of Computer Science.

## Preface

The author was employed in the motor and light engineering industries before returning to full-time study in 1987. He graduated with a B.Sc. (Hons.) Degree in Computer Engineering from the University of Manchester in 1990. The author was previously employed as a Research Associate on the ESPRIT-funded EDS project, being involved in operating system kernel developments for a message-passing multiprocessor architecture. He is currently employed as a Research Associate in the AMULET group at the University of Manchester on the Transforming Architectural Models (TAM-ARM) project.

## Acknowledgements

The work presented here was carried out as part of the TAM-ARM project funded within the Design Automation section of the DTI/SERC Advanced Technology Programme. The author gratefully acknowledges this support and the technical assistance provided by the industrial project partners: Advanced RISC Machines (ARM) Limited and GEC Plessey Semiconductors.

I would like to express my sincere thanks to my project supervisor Dr. L.E.M. Brackenbury, for her support and encouragement. I would also like to thank members of the original AMULET1 design team: Prof. Steve Furber, Nigel Paver, Paul Day and Jim Garside for revealing the innermost secrets of their creation.

The AMULET research group in the Computer Science department of the University of Manchester provided a stimulating and interesting environment in which to contemplate Life, the Universe and Asynchronous Processor Design - to the remaining group members, both staff and students, I am indebted to you for making it so.

Finally, to my wife, Kathryn, and daughters, Leah and Laura, who have endured so much over the past few months without complaint (well, almost!), I am eternally grate-ful.

## 1. Introduction

"By combining advances in integrated circuit technology, improvements in compiler design and new architectural ideas, significant performance improvements have been realised in the contemporary design of computer systems. These improvements have only been made possible by bringing together important technological advances with a better empirical understanding of how computers are used. From this fusion has emerged a style of computer design based on **empirical data**, **experimentation** and **simulation**."

These ideas, drawn from probably the most important text on computer design over the past decade - Computer Architecture: A Quantitative Approach [Henn90] - indicate the considerable benefits of producing a model of any proposed prototype system. The model should be capable of being exercised with a realistic workload to provide performance indicators and to enable the effects of design decisions to be explored.

The work presented in this thesis is concerned with the architectural modelling of an Asynchronous Bipolar Microprocessor. The prototype processor design is derived from AMULET1 [Furb94a], an asynchronous CMOS version of the ARM RISC microprocessor. Although the AMULET1 architecture was not the first asynchronous microprocessor [Mart89], it is the first to overcome the difficult implementation areas of handling interrupts and exact exceptions, and providing multi-cycle instruction support. The implementation technology is based on a high-performance, differential, current-mode logic family developed by GEC-Plessey Semiconductors. As outlined above, a simulation model is desirable before implementing a prototype system. When, as is the case

with this work, a novel system architecture produced using an unfamiliar design methodology is to be implemented on a new advanced bipolar process, then extensive simulation becomes essential.

There are several objectives of this thesis. The first is to introduce the reader to the issues involved in asynchronous logic design in Chapter 2 and to the specific asynchronous design style used for the project in Chapter 3. The second is to familiarise the reader with the chosen system modelling language in Chapter 4 and the high-performance bipolar technology used to implement the prototype system in Chapter 5. The next objective is to show how the system model components are constructed based on the circuit characteristics of the underlying implementation technology. This is presented in Chapter 6. A further objective, achieved in Chapter 7, is to introduce the ARM architecture and explain the operation of the asynchronous implementation. The final objective is to show how the modelling environment is used to incorporate the design methodology and to demonstrate how the information produced by the model may be used to improve the design of the system in Chapter 8.

The structure of the remainder of this thesis is as follows:

Chapter 2 explains the domination of synchronous design techniques in current electronic circuit synthesis. The problems with synchronous design, which are generating renewed interest in asynchronous design styles, are noted. An introduction to asynchronous logic is given, along with the signalling protocols used, and some of the issues involved in delay modelling are considered.

Chapter 3 gives an introduction to the particular asynchronous design methodology used in the development of the Asynchronous Bipolar microprocessor. Examples of the control circuit elements used are included.

Chapter 4 presents the modelling environment and demonstrates some of the language constructs and the hierarchical structure capabilities. An indication of how time is managed while exercising the model is given. Chapter 5 introduces the differential bipolar technology employed to implement the prototype system. The circuit operation is explained by considering some gate function examples.

Chapter 6 shows how the architectural models of the bipolar logic gates and functions are developed based on the circuit simulations of the equivalent transistor models of the basic gates. The effects of gate output loading and input drive characteristics are explored.

Chapter 7 outlines the ARM target architecture and the instruction set. The structure of the asynchronous bipolar architecture is then presented with detailed examination of the major functional units, namely the Register Bank, Address Interface, Data Interface and Execution Unit. Simulator output waveforms are included to demonstrate the operation of the units.

Chapter 8 illustrates how the architectural model of the asynchronous ARM was developed in the modelling environment using a hierarchical, modular structure. Some of the features of the modelling language are then elaborated and some examples of the modelling tools that have been constructed are demonstrated. Various executable programs used to validate the architecture and measure performance are presented. An illustration of how the system model is used to gain information regarding the operation of the design and subsequently, how this information is used to suggest system design enhancements is given.

Chapter 9 summarises the current state of the project and draws together the conclusions resulting from this work, discussing the applicability of the Verilog to the architectural modelling of asynchronous systems. Future research areas, continuing on from this work are suggested.

The Appendix contains the complete hierarchical Verilog model of the MDCML Asynchronous ARM including the functional subsystems, asynchronous control elements and standard logic gate primitives.

## 2. Asynchronous Logic

Computer technology has evolved rapidly over the past few decades and the demand for even higher performance machines seems set to continue as computing solutions to new, more complex and computationally intensive problems emerge.

Synchronous design techniques have dominated the field of digital logic synthesis during this development period. This supremacy has been brought about for several reasons:

□ The concepts required to create a synchronous solution to the production of a logic circuit are easily understood - the designer simply defines the combinatorial logic necessary to perform the required function and then surrounds it with latches which are enabled with a common clock. In a large design, the entire system is then a composition of subsystems communicating by passing data values between the clock-controlled registers.

□ The global clock fulfils two system functions - the clock *transitions* define the successive instants at which the system state changes can occur and the clock *period* is sufficient to account for the logic and wire delays. Since the clock period is specified to be greater than the slowest combinatorial path that could occur during the computation, circuit hazards and feedback problems can generally be ignored [Seit80].

□ By neglecting the effects of *clock skew* - the time difference between the arrival of the global clock signal at different points in the system - the total system state, when considered at the end of the clock period, is assumed to be deterministic and discrete, changing only at the edges of the system clock.

□ The synchronous design style is well-understood and formalised and is therefore readily accessible to potential digital logic engineers, the preponderance of synchronous circuits is then reinforced when these new engineers become productive.

□ Also, widely available standard components, which are well-specified and documented, have been positively developed for use in the synchronous style.

□ Verification of the correct operation of a synchronous design simply involves checking the setup and hold times of the outputs of the combinatorial logic sections of the design to ensure that they meet the requirements of the clocked registers.

□ CAD tool support has also been developed, in parallel with the synchronous design concepts, which manage much of the timing verification involved.

□ Testing is also a much easier proposition in a synchronous circuit since many techniques including, for example, Scan Paths and BILBO (Built-In Logic Block Observation) are well-developed.

Recently, however, significant interest has arisen in the field of asynchronous logic design. This interest may be as a consequence of the problems associated with the global clocking strategy becoming more acute, a recognition that the formal techniques for handling asynchronous behaviour and the automatic synthesis potential of asynchronous circuits are now worth exploiting, or that inspiration has been generated by recent publications in the field, most notably the 1988 Turing Award Lecture on *MICROPI-PELINES* given by Ivan Sutherland [Suth89].

As VLSI process technologies develop and feature sizes shrink, the global clocking schemes currently employed in synchronous systems are now beginning to experience severe difficulties in the following areas:

□ Since the clock signal controls the entire system, it must be distributed across the entire chip. This requirement for large scale clock driver circuitry is expensive - in current high performance microprocessors a considerable proportion of the silicon area used and power dissipation required is given over to the global clock logic [Dobb92].

□ The design effort needed for the clock driver circuitry, and consideration of the effects of clock skew, is non-trivial. It is becoming increasingly difficult to maintain the clock skew within reasonable bounds across all process, temperature and circuit operational speed parameters and may result in the clock period being extended. In current leading-edge synchronous microprocessor designs, a significant proportion of the clock period is used to account for the effects of clock skew.

□ The circuit modifications required when a relatively small subsection of the system is changed may have ramifications across the entire chip design.

□ The global clock period must allow for the worst-case logic delay, even though, if the system is not operated in an extreme environment, the worst-case delay may never actually occur. The resulting performance is then reduced as the system is effectively idle during the time between the outputs of the combinatorial logic settling and the arrival time of the (worst-case period) clock.

It has long been recognised by logic circuit designers that asynchronous circuits have a potentially higher performance that synchronous circuits, since an asynchronous circuit exhibits average-case performance (the processing commences as soon as the new input data arrives - the time required to complete the computation execution being dependent on the actual input data values). A synchronous ALU, for example, must be particularly designed to allow for worst-case execution time irrespective of the actual input data values presented to the circuit.

In general, arbitration is required when several sources compete for the same service (or resource), since the service request signals may arrive at the shared resource at any time. In a synchronous system, asynchronous inputs are synchronized to a local clock, allowing metastable effects to be (hopefully) resolved in a limited period. An asynchronous system can wait an arbitrary time for arbitration to occur before making a clear decision. As a result arbitration is inherently more robust and reliable.

However, the asynchronous design framework is unfamiliar to established engineers. The basic 'building blocks' of asynchronous logic synthesis need to be developed, since currently the components are unfamiliar and unoptimised. Also, the circuit size of an asynchronous solution, relative to the equivalent synchronous design, is possibly increased (in part, due to the unoptimised basic components); although this may be offset by the non-trivial requirement for clock-driver circuitry for larger systems.

The existence of circuit races or hazards causes a further complication in an asynchronous design. Fundamental Mode operation<sup>1</sup> must be employed, or various assumptions must be made regarding the relative delays or speeds of the circuit component elements. The testing of asynchronous circuits also causes problems. Sequential circuits are very difficult to test and techniques have not yet been fully developed to test asynchronous combinatorial logic. No high-level method has yet been produced to assist in checking the *liveness* (absence of deadlock) of a design.

Several methodologies have been developed to synthesize asynchronous circuits, some are based on enhancements to Petri nets [Pete81, Moln92], others are compilationbased on high-level languages [Mart90, Brun91] developed from CSP [Hoar85]. Surveys of asynchronous design methodologies and techniques can be found in [Gopa90, Hauc93]. Some of the asynchronous design terminology that may be encountered in the text will now be explained. This relates to the modelling of signal propagation delays and the mechanisms used for communication between asynchronous subsystems.

### 2.1 Delay Modelling

In a *BOUNDED DELAY* model, it is assumed that the delays in the circuit elements and wires are known (or at least have some upper bound). When input signals are applied to a circuit, then after a particular time interval has elapsed the output signals are known to be valid. Note that this is also the delay model used for synchronous designs.

*DELAY-INSENSITIVE* circuits use a contrasting model to that used in bounded delay circuits; it is assumed that all signal delays in both elements and wires are unbounded.

<sup>1.</sup> Fundamental mode operation requires that a circuit achieve a stable internal state after every individual input signal change.

No matter how long the circuit waits, there is no guarantee that an input signal will be received. Circuits designed in this style must include functions to detect when a new input value actually arrives.

The *SPEED-INDEPENDENT* model is a weaker form of the delay-insensitive paradigm, in that it is assumed that the element delays are unbounded but the interconnection wires have zero delay.

### 2.2 Signalling Protocols

Communication between modules or subsystems in an asynchronous environment is achieved by employing a commonly agreed set of control signals (and some associated operational rules) which are passed between adjacent modules. The method usually involves detecting an 'event' on the control signals, eg. a change in the voltage level of the interconnecting wire.

In order to construct asynchronous systems by the composition of individual subsystems, where each performs a specific (and different) function, a general signalling protocol is required. This protocol will operate between the various modules without any regard to the internal processing rates of individual modules, or of the actual signal propagation delays of the communication links. This can be achieved by placing no restrictions on the timing of the signals involved in the communication protocol. Only the *sequence* of the control signal transitions is significant.

The basis for some of the simplest protocols involves the use of two wires connected between adjacent modules: a REQUEST wire and an ACKNOWLEDGE wire.

Asynchronous systems usually employ one of two communication protocols: twophase (or transition) signalling or four-phase signalling.

#### 2.2.1 Two-Phase Signalling

In this protocol, any transition between the two logic levels, a HIGH to LOW transition or a LOW to HIGH transition, is accorded the same meaning.

A transition may also be referred to as an EVENT, hence the alternative name for this protocol is 'event signalling'.

Two-phase signalling operates between two modules in the following manner:

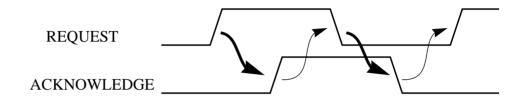

Figure 1 : Two-phase (transition) Signalling.

The sender generates an event (transition) on the REQUEST wire. At some point in time later, the receiver detects the request transition and indicates that it has received the request signal by generating an event on the ACKNOWLEDGE wire. The sender eventually receives the acknowledge event, signifying that the receiver is ready to receive another request.

The arrows on the diagram indicate the constraints on the sequence of events allowed on the control signals used in the protocol. The THICK arrows show the constraint imposed by the receiver: an acknowledge event cannot be generated until a request has arrived. The THIN arrows show the constraint imposed by the sender: the sender cannot generate another request until the previous request has been acknowledged by the receiver. The fact that each of the modules regulates the sequencing of one of the control signals indicates that the correct operation of the inter-module communication path will only occur when both sender and receiver obey the protocol rules.

Because BOTH edges are used in the two-phase scheme - the actual logic LEVEL of a particular control signal does not assume any significance - it provides the capability of

increasing the performance of communication protocols above that of conventional signalling methods, since *every* change in the signal carries some information content.

Initially, the concepts of transition signalling may be difficult to assimilate into the mindset of the conventional logic designer, since the two-phase circuits must be symmetrical with respect to the high and low logic levels of the control signals.

#### 2.2.2 Four-Phase Signalling

Four-phase (or 'Return to Zero') signalling is characterised by the control signals being active when in the HIGH (logic '1') state and then being required to return to the LOW (logic '0') state before subsequently becoming active again.

The protocol could take the following form:

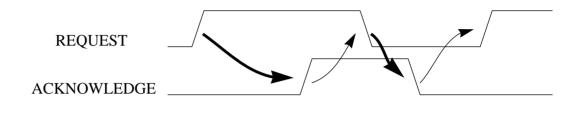

Figure 2 : Four-phase Signalling (incorrect operation).

The sending module raises the REQUEST line to its HIGH (active) state and after a short time interval deactivates the signal by taking it LOW again. The receiver, having detected the request line entering its active state, produces a response by briefly raising the ACKNOWLEDGE line to its HIGH state.

However, the protocol in this form may result in communication failure since, if the sender has a comparatively faster circuit operation than the receiver, the sender may raise then quickly lower the request line to produce a very narrow 'pulse' which the receiver may be unable to detect.

Correct protocol operation is enforced by requiring the sender to continue holding the request line in its active (HIGH) state until 'request reception' is indicated to the sender by the receiver raising the acknowledge line into its HIGH state. The request line is then deactivated, allowing the receiver to subsequently deactivate the acknowledge line.

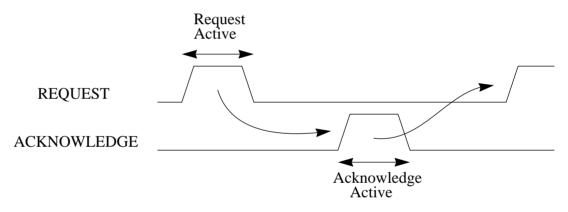

The properly functioning four-phase protocol is then:

Figure 3 : Four-phase Signalling (correct operation).

Again, each of the modules taking part in the communication imposes constraints on the sequencing of the control signal transitions. The THICK arrows indicate the constraints enforced by the receiver: the acknowledge line can only enter its active state after the request line is activated and can only be deactivated after the request line is deactivated. Similarly, the THIN arrows show the constraints imposed by the sender: the sender must not 'remove' the request signal until the receiver acknowledges that it has 'seen' the request and a subsequent request must not be generated until the acknowledge has entered its inactive state.

The four phases of the protocol can be observed by noting the four possible combinations of the control signals:

| Request LOW, Acknowledge LOW   | - | Inactive                              |

|--------------------------------|---|---------------------------------------|

| Request HIGH, Acknowledge LOW  | - | Requesting                            |

| Request HIGH, Acknowledge HIGH | - | Acknowledged                          |

| Request LOW, Acknowledge HIGH  | - | Request cleared, Acknowledge to clear |

Four-phase signalling may be more familiar to current logic designers since each phase of the protocol may easily be determined by examining the logic LEVELS of the control signals.

Also, four-phase signalling is easier to implement because of the widely-available standard components which have been developed to manage logic *levels*.

#### 2.2.3 Data Communications

In addition to the signalling protocols used to indicate control actions, outlined above, a mechanism for passing data values between modules is required.

The simple REQ/ACK scheme can only signal events. In order to transmit data values a method of differentiating between two alternative events (sending a '1' and sending a '0') must be employed. This method could be extended, by using two sets of REQ/ACK pairs, into a four-wire per bit signalling system where each pair is used to communicate a particular bit value: Req0/Ack0 is used to send and acknowledge zeros, Req1/Ack1 is similarly used for ones. In the simplest system, consisting of only four wires, multiple bit values, bytes or words, are sent in bit-serial fashion.

The number of wires required, per bit, may be reduced to three by noting that the two acknowledge wires Ack0 and Ack1 may be combined into one common acknowledge wire, Ack.

This idea of a common acknowledge wire can be used for the communication of multiple bit 'words'. Two request wires, R0 and R1, are provided for the transmission of each bit (a technique also known as DUAL-RAIL ENCODING) and the common word acknowledge signal is returned only when a transition has occurred on one of the request wires for each of the bits of the word.

#### 2.2.4 Bundled-Data Interface

Although the previous schemes provide a robust communication technique in an environment where signal propagation delays are unpredictable, the cost in terms of number of signal wires needed is high. This is especially the case when the communication is over a relatively long distance. There is also a cost in terms of the signal detection/completion circuitry required when dealing with multiple bit data 'words'.

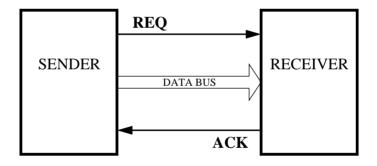

The *bundled data* interface seeks to significantly reduce the number of signal wires, particularly for large bit-width data values, to just one data wire per bit (as in conventional synchronous 'bus' structures). This set of signal wires is collectively known as a BUNDLE. For each wire, the logic *level* indicates the value. In addition, a request/ac-knowledge pair of control wires is needed per data word.

Assuming that two-phase (transition) signalling is used on the req/ack control wires, the data values are transmitted in the following manner:

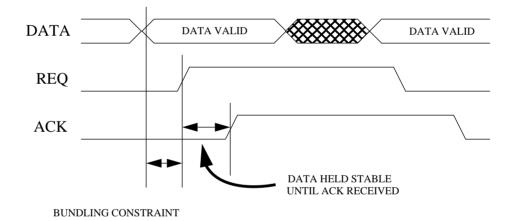

Figure 4 : Bundled Data Interface.

The sender places the n-bit value onto the data wires (bus) and then generates an event on the REQUEST line. At some later time, the receiver will detect the arrival of the request event which will indicate that the data bus is holding the correct transmitted value. The receiver will then latch the data value before generating an acknowledge event back to the sender. The sender is then free to remove the current data value and set up the next value for transmission.

Note that for correct operation, there is an implied assumption that the data value arrives at the receiver before the request event i.e. in the same order as they were generated by the sender. More formally - "The sequence relationships of events in a bundle are the same at the sender and the receiver." [Suth86]. This is a timing constraint on the use of the bundled-data interface and the logic circuit designer must ensure that this timing relationship is satisfied.

Also note that the sender may not change the data value, once it has generated a request, until it receives an acknowledgment from the receiver. From the point of view of the receiver, the data is only valid from the time of reception of the request event until the acknowledge is generated.

Figure 5 : Data Value Constraints.

## 3. Micropipelines

Pipelining is used in computer architectures to provide increased processing rates through the use of concurrency [Kogg82]. A large computation is divided into a series of operations, which execute in parallel.

Pipelines may be clocked (*synchronous*) or event-driven (*asynchronous*). In both synchronous and asynchronous pipelines, the *throughput* - the number of data items processed in a given time interval - is limited by the computational rate of the slowest subsystem (module) in the pipeline. However, the *latency* - the time taken for an individual data item to pass through the complete (empty) pipeline - of the synchronous and asynchronous pipelines differs.

For the synchronous case, the latency is calculated to be the number of pipeline stages multiplied by the processing time of the slowest element; the clock period must be specified to accommodate the slowest element, even though all other elements may be capable of sustaining much higher clocking rates.

The latency of an asynchronous pipeline is calculated to be the sum of the processing times of each element. This latency can be significantly less than that of the synchronous case if there is a wide range of processing rates for the component elements.

The lower latency of asynchronous pipelines may be exploited in, for example, processor instruction execution pipelines where the pipeline is frequently flushed when a branch instruction is executed.

Pipelines may also be categorised as ELASTIC or INELASTIC. For an inelastic pipeline, the input and output data rates must match, implying that the total amount of data contained in the pipeline is fixed. When an inelastic pipeline contains no processing elements, i.e. each stage consists of a storage element only, it acts like a simple SHIFT REGISTER. In contrast, the input and output rates of an elastic pipeline, however, may differ momentarily and therefore the amount of contained data is variable. An elastic pipeline without processing elements is a FIFO (First-In, First-Out).

FIFOs provide an important buffering function between systems acting at variable processing rates. The implementation of elastic FIFOs is difficult in a synchronous model: each stage must have a *full/empty* flip-flop, and each stage must be provided with *full/empty* information about the previous and successor stages. A particular stage receives a new data value if, at the appropriate clock transition, the stage is EMPTY and the previous stage was FULL. The stage can then <u>pass on</u> the data value if, at a subsequent clock transition, the next stage is EMPTY. The current stage can then make itself available to receive a new data value by changing its state flip-flop from FULL to EMP-TY.

Also, since the clocking rates at the input and output of an elastic pipeline may be different, some form of arbitration and synchronisation will need to be provided between the FIFO and the systems connected to it. An asynchronous implementation removes the requirement for arbitration by allowing the input and output processes of each stage of the FIFO to operate at their own pace.

In 1988, at the Turing Award Lecture, Ivan Sutherland put forward a modular approach to the design of computer systems using asynchronous logic. His idea was based on the use of simple data processing pipelines whose stages operate asynchronously. He termed these 'MICROPIPELINES' [Suth89]. A micropipeline is an elastic, boundeddelay, event-driven system using transition signalling and the bundled-data interface. A micropipeline without processing, a simple elastic FIFO, can be constructed from a basic component known as an Event Register (see Section 3.2.1). One of the benefits of micropipelines is that the registers, used to hold the data values as they flow through the pipeline, can be used to filter out hazards. This is achieved, in a similar manner to that used in synchronous designs (where the clock period is sufficiently long to account for hazards), by <u>locally</u> delaying the request output signal until all data values are stable. Also, any combinational logic structures can be used 'between' the pipeline registers including existing circuits used in synchronous designs.

As discussed in Chapter 2, the bundled-data interface is useful for data communications since it reduces the number of data wires required to transmit a value, particularly for large numbers of bits. In implementing an asynchronous 32-bit processor, for example, the inter-module completion-detection circuitry required if the data was transmitted using the '2 wires per bit' protocols would be prohibitively large.

Micropipelines offer the opportunity to construct complex systems by the hierarchical composition of simpler modules. The two-phase signalling protocol allows modules of widely-differing performance to be easily integrated into a complete, correctly functioning, system. The data-driven execution rates of the individual asynchronous modules allow the benefits of average-case performance. The micropipeline approach also provides the facility to replace a particular module with one of a higher performance without impacting on the correct operation of the total system (as would be the likely case with a synchronous global clocking scheme).

In the context of VLSI technology, the design cost of large systems both in terms of time and effort is beginning to outweigh the combined fabrication and production costs of the final integrated circuits. Since an 'ad hoc' design style is impractical for large scale circuits, micropipelines provide a basis for an asynchronous design methodology for the construction of such systems. Pre-synthesised modular solutions to standard problems, packaged in an asynchronous design library, can then be interconnected using the transition signalling protocol.

The circuit designer simply ensures that each module conforms to the interface protocol and need not be fully conversant with the internal intricacies of the asynchronous 'cells'. The inefficiencies of this 'standard module' approach may be negligible when compared to the extra design cost of a full custom approach.

### 3.1 Control Circuit Elements

The transition signalling control circuits used to coordinate the activities of micropipelines may be constructed from a standard set of 'event logic' modules [Suth86]. Some of the more widely-used modules are presented below.

#### 3.1.1 XOR (Merge)

The Exclusive-OR (or non-equivalence) gate provides an 'OR' function for transition signals. An output transition (event) occurs in response to a transition arriving at any of the inputs. This module is also known as a MERGE element.

#### 3.1.2 Muller-C (Join)

The Muller-C element serves as an 'AND' function for events. A transition occurs on its output only after a transition has occurred on <u>each</u> of its inputs. In logic level terms, when the input levels match, the output assumes the same logic level as the inputs, otherwise the output holds its previous level. A reset input may be added to force the output to a defined initial state. The standard AND logic symbol with a large 'C' inside is used to represent the Muller-C element, which is also known as a JOIN or RENDEZVOUS element.

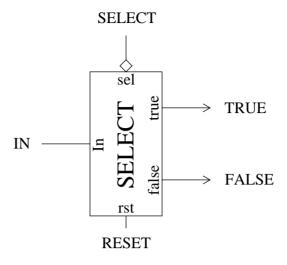

#### **3.1.3 Select**

The Select element 'steers' an input transition to one of the two outputs depending on the Boolean value of a second, 'select', input. The select Boolean value <u>must be val-</u> <u>id</u> before the input transition occurs. This is, effectively, a bundling constraint on the IN (event) input. The module is <u>NOT</u> delay-insensitive because of this requirement. Furthermore, while the Select element is essentially an event-triggered device, the logic <u>level</u> of the select input is significant.

#### 3.1.4 Toggle

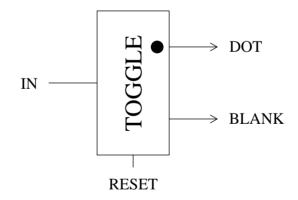

In a similar manner to the Select element above, an input transition of the Toggle element is steered to one of the two outputs. However, the output event is produced alternately on the two outputs in response to an input transition. Following a Reset signal, the first output to receive an event in response to an input event is marked with a heavy dot (see diagram), the outputs are then known as Dot and Blank (i.e. no dot).

#### 3.1.5 Decision-Wait

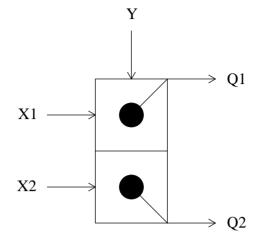

A Decision-Wait element has two sets of input signals and produces an output event when one event in each input 'set' has been received. For example, an event on input Y and an event on either X1 or X2 will produce an output event on either Q1 or Q2 respectively. Note that for correct operation, only one input event can be received on an X input (X1 or X2) for each event received on the Y input before the appropriate output transition occurs.

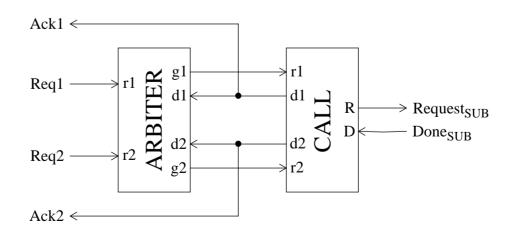

#### 3.1.6 Arbiter

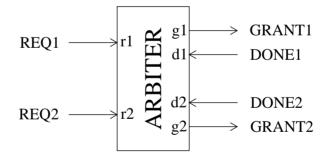

An Arbiter is used to guarantee mutually exclusive access to a shared resource for two competing independent requests. The arbiter chooses only one of the active input requests and allows only the corresponding output grant signal event to occur. When the arbiter is already in use by a requester, a second requester is inhibited until the "request done" acknowledge event is received (DONE1 or DONE2, depending on the currently active requester) indicating that the active requester is releasing control of the arbiter. The arbiter will then issue a grant signal (event) to the second requester. Although the input requests can occur at any time, even simultaneously, the output grant signals are guaranteed to be mutually exclusive or serialized.

#### 3.1.7 Call

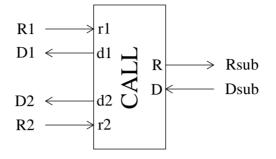

The Call element provides the functional equivalent of a "subroutine call". A request event for access to a common hardware function is received on one of the two request inputs, R1 or R2, which will subsequently generate a 'subroutine' request event on the Rsub output. When the subroutine function has completed, indicated by the arrival of an event on the Dsub (subroutine done) input, the Call element generates an output event on the appropriate 'request done' output (D1 or D2, depending on the active requester).

For correct operation, the full Request / Subroutine Request / Subroutine Done / Done cycle must complete before the next Request occurs and therefore the two input request signals, R1 and R2, must be mutually exclusive. For a circuit topology where R1 and R2 cannot be guaranteed to be mutually exclusive, the input requests may be routed to the Call element via an Arbiter.

#### 3 Micropipelines

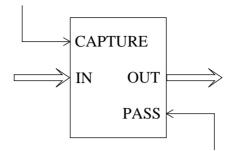

#### **3.1.8 Capture-Pass Latch**

The Capture-Pass latch is a storage element for use in an event-controlled system; unlike a traditional level-sensitive latch in which the *high* and *low* states of the clock/ enable signal indicate a different function, the event-controlled latch must provide equivalent responses to rising and falling transitions.

When the Capture and Pass inputs are in the same state (either both *high* or both *low*), the latch is in the **PASS** state: the output of the latch follows any change in the input value. When the Capture 'event' occurs, the latch will become insensitive to changes in the input data and will **CAPTURE** (store) the current input value, resulting in the output value being held stable. After a subsequent Pass 'event', the element will become transparent and the output will again follow the input.

For the Capture-Pass latch to operate correctly, the Capture and Pass events must alternate.

### **3.2 Control Circuit Examples**

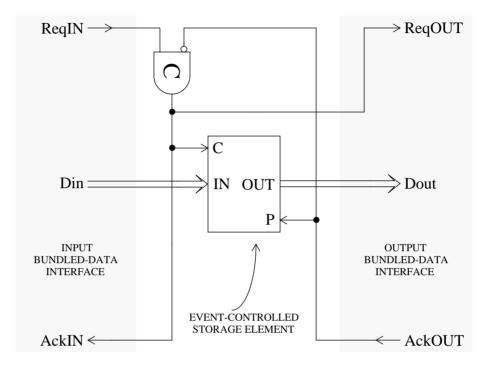

#### **3.2.1 Event Register**

As mentioned previously, an asynchronous FIFO can be constructed from a basic component known as an Event Register. An Event Register uses a two-phase signalling protocol on its input and output control circuits and incorporates an event-controlled storage element for the associated bundled-data value.

Figure 6 : Event Register.

Event Registers with 32-bit data values are used extensively throughout the Asynchronous ARM design.

The operation of the Event Register is as follows:

- i) Initially, assume all signals are LOW and the Capture-Pass latch is in the PASS (transparent) state.

- ii) An input data value is supplied followed by the arrival of a ReqIN event at the Muller-C and, because of the input inversion of the *LOW* state of the other input, an output event is generated from the Muller-C.

- iii) The Muller-C output event causes the Capture-Pass latch to enter the CAPTURE state: it latches the data value presented on its input.

- iv) Once the Capture-Pass latch has captured the data, an AckIN event is sent to the 'previous' stage (the previous stage can now prepare a new

input data value) and a ReqOUT event is sent to the 'next' stage of the pipeline.

Note that the Event Register will only capture the data in response to a ReqIN event if the stage is currently *EMPTY*. That is, if an acknowledge from the output stage is not pending from a previously generated ReqOUT event to the next stage.

Also, the Capture-Pass latch must be in the PASS state (Dout valid) before a Capture event occurs and, since the ReqOUT event is equivalent to the Capture event, the Dout data value must be valid before the ReqOUT event. The output interface of the Event Register therefore obeys the data bundling constraint.

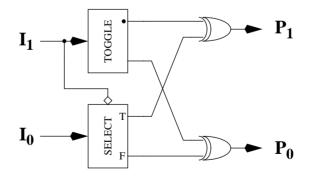

#### 3.2.2 Design Example: PARITY FUNCTION

A dual-rail encoded parity function using a transition signalling protocol was presented to the IFIP Working Conference on Asynchronous Design Methodologies (April 1993, Manchester) by Charles Molnar and this will be used as a design example:

The circuit will receive an input signal as an event on one of the two input wires,  $I_0$  or  $I_1$ , depending on whether a '1' or a '0' is indicated. The circuit must then provide an output event on one of the two output wires, P0 or P1, to indicate the *cumulative* parity of all of the inputs received up to that point.

A general, high-level, formal method of synthesizing Micropipeline control circuits does not, as yet, exist. A pragmatic approach must therefore be taken to derive a design for the parity function circuit using the Micropipeline control blocks outlined previous-ly in Section 3.1.

Assume that after a global reset, all the interface signals (inputs and outputs) of the parity function are *LOW*.

It can be noted that the accumulated parity of the received inputs is actually given by the logic level of the  $I_1$  input. If  $I_1$  is *HIGH*, the accumulated parity is '1', if  $I_1$  is *LOW*, the parity is '0'.

Events occurring on the  $I_1$  input cause alternating output parity signals to occur, since an  $I_1$  event indicates the arrival of a '1' and this will cause the accumulated parity to change. A **TOGGLE** element can be used to alternate the parity output events when the  $I_1$  input event indicates another '1' has been received.

Events occurring on  $I_0$  (indicating a '0' has arrived) cause an output event on  $P_1$  or  $P_0$  depending on the current accumulated parity value. That is, the output to be activated is indicated by the logic level of the  $I_1$  input signal. A **SELECT** block can be employed to 'steer' the  $I_0$  input event to the appropriate parity function output based on the logic level of  $I_1$ .

Two **XOR** elements are used to merge each of the separate sources of the  $P_1$  and  $P_0$  output events (from the Toggle and Select blocks) onto the actual parity function outputs. The Micropipeline control block implementation<sup>1</sup> is shown in Figure 7.

Figure 7 : Micropipeline Control Block Implementation of Parity Function.

<sup>1.</sup> Since Micropipeline control circuits are usually concerned with the control of datapath elements using the bundleddata convention, this example circuit is not typical of those found in an asynchronous Micropipelined microprocessor.

## 4. Verilog HDL

### **4.1 Introduction to HDLs**

When viewed at its lowest level, a digital system, particularly in the context of a VLSI implementation, may consist of several hundreds of thousands of primitive components. These components may be transistors or simple logic gates. At a higher level, these elements may be logically grouped into functional units such as Arithmetic Logic Units (ALUs), cache memories and Floating Point Units (FPUs) [Thom92].

Hardware Description Languages (HDLs) have been developed to assist the design process of such systems in managing the complexity involved in the synthesis of complex digital systems [Hart87]. The system may contain a large number of elements and a wide range of logical and physical implementation abstractions, in order to give a total overview of the system.

Initially, a conceptual idea of the required logical system is coupled with a set of constraints (relating to performance, power requirements, circuit size etc.) that the implemented system must meet and a set of primitive components from which to construct the system. The creative design process is an iterative operation of either manual composition or automatic synthesis of alternative solutions, which are then compared against the given system constraints. Normally, the design is partitioned into smaller sub-units, in the classical engineering technique of "divide and conquer" (or top-down design), and each sub-unit is then further divided until the complete system is specified in terms of the known primitive components [Brow91].

## 4.2 Introduction to Verilog

The Verilog<sup>1</sup> Hardware Description Language [Veri92] describes a digital logic system as a collection of textual-based models that define the functionality of the component sub-units and connections to those sub-units. The language accommodates a wide range of levels of abstraction:

- ALGORITHMIC the component's operation is expressed in high-level (program-like) language constructs.

- REGISTER TRANSFER LEVEL (RTL) the flow of data between registers is described.

- GATE LEVEL the system is defined in terms of logic gate primitives and their interconnections.

- SWITCH LEVEL for low-level design, particularly for MOS implementation, the system may be described in terms of transistors and storage nodes.

The language supports the early conceptual stages of design with its behavioural levels of abstraction (algorithmic and RTL), and the later implementation stages with its structural levels of abstraction (gate and switch levels).

During the design process, behavioural and structural constructs can be mixed as each of the sub-systems is designed. Hierarchical constructs are also provided to allow the system designer to control the complexity of the description.

## 4.3 Modules

Verilog describes a digital system in the form of a set of MODULES. The logical structure of each module is expressed either in logic gate (or MOS primitives) terms or as a behavioural representation.

<sup>1.</sup> Verilog is a trademark of Cadence Design Systems, Inc.

A module definition includes declarations of the external interface presented to other modules and any internal state used by the module. The external interface is defined in terms of PORTS, which are specified in parentheses after the module name. Ports may be declared to be INPUTS, OUTPUTS or bidirectional INOUTS. A module body contains either behavioural statements which specify the functionality of the module, or statements which create instances of other user-defined modules or logic gate primitives. By allowing module definitions to instantiate other modules, a hierarchical description of the system can be specified. The use of a hierarchical modular approach accommodates the "bottom-up" and "top-down" design styles.

## 4.4 Structural Modelling

A structural representation of a functional unit is achieved using gate and/or switch level modelling. A set of 26 standard gate-level primitives are incorporated and these can be extended by employing user-defined primitives. This provides a compact and efficient way of describing an arbitrary block of logic.

The Verilog HDL facilitates the accurate modelling of signal contention, bidirectional pass gates, resistive MOS devices, dynamic MOS, charge sharing and other technology dependent network configurations by allowing net signal values to have a wide range of unknown values and different levels of drive strengths.

A declaration begins with the gatetype keyword specifying the required gate or switch primitive. Gatetype keywords include: **and**, **or**, **not**, **buf**, **nmos**, **pmos**, **pullup** etc. Gate and switch instances include an optional instance name and a required terminal connection list.

The propagation delay from input to output through a logic gate or switch primitive may be specified in a declaration. The drive strengths on the output terminals of a gate declaration instance may also be defined. 'Nets' are a fundamental data type of the language and are used to model an electrical connection. Except for the **trireg** net, which models a wire as a capacitor that holds electrical charge, nets do not store signal values. Nets only transmit values that are driven on them by structural elements (gate outputs or assign statements) or behavioural models (registers).

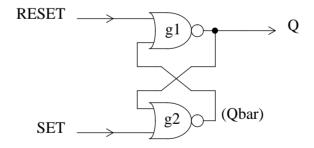

#### 4.4.1 Design Example: RS Flip-Flop

An RS flip-flop consists of two inputs, SET and RESET, and (normally) two outputs, Q and  $\overline{Q}$ . For the purposes of this design example, the  $\overline{Q}$  signal will not be generated as a module output. All the signals, inputs and output, will be active *HIGH* i.e. positive logic.

When the SET input is asserted (HIGH), the Q output signal goes HIGH and remains HIGH even when the SET input is deactivated. When the RESET input is asserted, the Q output goes LOW and again stays LOW when the RESET signal is deasserted. A conflict will occur if the SET and RESET inputs are both HIGH simultaneously. The logic circuit designer should ensure that this situation never arises.

A circuit implementation consists of two cross-coupled NOR gates [Mano84]:

Figure 8 : Possible Implementation of RS Flip-Flop.

An example module of a structural (gate-level) representation of a RS flip-flop is given overleaf. Each module definition begins with the **module** keyword and is terminated by the **endmodule** statement. The first line of the definition specifies the module name and the names of its ports.

| <pre>module RS_FF(set, reset, Q);</pre> | (1) |  |

|-----------------------------------------|-----|--|

| input set, reset;                       | (2) |  |

| output Q,                               | (3) |  |

| wire Qbar;                              | (4) |  |

|                                         |     |  |

| <pre>nor #10 g1(Q, reset, Qbar);</pre>  | (5) |  |

| <b>nor</b> #10 g2(Qbar, set, Q);        | (6) |  |

| endmodule                               |     |  |

In lines 2 and 3 in the example, the type of each port is specified: set and reset are input ports, Q is an output port. The module's logic gate primitive components are defined in lines 5 and 6. The first word in the line indicates the component type-name - in this case, **nor** gates. The #10 indicates that the propagation delay of the gate from input to output is 10 time units. The **nor** gates are then instantiated by giving each one an instantiation name (g1 and g2) and specifying the gate connections. The output is specified first, followed by any number of inputs (in this example two). There is a net (or wire) which is internal to the module, i.e. it is not an input or output, which connects the output of g2 to an input of g1. This internal net is declared and named in line 4.

## 4.5 Behavioural Modelling

When a system is modelled as a structural, gate-level representation, very little translation effort is required to convert the HDL model into a correctly functioning physical implementation. However, in many cases the circuit engineer requires the opportunity to derive many design alternatives and consider the merits of each design solution. Behavioural modelling facilitates the architectural refinement of a design. It allows the higher-level functional aspects of the prototype system to be easily evaluated in isolation, without regard to the final implementation of the proposed circuits [Russ89].

The syntax of the Verilog behavioural language is very similar to the high-level programming language 'C' [Kern88]. It contains a number of procedural constructs which include the familiar **if-then-else** conditional execution construct, the conditional assignment (**?**:) operator and the multi-way branch **case** statement. Four different statements are provided for iterative sequential behaviour: the **for**, **while**, **repeat** and **forever** loops. A full range of arithmetic, logical, bit-wise and reduction operators are also incorporated.

#### **4.5.1 Compound Statements**

Two or more statements may be grouped together by means of a *block* statement so that, syntactically, they act like a single statement. In a SEQUENTIAL block, which is delimited by the keywords **begin** and **end**, the statements execute in sequence. Control passes out of the block when the last statement executes. The delay values used in the assignment statements are relative to the execution time of the previous statement:

```

begin

#10 a = 1;

#5 b = 0;

#10 c = a;

end

```

In the example, register **a** is assigned the value 1 ten time units after the execution of the block statement commences. A further five time units later, i.e. fifteen time units from the start of the block statement, register **b** is assigned the value 0. Register **c** is then assigned the value of **a** (now equal to 1) a further ten time units later.

The keywords **fork** and **join** surround a CONCURRENT block statement in which the individual statements execute in parallel. Delay values in assignment statements are relative to the simulation time on entry to the block and control passes out of the block when all of the statements have executed:

```

fork

#10 a = 1;

#15 b = 0;

#25 c = a;

join

```

To achieve the equivalent effect to the sequential block statement, the assignment to register **b** in the second line must have a delay value of fifteen time units, since the delay is relative to the start of the block (not relative to the previous statement, as in the sequential block example). In a similar manner, the assignment to register **c** has a delay value of twenty-five time units.

#### 4.5.2 Process Control

The essence of a Verilog behavioural model is a PROCESS, which can be thought of as an independent flow of activity. The dynamic behaviour of a digital system is then a set of independent, inter-communicating processes. The basic Verilog control construct for describing a process is the **always** statement:

The always construct continually repeats the statement following, which may be a block statement (outlined earlier). All of the functionality of a module should be specified within an **always** statement.

A further Verilog control construct, called the **initial** statement, describes a process that is executed only once - it provides a means of initialising signals and internal module state variables:

```

initial

begin

busy = `false; // Initialise values

out = 0;

end

```

During simulation of a model, all of the activity flows defined by the **initial** and **always** statements start together at simulation time zero.

#### 4.5.3 Timing Control

Two types of explicit timing control are provided in Verilog to regulate when procedural statements are to occur in simulation time. The first type is a *delay* control in which a value expression specifies the time duration between the activity flow reaching a particular statement and the simulation time at which the statement actually executes. The second type of timing control is the *event* expression, which allows the execution of statements in a particular procedure to wait for the occurrence of some simulation event. The awaited simulation event will be generated by some other, concurrently-executing, procedure. A simulation event can be either the change of a value on a net, or in a register (an IMPLICIT event), or the occurrence of an explicitly named event that is triggered from other procedures (an EXPLICIT event). In many cases, the event control is the positive or negative edge of a clock signal.

Simulation time can only advance by one of the following three methods:

□ A *delay* control, which is introduced by the number symbol (#):

eg. **#100** out = ~in;

After 100 time units, the output is defined to be the inverse of the input signal.

□ An *event* control, which is introduced by the at symbol (@):

eg. always @(negedge clock)

out =  $\sim$ in;

At every clock transition from HIGH to LOW, the output becomes the inverse of the input.

□ The **wait** statement, which operates like a combination of a **while** loop and an *event* control:

```

eg. wait (reset) out = 0;

```

Suspend the process until the 'reset' signal is HIGH. When the reset signal does eventually go HIGH, the output signal is forced to zero.

## 4.5.4 Design Example: Behavioural Representation

```

module RS_FF(set, reset, Q);

(1)

input set, reset;

(2)

(3)

output Q;

req O;

(4)

initial

(5)

0 = 0;

(6)

always @ (set or reset)

(7)

case ({set, reset})

(8)

2`b10: #10 0 = 1;

(9)

2'b01: #10 Q = 0;

(10)

2'b11: begin

(11)

$display("RS_FF: SET and RESET active");

(12)

#10 \ Q = x;

(13)

end

(14)

(15)

endcase

endmodule

(16)

```

Again the module definition is enclosed in the **module** and **endmodule** keywords and, as in the structural representation, the ports and port types are declared in lines 2 and 3.

Line 4 declares a register with the same name as the output, Q, which will (implicitly) drive the output. Any value assigned to Q will be stored in the register and any value held in the register will be propagated to the output port. Registers are an abstraction of storage devices found in digital systems. Single-bit registers (like Q in the example) are termed scalar; multiple-bit registers are termed vector (eg. addr[31:0] is a 32 bit register).

The **initial** statement in line 5 is executed only once at the commencement of the simulation. This provides a mechanism for initialising the output value.

The **always** statement in line 7 is used to provide the dynamic functionality of the module. **always** @ (set or reset) indicates that the following statements should be executed whenever there is a change to one of the specified signals, i.e. the inputs. The **case** statement on the following line provides a decision capability based on the values of the SET and RESET inputs. Line 9 means that Q will be set HIGH, if the values of the SET and RESET inputs, when concatenated together ({set, reset}), match the 2-bit Boolean value 10 (2'b10). Basically, if the SET input is HIGH and the RESET input is LOW, then the output (register) Q will be set. Similarly, in line 10, if the SET input is LOW and the RESET input is HIGH, the output is driven LOW (reset).

Lines 11 to 14 indicate an important feature of the Verilog behavioural language, namely the ability to report diagnostic messages to the logic circuit designer while the simulation is running. As mentioned in the introduction to the design example, the SET and RESET inputs should never be active simultaneously. If this condition is detected, at line 11, the compound statements (enclosed in the **begin** and **end** keywords) on lines 12 and 13 are executed. An appropriate error message is displayed and the output value is set to undefined (x).

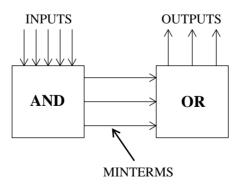

#### 4.5.5 Programmable Logic Arrays

Verilog allows the modelling of both a synchronous and an asynchronous programmable logic array (PLA). The synchronous form allows the designer to control the simulation time at which the array will evaluate the inputs and update the outputs. For the asynchronous type, evaluation is performed automatically whenever an input term changes value.

PLAs are modelled using 2 orthogonal planes:

The logic equations of the separate planes are defined by loading individual data files containing the associated bit patterns.

## 4.6 Verilog Simulator

The Verilog description of the system may be simulated using a digital logic simulator. This is a software tool that allows many design process tasks to be carried out without the various costs involved in constructing a hardware prototype. These design activities may include [Russ85]:

- **G** Functional Verification.

- □ Identification of design errors.

- Determination of the feasibility of new design ideas.

- **D** Timing Analysis

- □ Evaluation of several approaches to a design problem.

The simulator exercises the system model by applying external input signal stimuli. Any generated register or gate output signal changes are then propagated to other gate and module inputs. The main characteristic of the simulator is the ability to manage the concept of <u>time</u>; causing the changed signal values to appear at some specified time in the future. These predicted signal changes are typically stored in a time-ordered event queue.

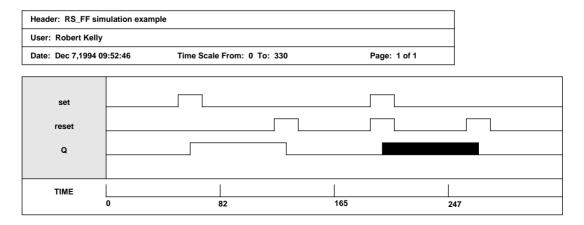

The RS flip-flop behavioural representation given in Section 4.5.4 is now used as an example to demonstrate the Verilog simulator operation.

In the top-level simulation test file (shown overleaf) the flip-flop module is instantiated (**RS\_FF**) with the instantiation name, f1. The input signal names are *set* and *reset*, and the output signal name is Q. In the first **initial** statement block, the input stimulus sequence is specified. In the second **initial** statement block, the required waveform output display is configured using the **\$gr\_waves**() system task.

```

`timescale 1ps /1ps

module test();

reg set, reset;

wire Q;

RS_FF

f1

(set, reset, Q);

initial

begin

set = 0; reset = 0;

#50 set = 1; #20 set = 0;

#50 \text{ reset} = 1; #20 \text{ reset} = 0;

#50 set = 1; reset = 1;

#20 set = 0; reset = 0;

#50 reset = 1; #20 reset = 0;

end

initial begin

$unfreeze_waves;

$ps_waves("waves.ps", "RS_FF simulation example", 0, 330);

#1 $finish;

end

endmodule

```

The console output text generated during the simulation execution is given below. Note the warning message displayed when the set and reset signals are simultaneously active:

> VERILOG-XL 1.7 Jan 20, 1995 09:27:16 Compiling source file "test.v" GRAPHICS 4.2.2 Thu May 27 23:28:23 PDT 1993 (cds2082) Highest level modules: test RS\_FF: SET and RESET active @ time=190 L29 "test.v": \$stop at simulation time 340 Type ? for help Cl > . L32 "test.v": \$finish at simulation time 341 114 simulation events End of VERILOG-XL 1.7 Jan 20, 1995 09:27:37

The graphical display waveforms can also be directed (using the **\$ps\_waves(**) system task) to a postscript file, which is shown below:

# 5. Multi-Level Differential Current Mode Logic

## 5.1 Introduction to Logic Families

Integrated circuit technology has developed dramatically over the past few decades, both in terms of gate switching speed and sophisticated circuit design, as a result of fabrication process enhancements and shrinking minimum geometries.

The nature of the semiconductor product market tends to segment customers into two groups: performance-oriented users who seek leading-edge performance technology at virtually any cost, and cost-sensitive users who need the best performance available at a given price. Since semiconductor economies depend heavily on a volume market, it is the more numerous cost-sensitive users who tend to drive the development of main-stream semiconductor technology [John91].

Early integrated transistors were **bipolar**, since these were much easier to fabricate. This fact led to the market success of bipolar transistor logic families (DTL, RTL through to TTL) during the early years of IC development. Eventually, the development of the planar process led to the introduction of **MOS** logic families. Initially, because of the more sophisticated processing requirements of CMOS, NMOS logic dominated. However, as chip sizes increased, power consumption problems emerged and the additional complexity in producing CMOS (the lowest power MOS technology) circuits was justified. CMOS technology has now advanced to become the dominant VLSI technology [West89].

When considering the merits of the various logic families several characteristics are examined:

Transistor switching speed - which translates into logic gate delay.

Noise immunity - a measure of the circuit's resilience to EMI.

Silicon layout size - the degree of integration possible on a given chip size.

Power dissipation - specialist techniques are required for high power circuits.

Fan-Out - the drive capability of the logic gates.

Except for the inability to operate at very high switching speeds, CMOS performs very well when judged against these criteria and as a result currently holds an unassailable advantage in the low and medium frequency ranges of the digital logic market.

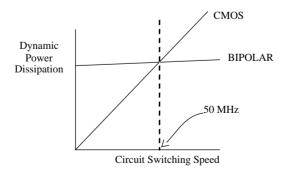

At low frequencies, CMOS dissipates considerably less power than bipolar circuits because of its virtually zero *static* power consumption brought about by its low leakage current.

However, as the operating frequency rises, the *dynamic* power dissipation of CMOS becomes the dominant factor up to a point where bipolar technologies actually dissipate less power. The power/speed trade-off point between bipolar and CMOS logic families was claimed to be around 50MHz in 1988 [GPS88]. However, with the continuing enhancements of process technologies (particularly with regard to CMOS) the trade-off figure may currently be higher.

Figure 9 : Dynamic Power Dissipation.

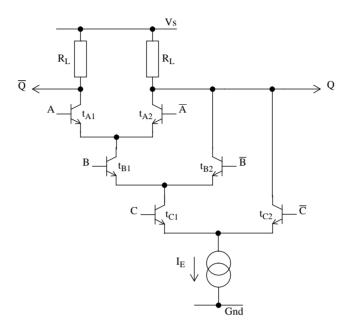

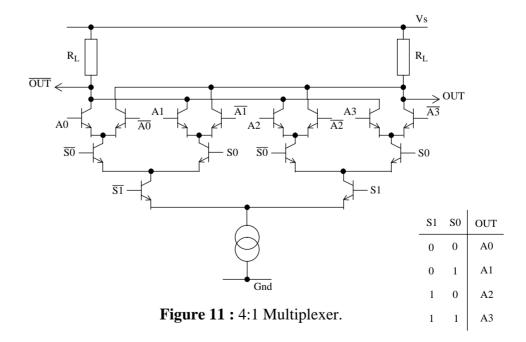

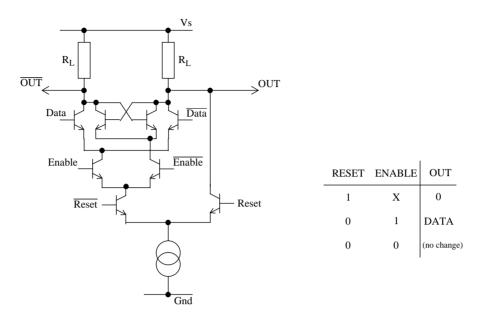

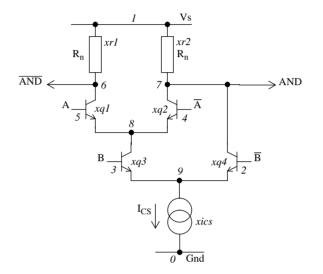

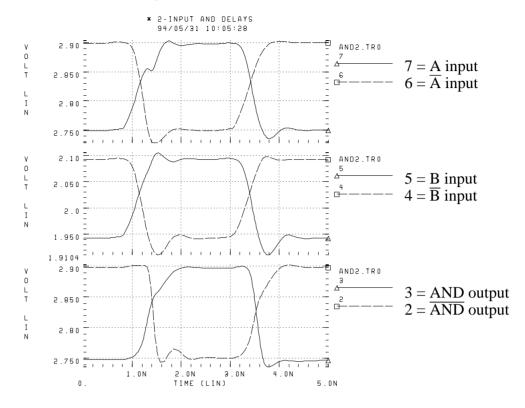

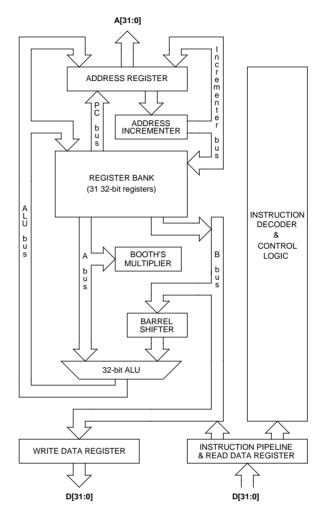

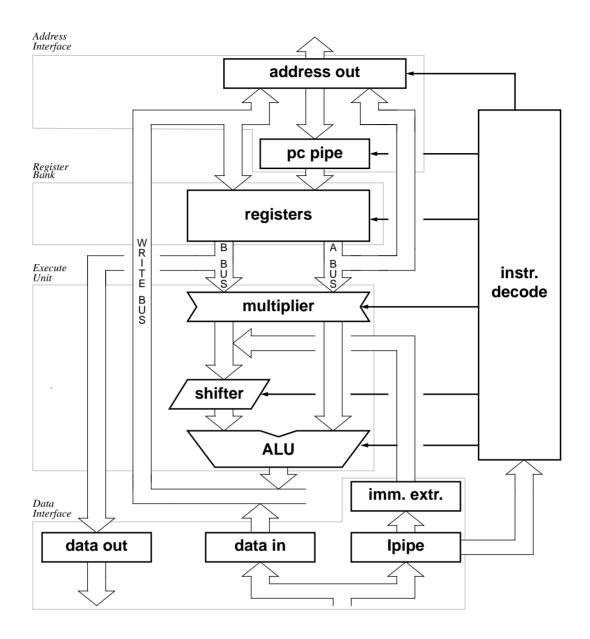

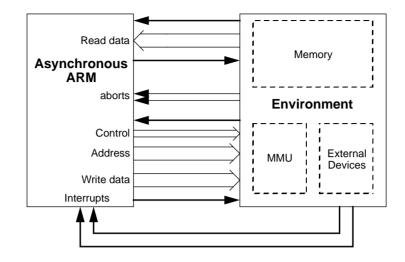

Emitter-Coupled Logic (ECL) operates by "steering current" through a differential ("long-tailed") pair of switching bipolar transistors which are coupled through an emitter resistor. ECL is an extremely fast logic family since it is non-saturating and keeps the logic signal swings relatively small (around 0.8V).