# Plasticity in large-scale neuromorphic models of the neocortex

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

IN THE FACULTY OF SCIENCE AND ENGINEERING.

2016

James Courtney Knight

School of Computer Science

### **Contents**

| Al | bstrac      | et                                      | 15 |  |

|----|-------------|-----------------------------------------|----|--|

| De | Declaration |                                         |    |  |

| Co | opyrią      | ght                                     | 19 |  |

| A  | cknov       | vledgements                             | 21 |  |

| 1  | Intr        | roduction                               | 23 |  |

|    | 1.1         | Publications                            | 26 |  |

|    | 1.2         | Contributions                           | 27 |  |

| 2  | Neu         | ral systems                             | 29 |  |

|    | 2.1         | Neurons                                 | 29 |  |

|    | 2.2         | The Neocortex                           | 33 |  |

| 3  | Mod         | delling Neural Systems                  | 37 |  |

|    | 3.1         | Neural modelling                        | 37 |  |

|    |             | 3.1.1 Point neuron models               | 38 |  |

|    |             | 3.1.2 Multi-compartmental neural models | 45 |  |

|    |             | 3.1.3 Synaptic input                    | 45 |  |

|    | 3.2         | Software simulation                     | 46 |  |

|   | 3.3  | GPU simulation                               | 48        |

|---|------|----------------------------------------------|-----------|

|   | 3.4  | Neuromorphic hardware                        | 49        |

|   | 3.5  | FPGA simulation                              | 50        |

|   | 3.6  | PyNN                                         | 52        |

|   | 3.7  | SpiNNaker                                    | 52        |

|   |      | 3.7.1 Hardware                               | 53        |

|   |      | 3.7.2 Spiking neural network simulation      | 55        |

|   |      | 3.7.3 Performance                            | 58        |

|   | G •1 |                                              | <b>~1</b> |

| 4 | Spik | te-timing dependent plasticity               | 61        |

|   | 4.1  | Spike-timing dependent plasticity (STDP)     | 63        |

|   |      | 4.1.1 Trace based models                     | 65        |

|   | 4.2  | Related work                                 | 71        |

|   | 4.3  | Implementation                               | 75        |

|   |      | 4.3.1 Postsynaptic history storage           | 75        |

|   |      | 4.3.2 Fixed-point representation             | 77        |

|   |      | 4.3.3 Algorithm                              | 79        |

|   | 4.4  | Performance                                  | 85        |

|   | 4.5  | Inhibitory plasticity in cortical networks   | 86        |

|   | 4.6  | The effect of weight dependencies            | 90        |

|   | 4.7  | Conclusions                                  | 93        |

| 5 | Dov  | esian Confidence Propagation Neural Networks | 95        |

| 3 | Баус | • 0                                          | 93        |

|   | 5.1  | Background                                   | 96        |

|   | 5.2  | Implementation                               | 99        |

|   | 5.3  | Validating BCPNN learning on SpiNNaker       | 02        |

|   | 5.4  | Demonstrating probabilistic inference        | 05        |

|   | 5.5  | Learning temporal sequences using a simplified neocortical het- |     |

|---|------|-----------------------------------------------------------------|-----|

|   |      | eroassociative memory model                                     | 107 |

|   | 5.6  | Conclusions                                                     | 117 |

| 6 | Syna | apse-centric simulation                                         | 119 |

|   | 6.1  | Analysis                                                        | 120 |

|   | 6.2  | Related work                                                    | 124 |

|   | 6.3  | Implementation                                                  | 125 |

|   | 6.4  | Static synaptic processing performance                          | 131 |

|   | 6.5  | Plastic synaptic processing performance                         | 137 |

|   | 6.6  | Conclusions                                                     | 142 |

| 7 | Con  | clusions                                                        | 145 |

|   | 7.1  | SpiNNaker                                                       | 148 |

|   | 7.2  | Models of the neocortey                                         | 150 |

This thesis contains 25722 words.

## **List of Figures**

| 2.1 | Structure of a pyramidal neuron                                     | 30 |

|-----|---------------------------------------------------------------------|----|

| 2.2 | A spike                                                             | 31 |

| 2.3 | Neocortical columnar connectivity                                   | 34 |

| 2.4 | Flow of information between layers of the neocortex                 | 36 |

| 3.1 | Response of a LIF neuron to a constant input current                | 42 |

| 3.2 | Response of an Izhikevich neuron to a constant input current        | 43 |

| 3.3 | The basic architecture of a SpiNNaker chip                          | 54 |

| 3.4 | Standard mapping of a neural network to SpiNNaker                   | 56 |

| 3.5 | Unpacking a sparse synaptic row                                     | 57 |

| 3.6 | Performance of a SpiNNaker core                                     | 58 |

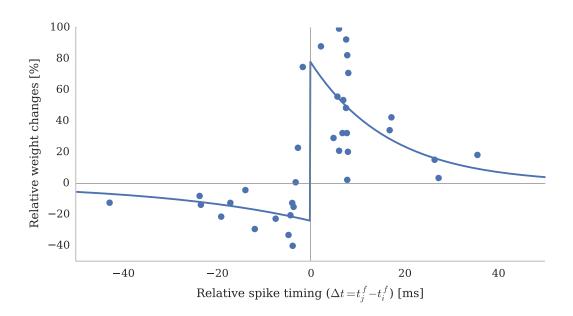

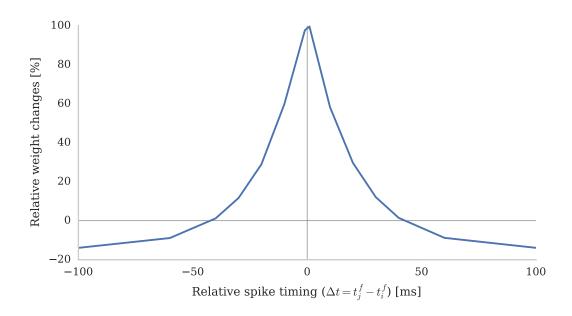

| 4.1 | Excitatory STDP curve                                               | 64 |

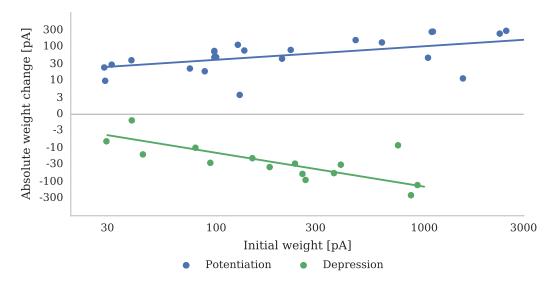

| 4.2 | Absolute change in synaptic efficacy after 60 spike pairs           | 64 |

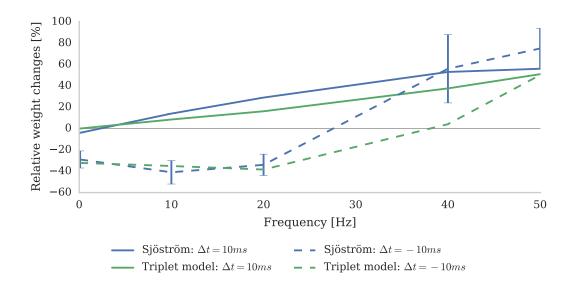

| 4.3 | Failure of pair-based STDP to reproduce frequency effects           | 65 |

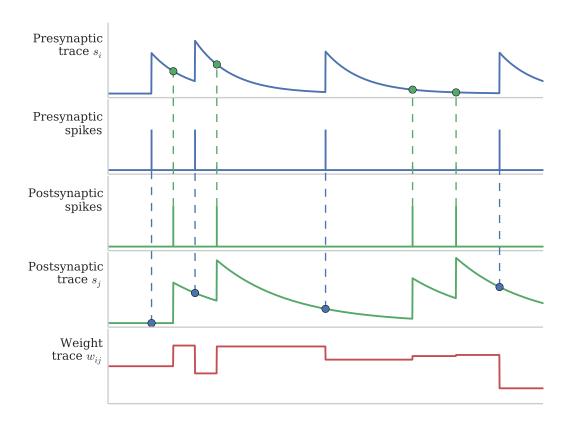

| 4.4 | Calculation of weight updates using pair-based STDP traces          | 66 |

| 4.5 | Inhibitory STDP curve                                               | 68 |

| 4.6 | Triplet rule matching frequency effects seen in experimental data . | 69 |

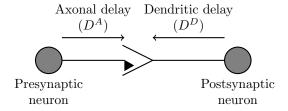

| 4.7 | The dendritic and axonal components of synaptic delay               | 71 |

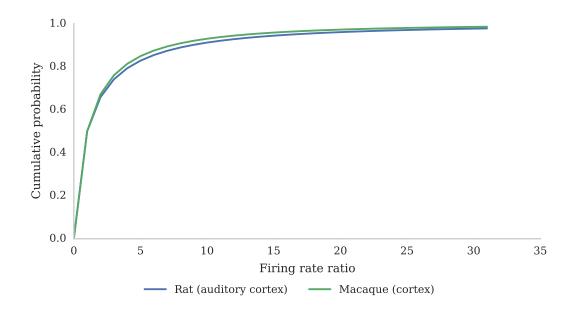

| 4.8 | Ratio distributions of cortical firing rates                        | 76 |

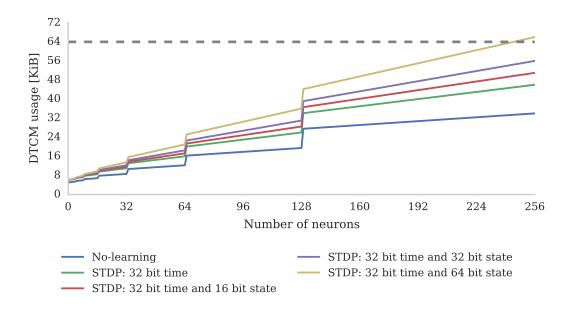

| 4.9 | DTCM memory usage of STDP event storage schemes                     | 77 |

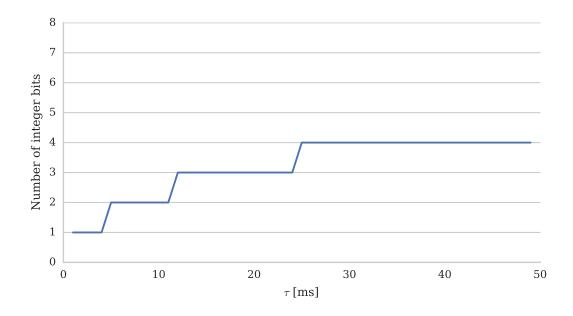

| 4.10 | Number of integer bits required to represent traces                | 79  |

|------|--------------------------------------------------------------------|-----|

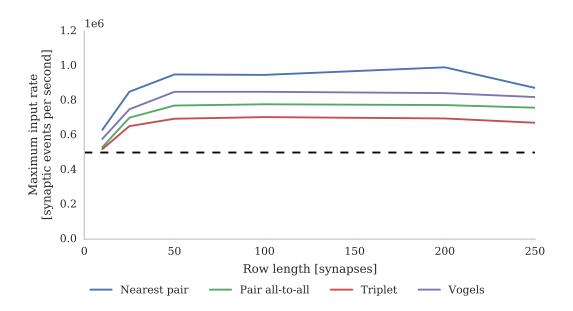

| 4.11 | Performance of a SpiNNaker core with STDP synapses                 | 83  |

| 4.12 | Performance of a SpiNNaker core with different STDP rules          | 84  |

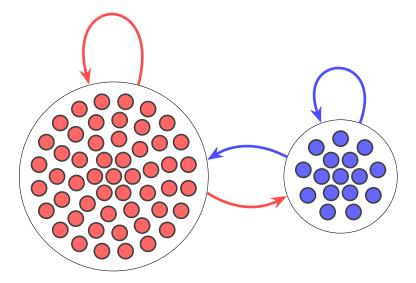

| 4.13 | A balanced random network                                          | 87  |

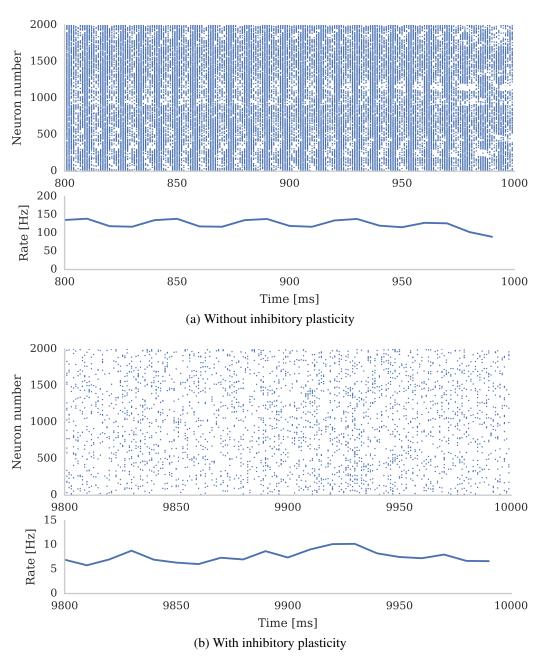

| 4.14 | The effect of inhibitory plasticity on a balanced random network . | 89  |

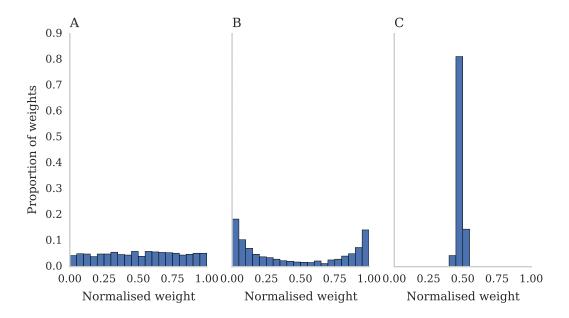

| 4.15 | Distributions of learnt synaptic weights                           | 92  |

| 5.1  | A naïve Bayesian classifier                                        | 97  |

| 5.2  | Spike-based BCPNN estimates rate-based BCPNN                       | 103 |

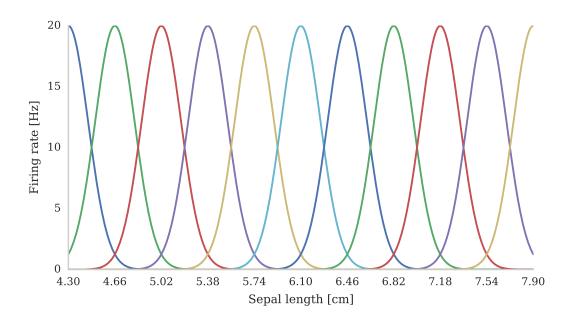

| 5.3  | An example of a set of Gaussian component functions                | 106 |

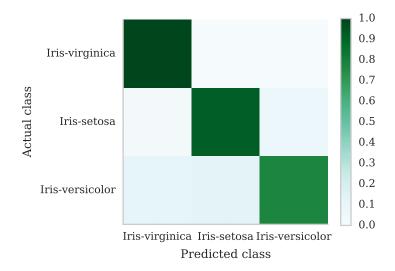

| 5.4  | Confusion matrix from classification of Iris dataset               | 107 |

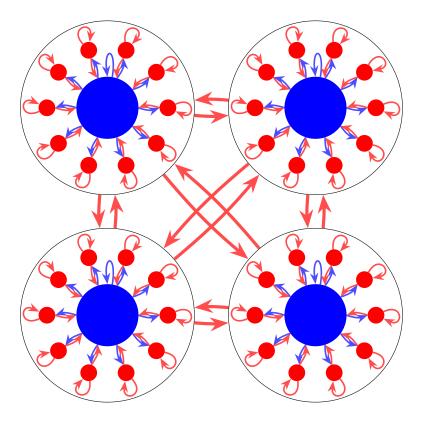

| 5.5  | Simplified neocortical architecture                                | 108 |

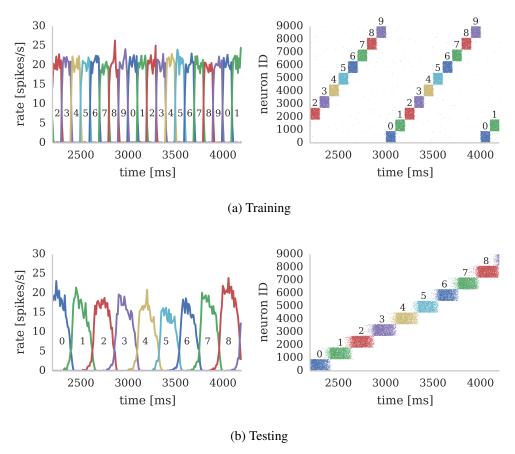

| 5.6  | Spiking activity during training and testing of temporal sequences | 111 |

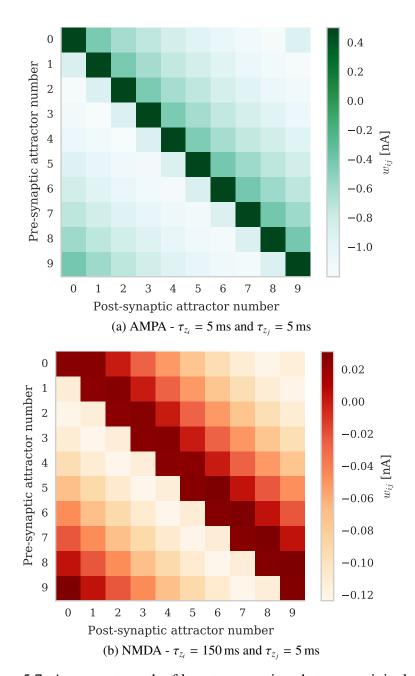

| 5.7  | Average strength of learnt connections between minicolumns         | 112 |

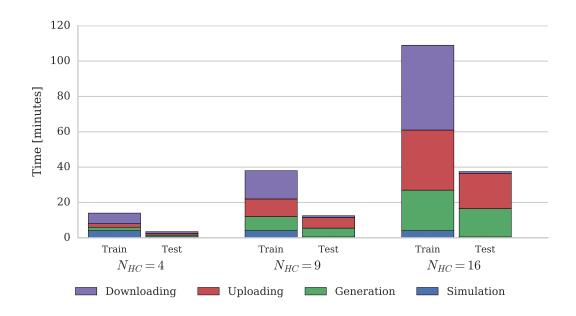

| 5.8  | Total simulation time on SpiNNaker                                 | 113 |

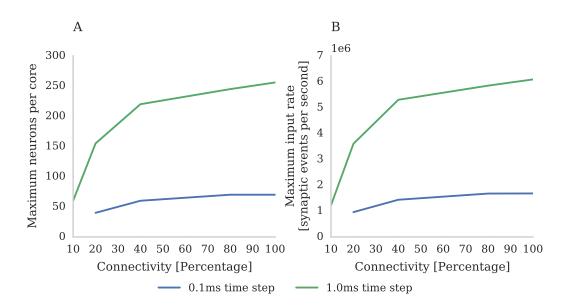

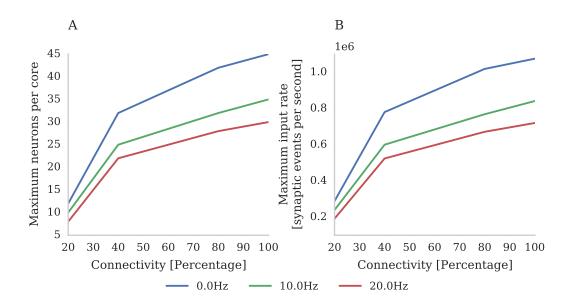

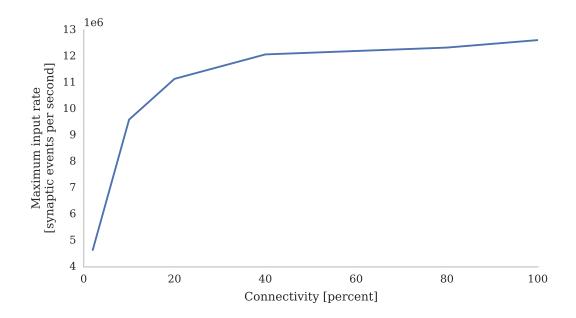

| 6.1  | Performance of a SpiNNaker core with fixed connectivity            | 122 |

| 6.2  | Performance of a SpiNNaker core with fixed STDP connectivity .     | 123 |

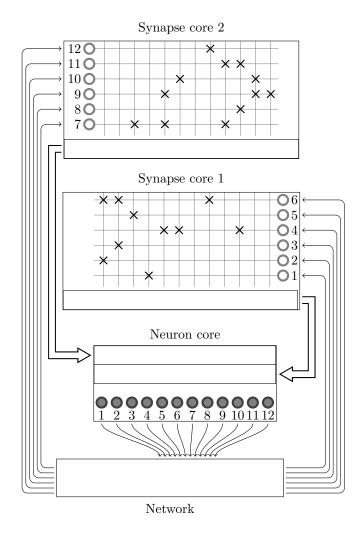

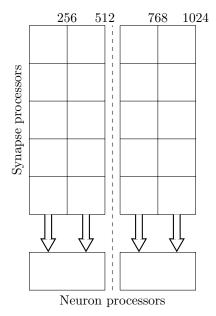

| 6.3  | Synapse-centric mapping of a neural network to SpiNNaker           | 127 |

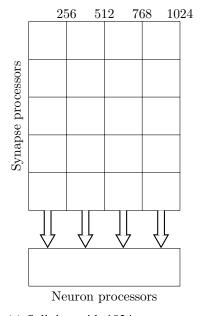

| 6.4  | Limitations on synapse-centric splitting of neurons and synapses . | 129 |

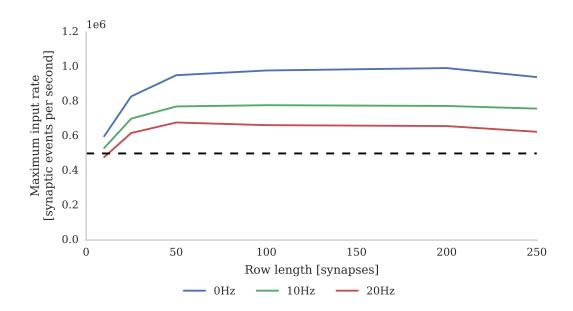

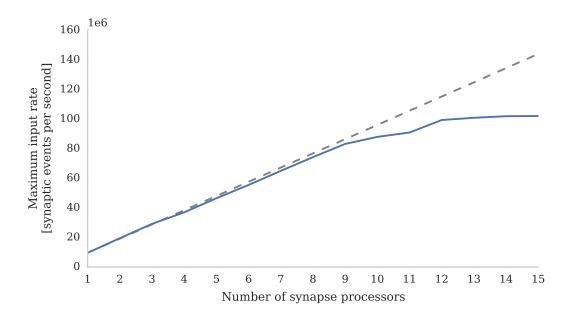

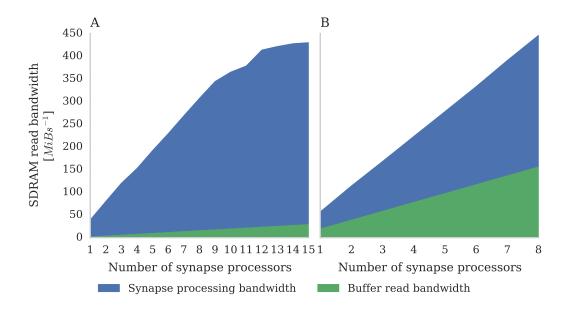

| 6.5  | Performance of a static synapse processor                          | 131 |

| 6.6  | Distribution of neurons amongst cores                              | 132 |

| 6.7  | Performance of a SpiNNaker chip                                    | 134 |

| 6.8  | External memory read bandwidth used by a SpiNNaker chip            | 135 |

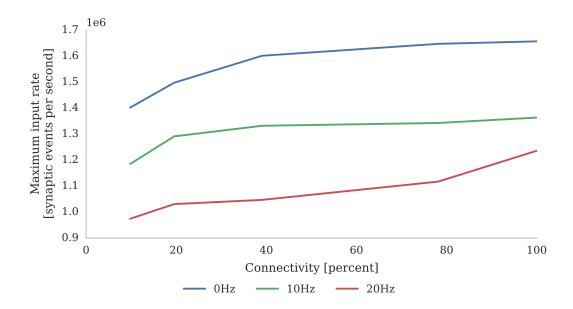

| 6.9  | Performance of an STDP synapse processor                           | 139 |

| 7.1  | SpiNNaker card frame                                               | 147 |

|      | 5 cabinet SniNNaker system                                         |     |

|      |                                                                    |     |

### **List of Tables**

| 3.1 | Model description of the benchmark network                     | 59  |

|-----|----------------------------------------------------------------|-----|

| 4.1 | Performance models of different STDP rules                     | 86  |

| 4.2 | Model description of the inhibitory plasticity network         | 88  |

| 4.3 | Model description of the synaptic weight distribution network  | 91  |

| 5.1 | Model description of the BCPNN validation network              | 104 |

| 5.2 | Comparison of Cray XC-30 and SpiNNaker simulations             | 114 |

| 6.1 | SpiNNaker simulations of the Vogels Abbott benchmark networks  | 138 |

| 6.2 | SpiNNaker simulations of the BCPNN modular attractor network . | 142 |

| 7.1 | Estimated requirements for simulation of mouse neocortex       | 147 |

### **List of Acronyms**

- **AMPA** is the name of a family of receptors which Glutamate a neurotransmitter released into the synaptic cleft by excitatory neurons binds onto causing the opening of fast-acting ion channels.

- **ANN** Artificial Neural Networks are computational models which inspired by the biological brain consist of large networks of neural units and can be used to solve machine learning problems.

- **ASIC** Application-Specific Integrated Circuits are chips customised for a particular use (unlike FPGAs which can be reprogrammed).

- **BCPNN** Bayesian Confidence Propagation Neural Network.

- **CPU** Central Processing Units are the electrical circuits at the heart of almost all computer systems which carries out the instructions specified by a computer program.

- **DMA** Direct Memory Access is a feature of many computer architectures which allows hardware subsystems to access memory directly rather than going through the CPU. This can improve overall system performance by freeing up the CPU for other things.

- **DTCM** Data Tightly-Coupled Memory is located on the processor die and therefore provides very low-latency, deterministic access to critical data.

- **fMRI** Functional Magnetic Resonance Imaging is a non-invasive imaging technique which uses a strong magnetic field and radio waves to measure blood flow in the brain and hence detect areas of activity.

- **FPGA** Field-Programmable Gate Arrays are chips containing a large number of programmable logic blocks whose function and the wiring connecting them can be configured after manufacturing, typically using a Hardware Description Language.

- **GABA** is the name of both a neurotransmitter released into the synaptic cleft by inhibitory neurons and of a family of receptors that these neurotransmitters bind onto.

- **GPU** Graphics Processing Units are specialised electronic circuits included in many types of computer which were historically designed to accelerate the rendering of 2D and 3D graphics. However, more recently, GPUs' highly-parallel architectures have been employed to accelerate a wide range of algorithms.

- **HPC** High-Performance Computing generally refers to the distribution of large, complex problems across parallel computer systems such as clusters or supercomputers so they can be run reliably and quickly.

- Hz Hertz are a unit of frequency defined as one cycle per second. In digital electronics Hz are used to measure clock speed. Additionally, in neuroscience,

Hz are often used to measure the expected number of events a Poisson processes might be expected to emit every second.

- **ISI** Interspike Intervals are the times between successive spikes.

- **ITCM** Instruction Tightly-Coupled Memory is similar to DTCM but used to store instructions rather than data.

- **LIF** Leaky integrate-and-fire is a simple spiking neuron model, described in more detail in section 3.1.1.

- **LUT** Lookup tables are arrays containing the pre-calculated results of evaluating a function which can subsequently be used at runtime rather than evaluating the function.

- **NMDA** is, like AMPA, the name of a family of receptors which Glutamate binds onto. However, unlike the ion channels which open in response to AMPA binding, the ion channels opened by NMDA binding are not only slower acting but also require a baseline level of activation.

- **NoC** Network-on-Chip is a term used for packet-based network technologies used to connect together multiple cores, caches etc in a modern CPU (rather than using the type of busses seen in older architectures).

- **ODE** Ordinary Differential Equations contain one of more functions of a *single* independent variable and its derivatives (unlike a Partial Differential Equation which may contain functions of multiple independent variables).

- **SDRAM** Synchronous Dynamic Random Access Memory is a generic name for various types of volatile memory (its contents is lost when the computer is turned off) which are synchronised to the CPU clock.

- **STDP** Spike-timing dependent plasticity is a hypothesis as to how the efficacy of connections between biological neurons (known as synapses) based on the activity of the neurons. STDP is discussed in detail in chapter 4.

- **TLU** Threshold Logic Units were an early computation model of neurons, described in more detail in section 3.1.1.

**WTA** Winner-Take-All is a computational principle applied to Artificial Neural Networks by which output neurons mutually inhibit each other while recurrently exciting themselves. This results in only the output neuron with the highest activity remaining active.

#### **Abstract**

PLASTICITY IN LARGE-SCALE NEUROMORPHIC MODELS OF THE NEOCORTEX

James Courtney Knight

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy, 2016

The neocortex is the most recently evolved part of the mammalian brain and enables the intelligent, adaptable behaviour that has allowed mammals to conquer much of planet earth. The human neocortex consists of a thin sheet of neural tissue containing approximately  $20 \times 10^9$  neurons. These neurons are connected by a dense network of highly plastic synapses whose efficacy and structure constantly change in response to internal and external stimuli. Understanding exactly how we perceive the world, plan our actions and use language, using this computational substrate, is one of the grand challenges of computing research. One of the ways to address this challenge is to build and simulate neural systems, an approach neuromorphic systems such as SpiNNaker are designed to enable.

The basic computational unit of a SpiNNaker system is a general-purpose ARM processor, which allows it to be programmed to simulate a wide variety of neuron and synapse models. This flexibility is particularly valuable in the study of synaptic plasticity, which has been described using a plethora of models. In this thesis I present a new SpiNNaker synaptic plasticity implementation and, using this, develop a neocortically-inspired model of temporal sequence learning consisting of  $2 \times 10^4$  neurons and  $5.1 \times 10^7$  plastic synapses: the largest plastic neural network ever to be simulated on neuromorphic hardware. I then identify several problems that occur when using existing approaches to simulate such models on SpiNNaker before presenting a new, more flexible approach. This new approach not only solves many of these problems but also suggests directions for architectural improvements in future neuromorphic systems.

### **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

### **Copyright**

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses

### Acknowledgements

Firstly I would like to thank Marli Roode. Many years ago, outside an East London pub she convinced me that I should quit my job and start a masters degrees and, over subsequent years, she has continued to inject entropy into my life.

For making this plan a reality I would like to thank my parents who have been nothing but supportive of this, somewhat drastic, change in life direction; Simon Moore who first placed the fanciful ideas of neuromorphic engineering in my head; and Steve Furber who, from our first email conversation onwards, has offered invaluable advice, support and just the correct amount of rope to hang myself in all number of interesting ways.

Since the first day I sat down next to them in IT302, Jonathan Heathcote and Andrew Mundy have been great lunch buddies, willing readers, stoic providers of Linux support and great friends to travel the world with. I would also like to thank Jim Garside for being such a welcoming force in the APT group – my PhD would have been nowhere near as much fun without his organisation of trips to various pubs and hills.

Finally I would like to thank the Engineering and Physical Sciences Research Council (EPSRC) and the President's Doctoral Scholar Award for financially supporting me during my throughout my PhD.

### Chapter 1

#### Introduction

The neocortex is the distinguishing feature of the mammalian brain and enables mammals to build an internal model of the ever-changing world, predict its future and adapt to it. If we could understand the operation of the neocortex we might, one day, be able to construct intelligent machines capable of solving problems currently only human beings are capable of solving.

However, the neocortex is one of the most complex systems we know of – in a human consisting of around  $20 \times 10^9$  neurons connected by  $150 \times 10^{12}$  synaptic connections [1]. In chapter 2 I give a brief overview of our current understanding of the function of the neocortex. However, furthering this knowledge through experiments on biological tissue alone is extremely difficult. Non-intrusive techniques such as functional magnetic resonance imaging (fMRI) provide only very limited temporal and spatial resolution and, while the number of neurons which can be simultaneously recorded using implanted electrodes is growing [2], it is currently limited to only a few hundred.

An alternative research direction is to build models of the brain and experiment on simulations of these models instead. Simulations not only allow us to fully control the input to the model being simulated but also to fully observe its outputs – both impossible within the brain of a living animal. The electrophysiological behaviour of individual neurons is now relatively well understood and several large scale projects are underway [3, 4] to build "connectomes" which can be thought of as wiring diagrams of the brain. While the task of simulating models at this scale is formidable, the development of petaFLOP supercomputers means that it is becoming increasingly computationally tractable [5], albeit at the cost of megawatts. In chapter 3 I discuss the software that enables large cortical networks to be simulated on such machines and how alternative technologies such as graphics processing units (GPUs), field-programmable gate arrays (FPGAs) and neuromorphic hardware may provide less power-hungry alternatives.

SpiNNaker is a digital neuromorphic architecture designed specifically for simulating networks of up to  $1 \times 10^9$  neurons in real time – enough to simulate the brains of ten mice [6]. While the fundamental computational element of a SpiNNaker system is a general purpose ARM processor, SpiNNaker systems – inspired by the brain – can combine up to a million such densely connected processors each responsible for simulating up to 1000 neurons.

Whereas, in older brain areas neurons are hard-wired to perform specific tasks, the neocortex has a relatively homogeneous structure within which neurons are densely connected by highly plastic synapses. The efficacy and structure of these synapses constantly changes in response to stimuli, allowing the neocortex to perform a wide range of functions. However due to the sheer number of these synapses and their plasticity, simulating them is a particularly complex problem which previous SpiNNaker solutions have been incapable of addressing. I have developed a new SpiNNaker synaptic plasticity implementation which has lower algorithmic complexity than prior approaches and employs new low-level optimisations to better exploit the ARM instruction set. In chapter 4 I discuss this implementation in depth and show that, not only does it almost double the perfor-

mance of previous solutions, but it is also flexible enough to support a wide range of different plasticity rules.

Bayesian inference provides an intuitive model of how our brains internalise uncertainty about the outside world and, using the Bayesian Confidence Propagation Neural Network (BCPNN) plasticity rule [7], it can be approximated using spiking neurons. In chapter 5 I present the first SpiNNaker implementation of BCPNN. Using this and a simple model of the neocortex, I demonstrate one way in which the neocortex might be able to learn and replay sequences of neuronal activity. Lashley [8] suggested that mammals' behaviour is based on hierarchical sequences of actions and experimental evidence [9] has suggested that these sequences of actions are realised as sequences of neuronal activity. Therefore the ability of my neocortical model to learn such sequences is an important step towards building functional models of the neocortex. I simulate the neocortical model at scales of up to  $20 \times 10^3$  neurons and  $51.2 \times 10^6$  plastic synapses: the largest plastic neural network ever to be simulated on neuromorphic hardware. However, while running this network on SpiNNaker uses less than 3 % of the power required to do so using a Cray XC-30 supercomputer system, it reveals some issues with simulating large-scale neocortical models on SpiNNaker.

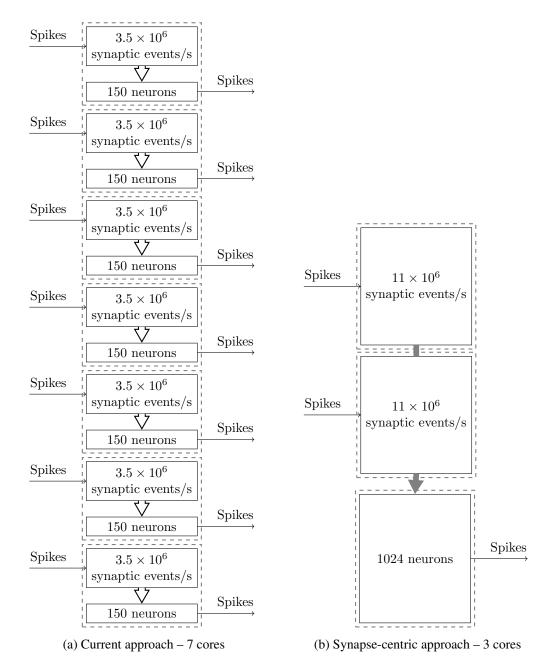

In chapter 6 I analyse these issues in more depth and find that, firstly, the performance of the current SpiNNaker neural simulator scales poorly when simulating neurons with the degree of connectivity seen in the neocortex. Secondly, I find that it would be difficult to extend the synaptic plasticity implementation developed in chapter 4 to support neurons whose input synapses have different synaptic plasticity rules. I solve both of these issues by developing a novel "synapsecentric" approach for mapping large-scale spiking neural networks to SpiNNaker where the simulation of neurons and synapses is distributed amongst different cores of a SpiNNaker chip. In a benchmark network where neurons receive in-

put from a biologically-plausible number of plastic synapses, this new approach quadruples the number of neurons that can be simulated on each SpiNNaker core. I also demonstrate that, using this new approach, the neocortical model developed in chapter 5 can be run in real time: double the speed that was previously achieved.

#### 1.1 Publications

Much of the work discussed in this thesis has previously been presented in the following publications:

J. C. Knight, P. J. Tully, B. A. Kaplan, A. Lansner, and S. B. Furber, "Large-scale simulations of plastic neural networks on neuromorphic hardware.," *Frontiers in Neuroanatomy*, vol. 10, no. April, p. 37, 2016, ISSN: 1662-5129 In this paper I first presented the SpiNNaker implementation of the BCPNN learning rule, the neocortical model of sequence learning and the comparisons with the supercomputer simulations discussed in chapter 5. This paper has been selected by the Faculty of Science and Engineering at the University of Manchester to be showcased as a "world leading paper".

J. Knight and S. Furber, "Synapse-centric mapping of cortical models to the SpiNNaker neuromorphic architecture," *Frontiers in Neuroscience*, vol. 10, p. 420, 2016, ISSN: 1662-453X In this paper I first presented the synapse-centric simulation approach discussed in chapter 6.

A. Mundy, J. Knight, T. C. Stewart, and S. Furber, "An efficient SpiN-Naker implementation of the Neural Engineering Framework," in *The 2015 International Joint Conference on Neural Networks (IJCNN)*, IEEE, 2015 I made modest contributions to this paper, primarily using the profiling tools devel-

oped for this thesis to analyse the performance of a novel SpiNNaker implementation of the Neural Engineering Framework (NEF) [13] developed by Andrew Mundy. This paper was nominated for the best paper award at the International Joint Conference on Neural Networks (IJCNN) 2015.

J. Knight, A. R. Voelker, A. Mundy, C. Eliasmith, and S. Furber, "Efficient SpiNNaker simulation of a heteroassociative memory using the neural engineering framework," in *The 2016 International Joint Conference on Neural Networks (IJCNN)*, 2016 This paper builds on the previous paper by investigating how two forms of synaptic plasticity [15, 16] can be incorporated into NEF models and used as the basis for large-scale heteroassociative memories which we demonstrated could be efficiently simulated on SpiNNaker. I presented this paper at IJCNN 2016 in Vancouver.

#### 1.2 Contributions

This thesis presents the following main contributions:

**Plasticity implementation** I develop a new synaptic plasticity implementation for SpiNNaker which is not only almost twice as fast as previous solutions, but is also a key component of the software developed for the Human Brain Project [17].

Bayesian Confidence Propagation Neural Networks BCPNN provides a means of approximating Bayesian inference using networks of spiking neurons. Not only do I implement the learning rule required to simulate such networks on SpiNNaker, but I also use it as the basis of the largest plastic neural network ever to be simulated on neuromorphic hardware.

**Synapse-centric simulation** I develop this entirely new means of simulating neural networks on SpiNNaker and demonstrate that it quadruples the number of neurons with biologically-plausible numbers of plastic synapses that can be simulated on a given SpiNNaker machine.

#### Chapter 2

#### **Neural systems**

To model the neocortex we need to understand the fundamental biological behaviour of both the neurons within it and of the circuits they form. In section 2.1 I present a brief background on how biological neurons communicate and process information and in section 2.2 I present evidence on the structure of the neocortex and theories on how this may enable it to perform high-level cognitive functions.

#### 2.1 Neurons

Like all animal cells, neurons consist of an impermeable cell membrane surrounding a nucleus, mitochondria and other organelles. However, neurons also have several specialised components which support electro-chemical computation and signalling. *Ion pumps* "pump" ions across the cell membrane at an approximately constant rate to maintain a "resting" potential difference between the cell's interior and the extracellular fluid which surrounds it. *Ion channels* also enable ions to cross the cell membrane but, unlike ion pumps, the rate at which ion channels transfer ions can be modulated by factors including the membrane potential and the concentration of various chemical messengers.

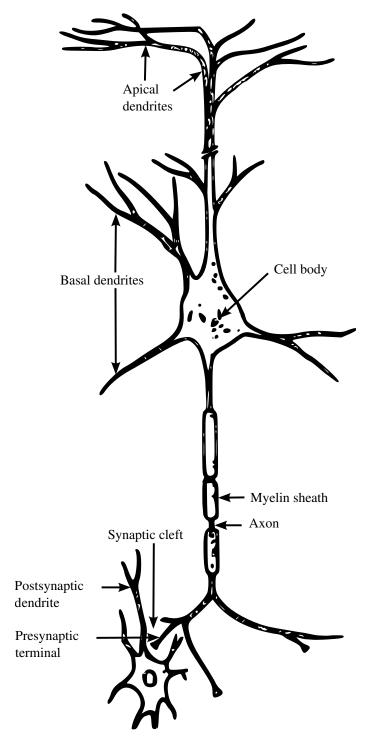

Figure 2.1: Structure of a pyramidal neuron. After [18].

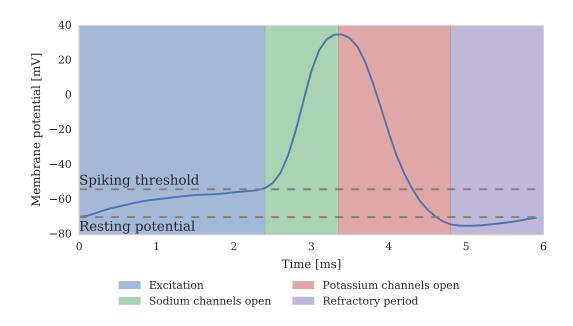

Figure 2.2: A spike. Dashed horizontal lines show the resting potential and the threshold at which sodium ion channels open.

Figure 2.1 shows the structure of a *pyramidal neuron* – one of the most common neuron types found in the neocortex. Changes in a neuron's membrane potential cause sodium and potassium ion channels to act together, generating *spikes*: the primary means of neuronal communication. When the membrane potential reaches a certain threshold, sodium ion channels open allowing positively charged sodium ions to rush into the neuron, rapidly increasing the membrane potential from around –70 mV to around 30 mV. This sudden increase in membrane potential causes potassium ion channels to open, allowing positively charged potassium ions to leave the neuron, and resulting in the stereotypical spike in membrane potential potential shown in figure 2.2. Spikes then propagate down the *axon* of the neuron as a wave of sodium and potassium ion channels open ahead of the spike. As the pyramidal neuron in figure 2.1 illustrates, axons can also be wrapped in a myelin sheath, through which spikes can propagate at much higher speeds. Be-

fore the neuron can spike again, ion pumps need to pump sodium ions out of the neuron and potassium ions back in, restoring the membrane potential to its resting level – a period known as the *refractory period*. To communicate spikes to other neurons connections known as *synapses* are formed at the *axon terminals*.

From the point-of-view of one of these synapses, the neuron from which spikes originate is known as the *presynaptic* neuron and the neuron which has made the synaptic connection is known as the *postsynaptic* neuron. In general spikes can have two effects on a postsynaptic neuron: excitatory spikes increase its membrane voltage and inhibitory spikes decrease it. Dale's law [19] states that a neuron cannot excite some of its postsynaptic targets and inhibit others. Therefore excitatory spikes are always emitted by excitatory neurons (such as the pyramidal neuron shown in figure 2.1) and inhibitory spikes are always emitted by inhibitory neurons. When a spike reaches an axon terminal, the increase in membrane potential causes calcium ion channels to open, drawing calcium ions into the neuron. The resultant increased calcium concentration inside the neuron causes neurotransmitters to be released into the *synaptic cleft* between the pre and postsynaptic neurons: primarily glutamate from excitatory neurons and GABA from inhibitory neurons. These neurotransmitters diffuse across the synaptic cleft and bind to receptors, causing a final class of ion channels to open on the postsynaptic neuron. The ion channels that open as result of glutamate binding allow current to flow into the neuron and those that open as a result of GABA binding allow current to flow out. Two important classes of ion channels that open in response to glutamate binding are known as AMPA and NMDA. AMPA ion channels open and close relatively quickly whereas NMDA ion channels not only open and close slower, but also require the neuron's membrane voltage to be elevated prior to activating. In section 5.5 I present a model which uses the different time constants of AMPA and NMDA synapses to learn features of temporal sequences at different time scales.

Synaptic connections can be made to almost any part of the neuron and how the position of these connections affects the integration of the input currents they supply is not fully understood. However, using the geometry of the neuron shown in figure 2.1 as an example, synaptic input applied directly to the cell body or to the nearby *basal dendrites* is likely to have more effect on spike generation than synaptic input applied to the *apical dendrites* further from the cell body [20]. There is also evidence that local computation occurs within dendritic branches [21] and that the interactions between NMDA ion channels and AMPA ion channels have an important role [22].

#### 2.2 The Neocortex

The neocortex is the most recent part of brain to evolve and consists of a sheet of neurons ranging in size from around 6 cm<sup>2</sup> in a rat to 2500 cm<sup>2</sup> in a human. While in older brain regions, specialised neurons and synaptic connections are "hardwired" to perform specific functions, the neocortex has a relatively homogeneous structure with highly plastic synaptic connections whose efficacy and structure constantly change in response to stimuli. This perhaps reflects the fact that, rather than performing a single function, much of the processing performed by the neocortex is learnt postnatally [23]. In fact, even in adulthood, the neocortex remains plastic enough to allow vision to be restored – after sufficient training – by projecting images from a camera onto a matrix of actuators attached to the skin [24].

The surface of neocortex is divided into areas responsible for processing visual, auditory and somatosensory stimuli; generating motor commands and performing higher-level cognitive functions. Within each of these areas there is then a hierarchy of *regions* connected together with both *feedforward* and *feedback* connections. Typically this hierarchy reflects an increasing level of information

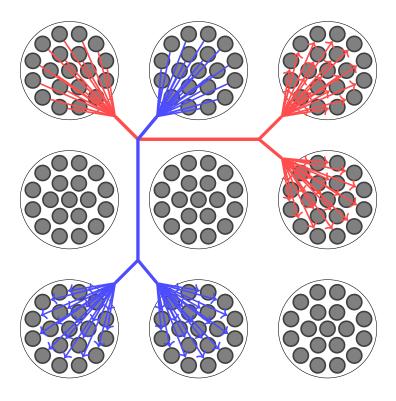

Figure 2.3: Neocortical columnar connectivity. Minicolumns (filled grey circles) arranged into 9 macrocolumns (large outlined circles) and connected with patchy connectivity.

abstraction within each region. For example the primary visual cortex – the lowest level of the visual cortex hierarchy – receives input relayed via the thalamus from the retina and responds to oriented line segments crossing the visual field [25] whereas the inferior temporal cortex – at the top level of the visual cortex hierarchy – has been shown to respond to high-level concepts such as human faces [26].

Each neocortical area is made up of a large number of *macrocolumns* with diameter in the range of 300 μm to 600 μm. Each of these macrocolumns consists of approximately 100 *minicolumns* bound together with short-range horizontal connections. Minicolumns are believed to be the basic functional unit of the neocortex with each one consisting of approximately 100 neurons, tuned to respond to the same stimuli [27, 28].

Across species and neocortical areas the size and structure of macrocolumns remain approximately constant – the neocortices of humans and higher primates simply have a larger number of macrocolumns than, for example, those of mice. The average number of synapses providing input to each cortical neuron also remains constant across species at around 8000 [1, 29, 30]. These properties are independent of the size of the neocortex because cortical long-range cortical connectivity follows the "patchy" structure illustrated in figure 2.3 [31–34]. The "fan-out" of each minicolumn varies between neocortical areas but, for example in the primary visual cortex, each minicolumn only connects to around 10 macrocolumns located within a radius of a few millimetres. The density of connections between individual neurons in the connected minicolumns varies widely but is always relatively sparse (recent measurements in the somatosensory cortex of rats [35] suggest that pyramidal neuron connectivity saturates at around 20%).

Hubel and Wiesel [25] provided the first experimental evidence of the role of macrocolumns in the primary visual cortex of Macaque monkeys. These macrocolumns apply what has become known as a winner-take-all (WTA) circuit to the output of the minicolumns which respond to the orientation of line segments. The WTA circuit inhibits the output of all of minicolumns in a macrocolumn aside from the one responding most strongly to the stimuli. While in higher cortical areas input cannot be directly manipulated, making it extremely difficult to perform equivalent experiments, Douglas and Martin [36] suggest that this WTA circuitry is fundamental to all neocortical areas.

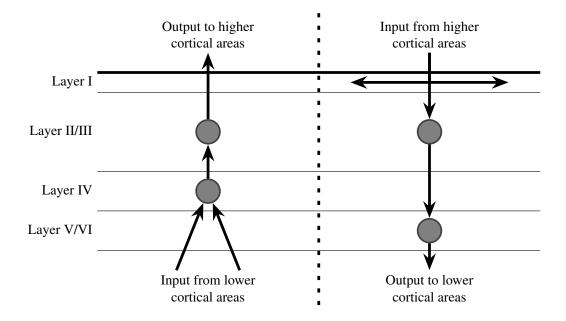

Perpendicularly to this columnar structure the neocortex is also divided into 6 layers which, as illustrated in figure 2.4, can be grouped as follows:

Layer I contains very few neurons and its role appears to be largely one of "scaf-folding" – a location where feedback synapses from higher cortical areas can make connections with the dendrites of neurons in layers II/III.

Figure 2.4: **Left**: upward and **Right**: downward flow of information between layers of the neocortex. Filled grey circles represent neurons taking part in the information flow.

Layer II/III are where associations between feedback and feedforward input are made; and fed forward to higher cortical areas and back via layers V/VI.

Layer IV is where feedforward input enters the macrocolumn from lower cortical areas and is passed to layers II/III.

Layer V/VI passes the feedback output from layers II/III on to the dendrites located in layer I of lower cortical areas.

However, even if we accept this cortical architecture, exactly how the brain uses this structure to implement high-level cognitive functions remains an open question.

# **Chapter 3**

# **Modelling Neural Systems**

Section 2.1 presented a high-level overview of the electrochemical behaviour of individual neurons and in section 3.1 I will discuss how this behaviour can be modelled at various levels of abstraction. In section 2.2 I went on to discuss how neurons in the neocortex are arranged in a highly-connected, three dimensional structure. This high degree of connectivity makes simulating large cortical networks particularly challenging and in sections 3.2 - 3.5 I will give an overview of some of the approaches that have been applied to this problem.

SpiNNaker is a digital neuromorphic architecture designed specifically for the simulation of large-scale neural networks and in section 3.7 I will discuss the SpiNNaker system and its performance characteristics in more depth.

# 3.1 Neural modelling

As figure 2.1 illustrates, biological neurons can have complex dendritic tree structures. However the classical view on their role, as described by Ramón y Cajal [37], is that:

"Dendrites exist solely to allow the cell to receive, and then transmit to the axon, the greatest variety of information from the most diverse sources."

From this assumption the entire neuron can be viewed as being somewhat analogous to a logic gate: gathering information from multiple sources and generating a single output in the soma (see figure 2.1). Models based on this assumption are known as *point neuron models* and in section 3.1.1 I present a brief overview of models of this type. In the remainder of this thesis I concentrate largely on simulating point neuron models. However it has been suggested that dendritic structure may play an important role in neurons' information processing functionality. Therefore in section 3.1.2 I briefly discuss how point neuron models can be extended to form *multi-compartmental models* that can be used to model neurons with more realistic dendritic structures.

#### 3.1.1 Point neuron models

#### **Binary models**

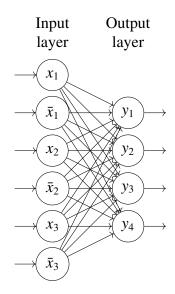

Coming from the logic gate analogy it is unsurprising that early computational models of neurons, such as the Threshold Logic Unit (TLU) developed by Mc-Culloch and Pitts [38], closely resemble logic gates. The TLU receives multiple binary inputs  $(x_i)$  and produces a single binary output (y) by applying a Heaviside step *activation function* to the sum of a bias term  $(\beta)$  and the inputs  $(x_i)$ , weighted with the weights  $(w_{ij})$ :

$$u = \beta + \sum_{i=1}^{n} w_i x_i$$

(3.1)

$$u = \beta + \sum_{i=1}^{n} w_{i} x_{i}$$

$$y = \begin{cases} 1 & \text{if } u \ge 0 \\ 0 & \text{if } u < 0 \end{cases}$$

(3.1)

This neuron model can be directly used to implement boolean AND and OR functions and, by building recurrent networks, where the output of some neurons fed back into others, it could be used to build simple memory systems.

#### Rate-based neuron models

The TLU model was subsequently generalised to use real valued inputs. In this case, the  $w_i$  and  $\beta$  parameters can be thought of as defining a plane through an n-dimensional input space, which defines a linear separation between two classes of input vectors. Neurons of this type have been used to build single layer artificial neural networks (ANNs) such as Perceptrons [39] which can be combined to form multi-layer networks capable of classifying patterns that are not linearly separable. To give these extra layers more computational power than is achievable by using a larger layer of linear neurons multi-layer networks typically use neurons that generate a real valued output based on a non-linear activation function. Furthermore to enable the use of the back-propagation algorithm [40] – a popular approach for training multi-layer ANNs – these activation functions are required to be differentiable. Therefore activation functions such as tanh or the sigmoid function [41] are common choices. In terms of modelling biological neurons this output can be thought of as representing the firing rate of the neuron.

#### Spiking neuron models

Although rate-based neuron models are mathematically convenient and the firing rates of neurons have been shown to encode stimuli [42] in many parts of the brain, both temporal [43] and spatial information [44] has also been shown to be encoded in the timings of individual spikes. To model these effects, more realistic spiking models must be used.

As discussed in section 2.1, neurons emit spikes when their membrane potential is rapidly depolarised by the opening of sodium ion channels before being immediately repolarised by the opening of potassium ion channels. The potential across an ion channel can be modelled using the following simple ODE:

$$C\frac{dV}{dt} = -g_{ion}(V - E_{ion}) \tag{3.3}$$

Where C is the membrane capacitance, V is the potential across the ion channel,  $G_{ion}$  is the conductance of the ion channel and  $E_{ion}$  is the channel's reversal potential. Hodgkin and Huxley [45] developed a neural model which combined the effect of 3 types of ion channel: a leak channel (L) with a constant conductance representing the action of the ion pumps and voltage-gated potassium (K) and sodium channels (Na):

$$C\frac{dV}{dt} = -g_K n (V - E_K) - g_{Na} m^3 h (V - E_{Na}) - g_L (V - E_L)$$

(3.4)

The voltage gating is achieved using the dimensionless n, m and h variables, each of which is modelled using a further differential equation:

$$\frac{dn}{dt} = \frac{n_{\infty}(V) - n}{\tau_n(V)} \qquad \frac{dm}{dt} = \frac{m_{\infty}(V) - m}{\tau_m(V)} \qquad \frac{dh}{dt} = \frac{h_{\infty}(V) - h}{\tau_h(V)}$$

(3.5)

Where  $n_{\infty}$ ,  $m_{\infty}$ ,  $h_{\infty}$ ,  $\tau_n$ ,  $\tau_m$  and  $\tau_h$  represent different, voltage-dependent functions.

Hodgkin-Huxley neurons, fitted to biological data, have been used for large-scale modelling [5], but are extremely computationally expensive to simulate and have a large number of parameters to configure. Therefore a common alternative approach is to model the subthreshold dynamics of the membrane voltage – up to the point at which the neuron emits a spike – using a simpler system and then artificially reset the membrane voltage to simulate rapid repolarisation. One of the simplest models of this type is the leaky integrate-and-fire (LIF) model whose subthreshold membrane voltage (V) is modelled using the following simple first-order ODE:

$$C\frac{dV}{dt} = -g_L(V - V_{rest}) + I_{app}$$

(3.6)

Where  $g_L$  and C represent the leak conductance of the membrane and its capacitance;  $V_{rest}$  represents the membrane's resting voltage and  $I_{app}$  represents the input current. In the absence of any input, V decays linearly with a time constant of  $\tau_m = \frac{C}{g_L}$ . However when V reaches a fixed threshold ( $V_{thresh}$ ) it is reset to  $V_{reset}$  and a spike is emitted. Additionally a timer can be started to prevent further input being integrated during the period in which a biological neuron would be in its refractory period. The LIF model has the advantage of being fast to compute and, as equation 3.6 has an algebraic solution, easy to analyse mathematically.

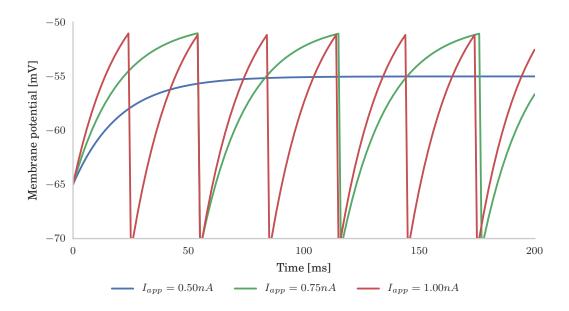

However, as figure 3.1 shows, the LIF model will always spike regularly when provided with a constant input current whereas cortical neurons have been shown

Figure 3.1: Response of a LIF neuron to a constant input current. Simulated using NEST 2.6 [46] with  $V_{thresh} = -51 \text{ mV}$ ,  $V_{reset} = V_{rest} = -70 \text{ mV}$ , C = 1 nF,  $g_L = 50 \, \text{nS}.$

to reproduce a wide range of spiking behaviours [47–49].

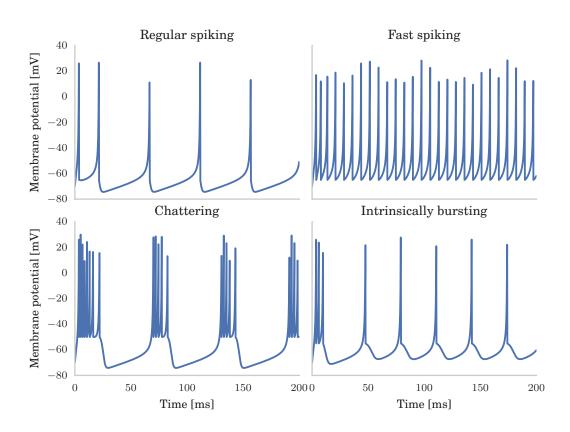

By modelling the subthreshold neural dynamics using a more complex two dimensional system Izhikevich [50] developed an integrate-and-fire neuron model which can replicate a much wider range of spiking behaviours while remaining fast to compute:

$$\frac{dV}{dt} = 0.04V^2 + 5V + 140 - u + I_{app}$$

$$\frac{du}{dt} = a(bV - u)$$

(3.7)

$$\frac{du}{dt} = a\left(bV - u\right) \tag{3.8}$$

Similarly to the LIF model, when V reaches a threshold, it is reset to a fixed value and u has an offset applied to it. The quadratic term of equation 3.7 enables the membrane voltage to rise in a faster, more realistic manner than that of the

Figure 3.2: Response of a Izhikevich neuron to a constant 10 pA input current. Simulated using NEST 2.6 [46] using parameters specified by Izhikevich [50].

LIF neuron during the period immediately before a spike. Additionally, the u state variable acts as a subthreshold adaptation mechanism – altering the firing rate of the neuron based on its past activity [51]. By using different values of the a, b, c and d parameters the Izhikevich neuron can reproduce the wide range of spiking behaviours illustrated in figure 3.2.

The adaptive exponential integrate-and-fire model (AdEx) [52] is another widely used neuron model and has been shown to accurately reproduce the behaviour of neurons modelled using the Hodgkin-Huxley equations. As with the Izhikevich model, the aEIF model is described by two coupled differential equations:

$$C\frac{dV}{dt} = -g_L(V - V_{rest}) + g_L \Delta_T \exp\left(\frac{V - V_{thresh}}{\Delta_T}\right) - w + I_{app}$$

(3.9)

$$\tau_w \frac{dw}{dt} = a(V - V_{rest}) - w \tag{3.10}$$

As with the LIF model,  $g_L$  and C represent the leak conductance of the membrane and its capacitance;  $V_{rest}$  represents the membrane's resting voltage;  $V_{thresh}$  the spiking threshold and;  $I_{app}$  the input current. The second w state variable plays the same role as u in the Izhikevich model – representing a subthreshold adaptation mechanism with a strength defined by a and a time constant of  $\tau_w$ . Finally  $\Delta_T$  defines the "sharpness" of the spiking threshold. The behaviour of the aEIF model at this threshold is somewhat different from that of the LIF and Izhikevich models as, when  $V \geq V_{thresh}$ , the exponential term causes the membrane to rapidly depolarise before it is artificially reset at a second, higher threshold V = 20 mV. At this point, similarly to the Izhikevich model, V is reset to  $V_{reset}$  and v is added to v (defining the strength of the spike-triggered adaptation).

In all of the integrate-and-fire neuron models discussed in this section I have represented the input to the neuron model as a single  $I_{app}$  term. While a constant

value of  $I_{app}$  can be used to perform the kind of simple experiments shown in figures 3.1 and 3.2, typically  $I_{app}$  is calculated from the conductances of the neuron's synapses using equation 3.3. Although synaptic conductance injection has been shown to better represent the behaviour of biological neurons [53], to make the model easier to analyse mathematically this additional non-linearity can be removed and synapses can be viewed as injecting current directly.

## 3.1.2 Multi-compartmental neural models

The point neuron models described in the previous section all assume that the membrane potential of a neuron is constant across its entire cell membrane. However, particularly when neurons have narrow sections such as those within the dendritic tree of the pyramidal neuron shown in figure 2.1, this may be a poor approximation. *Multi-compartmental models* address this by splitting the neuron into smaller *compartments* within which the membrane voltage is assumed to be constant. Each of these compartments can then be simulated using either a detailed Hodgkin-Huxley or a simpler integrate-and-fire model [54]. Compartments are then linked using ohmic channels allowing current to flow between neighbouring compartments [55, p. 217].

## 3.1.3 Synaptic input

As discussed in section 2.1, spike transmission between biological neurons is the result of a complex cascade of biological processes. Similarly to the Hodgkin-Huxley models of neurons discussed in section 3.1.1 highly detailed models of synaptic transmission have been developed [56] but, as with detailed neuron models, are costly to simulate. Therefore simpler models of the conductance of the postsynaptic ion channel are often employed.

The simplest models of ion channel conductance assume that a presynaptic spike at time  $t_0$  causes the ion channel to open immediately and its synaptic conductance  $(g_{syn})$  to increase immediately to  $\bar{g}_{syn}$  before exponentially decaying with time constant  $\tau$  as the neurotransmitters are reabsorbed and the ion channel closes:

$$g_{syn}(t) = \bar{g}_{syn} \exp\left(-\frac{t - t_0}{\tau}\right)$$

(3.11)

However, as the rise time of a real ion channel's conductance is finite, it is more realistic to describe this conductance using the difference of two exponentials:

$$g_{syn}(t) = \bar{g}_{syn}c\left(\exp\left(-\frac{t-t_0}{\tau_{decay}}\right) - \exp\left(-\frac{t-t_0}{\tau_{rise}}\right)\right)$$

(3.12)

Where c is a constant used to scale the peak amplitude to  $\bar{g}_{syn}$ ; and  $\tau_{rise}$  and  $\tau_{decay}$  are the time constants of the ion channel opening and closing respectively. In the special case where the peak synaptic conductance occurs at  $t = \tau$  this model can be simplified to an *alpha* function with a single time constant  $\tau$ :

$$g_{syn}(t) = \bar{g}_{syn} \frac{t - t_0}{\tau} \exp\left(1 - \frac{t - t_0}{\tau}\right)$$

(3.13)

## 3.2 Software simulation

In this section I will outline some strategies used to simulate spiking neural networks in software before briefly discussing a representative selection of the tools which use them. Clock-driven simulation algorithms, where time is advanced in discrete steps (typically 1 ms or 0.1 ms), are amongst the most common. In a typical clock-driven simulation algorithm the state of each neuron is updated every time step using some form of numerical integration technique such as Runge-Kutta [57]. However some models, such as simple forms of the LIF neuron discussed in section 3.1.1, are linear so can be solved by simply multiplying the previous state by a constant matrix [58]. After updating each neuron in this manner its spike threshold condition is checked and, if it is satisfied, the spike is propagated to all target neurons. While this spike propagation technique is convenient because "time models itself", its results are only approximate as spike threshold conditions are only tested at time step boundaries, and therefore exact spike timings are lost. The clock-driven simulation scheme can be extended to overcome this inaccuracy by calculating the times at which neurons spike within the simulation time step and passing these times, along with the spikes, to the target neurons. Neurons can then sort incoming spikes based on these times and apply them exactly.

An alternative approach is to employ an event-driven algorithm where the state of neurons and synapses are updated only when they receive spikes. This alleviates the inaccuracies caused by clock-driven approaches and has the potential to improve performance if spikes are sufficiently sparse. However, event-driven algorithms require that neuron and synapse models have explicit solutions i.e. that their state can be calculated at any time. All the static synapse models discussed in section 3.1.3 and many plastic synapse models (discussed further in chapter 4) have this property. However, of the neuron models discussed in section 3.1.1, only the LIF model has an explicit solution [59, 60]. Furthermore Morrison *et al.* [61] argue that, because cortical neurons receive input from the order of  $10 \times 10^3$  other neurons, the combined input event rate is such that any computational advantages of using an event-driven algorithm for simulating neurons is lost. Therefore many

software simulators – including NEST [46], NEURON [62] and Brian [63] – use a "hybrid" approach where neurons are simulated using a time-driven algorithm and synapses using an event-driven algorithm.

One common means of accelerating large-scale software simulations is by running them on distributed cluster systems or even supercomputers. Both NEST and NEURON support this mode of operation and have both been shown to enable supra-linear speedup across thousands of processors [64]. In fact NEST was used to run the largest neuronal network simulation to date consisting of  $1.73 \times 10^{12}$  neurons and  $10.4 \times 10^{18}$  synapses distributed across 82 944 processors of the K supercomputer and taking 40 min to simulate 1 s of neural activity [65].

## 3.3 GPU simulation

With 69 of the machines in the June 2016 Top 500 list [66] featuring GPU acceleration it is clear that GPUs have become a dominant force in the high-performance computing (HPC) landscape. Therefore, as a major HPC application, it is unsurprising that there has been significant interest in using GPUs to accelerate spiking neural network simulations.

Nageswaran *et al.* [67] developed a GPU simulator which was used to simulate a network with up to  $100 \times 10^3$  Izhikevich neurons and  $10 \times 10^6$  synapses at  $0.66 \times$  real time. Fidjeland and Shanahan [68] further optimised this approach to enable neurons with more realistic numbers of synapses to be simulated and used this to simulate a network with  $30 \times 10^3$  Izhikevich neurons and  $30 \times 10^6$  at approximately  $2 \times$  real time. However neither of these approaches offers a large speedup over a CPU implementation considering the raw computational power GPUs offer (Nageswaran *et al.* reported  $26 \times$ ).

Both Nageswaran et al. and Fidjeland and Shanahan identify that this bottle-

neck arises largely because synaptic transmission makes inefficient use of GPU architectures. Yavuz *et al.* [69] provided further evidence for this inefficiency by simulating networks of both Izhikevich and Hodgkin-Huxley neurons. They found that their GPU implementation offered a speedup of over 100× in simulations using Hodgkin-Huxley neurons where updating each neuron is a mathematically intensive operation. However they obtained only a 10× speedup in simulations of a simple cortical network built with integrate-and-fire neurons where synaptic transmission costs dominated. The neocortical models which are the focus of this thesis have properties much more similar to this second network and, as GPUs can also have a peak power usage of around 200 W, they seem ill-suited to the low power simulation of such models.

# 3.4 Neuromorphic hardware

As discussed in section 3.2, software simulators can scale to take advantage of the latest peta-scale supercomputers, allowing extremely large neural networks to be simulated. However supercomputers, like the GPUs discussed in the previous section, require considerable electrical power to do this.

In the late 1980s Mead [70] observed that transistors exhibit "hauntingly" similar electrical behaviour to neurons and synapses. Therefore Mead proposed that, instead of using power-hungry digital computers to simulate the brain, we could instead implement neurons and synapses using sub-threshold analogue circuits. This approach became known as "neuromorphic engineering" and, over the proceeding years, a number of neuromorphic systems have been built with the aim of reducing the power consumption and execution time of neural simulations. These systems have been constructed using a number of approaches: ROLLS [71], NeuroGrid [72] and BrainScaleS [73] are built using custom analogue hardware and

True North [74] is built using custom digital hardware. These systems all have the potential to simulate neural networks using many orders of magnitude less power than the software-based approaches discussed in the previous section. However, they also all share several limitations which hinder their ability to simulate the type of highly-connected, plastic models of the cortex that are the focus of this thesis. These limitations stem from how synapses are implemented in such systems. Both BrainScaleS and TrueNorth are fabricated with several hundred individual synapse circuits associated with each neuron. Although both systems have mechanisms that allow synapses to be "borrowed" from other neurons to implement higher connectivity, this is done at the expense of the total number of neurons the system can simulate. ROLLS and NeuroGrid use an alternative approach where each neuron has a single synaptic input circuit into which input currents from multiple synapses are injected. While this approach allows much higher degrees of connectivity to be achieved, synapses implemented in this manner cannot support plasticity. To overcome this limitation ROLLS also has a limited number of plastic synapses implemented as individual circuits.

### 3.5 FPGA simulation

The development of application specific integrated circuits (ASICS) of the type discussed in section 3.4 has become prohibitively expensive as process sizes shrink [75]. Therefore field-programmable gate arrays (FPGAs) – devices consisting of a large number of lookup-table based logic blocks, connected using a programmable fabric – are becoming a popular alternative in many small-volume applications. However the additional logic required to implement this programmability means that a given circuit may occupy  $40\times$  more silicon area if it is implemented using FPGA rather than ASIC logic [76]. Therefore employing the approach used

by the neuromorphic devices discussed in section 3.4 where individual neuron circuits are implementing in FPGA logic only scales to very small networks of neurons [77].

However modern FPGAs typically run at clock speeds in the order of hundreds of MHz: many times faster than biological neurons. Therefore, as simple integrate-and-fire neurons of the type discussed in section 3.1.1 can be evaluated in very few clock cycles, a single neuron circuit can be used to simulate large number of "time-division multiplexed" neurons. Moore *et al.* [78] used this approach in the multi-FPGA Bluehive system which is capable of simulating up to  $64 \times 10^3$  Izhikevich neurons and  $64 \times 10^6$  synapses on a single FPGA. Furthermore Moore *et al.* predict that the performance of Bluehive will scale linearly across up to 64 FPGAs. However the resultant system is still somewhat inflexible as the neuron model is directly implemented in FPGA logic.

One way in which FPGA designs can be made more flexible is by incorporating a general purpose CPU, implemented in FPGA logic, into the design so that non-performance-critical components can be implemented in software. Naylor *et al.* [79] developed a vector coprocessor which improves the performance of such a CPU to the point where it can accelerate neural simulations to within a factor of two of the Bluehive system. This approach shows much promise but it remains to be seen how competitive it would be at the scale of the SpiNNaker system discussed in section 3.7.

## **3.6 PyNN**

In the previous sections I have discussed a variety of simulation tools with different advantages and disadvantages. However researchers wishing to work across a number of these will typically have to learn new programming languages, APIs and possibly modelling paradigms.

While it is not a simulator in its own right the PyNN [80] project aims to address this issue by providing a standard abstraction layer for describing and simulating neural network models in Python. By using this abstraction layer a model defined in PyNN can, at least in principle, be run unmodified on any supported simulator. PyNN defines models in terms of *populations* and *projections*.

Populations are logical groups of neurons which can be simulated using the same neuron model. For example, in listing 3.1 two populations are created, one contains a single LIF neuron and the other a single *SpikeSourceArray* (an artificial neuron model that injects spikes into the network at pre-programmed times).

Projections represent connections between populations which can be simulated using the same synapse model. Projections also have an associated "connector" which defines how the individual neurons within the population are connected. For example, the *AllToAllConnector* used in listing 3.1, connects each neuron in the presynaptic population to every neuron in the postsynaptic population. PyNN also provides standard interfaces for controlling the simulation and recording its state.

# 3.7 SpiNNaker

SpiNNaker [81] is a massively parallel computer architecture which, inspired by the biological brain, has abandoned three features common to the majority of such architectures: memory coherence, synchronicity and determinism. Instead it has

Listing 3.1: Simple example model described using PyNN 0.7. The model consists of a spike source programmed to emit a single spike 0 ms into the simulation. The spike source is connected to a single leaky integrate-and-fire neuron whose output spikes and membrane voltage are recorded.

```

# Configure simulation time step to Ims

p.setup(timestep=1.0)

# Create two populations

pop_1 = p.Population(1, p.IF_curr_exp, {})

pop_2 = p.Population(1, p.SpikeSourceArray, {"spike_times": [0]})

# Connect the two populations together

p.Projection(pop_2, pop_1, p.AllToAllConnector(weights=5.0, delays=1))

```

# Record neural population's spikes and membrane voltage

been designed specifically for the low-power, real-time simulation of large networks of spiking neurons. Therefore, in our taxonomy of neural simulation techniques, SpiNNaker falls somewhere between the software simulators discussed in section 3.2 and the hardware simulators discussed in section 3.4.

#### 3.7.1 Hardware

import pyNN.nest as p

pop\_1.record()

pop\_1.record\_v()

p.run(10)

# Run simulation for 10ms

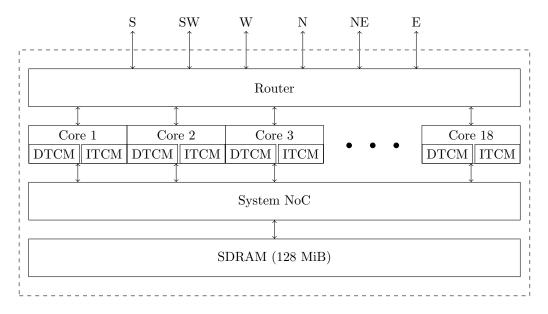

The SpiNNaker architecture can be used to build systems ranging in size from single boards to room-size machines, all using the same basic building block: the SpiNNaker chip. As shown in figure 3.3, a SpiNNaker chip contains 18, 200 MHz, ARM cores, each equipped with two small tightly-coupled memories: 32 KiB for instructions (ITCM) and 64 KiB for data (DTCM). The cores within a chip connect to each other, 128 MiB of external SDRAM and a multicast router using a network-on-chip (NoC) known as the "System NoC". Every chip's router connects

Figure 3.3: The basic architecture of a SpiNNaker chip.

to the routers of six immediate neighboring chips using a second NoC known as the "Communications NoC".

Beyond its lack of globally shared memory one notable restriction of the SpiN-Naker architecture is that, for reasons of silicon area and energy efficiency, no hardware floating point unit is included. While floating point operations can be emulated in software, this incurs a significant performance penalty meaning that performance-critical SpiNNaker software needs instead to use fixed-point arithmetic. Hopkins and Furber [82] discuss the challenges of using fixed-point arithmetic for neural simulation on the SpiNNaker platform in detail and highlight two main issues of particular importance. Firstly, the range of fixed-point numeric representations is static so, to attain maximal accuracy, the optimal representation for storing each state variable must be chosen ahead of time. Secondly, there is no standard means of calculating transcendental functions such as exp or log using fixed-point arithmetic. These functions can be approximated using, for instance, a Taylor series expansion. However, the resultant functions are likely to take the

order of 100 CPU cycles to evaluate [83], making them too slow for use in the most performance-critical SpiNNaker applications. Another approach is to use pre-calculated lookup tables (LUTs). These are particularly well suited to implementing periodic functions such as  $\sin(x)$  or functions such as  $\exp\left(\frac{-t}{\tau}\right)$  which (for small values of  $\tau$ ) decay to 0 after only a small number of table entries.

### 3.7.2 Spiking neural network simulation

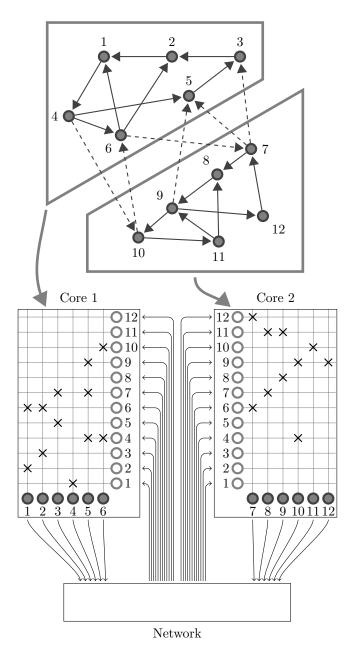

While SpiNNaker has a somewhat unusual memory hierarchy, its lack of global shared memory means that many of the problems related to simulating large spiking neural networks on a SpiNNaker system are shared with more typical distributed computer systems. Therefore the SpiNNaker neural simulator uses a very similar hybrid event and clock-driven approach to software simulators designed to run on distributed systems (section 3.2). Figure 3.4 illustrates how neural networks are mapped to SpiNNaker with each processing core being responsible for simulating a collection of neurons and their afferent synapses. The neurons are simulated using a time-driven approach with their state held in the DTCM. Each neuron is uniquely identified by a 32 bit ID and, when a simulation step results in a spike, a packet containing this ID is sent to the SpiNNaker router. These "spike" packets are then routed across the network fabric to all the cores on which neurons targeted by the spiking neuron are simulated. While, as discussed in section 3.2, this strictly clock-driven approach does not produce exact results, Hopkins and Furber [82] developed some extensions to the basic clock-driven algorithm which improve accuracy.

Due to the large number of synapses and the relatively low firing rate of single neurons, the synapses are simulated in an event-driven manner, meaning that they get updated only when they transfer a spike. On SpiNNaker this event-driven approach is also advantageous as, due to the sheer number of synapses, per-synapse

Figure 3.4: Standard mapping of a spiking neural network to SpiNNaker. An example network consisting of 12 neurons is distributed between two SpiNNaker cores. The synaptic matrix is split vertically and its columns are distributed between the two cores responsible for simulating the corresponding postsynaptic neurons (filled circles). Both cores contain synaptic matrix rows corresponding to all 12 presynaptic neurons (non-filled circles). The SpiNNaker router routes spikes from firing neurons (filled circles) to the cores responsible for simulating the neurons these spikes target.

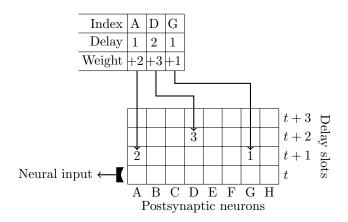

Figure 3.5: Unpacking a sparse synaptic matrix row with three synapses into a delay ring-buffer supporting delays of up to 3 simulation time steps and 8 neurons (labelled A–H).

data such as synaptic weights must be stored in the off-chip SDRAM which each core can only access at a maximum of 300 MiB s<sup>-1</sup> [84] – insufficient to transfer the per-synapse data associated with every synapse each simulation time step. Instead, on receipt of a "spike" packet, cores initiate a direct memory access (DMA) transfer to fetch the row of the connectivity matrix associated with the firing neuron from SDRAM. Each of these rows describes the synaptic connections between a presynaptic neuron and the postsynaptic neurons simulated on the core. As shown in figure 3.5, rows are represented using a sparse format where each synapse consists of a weight (the magnitude of the input conductance or current change the spike induces), the index of the target postsynaptic neuron and a transmission delay. This transmission delay is implemented using a data structure we call a ring-buffer which accumulates the weights due to be applied to each neuron in future simulation time steps. Once a row is retrieved, the synaptic weights it contains are inserted into the correct locations within the ring-buffer as illustrated in figure 3.5. The ring-buffer is then 'rotated' each simulation time step – the weights accumulated in the t + 1 delay slot are applied to the neuron and those accumulated in the t + 2 delay slot are moved into the t + 1 slot etc.

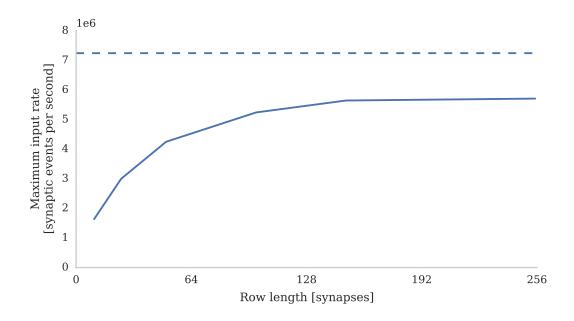

Figure 3.6: Performance of a SpiNNaker core simulating 256 neurons with varying sparseness of connectivity. Each data point represents the maximum Poisson input rate (provided by multiple 10 Hz sources) that the core can handle in real time. The dashed line illustrates the performance estimated using equation 3.14.

#### 3.7.3 Performance

The design of SpiNNaker was based on the assumption that each processing core would be responsible for simulating 1000 spiking neurons [86]. However profiling current models shows that updating the state of a single neuron requires 187 CPU cycles rather than the 50 CPU cycles estimated by Jin *et al.* Therefore 256 neurons are typically simulated on each core. As discussed in section 2.2 each cortical neuron receives input from an average of 8000 synapses meaning that the performance of the synaptic row processing stage discussed in the previous section is critical. Profiling of the row processing code shows that processing each synapse in a row takes 21 cycles allowing us to build the following simple model of the maximum rate at which a single 200 MHz SpiNNaker core can handle incoming spikes:

| Model Summary                                        |                                                                                                                                           |                  |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

| Populations                                          | Neurons, stimuli                                                                                                                          |                  |  |

| Connectivity                                         | Probabilistic with a fixed number of postsynaptic                                                                                         |                  |  |

|                                                      | neurons connected to each presynaptic neuron                                                                                              |                  |  |

| Neuron model                                         | nodel Leaky integrate-and-fire with exponential-shaped synaptic current inputs                                                            |                  |  |

|                                                      |                                                                                                                                           |                  |  |

| Synapse model                                        | Current-based with exponential-shaped PSCs                                                                                                |                  |  |

| Input                                                | Independent 10 Hz Poisson spike trains                                                                                                    |                  |  |

| Populations                                          |                                                                                                                                           |                  |  |

| Name                                                 | Elements                                                                                                                                  | Size             |  |

| Neurons                                              | LIF                                                                                                                                       | 256              |  |

| Stimuli                                              | Independent 10 Hz                                                                                                                         | As described     |  |

|                                                      | Poisson spike trains                                                                                                                      | in section 3.7.3 |  |

| Connectivity                                         |                                                                                                                                           |                  |  |

| Source                                               | Target                                                                                                                                    | Weight           |  |

| Stimuli                                              | Neurons                                                                                                                                   | 0 nA             |  |

| Neuron and synapse model                             |                                                                                                                                           |                  |  |

| Туре                                                 | Leaky integrate-and-fire with                                                                                                             |                  |  |

| • •                                                  | exponential-shaped synaptic current inputs                                                                                                |                  |  |

| Parameters $g_L = 0.05 \mu\text{S}$ leak conductance |                                                                                                                                           | _                |  |

|                                                      | C = 1  nF membrane capacitanc                                                                                                             | e                |  |

|                                                      | $V_{thresh} = -50 \text{mV}$ threshold voltage<br>$V_{reset} = -65 \text{mV}$ reset voltage<br>$V_{rest} = -65 \text{mV}$ resting voltage |                  |  |

|                                                      |                                                                                                                                           |                  |  |

|                                                      |                                                                                                                                           |                  |  |

|                                                      | $\tau_{syn} = 5 \text{ ms synaptic time const.}$                                                                                          | ant              |  |

|                                                      |                                                                                                                                           |                  |  |

Table 3.1: Model description of the benchmark network. After [85]

$$\mu_{input} \approx \frac{1}{21} \left( 200 \times 10^6 - \frac{187 N_{neurons}}{dt} \right) = 7.2 \times 10^6$$

(3.14)

Where the simulation time step dt = 1 ms and the number of neurons  $N_{neurons} = 256$ . Using equation 3.14 and the mean cortical firing rates of 2 Hz to 3 Hz measured by Buzsáki and Mizuseki [87] suggests that a single SpiNNaker core can easily simulate 256 neurons each with 8000 synapses.