# ENERGY EFFICIENT COMPUTER ARCHITECTURE

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

IN THE FACULTY OF SCIENCE AND ENGINEERING

October 1996

By

Henrik Scheuer

Department of Computer Science

## **Table of Contents**

| Abstrac | t                                       | 12 |

|---------|-----------------------------------------|----|

| Declara | tion                                    | 13 |

| Copyrig | ght Notice                              | 14 |

| The Aut | thor                                    | 15 |

| Acknow  | vledgments                              | 16 |

| Chapter | r 1 Introduction                        | 17 |

| 1.1     | Background                              | 18 |

| 1.2     | Overview of thesis                      | 23 |

| Chapter | r 2 Power consumption in an ARM3-system | 27 |

| 2.1     | Results from OMI-MAP                    | 27 |

| 2.2     | Evaluation of results                   | 30 |

| 2.3     | Power consumption in RAM                | 32 |

| 2.4     | Summary                                 | 33 |

| Chapter | r 3 Baseline HORN architecture          | 35 |

| 3.1     | Basic architecture                      | 36 |

| 3.2     | Local storage                           | 37 |

| 3.2     | 2.1 Global registers                    | 38 |

| 3.2     | 2.2 Local registers                     | 38 |

| 3.2     | 2.3 Operand queue                       | 39 |

| 3.3     | Branch architecture                     | 40 |

| 3.4     | Instruction format                      | 44 |

| 3.5     | Summary                                 | 47 |

| Chapter | r 4 Metrics and benchmarks              | 49 |

| 4.1     | Background on metrics                   | 50 |

| 4.2     | Evaluation of metrics and discussion    | 55 |

| 4.3     | Selection criteria for benchmarks       | 59 |

| 4.4     | Benchmark Suite                         | 60 |

| 4.4     | 4.1 Hello                               | 60 |

| 4.4     | 4.2 Espresso                            | 61 |

|         |                                         |    |

| 4.4.    | 3 Flex                                                      | 62  |

|---------|-------------------------------------------------------------|-----|

| 4.4.    | 4 Cacti                                                     | 62  |

| 4.4.    | 5 Fft                                                       | 63  |

| 4.4.    | 6 Dhrystone                                                 | 64  |

| 4.4.    | 7 Stcompiler                                                | 65  |

| 4.5     | Summary                                                     | 65  |

| Chapter | 5 Energy consumption in caches                              | 68  |

| 5.1     | Energy cost                                                 | 69  |

| 5.1.    | 1 RAM-compiler                                              | 69  |

| 5.1.    | Fundamental relations                                       | 72  |

| 5.1.    | 3 Multi-ported RAM                                          | 80  |

| 5.2     | Direct mapped cache                                         | 81  |

| 5.3     | N-way set-associative caches                                | 85  |

| 5.4     | Other cache organizations                                   | 87  |

| 5.4.    | 1 Sectored caching                                          | 89  |

| 5.4.    | 2 Cache Address Tag-caching                                 | 91  |

| 5.5     | Skewed-associativity                                        | 93  |

| 5.5.    | 1 Choosing a set of skewing functions                       | 96  |

| 5.6     | Replacement algorithms                                      | 96  |

| 5.7     | Cache timing                                                | 98  |

| 5.8     | Block buffering                                             | 100 |

| 5.9     | Fetch and Write Back buffers                                | 104 |

| 5.10    | Gray-coding fetches/writebacks                              | 106 |

| 5.11    | Selective writeback                                         | 109 |

| 5.12    | Summary                                                     | 110 |

| Chapter | 6 Dual instruction branch                                   | 113 |

| 6.1     | Improving hit-rate through dual instruction branches        | 113 |

| 6.1.    | 1 Effect on effective hit-rate                              | 114 |

| 6.1.    | Performance measurements                                    | 115 |

| 6.1.    | 3 Energy efficiency                                         | 120 |

| 6.2     | Reduction of cache miss penalty through two-instruction CTI | 122 |

| 6.3     | Alternative branch and loop architectures                   | 127 |

| 6.4     | Two-instruction CTI in a dual-issue implementation          | 129 |

| 6.5     | Sumr    | nary                                             | 132 |

|---------|---------|--------------------------------------------------|-----|

| Chapter | · 7 Reg | rister file architectures                        | 134 |

| 7.1     | Intro   | duction                                          | 134 |

| 7.2     | Temp    | oorary storage                                   | 135 |

| 7.3     | Mem     | ory mapped registers                             | 136 |

| 7.3     | 3.1     | Number of ports                                  | 138 |

| 7.3     | 3.2     | Total size                                       | 139 |

| 7.3     | 3.3     | Line size                                        | 141 |

| 7.3     | 3.4     | Associativity                                    | 143 |

| 7.3     | 3.5     | Writeback policy                                 | 144 |

| 7.3     | 3.6     | Results                                          | 145 |

| 7.3     | 3.7     | Summary                                          | 152 |

| 7.4     | Spill/  | fill                                             | 152 |

| 7.4     | l.1     | The spill/fill scheme                            | 154 |

| 7.4     | 1.2     | Statistics                                       | 156 |

| 7.4     | 1.3     | Implementing the spill/fill scheme               | 160 |

| 7.4     | 1.4     | Three ways of implementing the spill/fill scheme | 162 |

| 7.4     | 1.5     | The cache and memory models                      | 164 |

| 7.4     | 1.6     | Results                                          | 165 |

|         | 7.4.6.1 | Model 1, A conservative scheme                   | 165 |

|         | 7.4.6.2 | Model 2, A spill/fill engine                     | 167 |

|         | 7.4.6.3 | Model 3, A spill/fill cache                      | 169 |

| 7.4     | 1.7     | Summary                                          | 171 |

| 7.5     | Regis   | ster windows (SPARC)                             | 172 |

| 7.6     | Sumr    | nary                                             | 177 |

|         |         |                                                  |     |

| -       |         | truction fetching                                |     |

| 8.1     |         | duction                                          |     |

| 8.2     |         | ble-size instructions in the HORN architecture   |     |

| 8.3     |         | action fetch mechanisms                          |     |

| 8.3     |         | The alignment architecture                       |     |

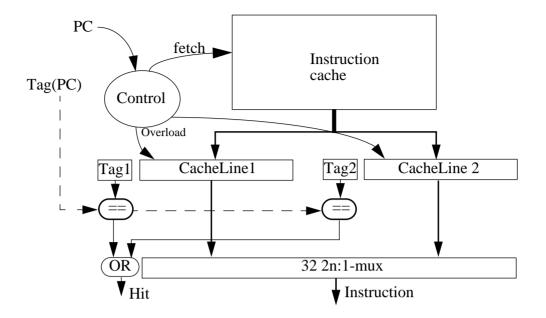

| 8.3     |         | The dual cache line architecture                 |     |

| 8.3     |         | The eXtra-line architecture                      |     |

| 8.4     | Sumr    | nary                                             | 198 |

| Chapter   | 9 Cache design and dimensioning                                     | 200   |

|-----------|---------------------------------------------------------------------|-------|

| 9.1       | Background for cache evaluation                                     | 201   |

| 9.2       | Performance and energy efficiency of separate cache configurations  | 203   |

| 9.3       | Unified cache                                                       | 213   |

| 9.3       | .1 Performance and energy efficiency of unified cache configuration | s 214 |

| 9.4       | Summary                                                             | 217   |

| Chapter   | 10 Conclusions                                                      | 219   |

| 10.1      | Summary                                                             | 219   |

| 10.2      | Assessment of work                                                  | 223   |

| 10.3      | Conclusions                                                         | 225   |

| 10.4      | Suggestions for future work                                         | 226   |

| Reference | ees                                                                 | 229   |

| Appendi   | x A Energy Efficiency versus power consumption                      | 237   |

| A.1       | Separate caches                                                     | 237   |

| A.2       | Unified cache                                                       | 239   |

| Appendi   | x B Energy Efficiency versus cache line size                        | 242   |

| Appendi   | x C Simulation results                                              | 245   |

# **List of Figures**

| Figure 3.1  | Example of packed arithmetic                                          | 37  |

|-------------|-----------------------------------------------------------------------|-----|

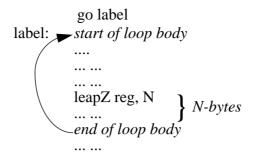

| Figure 3.2  | Example of a go-instruction outside a loop body                       | 42  |

| Figure 3.3  | Optimal migration of the 'go' and 'leap' instructions                 | 43  |

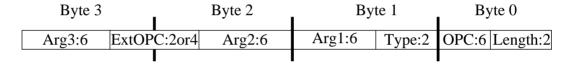

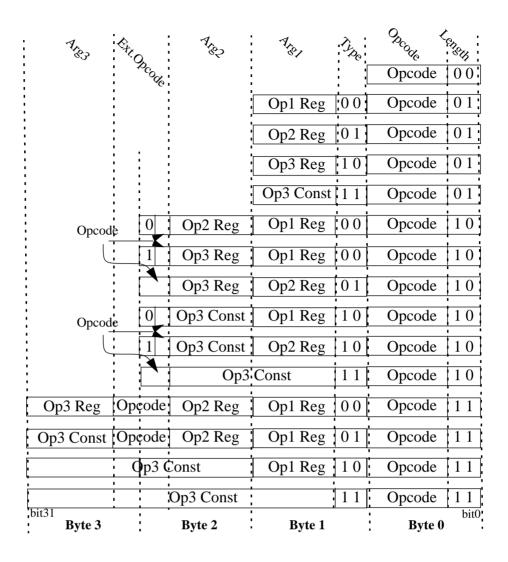

| Figure 3.4  | Instruction format                                                    | 44  |

| Figure 3.5  | Instruction encoding                                                  | 45  |

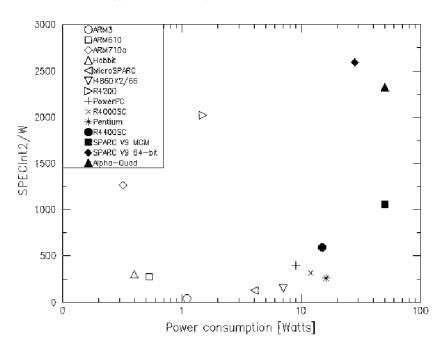

| Figure 4.1  | Energy Efficiency vs. power consumption for existing processor        | s59 |

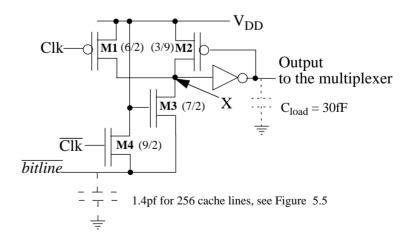

| Figure 5.1  | Sense amplifier without static power dissipation                      | 71  |

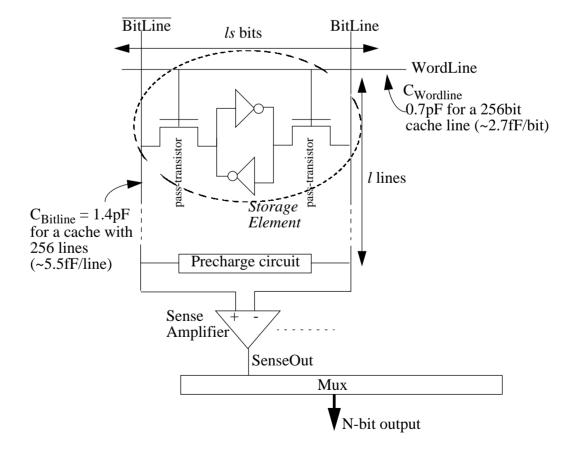

| Figure 5.2  | Extract from RAM circuit                                              | 73  |

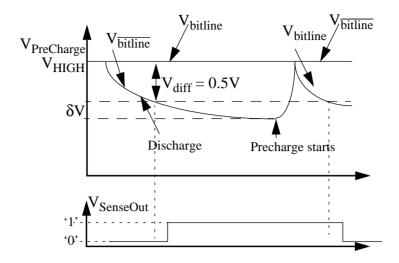

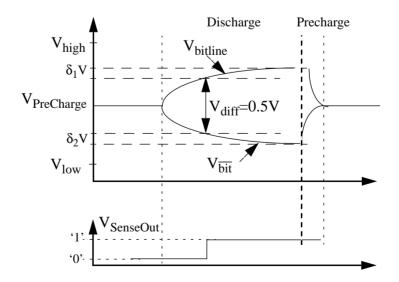

| Figure 5.3  | Voltage swing when discharging and precharging bit lines              | 74  |

| Figure 5.4  | V <sub>Bitline</sub> when precharging to an intermediate voltage      | 75  |

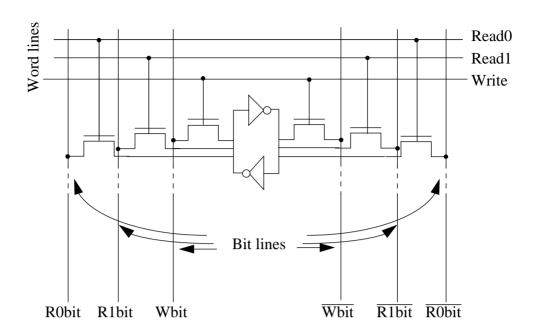

| Figure 5.5  | Extract of a bit cell from a multi-ported RAM circuit                 | 81  |

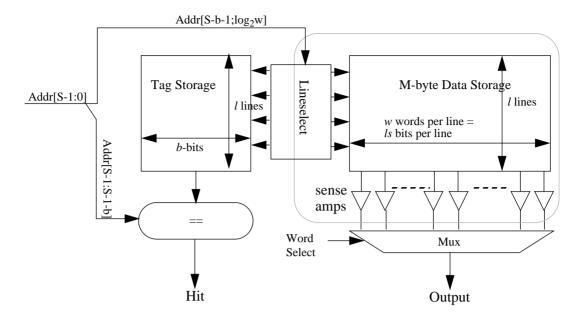

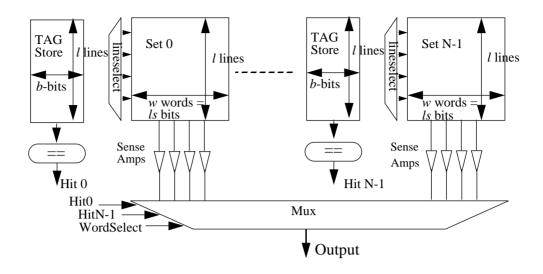

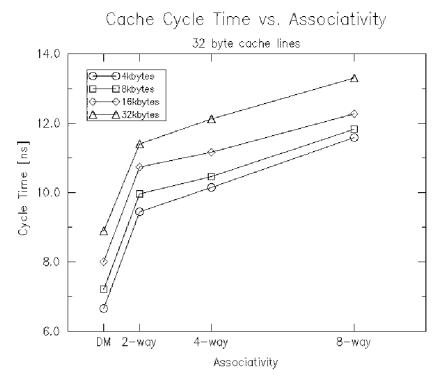

| Figure 5.6  | Block diagram for a direct mapped cache                               | 82  |

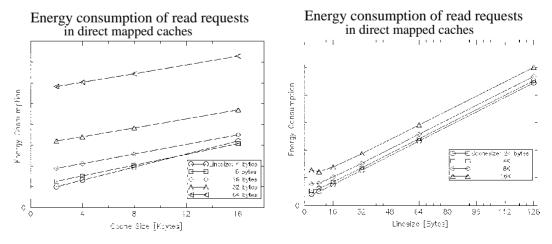

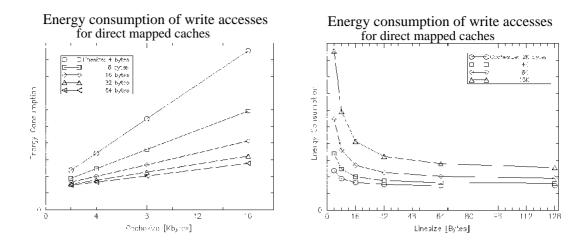

| Figure 5.7  | $E_{Cache,RR}$ vs. cache size and $E_{Cache,RR}$ vs. line size        | 84  |

| Figure 5.8  | $E_{Cache,RW}$ vs. cache size and $E_{Cache,RW}$ vs. line size        | 85  |

| Figure 5.9  | N-way set-associative cache                                           | 86  |

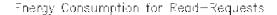

| Figure 5.10 | E <sub>Cache,RR</sub> vs. degree of associativity for a 8K-byte cache | 87  |

| Figure 5.11 | Sectored cache                                                        | 89  |

| Figure 5.12 | CAT-cache                                                             | 91  |

| Figure 5.13 | 2-way set- and skewed-associative caches                              | 94  |

| Figure 5.14 | Different mapping functions in different sets                         | 95  |

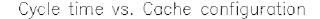

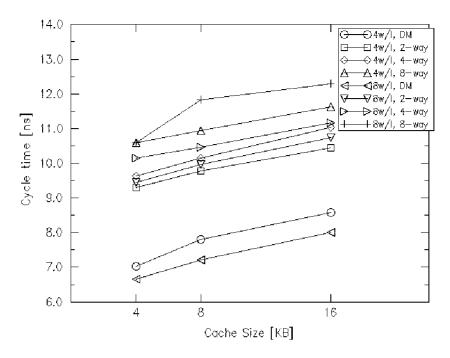

| Figure 5.15 | Cache cycle time versus cache size and organization                   | 99  |

| Figure 5.16 | Cache cycle time versus associativity                                 | 100 |

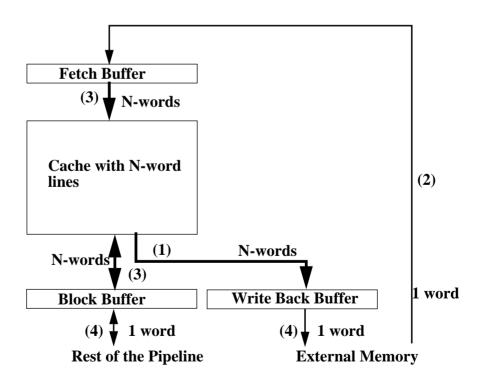

| Figure 5.17 | Block Buffering                                                       | 101 |

| Figure 5.18 | Cache with three block buffers                                        | 105 |

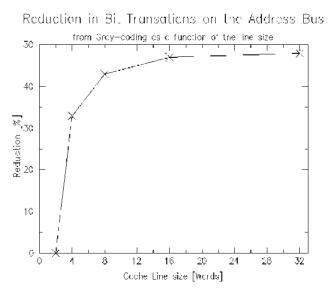

| Figure 5.19 | Reduction in bit-transitions on the address bus from Gray-coding      | 107 |

| Figure 6.1  | Go-leap structure                                                     | 113 |

| Figure 6.2  | Example of go-instruction migrating outside loopbody                  | 119 |

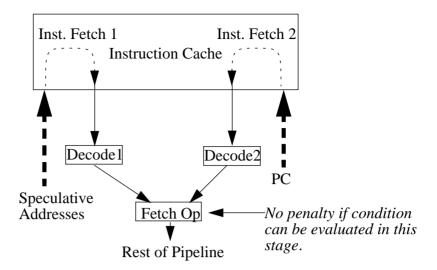

| Figure 6.3  | Doubling the early pipeline stages might eliminate branch penalty     | 123 |

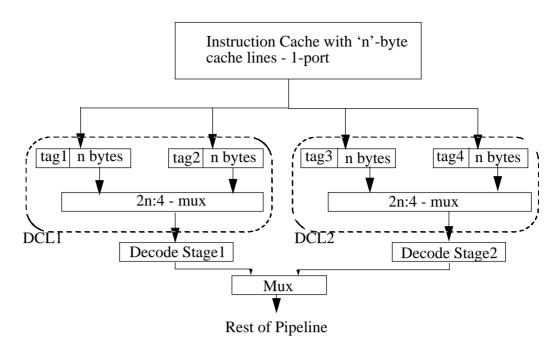

| Figure 6.4  | Replication of instruction alignment structure                 | 125  |

|-------------|----------------------------------------------------------------|------|

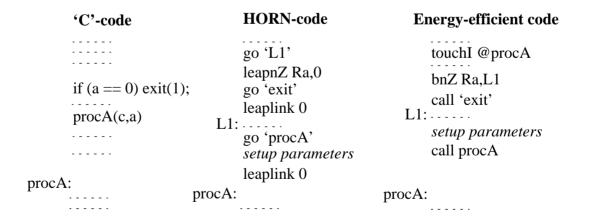

| Figure 6.5  | C-code compiled into HORN code and Energy-efficient code       | 128  |

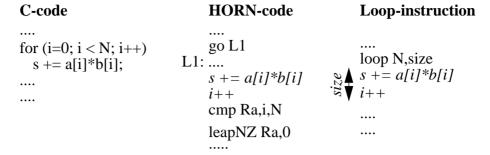

| Figure 6.6  | The principle of a 'loop'-instruction                          | 129  |

|             |                                                                |      |

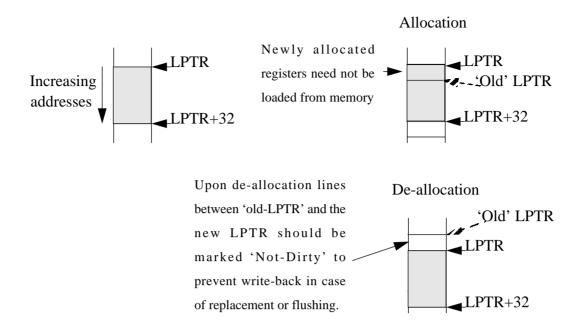

| Figure 7.1  | Allocating and de-allocating registers                         | 138  |

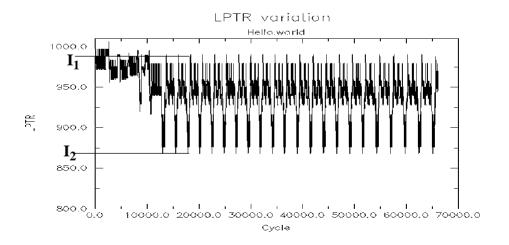

| Figure 7.2  | Variation of LPTR during execution, hello                      | 139  |

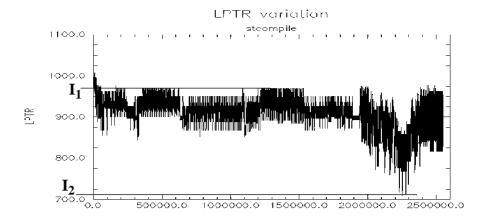

| Figure 7.3  | Variation of LPTR during execution, stcompiler                 | 140  |

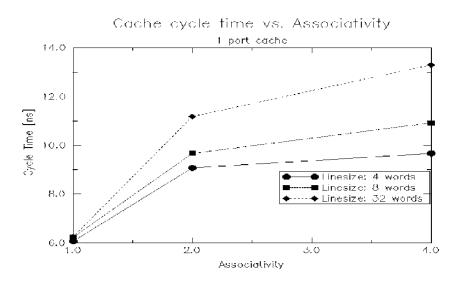

| Figure 7.4  | Cycle time vs. associativity for a 512-byte - 1 ported cache   | 144  |

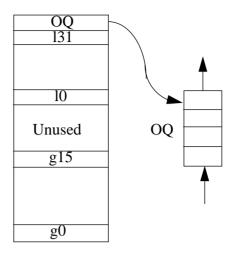

| Figure 7.5  | Register layout                                                | 153  |

| Figure 7.6  | Two register (de-)allocation schemes                           | 153  |

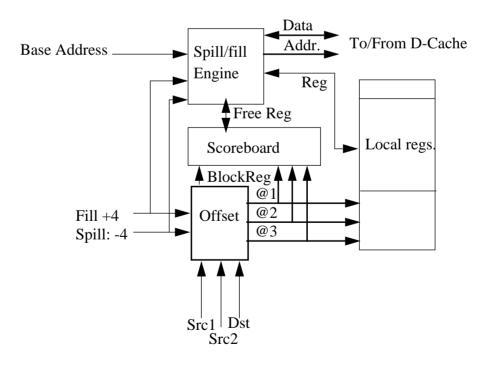

| Figure 7.7  | Block diagram of register file                                 | 155  |

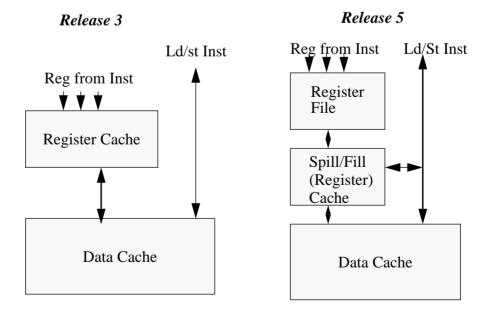

| Figure 7.8  | Principle difference between Release 3 and Release 5           | 161  |

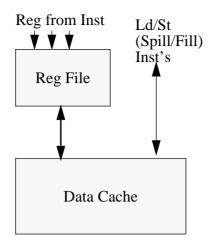

| Figure 7.9  | Simulated model                                                | 162  |

| Figure 7.10 | CPI vs. Cache size, Model 1                                    | 167  |

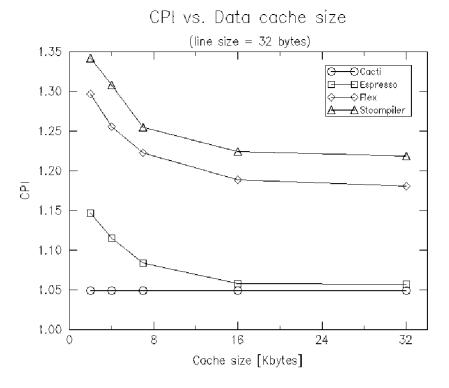

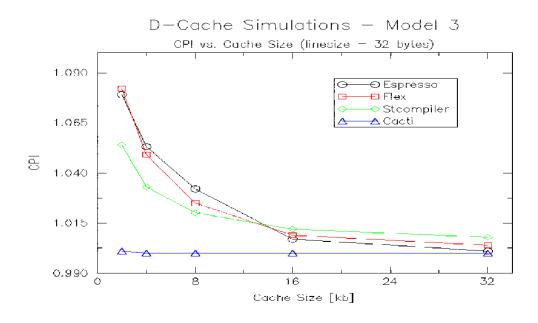

| Figure 7.11 | CPI vs. data cache size, 32 bytes/line, Model 3                | 170  |

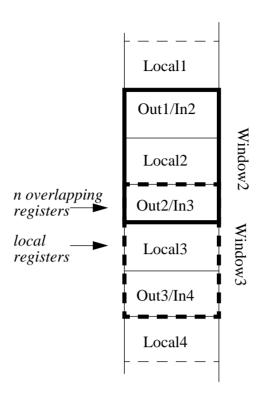

| Figure 7.12 | Principle of overlapping register windows in SPARC             | 172  |

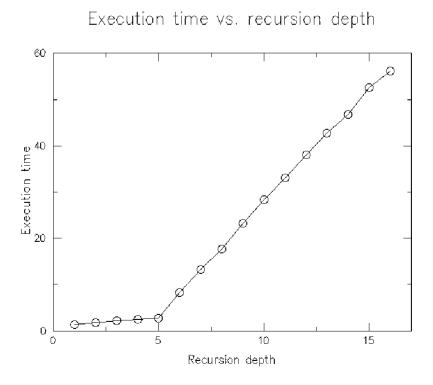

| Figure 7.13 | Execution time versus recursion depth on a SPARC station 5     | 173  |

|             |                                                                | 40.0 |

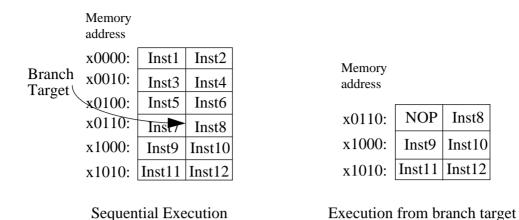

| Figure 8.1  | Branch to a non-aligned instruction                            |      |

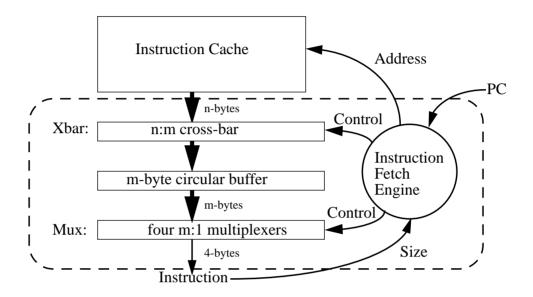

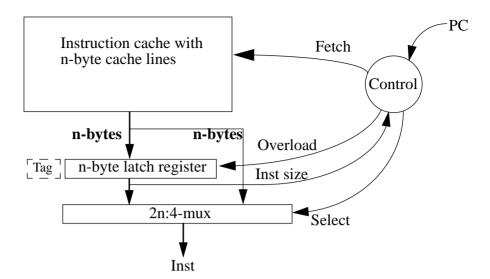

| Figure 8.2  | The alignment architecture                                     |      |

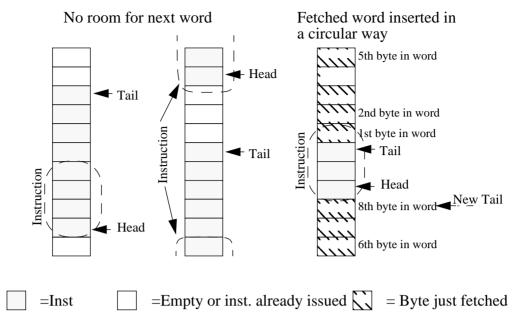

| Figure 8.3  | Principle operation of 11 byte circular buffer                 |      |

| Figure 8.4  | Dual cache line architecture                                   |      |

| Figure 8.5  | The eXtra-line architecture                                    | 196  |

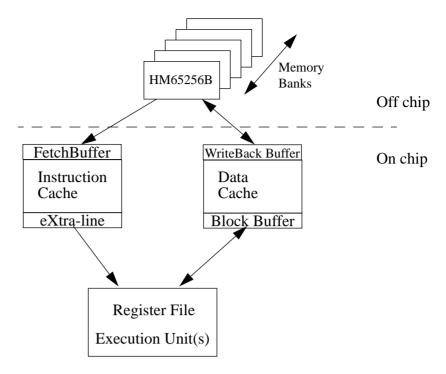

| Figure 9.1  | System architecture with separate caches                       | 204  |

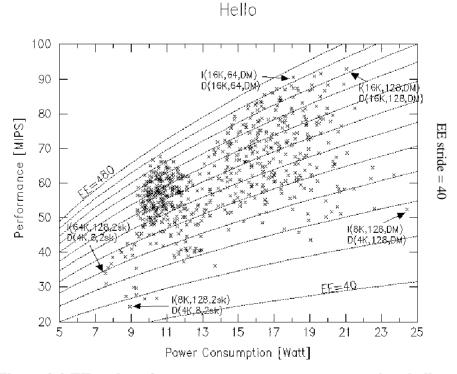

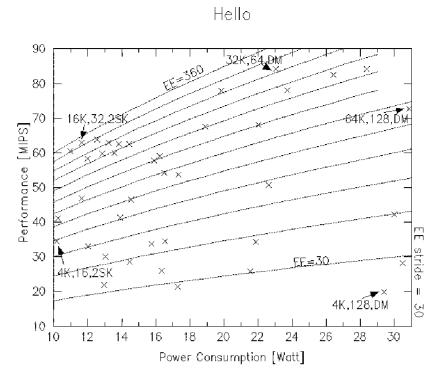

| Figure 9.2  | EE and performance versus power consumption, hello             |      |

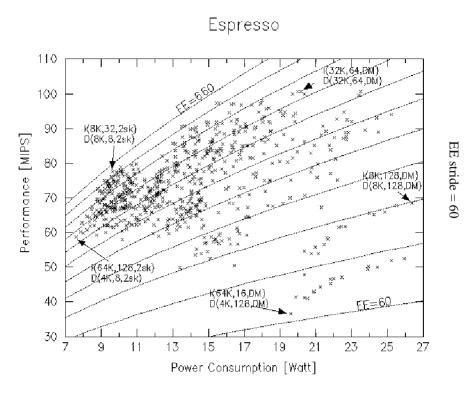

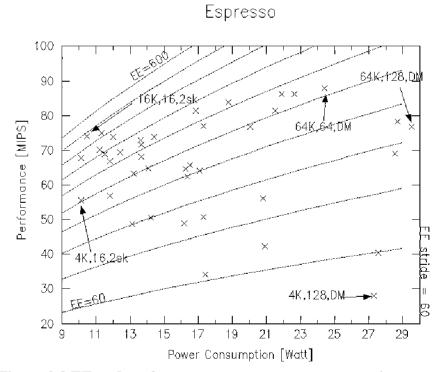

| Figure 9.3  | EE and performance versus power consumption, espresso          |      |

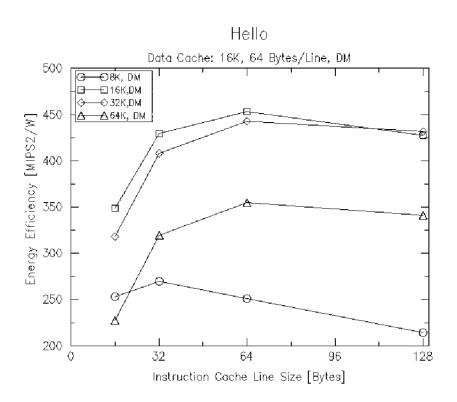

| Figure 9.4  | Energy Efficiency versus instruction cache line size, hello    |      |

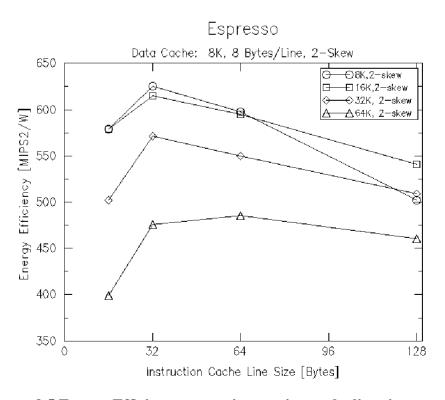

| Figure 9.5  | Energy Efficiency versus instruction cache line size, espresso |      |

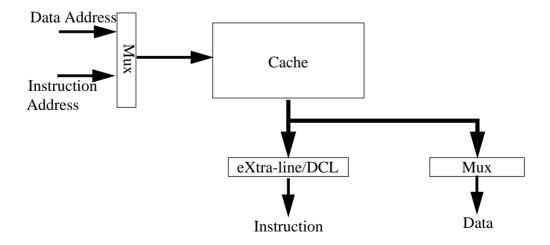

| Figure 9.6  | Unified cache serving both instruction- and data requests      |      |

| Figure 9.7  | EE and performance versus power consumption, hello             |      |

| Figure 9.8  | EE and performance versus power consumption, espresso          |      |

| - 10010 7.0 | s performance .erous power companipuon, copresso               | 210  |

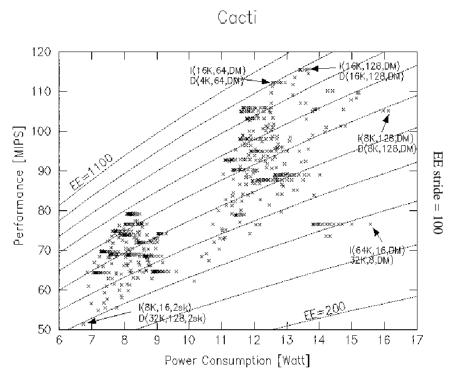

| Figure A.1  | EE and performance versus power consumption, cacti             | 237  |

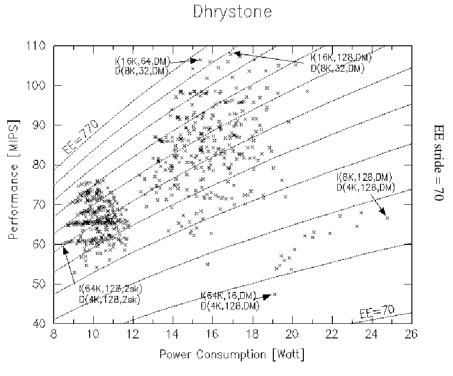

| Figure A.2  | EE and performance versus power consumption, dhrystone           | 237 |

|-------------|------------------------------------------------------------------|-----|

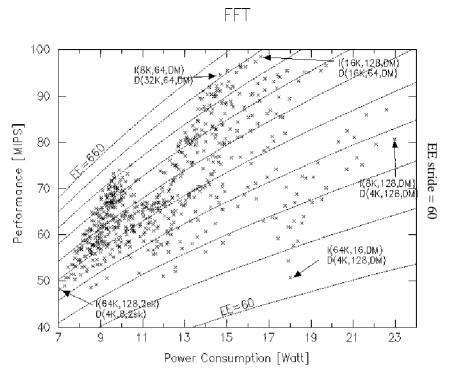

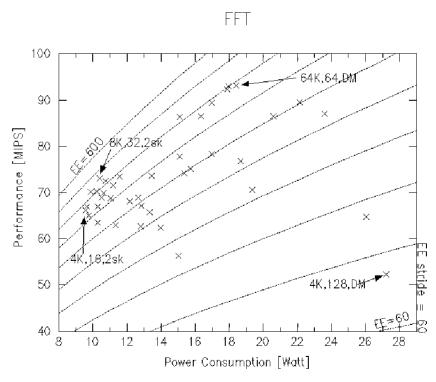

| Figure A.3  | EE and performance versus power consumption, fft                 | 238 |

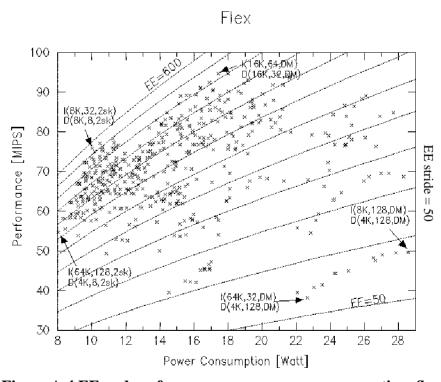

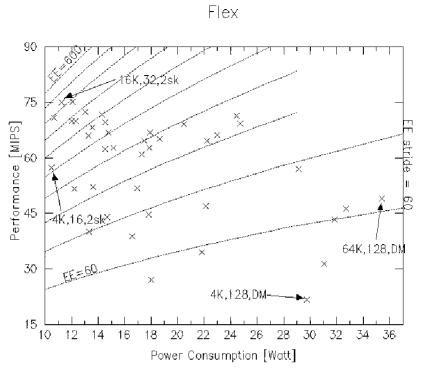

| Figure A.4  | EE and performance versus power consumption, flex                | 238 |

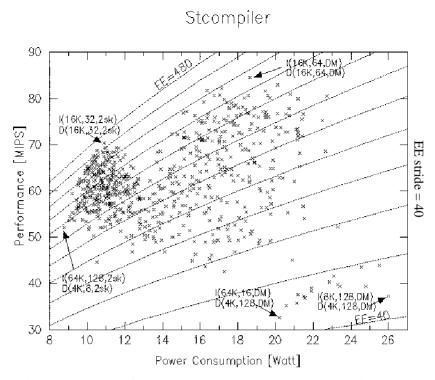

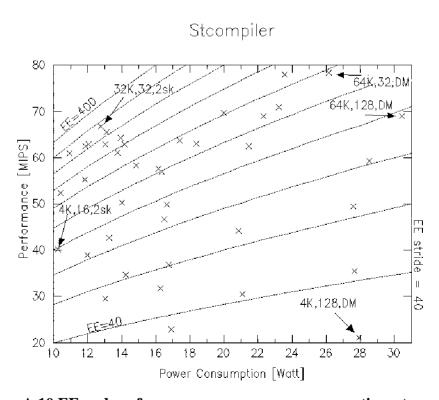

| Figure A.5  | EE and performance versus power consumption, stcompiler          | 239 |

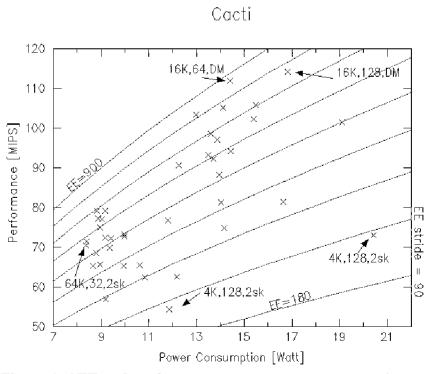

| Figure A.6  | EE and performance versus power consumption, cacti               | 239 |

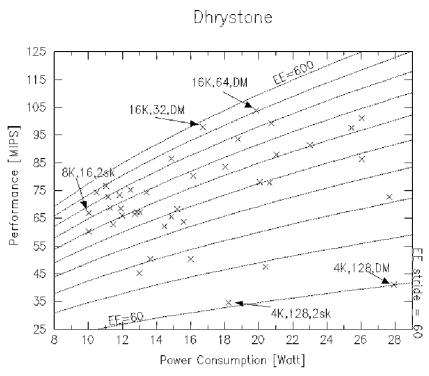

| Figure A.7  | EE and performance versus power consumption, dhrystone           | 240 |

| Figure A.8  | EE and performance versus power consumption, fft                 | 240 |

| Figure A.9  | EE and performance versus power consumption, flex                | 241 |

| Figure A.10 | EE and performance versus power consumption, stcompiler          | 241 |

|             |                                                                  |     |

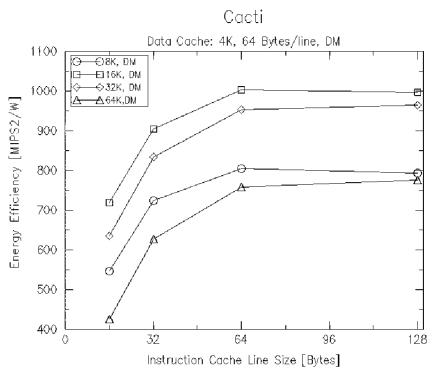

| Figure B.1  | Energy Efficiency versus instruction cache line size, cacti      | 242 |

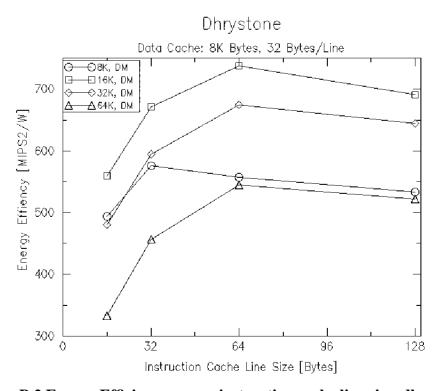

| Figure B.2  | Energy Efficiency versus instruction cache line size, dhrystone  | 242 |

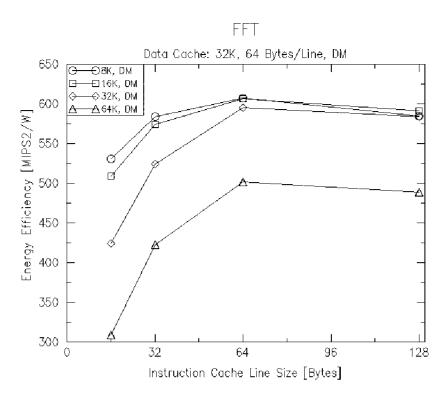

| Figure B.3  | Energy Efficiency versus instruction cache line size, fft        | 243 |

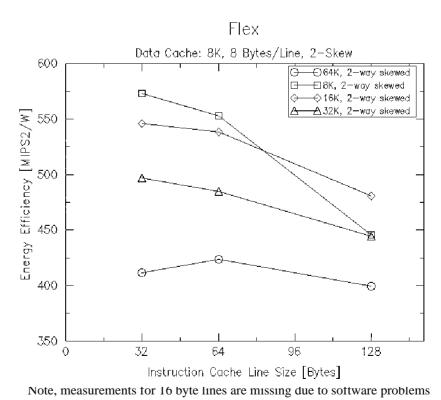

| Figure B.4  | Energy Efficiency versus instruction cache line size, flex       | 243 |

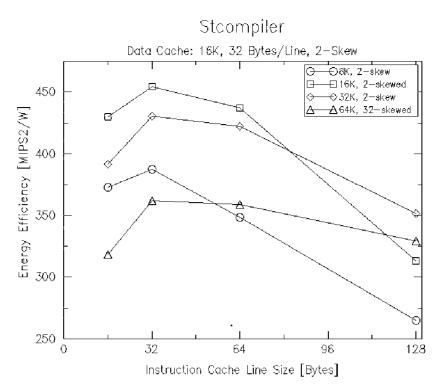

| Figure B.5  | Energy Efficiency versus instruction cache line size, stcompiler | 244 |

# **List of Tables**

| <b>Table 2.1</b> | Estimated internal ARM3 power consumption                            | 28  |

|------------------|----------------------------------------------------------------------|-----|

| Table 2.2        | Internal ARM3 power consumption (PLA structures are omitted)         | 29  |

| Table 2.3        | Current drawn of blocks in RISC processor [Sato]                     | 31  |

| Table 2.4        | ARM3 RAM dissipation - Pre-charge/Read Cycle                         | 32  |

| Table 2.5        | ARM3 RAM dissipation - Pre-charge/Write Cycle                        | 32  |

| Table 3.1        | Comparative register requirements                                    | 40  |

| Table 3.2        | Operand Queue usage and the corresponding instruction sizes          | 44  |

| Table 4.1        | Performance and power consumption for existing processors            | 56  |

| Table 5.1        | Dynamic energy consumption in RAM [VLSI]                             | 69  |

| Table 5.2        | ARM3 RAM dissipation - Pre-charge/Read Cycle                         | 78  |

| Table 5.3        | ARM3 RAM dissipation - Pre-charge/Write Cycle                        | 78  |

| Table 5.4        | Tag distribution - 8K byte unified cache, Direct mapped, 256 lines   | 88  |

| Table 5.5        | $\Delta$ CPI versus line size and prefetch distance[Uhlig]           | 90  |

| Table 5.6        | Performance of replacement algorithms                                | 98  |

| Table 5.7        | Effect of Block Buffering on cache traffic and energy consumption    | 103 |

| Table 5.8        | Gray-coding                                                          | 106 |

| Table 5.9        | Effect of Gray-coding in a 8K byte unified cache with 32-byte lines. | 108 |

| Table 5.10       | Writeback proportion of total I/O                                    | 109 |

| Table 5.11       | Frequency of 'dirty' words per cache line                            | 110 |

| Table 6.1        | Effect of prefetching on hit-rate in instruction cache               | 115 |

| Table 6.2        | Execution time, dhrystone                                            | 117 |

| Table 6.3        | Execution time, espresso                                             | 117 |

| Table 6.4        | Average distance between CTIs                                        | 118 |

| Table 6.5        | EE for different cache- and memory configurations, dhrystone         | 121 |

| Table 6.6        | EE for different cache- and memory configurations, espresso          | 122 |

| Table 6.7        | EE for prefetch and branch-prediction schemes - accuracy: 50%        | 126 |

| Table 6.8        | Prediction accuracy for the 'predict taken' model                    | 127 |

|                  |                                                                      |     |

| Table 6.9  | EE for prefetch and branch prediction schemes - accuracy: 77.7%            | 127 |

|------------|----------------------------------------------------------------------------|-----|

| Table 6.10 | Average number of instruction issued per cycle                             | 130 |

| Table 6.11 | EE for prefetch and branch prediction schemes (dual issue)                 | 132 |

|            |                                                                            |     |

| Table 7.1  | LPTR limits                                                                | 140 |

| Table 7.2  | ajlp offset distribution and frequency                                     | 141 |

| Table 7.3  | Execution time assuming 100% hit-rate in register cache                    | 145 |

| Table 7.4  | Stalled cycles due to register cache misses, espresso                      | 146 |

| Table 7.5  | Stalled cycles due to register cache misses, flex                          | 146 |

| Table 7.6  | Stalled cycles due to register cache misses, hello                         | 147 |

| Table 7.7  | Stalled cycles due to register cache misses, stcompiler                    | 147 |

| Table 7.8  | EE/EE <sub>0</sub> for different register cache configurations, espresso   | 150 |

| Table 7.9  | EE/EE <sub>0</sub> for different register cache configurations, flex       | 150 |

| Table 7.10 | EE/EE <sub>0</sub> for different register cache configurations, hello      | 150 |

| Table 7.11 | EE/EE <sub>0</sub> for different register cache configurations, Stcompiler | 151 |

| Table 7.12 | Memory access statistics                                                   | 156 |

| Table 7.13 | References to the 1st level data cache due to the two schemes              | 157 |

| Table 7.14 | Program statistics collected for four benchmarks                           | 159 |

| Table 7.15 | Data cache simulations, cacti - CPI <sub>ideal</sub> =1.048                | 166 |

| Table 7.16 | Data cache simulations, espresso - CPI <sub>ideal</sub> =1.05              | 166 |

| Table 7.17 | Data cache simulations, flex - CPI <sub>ideal</sub> =1.17                  | 166 |

| Table 7.18 | Data cache simulations, stcompiler - CPI <sub>ideal</sub> =1.22            | 166 |

| Table 7.19 | Distance between spill/fill and first ld/st/spill/fill                     | 167 |

| Table 7.20 | Hit-rate in data cache and CPI assuming a separate spill/fill cache        | 169 |

| Table 7.21 | Instruction overhead with the spill/fill scheme                            | 176 |

| Table 7.22 | Overflows in SPARC register file                                           | 176 |

|            |                                                                            |     |

| Table 8.1  | Average instruction sizes for the benchmarks                               | 184 |

| Table 8.2  | Percentage of instructions which straddle cache line boundaries            | 185 |

| Table 8.3  | Instruction cache miss rate for 4 byte- and variable-size instructions     | 186 |

| Table 8.4  | Percentage of instructions which require two cache accesses                | 190 |

| Table 8.5  | Number of fetches from instruction cache into alignment structure          | 190 |

| Table 8.6  | Percentage of instructions which cannot be fetched in one cycle            | 193 |

| Table 8.7  | Number of fetches from instruction cache into DCL                          | 194 |

| Table C.1  | Cache configuration measurements, espresso245                           |  |

|------------|-------------------------------------------------------------------------|--|

| 1 able 9.9 | Comparison between large unified cache and smaller separate caches. 217 |  |

| Table 9.9  | Comparison between large unified cache and smaller separate caches.217  |  |

| Table 9.8  | Simulated configurations                                                |  |

| Table 9.7  | Optimal Energy Efficiency configurations (cycle time = 15ns)212         |  |

| Table 9.6  | Optimal performance configurations (cycle time = 15ns)212               |  |

| Table 9.5  | Optimal Energy Efficiency configurations                                |  |

| Table 9.4  | Optimal performance configurations                                      |  |

| Table 9.3  | Reduction in cache accesses due to fetch- and writeback-buffers [%]206  |  |

| Table 9.2  | Simulated configurations                                                |  |

| Table 9.1  | Cache cycle time [ns] for different configurations202                   |  |

| Table 8.9  | Percentage of instructions which cannot be fetched in one cycle198      |  |

| Table 8.8  | Number of fetches from instruction cache into eXtra-line                |  |

| - 11 00    | 37 1 00 1 0 1 1 1 1 77 1                                                |  |

## **Abstract**

This thesis describes architectural approaches to improve the energy efficiency of RISC-style microprocessors. By breaking the convention that instructions in RISC architectures must be of fixed size, the performance and energy efficiency of a RISC microprocessor can be improved. Special instruction cache architectures are suggested to ensure an issue rate comparable with that of conventional RISC processors whilst reducing the energy consumption in the instruction cache considerably.

A high proportion of the energy consumption of a microprocessor system is consumed within the caches and external RAM. A significant proportion of memory traffic relates to allocating and de-allocating registers. Register file architectures are proposed to reduce this traffic. Of the schemes investigated, memory mapped registers held in a small separate register cache, has proved to perform well and be energy efficient.

A new branch architecture, which has the potential to eliminate or significantly reduce the miss-prediction penalty of branches through prefetching, will be examined. This scheme, which also improves the hit-rate, employs a pair of instructions. It allows the potential branch target to be prefetched into the cache and into the first stages of a shadow pipeline, before the outcome of the condition evaluation is known and thus reduce or eliminate branch penalties. The overall effect is improved performance. However due to increased cache traffic, the scheme is not energy efficient.

In conclusion, the energy efficiency of a RISC microprocessor can be improved by reducing the average instruction size. The memory traffic can be reduced and the energy efficiency consequently improved, if the allocation/de-allocation of registers can be organised such that interaction with the data cache is minimised. The examined branch architecture may improve performance but is not energy efficient. However, it shows that the Achilles' heel for performance is also the Achilles' heel for energy efficiency.

# **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or institution of learning.

# **Copyright Notice**

- (1) Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without permission (in writing) of the Author.

- (2) The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for the use of third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of Department of Computer Science.

## The Author

The author graduated from the Technical University of Denmark in January 1990 with a M.SC.EE degree. He joined Advance Computer Research Institute, ACRI, Lyon, France in February 1990 where he, as part of a small team, carried out a feasibility study for a supercomputer project. Later, as a part of the architecture group in ACRI, he wrote the reference model for the ACRI supercomputer architecture. Experience from this work was fed back as contributions to the architecture. The work involved working closely with both hardware and software groups. In February 1994 he joined the AMULET group at Manchester University Department of Computer Science as a research associate. He was working in the ESPRIT-funded HORN sub-group, which investigates ways to improve the energy efficiency of microprocessor architectures.

# **Acknowledgments**

This work has been supported as part of the ESPRIT project 7249, OMI/HORN. I am grateful for this support from the CEC and from SGS-Thomson Microelectronics, the project's prime contractor. I will especially like to thank Mark B. Hill, Andy Sturges and Mark Debbage of PACT, Bristol, for their feed-back in response to presentations, support of software tools and for their openness to queries about the HORN architecture. Furthermore I would like to thank Henk Muller, PACT for his suggestions on the graphical presentation of the simulation results in Chapter 9.

Dr. J.V. Woods, my supervisor, has been a constant source of encouragement. Especially, I would like to thank him for sending me to all the HORN status-meetings. The feed-back from these meetings has been very useful to me.

Thanks are due to Dr. Rhodri M. Davies. Rhods experience with software tools and languages has been valuable and has saved me a lot of time throughout the project. Furthermore I would like to thank him for his very complete proof-reading of this thesis.

During my time in ACRI, Dr. Peter L. Bird taught me many things about computer architecture which motivated me to pursue reseach within this field. I would like to thank him for convincing me that it was a feasible career move and for his encouragement to finish the work.

Finally, I will like to thank Mr. Alasdair Rawsthorne and Dr. Alan E. Knowles for having highlighted the opportunity here at Manchester University and for their support, especially during the difficult phase of settling in a new town and country.

## **Chapter 1 Introduction**

Microprocessors have conventionally been designed to yield maximum performance. Different design approaches have been taken and implementation technologies have improved significantly over the years. Early microprocessors such as the Z80 [Z80] had operating frequencies of approximately 1MHz. Today, in 1996, microprocessors such as the Pentium from INTEL runs at speeds of 200MHz [Child] and the Alpha [DEC21064] from Digital Equipment runs at more than 300MHz. These increases in processor speed have mainly been made possible through improvements in semiconductor technology and chip fabrication which have also allowed an increasing proportion of a computer system to be integrated onto one chip. As chips became larger it became possible to integrate, for example, larger register files and larger caches. Higher levels of integration also allowed architectural innovations such as pipelining [Patt] which overlaps phases of instruction execution and increases performance. Superscalar architectures such as the PowerPC [Gerosa] also became feasible to implement. These developments have resulted in constantly increasing performance.

In the drive for improved performance through higher integration little attention has been paid to power consumption. This thesis shows how architectural features and performance can be traded against power consumption to improve the performance-energy efficiency. The meaning of this term will be discussed at length in Chapter 4.

Improved performance-energy efficiency can be obtained by optimizing the architecture and the chip implementation. This work has examined architectural-level optimizations only, and the results presented are from a number of architectural models. Some implementation-related assumptions have been made; the sensitivity of the architectural results to these assumptions has been reduced as far as possible. The goal is to examine

whether architectural features which improve the performance of an architecture also improve the performance-energy efficiency.

Based upon the observation that caches in a typical Reduced Instruction Set Computer (RISC) processor affect both performance and energy consumption, a significant proportion of this thesis is devoted to an understanding of how cache parameters affect the performance-energy efficiency of a microprocessor system with the objective of specifying a performance-energy efficient cache architecture. Register-file and branch architectures are other key-components in a RISC architecture. Different types of register file and branch architectures are examined to gain an understanding of how they affect performance-energy efficiency. Finally the effect of ignoring the dogma, that RISC architectures must have fixed-size instructions is examined. During this examination a number of instruction-fetch mechanisms are developed; the 'eXtra-line architecture', described in section 8.3.3, is novel and represents a way of eliminating most of the disadvantages of variable size instructions while retaining the improved cache performance and performance-energy efficiency of this instruction format.

#### 1.1 Background

Compared to earlier 'Complex Instruction Set Computer', (CISC) processors such as the 8080 [Spack] and 68000 [Robin], the first RISC [Patt] architectures reduced the semantic content of instructions. Consequently, the instruction count increased. However, due to the simplification of the hardware, higher clock frequencies could be obtained and he overall effect was a *decrease* in execution time.

The quality of the compiler is an important factor in designing a efficient computer *system*. If the compiler takes account of pipeline length and register structure, the code can be scheduled to improve performance through optimized register allocation.

Computer system design is thus a two-branch discipline of providing both fast computer hardware and software tools which optimize the use of the hardware resources. The trend being that some increase in hardware complexity is accepted, if a subsequent reduction in execution time can justify it.

In order to reach the largest market, a wide software base needs to be available implying that binary compatibility must be preserved across a family of processors. The success of the Personal Computer (originally from IBM) can, in part, be explained in terms of the binary compatibility which has been retained through generations of PCs employing the Intel x86-processor family. Binary compatibility is less of an issue in the high-end workstation market, which is dominated by RISC architectures. However, some of the success of Sun's SPARC workstations is explained by the binary compatibility which exists between the different models.

As outlined above, microprocessor development has been driven almost solely by the wish to increase performance; power consumption has rarely been an issue. Improved packaging and cooling technologies, as well as improvements in the semiconductor technologies, have been sufficient to allow processor designers to ignore power consumption when specifying a microprocessor architecture.

It is only recently that computer architects have been forced to pay attention to the power consumption of microprocessors. At a chip level, the increased power consumption has implied that an increasing proportion of the chip area is used for power distribution; it has also implied an increasing number of bonding wires between the chip and the packaging. At a system level, larger and more expensive power supplies and cooling systems are required. To minimise these costs a processor architecture must now be optimized to yield a high performance within the constraints of a limited power consumption.

19

For example, in order to limit power consumption and thus use a relatively 'ordinary' packaging technology, Digital Equipment Corperation accesses the second-level cache in the Alpha processor in a sequential way: Two cycles to lookup and perform the tag comparison and, assuming a hit, a third cycle to read from the data storage thus reducing the power consumption of the processor by 10W (16% of the total power consumption) [Bensch]. It had become necessary to trade performance against power consumption. A performance-energy efficiency measure is useful when making such optimizations; i.e how can the performance remain high while the energy/power consumption is reduced. Chapter 4 shows that the Alpha processor is among the most performance-energy efficient processors currently available on the market (spring 1996).

There is currently a trend towards portable electronic equipment. Early portable computers, such as the first portable PC's, were portable only in that they had handles and that screen, keyboard etc. could be packed in a convenient way; they were still powered from the mains. Battery-driven lap-top computers were made possible by significant improvements in screen and battery technologies. However, battery life-time - or time between recharges - still leaves much to be desired. In recent years other portable products such as electronic personal organizers and mobile phones have also been introduced to the market.

Improvements in the performance-energy efficiency of microprocessors for the portable battery-driven market is not being driven by the high-end, highest-performance processor-market. ARM Ltd. has had considerable success with their microprocessors which have gained a reputation for delivering a 'reasonably' high performance for a relatively low power consumption. Targeting equipment such as portable telephones has brought considerable commercial success. Other markets include portable computers, electronic personal organizers and portable digital assistants (PDAs) such as the Apple

Newton [Culbert]. These products are becoming increasingly compact and do not contain devices such as cooling fans. A PDA will typically contain no mechanical device such as a hard disk, but will require significant computing power for complex tasks such as handwriting recognition. It should be able to perform tasks such as text formatting or spreadsheet calculations in parallel with the handwriting recognition task. This has to be done without increasing the power consumption significantly as such an increase implies a reduction in battery life-time and/or an increase in the weight due to the number, or size, of batteries. Despite the high performance requirement it is unlikely that the Alphaprocessor will be used in portable equipment where battery life time is a very important factor, because, although performance-energy efficient, it has a high power consumption.

To improve the performance of systems such as portable computers and PDAs *and* allow normal usage of these products for at least a working day (10 hours) the *performance-energy efficiency* of the microprocessor is an important measure. The power consumption and performance-energy efficiency of the microprocessor are thus key design-parameters in the product specification along with processor performance and memory size etc.

This performance-energy efficiency measure has been developed only recently. Consequently there is little literature available on performance-energy efficiency of microprocessors. Several conferences have 'low power' sessions, but papers presented tend to examine performance-energy efficiency/power efficiency of sub-systems, especially caches rather than considering the performance and energy consumption of the entire system. This thesis examines how the performance-energy efficiency of a complete microprocessor architecture can be optimized by trading architectural features and their performance against energy consumption.

The work reported in this thesis was carried out within the OMI-HORN project (ESPRIT project 7249). The goal for the group at Manchester University was to specify ways in

which the performance-energy efficiency of the HORN processor architecture [HORNV3] [HORNV5] can be improved. As a result much of the work reported centres around an already defined instruction set architecture. This has had the benefit that tools such as compilers, assemblers, functional simulators and some relatively complete libraries were available early in the project.

During the period of the project, some fundamental changes were made in the HORN architecture. The subsequent changes in the tool chain have allowed detailed comparisons between the different architectures. In addition extrapolations to other architectures have been made.

Early in the study it became clear that the power consumption in caches and I/O drivers are major factors in the total power consumption for a microprocessor chip. A detailed study of the ARM3-processor indicated that the 4Kbyte, unified, cache in an ARM3 [OMIMAP] processor consumes 46% of the total power consumption of the chip. A significant proportion of this thesis is therefore devoted to describing how cache parameters such as size, line size and associativity affect energy consumption, not only in the cache, but in the entire system.

Another important issue in performance-energy efficiency is execution time. Given that the project has centred around the HORN-processor, which is a RISC style processor, the instruction count and instruction format are important factors in the expression for execution time. Although the HORN-architecture is RISC-style, the instruction format is unusual in that instructions do not have a fixed size. The implications of this for instruction issuing and cache performance is analyzed in Chapter 10.

Furthermore, a number of register-file architectures have been analyzed. Register allocation handling has a significant influence on both performance and cache access pattern and hence the performance-energy efficiency of the entire processor system.

#### 1.2 Overview of thesis

Chapter 2 describes the power consumption pattern in the ARM3 processor. It reports the results presented in a deliverable to the OMI-MAP project [OMIMAP] which show that the cache consumes a significant proportion of the power in a standard microprocessor. These results are used as a basis for the rest of the work reported in this thesis. In addition, section 2.3 summarizes the power consumption in commercially available RAM.

Chapter 3 describes the HORN-processor architecture, which forms the basis of this work. The instruction format and various register file architectures which have been proposed throughout the specification phase of the project are presented. The special branch structure that the HORN architecture employs is also described. Section 3.5 describes the processor *system*, which will be considered the baseline system for the experiments described in the following chapters.

Chapter 4 discusses how performance-energy efficiency should be measured. The section divides the 'architecture space' into three classes and suggests metrics for each. For microprocessor architectures such as the HORN-architecture, the metric MIPS<sup>2</sup>/W was suggested. However T. Burd, University of California, Berkeley [Burd] has suggested an even more general measure based upon the energy-delay product which consequently was adopted. This metric is termed 'energy-efficiency' to comply with terms established in the literature. To establish a basis for comparison, performance and power consumption measures have been collected for a number of processors. The results are presented in section 4.2.

Not all applications can be evaluated using this metric. Many digital signal processing (DSP) applications have a throughput requirement which cannot be traded against lower energy consumption. The decision to use a metric based on the energy-delay product throughout the thesis implies that there should be no DSP-applications in the benchmark suite. Consequently a number of suitable benchmarks have been ported to the HORN architecture. This work has partly been done by Dr. R.M. Davies of the HORN-group, Department of Computer Science, Manchester University and partly by the author.

Chapter 5 establishes how energy consumption of a cache scales with the cache parameters and derives expressions for cache energy consumption. Section 5.1.1 summarizes results from a commercially available RAM-compiler. Based on circuit capacitances extracted from the Amulet2e [Garside]; expressions for energy consumption in RAM are developed. Sections 5.2 and 5.3 derive expressions for energy consumption in direct mapped and n-way set-associative caches.

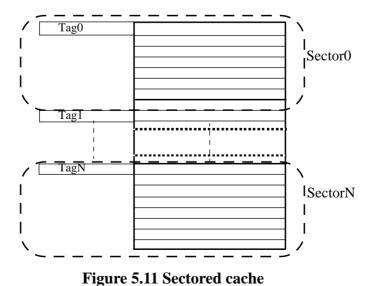

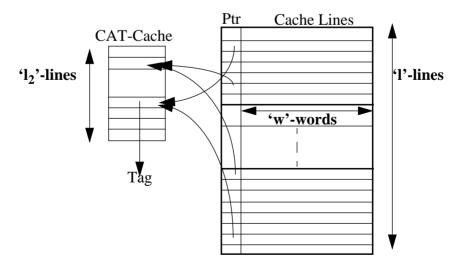

Based upon observations on redundancy in the tag storage of caches, [Seznec2][Wang] and [Burd] describe a number of cache architectures which can reduce/eliminate this redundancy. Section 5.4 quantifies the degree of redundancy and derives expressions for two of the organizations, sectored caching [Seznec2] and CAT-caching [Wang]. The results presented in these sections have been collected as a part of the author's work.

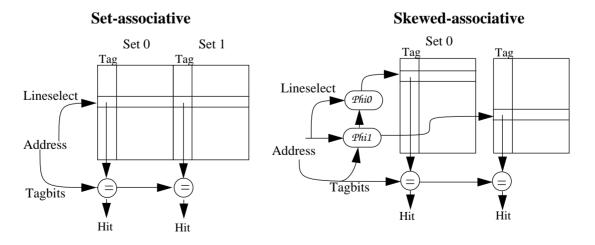

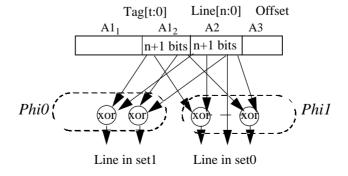

Section 5.5 describes skewed-associativity [Seznec] as a way of improving cache performance. Within a class of skewing function, it has been investigated whether an optimal set of functions exist, section 5.5.1 concludes that it is not the case. Section 5.6 quantifies the effect different replacement algorithms have on the hit rate in the cache. Section 5.7 describes how the cache parameters affect the timing of the cache. The relationships have been established using the Cacti-tool from Digital Equipment [Wilton].

Sections 5.8 - 5.11 describe techniques to reduce the activity and thereby the energy consumption within a cache.

Chapter 6 describes the effect of branch architectures on the performance and energy efficiency of a microprocessor system. Since the introduction of pipelines in processors, branch instructions have attracted much attention as they disrupt the flow of the pipeline and therefore affect the performance of the system. Many branch prediction schemes have been proposed [Patt] to limit this disruption.

Branch instructions may transfer control to locations which are not in the instruction cache hence affecting the performance negatively. An ability to prefetch the potential branch targets into the instruction cache is therefore beneficial. The HORN architecture specifies a branch structure which allows such prefetching. Chapter 6 assesses the value of the proposed branch instruction architecture both in terms of performance and in terms of energy efficiency. The section concludes that the dual-instruction branch architecture suggested in the HORN architecture is not energy efficient. All the work described and the results reported in Chapter 6 has been undertaken by the author as a part of the HORN project.

The register file architecture affects the instruction count (and thereby the performance). An 'insufficient' number of registers implies a high number of save-restore instructions, as 'old' register-variables are saved to memory to give room for new variables. The saved value may later need to be restored. The ability to allocate<sup>1</sup> new registers when required is therefore important. Increasing the number of registers is not always a suitable solution as more registers require more specification bits in the instructions, resulting in wider buses and lower instruction cache performance. Performance and energy efficiency must

<sup>1. &#</sup>x27;allocate' in this context means providing a new register. De-allocating is the opposite process, freeing a register.

thus be traded against the number of registers and the mechanisms to allocate new registers. Chapter 7 analyzes the different register-file architectures which have been suggested throughout for the HORN architecture. All the work reported in Chapter 7 has been carried out by the author.

The HORN architecture specifies variable-size instructions but now the instruction format requires more than four bytes. Compared to a conventional RISC architecture with fixed-size instructions such as MIPS R2000 [Farquhar], this ensures that a higher fraction of a program can reside in a cache of a given size; this implies a higher hit rate in the instruction cache. However, variable-size instructions introduce the problem that instructions may straddle cache lines and hence require two cache accesses to be fetched and issued. Chapter 8 proposes three cache architectures aimed at reducing these instances and evaluates them for performance and performance-energy efficiency. The architecture described in section 8.3.3, a novel extension to a block buffering scheme proposed by [Su], almost eliminates the performance penalty associated with variable size instructions. Finally, Chapter 9 evaluates the optimal cache configuration for both performance and energy efficiency. All the results presented in Chapter 9 have been collected by the author.

Chapter 10 draws together the conclusions resulting from this work, assesses the results and presents suggestions for future investigations.

## Chapter 2 Power consumption in an ARM3-system

To put the simulation results obtained with the HORN architecture into perspective a 'low power' and popular microprocessor family, the ARM processors are studied in this chapter.

The reasons for this choice were two-fold. Firstly, the ARM architecture has some features which resemble features of the HORN-architecture. It was therefore decided to extrapolate some of the results from this processor family onto the HORN-architecture. Secondly, the AMULET group at Manchester University has strong links with ARM Ltd. This has led to several projects amongst which the development of the asynchronous implementation of the ARM-architecture, in the AMULET-1 chip [Furber2], has attracted much attention. Furthermore, a number of ESPRIT projects have seen collaboration between the AMULET group and ARM Ltd. A deliverable to the OMI-MAP P5386 project [OMIMAP] has been particularly useful to this project and some of its main results will therefore be described here.

#### 2.1 Results from OMI-MAP

The processor analyzed in the OMI MAP project was an ARM3 processor which is an ARM2 processor core with a 4K-byte, fully-associative, unified on-chip cache with 256 lines of 16 bytes.

Instead of building a 256-entry CAM to form the tag-store which would have resulted in very high power consumption, ARM split the CAM into four blocks making it 64-way 4-set associative. This reduces the energy consumption of the overall cache by 21%, as only one quarter of the total CAM need be activated during cache lookups.

The power estimates were based upon two types of 'measurements': Spice simulations and estimates based upon the total switching capacity within the design.

The system was broken up into 7 major blocks:

- 1. A3RAM 1K x 32 bits SRAM

- 2. A3CAM 4 x 64 22 bit contents addressable memories (CAMs)

- 3. A3PROC ARM2 CPU macrocell

- 4. A3CTL Main Cache Control Logic

- 5. A3COP Co-processor interface

- 6. Cdata Internal databus (32 bits) RAM/PROC/Databus pads

- 7. PADS Input/output pads

The power consumption of each block is shown in Table 2.1 It is clear from the table that

Table 2.1 Estimated internal ARM3 power consumption

| Block  | Average Power<br>Consumption <sup>a</sup><br>[mW] | Percentage of<br>Total Power |

|--------|---------------------------------------------------|------------------------------|

| A3RAM  | 332                                               | 30.0                         |

| A3CAM  | 100                                               | 9.0                          |

| A3PROC | 330 (240) <sup>b</sup>                            | 29.8                         |

| A3CTL  | 91                                                | 8.2                          |

| A3COP  | 112 (64)                                          | 10.1                         |

| Cdata  | 50                                                | 4.5                          |

| PADS   | 91                                                | 8.2                          |

| Total  | 1106                                              | 100                          |

a. (based on 1.5 µm SPICE data)

the power consumption in the cache and in particular the RAM is a major factor in the total power consumption figure. The cache accounts for almost 40% of the total power

b. The numbers in parentheses indicate the power which

is consumed in PLAs within the block.

consumption. Reducing the power consumption in the cache will therefore yield a significant reduction in the total power consumption of the processor.

The OMI-MAP report also comments on the use of PLA<sup>1</sup>s in the processor implementation. PLAs are simple to implement, and simple to correct in case of mistakes; without disturbing the chip layout, something which might be required if the combinatorial logic was implemented using 'discrete' gates.

The report points out that the PLAs have a static power consumption component, accounting for 70% of the power consumed, implying that the static PLA technique is not appropriate for low power designs!

Table 2.2 shows how the total power consumption drops by 19% if static PLAs are avoided in the design. It also emphasizes the importance of the power consumption of the cache blocks since the percentage for A3RAM and A3CAM has increased to 48.4% or almost half of the total power budget.

Table 2.2 Internal ARM3 power consumption (PLA structures are omitted)

| Block  | Average Power<br>Consumption <sup>a</sup><br>[mW] | Percentage of<br>Total Power |

|--------|---------------------------------------------------|------------------------------|

| A3RAM  | 332                                               | 37.2                         |

| A3CAM  | 100                                               | 11.2                         |

| A3PROC | 162                                               | 18.1                         |

| A3CTL  | 91                                                | 10.2                         |

| A3COP  | 67                                                | 7.5                          |

| Cdata  | 50                                                | 5.6                          |

| PADS   | 91                                                | 10.2                         |

| Total  | 893                                               | 100                          |

a. based on 1.5 µm SPICE data

<sup>1.</sup> Programmable Logic Array

It is suggested that the static PLAs are replaced by dynamic PLAs; these use dynamic AND and OR planes to implement the PLA, with dummy terms to generate self-timing

signals to indicate when a result is valid at which point the PLA is put into its pre-charge

state and the output is latched [OMIMAP].

[OMIMAP] also gives an example of the area- and timing implications of using a dynamic

PLA in the case of the ALU control circuit, A3CTL:

Area:

Dynamic:

$452\lambda \times 684\lambda$

Static:

$410\lambda \times 579\lambda$

Delay:

Dynamic:

22.2ns

Static:

22.0ns

i.e. the area taken by the A3CTL-block increases by 30%; while the delay through the block increases by less than one percent when changing from the conventional static PLA

design to a dynamic design.

2.2 Evaluation of results

The ARM3 processor described in the previous section might be considered obsolete and

the value of the power measurements therefore questionable. However, a study of the

R3000 architecture from MIPS [BurdPeters], shows that the power consumption in that

processor is also dominated by the cache. The report describes power consumption

estimates by measuring the amount of switching capacity. It also reports that almost 10%

of the power consumed in the MIPS R3000 is consumed in the register file and that the

power consumption in the tag-storage of the 2-Kbyte instruction and data caches each

consume another 10% of the total power consumption. Comparing this value with that for the A3CAM in Table 2.2 shows that the proportion of energy/power consumed in the different blocks is similar in the R3000 and in the ARM3.

The development of the PA-RISC Microprocessor PA/50L [Okada] came to the same conclusion; that power is mainly consumed in internal memories and external signal drivers.

[Sato] reports on a tool, ESP, which is used to assess the implications of architectural changes on the power consumption. Results [Sato] confirm that caches are the dominating components, see Table 2.3.

Table 2.3 Current drawn of blocks in RISC processor [Sato]

| Block              | Current [mA] | Activity Rate [%] | Average<br>current<br>[mA] | % of total current |

|--------------------|--------------|-------------------|----------------------------|--------------------|

| Instruction cache  | 30.0         | 99.6              | 29.8                       | 38.9               |

| Branch unit        | 9.1          | 99.6              | 9.06                       | 11.8               |

| Increment addr.    | 0.1          | 99.6              | 0.10                       | 0.1                |

| Register file      | 13.0         | 97.4              | 13.64                      | 17.8               |

| ALU                | 9.1          | 59.0              | 5.37                       | 7.0                |

| Data cache         | 32.5         | 47.8              | 15.54                      | 20.2               |

| Address calculator | 9.1          | 30.1              | 2.74                       | 3.6                |

| Shifter            | 5.6          | 6.4               | 0.36                       | 0.5                |

| Multiply-Add unit  | 40           | 0.2               | 0.08                       | 0.1                |

|                    |              | Total:            | 76.8                       | 100                |

The power consumption of the main RAM-block in the cache is said to be independent, to a first degree, of the dimensions of the cache, due to other overheads, such as I/O buffers and sense amplifiers [BurdPeters]. However the detailed study of the ARM3, described above, shows that is not necessarily the case.

#### 2.3 Power consumption in RAM

As indicated in Tables 2.1 and 2.2, the power consumption of the cache RAM represents a significant proportion of the total power budget in the ARM3. [OMIMAP] also investigated where power is consumed within the RAM. The analysis was divided into two: a 'pre-charge read cycle' and a 'pre-charge write cycle'. This section gives a summary of the results and their implications for the HORN architecture.

Table 2.4 ARM3 RAM dissipation - Pre-charge/Read Cycle

| Block        | Average power consumption [mW] | Comments           | % of total power in RAM |

|--------------|--------------------------------|--------------------|-------------------------|

| ARM3 storage | 162.3                          | The main RAM array | 40.6                    |

| I/O buffers  | 68.3                           | CDATA bus          | 17.1                    |

| A3RAMrd8     | 81.0                           | 32-Sense Amps      | 20.3                    |

| ARM3row128   | 41.0                           | Decode+precharge   | 10.3                    |

| Other blocks | 47.4                           | -                  | 11.9                    |

| Total        | 400.0                          |                    | 100                     |

Table 2.4 shows the power consumption in the cache RAM during read cycles. It is clear that the storage itself is the major consumer of power, but I/O buffers and sense amplifiers represent a significant 37% of the RAM power budget during read cycles. Other blocks represent only a small percentage of the on-chip RAM power budget.

Table 2.5 ARM3 RAM dissipation - Pre-charge/Write Cycle

| Block        | Average power consumption [mW] | Comments           | % of total power in RAM |

|--------------|--------------------------------|--------------------|-------------------------|

| ARM3 storage | 162.3                          | The main RAM array | 64.9                    |

| I/O buffers  | 0.0                            | CDATA bus          | 0.0                     |

| A3RAMrd8     | 0.0                            | 32-Sense Amps      | 0.0                     |

| ARM3row128   | 41.0                           | Decode+precharge   | 16.4                    |

| Other blocks | 46.7                           | -                  | 18.7                    |

| Total        | 250.0                          |                    | 100                     |

Table 2.5 shows the equivalent results for a write cycle. The power consumed in the RAM block and in the decode/pre-charge is the same as during the read cycle, see Table 2.4. The

significant difference is that the sense amplifiers and the I/O buffers do *not* consume any power during a write cycle, resulting in a much lower total power consumption. A write cycle consumes only 63% of the energy of a read cycle. Note that the average power dissipation of 332mW quoted in Table 2.2 approximates to the average of the dissipation during read and write cycles. From [OMIMAP] it is not clear why the I/O drivers do not consume any power during write cycles. It will be assumed that the cost of driving the bit-lines is 'hidden' in 'Other blocks'.

The results in the two tables indicate that the sense amplifiers are important components with considerable impact on the power consumption of the cache and, thereby, of the entire processor.

Note that although the ARM3 cache is organised with 16-byte cache lines, the RAM block used for the storage of the cache contents is organised with only one (32-bit!) word per line within the RAM. Short lines/words in the RAM yield a lower energy consumption per request than longer lines, see Chapter 5.

#### 2.4 Summary

This chapter has reported where power is consumed within the ARM3. These results are from the OMI-MAP-project and show that a significant proportion of the power is consumed within the on-chip cache.

The power consumption of the cache has been split into components for the tag-store which, in the case of the ARM3, is composed of four CAM-cells and for the RAM-block which stores data. Tables 2.4 and 2.5 have shown that it is the RAM block together with the sense amplifiers consume the majority of the power. This leads to the conclusion that reducing the power consumption of the cache will reduce the power consumption of the

entire processor considerably. The results from this chapter are used to extrapolate the power consumption of the cache architectures proposed in later chapters.

Table 2.2 shows that there are further sub-designs which, if optimised for low power, could improve the performance-energy efficiency of a microprocessor system. This is particularly the case for the pad-drivers. Later chapters will show how Gray coding [Kohavi] can reduce the power consumption of this sub-design and thereby improve the energy-efficiency of the entire processor further.

## **Chapter 3 Baseline HORN architecture**

The baseline architecture used throughout this dissertation is the HORN architecture developed during OMI-HORN, Esprit project 7249.

Key attributes of the HORN architecture are:

- 1. Modularity

- 2. Compatibility over a range of products covering a wide range of processing and communications performance.

- 3. Support for multiprocessing.

- Provision for a standard programming model which eases the porting of operating systems, compilers and programming languages.

- 5. 64-bit processor supporting 32-bit operations.

Early releases of the architecture were targeted at the server market; systems with a high number of CPUs, capable of running multiple processes 'simultaneously'. This required optimization of the thread-change-overhead; i.e. minimising the 'state' which needed to be saved and providing efficient ways of saving that state. Efficient inter-processor communications protocols were also required.

During the development process the target markets for the processor changed. The new target markets are *multimedia* systems such as games, video-decoders and Set-Top Boxes (STB), but the processor also targets video-servers providing 'video on demand'. For these applications the thread changes are expected to be less frequent and the importance of fast thread changes is reduced.

This chapter describes the basic HORN architecture and summarizes the changes it has undergone. It does not describe any original work undertaken by the author but has been included to explain and justify the direction of the investigations described in later chapters.

Section 3.1 gives a general introduction to the HORN-architecture. Sections 3.2-3.4 describe the major features which differentiate the HORN architecture from a conventional RISC, while section 3.5 describes the system considered for this thesis.

#### 3.1 Basic architecture

The HORN architecture is fundamentally a RISC [Patt] in that arithmetic and logical instructions operate on register storage only. Only load and store instructions can access data in memory.

The processor is a byte-addressed, 64-bit processor, i.e. the internal and external data buses are 64 bits wide. Few existing programs require 64-bit variables and the HORN processor's instruction set offers a wide range of operations on sub-ranges: integers of 1,2,4 or 8 bytes and 32- and 64-bit floating point values. Furthermore, to make better use of the wide data bus, the processor includes a new class of instructions: packed arithmetic. These 'packed-arithmetic' instructions operate on a 64-bit quantity as a collection of smaller data quantities. Figure 3.1 shows an example of packed arithmetic, where eight bytes are packed into a 64-bit word and added to a similarly 'composed' word. The result is eight one-byte sums packed into a 64-bit word. Note that any overflow or carry from the eight individual operations is lost.

This technique is potentially very powerful and can be used by the compiler to unroll loops and hence increase the performance and energy efficiency of the processor. It is

|   | Byte 0           | Byte 1           | Byte 2           | Byte 3            | Byte 4            | Byte 5            | Byte 6            | Byte 7            |

|---|------------------|------------------|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| + | Byte 8           | Byte 9           | Byte10           | Byte 11           | Byte 12           | Byte 13           | Byte 14           | Byte 15           |

|   | Byte 0<br>Byte 8 | Byte 1<br>Byte 9 | Byte 2<br>Byte10 | Byte 3<br>Byte 11 | Byte 4<br>Byte 12 | Byte 5<br>Byte 13 | Byte 6<br>Byte 14 | Byte 7<br>Byte 15 |

Figure 3.1 Example of packed arithmetic

especially useful for graphics applications where the representation of pixel colours requires only a limited number of bits.

Memory referencing (load and store) instructions can access 1,2,4 and 8-byte quantities. References to these quantities need not be aligned, e.g. a reference to a 32-bit datum need not be aligned on a 4-byte boundary.

Furthermore the HORN architecture has broken away from the convention associated with the RISC concept, such as fixed-size instructions and has introduced a new type of control transfer instruction.

# 3.2 Local storage

During the project the form of local storage (register-file) structure has changed several times. This section briefly describes the different types of storage and their main advantages. Later chapters will describe the features of each architecture and evaluate their potential in a energy efficient implementation.

The register, or local-storage of the architecture was originally divided into three classes: Global registers, Local registers and a 4-word operand queue.

#### 3.2.1 Global registers

Global registers are intended to contain stack pointer(s), global variables and constants. Early versions of the HORN architecture mapped a block of 16 global registers to memory through a pointer, GPTR, which could be altered during program execution. This implemented register renaming; the contents of 'global-register N' before an adjustment of GPTR by 'M' could be accessed through 'global-register M+N' after the adjustment. Memory coherency was only ensured after the use of a special form of the 'adjust-global-pointer', ajgp-instruction. Later versions of the architecture considered the global registers as a conventional register block.

#### 3.2.2 Local registers

The architecture specifies 32 local registers. The local registers were also originally mapped to memory through a pointer, LPTR. The pointer was intended to be manipulated during execution of a program to allocate/deallocate registers at procedure entry/exit. Registers in scope did not need to be coherent with the memory location they mapped. This scheme will later be referred to as the 'ajlp-scheme' after the instruction which 'adjusted' the value of LPTR. As for the global registers, coherency was only ensured after the use of a special form of the ajlp instruction.

These schemes with memory mapped registers are very powerful in environments where thread-changes are frequent and therefore need to be fast. Saving the state of a register file (or restoring it) only requires the change of the two pointers, LPTR and GPTR, at the minimal cost of two instructions lasting only a few cycles.

As the architecture evolved and the product was targeted at multimedia applications, where there was less need for a fast context switch mechanism, the memory mapped scheme was replaced by register renaming instructions. These, in addition to renaming the

registers, also spilled/filled four registers to/from the memory hierarchy thereby effectively implementing register windows [Weaver]. This scheme will later be referred to as the 'spill/fill'-scheme after the instructions 'spill' and 'fill', which caused the actions just described. The difference between this and the more familiar SPARC register windows implementation [Weaver] is that once a register is out of scope in the HORN architecture, its contents should be visible to memory accessing instructions; this is not a requirement in the SPARC architecture.

While the spill/fill scheme might be simpler than the pointer schemes described above, it makes thread and context switches slower; there is now only one way of saving the state of the register file by spilling it to memory. The 'state-content' of the new thread can be installed using 'fill' instructions. This requires many more instructions than were required with the 'ajlp'-scheme described above: 32 registers / 4 registers-per-spill/fill = 8 instructions; it may also be much slower, dependent on the exact implementation of the two schemes.

## 3.2.3 Operand queue

The HORN processor has a set of temporary operand locations. These are organized as a four-entry first-in-first-out (FIFO) queue, which is accessed implicitly. The queue can replace any register reference in any instruction. This reduces the need to use registers for temporary variables and hence the need, temporarily, to store and later re-load, variables to/from the rest of the memory hierarchy.

Table 3.1 compares the result of compiling an expression into machine instructions in a conventional RISC and in the HORN processor. The RISC processor accesses six registers -  $R_A$ ,  $R_B$ ,  $R_C$ ,  $R_D$ ,  $R_E$ ,  $R_t$  - while the HORN processor will require only the five registers -  $R_A$ ,  $R_B$ ,  $R_C$ ,  $R_D$ ,  $R_E$ . The 'lifetime' of the variable in the temporary register ' $R_t$ '

**Table 3.1 Comparative register requirements**

Expression:

A = B \* C + D \* E

| RISC-code         | HORN-code                     |

|-------------------|-------------------------------|

| $R_A = R_B * R_C$ | Queue = $R_B * R_C$           |

| $R_t = R_D * R_E$ | Queue = $R_D * R_E$           |

| $R_A = R_A + R_t$ | R <sub>A</sub> =Queue + Queue |

in the RISC code is very short and it is unlikely that it will be required in future calculations; it has however increased the use of the register file and the contents of a register might have to be written to memory to release the space for the  $R_t$  value. This saved value might later need to be re-loaded from memory if it is required in later computations.

In the HORN architecture this extra register is not required as the temporary results will be stored in the FIFO-queue and as soon as they are consumed in the following instruction  $(R_A = \text{Queue} + \text{Queue})$  they will release their storage. It will therefore not be necessary to store any 'old' values to memory or to re-load them later.

Note, that the operand queue is a part of the state of the processor and the contents of the queue needs to be preserved across interrupts.

## 3.3 Branch architecture

'Control Transfer Instruction' (CTI) is a generic term for any instruction which can alter the execution flow of a program, such as a branch, jump or call. The actions of this class of instructions can be split into:

- 1. Compute the potential target

- 2. Evaluate a condition conditional branches only

- 3. Continue execution from the computed target

Some of the actions are orthogonal in that the potential target can be computed independently of the evaluation of the condition.

In modern, pipelined implementations of RISC architectures (see [Farquhar], [Weaver] and [DEC21064]) these three actions are usually combined in one 'branch', 'jump' or 'call' instruction. Due to pipelining it is often not possible to compute the succeeding instruction address fast enough to issue it correctly in the following cycle. Branch delay slot(s) were introduced [Patt] as a way of reducing or eliminating this penalty. Statistics showed that between 40 and 60% of delay slots following conditional branches could be filled and 90% following unconditional branches [Katevenis]. Recent architectures such as the PowerPC architecture [IBM] specify two versions of CTI's: 'Branch and Execute' which executed the instruction following the branch and conventional non-delay-slot branches rather than filling delay-slots with NOP<sup>1</sup>-instructions. The HP-Precision Architecture [Mahon] left it as a part of the instruction to specify whether the following instruction was a delay slot instruction.

The HORN architecture takes a different approach to branching in that it separates the actions into two classes of instructions, the 'go' and the 'leap' class. The computation of the target is split from the evaluation of the condition, thus requiring two instructions per CTI.

The 'go' class of instructions sets up the potential target for the branch; there are a variety of formats covering PC relative offsets, absolute addressing and register relative offsets. Note that a 'go-class' instruction overrides the effect of a previous 'go-class' instruction.

Once the potential target has been set up, the condition is evaluated using the 'leap' class of instructions. Leap-instructions evaluate the contents of a register for a number of

Baseline HORN architecture

<sup>1.</sup> NOP = No OPeration

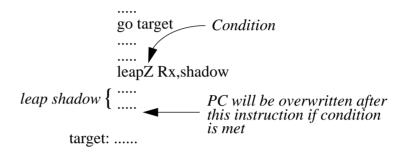

Figure 3.2 Example of a go-instruction outside a loop body

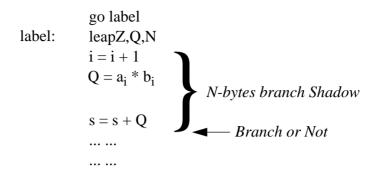

conditions ranging from un-conditional to conditions such as 'zero', 'negative', 'positive or zero'. The value to be evaluated must be held in the local storage, see section 3.2. Furthermore 'leap' instructions specify *when*, relative to its position, the execution route should be altered if the condition evaluation is positive. This is implemented by specifying a *variable leap shadow* - a number of bytes, potentially covering several instructions, between the leap instruction and the branch location.

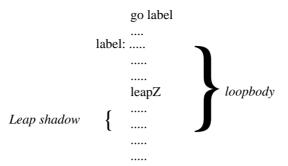

This scheme allows the set up of a target instruction stream in advance and allows prefetching of instructions into the cache and/or into a shadow pipeline. The value of this technique will be explored in Chapter 6. Furthermore, in the case of a simple loop the compiler can migrate the go-class instruction outside the loop body and hence reduce the number of instructions issued inside a loop, see Figure 3.2.

This scheme is more flexible than that employed in many commercially available RISC machines such as the SPARC [Weaver]. In these architectures, the size of the branch delay slot is fixed at one instruction, and there is often a significant branch penalty associated with misprediction. With the HORN architecture this mispredicted branch penalty might be eliminated if it is possible for the compiler to migrate the leap-instruction far enough back in the instruction stream.

Figure 3.3 illustrates how the leap instruction can migrate to the very top of the loop body. As the figure illustrates there is now plenty of time to evaluate the outcome of the

Figure 3.3 Optimal migration of the 'go' and 'leap' instructions