# STRATEGIES FOR THE MODELLING AND SIMULATION OF ASYNCHRONOUS COMPUTER ARCHITECTURES

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

IN THE FACULTY OF SCIENCE AND ENGINEERING

September 1995

By

${\bf Georgios\ Theodoropoulos}$

Department of Computer Science

# Contents

| A            | Abstract                    |                                               |    |  |  |

|--------------|-----------------------------|-----------------------------------------------|----|--|--|

| $\mathbf{T}$ | he aı                       | ithor                                         | 19 |  |  |

| A            | ckno                        | wledgements                                   | 22 |  |  |

| 1            | roduction                   | 23                                            |    |  |  |

|              | 1.1                         | Background                                    | 23 |  |  |

|              | 1.2                         | Motivation and Objectives                     | 23 |  |  |

|              | 1.3                         | Structure of the Thesis                       | 24 |  |  |

|              |                             | 1.3.1 Related Publications                    | 26 |  |  |

| 2            | $\operatorname{Th}\epsilon$ | Quest for High Performance                    | 27 |  |  |

|              | 2.1                         | Introduction                                  | 27 |  |  |

|              | 2.2                         | Bit and Instruction Level Parallelism         | 28 |  |  |

|              | 2.3                         | Reduced Instruction Set Computers             | 29 |  |  |

|              | 2.4                         | The Limits of Sequential Computation          | 30 |  |  |

|              | 2.5                         | Parallel Computer Architectures               | 31 |  |  |

|              |                             | 2.5.1 SIMD                                    | 32 |  |  |

|              |                             | 2.5.2 MIMD                                    | 33 |  |  |

|              |                             | 2.5.2.1 Shared Memory MIMD Architectures      | 33 |  |  |

|              |                             | 2.5.2.2 Distributed Memory MIMD Architectures | 35 |  |  |

|   |     | 2.5.3 Parallel Programming Models and Languages |            |                                           |    |

|---|-----|-------------------------------------------------|------------|-------------------------------------------|----|

|   |     |                                                 | 2.5.3.1    | Communicating Sequential Processes        | 37 |

|   | 2.6 | Occan                                           | and the    | Transputer                                | 38 |

|   |     | 2.6.1                                           | The Occ    | cam Programming Language                  | 38 |

|   |     |                                                 | 2.6.1.1    | The SEQ and PAR Constructs                | 40 |

|   |     |                                                 | 2.6.1.2    | The ALT Construct                         | 41 |

|   |     |                                                 | 2.6.1.3    | Timers                                    | 42 |

|   |     |                                                 | 2.6.1.4    | Functions and Procedures                  | 45 |

|   |     | 2.6.2                                           | The Tra    | nsputer                                   | 45 |

|   |     |                                                 | 2.6.2.1    | Configuring Occam Programs                | 48 |

|   |     |                                                 | 2.6.2.2    | The T9000 Transputer                      | 49 |

|   | 2.7 | Summ                                            | ary        |                                           | 50 |

| 3 | Mod | delling                                         | and Sin    | nulation                                  | 51 |

|   | 3.1 | Introd                                          | uction .   |                                           | 51 |

|   | 3.2 | Discre                                          | te Event   | Simulation Modelling                      | 55 |

|   | 3.3 | The N                                           | eed for P  | arallel Discrete Event Simulation         | 57 |

|   |     | 3.3.1                                           | Exploiti   | ng Parallelism                            | 58 |

|   | 3.4 | The L                                           | ogical Pro | ocess Paradigm                            | 60 |

|   |     | 3.4.1                                           | Timing     | Issues                                    | 61 |

|   | 3.5 | Synch                                           | ronous ve  | rsus Asynchronous Simulation              | 63 |

|   | 3.6 | Time                                            | Driven Lo  | ogical Process Simulation                 | 64 |

|   | 3.7 | Event                                           | Driven L   | ogical Process Simulation                 | 65 |

|   |     | 3.7.1                                           | Conserv    | ative Techniques                          | 67 |

|   |     |                                                 | 3.7.1.1    | Deadlock Avoidance                        | 68 |

|   |     |                                                 | 3.7.1.2    | Deadlock Detection and Recovery           | 70 |

|   |     |                                                 | 3.7.1.3    | Characteristics of Conservative Protocols | 70 |

|   | 3.8 | 0.4:                                            | iatia Crm  | chronization Protocols                    | 71 |

|   |      | 3.8.1  | Time W    | arp                                               | 72 |

|---|------|--------|-----------|---------------------------------------------------|----|

|   |      |        | 3.8.1.1   | Global Virtual Time                               | 72 |

|   |      |        | 3.8.1.2   | State Saving and Memory Management                | 73 |

|   |      |        | 3.8.1.3   | Characteristics of Optimistic Protocols           | 74 |

|   | 3.9  | Model  | ling and  | Simulation in Computer Architecture Research      | 74 |

|   |      | 3.9.1  | The Nee   | ed for Improved Digital System Simulation Perfor- |    |

|   |      |        | mance     |                                                   | 78 |

|   |      |        | 3.9.1.1   | Parallel Digital System Simulation                | 78 |

|   | 3.10 | Summ   | ary       |                                                   | 80 |

| 4 | Asy  | nchroi | nous Sys  | etems                                             | 81 |

|   | 4.1  | Introd | uction .  |                                                   | 81 |

|   | 4.2  | Advan  | itages of | Asynchronous Systems                              | 82 |

|   |      | 4.2.1  | Clock D   | istribution Problems                              | 83 |

|   |      | 4.2.2  | Potentia  | al for Low Power                                  | 83 |

|   |      | 4.2.3  | Potentia  | al for High Performance                           | 84 |

|   |      | 4.2.4  | Better 7  | Technology Migration Potential                    | 85 |

|   | 4.3  | Basic  | Characte  | ristics of Asynchronous Systems                   | 85 |

|   |      | 4.3.1  | Timing    | Model                                             | 85 |

|   |      | 4.3.2  | Signallin | ng Protocols                                      | 86 |

|   |      |        | 4.3.2.1   | Two-phase Signalling                              | 86 |

|   |      |        | 4.3.2.2   | Four-phase Signalling                             | 87 |

|   |      | 4.3.3  | Data Pa   | assing Techniques                                 | 88 |

|   |      |        | 4.3.3.1   | The Four-Wire Technique                           | 88 |

|   |      |        | 4.3.3.2   | The Three-Wire Technique                          | 88 |

|   |      |        | 4.3.3.3   | The Two-Plus-Wire Technique                       | 89 |

|   |      |        | 4.3.3.4   | The Bundled Data Technique                        | 90 |

|   | 4.4  | Micro  | pipelines |                                                   | 90 |

|   |     | 4.4.1   | Event Control Elements                  |

|---|-----|---------|-----------------------------------------|

|   |     | 4.4.2   | Event Controlled Storage Element        |

|   |     | 4.4.3   | Micropipelines Without Processing       |

|   |     | 4.4.4   | Micropipelines With Processing          |

|   | 4.5 | AMUI    | LET                                     |

|   | 4.6 | The A   | MULET1 Microprocessor                   |

|   |     | 4.6.1   | The AMULET1 Interface                   |

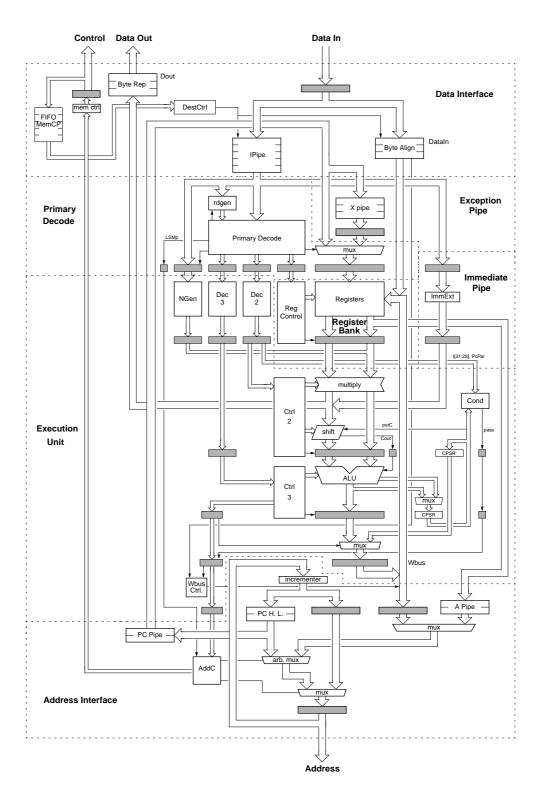

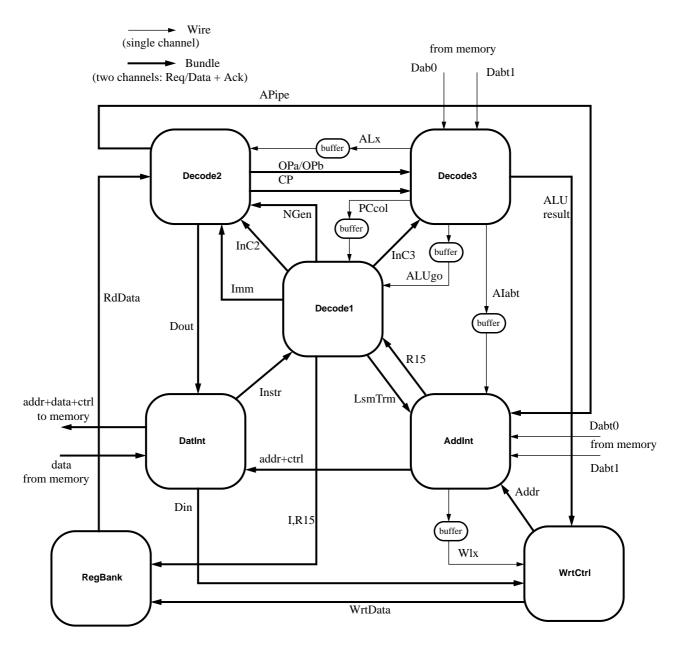

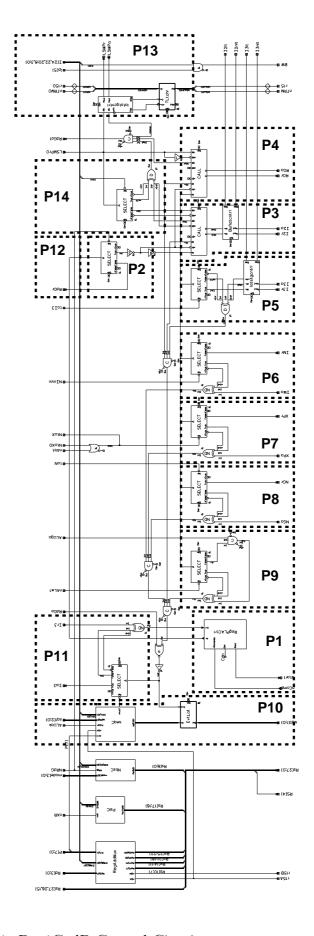

|   |     | 4.6.2   | The AMULET1 Internal Organization 100   |

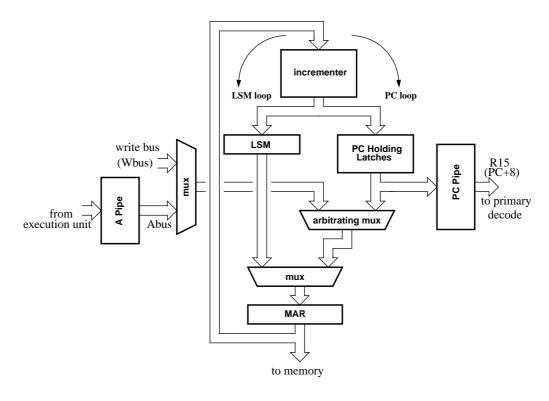

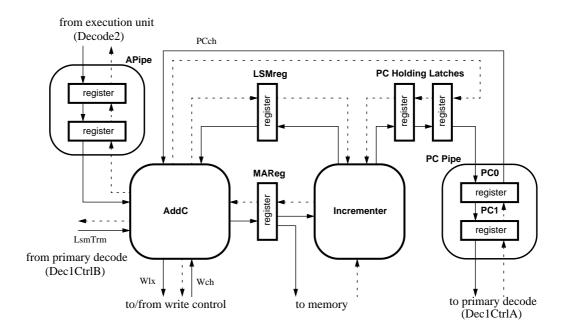

|   |     |         | 4.6.2.1 The Address Interface Unit 100  |

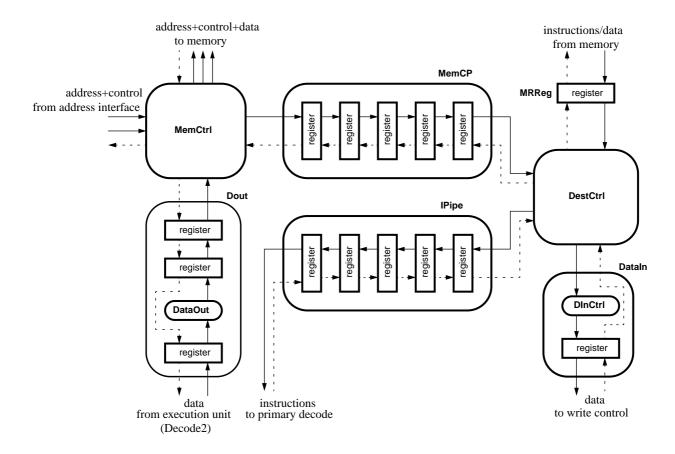

|   |     |         | 4.6.2.2 The Data Interface Unit         |

|   |     |         | 4.6.2.3 The Register Bank Unit          |

|   |     |         | 4.6.2.4 The Execution Unit              |

|   |     |         | 4.6.2.5 The Primary Decode Unit         |

|   |     | 4.6.3   | AMULET2                                 |

|   | 4.7 | Summ    | ary                                     |

| 5 | Mod | delling | Asynchronous Systems 107                |

|   | 5.1 | Introd  | uction                                  |

|   | 5.2 | Model   | ling Techniques                         |

|   |     | 5.2.1   | CSP-based Modelling Approaches          |

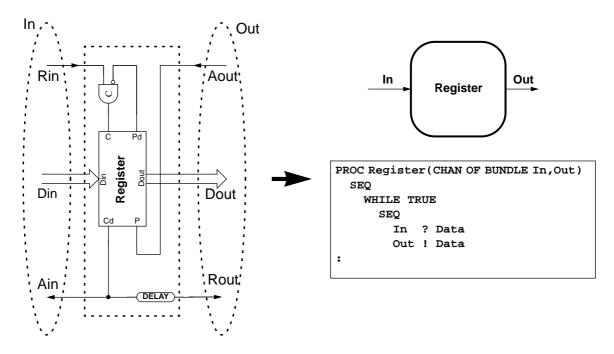

|   | 5.3 | Model   | ling Micropipelined Systems with Occam  |

|   |     | 5.3.1   | Why Occam                               |

|   |     |         | 5.3.1.1 The Deadlock Problem            |

|   |     | 5.3.2   | The Modelling Philosophy                |

|   |     | 5.3.3   | Modelling a Pipeline Without Processing |

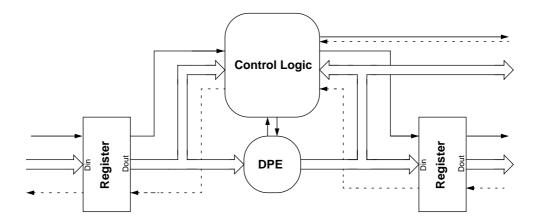

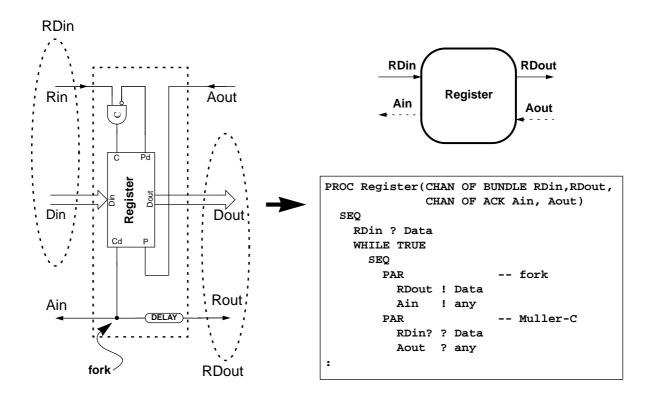

|   |     | 5.3.4   | Modelling a Pipeline With Processing    |

|   |     | 5.3.5   | Modelling Control Logic                 |

|   |     | 5.3.6   | Timing Issues                           |

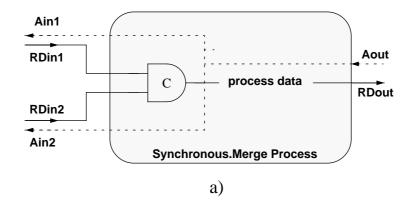

|   |     |        | 5.3.6.1   | Synchronous Merge                     | 120 |

|---|-----|--------|-----------|---------------------------------------|-----|

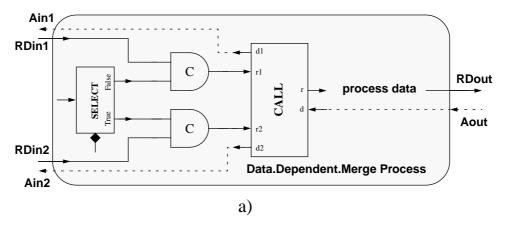

|   |     |        | 5.3.6.2   | Data Dependent Merge                  | 121 |

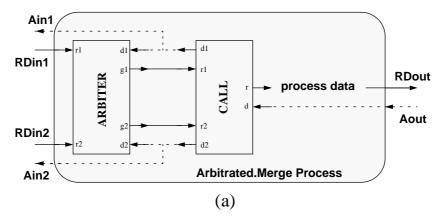

|   |     |        | 5.3.6.3   | Arbitrated Merge                      | 122 |

|   |     |        | 5.3.6.4   | Delay Independence                    | 125 |

|   | 5.4 | Summ   | nary      |                                       | 126 |

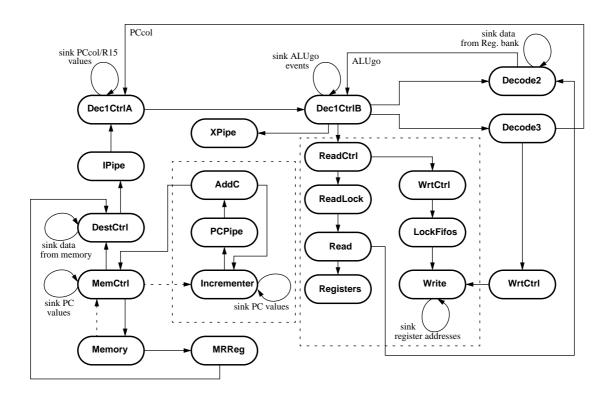

| 6 | Occ | arm:   | An Occa   | m Model of AMULET1                    | 127 |

|   | 6.1 | Introd | luction . |                                       | 127 |

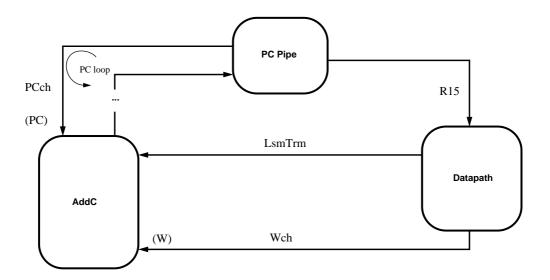

|   | 6.2 | Occar  | m Genera  | l Structure                           | 128 |

|   |     | 6.2.1  | Non-Bu    | ndled Signals                         | 130 |

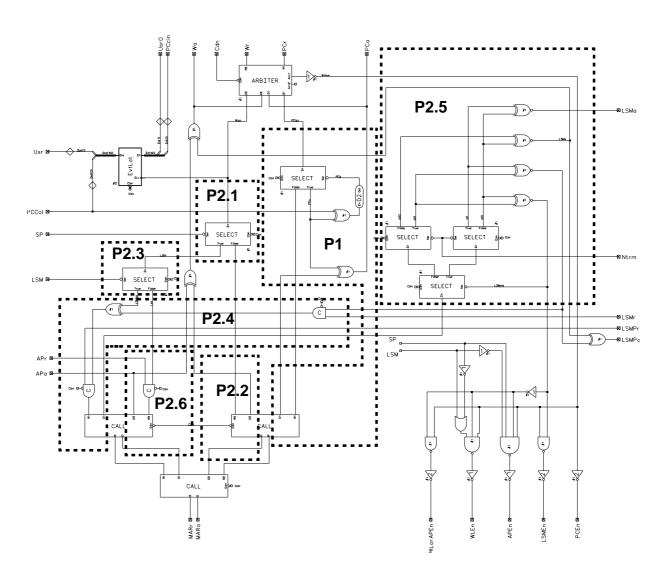

|   | 6.3 | The A  | ddress In | terface                               | 131 |

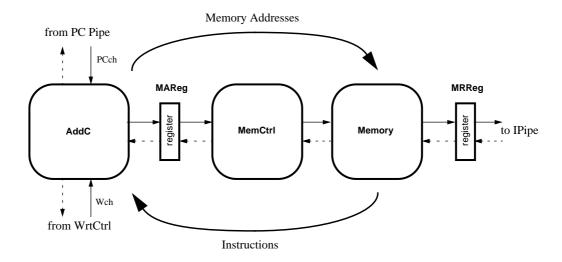

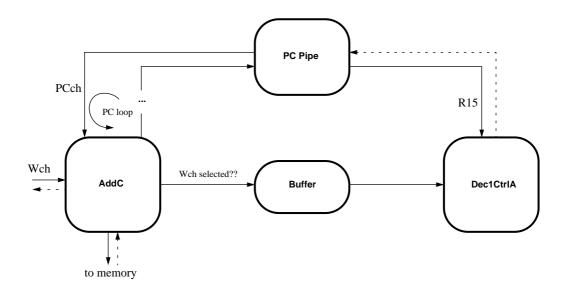

|   |     | 6.3.1  | The Ado   | dress Interface Internal Organization | 131 |

|   |     |        | 6.3.1.1   | The PC Loop                           | 131 |

|   |     |        | 6.3.1.2   | The PC Pipe                           | 133 |

|   |     |        | 6.3.1.3   | The LSM Loop                          | 134 |

|   |     | 6.3.2  | The Ado   | dress Interface Occam Model           | 135 |

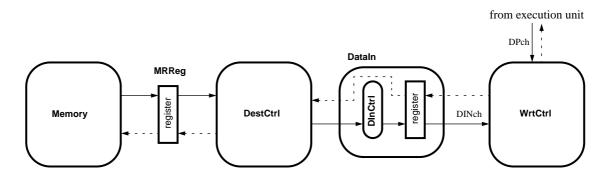

|   | 6.4 | The D  | ata Inter | face                                  | 137 |

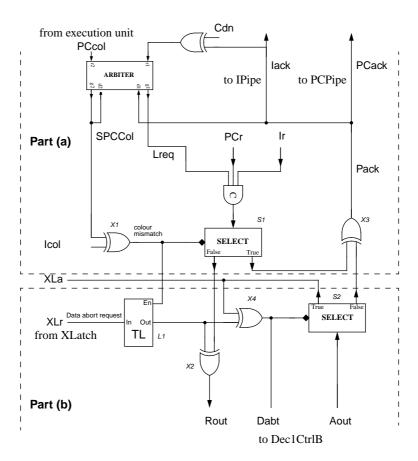

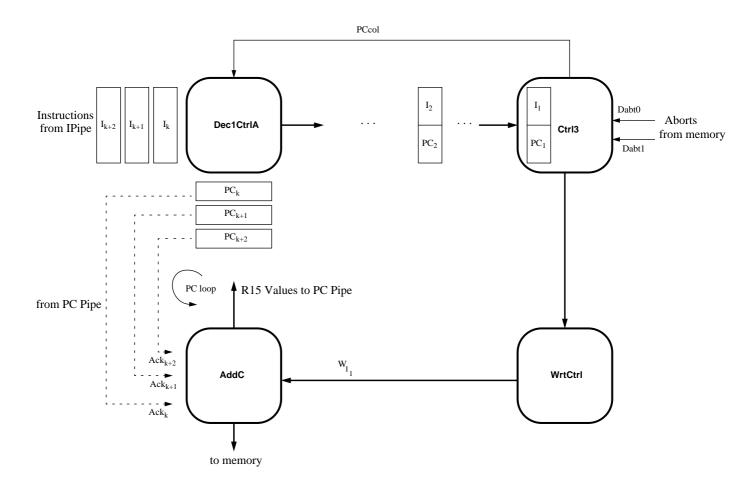

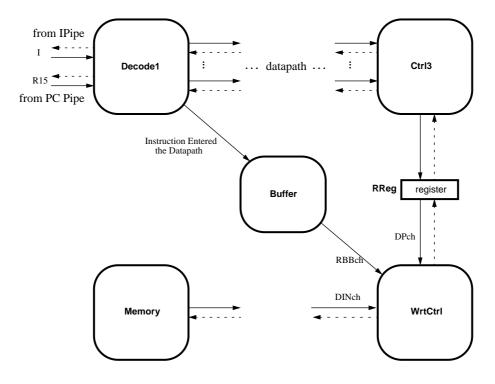

|   | 6.5 | Instru | ction Flo | w Control                             | 139 |

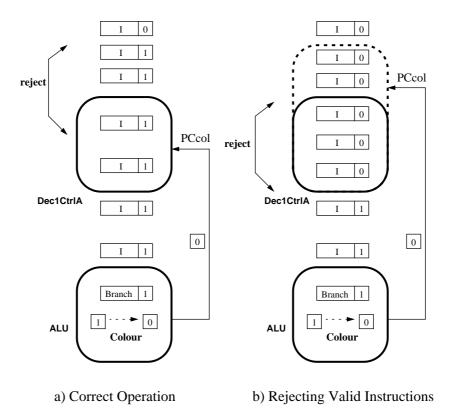

|   |     | 6.5.1  | Conditio  | on Code Evaluation                    | 140 |

|   |     | 6.5.2  | Branch    | Execution                             | 140 |

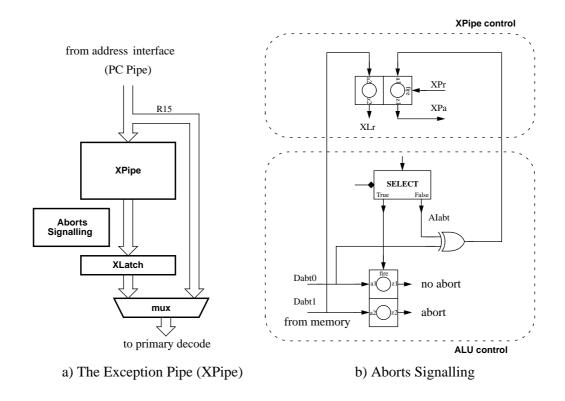

|   |     | 6.5.3  | Exception | on Handling                           | 142 |

|   |     |        | 6.5.3.1   | Software Interrupts                   | 143 |

|   |     |        | 6.5.3.2   | Instruction Prefetch Aborts           | 143 |

|   |     |        | 6.5.3.3   | Hardware Interrupts                   | 143 |

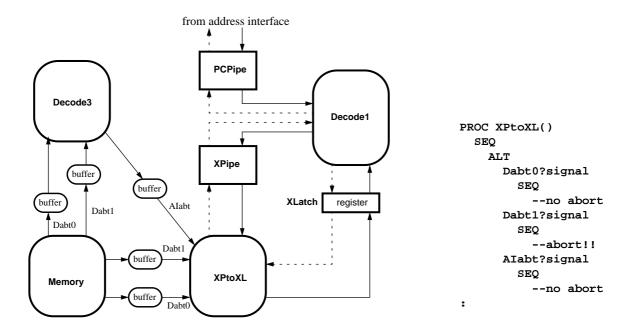

|   |     |        | 6.5.3.4   | Data Transfer Aborts                  | 144 |

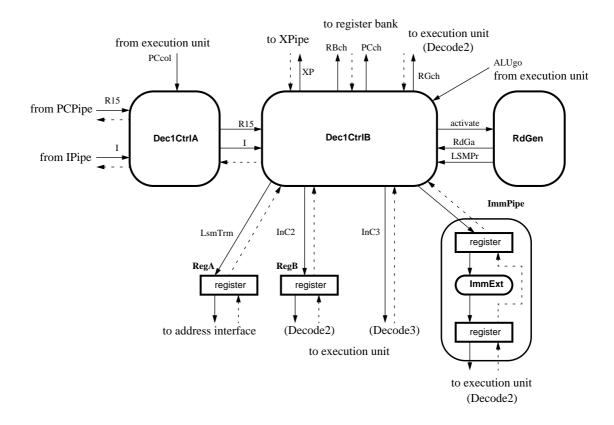

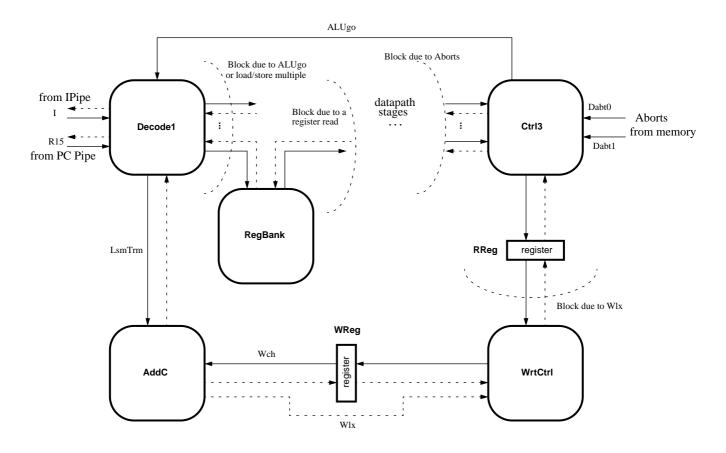

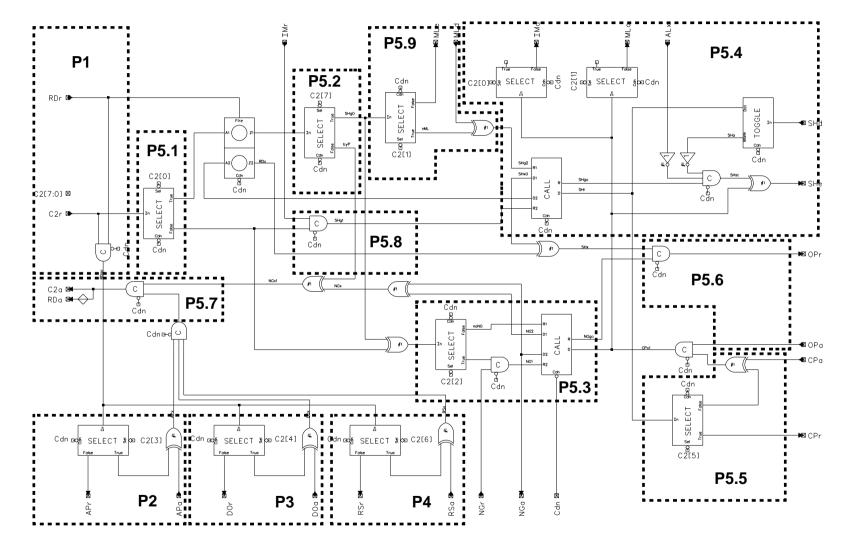

|   | 6.6 | The P  | rimary D  | ecode                                 | 147 |

|   |     | 6.6.1  | The Dec   | e1CtrlA Process                       | 148 |

|   |     |        | 6.6.1.1   | Modelling of the Arbitration logic    | 149 |

|   |      |         | 6.6.1.2     | Detecting Da   | ata Abort | S        |       |    | <br> | <br>152 |

|---|------|---------|-------------|----------------|-----------|----------|-------|----|------|---------|

|   |      | 6.6.2   | The Dec     | 1CtrlB Proces  | SS        |          |       |    | <br> | <br>154 |

|   | 6.7  | The R   | egister Ba  | nk             |           |          |       |    | <br> | <br>155 |

|   |      | 6.7.1   | Modellin    | g the Registe  | r Bank .  |          |       |    | <br> | <br>157 |

|   | 6.8  | The E   | xecution V  | Unit Model .   |           |          |       |    | <br> | <br>160 |

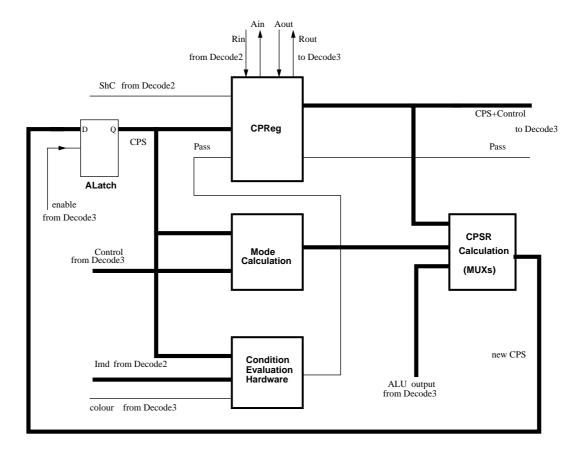

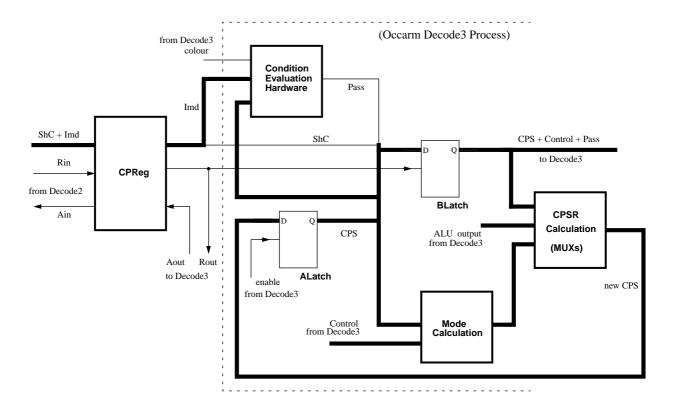

|   |      | 6.8.1   | The CPS     | SR Model       |           |          |       |    | <br> | <br>161 |

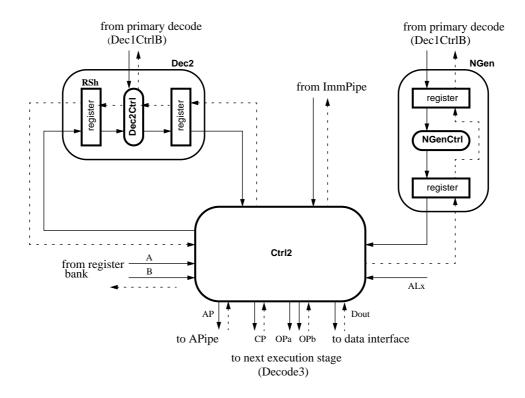

|   |      | 6.8.2   | Decode2     |                |           |          |       |    | <br> | <br>162 |

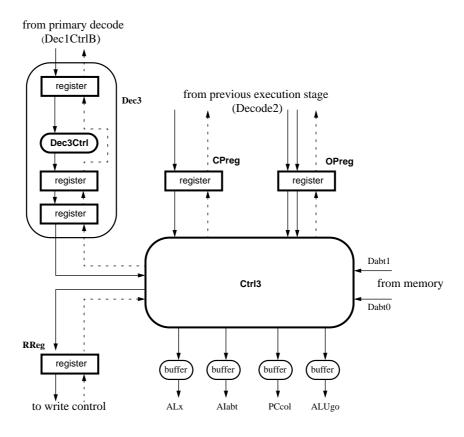

|   |      | 6.8.3   | Decode3     |                |           |          |       |    | <br> | <br>164 |

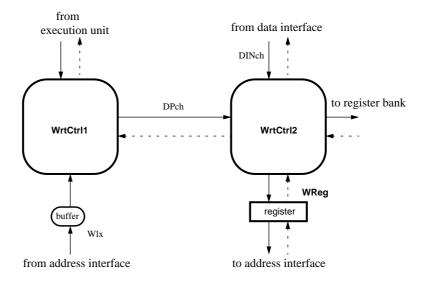

|   | 6.9  | The W   | Trite Bus ( | Control        |           |          |       |    | <br> | <br>165 |

|   | 6.10 | Summ    | ary         |                |           |          |       |    | <br> | <br>166 |

| 7 | Sim  | ulatior | ı Issues    |                |           |          |       |    |      | 168     |

|   | 7.1  | Introd  | uction      |                |           |          |       |    | <br> | <br>168 |

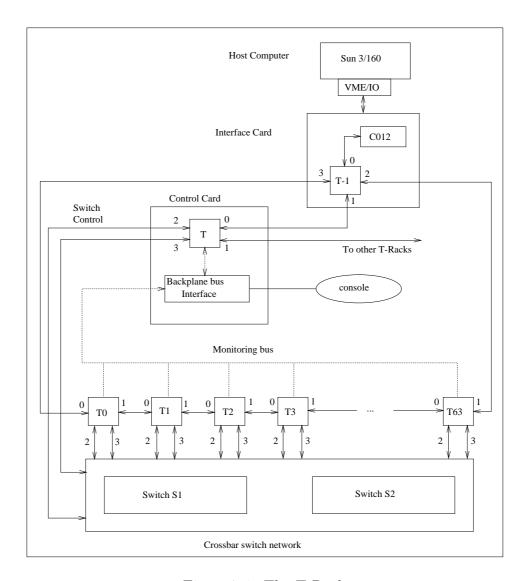

|   | 7.2  | The H   | ost Machi   | ne: The ParS   | SiFal T-R | ack      |       |    | <br> | <br>169 |

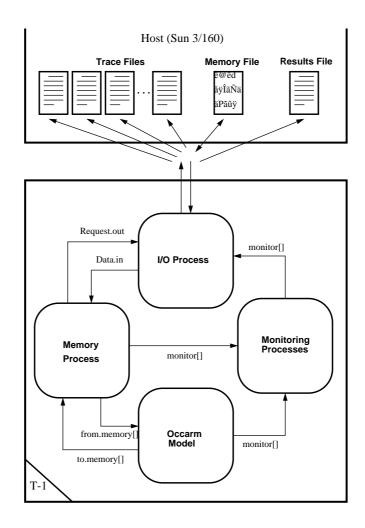

|   | 7.3  | Monito  | oring       |                |           |          |       |    | <br> | <br>171 |

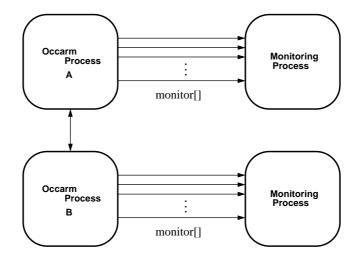

|   |      | 7.3.1   | Monitori    | ng Occarm .    |           |          |       |    | <br> | <br>175 |

|   |      |         | 7.3.1.1     | Debugging .    |           |          |       |    | <br> | <br>176 |

|   |      |         | 7.3.1.2     | Performance    | Evaluati  | on       |       |    | <br> | <br>177 |

|   | 7.4  | Termin  | nation      |                |           |          |       |    | <br> | <br>180 |

|   | 7.5  | The Si  | mulator I   | Environment    |           |          |       |    | <br> | <br>182 |

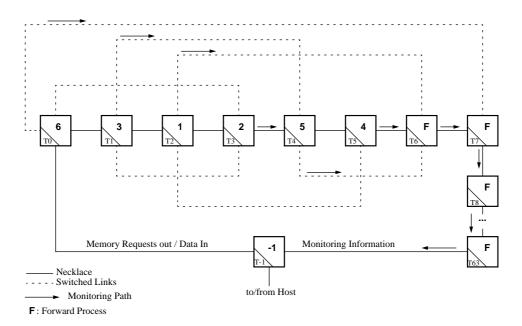

|   | 7.6  | Multip  | processor l | Implementation | on        |          |       |    | <br> | <br>183 |

|   |      | 7.6.1   | Mapping     | Occarm onto    | the T-R   | ack .    |       |    | <br> | <br>184 |

|   |      |         | 7.6.1.1     | Balancing th   | e Worklo  | ad       |       |    | <br> | <br>186 |

|   |      |         | 7.6.1.2     | Balancing th   | e Commu   | ınicatio | on Lo | ad | <br> | <br>187 |

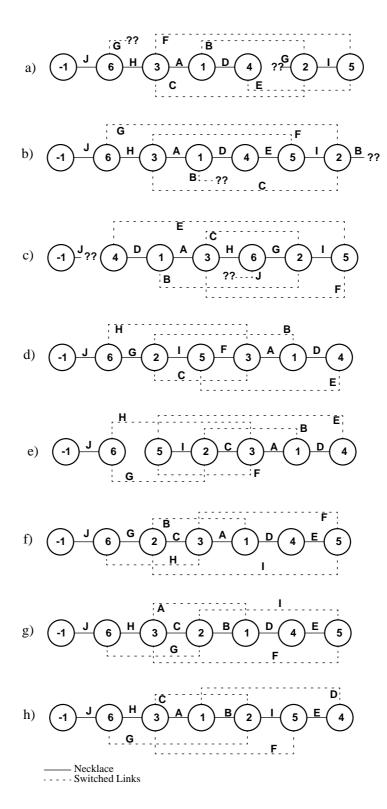

|   |      |         | 7.6.1.3     | The Monitor    | ing Path  |          |       |    | <br> | <br>190 |

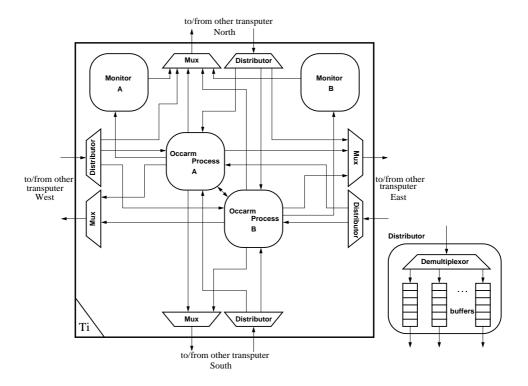

|   |      |         | 7.6.1.4     | The Generic    | Simulato  | or Node  | ·     |    | <br> | <br>191 |

|   | 7.7  | Summ    | ary         |                |           |          |       |    | <br> | <br>191 |

| 8 | Val            | idation | of the    | Occarm Model                             | 192 |

|---|----------------|---------|-----------|------------------------------------------|-----|

|   | 8.1            | Introd  | luction . |                                          | 192 |

|   | 8.2            | Bench   | mark Pro  | grams                                    | 193 |

|   | 8.3            | Accur   | acy       |                                          | 195 |

|   | 8.4            | Perfor  | mance.    |                                          | 204 |

|   | 8.5            | Summ    | nary      |                                          | 208 |

| 9 | $\mathbf{Adc}$ | dressin | g the Ti  | me Modelling Problem                     | 209 |

|   | 9.1            | Introd  | luction . |                                          | 209 |

|   | 9.2            | Requi   | rements   |                                          | 210 |

|   | 9.3            | The P   | rogram D  | Oriven Synchronization Protocol (PDSP)   | 211 |

|   |                | 9.3.1   | The Bas   | is                                       | 211 |

|   |                | 9.3.2   | The Rul   | es                                       | 212 |

|   |                | 9.3.3   | The PD    | SP Arbiter Process                       | 213 |

|   |                |         | 9.3.3.1   | Improving PDSP Performance               | 214 |

|   |                | 9.3.4   | The Lin   | nitations                                | 216 |

|   | 9.4            | Apply   | ing PDSF  | o to Occarm                              | 217 |

|   | 9.5            | The A   | ddress In | terface Arbiter                          | 218 |

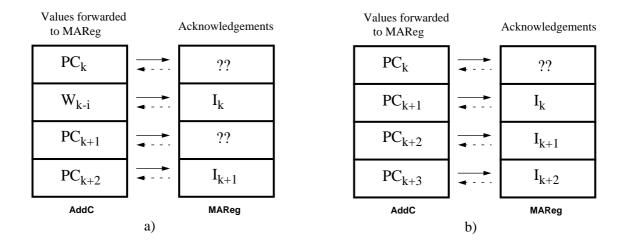

|   |                | 9.5.1   | Providin  | g Instruction Lookahead Information      | 218 |

|   |                | 9.5.2   | The PC    | ch Link                                  | 221 |

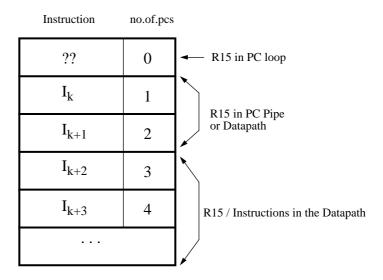

|   |                |         | 9.5.2.1   | Filling of the Datapath                  | 224 |

|   |                |         | 9.5.2.2   | Register Read Instructions               | 230 |

|   |                |         | 9.5.2.3   | Instructions Activating the ALUgo Signal | 232 |

|   |                |         | 9.5.2.4   | Load/Store Multiple Instructions         | 233 |

|   |                |         | 9.5.2.5   | The Instruction Lookahead Table          | 233 |

|   |                | 9.5.3   | The Wc    | h Link                                   | 234 |

|   |                |         | 9.5.3.1   | Colour Mismatch                          | 235 |

|   |                |         | 9532      | Condition Codes Failure                  | 236 |

|               | 9.6   | The Primary Decode Arbiter                                   | 238         |

|---------------|-------|--------------------------------------------------------------|-------------|

|               | 9.7   | The Write Control Arbiter                                    | 242         |

|               |       | 9.7.1 The DINch Link                                         | 242         |

|               |       | 9.7.2 The DPch Link                                          | 244         |

|               | 9.8   | Performance Evaluation of PDSP                               | 248         |

|               | 9.9   | Summary                                                      | 249         |

| 10            | Con   | clusions and Further Work                                    | <b>25</b> 0 |

|               | 10.1  | Background                                                   | 250         |

|               | 10.2  | Contribution of the Thesis                                   | 252         |

|               |       | 10.2.1 Modelling                                             | 252         |

|               |       | 10.2.2 Simulation                                            | 253         |

|               | 10.3  | The Program Driven Synchronization Protocol                  | 255         |

|               | 10.4  | Performance                                                  | 256         |

|               | 10.5  | Occam as an Asynchronous Hardware Description Language $\ .$ | 257         |

|               | 10.6  | Further Work                                                 | 258         |

|               |       | 10.6.1 Modelling and Simulation                              | 258         |

|               |       | 10.6.2 Automatic Synthesis                                   | 259         |

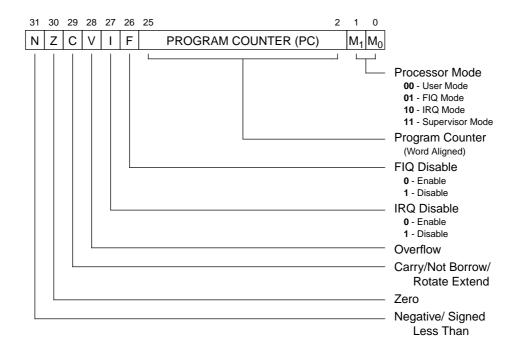

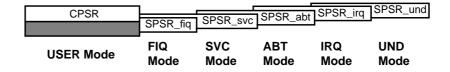

| $\mathbf{A}$  | The   | ARM6 Programmer's Model                                      | <b>26</b> 0 |

|               | A.1   | The Registers                                                | 260         |

|               | A.2   | The Instruction Set                                          | 262         |

| В             | Mod   | delling the Control Logic of AMULET1                         | 266         |

| $\mathbf{Bi}$ | bliog | raphy                                                        | 277         |

# List of Tables

| 7.1 | Communication Load on Occarm Links                        |

|-----|-----------------------------------------------------------|

| 8.1 | Timestamp Drift                                           |

| 8.2 | Dhrystone Numbers                                         |

| 8.3 | AMULET1 Pipeline Occupancy (Dhrystone (1 loop)) 196       |

| 8.4 | AMULET1 Pipeline Stalls (Dhrystone (1 loop))              |

| 8.5 | Asim versus Occarm (Single Transputer Implementation) 206 |

| 8.6 | Performance of Occarm                                     |

|     |                                                           |

| 9.1 | PDSP: Number of Free Stages in the Datapath               |

| 9.2 | Performance of PDSP (Address Interface)                   |

# List of Figures

| 2.1  | The Use of the Occam SEQ and PAR Constructs               | 40  |

|------|-----------------------------------------------------------|-----|

| 2.2  | The Occam ALT Construct                                   | 41  |

| 2.3  | Introducing Delays with Occam Timers                      | 42  |

| 2.4  | Programming Timeout Behaviour                             | 43  |

| 2.5  | An Example Occam Program                                  | 44  |

| 2.6  | The Architecture of the T800 Transputer                   | 46  |

| 3.1  | A Taxonomy of Models                                      | 53  |

| 3.2  | Abstraction Levels in Digital Systems                     | 75  |

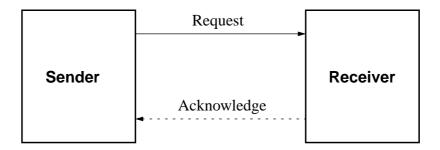

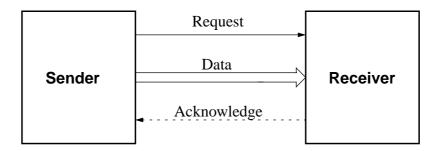

| 4.1  | The Request-Acknowledge Interface                         | 86  |

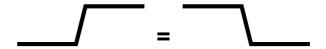

| 4.2  | Two-phase Signalling: Rising and Falling Edges Equivalent | 86  |

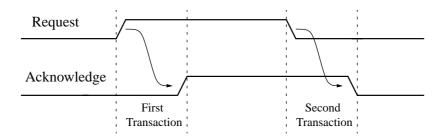

| 4.3  | Two-phase Signalling Protocol                             | 87  |

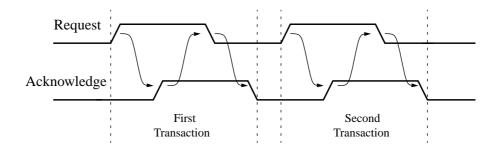

| 4.4  | Four-phase Signalling Protocol                            | 87  |

| 4.5  | The Bundled Data Interface                                | 89  |

| 4.6  | The Two-phase Bundled Data Protocol                       | 89  |

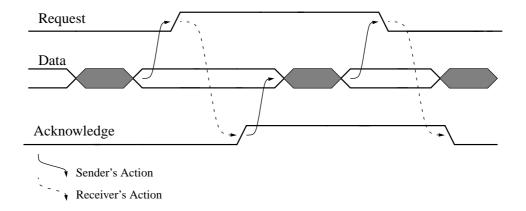

| 4.7  | Event Control Modules                                     | 91  |

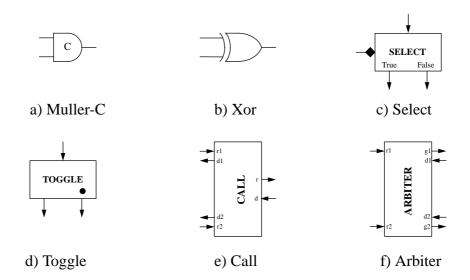

| 4.8  | The Capture-Pass Storage Element                          | 93  |

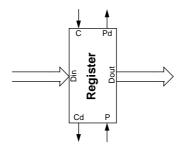

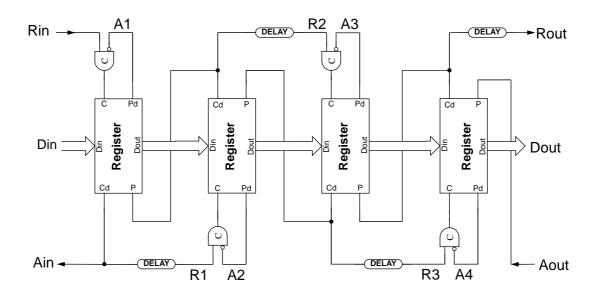

| 4.9  | Micropipeline Without Processing                          | 94  |

| 4.10 | Micropipeline With Processing                             | 96  |

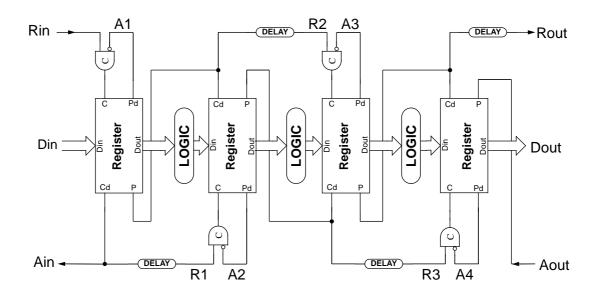

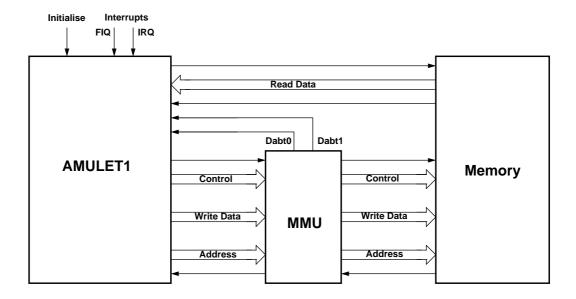

| 4.11 | The AMULET1 Interface                                     | 99  |

| 4.12 | The AMULET1 Internal Organization                         | 101 |

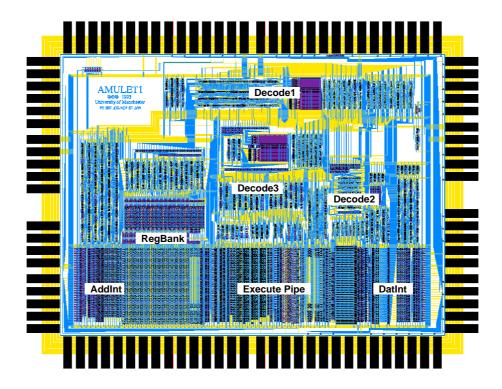

| 4.13 | The AMULET1 Processor Physical Layout                    |

|------|----------------------------------------------------------|

| 5.1  | Micropipeline Without Processing: The Register Model 116 |

| 5.2  | Micropipeline With Processing: A High Level View         |

| 5.3  | Micropipeline With Processing: The Register Model        |

| 5.4  | Synchronous Merge                                        |

| 5.5  | Data Dependent Merge                                     |

| 5.6  | Arbitrated Merge                                         |

| 6.1  | Occarm Top Level Process Graph                           |

| 6.2  | The Buffer Process                                       |

| 6.3  | The Address Interface                                    |

| 6.4  | The Address interface Model (AddInt)                     |

| 6.5  | The Data Interface Model (DatInt)                        |

| 6.6  | The Exception Pipe                                       |

| 6.7  | Aborts Modelling                                         |

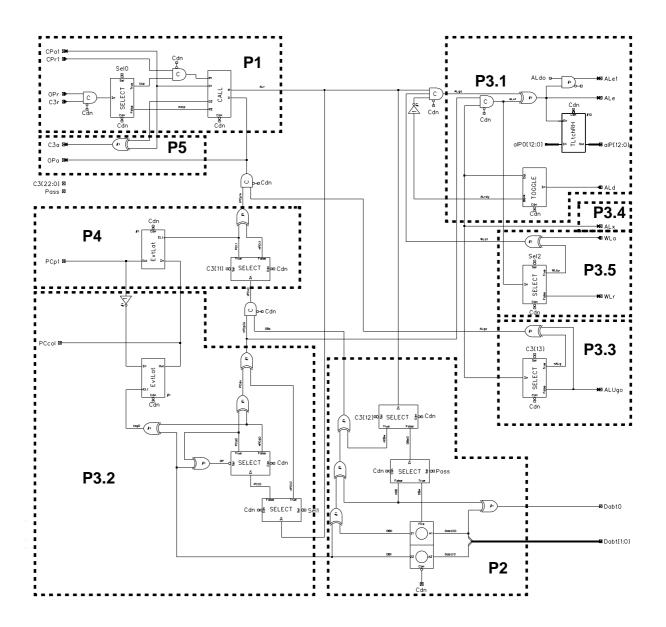

| 6.8  | The Primary Decode Model (Decode1)                       |

| 6.9  | Dec1CtrlA Logic                                          |

| 6.10 | Detecting the PCcol                                      |

| 6.11 | Modelling Dec1CtrlA Arbitration Logic                    |

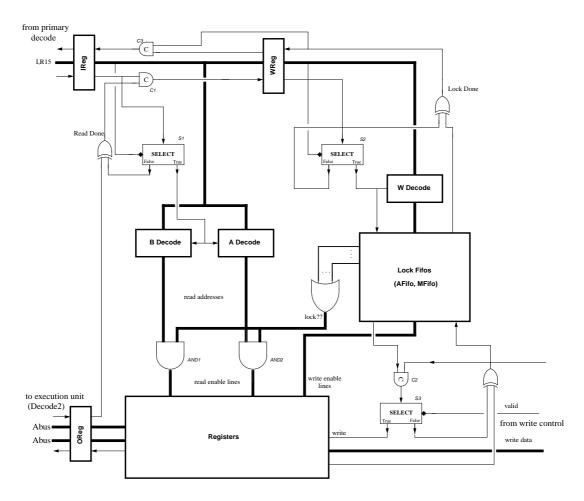

| 6.12 | The Register Bank Internal Organization                  |

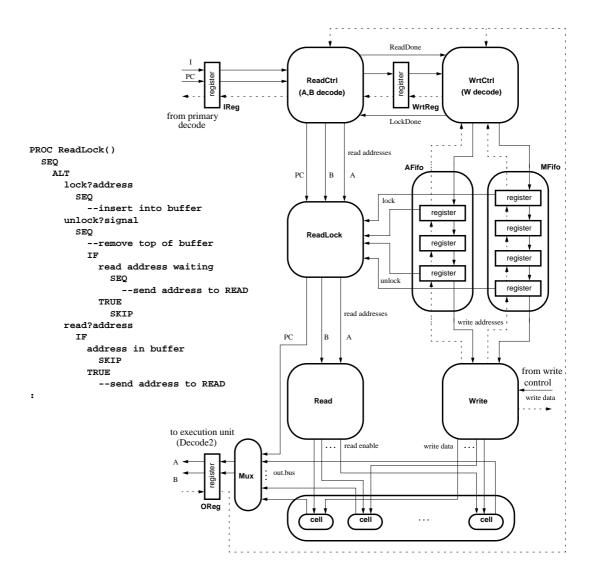

| 6.13 | The Register Bank Model (RegBank)                        |

| 6.14 | The Execution Unit of AMULET1                            |

| 6.15 | The CPSR Unit                                            |

| 6.16 | CPSR: An Alternative Design                              |

| 6.17 | The First Execution Stage Model (Decode2)                |

| 6.18 | The Second Execution Stage Model (Decode3) 165           |

| 6.19 | The Write Bus Control Model                              |

| 7.1  | The T-Rack                                           | 39 |

|------|------------------------------------------------------|----|

| 7.2  | Event Traces for Debugging                           | 75 |

| 7.3  | Collecting Event Traces in Occarm                    | 78 |

| 7.4  | Terminating Occarm                                   | 30 |

| 7.5  | The Single transputer Environment of Occarm          | 32 |

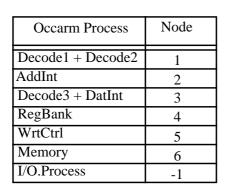

| 7.6  | Occarm Process Connectivity Table                    | 35 |

| 7.7  | Modified Occarm Top Level Process Graph              | 36 |

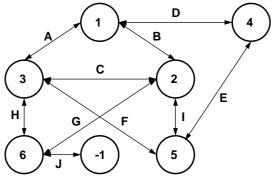

| 7.8  | Occarm Graph Mappings                                | 38 |

| 7.9  | Mapping Occarm onto the T-Rack                       | 39 |

| 7.10 | The Generic Simulator Node                           | 90 |

| 8.1  | A Section of the Dhrystone Synthetic Benchmark       | 93 |

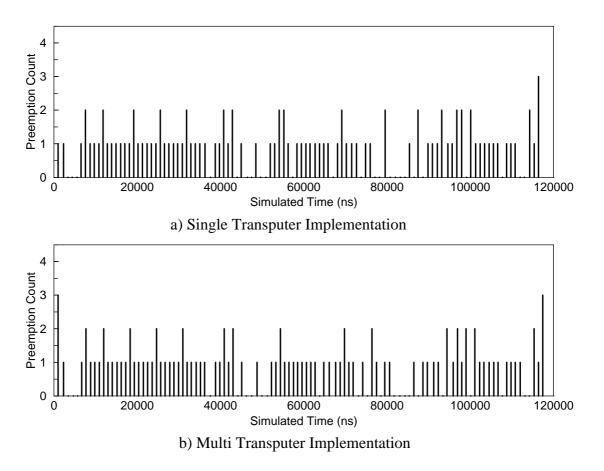

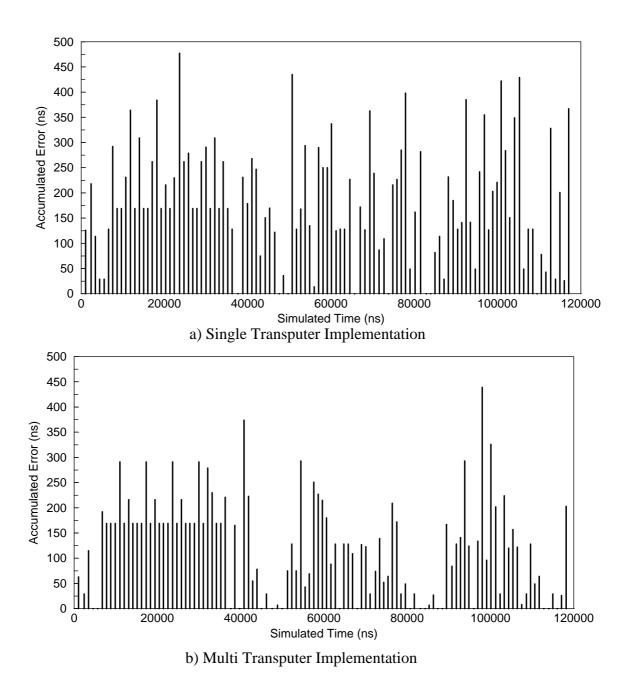

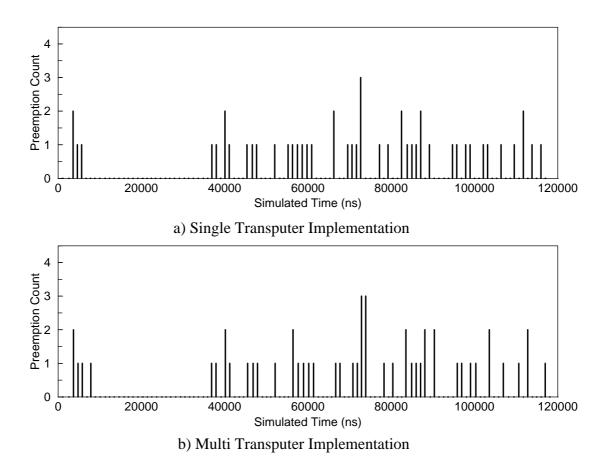

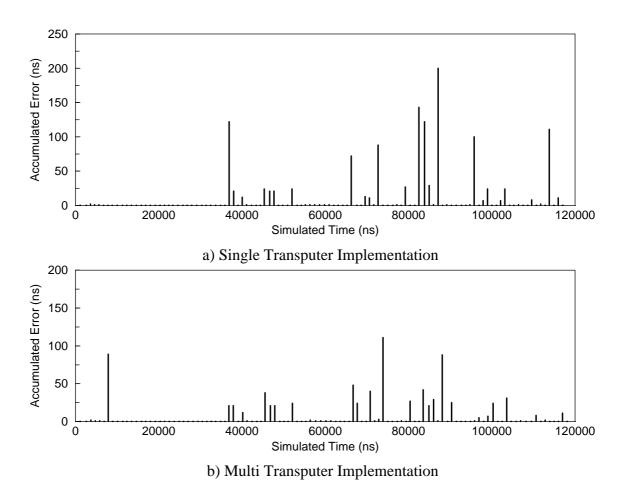

| 8.2  | Decode1: Preemption Count (1 Dhrystone Loop)         | 99 |

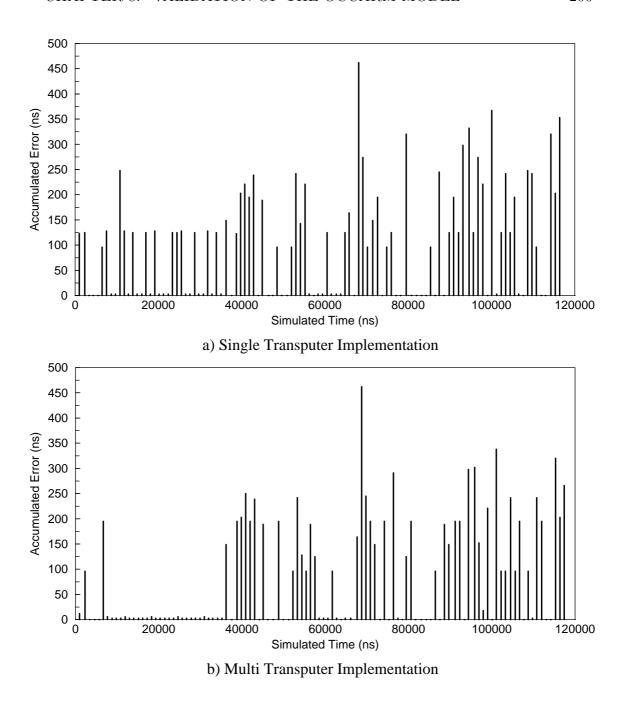

| 8.3  | Decode1: Preemption Magnitude (1 Dhrystone Loop) 20  | )( |

| 8.4  | AddInt: Preemption Count (1 Dhrystone Loop) 20       | )1 |

| 8.5  | AddInt: Preemption Magnitude (1 Dhrystone Loop) 20   | )2 |

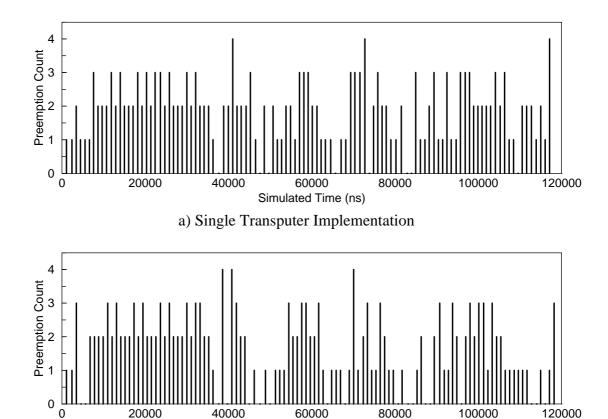

| 8.6  | WrtCtrl: Preemption Count (1 Dhrystone Loop)         | )3 |

| 8.7  | WrtCtrl: Preemption Magnitude (1 Dhrystone Loop) 20  | )4 |

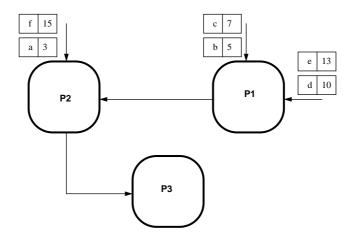

| 8.8  | An Example Process Graph                             | )5 |

| 9.1  | The PDSP Arbiter Process                             | 14 |

| 9.2  | PDSP: Taking MLL into Account                        | 17 |

| 9.3  | Providing Instruction Lookahead Knowledge to AddC 21 | 19 |

| 9.4  | The Arrival of Instruction Lookahead Information     | 20 |

| 9.5  | The Address Interface - Datapath Loop                | 23 |

| 9.6  | Stalling of the Datapath                             | 24 |

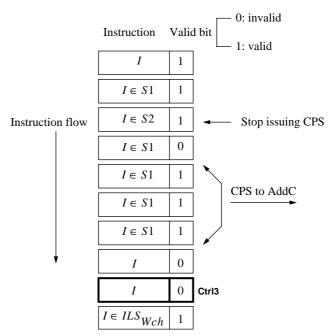

| 9.7  | PDSP: Providing CPS to AddC                          | 28 |

| 9.8  | Informing AddC of Colour Mismatches at Decode1       | 31 |

| 99   | The Instruction Lookahead Table                      | 33 |

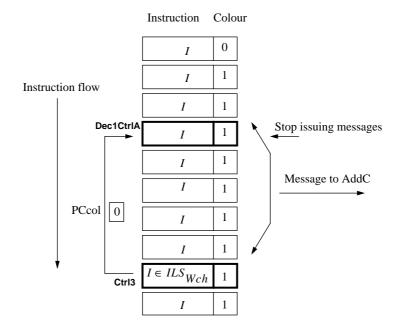

| 9.10 | PDSP messages from Ctrl3 to AddC                | 237 |

|------|-------------------------------------------------|-----|

| 9.11 | The Decode1 Arbiter: PCcol due to Aborts        | 240 |

| 9.12 | Informing Decode1 of the selected channel       | 241 |

| 9.13 | The Memory-WrtCtrl pipeline                     | 243 |

| 9.14 | WrtCtrl: Reading data values from memory        | 244 |

| 9.15 | Bypassing the register bank                     | 246 |

| 9.16 | WrtCtrl: Reading messages from the datapath     | 246 |

| A.1  | The ARM6 Register Organization                  | 261 |

| A.2  | The ARM Program Counter and Program Status Word | 262 |

| A.3  | The ARM6 Program Status Registers               | 262 |

| A.4  | ARM Instruction Formats                         | 263 |

| В.1  | Dec1CtrlB Control Circuit                       | 267 |

| B.2  | The Dec1CtrlB Process                           | 268 |

| B.3  | AddC Control Circuit                            | 269 |

| B.4  | The AddC Process                                | 270 |

| B.5  | Ctrl2 Control Circuit                           | 271 |

| B.6  | The Ctrl2 process                               | 272 |

| B.7  | Ctrl3 Control Circuit                           | 273 |

| B.8  | The Ctrl3 process                               | 274 |

| B.9  | Write Control Circuit                           | 275 |

| B 10 | The WrtCtrl2 process                            | 276 |

# Abstract

Synchronous VLSI design is approaching a critical point, with clock distribution becoming an increasingly costly and complicated issue and power consumption rapidly emerging as a major concern. Asynchronous digital design styles promise to liberate VLSI systems from clock skew problems, offer the potential for low power and high performance and encourage a modular design philosophy which makes incremental technological migration a much easier task. The desire to exploit the potential advantages offered by asynchronous logic has recently fueled a revival of interest in asynchronous systems.

Modelling and simulation, being at the heart of digital system design, may perform a catalytic role in the quest for the realization of the potentials offered by asynchronous logic. Hence, the recurrence of interest in asynchronous design has been accompanied by an intense research activity aiming at developing techniques appropriate for modelling and simulating asynchronous systems.

Contributing to this effort, and motivated by the increasing debate regarding the potential use of CSP for this purpose, this thesis investigates the suitability of occam, a CSP-based programming language, for the modelling and simulation of complex asynchronous designs.

A modelling approach is introduced which aims to exploit the strong relationship between the semantics of occam and the structure and operation of asynchronous systems, as well as the parallelism inherent in asynchronous hardware to achieve the rapid development of asynchronous architectural simulation models, which may be executed on transputer networks to achieve high performance.

The applicability and robustness of the approach is demonstrated by employing it to construct occarm, an occam model of the AMULET1 asynchronous microprocessor.

The distributed nature of the proposed modelling approach introduces the problem of maintaining temporal precision and ensure that the causality principle is not violated.

The thesis provides a quantitative analysis regarding the timing error introduced in the model if violations of the causality principle are permitted. It then introduces the Program Driven Synchronization Protocol, a novel conservative, deadlock avoidance synchronization technique for dealing with causality problems within the framework of the proposed modelling approach.

Monitoring, debugging, termination and load balancing issues are also discussed.

### **DECLARATION**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institution of learning.

All trademarks cited within this work are acknowledged by the author.

# COPYRIGHT AND OWNERSHIP OF INTELLECTUAL PROPERTY RIGHTS

- 1. Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rynalds University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

- 2. The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such arrangement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of Department of Computer Science, University of Manchester.

# The author

The author obtained a Diploma degree in Computer Engineering and Informatics from the University of Patras, Greece, in July 1989. He was subsequently awarded a scholarship for graduate studies in Computer Science by the University of Manchester, U.K. In October 1990, he joined the Department of Computer Science at the University of Manchester as a research student (ParSiFal group) and a year later he completed his MSc (Method II-by research). In October 1991 he joined the AMULET group at the Department of Computer Science, University of Manchester to pursue a Ph.D.

στους γονεὶς μου, Κωνσταντὶνο και Χρυσοὺλα,

$\sigma \tau \eta \nu \ \alpha \lambda \dot{\eta} \vartheta \varepsilon \iota \alpha ...$

to my parents, Konstantinos and Chrysoula,

to the truth...

"Η Ιθὰκη σ' ὲδωσε τ' ωραὶο ταξεὶδι. Χωρὶς αυτὴν δὲν θὰβγαινες στο δρὸμο. 'Αλλα δὲν ὲχει να σε δὼσει πιὰ. Κι' αν φτωχικὴ την βρεὶς, η Ιθὰκη δὲν σε γὲλασε. 'Ετσι σοφὸς που ὲγινες, με τὸση πεὶρα, ὴδη θα το κατὰλαβες η Ιθὰκες τι σημαὶνουν."

$K. K\alpha\beta \alpha \varphi \eta \varsigma$

"Ithaca gave you the lovely journey.

Without her you would never have set out.

But she has nothing more to give you.

And if you find her poor, Ithaca has not deceived you.

Wise as you will have become, so full of experience,

you must have understood already the meaning of Ithacas."

C. Cavafy.

# Acknowledgements

I am grateful to my supervisor, Dr. J. V. Woods for his support during the four years in which the research for this thesis was carried out. Professor S. B. Furber, as my co-supervisor and director of the AMULET group, has always been a source of inspiration; for this, for his advice and guidance, and for patiently providing me with the facilities to carry out the research for this thesis I express my thanks.

I also wish to thank Dr. P. Capon, for allowing me access to the T-Rack, and for his invaluable assistance during the implementation of the occam systems required for the research presented in this thesis. Thanks are also due to all those who supported the T-Rack the last four years, allowing me to complete my research.

I would also like to thank all the members of the AMULET group for their support all these years. In particular, I wish to express my thanks to Rob Kelly, (now with ICL, Manchester), Paul Day, Nigel Paver and Steve Temple for always being prepared to discuss and provide answers to my questions regarding the peculiarities of the AMULET1 architecture; Rob's help during some crucial moments of the work was invaluable. David Jackson, Craig Farnsworth, Rahul Mehra, Rhod Davies, Jim Garside, Oleg Petlin, Steve Nicklin, Dave Gilbert, they all helped me in a number of occasions and I thank them all. Nigel also provided his Lapwing Court 'mansion', which proved an excellent environment for writing up this thesis, not least because of his strict "Ph.D policing"; my special thanks.

The many friends I made during my five year stay in Manchester have been an invaluable source of emotional support and have made the Ph.D a less stressful task to undertake and Manchester a great place to live; I thank them all.

The research presented in this thesis was funded by a University of Manchester Research Scholarship and by the Mpakalas Foundation, Athens, Greece; I gratefully acknowledge this support.

# Chapter 1

## Introduction

## 1.1 Background

This thesis is concerned with methodologies and techniques to support the modelling and distributed simulation of asynchronous computer architectures. The research presented in this thesis took place in the period 1991-1994 and relates to work in asynchronous system design undertaken by the AMULET group at the Department of Computer Science, University of Manchester.

#### 1.2 Motivation and Objectives

Clocked VLSI systems are approaching a critical point, due to certain deficiencies inherent in the synchronous operation. Asynchronous logic promises to provide the means to overcome these deficiencies and limitations of the synchronous VLSI design approach. Hence, recently, there has been a resurgence of interest in asynchronous design techniques.

The quest for the exploitation of the potential advantages offered by asynchronous logic has revealed a need for modelling and simulation techniques, which would be appropriate for the asynchronous design style. Thus, the recurrence

of interest in asynchronous design has fueled intense research activity aiming to develop techniques appropriate for modelling and simulating asynchronous systems. CSP, in particular, has attracted the attention of many researchers as a potential notation for describing asynchronous behaviour. Contributing to the quest for modelling and simulation techniques suitable for asynchronous design, and motivated by the increasing debate regarding the potential of CSP for this purpose, the work described in this thesis investigates the suitability of occam, a CSP-based programming language, for the modelling and simulation of complex asynchronous systems.

#### 1.3 Structure of the Thesis

The thesis comprises 10 chapters. Chapters 2, 3, 4 and the first part of chapter 5 provide a theoretical background to the areas directly related to the subject of the thesis, namely parallelism, simulation modelling, asynchronous systems and modelling techniques for asynchronous hardware respectively. The remainder of the thesis, namely the second part of chapter 5 and chapters 6, 7, 8 and 9, describe the author's work and contribution.

Chapter 2 provides a short introduction to parallelism as a natural path to the quest for high performance, with emphasis on the MIMD approach to parallel computation. The various parallel programming models are mentioned and the CSP model of computation is discussed. Finally, a more detailed description of the occam programming language and its associated processor, the transputer, is provided.

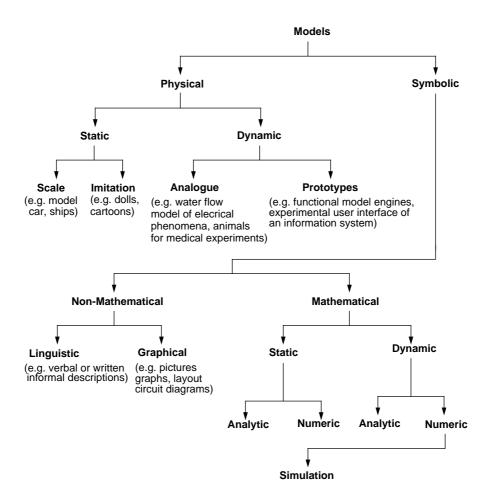

Chapter 3 deals with the issues of modelling and simulation. After a short introduction to modelling, the chapter concentrates on discrete event simulation modelling, and in particular, its distributed implementation. The various

approaches for exploiting parallelism in simulation are mentioned, and the Logical Process Paradigm is described. The causality-related issues arising from the distributed nature of the Logical Process Paradigm are described and the techniques that have been developed to address these issues are discussed. The chapter concludes with a discussion on the role of modelling and simulation in digital system design.

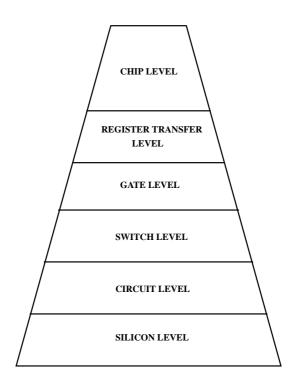

Chapter 4 discusses issues related to asynchronous design techniques. After a short discussion on the nature and advantages of asynchronous logic, the chapter presents some of the most influential asynchronous design techniques and then proceeds to provide a more detailed description of the Micropipeline design approach. The final part of the chapter is occupied by a short description of the Micropipelined AMULET1 microprocessor.

The thesis then moves to the modelling of asynchronous systems. Chapter 5 provides an overview of existing notations and techniques; emphasis is placed on the techniques that employ CSP-like notations. Advocating the potential use of occam for the modelling and simulation of asynchronous systems, a methodology is introduced which employs occam to build parallel models of asynchronous systems based on the Micropipeline approach. This neglects causality problems, thus allowing timing errors to occur. It is argued however that the timing inaccuracy will be acceptable.

Chapter 6 describes how the modelling approach introduced in chapter 5, has been employed to build an occam model of the AMULET1 asynchronous microprocessor. Emphasis is given to the aspects of the modelling that proved to be complex. The chapter also includes a more detailed description of the operation of the AMULET1 processor, as this defines the functionality of the model as well.

Chapter 7 addresses issues related to the execution of the occam model on

a computer system. Two environments are presented, for the execution of the model on a single and multiple transputers respectively. Monitoring, termination, mapping and load balancing issues are discussed.

Chapter 8 presents a validation of the occam model, providing quantitative results and analysis regarding both, the accuracy and performance of the model.

Chapter 9 introduces the "Program Driven Synchronization Protocol" (PDSP), a novel approach for eliminating the timing problems raised by the distributed nature of the proposed modelling philosophy. The concept of "Instruction Lookahead" is introduced and a set of rules are presented which specify the behaviour of processes in the occam model so that timing accuracy is ensured. The application of PDSP onto the occam model of AMULET1 is then described. Finally, some performance results are given.

Chapter 10 epitomizes the conclusions drawn by the research presented in the thesis, and indicates a number of areas where further research and development work is possible.

#### 1.3.1 Related Publications

Different aspects of the research work presented in this thesis have been presented in the AMULET Modelling Workshop (Windermere, Cumbria, England) [Theo94], the World Transputer Congress 1994 (Como, Italy) [Theo94a], the European Simulation Symposium 1994 (Istanbul, Turkey) [Theo94b], the Eurosim Congress 1995 (Vienna, Austria) [Theo95] the World Transputer Congress 1995 (Harrogate, England) [Theo95a] and the 4th Euromicro Workshop On Parallel And Distributed Processing (Braga, Portugal) [Theo95b].

# Chapter 2

# The Quest for High Performance

#### 2.1 Introduction

The principles of computer organization have traditionally been based upon the processing model described by John von Neumann in the late 1940s, whereby a computer comprises a single processing unit connected to a single<sup>1</sup> memory in which both, the program code and the data to be operated upon are stored. This is commonly referred to as the von Neumann model of computation. The operation of the system consists of sequential fetches of instructions and their operands from memory, which are then executed, with the result of the execution written back to memory. The memory addresses of all instructions and data involved in a computation as well as the instructions their operands and the produced results are communicated over the single path that connects the processor and the memory; Backus called this path as the "von Neumann bottleneck" [Back78].

Since the first commercial, general purpose von Neumann computers were commissioned in the early 1950s, there has been an ever increasing demand for

<sup>&</sup>lt;sup>1</sup>The basic memory model, which uses the same physical memory to save both instructions and data is referred to as the "Princeton Architecture".

more computational power and speed. Traditionally, this demand has been satisfied by enchancing the performance of sequential computers through technological advances and architectural innovations.

The progression from electromechanical relays, vacuum tubes, William's tubes and magnetic drums, to transistor switching devices and solid state memories, to integrated circuits and eventually to VLSI semiconductor devices has had a dramatic impact on computational speed. Reduced physical size and shorter device switching times have resulted in digital systems that can be driven at extremely high clock rates (e.g. the 21164 EV-5, successor of the Dec's Alpha processor, is expected to run at a speed of 300MHz [Gwen94]). Optical technology promises to reduce gate delays to picoseconds while increasing the bandwidth and the numbers of interconnections [Huan90].

Advances in technology have been accompanied by architectural novelties. These include the use of cached store hierarchies, virtual address spaces, arithmetic optimizations and more efficient instruction sets. Techniques to overcome the von Neumann bottleneck have also been devised; these include the "Harvard Architecture" which uses separate instruction and data memories and memory interleaving, which allows concurrent access to several independent memory modules [Kraf79] [Ibbe82] [Furb89] [Heud92].

#### 2.2 Bit and Instruction Level Parallelism

A technique which has made a significant contribution to the improvement of the performance of von Neumann architectures has been the exploitation of parallelism at bit and instruction levels.

Bit-parallel arithmetic was the first technique to be employed as hardware components became less expensive.

Bit parallelism was followed by the introduction of multiple functional units

(stages) which could operate in an overlapped manner. These stages are connected one to the next to form a pipeline; instructions enter at one end of the pipeline and travel through consecutive stages to exit at the other end. This arrangement allows an instruction to be (pre)fetched and decoded while the previous instruction is being executed. The execution unit may also be divided into a number of stages, with each stage performing a different operation contributing to the execution of an instruction. Several advanced architectural techniques have been devised to optimize pipelined operation; these include branching schemes (e.g. delayed branch), advanced scheduling techniques, register bank management techniques, superpipelining, superscalar and very long instruction word (VLIW) systems [Henn91]. Superpipelined machines employ "deeper" pipelines, while superscalar machines issue more than one instruction per clock cycle in the pipeline; in VLIW systems the compiler finds operations which can be issued in the pipeline together and creates a single instruction containing those operations. In general, the utilization of multiple pipelined units can reduce the average execution time per instruction and improve throughput significantly; however, data and control dependencies may cause considerable delays [Kogg81]. Traditionally, pipelines have been driven by a common external clock. Recently unconventional techniques have been developed which allow the asynchronous operation of pipeline stages; these techniques are at the core of the research work described in this thesis and are discussed in detail in chapter 4.

#### 2.3 Reduced Instruction Set Computers

A milestone in computer architecture research was the development of Reduced Instruction Set Computers (RISCs).

The quest for high performance and the aim to reduce the "semantic gap"

between hardware and high level programs had generated a trend towards increasingly sophisticated and complex hardware and instruction sets [Furb89]. Against this background of increasing complexity the concept of RISC was introduced in 1980, advocating simplicity and efficiency [Patt80]. RISC systems implement small instruction sets using simple and fixed instruction formats on load/store architectures to achieve fast and single cycle execution [Stal88]. They employ pipelining and hardwired (instead of microcoded) control and rely on optimising compilers and large cache memories to maximise the use of registers and minimize references to main memory. The underlying principles of the RISC approach had already been laid down by IBM in their 801 computer, developed in late 1970s at IBM's Thomas J Watson Research Center [Radi83]; the first prototype VLSI RISC processors were developed in early 1980s at the University of California, Berkeley [Kate85] and at Stanford University [Henn81]. Since then, and amidst an ever lasting controversy on the issue of system complexity [Whar92] [Alli92], several commercial powerful RISC processors have been developed, including the VL86C010 Acorn RISC Machine (ARM) [Furb89] [VLSI90], the MB86900 SUN SPARC [Fuji87] [Sun87], the MIPS R2000 [Kane87], AT&T's CRISP [Ditz87], AMD's Am29000 [AMD87], Hewlett-Packard's HPPA [HP86] and Motorola's M88000 [Dobb88]; comprehensive surveys of VLSI implementations of RISC architectures may be found in [Furb89] and [Heud92].

#### 2.4 The Limits of Sequential Computation

Technological and architectural advances have yielded a dramatic rise in the performance of von Neumann machines and computational speed increases of an order of magnitude every five years have been witnessed. However, this rate of improvement can not be sustained due to fundamental limitations imposed on VLSI technology by the laws of physics [Lind93] [Prep94]. One such limitation

is the speed at which electrical signals can be transmitted over the physical links which connect the circuit components; this speed cannot be greater than the speed of light (i.e. about 0.3 metres per nanosecond) [Russ78]. Miniaturization techniques aim at high package densities and a high degree of integration to reduce distances between components, but are limited by the heat dissipation and the quantum effects at sub-micron levels [Mead80]. These two fundamental constraints impose an ultimate limit to the maximum theoretical performance that can be achieved by a single von Neumann computer; this performance has been estimated to be around 3 Gigaflops (3 billion floating point operations per second) [Wile87].

#### 2.5 Parallel Computer Architectures

Despite the dramatic rise in their performance, sequential von Neumann computers still can not offer the processing rates required for the solution of a wide range of applications (the so called "Grand Challenge" problems) [Fox89] [Lazo93] [Kung94]. This has led to the introduction of architectural concepts which attempt to take advantage of the high level, algorithmic or data-set, parallelism inherent in many problems. These concepts call for the utilization of multiple processing elements which can operate in parallel [Hwan84] [Hock88] [Dunc90] [Mold93].

Traditionally, parallel computer architectures are classified as either SIMD (Single Instruction Multiple Data Streams) or MIMD (Multiple Instruction Multiple Data Streams), following Flynn's taxonomy [Flyn72]. This taxonomy defines two more classes of architectures, namely SISD (Single Instruction Single Data Streams) and MISD (Multiple Instruction Single Data Streams). SISD refers to conventional, serial von Neumann machines; in these computers at any instant, one stream of instructions (and therefore, only one instruction processing unit)

operates on a single data stream. MISD would involve multiple processing units applying different instructions to a single datum; this theoretical possibility is generally deemed impractical.

#### 2.5.1 SIMD

Two major classes of SIMD machines exist, namely vector processors and array processors.

Vector processors utilize multiple pipelined processing elements to apply identical arithmetic operations to a data stream linearly organised in vector registers. Vectorising compilers are employed to replace blocks of sequential code by vector instructions. Examples of successful commercial vector machines are the CRAY-1 [Russ78], the Control Data Corporation CYBER 200 series [Linc82] and the Fujitsu VP-200 [Miur84].

Array processors typically employ a central control unit and multiple processing elements which operate in parallel applying the same instruction sequence on arrays of data in a *synchronized* fashion. Array machines can achieve high performance rates with suitable problem classes where the same operation must be performed on different data sample points. Generally, parallelism must be expressed explicitly by the programmer, although compiling techniques can also be used for this purpose. Examples of array processors are the ILLIAC IV [Hord82], the Burroughs Scientific Processor (BSP) [Aust79], the ICL Distributed Array Processor (DAP) [Redd79], the Goodyear Aerospace MPP [Batc80] and the Connection Machine [Hill85].

SIMD machines are well suited to data parallel applications such as weather forecasting, image processing, finite state analysis and general linear algebra problems.

#### 2.5.2 MIMD

MIMD architectures employ multiple connected processors which can execute independent instruction streams. MIMD computers are asynchronous systems characterized by decentralized hardware control. They offer greater flexibility than their SIMD counterparts and they support higher level parallelism (subprogram and task levels) which can be exploited by divide and conquer algorithms; a large problem is split into a number of sub-tasks, which can then be executed concurrently on different processors.

The degree of coupling between processors categorizes MIMD machines as either tightly or loosely coupled. In tightly coupled (or shared memory) systems, processors communicate and synchronize through a global shared main memory. In loosely coupled (or distributed memory) systems, each processor has its own local store and communicates with the other processors by exchanging messages via a network<sup>2</sup>. Virtual shared memory systems have also been developed, wherein the memory is physically distributed but it is logically viewed by the programmers as a single global shared memory: these systems include DDM [Warr88] and KSR-1 [KSR].

#### 2.5.2.1 Shared Memory MIMD Architectures

In shared memory architectures, performance may be degraded due to store contention problems which may occur if more than one processor requires access to the store simultaneously. To reduce this possibility, multiple banks of store may be used. Another technique uses local cache memories to reduce accesses to the global memory. This introduces the issue of maintaining coherency among the multiple copies of the same data that may exist in various processors' caches at a given time. Cache coherency protocols, implemented in hardware or software,

<sup>&</sup>lt;sup>2</sup>Distributed memory architectures are also referred to as message-passing systems.

may solve this problem but usually reduce the performance of the system [Hill89] [Sten90].

Various alternatives for connecting multiple processors to shared memory have been proposed. Small machines with relatively few processors typically feature a time-shared data bus; processors contest control of this to access the store. Bus saturation problems make this scheme ineffective for large processor numbers. Flexible Corporation's Flex/32, the Encore Computer's Multimax and the Sequent Balance machines [Hock88] are examples of bus based architectures. Crossbar interconnection technology uses a crossbar switch of  $n^2$  crosspoints to connect n processors to n memories. Carnegie Mellon multi-mini-processor (C.mmp) [Wulf72] was based on this interconnection scheme. Power, pinout, and size considerations make fully connected networks very expensive because the complexity grows as the square of the number of processors and memories. Multistage interconnection networks such as Delta and Omega networks [Pate79] provide the same connectivity as crossbar networks but at reduced cost<sup>3</sup>; an example of a multilevel switching network based machine is the Illinois Cedar computer [Gajs83] which uses an Omega network to connect clusters of processors to global memory modules.

Another problem associated with shared memory architectures is the issue of *mutual exclusion*, namely preventing a task from accessing a shared data structure while this is being modified by a different parallel task. Signals [Wirt77], semaphores [Dijk68], conditional critical regions [Hoar72] [Hans73], and monitors [Hoar74] are schemes that have been developed to solve the mutual exclusion problem. Languages based on these concepts have also been developed including Ada [Barn89] and Modula [Wirt77].

<sup>&</sup>lt;sup>3</sup>Delta networks for instance have a cost logarithmic to the number of inputs.

#### 2.5.2.2 Distributed Memory MIMD Architectures

Message passing MIMD machines have principally been constructed in an effort to provide architectures with the potential to scale up into systems consisting of many thousands of processors.

In distributed memory architectures<sup>4</sup>, processors are connected by an interconnection network; bus-based configurations also exist (e.g. the PRINGLE computer [Hock88]) but are not common.

The network that provides for the connection of the processors in a message passing system can be either static or reconfigurable. In the first case, the connections between the processors are fixed and permanent. In static networks, communication between non-neighbouring processors can result in significant latency as data is queued and forwarded by intermediate nodes to reach its destination. Various interconnection network topologies have been proposed to support expandability and scalability and to minimize latency for certain classes of problems [Sieg85] [Reed87]; these include rings, grid based networks such as meshes, cylinders, toroids, trees, cube connected cycles, shuffle exchange networks, and hypercubes.

Reconfigurable topology architectures provide programmable switches that allow users to select a logical topology which matches a particular application's communication pattern. Usually the desired configuration is arranged in advance, though dynamic reconfiguration is also an available option [Murt91].

Examples of commercial distributed memory MIMD machines are the BBN Butterfly [Hock88], the Cosmic Cube [Seit85], the ChiP computer [Snyd82] and the Intel iPSC [Inte86].

Recently, some less conventional MIMD based architectural paradigms have

<sup>&</sup>lt;sup>4</sup>The term typically applies to systems in which the nodes are closely connected via very high speed communication links. Physically distributed computers connected by slow message passing networks (e.g. ARPANET) are usually excluded.

been developed. Dataflow architectures [Gurd85] and graph reduction machines [Trel82] are examples of such paradigms.

#### 2.5.3 Parallel Programming Models and Languages

The von Neumann model of computation is typically characterized as *control driven*. There is a single thread of control normally passed sequentially from instruction to instruction thus determining the sequence in which instructions are executed. The control driven model of computation is supported by conventional imperative languages such as C [Kern88].

The advent of parallel architectures has resulted in a strong interest in different computation models which have the potential for parallel execution and new programming styles and languages to support them.

In the *data driven* model of computation, an instruction may be executed as soon as the necessary data are available, without taking into account its textual position in the program. This model is supported by *single assignment* languages such as SISAL [Böhm91] and LUCID [Asch77]. Data flow machines constitute implementations of the data driven model of computation.

In the *demand driven* model, an operation is performed only when its result is required. *Functional languages* [Glas84] [Read89] such as HASKELL [Huda90] are well suited for this model, while graph reduction architectures provide for their efficient implementation.

Logic languages are based on pattern driven models of computation [Alma89]. In Prolog [Cloc81] for instance, the execution of a program consists of a search for facts (patterns) which satisfy a given query; the facts are organized to form a search tree which may be searched in parallel (using AND-parallelism or OR-parallelism).

The three aforementioned models of computation support fine grain parallelism which is the responsibility of the compiler to exploit. However, the predominant computational model for MIMD architectures, is based upon the concept of concurrent processes that communicate and synchronize through the exchange of messages (message passing); this model is well suited to distributed memory machines though it can also be implemented on shared memory systems. The process based model of computation exploits the algorithmic parallelism of programs and calls for their partitioning into a number of different processes which perform different parts of the overall algorithm<sup>5</sup>. The parallel processes may then be mapped onto different processors of the parallel architecture. The detection of algorithmic parallelism and the mapping of the resulting partitioning onto the multiple processors of an MIMD machine are two major problems associated with the process based model of computation. Ideally, the latter task should be performed automatically, though in general it is the programmer's responsibility; chapter 7 discusses how this problem has been tackled within the context of the research presented in this thesis.

Various process based programming models have been proposed, including PLITS (Programming Language in the Sky) [Feld79], Linda [Ahuj86], and CSP (Communicating Sequential Processes) [Hoar78] [Hoar85]. These differ in the naming convention they use to refer to sender and receiver processes and the semantics of their communication.

## 2.5.3.1 Communicating Sequential Processes

The theoretical model of Communicating Sequential Processes is one of the most elegant schemes which have been proposed for process based parallel computation.

Within the framework of CSP, a program is a collection of sequential processes

<sup>&</sup>lt;sup>5</sup>Usually the process structure of an algorithm implemented using message passing is represented by a graph whose nodes represent the processes and edges represent the communication paths between them.

which execute asynchronously and concurrently and communicate by exchanging messages through *channels*.

The communication is unbuffered, point-to-point and synchronous. A communication requires a *rendezvous* between the sender and the receiver processes and will take place only if both these processes have requested participation in such an activity; otherwise the process that arrives at the rendezvous first has to block until the corresponding action is reached at the other end of the channel.

A guarded input construct [Dijk75] is available which provides the means for a receiver process arbitrarily to select to communicate via one of several input channels depending on the readiness or otherwise of these channels; the choice is nondeterministic.

# 2.6 Occam and the Transputer

With the aim of providing a practical realization of the CSP model of computation, in early 1980s Inmos Limited developed the *occam* programming language [Inmo88] and the *transputer* [Inmo86] [Inmo88a], a microprocessor designed to support the execution of occam.

# 2.6.1 The Occam Programming Language

The basic unit of the occam language<sup>6</sup> is the *process*. The concept of the process can be viewed at many levels within an occam program, the lowest being the command level. Occam programs are built from three *primitive* processes namely

<sup>&</sup>lt;sup>6</sup>Within the context of this thesis, the term occam refers to the occam2 language. This is a development of an earlier occam language known as occam1 or proto-occam. The main difference between the two occam variants is that occam2 allows the transmission of structured data types along channels, by providing extended channel protocols. Recently, Inmos developed another variant of occam, referred to as occam3, which supports records and user-defiable data types [Inmo92]. Tutorial introductions of occam2 may be found in [Kerr87] [Poun87] [Burn88] [Gold88] [Dows88] and [Gall90].

CHAPTER 2. THE QUEST FOR HIGH PERFORMANCE

39

assignment, input and output:

• v := e: assign expression e to variable v

• c ! e : output expression e to channel c (send)

• c ? v: input variable v from channel c (receive)

Channels are used to enable the exchange of messages between concurrently executing processes. The semantics of occam channel communications are based on CSP. A communication through a channel is unidirectional, unbuffered, point-to-point, and synchronous; as in CSP, a sender and a receiver have to establish a rendezvous in order to communicate.

The primitive processes may be combined to form *constructs*:

• IF: conditional

• WHILE: iterative

• SEQ: sequential

• PAR: parallel

$\bullet$  ALT: alternative

A construct is itself a process and may be used as a component of another construct. The scope of these constructs is indicated in the text of the program by indentation (a single unit of indentation being two spaces). The execution of a compound construct terminates when all the processes within it (i.e. constructs and primitive processes) have terminated.

IF and WHILE constructs are the standard conditional and iterative commands respectively, encountered in all imperative languages.

```

SEQ

P1

P2

PAR

P3

SEQ

P4

P5

P6

```

Figure 2.1: The Use of the Occam SEQ and PAR Constructs

## 2.6.1.1 The SEQ and PAR Constructs

The mode of process execution is declared using the SEQ and PAR constructs. Processes which are grouped using SEQ are executed in sequential, textual order. Processes grouped by means of PAR, are not restricted to any specific order of execution and may thus be executed in parallel. SEQ and PAR constructs may be combined to allow the specification of arbitrarily complex execution orderings; the only restriction is adherence to the communication rules (e.g. parallel output to the same channel is illegal).

In figure 2.1, processes P1 and P2 will execute sequentially. Upon completion of P2 the PAR construct is activated which allows processes P3, P6 and any one of the processes P4 and P5 to execute concurrently; P4 and P5 have to execute sequentially. Upon the termination of the PAR construct, P7 is executed.

Occam allows the *replication* of the SEQ and PAR constructs by providing an extension of their syntax. A replicated SEQ corresponds to the FOR command, encountered in most imperative languages. The parallel replicator is more interesting, for with it arrays of parallel, identical processes may be specified.

Priorities among parallel processes executing on the same processor may be

Figure 2.2: The Occam ALT Construct

enforced by the use of the PRI operator (i.e. PRI PAR); the precedence in this case is declared by the textual order of the processes within the PRI PAR construct.

The transputer implementation of occam supports two levels of priority, namely low and high. Low priority processes are time-sliced and are executed only when there is no active high priority processes. High priority processes are not time sliced. Both, low and high priority processes are descheduled each time they need to wait on a channel or a timer communication (see section 2.6.1.3). By default, occam processes execute at low priority.

## 2.6.1.2 The ALT Construct

The ALT construct implements the guarded input command of the CSP model. A guard can be either an input process or an input clause accompanied by a boolean condition (figure 2.2).

ALT enables a receiver to select for execution one of several alternative channel input processes; this allows the receiver to communicate with more than one sender process, receiving randomly ordered messages. The input process selected for execution is the one whose boolean condition, if any, is TRUE

```

VAL Delay IS 15625: --Constant definition

TIMER Clock: --Timer channel declaration

INT Now:

SEQ

Clock ? Now --Read current clock value

Clock ? AFTER (Now PLUS Delay) --Deschedule

--Resume Operation

:

```

Figure 2.3: Introducing Delays with Occam Timers

and the corresponding sender process at the other end of the channel is first ready to communicate; if more than one ready sender exists, an arbitrary, nondeterministic choice is made.

A prioritized ALT is also provided (i.e. PRI ALT), in which case the readiness of the guards is examined in their textual order.

## 2.6.1.3 Timers

One of the original target areas of occam was in embedded systems applications, where support for real time control is required. This support is provided in occam by means of *timers*. Timers are syntactically treated as communication channels which can provide only input. The value returned is the current time which is represented as an integer value. The duration of the clock tick depends on the priority level of the process wherein the timer is invoked. In transputer implementations of occam, for low priority processes, each clock tick represents 64 microseconds; for high priority processes, the clock is incremented every 1 microsecond.

Timers can be used to control the temporal behaviour of occam programs by forcing processes to delay their execution for a pre-determined period. This is illustrated in figure 2.3. The timer input statement, when used in conjunction

```

VAL Time.Out IS 15625:

--Constant definition

--Timer channel declaration

TIMER Clock:

INT Now:

BYTE any:

SEO

Clock ? Now

--Read current clock value

WHILE (NOT end)

SEQ

ALT

ch1? any --Poll channel ch1

Ρ1

Clock ? AFTER (Now PLUS Time.Out) -- Timeout?

P2

:

```

Figure 2.4: Programming Timeout Behaviour

with the AFTER keyword, causes the timer input to be held up until the current clock reaches the value specified in the AFTER clause. During this period, the process remains descheduled. In general, scheduling delays introduced by the transputer's scheduler (see section 2.6.2) will slightly extend the period that the process remains inactive [Gall90]. Furthermore, an extra delay is imposed by the latency of the process queue of the processor, namely the time from when the process is rescheduled to the time at which reaches the front of the queue and starts processing; the maximum latency is estimated to be  $(2n-2)*time\_slice$ , where n is the number of processes in the queue when the timer process is rescheduled [Mitc90]. Therefore, the period that a process may be caused to delay its execution can only be approximate and non-deterministic and is generally greater than the delay specified in the AFTER clause.

Used within an ALT construct, a timer may generate time-out behaviour and thus prevent deadlock situations that might be caused by processes waiting for input on unresponsive channels. Figure 2.4 depicts a process with time-out behaviour; if channel ch1 fires before the Time.Out period has elapsed, P1 will be

```

PROC Pipeline(...)

VAL INT N IS ...:

--Size of pipeline

[N+1] CHAN OF INT ch: --Array of channels

INT i:

--Definition of the Feed.Pipe process

PROC Feed.Pipe(CHAN OF INT To.Pipe)

INT x:

SEQ

x:=0

WHILE TRUE

SEO

To.Pipe ! x

x:=x+1

--Definition of the Flush.Pipe process

PROC Flush.Pipe(CHAN OF INT From.Pipe)

INT x:

SEQ

WHILE TRUE

SEQ

From.Pipe ? x

--Definition of the Pipe.Stage process

PROC Pipe.Stage(CHAN OF INT From.Previous, To.Next)

SEQ

WHILE TRUE

SEO

From.Previous ? x

To.Next ! x

--Body of the calling Pipeline process

SEQ

Feed.Pipe(ch[0])

PAR i=0 FOR N

Pipe.Stage(ch[i], ch[i+1])

Flush.Pipe(ch[N])

```

Figure 2.5: An Example Occam Program

executed, otherwise the timer channel will fire and process P2 will be executed.

#### 2.6.1.4 Functions and Procedures

As in all modular imperative languages, occam allows the definition of functions (FUNCTION) and procedures (PROC). Procedures encapsulate occam processes; a call to a procedure instantiates the occam process defined by the body of the procedure.

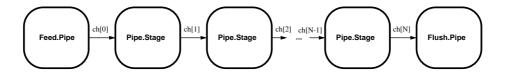

To illustrate the structure and philosophy of occam systems, a small example program is presented in figure 2.5.

Three different processes namely Feed.Pipe, Flush.Pipe and Pipe.Stage are defined as occam procedures. A replicated PAR construct is used to create a pipeline of N processes of type Pipe.Stage. Each process in the pipeline inputs data from the preceding process and outputs data to the succeeding process after performing some processing on the data. The pipeline may thus produce an overlapped operation with each component process of the replicated PAR executing concurrently with every other component process, input and output being automatically synchronized between processes, and a stream of data passing through the pipeline. A one-dimensional array of channels ch is declared, along the elements of which the processes communicate.

## 2.6.2 The Transputer

To provide the means for the efficient execution of occam based parallel applications, Inmos accompanied the development of occam with the design and implementation of a new family of microprocessors, collectively referred to as the *transputer*. The most important classes of the family have been the T400 series and the T800 series; recently Inmos have developed a more advanced type of transputer, namely the T9000.

The transputer is distinguished from conventional microprocessors in that it is particularly designed as a building block for distributed memory MIMD systems.

Figure 2.6: The Architecture of the T800 Transputer

Such a system can be constructed from a collection of transputers which operate concurrently and communicate through serial communication links.

In the transputer, INMOS have implemented on a single chip the main components of a traditional von Neumann computer, while at the same time providing a high level of support for a concurrent, process-based view of computation.

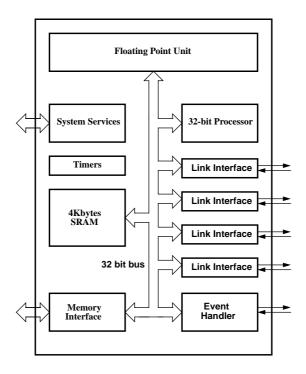

The processing part of the transputer is a 32-bit processor which executes a small<sup>7</sup> range of instructions and addressing modes at a rate of up to 10 MIPS (for 20MHz implementations). The T800 (figure 2.6) features a microcoded 64 bit floating point unit, providing a sustainable performance of 1-2 MFLOPS. The devices of the T400 series do not have a floating point unit and give an estimated performance of 0.1 MFLOPS.

The transputer has two (T400) to four (T800) Kbytes of high speed, on-board

<sup>&</sup>lt;sup>7</sup>The transputer is often classified as a RISC, although there is a controversy on the correctness of this classification.

static RAM which is used as local memory. Off-chip memory may be accessed via a 32-bit wide external memory interface which allow data transfer rates of more than 25 Mbytes per second. In multi-transputer systems, each transputer has sole use of its own on-chip and off-chip memory and thus does not have to compete with the other transputers for common memory accesses.

The transputer incorporates four communication links. Each link can transfer data at over 1 Mbytes/s with automatic handshaking synchronization in each direction, providing a bidirectional, point-to-point, synchronous connection between transputers. A transputer may be linked to four other transputers. In this way networks of transputers of various sizes and topologies may be built up. Each transputer in a network operates as an independent unit communicating as and when necessary with the other transputers to which it is linked.

All transputer components operate concurrently; each of the four links and the floating-point coprocessor (on the T800) can all perform useful work while the processor is executing other instructions.

The transputer is closely integrated with the occam programming language: occam reflects the concurrency found in the transputer and provides for control of the transputer hardware, while the transputer provides efficient support for the occam model of concurrency and communication.

In occam, concurrency may be specified between transputers or indeed within a single transputer. To support internal concurrency, the transputer includes a process queue, with a microcoded scheduler which enables any number of concurrent processes to be executed together sharing the processor time. The microcoded scheduler, combined with a minimal context for each active process, achieve very rapid process switching (typically less than one microsecond).

Examples of T400/T800 transputer based machines are the ESPRIT Supernode Machine [Hock88], the Meiko Computing Surface [Bott86], the Parsytec's

GCel and XPlorer machines [Pars], and the T-Rack [Capo86], a 64 transputer machine which has been implemented at the University of Manchester (the T-Rack is described in chapter 7).

## 2.6.2.1 Configuring Occam Programs

At the top level, an occam program is a network of concurrent communicating processes, defined as occam procedures. These procedures are independent, without reference to any shared program variables or data structures; any required communication takes place by exchanging messages over channels.

The top level occam processes may run time-sliced on a single transputer or be distributed over a network of transputers to achieve real parallelism.

In the first case, the communication channels are realized by internal (or *soft*) links. These are implemented by means of a status word in memory which may be accessed by both the sending and the receiving processes. Consequently, the number of internal occam channels is limited only by the size of local memory.