## POWER-EFFICIENT EMBEDDED PROCESSING

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Engineering and Physical Sciences

2005

By Yijun Liu School of Computer Science

## Contents

| Abstract |                                     |                                            |    |  |  |  |

|----------|-------------------------------------|--------------------------------------------|----|--|--|--|

| De       | Declaration 1<br>Copyright 1        |                                            |    |  |  |  |

| Co       |                                     |                                            |    |  |  |  |

| A        | cknov                               | vledgements                                | 13 |  |  |  |

| 1        | Introduction                        |                                            |    |  |  |  |

|          | 1.1                                 | Research goals and contributions           | 17 |  |  |  |

|          | 1.2                                 | Thesis overview                            | 18 |  |  |  |

| <b>2</b> | Low power design                    |                                            |    |  |  |  |

|          | 2.1                                 | Power dissipation sources in CMOS circuits | 20 |  |  |  |

|          | 2.2                                 | Dynamic power-saving techniques            | 22 |  |  |  |

|          | 2.3                                 | Power breakdown of microprocessors         | 24 |  |  |  |

|          | 2.4                                 | Low power processing techniques            | 27 |  |  |  |

|          |                                     | 2.4.1 Minimizing timing control power      | 27 |  |  |  |

|          |                                     | 2.4.2 Minimizing memory power consumption  | 27 |  |  |  |

|          |                                     | 2.4.3 Increasing code-density              | 29 |  |  |  |

|          |                                     | 2.4.4 'Hard-controlled' processing         | 30 |  |  |  |

|          | 2.5                                 | Metrics for power efficiency               | 30 |  |  |  |

|          | 2.6                                 | Summary                                    | 32 |  |  |  |

| 3        | Power-efficient asynchronous design |                                            |    |  |  |  |

|          | 3.1                                 | Introduction to asynchronous logic design  | 33 |  |  |  |

|          |                                     | 3.1.1 Asynchronous timing strategy         | 34 |  |  |  |

|          |                                     | 3.1.2 Delay models                         | 36 |  |  |  |

|          |                                     | 3.1.3 Data encodings                       | 38 |  |  |  |

|   |     | 3.1.4  | Handshake protocols                                                                                                                                    | ) |

|---|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   |     | 3.1.5  | Asynchronous pipeline latch controllers                                                                                                                |   |

|   | 3.2 | Comp   | arison of the power consumption of synchronous and asyn-                                                                                               |   |

|   |     | chrono | pus designs                                                                                                                                            | ; |

|   |     | 3.2.1  | Global clock and handshakes                                                                                                                            | ) |

|   |     | 3.2.2  | Average latency leading to a simple implementation 46                                                                                                  | j |

|   |     | 3.2.3  | Registers and latches                                                                                                                                  | , |

|   |     | 3.2.4  | Zero standby dynamic power consumption                                                                                                                 | , |

|   |     | 3.2.5  | Fine-grain clock gating                                                                                                                                | ) |

|   | 3.3 | Low-p  | ower asynchronous design                                                                                                                               | , |

|   |     | 3.3.1  | Latch controller selection                                                                                                                             | , |

|   |     | 3.3.2  | Data representation                                                                                                                                    | ; |

|   |     | 3.3.3  | Indication selection                                                                                                                                   | , |

|   | 3.4 | Summ   | ary                                                                                                                                                    | ; |

|   | Ŧ   |        |                                                                                                                                                        |   |

| 4 |     | -      | r arithmetic unit design 59                                                                                                                            |   |

|   | 4.1 |        | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                   |   |

|   | 4.2 | -      | style selection $\ldots \ldots \ldots$ |   |

|   | 4.3 |        | representations                                                                                                                                        |   |

|   | 4.4 |        | design $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                |   |

|   |     | 4.4.1  | Architecture selection                                                                                                                                 | 2 |

|   |     | 4.4.2  | The design of an asynchronous carry-lookahead adder based                                                                                              |   |

|   |     |        | on data characteristics                                                                                                                                |   |

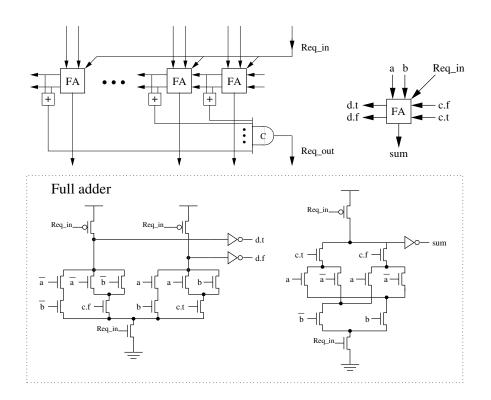

|   |     | 4.4.3  | An asynchronous carry-lookahead adder                                                                                                                  |   |

|   |     | 4.4.4  | Completion detector design                                                                                                                             |   |

|   |     | 4.4.5  | 1                                                                                                                                                      |   |

|   | 4.5 | -      | plier design $\ldots$ $75$                                                                                                                             |   |

|   |     | 4.5.1  | Basic building blocks and architectures                                                                                                                |   |

|   |     | 4.5.2  | Commonly-used algorithms                                                                                                                               |   |

|   |     | 4.5.3  | Architecture selection                                                                                                                                 |   |

|   |     | 4.5.4  | Input vector characteristics                                                                                                                           |   |

|   | 4.6 |        | power iterative multiplier                                                                                                                             |   |

|   |     | 4.6.1  | A shift-iterative architecture                                                                                                                         |   |

|   |     | 4.6.2  | A radix-2 algorithm                                                                                                                                    |   |

|   |     | 4.6.3  | Sign-changing Algorithm                                                                                                                                | ì |

|   |     | 4.6.4  | Circuit implementation                                                                                                                                 | ; |

|          |      | 4.6.5    | Experimental results                                                                                                                                          |

|----------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.7  | Summa    | ary                                                                                                                                                           |

| <b>5</b> | A lo | ow-pow   | er embedded SRAM macro design 92                                                                                                                              |

|          | 5.1  | SRAM     | design overview                                                                                                                                               |

|          |      | 5.1.1    | Conceptual SRAM structure                                                                                                                                     |

|          |      | 5.1.2    | Low power SRAM design techniques                                                                                                                              |

|          |      | 5.1.3    | Block partitioning                                                                                                                                            |

|          | 5.2  | Low-sw   | ving write techniques                                                                                                                                         |

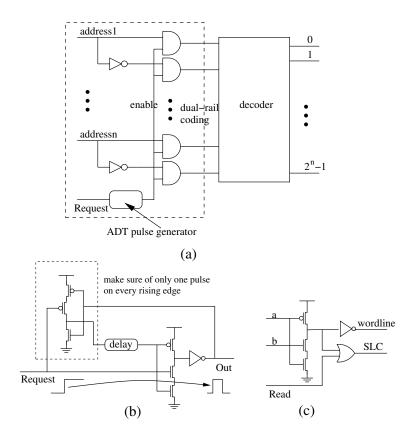

|          | 5.3  | A dual   | -rail decoder $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $102$                                                                   |

|          | 5.4  | Archite  | ecture and timing $\ldots \ldots 105$                                            |

|          | 5.5  | Layout   | and experimental results                                                                                                                                      |

|          | 5.6  | Summa    | ary                                                                                                                                                           |

| 6        | Low  | -power   | hierarchical processing 110                                                                                                                                   |

|          | 6.1  | Hierarc  | chical processing                                                                                                                                             |

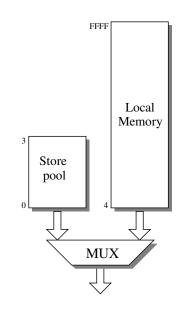

|          | 6.2  |          | archical processing architecture                                                                                                                              |

|          |      | 6.2.1    | The overall architecture                                                                                                                                      |

|          |      | 6.2.2    | Coupling the CPU and the coprocessor                                                                                                                          |

|          | 6.3  | RISC c   | coprocessor design                                                                                                                                            |

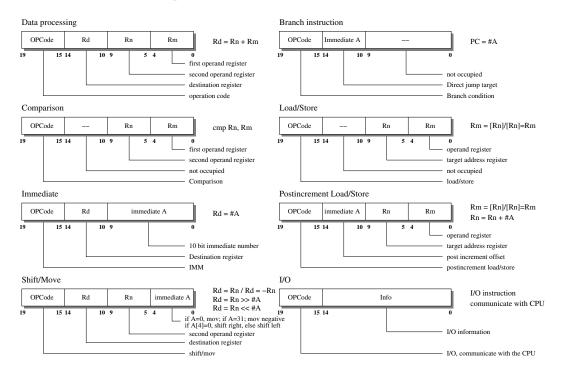

|          |      | 6.3.1    | Instruction set design                                                                                                                                        |

|          |      | 6.3.2    | The cost of pipelining $\ldots \ldots \ldots$ |

|          |      | 6.3.3    | The proposed RISC coprocessor architecture                                                                                                                    |

|          |      | 6.3.4    | Primary experimental results                                                                                                                                  |

|          | 6.4  | Summa    | ary                                                                                                                                                           |

| 7        | The  | e design | of a dataflow coprocessor 132                                                                                                                                 |

|          | 7.1  | Introdu  | action to dataflow machines $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 132$                                                       |

|          |      | 7.1.1    | Dataflow graphs                                                                                                                                               |

|          | 7.2  | The pr   | oposed dataflow model                                                                                                                                         |

|          | 7.3  | The da   | taflow coprocessor architecture                                                                                                                               |

|          | 7.4  | Circuit  | implementation $\ldots \ldots 144$                                        |

|          |      | 7.4.1    | Controller design                                                                                                                                             |

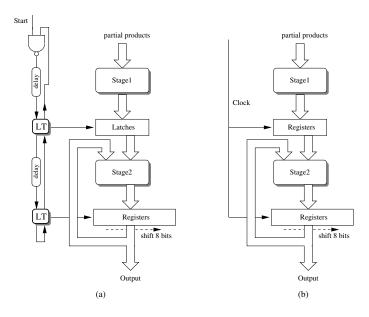

|          |      | 7.4.2    | Pipeline control for various stage numbers 145                                                                                                                |

|          | 7.5  | An aut   | omatic mapping algorithm $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 146$                                                                        |

|          | 7.6  | Experii  | mental results and comparisons                                                                                                                                |

|                  |               | 7.6.1  | Experimental results | 151 |  |

|------------------|---------------|--------|----------------------|-----|--|

|                  |               | 7.6.2  | Comparisons          | 153 |  |

|                  | 7.7           | Summ   | ary                  | 159 |  |

| 8                | 8 Conclusions |        |                      | 161 |  |

|                  | 8.1           | Future | work                 | 163 |  |

| Bibliography 165 |               |        |                      |     |  |

## List of Tables

| 3.1 | The characteristics of the Amulet3 processor $[1]$                | 45  |

|-----|-------------------------------------------------------------------|-----|

| 3.2 | Power comparison of multipliers using three different data repre- |     |

|     | sentations                                                        | 54  |

| 3.3 | Power and delay comparisons                                       | 56  |

| 4.1 | Comparison of different adder architectures $[2]$                 | 66  |

| 4.2 | Input vectors                                                     | 69  |

| 4.3 | The comparison of different adders                                | 75  |

| 4.4 | The modified Booth's algorithm scheme                             | 78  |

| 4.5 | Characteristics of multiplier architectures                       | 81  |

| 4.6 | Operand distribution between positive and negative                | 81  |

| 4.7 | Numbers of transitions in Booth's and non-Booth's multipliers     | 86  |

| 4.8 | Power comparison of 4 multipliers                                 | 89  |

| 5.1 | Comparisons between the new SRAM and ST macrocell                 | 107 |

| 6.1 | The coprocessor instruction set                                   | 122 |

| 6.2 | Data size distribution $[3]$                                      | 129 |

| 6.3 | The characteristics of the proposed RISC coprocessor components   | 130 |

| 7.1 | The structure of an instruction                                   | 139 |

| 7.2 | The characteristics of the dataflow coprocessor                   | 151 |

| 7.3 | The characteristics of the components                             | 151 |

| 7.4 | The statistic of energy of the benchmarks                         | 152 |

## List of Figures

| 1.1  | Trends in the power consumption of battery-powered chips $[4]$                                              | 16 |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 2.1  | The power breakdown of a StrongARM processor [5] $\ldots \ldots$                                            | 25 |

| 3.1  | A synchronous pipeline circuit                                                                              | 35 |

| 3.2  | An asynchronous pipeline circuit                                                                            | 36 |

| 3.3  | The relations and delay assumptions of asynchronous circuits using                                          |    |

|      | unbounded-delay models                                                                                      | 37 |

| 3.4  | An asynchronous pipeline using a code-data coding $\ldots \ldots \ldots$                                    | 39 |

| 3.5  | A dual-rail encoding scheme and its completion detector $\ldots$ .                                          | 40 |

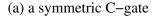

| 3.6  | Example logic symbols and schematics of symmetric and asym-                                                 |    |

|      | metric C-gates                                                                                              | 41 |

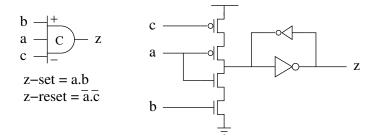

| 3.7  | A 1-of-4 encoding scheme and its completion detector                                                        | 42 |

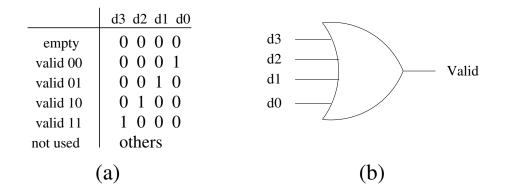

| 3.8  | The validity scheme of a 2-phase protocol                                                                   | 42 |

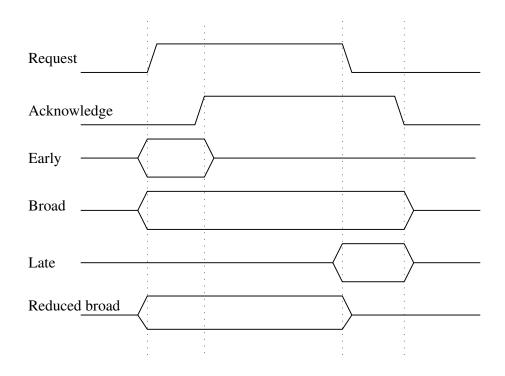

| 3.9  | The validity schemes of 4-phase protocols                                                                   | 43 |

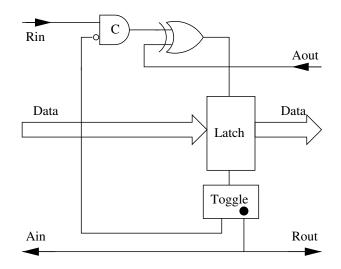

| 3.10 | The schematic of a 2-phase latch controller                                                                 | 44 |

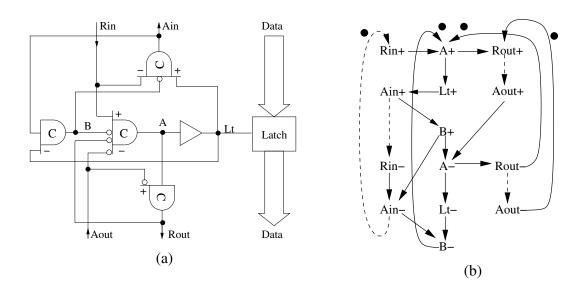

| 3.11 | A 4-phase latch controller and its STG description                                                          | 45 |

| 3.12 | An asynchronous multiplier datapath and its synchronous coun-                                               |    |

|      | terpart                                                                                                     | 50 |

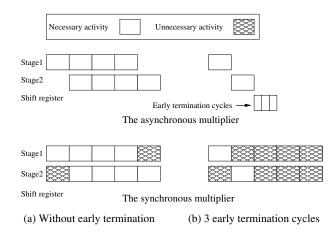

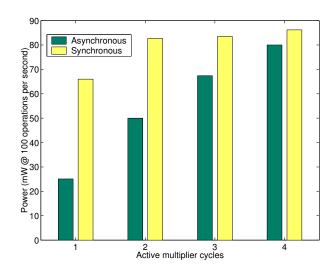

| 3.13 | The pipeline activities of two multipliers                                                                  | 51 |

| 3.14 | The power consumptions of two multipliers                                                                   | 51 |

| 3.15 | Transition numbers in different data representations                                                        | 53 |

| 3.16 | The capacitance distribution of a CMOS gate $\ldots \ldots \ldots \ldots$                                   | 54 |

| 3.17 | Two schemes for long distance interconnection                                                               | 56 |

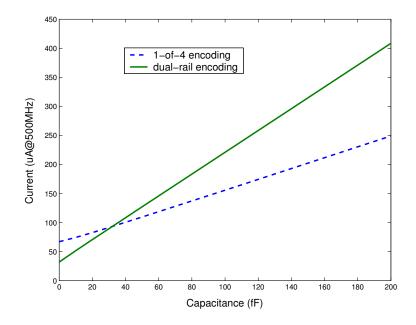

| 3.18 | Power vs. wire capacitance                                                                                  | 57 |

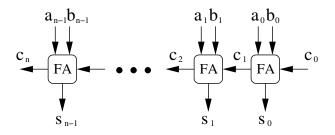

| 4.1  | A ripple carry adder                                                                                        | 60 |

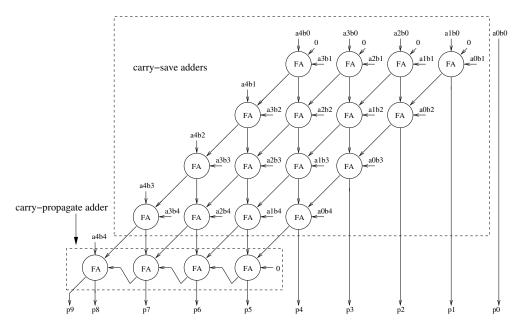

| 4.2  | A 5 $\times$ 5-bit array multiplier $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 61 |

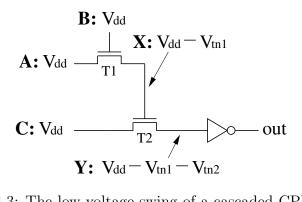

| 4.3  | The low voltage swing of a cascaded CPL circuit                                                             | 63 |

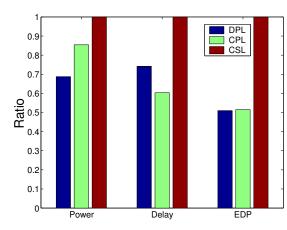

| 4.4  | Comparison of DPL, CPL and CSL $8 \times 8$ -bit multiplier $\ldots \ldots 64$                                                                                                        |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.5  | A hybrid asynchronous adder which displays average-case latency 67                                                                                                                    |

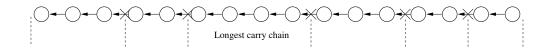

| 4.6  | A weakly indicating asynchronous carry chain                                                                                                                                          |

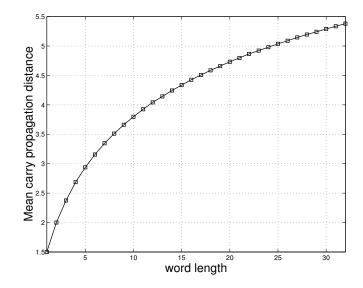

| 4.7  | Average size of the longest carry chain for different word lengths                                                                                                                    |

|      | assuming random data distribution [6] 68                                                                                                                                              |

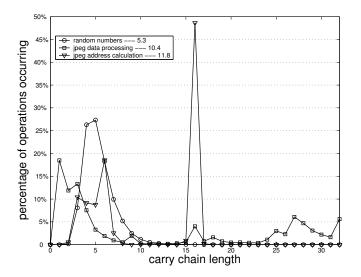

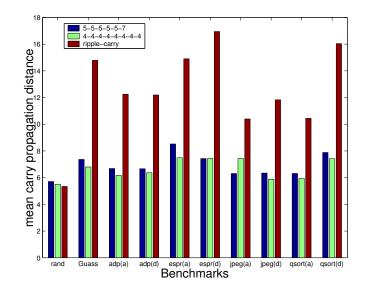

| 4.8  | Longest carry propagate distance distribution                                                                                                                                         |

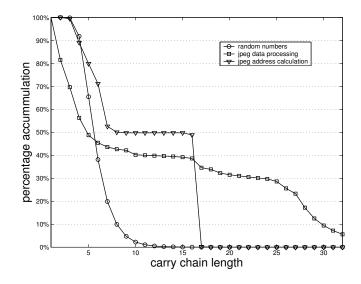

| 4.9  | Proportion of longest carry chains exceeding given length 70                                                                                                                          |

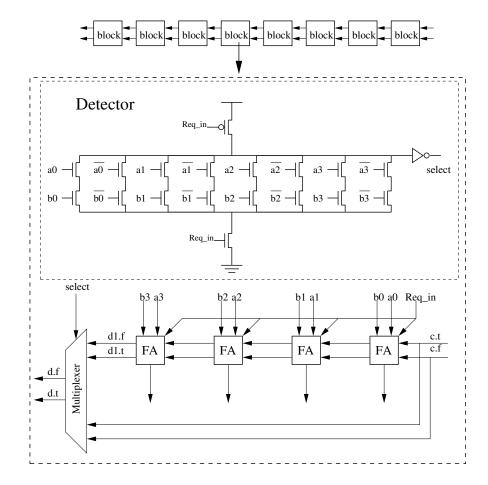

| 4.10 | The proposed adder                                                                                                                                                                    |

| 4.11 | Delay comparison of three asynchronous adders                                                                                                                                         |

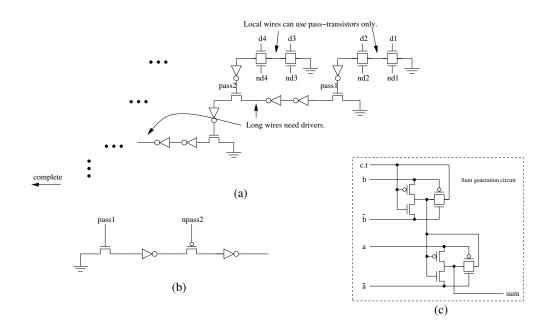

| 4.12 | The pass-transistor tree completion detector and sum generation                                                                                                                       |

|      | circuit                                                                                                                                                                               |

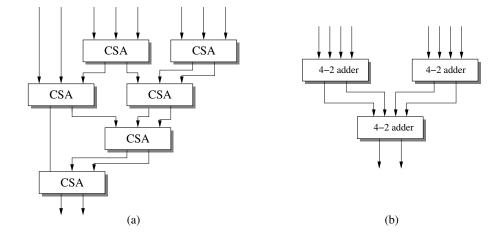

| 4.13 | Two 8-2 tree adders using 3-2 adders and 4-2 adders                                                                                                                                   |

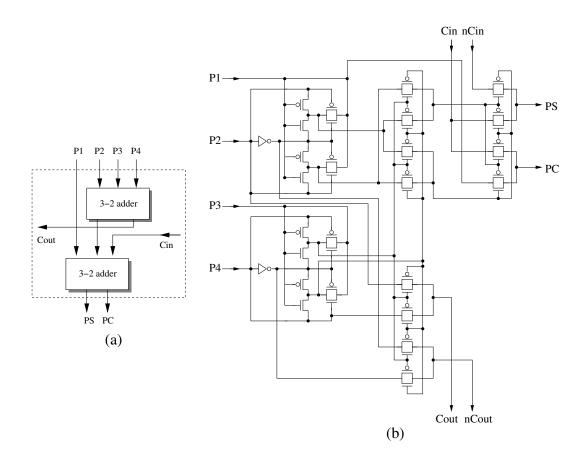

| 4.14 | Two ways of implementing a 4-2 adder                                                                                                                                                  |

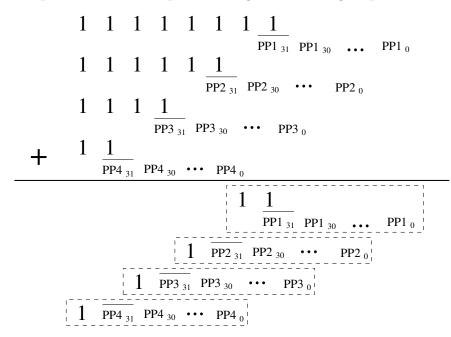

| 4.15 | The principle of an improved sign extension algorithm                                                                                                                                 |

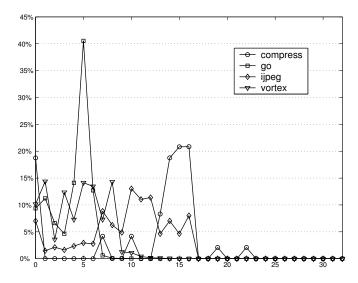

| 4.16 | SBC distributions for the benchmark programs                                                                                                                                          |

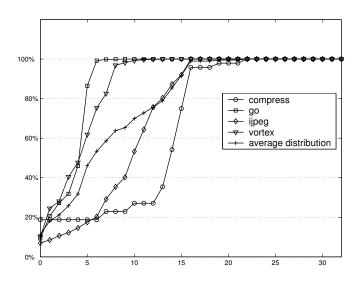

| 4.17 | Proportion of operands having SBC below given number 82                                                                                                                               |

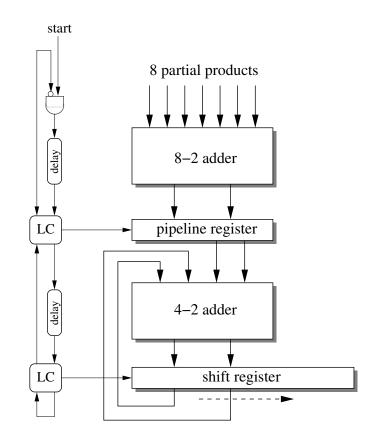

| 4.18 | A shift-iterative architecture                                                                                                                                                        |

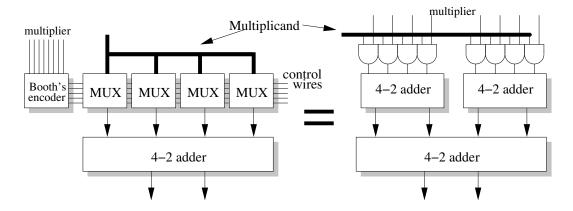

| 4.19 | Two kinds of 8-2 adder trees                                                                                                                                                          |

| 4.20 | Distributing the higher-order 1s                                                                                                                                                      |

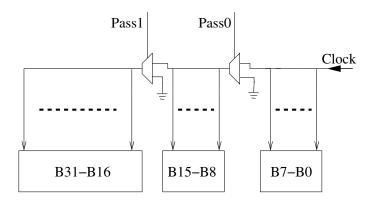

| 4.21 | 32-bit split register organization                                                                                                                                                    |

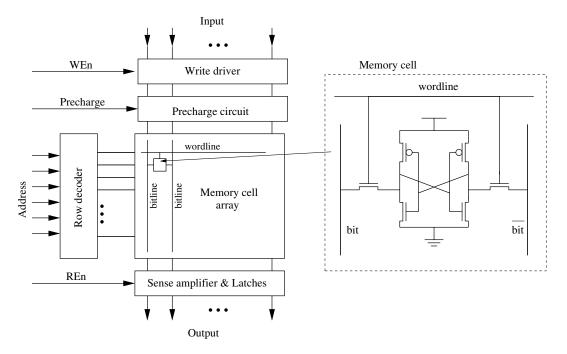

| 5.1  | A conceptual SRAM architecture                                                                                                                                                        |

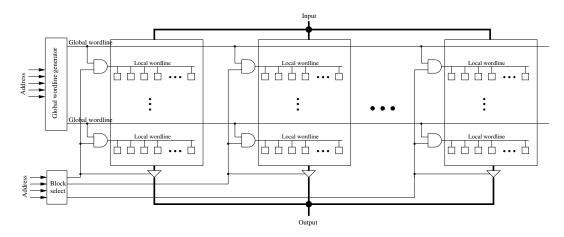

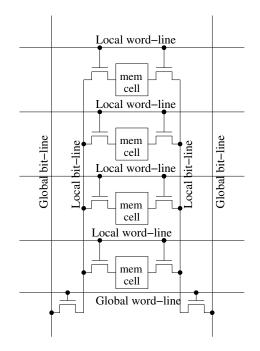

| 5.2  | A divided word-line approach                                                                                                                                                          |

| 5.3  | A divided bit-line approach                                                                                                                                                           |

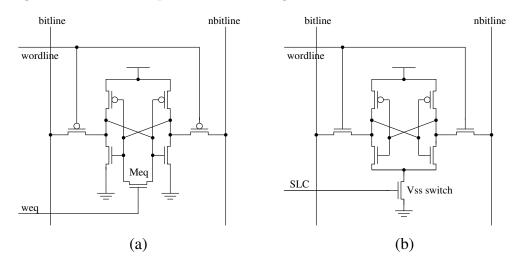

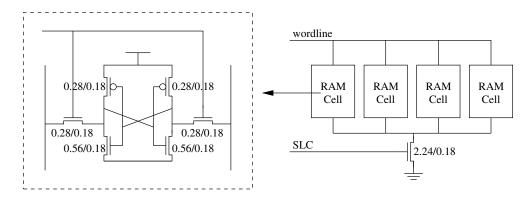

| 5.4  | 'Input-sensitive' RAM cells                                                                                                                                                           |

| 5.5  | Amrutur's low write scheme                                                                                                                                                            |

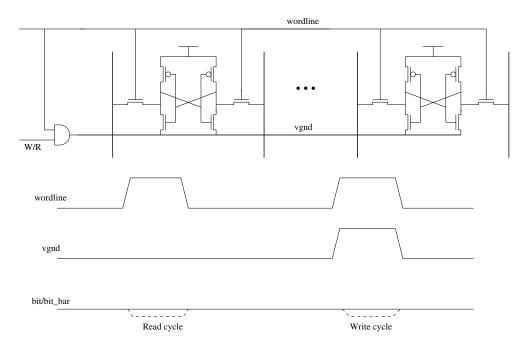

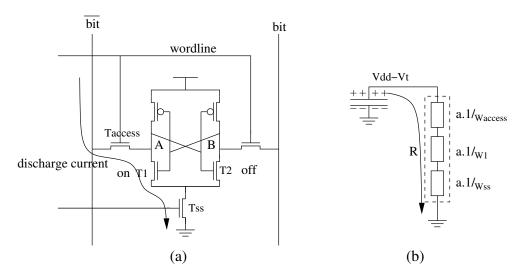

| 5.6  | Discharge current during read                                                                                                                                                         |

| 5.7  | Shared $T_{ss}$ scheme to reduce area overhead $\ldots \ldots \ldots$ |

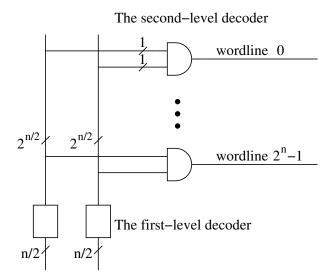

| 5.8  | A two-level decoder                                                                                                                                                                   |

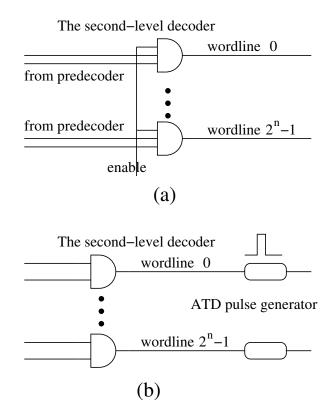

| 5.9  | Pulsing word-line techniques                                                                                                                                                          |

| 5.10 | The proposed dual-rail decoder                                                                                                                                                        |

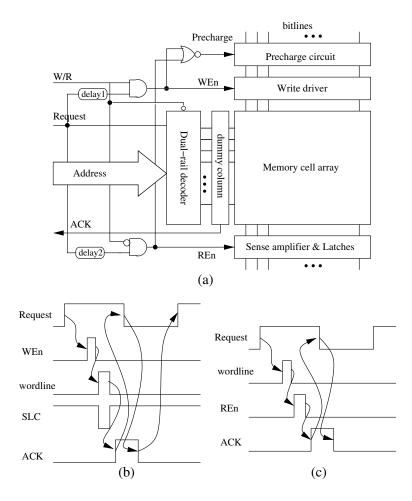

| 5.11 | The architecture and timing of the proposed SRAM 106                                                                                                                                  |

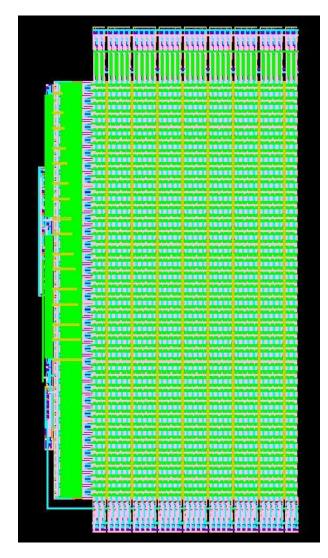

| 5.12 | The layout of the proposed SRAM 108                                                                                                                                                   |

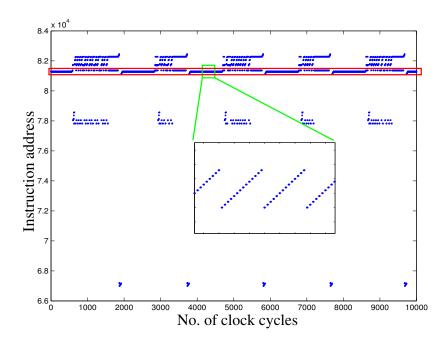

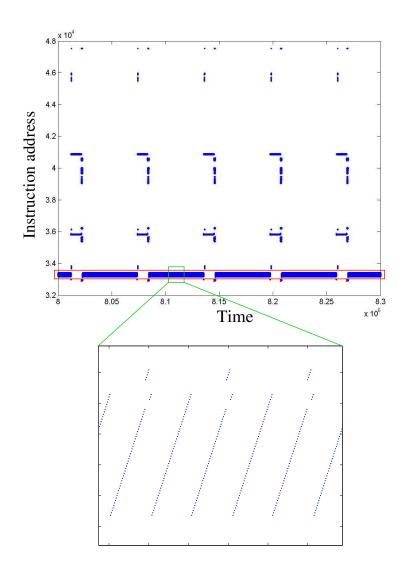

| 6.1  | The running trace segment of a JPEG program 112                                                                                                                                       |

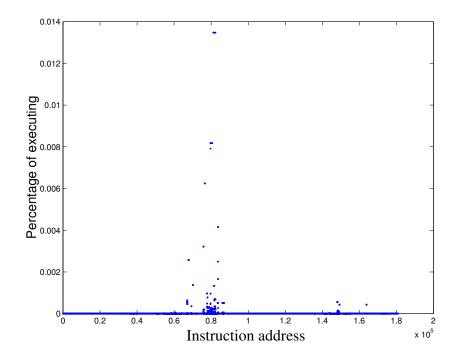

| 6.2  | The distribution of execution time for instructions in a JPEG pro-                       |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | gram                                                                                     | 113 |

| 6.3  | The running trace segment of a media processing program $\ldots$ .                       | 114 |

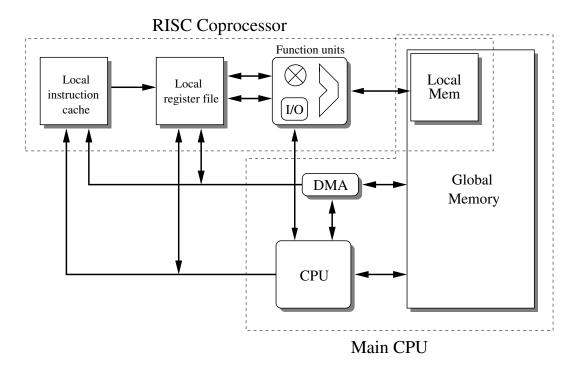

| 6.4  | The proposed hierarchical processing architecture                                        | 116 |

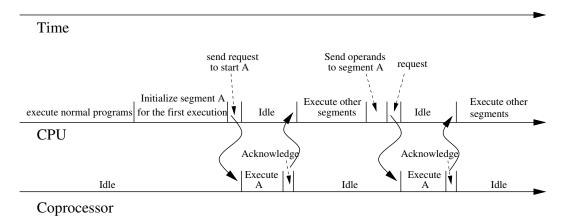

| 6.5  | The cooperation between the CPU and the coprocessor $\ . \ . \ .$ .                      | 118 |

| 6.6  | The structure of the instruction set $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$  | 121 |

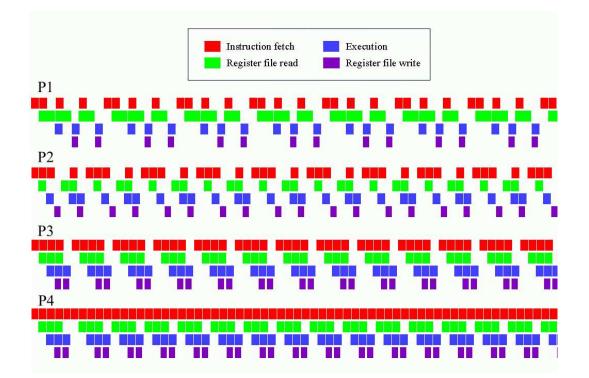

| 6.7  | The pipeline operations of the four processors $\ldots \ldots \ldots \ldots$             | 125 |

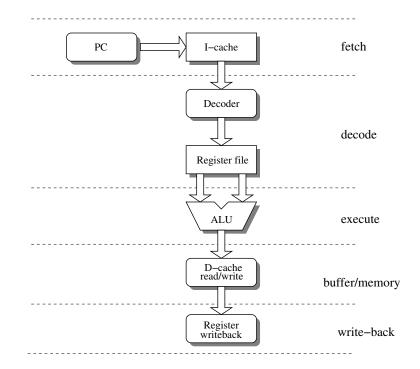

| 6.8  | A conventional 5-stage RISC pipeline architecture                                        | 127 |

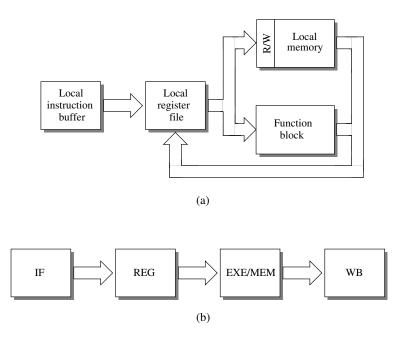

| 6.9  | The organization and pipeline architecture of the coprocessor                            | 128 |

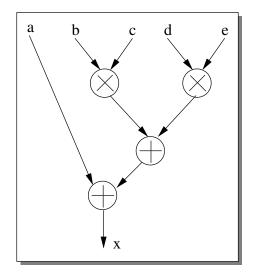

| 7.1  | A dataflow graph for a long equation                                                     | 134 |

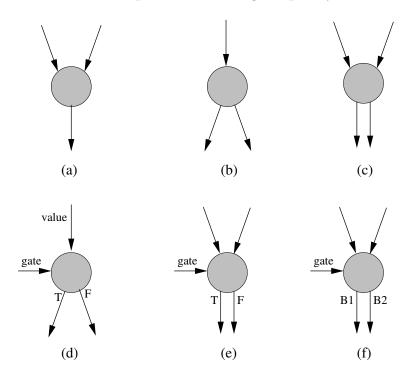

| 7.2  | Basic dataflow nodes                                                                     | 135 |

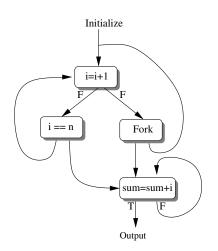

| 7.3  | A dataflow graph for $sum = 1 + 2 + \dots + n$                                           | 136 |

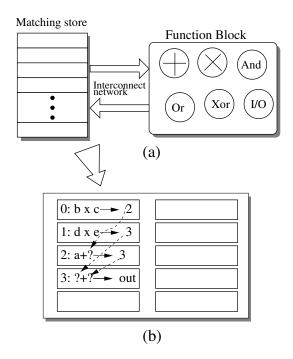

| 7.4  | A static dataflow architecture                                                           | 137 |

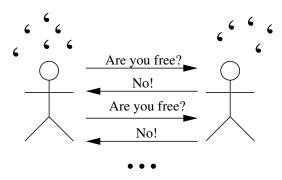

| 7.5  | The comparison of two different synchronization schemes                                  | 139 |

| 7.6  | The state transition diagram of an instruction                                           | 142 |

| 7.7  | The proposed dataflow architecture                                                       | 143 |

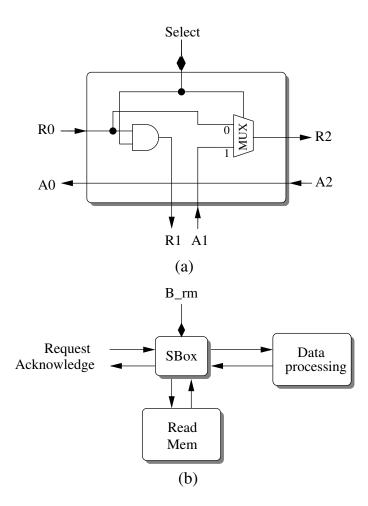

| 7.8  | The interface of the control FSM                                                         | 144 |

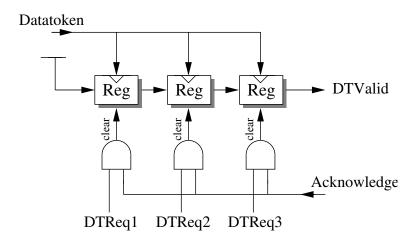

| 7.9  | The schematic of the data token counter $\ldots \ldots \ldots \ldots \ldots$             | 145 |

| 7.10 | An implementation of a pipeline with various stage number                                | 146 |

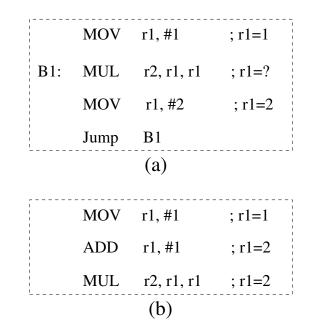

| 7.11 | An example of mapping RISC codes to dataflow codes                                       | 147 |

| 7.12 | Two problems of automatic mapping                                                        | 148 |

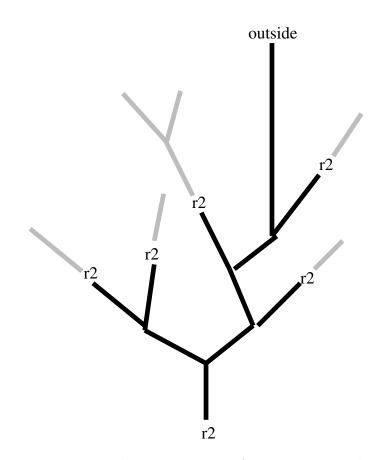

| 7.13 | The actual trace of a converse search $\hdots \ldots \ldots \ldots \ldots \ldots \ldots$ | 149 |

| 7.14 | An architecture for reducing duplications                                                | 156 |

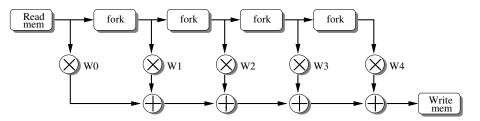

| 7.15 | A dataflow diagram for FIR                                                               | 158 |

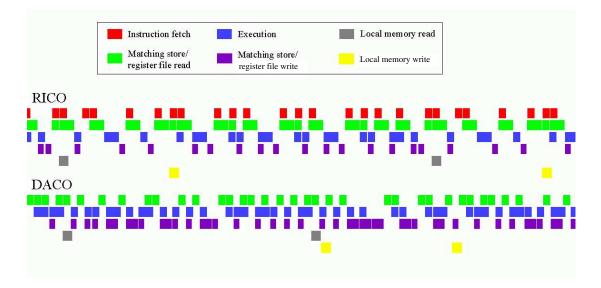

| 7.16 | The pipeline operations of FIR in RICO and DACO                                          | 159 |

## Abstract

As more and more transistors and functionality are integrated in single chips, power consumption has become one of the most important design parameters in modern embedded circuits. The purpose of the work described in this dissertation is to identify ways to reduce the power consumption of embedded systems. Lowpower design is a complex task requiring care at all levels of the design hierarchy. In this dissertation, the focus is mainly on the following low-power techniques:

- Exploring asynchronous logic design for its low-power potential. The powerefficiencies of asynchronous and synchronous designs are compared. Different asynchronous design issues are also discussed in terms of their powerefficiency.

- Circuit-level optimizations to reduce the power consumption of function units, including adders and multipliers, and memory. An asynchronous carry-lookahead adder and a pipelined iterative multiplier are presented, both of which are designed based on analyses of their input data characteristics. The circuit-level design issues of a low-power embedded SRAM macro are also presented.

- Architecture-level optimizations to reduce the execution overheads of softprogrammable processors. A hierarchical processing architecture is proposed based on an analysis of embedded processing programs. A RISC-like coprocessor has been designed to demonstrate the power-efficiency of a hierarchical processing architecture. A dataflow coprocessor has also been designed which is more power-efficient and faster than the RISC-like coprocessor.

Together these results demonstrate that there is scope for improvements in power-efficiency at several different levels in the design hierarchy, underlining the need to treat low-power design as a holistic process.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institution of learning.

## Copyright

Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the head of School of Computer Science.

## Acknowledgements

The work leading to this dissertation was done during my three years as a postgraduate student in the APT group in the School of Computer Science at the University of Manchester, UK. These years have been very stimulating and instructive. The friendly people and atmosphere in the group has greatly helped the work described in the thesis.

First of all I would like to give my deepest thanks to my supervisor, Professor Steve Furber, whose support and guidance over the post few years have been invaluable for this work.

Special thanks are due to Dr. Jim Garside, my advisor, for his very beneficial advice on many different problems. Special thanks are also due to Dr. Steve Temple and Dr. Viv Woods not only for their patience in proofreading the draft of the thesis but also for their kind help with CAD tools and my English.

Many thanks to everyone else in the APT group for their support, encouragement and friendship.

I would also like to acknowledge with gratitude the support of an ORS grant from Universities UK and a research scholarship from the School of Computer Science. to my family

## Chapter 1 Introduction

The exponential development of CMOS technology [7] makes it possible to embed high-performance data processing units in portable and wireless devices such as cell phones, personal digital assistants (PDAs), multi-media players and sensor network applications. The high data processing ability allows these devices to support a wide range of functions and wireless communications, making these devices popular and necessary for daily life. The worldwide market for digital signal processing (DSP) has grown to 7.8 billion dollars per annum and is developing at an annual growth rate of 30%. Of these DSP chips, 71.5% are used in wireless applications, mostly in cell phones [4]. The rapid growth of the wireless market also inspires the growth in the functionality of PDAs, digital cameras and multi-media players. The increasing prominence of portable and wireless devices has become one of the major impetuses that drives CMOS VLSI design.

Although performance is still a very important issue in the design of wireless and portable devices, it is not the only concern. Battery life, package size, device weight and, of course, cost are also important metrics. The power consumption of the CMOS circuits in these devices has a direct relation to these factors. Wireless and portable applications call for low-power design.

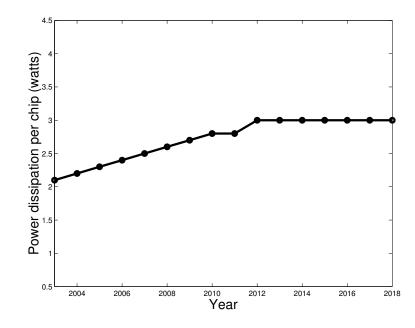

Figure 1.1 shows the power consumption growth of battery-powered chips predicted by the International Technology Roadmap for Semiconductors (ITRS) [8]. ITRS predicts that after 2012, the power consumption of battery-powered chips will be maintained at 3 watts. However, this prediction is not reliable if the power consumption of VLSI chips is maintained only by CMOS technology scaling (although it is the major contributor) without addressing low-power design techniques. Moreover, the demand to prolong the operation of portable devices

Figure 1.1: Trends in the power consumption of battery-powered chips [4]

between charges will never stop. Some new applications bring forward even more 'critical' requirements for circuit power-efficiency. For example, sensor network designers suggest that a small battery (maybe an "AA"-size battery) should power the whole device life of a sensor node [9]. Low-power techniques are extremely important in the design of the CMOS circuits in these applications. Low-power techniques also allow devices to operate without thermal management, resulting in a cheaper package and smaller size. High power consumption affects the reliability of CMOS circuits, so low-power techniques improve the robustness of devices as well.

As the requirements of portable and wireless devices shift from high performance to high portability and long battery life, a rethinking of design flow and techniques is necessary. For embedded data processing circuits, the 'performance first' CMOS design philosophy needs to be changed. Power consumption concern should be considered as one of the most important metrics in CMOS circuit design together with performance and area considerations. This thesis will address low-power techniques for data processing especially in battery-powered embedded applications.

The remainder of this chapter presents the research goals and major contributions. It concludes with an overview of the rest of the thesis.

#### 1.1 Research goals and contributions

It would be impossible to include all low-power processing design issues in a single thesis. Instead, low-power asynchronous logic, power-efficient arithmetic units, low-power memory design and a coprocessor architecture based on the characteristics of embedded processing applications are the emphases of this thesis. The key research contributions include:

- Evaluating the contribution of asynchronous logic to the design of low-power data processing;

- The development of a set of power-efficient arithmetic function units, including an iterative pipelined multiplier and an asynchronous carry-lookahead adder. The design of these functional units begins with the analysis of the characteristics of input vectors; these guide the power-saving techniques used in the arithmetic units.

- The design of a low-power embedded SRAM macro, which adopts a novel dual-rail row decoder and a low-swing write-voltage scheme.

- The development of a hierarchical architecture which aims to reduce the power consumption of most commonly executed short code segments, such as small loops and long equation evaluations. Several architectures are evaluated in terms of power-efficiency, including conventional RISC architectures and a dataflow architecture using a novel synchronization scheme. The experimental results demonstrate an order of magnitude of improvement in power-efficiency over current general-purpose processors.

The research described in this thesis has led to the following publications:

- "The design of an asynchronous carry-lookahead adder based on data characteristics", Proceedings of PATMOS 2005, Springer, Lecture Notes in Computer Science.

- "A Low Power Embedded Dataflow Coprocessor", Proceedings of the 2005 International Symposium on VLSI System Design.

- "The Design of a Low-Power Asynchronous Multiplier", Proceedings of the 2004 International Symposium on Low Power Electronics and Design.

- "Minimizing the Power Consumption of an Asynchronous Multiplier", Proceedings of PATMOS 2004, Springer, Lecture Notes in Computer Science.

- "A Transistor-Level Delay-Insensitive Register File for Deep Sub-micron SoC", Proceedings of the Embedded Systems Show, October, 2004.

- "The Design of a DI adder using 1-of-4 code", Proceedings of the 15th UK Asynchronous Forum, Cambridge, January, 2004.

- "A Low-Power Asynchronous multiplier", Proceedings of the IEE Seminar on SoC Design, Test and Technology, September, 2003.

#### 1.2 Thesis overview

Chapter 2 reviews the fundamentals of low-power CMOS design. It analyses the power consumption of conventional processors and gives an overview of low-power processing techniques.

Chapters 3 to 5 focus on more detailed low-power techniques for low-level CMOS circuit implementations, including:

Chapter 3 addresses low-power techniques in a specific field — asynchronous design. It briefly introduces basic asynchronous logic design; it then compares the power-efficiency of synchronous and asynchronous design; finally, low-power asynchronous logic techniques are discussed.

Chapter 4 presents the designs of two power-efficient arithmetic units, an adder and a multiplier, based on the analysis of the input vector characteristics of arithmetic units.

Chapter 5 addresses the design issues of a low-power embedded RAM macro.

Chapters 6 and 7 discuss architecture-level design issues aiming at reducing the power consumption of soft programmable embedded processors, including:

Chapter 6 presents an analysis of embedded processing programs and proposes a hierarchical processing scheme based on a CPU-coprocessor architecture. The coprocessor can do a lot of the work of a general-purpose processor and is more flexible than a conventional coprocessor which supports only a limited set of functions, such as floating-point calculations. The coprocessor need not support those complex functions of a general-purpose processor, such as a wide range of addressing modes and instructions, and in this way power overheads due to complex control and instruction decoding can be avoided. Chapter 6 analyzes the power savings that can be achieved by using different RISC-like architectures and their performance implications.

Chapter 7 studies the power-efficiency of another less-studied strategy — a dataflow architecture. Detailed issues of a low-power dataflow architecture are addressed in this chapter and the advantages and disadvantages of dataflow and conventional RISC architectures are compared.

Chapter 8 provides the conclusions of the thesis and directions for future work.

## Chapter 2

## Low power design

This chapter presents a review of circuit-level low-power CMOS design techniques. The sources of power dissipation in CMOS circuits, fundamental dynamic power saving techniques and power-efficiency metrics are briefly described. The power dissipation of conventional data processing units — microprocessors — is analyzed which gives the direction for further power saving. The chapter also gives a survey of low-power processing techniques.

#### 2.1 Power dissipation sources in CMOS circuits

There are four sources of power consumption in a CMOS circuit, as described in the following equation [10]:

$$P_{total} = P_{dynamic} + P_{leakage} + P_{short} + P_{static}$$

where  $P_{total}$  is the total power consumption of the circuit, being the sum of four factors:  $P_{dynamic}$  — the dynamic power consumption,  $P_{leakage}$  — the leakage power consumption,  $P_{short}$  — the short-circuit power consumption and,  $P_{static}$  the static power consumption.

• Dynamic power consumption

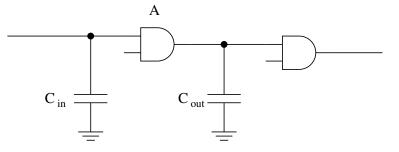

The dynamic power consumption of a CMOS circuit results from the charging and discharging of the capacitances of wires and transistors. The dynamic power consumption of a CMOS gate is equal to:

$$P_{dynamic} = \frac{1}{2} \cdot C_{load} \cdot V_{dd}^2 \cdot N \cdot f \tag{2.1}$$

where  $C_{load}$  is the overall capacitance of its output node and the gate(s) it drives;  $V_{dd}$  is the supply voltage; N is the average number of transitions in one clock cycle; f represents the switching frequency of the clock. The dynamic power consumption of a CMOS gate depends on how frequently the gate is switched. If a gate does nothing, there is no dynamic power dissipation. Since CMOS circuits normally run at very high clock frequencies, the dynamic power consumption is the dominant factor in the overall power consumption of CMOS circuits (This situation may change when using deep sub-micron CMOS technologies). Methods to reduce dynamic power consumption are the emphasis of this thesis.

• Leakage power consumption

Leakage power dissipation has two components: the reverse-bias diode leakage current at transistor drains and the sub-threshold current through a turned-off transistor channel. Leakage power dissipation is one of the proportions of overall power dissipation not caused by switching activity. Leakage current exists even when a circuit is idle. Therefore, although the leakage current of a single transistor is very small, the total effect of the leakage current can be significant in a big chip. Moreover, the leakage increases rapidly when the threshold of the devices drops. Deep sub-micron CMOS circuits normally have very low threshold voltages. Therefore, leakage is becoming another significant factor of power dissipation in these circuits. Although minimizing leakage power dissipation is an important aspect of CMOS power saving, it is a general problem, normally not depending on the different data being processed. Reducing leakage power consumption is outside the scope of this thesis. More detailed information on leakage power reduction can be found elsewhere [11] [12].

• Short-circuit power consumption

Ideally, in a complementary CMOS gate, the pull-up pMOS network and the pull-down nMOS network should not conduct at the same time. However, in practice, there is a short period during each switching transition when both the pMOS and nMOS networks conduct, allowing a current to flow directly from  $V_{dd}$  to ground. This current is called the short-circuit current. If the input transition is slow, the duration of the short-circuit current becomes correspondingly longer, resulting in significant short-current power

dissipation. However, good design will avoid slow edges and can keep shortcircuit power dissipation to a small fraction of the dynamic power.

• Static power consumption

For traditional complementary static circuits using full voltage swing, there is no static power consumption caused by a constant static current flow because, during any operation, either the pMOS or the nMOS network is closed. However, in circuits using other CMOS logic styles, a constant static current may exist; pass-transistor logic and pseudo-nMOS logic are two examples. For a pass-transistor circuit, the low output voltage-swing of a pass-transistor gate (such as a weak 1 after an n-pass-transistor) may cause both the p-transistor network and the n-transistor network after the passtransistor gate to conduct, allowing a static current from Vdd to ground. A pseudo-nMOS logic gate contains a single p-transistor, whose gate is always connected to ground; when the pull-down nMOS network conducts, a static current exists between Vdd and ground.

#### 2.2 Dynamic power-saving techniques

Equation 2.1 revealed the three degrees of freedom inherent in dynamic powersaving techniques: supply voltage, physical capacitance and switching activity.

• Voltage reduction:

Because of its quadratic relationship to power, voltage reduction offers the most effective means of minimizing power consumption. The power-saving techniques due to supply voltage reduction are as follows:

- More advanced CMOS technologies need lower supply voltages and hence using these CMOS technologies contributes to low-power VLSI design.

- If the speed of a circuit using a standard CMOS supply voltage is fast enough, the circuit can be powered by a voltage lower than the standard supply voltage and may still meet the throughput and peak performance requirements of applications. If the supply voltage is too low to meet the performance requirements, some dedicated techniques

can be used to speed up the circuit, such as parallelism and pipelining [13].

• Capacitance reduction:

Dynamic power consumption depends on the switched capacitance, thus minimizing the effective capacitance which is charged and discharged also results in power saving.

CMOS technology scaling greatly contributes to reducing the power consumption of CMOS circuits. Technology scaling reduces the capacitance of transistors and wires. It also allows devices to have a low supply voltage while maintaining their performance because devices have a low threshold voltage.

Using the same CMOS technology, capacitance can be kept at a minimum by using simple circuit implementations, more efficient logic styles, fewer transistors, or shorter interconnect wires.

• Switching activity reduction:

The goal of reducing switching activity is to reduce the average number of transitions in a clock cycle (N in Equation 2.1). Switching activity reduction techniques can be separated into two categories: minimizing unwanted activity and minimizing the required activity.

Ideally, the gates of a CMOS circuit should only switch when performing useful tasks. However, in real designs, unwanted transitions unavoidably exist. For example, in a synchronous circuit, all registers are linked to a global clock signal and their gate loads are forced to charge and discharge in every clock cycle even when they have no valid inputs. These unnecessary transitions contribute to make the global clock one of the largest loads in synchronous circuits. One efficient way to minimize the unnecessary transitions is by gating off sub-blocks which perform no required activity [14].

Another source of unwanted switching activity is glitches; these are spurious transitions which occur before a node settles down to its final steady-state value. One example of a glitch is the sum signals of a carry-propagate adder. Because of the chain of carry signals, some intermediate states occur at the outputs of the sum signals and cause a lot of unnecessary switching activity inside the adder. A more serious situation is when these output glitches are propagated through the whole pipeline and cause a sequence of unwanted activity. It is difficult to get rid of all glitches in a circuit, but the number and their effects can be minimized. An efficient way to minimize the impact of glitches is to isolate them within a pipeline stage by opening pipeline registers for a short period only when data is to be admitted.

Using a simpler and more efficient implementation to achieve the same logic function is the basic idea in minimizing the required activity. There are often many ways to implement a logic function and an efficient way should be found for power saving. To minimize the power consumption of an existing CMOS circuit, data representations, signal encoding schemes and algorithms need to be reconsidered in terms of power-efficiency.

#### 2.3 Power breakdown of microprocessors

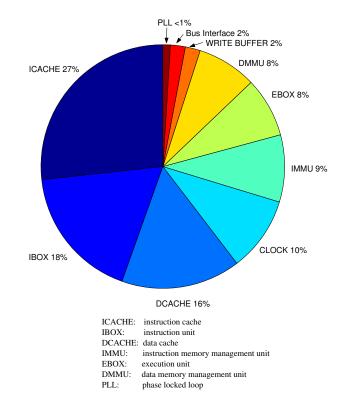

Analyzing the power breakdown of processors indicates directions which potentially lead to power savings. Figure 2.1 shows the power breakdown of an embedded low power RISC microprocessor — a StrongARM microprocessor [5], which is a general-purpose, 32-bit microprocessor with a 16KB instruction cache, a 16KB write-back data cache, a write buffer, and a memory management unit combined in a single chip. It implements the ARM V4 instruction set and is designed for low-power and low-cost applications.

Although Figure 2.1 shows the power breakdown of one particular processor, it displays a general characteristic of processor power breakdown. There is little difference in power breakdown between the StrongARM processor and some other processors, for example, a CISC Pentium-Pro processor [15], a high-performance RISC processor — Alpha 21264 [16] and an asynchronous RISC ARM — the Amulet3 processor [17]. The actual power consumptions of the various processors differs, but their power breakdowns are similar. As can be seen from Figure 2.1, four parts contribute most to the overall processor power dissipation and may have the greatest power-saving potential; these are as follows:

• Timing control:

For a synchronous processor, the power consumption of the timing control is the power dissipated in its global clock. Figure 2.1 shows that the global clock uses as much as 10% of the overall power, but this includes only the

Figure 2.1: The power breakdown of a StrongARM processor [5]

power dissipated in the main clock distribution network and its drivers. If the local clock power for every sub-block is extracted and summed, it is as high as 25% of the total chip power [5]. For some Alpha processors, the timing control power contributes 40% to the overall power consumption [16].

For asynchronous processors, timing control is accomplished by 'local handshakes'. The contribution of handshakes and delay-matching circuits to overall processor power consumption is still very high as discussed in the next chapter.

• Memory access:

Memory stores instructions and data and, ideally, a processor should have a large memory to store a lot of instructions and data. A larger memory implies more power consumption and a longer access latency. Modern processors usually have large memories which use significant power. The StrongARM processor with only 32KB on-chip cache uses 43% of the overall chip power in its caches, most of which is used by the instruction cache. A further 17% of the overall power is indirectly used by memory — the memory management units for data and instructions (DMMU and IMMU).

• Instruction operations:

A major part of the hardware involved in the execution of instructions is the instruction decoder. Modern processors have a wide range of instructions to make them more 'friendly' to programmers and to support these, the instruction decoder becomes a complex circuit implementation to translate instructions to control signals. Many instructions are rarely used, but design complexities are still needed to support them. Instruction operation hardware also includes some other parts, including program counters and address incrementers. The power used by instruction operations of the StrongARM is included in the IBOX sector of Figure 2.1, which contributes 18% to the overall power consumption.

• Register file:

Processors refer to register files in almost every clock cycle, reading operands and writing results, resulting in a high switching activity. Moreover, to support high performance, register files normally have multiple read and write ports, resulting in a larger switching capacitance than a similar-sized single-port SRAM. These two factors make the register file a power-hungry component. The power used by the register file in Figure 2.1 is included in the EBOX sector. According to the power data from the Amulet3, 15% of the chip power is used by its register file [17].

It can also be seen from power analyses of microprocessors that the "real work" — data processing — uses only a very small proportion of the overall processor power. This is a common problem in all "soft-programmable" data processors. In these processors, data processing is guided by a set of 'commands' — instructions, so that every data processing operation is accompanied by at least one instruction. Instructions indicate not only data values but also the addresses of the data values. Therefore, much more power is dissipated in control flow than data processing. A pure RISC processor has a fixed instruction-length and a load-store architecture, which require a larger code size to describe a given task (poor code-density) and more power for instruction fetching and data transfer than many CISC processors.

#### 2.4 Low power processing techniques

As can be seen from the previous analysis, the most effective way to design a low power data processor is to minimize execution overheads, including timing control power, memory (including the register file) power and the number of instructions needed to describe programs.

#### 2.4.1 Minimizing timing control power

Reducing the clock frequency can minimize timing control power but is not the choice of many CMOS designers since this approach slows down the processor. Another way to minimize timing control power is to reduce the switching capacitance attached to clock signals.

Clock switching capacitance can be reduced by using more efficient registers [18] (for example, the registers for PowerPC and StrongARM), or by using both edges of clock signals to control dual-edge-triggered flip-flops (DETFFs) [19]. Reducing clock switching power can also be done by using a half-swing clocking scheme at the cost of a longer flip-flop delay [20].

Minimizing clock capacitance can also be achieved by using clock gating [21], here gating is used to separate a circuit into several blocks, each of which has its own local timing regenerator with a gating signal. The gating signal can gate the local timing regenerator off when the corresponding block has no required activity, so the clock capacitance of the block does not contribute to the overall capacitance when inactive. The global clock controls only the local timing generator drivers and thus has a much smaller capacitance than when used to drive the whole chip. However, clock gating also has some disadvantages which will be discussed in Section 3.2.1. Asynchronous logic is claimed to have the advantage of providing natural fine-grain clock gating. Asynchronous and synchronous clock gating schemes are compared in Section 3.2.1.

#### 2.4.2 Minimizing memory power consumption

A number of low-power memory techniques have been proposed. Among them, the most important may be the 'principle of locality' [3], which directly leads to memory hierarchy design. Locality is a fundamental property of programs and is of two types as follows:

- Temporal locality Recently accessed data and instructions are likely to be accessed again in the near future.

- Spatial locality Instructions fetched by processors are likely to have adjacent addresses and data are also adjacent to each other.

Locality observations influence memory hierarchy architectures. Modern computers employ a large amount of storage memory and the larger the storage memory, the slower it is and the more power is needed to access it. The access latency of a hard disc, the largest capacity memory, is several milliseconds, which is clearly not compatible with the few nanoseconds occupied by a processor in executing an instruction. Clearly, a unified memory architecture does not meet the requirement for high performance and hence a multi-level memory hierarchy must be used to close the processor-memory performance gap.

A register file can be regarded as the lowest level of a memory hierarchy, which stores current operands and some temporary variables. A register file is usually very fast — few hundred picoseconds latency, while its size is normally relatively small — for example 32 words or 1K bits. The next hierarchy level may be a small on-chip memory block called a 'cache' used to store recently used instructions and data; this is also fast — several nanoseconds access latency and small — several dozens of kilobits. Other levels of memory hierarchy may be an off-chip cache, a main memory and a hard disc. The latencies of adjacent levels change by factors of about 10 and the sizes of adjacent levels change by factors of about 1000.

A memory hierarchy not only increases performance but also reduces power consumption. Since accessing a smaller memory needs less power, if most of the data processing operations of a processor are done within a small memory, significant power can be saved.

Since the concept of memory hierarchy was introduced in the 1940s, improving the efficiency of memory hierarchy architecture has attracted a lot of researchers. Bajwa et al. [22] and Lea et al. [23] proposed a hardware addition called a 'loop cache' or 'loop buffer' to minimize the power used by refetching instructions in small loops. The idea of the loop cache scheme was based on two observations as follows:

• For embedded applications, power consumption due to instruction access is typically higher than that due to data access because one data access may be accompanied by 3-4 instruction accesses. Hence, reducing instruction fetching can result in power saving.

• The dynamic execution traces of embedded programs are dominated by small program loops containing a small number of instructions (32 or fewer).

Based on the principle of locality, embedding a small instruction cache to hold the small program loops can greatly reduce overall processor power consumption, since a loop cache can be of a very small size and be situated near the processor. Loop cache schemes have been reported to reduce by 37.9% the main instruction cache accesses and to save the same proportion of instruction power without any delay penalty [23].

Bajwa and Lea's scheme handles only the innermost small program loops which do not contain if-else statements. Wu and Hwang improved Lea's scheme by proposing a loop cache with a stack-based architecture, which supported nested loops containing if-else statements [24]. A further 40% reduction in instruction power was reported compared to Lea's scheme.

To summarise, a loop cache is another level of memory hierarchy, possibly below the on-chip instruction cache. The rationale for loop caches is based on a characteristic of embedded programs — the domination of program loops with a small number of instructions.

#### 2.4.3 Increasing code-density

Processors with a high code-density use fewer or smaller instructions to describe a given program, thus the power used by instruction fetching is reduced. Increasing processor code-density can be achieved in several ways, such as:

- Minimize redundant space and reduce instruction lengths, such as the ARM Thumb-1, Thumb-2 and MIPS16 instruction sets [25];

- Support more addressing modes and instruction set architectures, such as memory-memory and register-memory architectures [26], so separate address calculation instructions in a load-store (register-register) architecture can be saved.

However, increasing code-density means more complex instruction decoders, resulting in more hardware, lower decoding speed and higher decoder power. Therefore, changing an instruction set needs careful consideration of the tradeoffs between these factors.

#### 2.4.4 'Hard-controlled' processing

A carefully designed 'hard-controlled' circuit is usually much more power-efficient than a soft programmable processor. A specifically-tailored ASIC can get rid of execution overheads such as temporary variable transfer, instruction fetching and decoding. It executes only useful data processing operations and thus has the highest power-efficiency. Even in general-purpose processors, the idea of using a direct hardware implementation to replace a set of instructions to perform a logic function is also used, an example is the 'count leading zeros' (CLZ) instruction in the ARM V5 instruction set [1]. The problem with ASICs is that, once they are fabricated, there is little possibility to change functionality.

Reconfigurable processors [27] offer an intermediate approach between ASICs and general-purpose processors, potentially achieving power efficiency by direct hardware mapping, while maintaining a higher flexibility than an applicationspecific circuit. Although reconfigurable processors are claimed to offer greater flexibility than ASICs, it is very difficult to design a reconfigurable hardware architecture having the flexibility and general-purpose processing ability close to that of a soft programmable processor.

#### 2.5 Metrics for power efficiency

Energy- or power- efficiency is always linked to performance, so a brief introduction to performance metrics is necessary. Two circuits (or processors), say A and B, are appointed the same task. If A finishes the task before B, A is regarded as a faster processor. However, since A and B may have different instruction sets and are designed for different applications, it may be difficult to find identical programs that can be executed in both A and B. *MIPS* (million instructions per second) is used as a metric to compare the performance of processors; it is the rate of operations per unit time and is defined as follows:

$$MIPS = \frac{Number \ of \ Instructions \ executed}{Execution \ time} \times 10^{-6}$$

Some metrics can be used to measure the energy-efficiency of processors. One

popular metric is MIPS/watt (MIPS/W) which means how many instructions a processor can execute with the energy supply of 1 joule. Since

$$MIPS/watt = \frac{10^{-6} \cdot instructions/seconds}{joules/seconds} = \frac{10^{-6}}{joules/instructions}$$

a reciprocal metric of *MIPS/watt* is *energy per instruction* which means on average how much energy a processor needs to execute an instruction. Since

$$energy \ per \ instruction = \frac{joules}{instructions} = \frac{joules/seconds}{instructions/seconds} = power \times delay$$

an equivalent metric of energy per instruction is power delay product.

MIPS/W and its equivalent metrics are very important in battery-powered applications and they define with a given battery energy how many tasks processors can execute. However, these metrics define only energy-efficiency. Two processors, A and B, may have the same energy-efficiency but A is faster than B; these metrics cannot differentiate between the two processors. Another metric—  $MIPS^2/watt$  is used to measure the compromise between energy efficiency and performance. Since

$$MIPS^{2}/watt = \frac{instructions^{2}/seconds^{2}}{joules/seconds}$$

$$= \frac{1}{seconds/instructions \cdot joules/instructions} = \frac{1}{energy \times delay}$$

Energy delay product (EDP) is a reciprocal metric of  $MIPS^2/watt$ .

$MIPS^3/watt$  is another important metric to measure energy efficiency.

$$MIPS^{3}/watt = \frac{MIPS}{energy \cdot delay} = \frac{1}{energy \cdot delay^{2}}$$

Since  $energy \propto power \cdot delay \propto C \cdot V_{dd}^2 \cdot (1/delay) \cdot delay \propto V_{dd}^2$  and  $delay \propto 1/V_{dd}$ ,  $MIPS^3/watt$  is independent of the supply voltage  $V_{dd}$ . Thus it can be used to evaluate CMOS processors when voltage-scaling is taken into account and to compare processors using different supply voltages.

The similar metric  $E \times D^n (n \ge 3)$  is also used depending on the importance of the delay increase caused by an energy reduction technique. As an alternative to using these metrics, a fairer way to compare the powerefficiencies of two processors is to define several 'standard programs' (benchmarks), execute these benchmarks in both processors (which may have different instructions, so reprogramming may be needed), and then compare the energy used. Choosing 'typical' and 'fair' benchmarks is another difficulty. The benchmarks should represent the common characteristics of the applications for which the processors are designed.

#### 2.6 Summary

This chapter has presented the sources of power dissipation in CMOS circuits and techniques to reduce dynamic power consumption. Following the power breakdown of a StrongARM and other processors, this chapter pointed out the four functions (or components) that contribute most to overall processor power consumption: timing control, memory access, instruction operations and the register file. The analysis provides the directions leading to the low-power processing techniques to be introduced in the remainder of this thesis — Chapter 4 addresses how to minimize timing control power; Chapter 5 presents low-power memory techniques and Chapters 6-7 discuss low-power instruction and register file techniques. This chapter also reviewed existing low-power processing techniques and addressed the metrics for power-efficiency.

The next chapter will discuss low-power techniques in a specific field — asynchronous logic design.

### Chapter 3

# Power-efficient asynchronous design

This chapter explores asynchronous logic design for its low-power potential. A brief introduction to asynchronous logic design is given in Section 3.1. The power-efficiencies of synchronous and asynchronous designs are compared in Section 3.2. Different low-power asynchronous logic techniques are addressed in Section 3.3. It is impossible to cover the whole field of asynchronous logic design and the chapter will focus on low-power asynchronous design. More detailed information on asynchronous design can be found elsewhere [28] [29].

#### 3.1 Introduction to asynchronous logic design

Synchronous logic has dominated digital circuit design for decades because a global clock assumption makes circuits easier to understand and simpler to design. As an alternative design methodology, there has been a resurgence of interest in asynchronous logic design in both industrial and academic circles since the 1990s. Synchronous circuits use a globally-distributed clock signal to provide timing references and to synchronize data transfers. Asynchronous circuits, on the other hand, utilise no global signal; dataflow and synchronization are controlled using locally-generated 'handshake' signals. The difference in timing control gives asynchronous logic inherent properties which may be exploited to advantage:

• Low power consumption:

Asynchronous logic provides a natural fine-grain clock gating, which dissipates power 'on demand'. When idle, asynchronous circuits can achieve zero standby dynamic power consumption.

• High operating speed:

Theoretically, the run-time latency of an asynchronous circuit is determined by the sum of the total local latencies rather than the global worst-case latency. However, for pipelined designs, the throughput of an asynchronous circuit depends on the slowest pipeline stage(s). In some operation cycles, however, it may achieve a lower latency than its synchronous counterparts.

• Avoidance of clock skew problems:

Asynchronous logic replaces a global distributed clock network with multiple locally generated signals which have shorter wire lengths. This reduces the area and design complexity (as well as power) and avoids the need to provide the required stability and low skew of a global clock distribution network.

• Low emission of electro-magnetic noise:

All components in a synchronous circuit switch simultaneously with the edges of the global clock. This phenomenon concentrates the radiated energy emission of a circuit at the harmonic frequencies of the clock, thus maximising electro-magnetic noise. Asynchronous design works in a different way. Different parts of a circuit are controlled by discrete local timing signals and, as a result, asynchronous circuits produce broadband distributed interference spread across the electromagnetic spectrum at a much lower level.

In the remainder of this section, a brief introduction to asynchronous logic is presented, including: asynchronous timing strategies, asynchronous delay models, data encodings, handshake protocols, and asynchronous pipeline latch controllers.

#### 3.1.1 Asynchronous timing strategy

It takes some time for a gate to generate valid outputs and for a wire to propagate a digital signal. The period of transfer and evaluation is referred to as 'delay' and the phenomenon of unpredictable results due to the existence of delays is called a 'hazard'. A 'glitch' is another phenomenon that should be avoided. Between two stable valid outputs, a combinatorial circuit may produce many spurious transient states. These unexpected transient states are referred to as 'glitches'. To avoid hazards and glitches, there must be some dedicated timing signals to indicate when signals are stable and valid. Synchronous design and asynchronous design differ in the ways they define these timing signals.

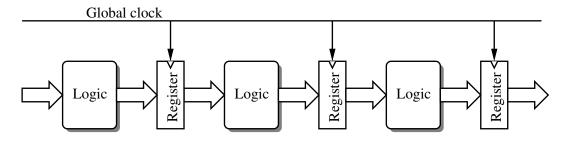

A global clock is used as a timing reference in a synchronous design to define the validity of data items. A synchronous circuit can be viewed as a finite-state machine with registers holding the current states; it changes from one state to another on the edges of the global clock. A typical synchronous pipeline circuit is illustrated in Figure 3.1. The transitions of the global clock signal (the falling or rising edges) indicate the validity of the outputs from the combinatorial logic blocks. The clock period must be no shorter than the delay of the slowest logic block to ensure valid outputs.

Figure 3.1: A synchronous pipeline circuit

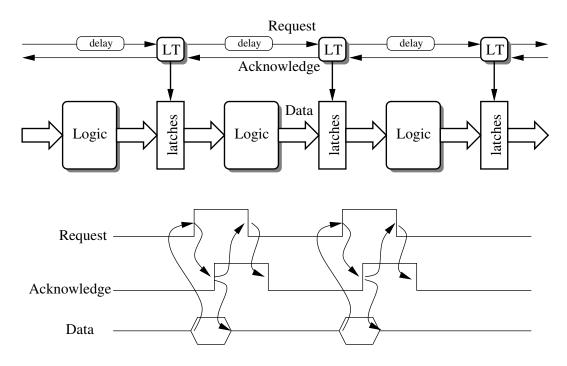

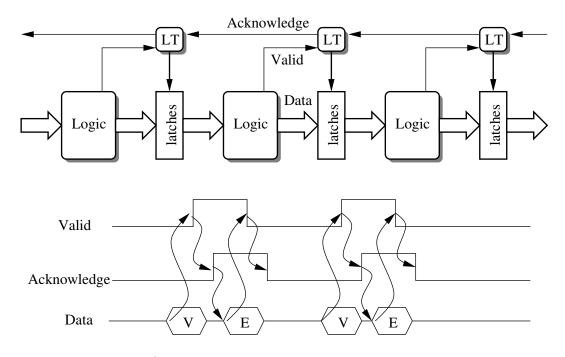

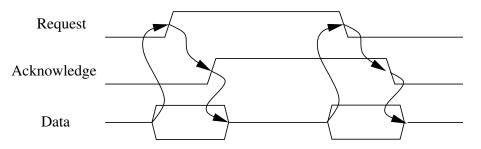

Asynchronous logic, on the other hand, normally uses *Request-Acknowledge* handshake signals to indicate the validity and acceptance of data items. Figure 3.2 illustrates an asynchronous pipeline circuit, in which several pipeline stages are separated by pipeline registers or latches. The latch controllers (LT) control the states of the pipeline registers so that a data item can be propagated through the datapath as soon as possible without overwriting preceding items. The synchronization between two pipeline stages utilises a handshake protocol, one commonly used, the 4-phase bundled-data protocol, is shown in the figure. Other asynchronous handshake protocols are presented in the remainder of this section.

Using a 4-phase handshake protocol, the communication between the 'sender' and the 'receiver' proceeds through a sequence of actions as follows:

• The sender puts a valid data item on a bus and issues a logic high on the

Figure 3.2: An asynchronous pipeline circuit

Request wire;

- The receiver accepts the data item when it is ready to do so, then it issues a logic high on the *Acknowledge* wire;

- The sender removes the data item and pulls the *Request* low;

- The receiver then initializes the next communication by pulling low the *Acknowledge* signal.

#### 3.1.2 Delay models

To obtain valid data in digital circuits, assumptions must be made regarding wire and gate delays. All synchronous circuits use a *bounded-delay model*, where the delays in both the gates and wires are assumed to be within a bounded range. However, it becomes more and more difficult to set a bounded-delay range for a modern VLSI CMOS circuit, where the wire delays are no longer ignorable compared with gate delays. Asynchronous logic offers more flexible delay models than synchronous logic and allows *unbounded* delay assumption on gate or/and wire delays. In an *unbounded-delay model*, the delays can be any finite value. Asynchronous circuits using an unbounded-delay model can be classed as being speed-independent, quasi-delay-insensitive or delay-insensitive depending on the delay assumptions made:

• Delay-insensitive (DI) [30]

A delay-insensitive circuit operates correctly in spite of unknown delays in wires and gates. Although delay-insensitive circuits are the most robust, the constraints on delay-insensitive circuits are very restrictive [31], and the strict timing assumptions make their implementation the most expensive in terms of in hardware and power consumption.

• Quasi-delay-insensitive (QDI) [31]

Quasi-delay-insensitive circuits are delay-insensitive circuits augmented with isochronic forks [31]. Isochronic forks are sets of interconnecting wires that have delays whose differences are negligible compared with gate delays.

• Speed-independent (SI) [32]

A speed-independent circuit is an asynchronous circuit that operates correctly regardless of unknown gate delays, while wire delays are assumed to be negligible compared with gate delays.

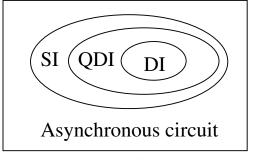

The relation and distinction between DI, QDI and SI circuits are illustrated in Figure 3.3.

Relation

|     | gate delay | wire delay                     |

|-----|------------|--------------------------------|

| DI  | unbounded  | unbounded                      |

| QDI | unbounded  | unbounded +<br>isochronic fork |

| SI  | unbounded  | small                          |

#### Delay assumptions

Figure 3.3: The relations and delay assumptions of asynchronous circuits using unbounded-delay models

#### 3.1.3 Data encodings

In asynchronous design, timing can either be indicated by some dedicated delaymatching blocks (such as an inverter chain) or be extracted from data items that hold extra timing information by using specific data-encoding schemes. Asynchronous logic uses different data-encoding schemes as follows:

• Bundled-data encoding

A bundled-data encoding is also called a single-rail encoding because it uses a single wire per bit, just as in synchronous circuits. The data items of a single-rail circuit cannot indicate any timing information themselves; a delay-matching block is needed to indicate the validity of the outputs from a bundled-data circuit. A typical asynchronous circuit using a bundleddata encoding was introduced in Figure 3.2, where the delay in the control matches the logic delay.

• Code-data encoding

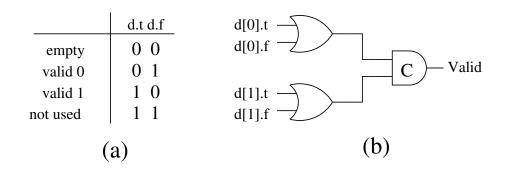

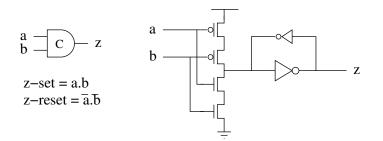

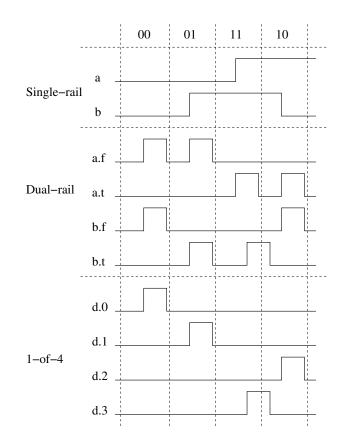

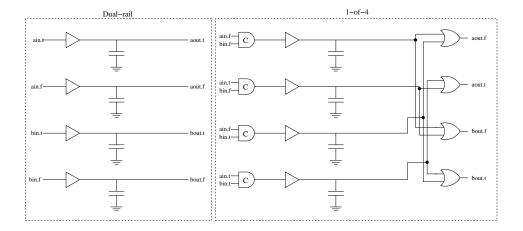

A codeword using a code-data encoding contains both a data value and timing information. An asynchronous circuit using a code-data encoding may need no delay-matching blocks and can be delay-insensitive. Examples of code-data encodings are [30]: Berger encoding and N-of-M encoding. This section describes two kinds of N-of-M encoding: dual-rail encoding and 1-of-4 encoding.