## An Investigation into the Security of Self-timed Circuits

A thesis submitted to the University of Manchester

for the degree of Doctor of Philosophy in the

Faculty of Science & Engineering

2003

ZHONGCHUAN YU

Department of Computer Science

## Contents

| Contents                                             |    |

|------------------------------------------------------|----|

| List of Figures                                      |    |

| List of Tables                                       |    |

| Abstract                                             |    |

| Declaration                                          |    |

| Copyright                                            |    |

| The Author                                           |    |

| Acknowledgements                                     |    |

| Chapter 1: Introduction                              | 15 |

| 1.1 Research goal and contributions                  |    |

| 1.2 Related work                                     |    |

| 1.3 Thesis organization                              |    |

| Chapter 2: Smartcard Security and DPA Attacks        |    |

| 2.1 Introduction                                     |    |

| 2.2 Cryptography background                          |    |

| 2.2.1 Symmetric cryptography                         |    |

| 2.2.2 Asymmetric cryptography                        |    |

| 2.2.3 Block cipher                                   |    |

| 2.2.4 Stream cipher                                  |    |

| 2.2.5 Data Encryption Standard (DES)                 |    |

| 2.3 Attacks on smartcards                            |    |

| 2.3.1 Non-invasive attacks                           | 29 |

| 2.4 Power consumption and attacks                    | 30 |

| 2.4.1 Power consumption in CMOS circuits             | 31 |

| 2.4.2 Simple Power Analysis attack                   | 32 |

| 2.4.3 Differential Power Analysis attack             |    |

| 2.5 Summary of chapter                               | 36 |

| Chapter 3: Asynchronous Design and Hardware Security | 37 |

| 3.1 Introduction                                     |    |

| 3.2 Asynchronous design                              |    |

| 3.2.1 Asynchronous circuit models                    | 39 |

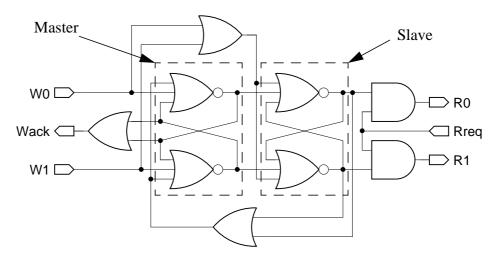

| 3.2.2 Handshake signalling protocol                  | 40 |

| 3.2.3 Data encoding                                  |    |

| 3.2.4 Muller C-elements                              |    |

| 3.3 Asynchronous design for hardware security        |    |

| 3.3.1 Power consumption randomization                |    |

| 3.3.2 Balancing power consumption                    |    |

| 3.3.3 Defeating clock and power supply glitches      | 47 |

| Chapter 4: Asynchronous Power Analysis Methodology   | 49 |

| 4.1 Challenges for asynchronous power analysis       |    |

| 4.1.1 No timing reference                            | 50 |

|        | 4.1.2 No periodicity                                       | 50  |

|--------|------------------------------------------------------------|-----|

|        | 4.1.3 Fadeout of obvious power consumption peaks           | 51  |

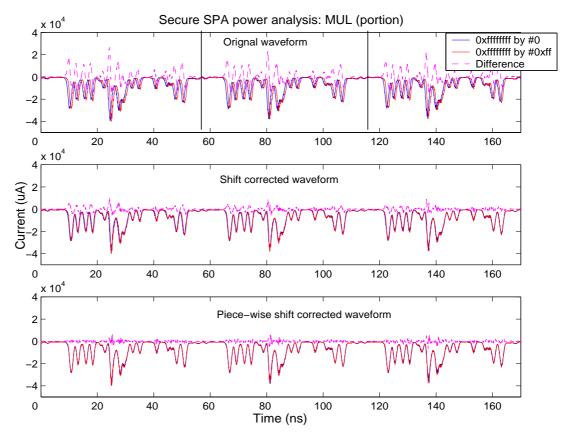

|        | 4.1.4 Overlapped and shifted waveforms                     |     |

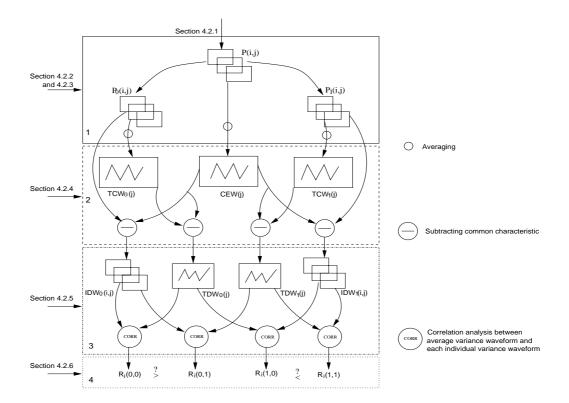

| 4.2    | Asynchronous differential power analysis                   |     |

|        | 4.2.1 Data sampling                                        | 55  |

|        | 4.2.2 Waveform partitioning                                |     |

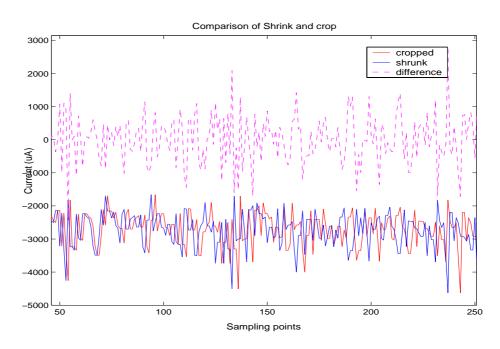

|        | 4.2.3 Waveform correction                                  |     |

|        | 4.2.4 Waveform averaging                                   | 61  |

|        | 4.2.5 Waveform correlation analysis                        | 62  |

|        | 4.2.6 Percentage of Correct Deduction (PCD)                |     |

|        | 4.2.7 Signal-to-noise ratio                                |     |

| 4.3    | Summary of chapter                                         |     |

|        | • •                                                        |     |

|        | er 5: LFSR Design and Implementation                       |     |

|        | Introduction                                               |     |

|        | Feedback shift register                                    |     |

| 5.3    | Theories of LFSR                                           |     |

|        | 5.3.1 LFSR, a state machine                                |     |

|        | 5.3.2 Maximal periodicity of an LFSR                       |     |

|        | 5.3.3 The LFSR in real cryptographic applications          |     |

| 5.4    | Synchronous LFSR design                                    |     |

|        | 5.4.1 Single-rail clocked LFSR                             |     |

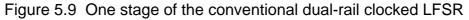

|        | 5.4.2 Conventional dual-rail clocked LFSR                  |     |

|        | 5.4.3 Secure dual-rail clocked LFSR                        |     |

| 5.5    | Asynchronous LFSR design                                   |     |

|        | 5.5.1 Single-rail (bundled-data) asynchronous LFSR         |     |

|        | 5.5.2 Conventional dual-rail asynchronous LFSR             |     |

|        | 5.5.3 Secure dual-rail asynchronous LFSR                   |     |

| 5.6    | Summary of chapter                                         | 86  |

| Chante | er 6: Differential Power Analysis of LFSR                  |     |

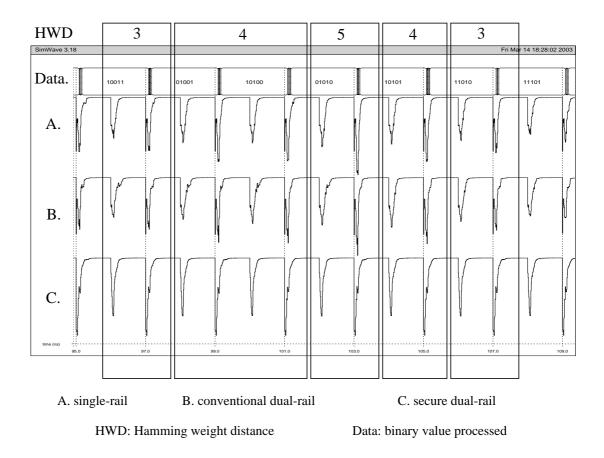

| _      | Clocked LFSR power waveforms                               |     |

| 0.1    | 6.1.1 Single-rail clocked LFSR power waveform              |     |

|        | 6.1.2 Conventional dual-rail clocked LFSR power waveform . |     |

|        | 6.1.3 Secure dual-rail LFSR power waveform                 |     |

| 62     | Asynchronous LFSR power waveforms                          |     |

| 0.2    | 6.2.1 Single-rail asynchronous LFSR waveform               |     |

|        | 6.2.2 Conventional dual-rail asynchronous LFSR waveform    |     |

|        | 6.2.3 Secure dual-rail asynchronous LFSR waveform          |     |

| 63     | Comparison of clocked and self-timed waveforms             |     |

|        | Analysis of LFSR power waveforms                           |     |

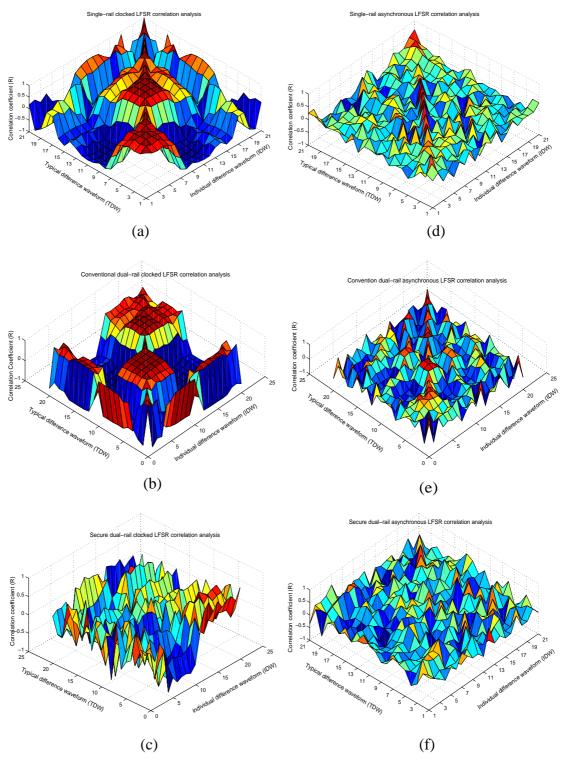

| 0.1    | 6.4.1 Correlation analysis of LFSRs                        |     |

|        | 6.4.2 Differential energy analysis of LFSRs                |     |

|        | 6.4.3 Signal-to-noise analysis of LFSRs                    |     |

| 65     | Analysis results                                           |     |

|        | Summary of chapter                                         |     |

|        |                                                            |     |

|        | er 7: Security Investigation on SPA: at Layout Level       |     |

|        | Introduction                                               |     |

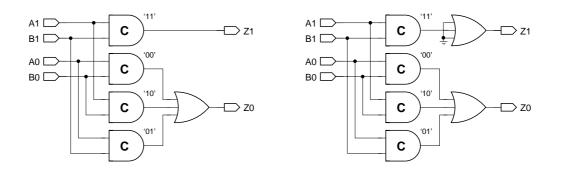

| 7.2    | SPA security features                                      | 109 |

| 7.2.1 Security in data communication109               |

|-------------------------------------------------------|

| 7.2.2 Security in data processing109                  |

| 7.2.3 Security in data storage                        |

| 7.2.4 Security in timing                              |

| 7.2.5 Security in behaviour 112                       |

| 7.3 SPA security analysis                             |

| 7.4 Differential power analysis of SPA114             |

| 7.5 Timing analysis of SPA120                         |

| 7.6 Summary of chapter125                             |

| Chapter 8: Security Investigation on G3card Chip127   |

| 8.1 Introduction                                      |

| 8.2 The investigation environment                     |

| 8.2.1 Measuring power supply current                  |

| 8.3 ARM instruction power analysis                    |

| 8.3.1 Differential power analysis of SPA instructions |

| 8.4 Analysis of DES algorithm on SPA                  |

| 8.4.1 Running DES on SPA                              |

| 8.4.2 DES waveform partitioning                       |

| 8.4.3 DES analysis results                            |

| 8.5 Summary of chapter                                |

|                                                       |

| Chapter 9: Conclusions                                |

| 9.1 Difficulties and methodology                      |

| 9.2 Improved security                                 |

| 9.2.1 Suggestions for improving the security of SPA   |

| 9.3 Further work                                      |

| 9.4 The future                                        |

| 9.4.1 Alternative technologies151                     |

| Reference153                                          |

## List of Figures

| 1.1: | Information leakage in cryptosystems                       | 16 |

|------|------------------------------------------------------------|----|

| 2.1: | The DES encryption algorithm                               | 25 |

| 2.2: | Current variation with the number of switching transistors | 32 |

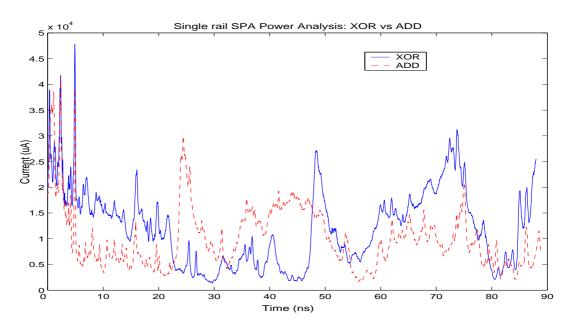

| 2.3: | Power consumption of XOR and ADD instructions              | 33 |

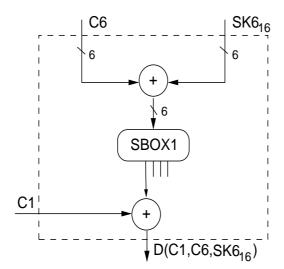

| 2.4: | The diagram of the partitioning function for               |    |

|      | differential power analysis on DES                         | 34 |

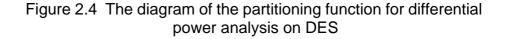

| 3.1  | Synchronous design vs. asynchronous design                 | 38 |

| 3.2  | Handshake protocols (push channel)                         | 40 |

| 3.3: | Dual-rail encoding                                         | 42 |

| 3.4: | C-elements and their state graphs                          | 44 |

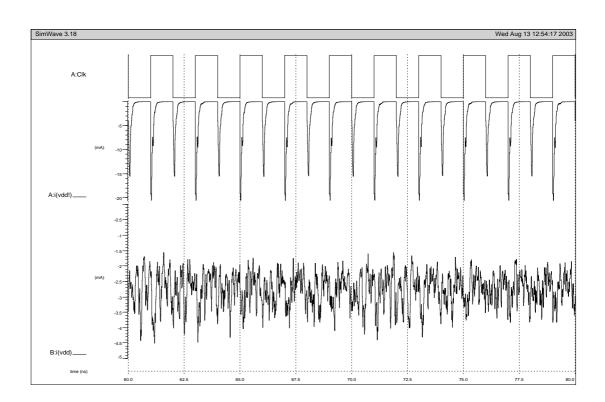

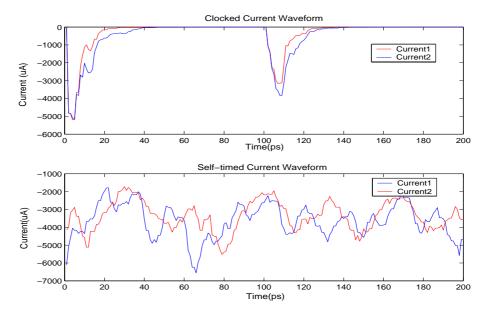

| 4.1: | Typical power waveforms:                                   |    |

|      | synchronous (middle) and asynchronous (bottom)             | 51 |

| 4.2: | The problem of shifted waveforms                           | 53 |

| 4.3: | The new power analysis methodology                         | 54 |

| 4.4: | Shrunk and cropped waveforms                               | 57 |

| 4.5: | An example of waveform shift correction                    | 60 |

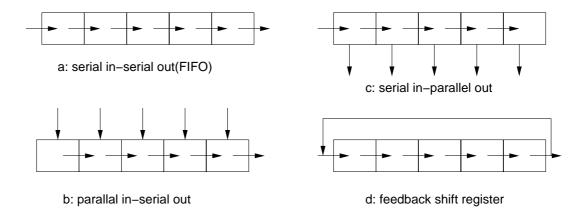

| 5.1: | Shift register data movements                              | 68 |

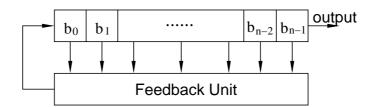

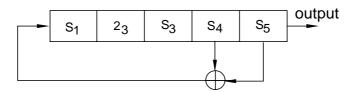

| 5.2: | A feedback shift register                                  | 69 |

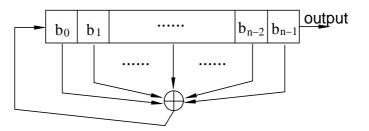

| 5.3: | A linear feedback shift register                           | 70 |

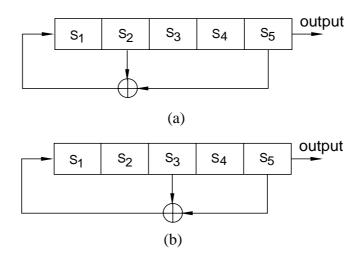

| 5.4: | 5-stage maximal period linear feedback shift register      | 73 |

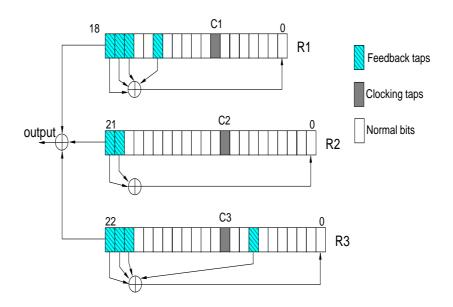

| 5.5: | A5/1 cipher system architecture in GSM                     | 75 |

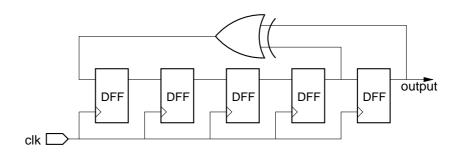

| 5.6: | A linear feedback shift register                           | 77 |

| 5.7: | Single-rail clocked LFSR                                   |    |

|      |                                                            |    |

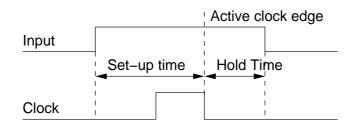

| 5.8:  | Flip-flop set-up and hold times                                       | . 78 |

|-------|-----------------------------------------------------------------------|------|

| 5.9:  | One stage of the conventional dual-rail clocked LFSR                  | . 79 |

| 5.10: | Secure dual-rail clocked latch                                        | . 80 |

| 5.11: | Asynchronous bundled-data LFSR stage structure                        | . 82 |

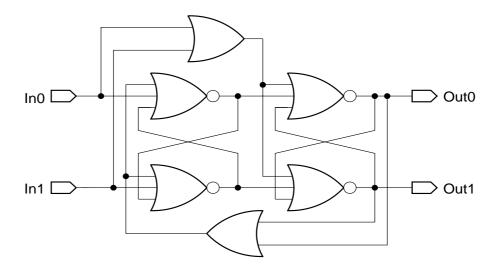

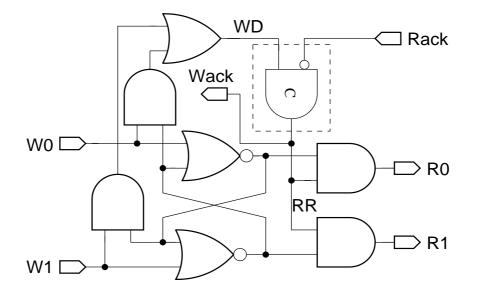

| 5.12: | An asynchronous latch control circuit using a 4-phase Muller pipeline | . 82 |

| 5.13: | STG of an asynchronous latch controller                               | . 83 |

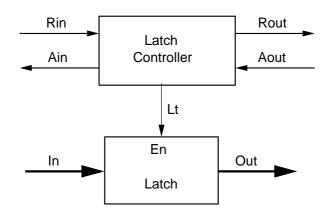

| 5.14: | Latch for conventional dual-rail asynchronous LFSR                    | . 84 |

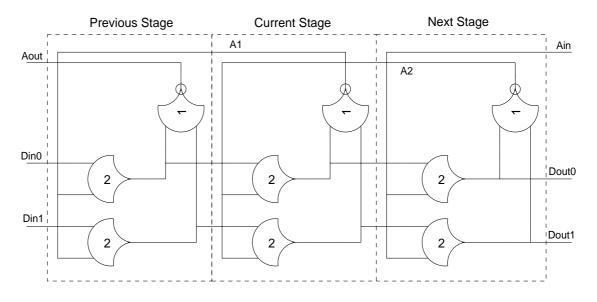

| 5.15: | Three-stage NCL shift register                                        | . 85 |

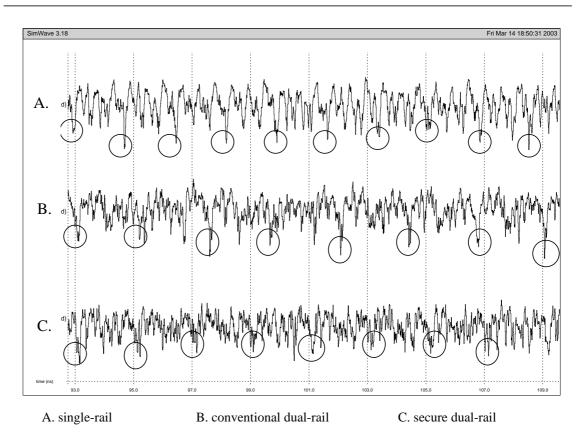

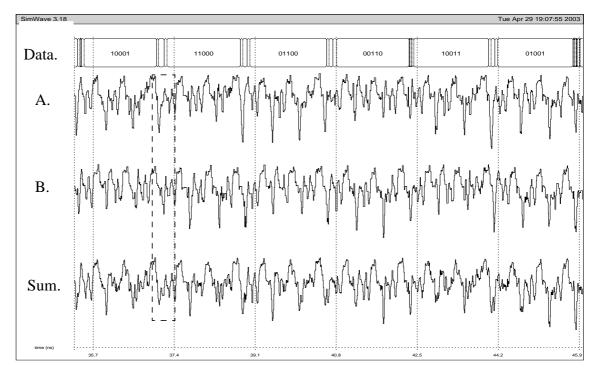

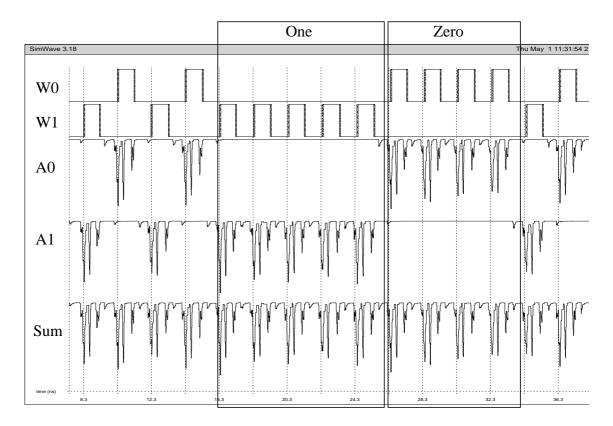

| 6.1:  | Power waveforms of clocked LFSRs                                      | . 89 |

| 6.2:  | Power waveforms of asynchronous LFSRs                                 | . 91 |

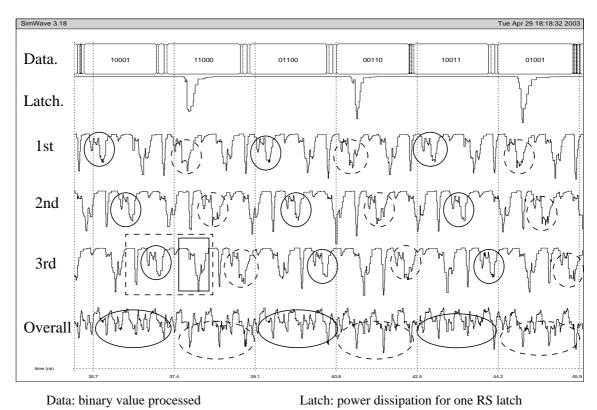

| 6.3:  | Power analysis of the single-rail asynchronous LFSR:                  |      |

|       | One bit power consumption                                             | . 93 |

| 6.4:  | Power analysis of the single-rail asynchronous LFSR:                  |      |

|       | Two bits power consumption                                            | . 94 |

| 6.5:  | Conventional dual-rail asynchronous power analysis:                   |      |

|       | RS latch power consumption                                            | . 95 |

| 6.6:  | Power analysis of the secure dual-rail asynchronous LFSR:             |      |

|       | One stage power waveform                                              | . 96 |

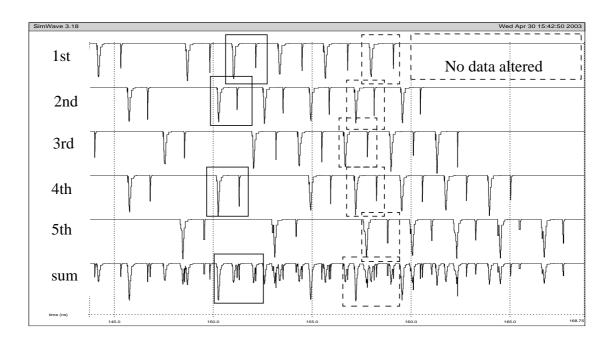

| 6.7:  | Correlation analysis of power waveforms for LFSRs                     | 101  |

| 7.1:  | Dual-rail AND gate implementations                                    | 110  |

| 7.2:  | Secure dual-rail latch                                                | 111  |

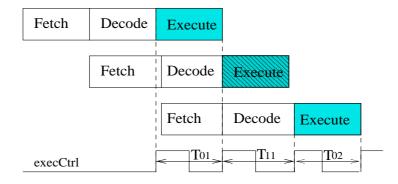

| 7.3:  | The SPA 3-stage pipeline                                              | 114  |

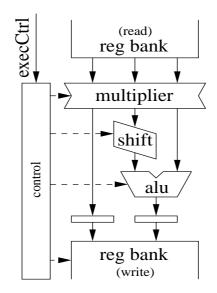

| 7.4:  | The SPA execution stage                                               | 115  |

| 7.5:  | SPA execution time breakdown                                          | 116  |

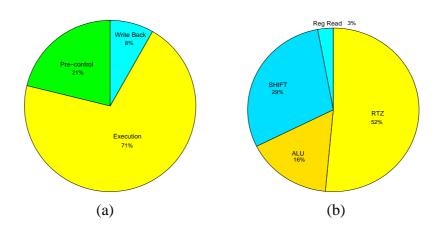

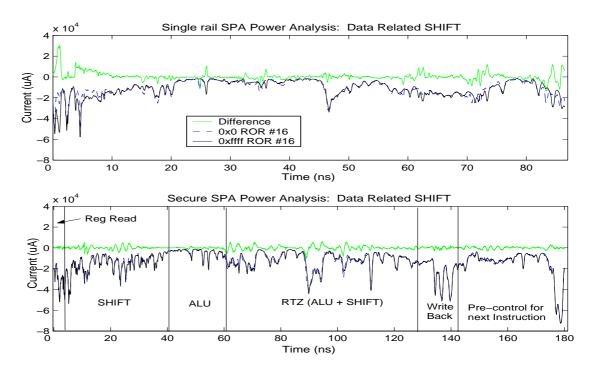

| 7.6:  | Differential power waveform of the data-related SHIFT instruction     | 117  |

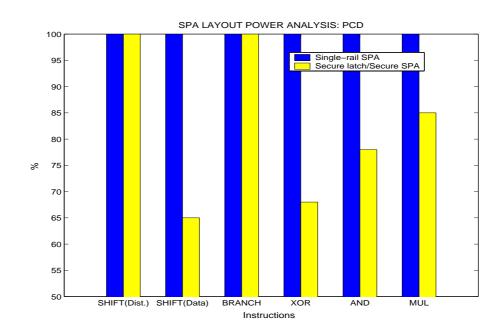

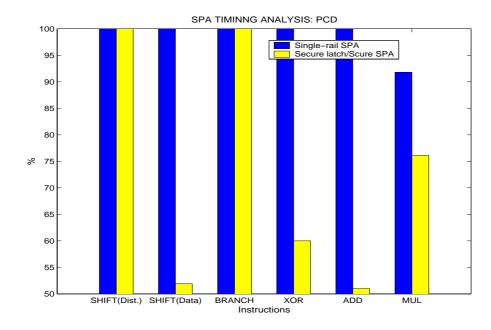

| 7.7:  | SPA power analysis: percentage of correct deduction (PCD)             | 118  |

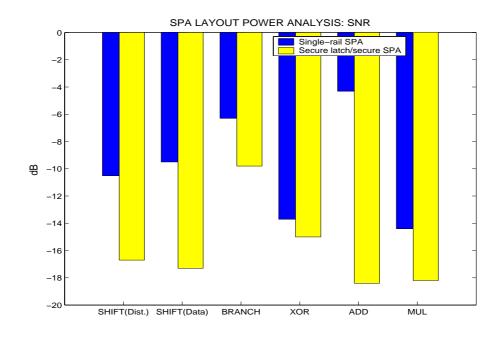

| 7.8:  | SPA power analysis: signal-to-noise ratio                             | 119  |

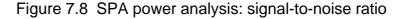

| 7.9:  | SPA ADD instruction timing analysis                                   | 121  |

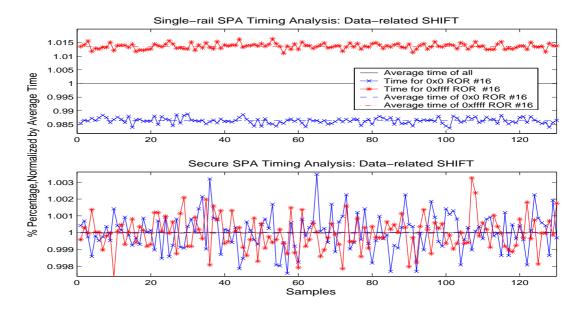

| 7.10: | SPA timing analysis: Data-related SHIFT                               | 124  |

| 7.11: | SPA timing analysis: percentage of correct deduction (PCD)            | 125  |

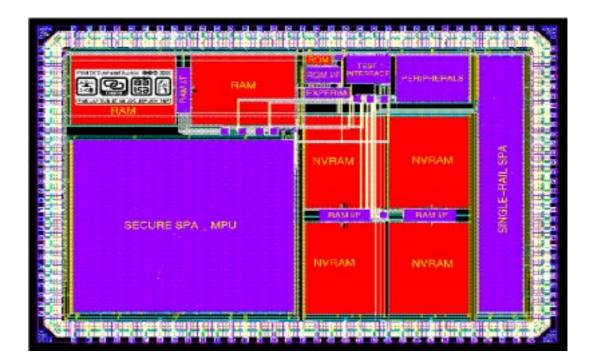

| 8.1:  | The G3Card test chip                                                  | 128  |

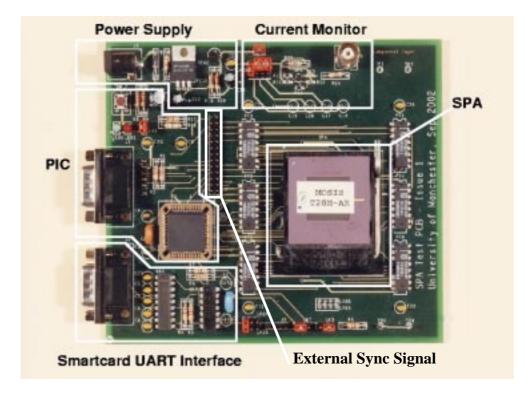

| 8.2:  | The PCB hosting the G3Card test chip                                  | 129  |

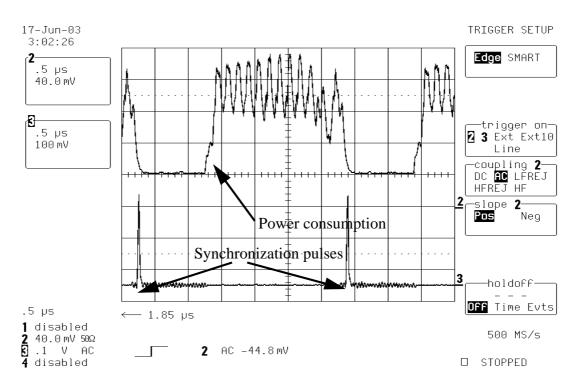

| 8.3:  | G3Card power consumption trace on an oscilloscope                    |

|-------|----------------------------------------------------------------------|

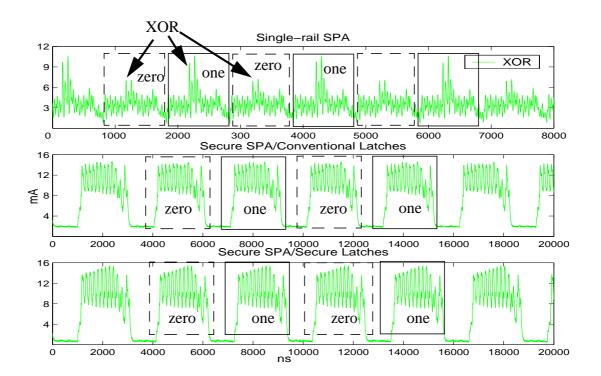

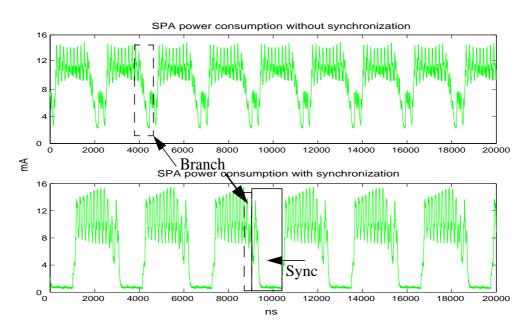

| 8.4:  | Power consumption of the XOR instruction on G3Card chip132           |

| 8.5:  | Power consumption of SPA with and without synchronization signal 133 |

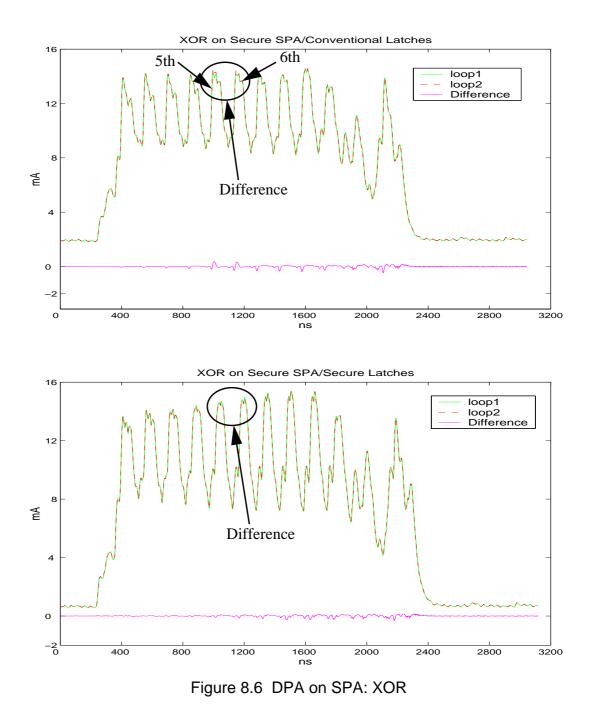

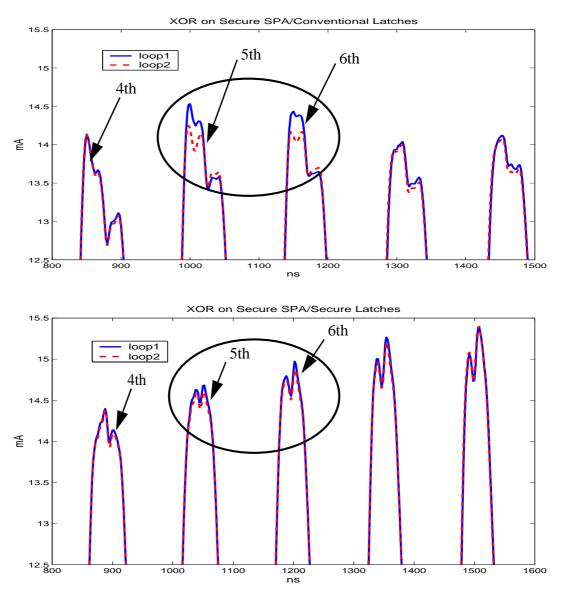

| 8.6:  | DPA on SPA: XOR                                                      |

| 8.7:  | DPA on SPA: close up view of XOR                                     |

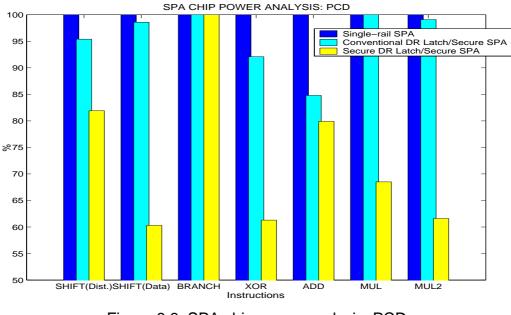

| 8.8:  | SPA chip power analysis: PCD                                         |

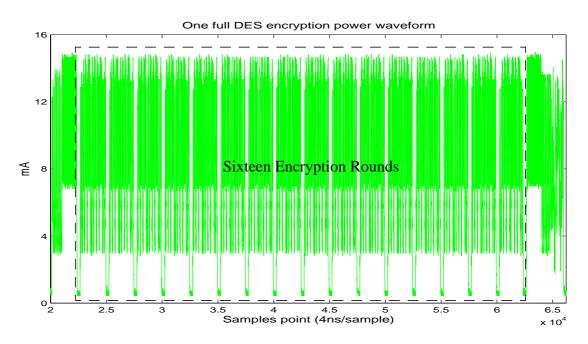

| 8.9:  | Power consumption of SPA: one full DES encryption                    |

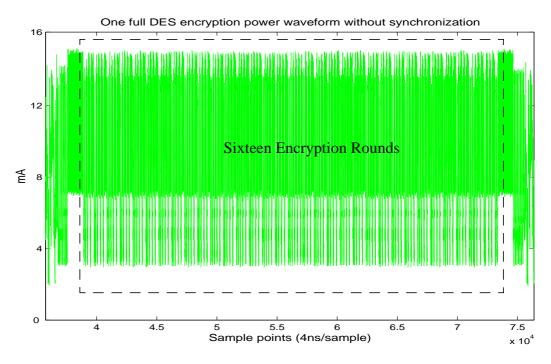

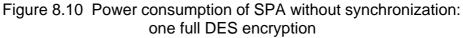

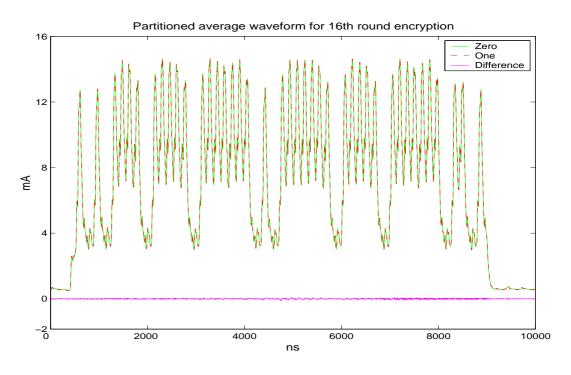

| 8.10  | Power consumption of SPA without synchronization:                    |

|       | one full DES encryption                                              |

| 8.11: | Power consumption of SPA: the 16th round of DES encryption140        |

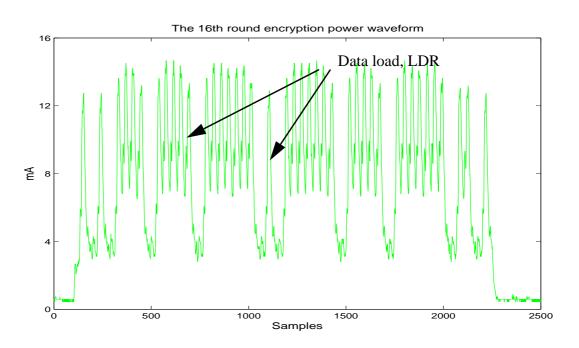

| 8.12: | Waveform shift problem and correction142                             |

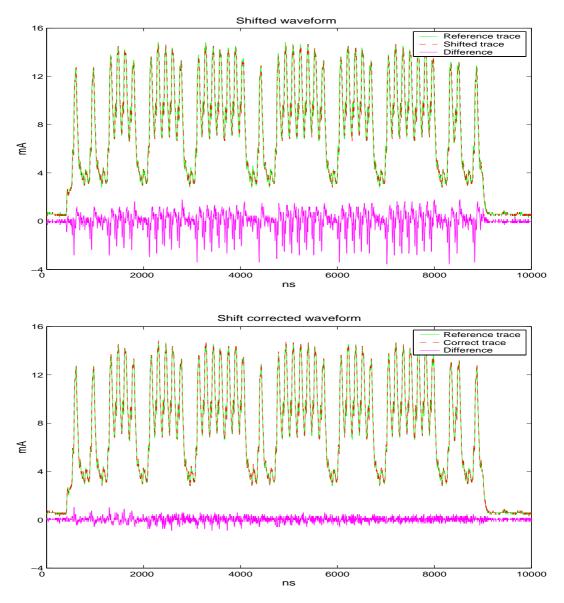

| 8.13: | Partitioned average power waveform for the 16th round encryption 143 |

## List of Tables

| 2.1: | The DES expansion and permutation tables                     |     |

|------|--------------------------------------------------------------|-----|

| 5.1: | Primitive polynomials                                        | 72  |

| 5.2: | Comparison of sequences of two 5-stage LFSRs                 | 74  |

| 6.1: | Percentage of correct deduction of LFSR correlation analysis | 103 |

| 6.2: | PCD of differential energy analysis of LFSR                  | 104 |

| 6.3: | Signal-to-noise ratio of the LFSR power waveforms            | 105 |

| 7.1: | Average instruction execution times                          | 122 |

| 7.2: | Standard deviation of average instruction execution times    | 123 |

#### Abstract

The Differential Power Analysis (DPA) attack poses a great threat to the security of cryptosystems such as smartcards. Asynchronous design has the potential to improve the resistance to such attacks, and to other non-invasive attacks. The self-timed ARM-compatible SPA processor designed at Manchester aims to demonstrate these advantages for secure applications. The security evaluation of self-timed circuits becomes a crucial design task in demonstrating that the security has, indeed, been enhanced by these techniques.

This thesis introduces a methodology suitable for asynchronous power analysis which copes with the lack of a timing reference and other difficulties that do not affect the analysis for synchronous systems. Investigations into the security properties of asynchronous logic using this methodology are then presented.

As the Linear Feedback Shift Register (LFSR) is commonly used in cryptosystems, the LFSR was taken as a small example to demonstrate how self-timed circuits and dual-rail encoding can improve security. Six LFSRs were implemented using different design technologies with the objective to evaluate the impact on security of those technologies. This experiment offers an opportunity to understand the fundamental difference in power consumption characteristics between synchronous circuits and asynchronous circuits.

An investigation is also presented into the security of the SPA processor using both extracted layout simulation and silicon chip measurement. The power consumption of a single-rail and a dual-rail self-timed processor are analyzed and the security impact of using a novel, secure latch is also investigated. Finally, side-channel leakage from a DES encryption algorithm running on the SPA chip is analyzed to expand the investigation.

Together, the research demonstrates how to perform differential power analysis attacks on asynchronous circuits. The results reveal that the security of single-rail self-timed circuits is inadequate and that dual-rail self-timed circuits have high resistance to differential power analysis attacks. In particular, the work shows that secure latches make a vital contribution to the security of self-timed circuits.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institution of learning.

## Copyright

- (1) Copyright in text of this thesis rests with the Author. Copies (by any process) either in full, or of extracts, may be made **only** in accordance with instructions given by the Author and lodged in the John Rylands University Library of Manchester. Details may be obtained from the Librarian. This page must form part of any such copies made. Further copies (by any process) of copies made in accordance with such instructions may not be made without the permission (in writing) of the Author.

- (2) The ownership of any intellectual property rights which may be described in this thesis is vested in the University of Manchester, subject to any prior agreement to the contrary, and may not be made available for use by third parties without permission of the University, which will prescribe the terms and conditions of any such agreement.

Further information on the conditions under which disclosures and exploitation may take place is available from the Head of the Department of Computer Science.

## The Author

Zhongchuan Yu graduated from the Beijing University of Chemical Technology, China, in 1998, majoring in Automation Control. Upon completing this undergraduate study he worked at the R&D centre of SUPCON Ltd., a part of the National Engineering Research Centre for Industrial Automation, China, participating in the design of industrial processing distributed control systems (known as DCS).

Since 2000, he has been conducting his Ph.D. research in the APT group (formerly known as the AMULET group) at the Department of Computer Science at the University of Manchester. His work focuses on the investigation of the potential of asynchronous design to enhance the security of digital systems.

### Acknowledgements

First, I would particularly like to thank my supervisor Professor Steve Furber without whose invaluable insights, guidance and support this work would not have been possible. Thanks also go to my advisor, Dr. Doug Edwards, and to Dr. Luis A. Plana for many insightful comments on many issues.

I would also like to thank Dr. Aris Efthymiou who endured many questions and gave many valuable comments on my thesis. Special thanks to my proof readers: Dr. John Bainbridge, Dr. Steve Temple, Peter Riocreux, Dr. Andrew Bardsley and Professor David Bree for proof reading and commenting on the draft of this thesis. Steve also provided assistance with the design tools.

I am grateful to Dr. Jim Garside for many valuable comments on my work, and to Dr. Viv Woods for his kind arrangement of presentations. I would also like to acknowledge other members in the group who shared their striking thoughts with me.

I gratefully acknowledge the *G3Card* project for offering me the opportunity to analyze the security of the SPA processor. Thanks also go to Dr. Ross Anderson for introducing me to background material on cryptography, especially stream ciphers.

My heartfelt thanks go to my fiancee Yi, for her love, encouragement and support which helped me through difficult times; and to my parents for their timeless support. Last, but not least, I would like to thank other friends here for sharing a good time. To:

My Parents

Yi

## Chapter 1: Introduction

Today, more and more digital applications have become part of our daily life, such as online shopping, e-banking, on-line music and e-business etc. [1]. Many of these applications involve the transfer or use of information of high financial value or sensitivity that must be protected. Smartcards have seen a rapid deployment in some areas, such as banking and cable-television reception, as part of a secured platform using cryptography.

A smartcard chip usually consists of three principal components: a microprocessor capable of running software applications, a memory to store programs and data, and an I/ O interface for communication with a host machine or card-reader. In some applications, smartcards may also contain a secure co-processor for handling the encryption algorithms. By implementing a whole encryption-protected system on a single CMOS die, with suitable tamper-protection circuits built-in, a smartcard provides a low-cost reliable approach to security. This is why they have been so successfully deployed in many applications, such as banking, access control, pre-paid telephone cards and health care. In China, the Chinese central government decided to replace the paper-based identity card with smartcards [2]. Another reason for their success is that multi-applications smartcards will be possible for use in a variety of areas. For instance, a personal identity card could be also used as a health record card and pre-paid transportation card.

The popularity of smartcards is essentially based on their security and convenience. However, one may ask "is the smartcard really secure against malicious attacks?". Is the tamper-resistant hardware really secure and are the embedded cryptographic algorithms really unbreakable? Thus, cryptanalysis and the evaluation of security devices have become as important as the design of security devices themselves. During World War II, German and Japanese cryptosystems were broken by attackers with knowledge of the underlying algorithms. From the 1960s, the use of extra information leaked from the side-channels of cryptosystems became another interesting source cryptanalysts use to mount attacks. In 1960, at the request of the British prime minister, the British intelligence agency, MI5, listened to the French embassy on the negotiations about joining the EEC. Attackers found an extra faint signal on the encrypted signal from the embassy. The leaked signal turned out to be the plain-text of the enciphered message [3].

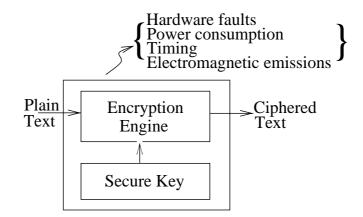

Figure 1.1 shows a cryptosystem which leaks side channel information through hardware faults, power consumption fluctuation, timing information and electromagnetic emissions. Attacks have been successfully mounted on smartcards using such side-channel information to retrieve supposedly secret data: In 1996, Anderson and Kuhn indicated that many smartcards could be broken by inserting *glitches* in their power or clock lines [4, 5]. Kocher showed how secret information could be extracted by precisely measuring the different amount of time taken to process different data on common cryptosystems [6]. In 1998, Kocher again demonstrated that most smartcards on the market were vulnerable to differential power analysis attacks [7,8]. In 2000, a similar attack was demonstrated using electromagnetic leakage from the security device running an encryption algorithm [9, 10]. Unlike mathematical cryptanalysis attacks, these kinds of attacks exploit leaked information from the weakness of the physical implementation of the cryptosystem [11, 12] rather than algorithmic aspects, and are more difficult to

Figure 1.1 Information leakage in cryptosystems

defeat [24]. Among the attack techniques so far described, the differential power analysis (DPA) may be the most effective on smartcards and the most difficult to defeat.

The basic theory behind DPA is that the power consumption is related to the data being processed and, for a programmable machine, the instruction being executed. This data-dependency enables an attacker to obtain secret information by observing small fluctuations in the power consumption waveform and then using statistical analysis to amplify these small differences. The provision of a global clock signal in conventional clocked circuits provides a timing reference and allows statistical analysis to be carried out easily.

It has been suggested that smartcard security can be improved by using self-timed design technology [13, 14] where the absence of a global clock signal makes power analysis more difficult as there is no obvious timing reference, and the power consumption is less predictable because activity is no longer regulated by the clock. Other security advantages derived from not using a clock include immunity to clock and power glitches [14]. Furthermore dual-rail encoding, which is very often used in self-timed circuits, uses two wires to encode binary data. Transitions on one wire indicate a logic one and on the other wire a logic zero. With the return-to-zero signalling protocol described in chapter 3, the transmission of one bit of data always consumes two transitions, one rising and one falling, regardless of the data value, making the processing data-independent. Thus the power consumption could, in principle, be balanced so as to defeat differential power analysis attacks.

#### 1.1 Research goal and contributions

The goal of this research is to investigate how and to what extent asynchronous design technologies improve a CMOS circuit's resistance to differential power analysis attacks, and to investigate the potential of self-timed design in security applications. The main contributions of this work are highlighted as follows:

• The lack of a global clock signal in self-timed circuits creates several difficulties for power analysis making that conventional power analysis methods as used to analyze synchronous waveforms are not readily applicable to asynchronous waveforms. A

suitable methodology for asynchronous power analysis is introduced to overcome these difficulties. The work described in this thesis shows how differential power analysis can be carried out on asynchronous circuits.

- The results show that single-rail self-timed circuits do not provide adequate security; their security is comparable to that of clocked circuits.

- The results confirm that dual-rail encoding is the key technology to defend against differential power analysis attacks and self-timed technologies offer extra security by making analysis much more difficult due to the lack of a timing reference.

- The security investigation also indicates that security in storage has a significant impact on security and are vital for security improvement.

- The research provides basic guidelines for applying asynchronous technologies to design secure applications in the future.

The following papers describing aspects of the work in this thesis have been published:

- SPA A Secure Amulet Core for Smartcard Applications [15]; appeared in the Microprocessors and Microsystems Journal, 27/9; Co-author.

- An investigation into the security of self-timed circuits [16]; appeared in the proceedings of the 9th International Symposium on Advanced Research in Asynchronous Circuits and Systems (ASYNC'03); Author.

- *Defeating power analysis attacks* [17]; appeared in the proceedings of the 9th UK Asynchronous Forum; Author.

- *Power analysis of linear feedback shift registers* [18]; appeared in the proceedings of the 10th UK Asynchronous Forum; Author.

#### 1.2 Related work

This research has a close connection to the *G3Card* project, a joint project involving the University of Manchester, the University of Cambridge and other industrial and academic

partners. Significant effort was focused on the security investigation of the SPA, a selftimed ARM-compatible processor designed within the *G3Card* project group in Manchester [19]. The XPS test chip designed by the Cambridge group consists of five 16bit processors designed with different technologies [14]. Both groups aim to improve smartcard security using self-timed design technologies.

#### 1.3 Thesis organization

This thesis is divided into nine chapters. The remainder of the thesis is organized as follows:

Chapter 2 provides background information on smartcards and cryptography, and smartcard security and attacks are discussed. The conventional differential power analysis attack and the theory of CMOS VLSI power consumption are also reviewed.

Chapter 3 introduces asynchronous VLSI design techniques. The fundamental differences between asynchronous and synchronous design and the impact of the absence of a global clock signal are addressed.

Chapter 4 discusses the difficulties of performing asynchronous power analysis and presents a suitable methodology. It handles those difficulties and applies correlation analysis to characterize asynchronous power waveforms.

Chapter 5 describes the design of six linear feedback shift registers implemented with different technologies to allow an evaluation of the security impacts of those technologies.

Chapter 6 analyses the power consumption of the LFSRs described in chapter 5 using the methodology discussed in chapter 4 and evaluates the impact of the different technologies.

Chapter 7 investigates the security of the SPA processor core. Several instructions are studied using extracted layout simulation to determine the security improvement of dual-rail encoding and secure latches.

Chapter 8 extends the investigation undertaken in chapter 7 by analyzing measurements taken from the silicon chip. A popular encryption algorithm, DES, is run on the SPA processor and the power consumption of DES is examined.

Finally, chapter 9 draws conclusions from the research presented in this thesis and makes suggestions for further work.

# Chapter 2: Smartcard Security and DPA Attacks

#### 2.1 Introduction

Smartcards have evolved since their introduction in the 1970s from simple memory cards to microprocessor-based devices with advanced cryptographic co-processors embedded on the card. Unlike magnetic strip cards, where only a few hundred bytes of information can be kept on the card, smartcards have sufficient memory to allow sophisticated encryption algorithms to be used on the card. The design of a microprocessor for use in smartcards, however, has to meet special limitations set in the industrial standard, ISO/ IEC 7816 [20, 21]. The silicon area of the smartcard chip must not exceed 25 mm<sup>2</sup> (5 mm in length and 5 mm in width). At present, most smartcards use an 8-bit microprocessors, which is significantly less advanced than current general-purpose microprocessors. This is largely because of the physical die area limitation of a smartcard chip. However, the industry is starting to plan for the use of 32-bit RISC microprocessors in smartcards [22].

The principal reason for using smartcards is to increase security. However, many successful attacks have been made on smartcards, some of which have seriously damaged confidence in their security. A security system fails because of many reasons [23]. The availability of side-channel information leakage allows a wide range of attacks on smartcards [24 - 26]. Differential power analysis, one of the most successful attack methodologies on smartcards using leaked information, has become a real threat to security.

This chapter will first review basic techniques and the theory of cryptography and then review some common attacks on smartcards with an emphasis on differential power analysis (DPA).

#### 2.2 Cryptography background

With today's increasing interest in electronic life, cryptography has been widely used in many applications, including smartcards. This section will briefly review some necessary aspects of cryptography. Further information about cryptography and security can be found in the literature [27-29].

#### 2.2.1 Symmetric cryptography

A cryptosystem implemented with symmetric cryptography has one key used by both communicating parties, commonly referred to as Alice and Bob, to encrypt and decrypt data. For example, Alice encrypts message M with key K to yield a ciphered text C=E(M, K). When Bob receives the ciphered text C, he uses the same key to decrypt the text to recover the original message, M=D(C,K). One of the most famous and widely used symmetric cryptographic algorithms is the Data Encryption Standard (DES) algorithm [30]. The Advanced Encryption Standard (AES) [31] and other AES candidates [32-35] are also symmetric cryptographs.

One major problem with symmetric cryptography is the key distribution. As the same key is used for both encryption and decryption, it must be assured that the key has not been leaked to or stolen by any parties other than those authorized to know it. Thus, Alice has to give the key to Bob via a secure channel, avoiding leaking the key information, otherwise, the communication between Alice and Bob will not be secure. Therefore both Alice and Bob share the responsibility to keep the secret key safe and, furthermore, if Alice has ten friends to communicate with she perhaps needs to manage ten different keys. What if she has 100 people to communicate with? The problem can clearly grow to an unmanageable size. Thus key management is also an important issue in symmetric cryptography.

#### 2.2.2 Asymmetric cryptography

Asymmetric cryptography, on the other hand, uses different keys for encryption and decryption. Bob generates a *private key*, which he keeps to himself in a secure place, and a *public key*, which he gives to anyone who wants to have secure communications with him. For instance, when Alice needs to send a ciphered message to Bob, she encrypts the

message M with Bob's public key  $K_e$  to produce the ciphered text  $C=E(M, K_e)$  and sends it to Bob. When Bob gets the ciphered message he uses his private key,  $K_d$ , to recover the original message  $M=D(C, K_d)$ . Although  $K_e$  and  $K_d$  are related, it is impossible to derive  $K_d$  from  $K_e$ .

The first and most famous public-key cryptography algorithm was the Diffie-Hellman key exchange protocol created by Diffie and Hellman in 1977, which was a milestone in the history of cryptography [36]. One of the main advantages of public-key cryptography is the ease of key management. Bob publishes his public key, on a web-site for example, so that anyone who wants to send secure messages to him can use this public key and Bob only needs to manage his one private key, no matter how many friends he needs to communicate with securely. Moreover, he does not necessarily need to keep his friends' public keys in a secure place which is much easier to maintain. Compared with symmetric cryptography, it makes life much easier for Bob to manage only the one private key as well as for Alice who is not particularly required to keep Bob's public key in secure place.

There are many applications for asymmetric cryptography, such as authorization and digital signatures, as well as its use in the distribution of keys for symmetric cryptography. For example, if Alice wants to send a symmetric cryptography key K to Bob, she first encrypts key K with Bob's public key  $K_e$  and sends it to Bob. Because the ciphered text containing the key K can only be decrypted by Bob with his private key,  $K_d$ , Alice can send the ciphered K through an open communication channel without worrying about leaking key information.

However, the security of both symmetric and asymmetric cryptography depends largely on the security of the secret key. In the former case, Alice and Bob have to make the key safe and, for the latter case, Bob has to keep his private key secure. Given the fact that modern cryptographic algorithms often use a large key (1024 bits for instance), it is almost impossible or impractical to memorize keys. Therefore, key management becomes an important issue in cryptography. Smartcards bring a solution because the secret keys can be stored and maintained on the same smartcards that perform the encryption algorithms. Currently, both symmetric and asymmetric algorithms can be embedded on smartcards.

#### 2.2.3 Block cipher

If an encryption algorithm takes a fixed length of plain-text input and produces the same length of ciphered-text output, the algorithm is called a *block cipher* that is the most common and important method used in modern cryptography. The main actions in a block cipher are *permutation* and *substitution*. Permutation changes the position of each bit while substitution replaces one data pattern with another using a hardware or software mechanism (often known as an SBOX). Most cryptographic algorithms are block ciphers, such as DES, AES and other candidates for AES [30 - 35].

#### 2.2.4 Stream cipher

Stream cipher is another kind of encryption algorithm which encrypts one bit (or byte or word) in each step. Usually, the central part of the stream cipher system is a random number generator. The security of a stream cipher depends largely on the random number generator. If the generator generates only a repeated number stream (for instance repeating every 16 bits), then this stream cipher is not going to be secure. Ideally, the random number generator should produce random numbers that never repeat. Practically, a generator should be able to produce a pseudo-random number stream which is long enough to be computably secure. In many stream cipher systems, the design of the pseudo-random number generator centres on linear feedback shift registers (LFSR) which will be looked at in more detail in chapter 5.

Compared to the block cipher, a stream cipher can be implemented with a smaller number of logic gates while still being able to offer good security. In the early VLSI era, the stream cipher was widely used in cryptosystems because of the prohibitive cost of the large VLSI circuits required for block ciphers.

#### 2.2.5 Data Encryption Standard (DES)

The DES encryption algorithm [30] was originally developed by IBM in the 1970s and has been widely used in many secure applications. The following section describes the encryption process.

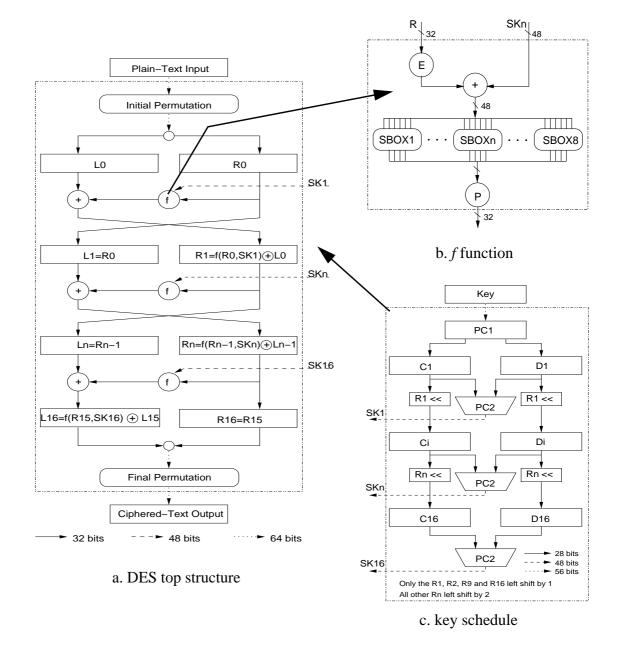

The DES algorithm, as shown in Figure 2.1, is a block cipher and was designed to encrypt and decrypt blocks of 64-bit data under the control of a 64-bit secure key. The algorithm contains three processes: an initial permutation (IP), 16 rounds of key-dependent computation, and a final permutation (FP) which is a reverse of IP. The two permutations are defined by their permutation tables, and the key-dependent 16-rounds of computation can be summarised as equation (1):

$$L_{n} = R_{n-1}, R_{n} = L_{n-1} \oplus f(R_{n-1}, SK_{n})$$

(1)

Figure 2.1 The DES encryption algorithm

where n is from 1 to 16, the function f is the main body of the DES algorithm as shown in Figure 2.1b, and the 48-bit subkey, *SKn*, is computed by the key schedule scheme shown in Figure 2.1c.

The key schedule function, shown in Figure 2.1c, is used to generate 48-bit subkeys for the 16 encryption rounds from the 56-bit key (64 bits minus 8 bits which are only used for parity check). The 56-bit key is first permuted according to the permutation choice #1, PC1, and the 56-bit output of PC1 is then divided into two sets for the 28-bit C and D shift registers respectively. The left most 28 bits are assigned to C register while the right most 28 bits are assigned to D register. These two shift registers shift their data values accordingly and the shifted value is reunited and then permuted according to the permutation choice #2, PC2, to generate one 48-bit subkey. This operation continues until all sixteen subkeys are generated. Table 2.1d. shows the PC1 and PC2 permutation tables.

The function f, shown in Figure 2.1b, contains eight SBOXes (Substitution BOXes). First, using an expansion table E shown in Table 2.1c., the 32-bit input from the register R is expanded to a 48-bit intermediate output which is XORed with the 48-bit subkey from the key schedule unit. The result of the XOR is divided into 8 groups of 6 bits to form the inputs to the 8 distinct SBOXes from which 8 groups of 4 bits of output are produced according to their respective substitution tables. Each substitution table has 4 rows and 16 columns. The eight 4-bit output of the SBOXes form a 32-bit output which is then permuted according to the P permutation table in Table 2.1c. to yield the 32-bit output of the f function.

To describe how the SBOX works, we take SBOX1 as an example. The first and the last bit of the 6-bit input (bit #1 and bit #6) represent the row number, denoted as i, in the range of 0 to 3, and the middle 4 bits (bit #2 to bit #5) represent the column number, denoted as j, in the range of 0 to 15. For each 6-bit input, a number in the range of 0 to 15, that is, a 4-bit binary data value can be found in the i<sup>th</sup> row and the j<sup>th</sup> column in the table. For instance, if the 6-bit input is 101100, then the row number is 10 (the 2nd row) and the column number is 0110 (the 6th column), therefore the output is 2, as highlighted in Table 2.1a, giving a 4-bit output of 0010. The other SBOXes have the same operation but with different tables.

The DES decryption process is the reverse of the encryption using the same key. The last round in encryption is the first round in decryption and the last round subkey in encryption is the first round subkey in decryption

| S1 | 14 | 4  | 13 | 1  | 2  | 15 | 11 | 8  | 3  | 10 | 6  | 12 | 5  | 9  | 0  | 7  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    | 0  | 15 | 7  | 4  | 14 | 2  | 13 | 1  | 10 | 6  | 12 | 11 | 9  | 5  | 3  | 8  |

|    | 4  | 1  | 14 | 8  | 13 | 6  | 2  | 11 | 15 | 12 | 9  | 7  | 3  | 10 | 5  | 0  |

|    | 15 | 12 | 8  | 2  | 4  | 9  | 1  | 7  | 5  | 11 | 3  | 14 | 10 | 0  | 6  | 13 |

| S2 | 15 | 1  | 8  | 14 | 6  | 11 | 3  | 4  | 9  | 7  | 2  | 13 | 12 | 0  | 5  | 10 |

|    | 3  | 13 | 4  | 7  | 15 | 2  | 8  | 14 | 12 | 0  | 1  | 10 | 6  | 9  | 11 | 5  |

|    | 0  | 14 | 7  | 11 | 10 | 4  | 13 | 1  | 5  | 8  | 12 | 6  | 9  | 3  | 2  | 15 |

|    | 13 | 8  | 10 | 1  | 3  | 15 | 4  | 2  | 11 | 6  | 7  | 12 | 0  | 5  | 14 | 9  |

| S3 | 10 | 0  | 9  | 14 | 6  | 3  | 15 | 5  | 1  | 13 | 12 | 7  | 11 | 4  | 2  | 8  |

|    | 13 | 7  | 0  | 9  | 3  | 4  | 6  | 10 | 2  | 8  | 5  | 14 | 12 | 11 | 15 | 1  |

|    | 13 | 6  | 4  | 9  | 8  | 15 | 3  | 0  | 11 | 1  | 2  | 12 | 5  | 10 | 14 | 7  |

|    | 1  | 10 | 13 | 0  | 6  | 9  | 8  | 7  | 4  | 15 | 14 | 3  | 11 | 5  | 2  | 12 |

| S4 | 7  | 13 | 14 | 3  | 0  | 6  | 9  | 10 | 1  | 2  | 8  | 5  | 11 | 12 | 4  | 15 |

|    | 13 | 8  | 11 | 5  | 6  | 15 | 0  | 3  | 4  | 7  | 2  | 12 | 1  | 10 | 14 | 9  |

|    | 10 | 6  | 9  | 0  | 12 | 11 | 7  | 13 | 15 | 1  | 3  | 14 | 5  | 2  | 8  | 4  |

|    | 3  | 15 | 0  | 6  | 10 | 1  | 13 | 8  | 9  | 4  | 5  | 11 | 12 | 7  | 2  | 14 |

| S5 | 2  | 12 | 4  | 1  | 7  | 10 | 11 | 6  | 8  | 4  | 3  | 15 | 13 | 0  | 14 | 9  |

|    | 14 | 11 | 2  | 12 | 4  | 7  | 13 | 1  | 5  | 0  | 15 | 10 | 3  | 9  | 8  | 6  |

|    | 4  | 2  | 1  | 11 | 10 | 13 | 7  | 8  | 15 | 9  | 12 | 5  | 6  | 3  | 0  | 14 |

|    | 11 | 8  | 12 | 7  | 1  | 14 | 2  | 13 | 6  | 15 | 0  | 9  | 10 | 4  | 5  | 3  |

| S6 | 12 | 1  | 10 | 15 | 9  | 2  | 6  | 8  | 0  | 13 | 3  | 4  | 14 | 7  | 5  | 11 |

|    | 10 | 15 | 4  | 2  | 7  | 12 | 9  | 5  | 6  | 1  | 13 | 14 | 0  | 11 | 3  | 8  |

|    | 9  | 14 | 15 | 5  | 2  | 8  | 12 | 3  | 7  | 0  | 4  | 10 | 1  | 13 | 11 | 6  |

|    | 4  | 3  | 2  | 12 | 9  | 5  | 15 | 10 | 11 | 14 | 1  | 7  | 6  | 0  | 8  | 13 |

| S7 | 4  | 11 | 2  | 14 | 15 | 0  | 8  | 13 | 1  | 12 | 9  | 7  | 5  | 10 | 6  | 1  |

|    | 13 | 0  | 11 | 7  | 4  | 9  | 1  | 10 | 14 | 3  | 5  | 12 | 2  | 15 | 8  | 6  |

|    | 1  | 4  | 11 | 13 | 12 | 3  | 7  | 14 | 10 | 15 | 6  | 8  | 0  | 5  | 9  | 2  |

|    | 6  | 11 | 13 | 8  | 1  | 4  | 10 | 7  | 9  | 5  | 0  | 15 | 14 | 2  | 3  | 12 |

| S8 | 13 | 2  | 8  | 4  | 6  | 15 | 11 | 1  | 10 | 9  | 3  | 14 | 5  | 0  | 12 | 7  |

|    | 1  | 15 | 13 | 8  | 10 | 3  | 7  | 4  | 12 | 5  | 6  | 11 | 0  | 14 | 9  | 2  |

|    | 7  | 11 | 4  | 1  | 9  | 12 | 14 | 2  | 0  | 6  | 10 | 13 | 15 | 3  | 5  | 8  |

|    | 12 | 1  | 14 | 7  | 4  | 10 | 8  | 13 | 15 | 12 | 9  | 0  | 3  | 5  | 6  | 11 |

a.

|    |    |    | I  | Ρ  |    |    |   |    |   | F  | Р  |    |    |    |    |

|----|----|----|----|----|----|----|---|----|---|----|----|----|----|----|----|

| 58 | 50 | 42 | 34 | 26 | 18 | 10 | 2 | 40 | 8 | 48 | 16 | 56 | 24 | 64 | 32 |

| 60 | 52 | 44 | 36 | 28 | 20 | 12 | 4 | 39 | 7 | 47 | 15 | 55 | 23 | 63 | 31 |

| 62 | 54 | 46 | 38 | 30 | 22 | 14 | 6 | 38 | 6 | 46 | 14 | 54 | 22 | 62 | 30 |

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 | 37 | 5 | 45 | 13 | 53 | 21 | 61 | 29 |

| 57 | 49 | 41 | 33 | 25 | 17 | 9  | 1 | 36 | 4 | 44 | 12 | 52 | 20 | 60 | 28 |

| 59 | 51 | 43 | 35 | 27 | 19 | 11 | 3 | 35 | 3 | 43 | 11 | 51 | 29 | 59 | 27 |

| 61 | 53 | 45 | 37 | 29 | 21 | 13 | 5 | 34 | 2 | 42 | 10 | 50 | 28 | 58 | 26 |

| 63 | 55 | 47 | 39 | 31 | 23 | 15 | 7 | 33 | 1 | 41 | 9  | 49 | 27 | 57 | 25 |

| E P |    |    |    |    |    |    |    |    | PC1 |    |    |    |    |    |    |    | PC2 |    |    |    |    |    |

|-----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|-----|----|----|----|----|----|

| 32  | 1  | 2  | 3  | 4  | 5  | 16 | 7  | 20 | 21  | 57 | 49 | 41 | 33 | 25 | 17 | 9  | 14  | 17 | 11 | 24 | 1  | 5  |

| 4   | 5  | 6  | 7  | 8  | 9  | 29 | 12 | 28 | 17  | 1  | 58 | 50 | 42 | 34 | 26 | 18 | 3   | 28 | 15 | 6  | 21 | 10 |

| 8   | 9  | 10 | 11 | 12 | 13 | 1  | 15 | 23 | 26  | 10 | 2  | 59 | 51 | 43 | 35 | 27 | 23  | 19 | 12 | 4  | 26 | 8  |

| 12  | 13 | 14 | 15 | 16 | 17 | 5  | 18 | 31 | 10  | 19 | 11 | 3  | 60 | 52 | 44 | 36 | 16  | 7  | 27 | 20 | 13 | 2  |

| 16  | 17 | 18 | 19 | 20 | 21 | 2  | 8  | 24 | 14  | 63 | 55 | 47 | 39 | 31 | 23 | 15 | 41  | 52 | 31 | 37 | 47 | 55 |

| 20  | 21 | 22 | 23 | 24 | 25 | 32 | 27 | 3  | 9   | 7  | 62 | 54 | 46 | 38 | 30 | 22 | 30  | 40 | 51 | 45 | 33 | 48 |

| 24  | 25 | 26 | 27 | 28 | 29 | 19 | 13 | 30 | 6   | 14 | 6  | 61 | 53 | 45 | 37 | 29 | 44  | 49 | 39 | 56 | 34 | 53 |

| 28  | 29 | 30 | 31 | 32 | 1  | 22 | 11 | 4  | 25  | 21 | 13 | 5  | 28 | 20 | 12 | 4  | 46  | 42 | 50 | 36 | 29 | 32 |

|     |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |     |    |    |    |    |    |

|     |    |    |    | с. |    |    |    |    |     |    |    |    |    |    |    | d. |     |    |    |    |    |    |

Table 2.1: The DES expansion and permutation tables

#### 2.3 Attacks on smartcards

The smartcard is believed to be an effective solution for many secure applications. However, many attacks have been successfully carried out on smartcards. Attacks on smartcards can be classified into invasive attacks and non-invasive attacks. In some hostile environments such as distributed and point-of-sale systems, attackers have access to the smartcard over an extended period of time. This can make smartcards very vulnerable, and those without physical access protection can be exposed to invasive attacks. Kommerling and Kuhn have discussed many invasive approaches to attack smartcard chips, such as de-packing smartcard chips, memory reverse engineering, memory modification and rewriting and microprobing [5]. Anderson and Kuhn also showed a number of invasive attacks that can be carried out by opponents with much shallower pockets [37]. A good cryptosystem is usually equipped with mechanisms, such as electromagnetic shielding, low-pass filters and autonomous clock signal generators, to protect it from those invasive attacks.

However, smartcards with physical access protection may still be vulnerable to noninvasive attacks. Manufacturers always overestimate the quality of their products' security features. Many cryptosystem algorithms can be broken by non-invasive attacks such as timing attacks, electromagnetic emission attacks, hardware fault attacks [28] and, more recently, power analysis attacks [8]. Among these attacks, power analysis attacks are probably the most powerful techniques for breaking into today's cryptographic implementations on smartcards. Many RSA and DES algorithm implementations on smartcards are vulnerable to power analysis attacks. Differential power consumption is the key source of information for attacks on RSA and DES as side-channel information may be leaked when RSA is executing modular multiplication or during the 16 rounds of encryption in DES. The attack measures variations in power consumption and uses techniques such as statistical analysis to amplify the difference and obtain the secret keys from the cryptosystem. This approach has been very successful and has received widespread attention.

These non-invasive attacks exploit information leaked from the microchip, which succeeds because the designer of a cryptosystem usually focuses on the encryption algorithm but pays less attention to the possibility of side-channel information leakage. In fact, this side-channel information leakage is difficult to avoid in practice even when the designer does consider the problem carefully. A digital system produces many analog side-effects which can be used by non-invasive attacks.

Obviously invasive and non-invasive attacks are likely going to be used together to attack a security device. This gives attackers much more power to break into the security device. For example, an attacker can learn the architecture of a device by using invasive methods and carry out attacking the devices using non-invasive methods.

#### 2.3.1 Non-invasive attacks

An invasive attack accesses the physical circuits and the location of memory patterns on the chip. Non-invasive attack is where the attacker does not necessarily know the details of the inside of the security implementations and makes no attempt to access the devices. Non-invasive attacks include power consumption analysis, timing attack, clock and power glitching, fault analysis attack, etc. Non-invasive attacks are the main focus of this thesis.

#### **Timing attack**

A timing analysis attack [6] has a similar basis to power analysis attacks. Instead of using differential power information, timing analysis uses the leakage of information through data- and instruction-dependent timing variations. If a secure implementation takes a different amount of time to execute different instructions or to process different data, then the secure information can be extracted by analysing the timing differences. For instance, many multiply architectures employ clever algorithms, such as Booth's algorithm [75], to speed up their operation; however the timing differences may leak information that can be used to determine the Hamming weight of the multiplier's operands.

#### Clock and power glitch attacks

The idea behind clock and power glitch attacks [5, 14] is that increasing the clock frequency or decreasing the power supply for a very short time induces a malfunction on

the circuit, so the attack can redirect the execution of the algorithm. In general, smartcards execute a routine that detects unauthorized access attempts through erroneous input. However, an attacker can create a malfunction that manages to bypass the sophisticated cryptographic barrier by preventing the execution of this code.

Clock glitches increase the clock frequency for a time so short that it can not be detected even by the high-frequency detector, which is used to determine high frequency signals, on the smartcard. Such temporary increase in the clock frequency causes some instructions, for example conditional jumps, to have insufficient time to execute correctly: the branch condition does not have enough time to evaluate, as the current cycle is artificially shortened, and instead of taking the branch, the execution falls through to the next instruction.

Such a trick can be used to override a system's response to an attack. Power supply fluctuations can affect the charge and the discharge time of transistors. Decreasing the power supply voltage can decrease the speed of the circuit, and therefore some instructions may not have enough time to complete, leading to the same effect as a clock glitch.

#### 2.4 Power consumption and attacks

Technological constraints in CMOS VLSI circuits result in a different power consumption when manipulating a logic "one" compared to manipulating a logic "zero", see below in Section 2.4.1. Consequently, cryptographic algorithms often consume a slightly different amount of power when performing different encryption operations. The power analysis attack is based on observations of the power or current consumed by the microcontroller during the execution of decryption or encryption on a cryptosystem. The basic philosophy behind this observation is that there is a correlation between the power consumption and the data being processed when certain operations are being executed. If the variations in the power consumption can be recorded somehow by precisely monitoring the power current, those operations and data can possibly be identified.

Power analysis attacks have put smartcards at high risk because of the leakage of this side channel power consumption information. Techniques developed by Kocher [7] show how

the attack exploits the small amount of side-channel information to break widely-used cryptographic algorithms. The following section starts with looking at power consumption in CMOS circuits, then power analysis attack techniques are discussed.

#### 2.4.1 Power consumption in CMOS circuits

A CMOS VLSI circuit is built out of individual transistors which act as a switches. The motion of electrical charge consumes power and yields electromagnetic radiation, both of which are externally observable. If individual transistors produce externally readable electrical information, it is possible to identify aspects of the whole circuit behaviour by measuring the power consumption.

The power consumption of a CMOS VLSI circuit consists of three parts: static consumption, dynamic consumption and short-circuit consumption [40, 41]. The dynamic consumption,  $P_d$ , is normally the dominant component and is primarily responsible for information leakage. It is the result of the charging and discharging of the load capacitance, and is given by:

$$P_d = \frac{1}{2} \cdot f \cdot C_l \cdot V_{dd}^2 \cdot A_c \tag{2}$$

where  $A_c$  is the circuit activity (the proportion of the total capacitance switching in each clock cycle on average), *f* is the frequency of switching,  $C_l$  is the total circuit capacitance and  $V_{dd}$  is the power supply voltage.

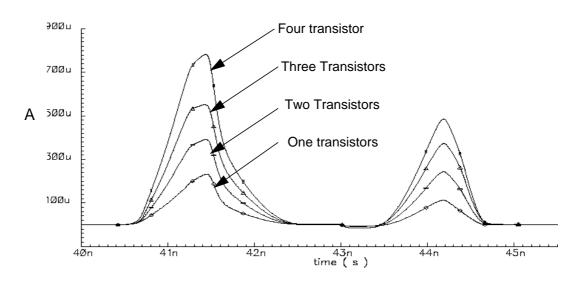

From this equation it can be seen that, for a given circuit where the load capacitance and supply voltage are constant, the dynamic power consumption depends on the circuit activity,  $A_c$ . In other words, the more capacitance that is switched, the more power is dissipated. Figure 2.2 shows how the power consumption varies with the number switching transistors. It also illustrates that switching transistors from "low" to "high" (the left side) consumes more power than switching from "high" to "low" (the right side).

For the attacker of a secure system, this is the characteristic of CMOS VLSI circuits that inspires power analysis attacks. For example, a multiplier adds an appropriately shifted multiplicand to a running sum when the multiplier operand bit is one whilst it does nothing when zero. Hence the multiplier dissipates more power processing a multiplier bit which is a one than when it is a zero. If the multiplier operand is a secret key, then power analysis on the multiplication operation yields vital information about the key.

#### 2.4.2 Simple power analysis attack

A simple power analysis attack observes the power consumption waveform directly and measures the obvious peaks which are known (through prior investigation) to relate to security information. If a smart attacker has a detailed knowledge of the insides of a smartcard and knows where the security information is, then the attacker will use power information efficiently to extract that security information. Individual operations can be identified if power consumption varies significantly when performing different operations. For example, conditional branches typically need to test the value of the conditional bit. The power consumption and the execution time may differ significantly depending on the value, "one" or "zero", of this bit. Therefore, conditional branches are vulnerable since the value of this bit can be determined by observing the power consumption at the clock cycle of the instruction that computes the bit. Kocher claimed that 16 rounds and the final permutation of DES can be determined by simple power analysis attacks [7].

By measuring power information attackers may be able to identify the instructions being executed. Figure 2.3 shows the power information revealed when executing XOR and

Figure 2.3 Power consumption of XOR and ADD instructions

ADD instructions on the single-rail SPA processor [15]. The solid curve is the power waveform for the XOR and the dashed curve the waveform for the ADD instruction. It is clear that the two waveforms are readily distinguishable. Such difference is likely due to processing different instructions rather than different data, which normally results in much smaller difference. This simple observation indicates the power consumption of single-rail SPA is instruction-dependent. Similarly, attackers can extract information on the data being processed if there is data-dependent side-channel information leakage.

#### 2.4.3 Differential power analysis attack (DPA)

DPA is much more difficult to defend against than simple power analysis [8, 13]. Attackers do not necessarily need to know the implementation details of the cryptosystem on which the DPA attack is mounted. DPA uses statistical analysis techniques to maximize the information extracted from power variations by subtracting the average power (which is not correlated to the data) and other extraneous signals from the waveforms. DPA aims to eliminate the power consumption and other measurement noise that is not relevant to security information, and to amplify the power consumption that is correlated with the secure information.

A DPA attack involves two steps: data collection and data analysis. Similar to the simple power analysis attack, data is collected by monitoring the power consumption of the device when running algorithms. Using statistical data analysis helps to maximize leaked side-channel information and to identify a single trace from the observations. An attack on DES as an example of a DPA process is briefly reviewed below.

Firstly, the DES algorithm is executed for N iterations and one power trace is obtained for each iteration with M sampling points for each trace, denoted as P(i, j) where i=1...N, indicates the number of the iteration and j=1...M is the sampling point of each iteration. Meanwhile, the ciphered-text output and the plain-text input for each operation is assumed to be available to the attacker, denoted as  $CTO_i$  and  $PTI_i$  respectively. Then a partitioning function is chosen to split the extracted waveforms into two sets in order to see if there is a difference in power consumption when different data (plain-text input) is being processed. Because, at some point during the DES operation, the value of the bit obtained from equation (3) needs to be computed, this equation is chosen as a partitioning function for the differential power analysis attack on DES encryption.

$$D(C_{1}, C_{6}, SK6_{16}) = C_{1} \oplus SBOX1(C_{6} \oplus SK6_{16})$$

(3)

- SK6<sub>16</sub>: the first six bits from the 16th sub-key, SK<sub>16</sub>

- C6: six bits from ciphered text output, CTO, that XOR with SK6<sub>16</sub>

- C1: one bit from CTO that XORs with the first bit of 4-bit SBOX1 output

This partitioning function is also illustrated in Figure 2.4, where  $C_6$  is six corresponding bits of the ciphered output,  $CTO_i$ , that XORs with  $SK6_{16}$ , the first six bits of a guessed 16th round subkey,  $SK_{16}$ , to form a six-bit input to SBOX1, the first of the eight SBOXes in DES. The one bit output of the D function results from XORing  $C_1$ , which is one corresponding bit of the ciphered output, with the first bit of the 4-bit SBOX1 output.

The power waveforms, P(i,j), are partitioned into two groups, group zero, P0, and group one, P1. according to the partitioning function as follows:

$$P(i, j) \in P_0 | D(C_1 \cdot C_6 \cdot SK6_{16}) = 0$$

(4)

$$P(i, j) \in P_1 | D(C_1 \cdot C_6 \cdot SK6_{16}) = 1$$

(5)

The partitioned two groups of waveforms are then averaged separately to obtain their typical characteristic waveforms, denoted by  $P_0[j]$  and  $P_1[j]$  respectively, following equations (4) and (5). Then, the difference between these two characteristic waveforms, denoted as dP[j], can be computed as follows:

$$dP[j] = P_1[j] - P_0[j]$$

(6)

If information leakage exists on the target device through the difference in power consumption, then whenever the partitioning bit is manipulated, the result of equation (6) will display a small difference, denoted as *e*, in the power consumption corresponding to the value of this bit, 'one' or 'zero'. At any other time, because the operation is not correlated to the D function, it will theoretically be equal to zero. Note that, in reality, it may not be zero because of measurement noise.

Since the ciphered-text output,  $CTO_i$ , is known, the only thing the attacker does not know is the six bit portion of subkey,  $SK6_{16}$ . The attacker could guess all of the 2<sup>6</sup> possibilities using a brute force search. For each guess, a new partition is computed and a new difference trace, dP[j], is formed. One of the 2<sup>6</sup> difference traces will show bias whenever the partitioning bit is computed. All other difference traces will not show any significant bias. The guessed portion of the subkey for the partitioning which generates bias would likely be the correct guess. By applying this approach to the other seven SBOXes, the remaining portion of the subkey could be discovered [13].

#### 2.5 Summary of chapter

This chapter has introduced some basic background material on both smartcards and cryptography, including describing the Data Encryption Standard (DES) algorithm which will be used in chapter 8. Smartcard security and some common attacks on smartcards, both invasive and non-invasive attacks, were discussed with a focus on power analysis attacks. This chapter also reviewed how CMOS VLSI consumes power in addition to introducing the Differential Power Analysis (DPA) attack in detail based on the DES algorithm. The following chapter introduces asynchronous design technologies and hardware security.

# Chapter 3: Asynchronous Design and Hardware Security

This chapter presents an introduction to asynchronous design technology, including delay models, handshake signalling protocols, data encoding methods as well as synthesis tools for asynchronous design, and the advantages and disadvantages of asynchronous design. This chapter also discusses issues relating to hardware design for security.

# 3.1 Introduction

The design of digital systems can be classified into two methods, synchronous (clocked) and asynchronous (also widely known as self-timed or clockless) design. Although the two design methodologies were both developed in the early days of digital design before the introduction of VLSI (Very Large Scale Integration) circuit technology, synchronous design has dominated digital circuit design for several decades because it offers a simple design style by employing one or more globally distributed sources of timing information, the clock(s), to sequence systems. The clock signal controls the change of state within the system and all activities regulated by the clock in the system have to be completed within the clock cycle time in order to ensure that correct data is latched into storage. Figure 3.1a shows a typical synchronous communication system where both the sender and the receiver are regulated by the clock signal, clk. At the active clock edge (rising in this case), data is sent from the sender to the receiver. Data has to be ready at the sender side before that edge and must be held until received by the receiver as in Figure 3.1b.

In contrast, asynchronous circuit design does not use a global clock but employs a handshaking protocol to control communication between independent units in the system via *channels* which usually are unidirectional. Local handshake signals are used to indicate the availability of data at the sender and the acceptance of data at the receiver.

Figure 3.1 Synchronous design vs. asynchronous design

Figure 3.1c shows a self-timed communication system where data is transmitted through *a push channel* where data and the request signal travel in the same direction. (The alternative, a *pull channel*, is where the request signal travels in the reverse direction to the data.) A *request* signal travels on the req wire to indicate when the data is ready for transfer, and the *acknowledge* signal travels back to the sender on the ack wire to indicate the acceptance of data and the readiness for further data. Regulated by these two handshake control signals, data is safely transmitted through the channel. The sequences for these signals using *2-phase* and *4-phase* handshake protocols (described in the following section) will be shown in Figure 3.2.

Given such examples for comparison, the fundamental differences between synchronous and asynchronous VLSI design methodologies are:

- Activities on a synchronous circuit are dominated by the globally distributed clock signal and triggered simultaneously and completed within the clock cycle.

- Events on self-timed circuits, on the other hand, are managed by locally distributed handshake control signals, and activated at their own pace and completed accordingly.

# 3.2 Asynchronous design

The following sections describe some fundamental aspects of asynchronous logic design technology; many others can be found in the literature [42, 43].

## 3.2.1 Asynchronous circuit models

An asynchronous circuit can be characterised by the delay model as follows:

- *Bundled-data* circuits assume a pre-determined timing relationship between data and control signals, which must take account of gate and wire delays. The data must be valid before the request signal. That is, the delay in the control signal must be no less than the delay in the data path. For example, the data value in Figure 3.1c must be valid at the receiver end before the arrival of the request signal, req, otherwise incorrect data may be latched.

- *Speed-independent* (SI) circuits operate correctly regardless of gate delays, but the wire delays are assumed to be zero or so small that they can be neglected. This assumption normally holds only in small circuits since, in a large circuit where the interconnect inevitably causes long delays, the wire delays cannot be assumed to be zero.

- *Delay-insensitive (DI)* circuits are those which do not depend on gate delays or wire delays, which means that the circuit works properly despite delays on wires and gates. For a large and complex asynchronous circuit, this model is usually applied to the higher levels of the design.

- *Quasi-delay-insensitive* (QDI) circuits are similar to delay-insensitive circuits but they assume that branches in a forked wire have the same delay (the isochronic fork assumption), or at least the differences between delays in forks are negligible compared with the delays in circuit elements.

### 3.2.2 Handshake signalling protocol

The transfer of data between sender and receiver in asynchronous circuits is handled by the handshake signals: a request signal, req, which the sender uses to start the transfer, and an acknowledge signal, ack, by which the receiver responds to the transfer. A req indicates data validity and readiness for transmission while the acknowledge from the receiver indicates the acceptance of the transmitted data and the receiver's readiness to accept further data.

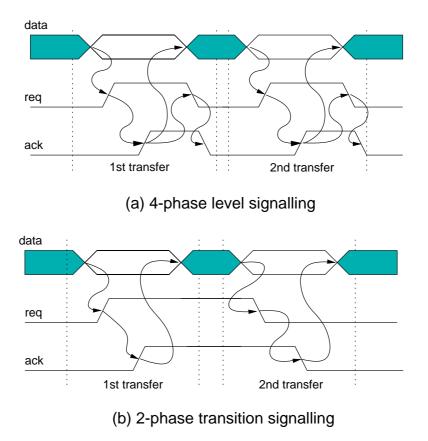

A handshake signal can be sent either on a separate wire or encoded into the data. Two different signalling protocols are commonly used to pass these signals: a 4-phase (level signalling) protocol or a 2-phase (transition signalling) protocol, as shown in Figure 3.2.

#### 4-phase level signalling protocol

4-phase level signalling is a return-to-zero signalling scheme, shown in Figure 3.2(a). It uses the level of a signal to indicate handshake information. The request and acknowledge

Figure 3.2 Handshake protocols (push channel)

events have to be passed in sequence. That is, a second request must not occur until after an acknowledgement has been received. A return-to-zero phase is needed to reset the state before the next data transfer.

#### 2-phase transition signalling protocol

In the 2-phase protocol scheme shown in Figure 3.2(b), the logic level of the signals is no longer important. Instead, events are signalled by the transitions (both rising and falling) of the signals. Similar to the 4-phase protocol, the request and the acknowledge signals have to be in sequence. However, the 2-phase protocol does not need a return-to-zero phase. In fact, because of the lack of a return-to-zero phase, the 2-phase protocol has the potential advantages of high performance and lower power as this scheme uses only half as many transitions per transfer as the 4-phase protocol.

It is obvious that the 2-phase protocol has some advantages if it is used in communication systems (rather than computation) where the power dissipation is determined by the number of transitions required to send an amount of data. Because fewer transitions are need to transmit the same amount of data, 2-phase signalling will consume less energy. However, 4-phase control circuits are often simpler than 2-phase systems because the level sensitive signals in 4-phase circuits can be easily used to control latches.

#### 3.2.3 Data encoding

This section describes the general categories of data encodings commonly used in asynchronous circuits, including single-rail, dual-rail, N-of-M and one-hot encodings. Among them, dual-rail encoding will be extensively used in this research and its ability to balance power consumption will be discussed throughout the thesis.

#### Single-rail encoding

Similar to conventional synchronous circuits, single-rail encoding uses only one wire to represent two logic values, "one" and "zero". In asynchronous circuits, the encoding scheme will require additional wire(s) to indicate the request and acknowledge signals.

This encoding is often referred to as "bundled-data" because the data is "bundled" with the request signal.

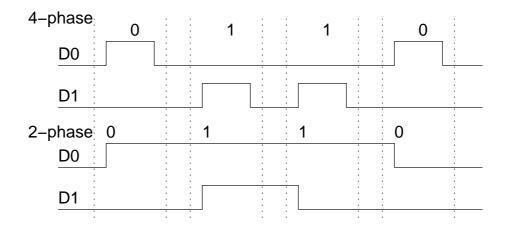

#### Dual-rail encoding

Dual-rail encoding, as shown in Figure 3.3, requires two wires to express one bit of data, each line representing one of the two binary values. To transfer n-bit information in parallel needs 2n wires. An additional wire to transmit the acknowledge signal to complete the handshake protocol may also be required to build dual-rail channels. Transitions on one wire indicate a logic "one" and similarly transitions on the other mean a logic "zero". Thus, no matter what data value is transmitted, the same number of transitions is needed for each transfer. Therefore, the same amount of power is dissipated. Differences in power consumption when processing different data could be reduced significantly. This is the motivation for using dual-rail encoding to implement a secure device.

A dual-rail circuit does not necessarily require a separate wire for the request signal because it is possible to determine the validity of the data by detecting valid data on one of the two wires for each bit of the data. If an active level (in 4-phase signalling) or an event (in 2-phase signalling) is detected new data is ready to be transferred. In other words, a completion detection tree, a mechanism to determine the validity of the data, is required.

Figure 3.3 Dual-rail encoding

#### N-of-M encoding

An N-of-M code communicates by signalling an event on exactly N of the M wires of a code group. Data encoded using N-of-M encoding will be transmitted correctly regardless of the delay in the wires and the gates, and thus this scheme is delay-insensitive. It requires a completion detection tree to determine the validity of the data [44]. An N-of-M code can encode  $\frac{M!}{N! \cdot (M-N)!}$  possible symbols representing data values. For example, a 3-of-6 encoding has twenty possible symbols which could be used to indicate a 4-bit binary value, and also End, Start and Ack events. Similarly, a 2-of-7 code can produce 21 possible symbols. Comparing these two N-of-M codes the former uses only 6 wires instead of the 7 wires used by latter whilst the 3-of-6 code uses 3 transitions instead of the 2 transitions of the 2-of-7 code to send a symbol (or 6 and 4 transitions in the level signalling protocol respectively). Dual-rail encoding can be defined as a special case of N-of-M encoding, 1-of-2 encoding. As with dual-rail encoding, N-of-M encoding consumes the same number of transitions regardless of what the data value is. It therefore has the same potential as dual-rail encoding to balance the power consumption used when processing different data values.

#### One-hot encoding

One-hot encoding can be recognized as a special N-of-M encoding where N is equal to one, each of the M wires representing one symbol which represents one data value. Thus it requires 2<sup>m</sup> wires to encode an m-bit binary data value. Similarly, ten wires can directly express decimal values. Like N-of-M encoding, a completeness detection tree is required to determine the validity of the data presented.

Null Conventional Logic or NCL technology developed at Theseus logic Inc. [45] combines one-hot delay-insensitive asynchronous logic with a return-to-zero protocol. NCL defines digital circuits having three logic values, "one", "zero" and "NULL". Since a single wire is limited only to two values and one of them must be assigned to NULL, there is only one value left to express data, so at least two wires are required to address a one-bit binary value: one wire represents "one" and the other "zero", while both wires return to zero to assert NULL.

In NCL, threshold gates [46] are used to implement circuits. A threshold gate yields a high output if a specified number of inputs become high and the output will remain high until all inputs fall to zero. For instance, a 2/3 threshold gate requires two of the three inputs be high to yield a high on the output, and the output remains high until these two inputs return to zero.

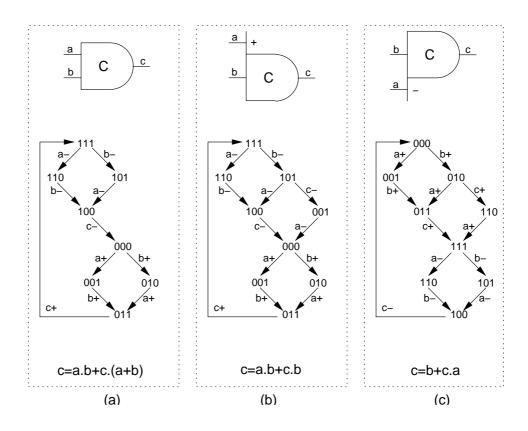

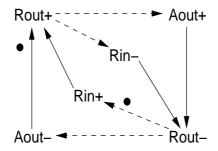

#### 3.2.4 Muller C-elements

The Muller C-element is the most common gate encountered in asynchronous circuits. The basic functions of a C-element are event synchronization and state holding. Figure 3.4 shows three different C-elements and their state graphs, which describes all possible states combinations of output ports and input ports by changes in inputs and outputs: one symmetric 2-input C-element (a.) and two asymmetric 2-input C-elements (b. and c.). An input controls both edges when it connects to main body of the gate. It controls only the rising edge when connected to the '+' extension and controls only the falling edge if it is connected to the '-' extension.

Figure 3.4 C-elements and their state graphs

Figure 3.4(a) shows a symmetric C-element with two inputs connected to the main body of the gate. Both inputs control both rising and falling edges, that is, the change of output c is dependent on both inputs, a and b. For example, the state graph below the symbol shows the c+ can only happens when both a+ and b+ have happened allowing states changes from 000 to 011 and finally to 111.

Figure 3.4(b) is an asymmetric C-element that has one input connected to the '+' extension, which means that this input controls only the rising edge of the output. So setting output c to high needs both inputs a and b to be set high. However, the return to low of input b will lower the output regardless of input a. The state graph below the symbols shows the full behaviour of the asymmetric C-element.