# Computation Reduction for Statistical Analysis of the Effect of Nano-CMOS Variability on Integrated Circuits

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2012

By

Zheng Xie School of Computer Science

## Contents

| Lis | List of Figures 7 |         |                                                            |    |  |

|-----|-------------------|---------|------------------------------------------------------------|----|--|

| Ab  | strac             | t       |                                                            | 10 |  |

| Dec | elara             | tion    |                                                            | 11 |  |

| Co  | pyrig             | ht      |                                                            | 12 |  |

| Acl | know              | ledgem  | ents                                                       | 13 |  |

| 1   | Intr              | oductio | n                                                          | 14 |  |

|     | 1.1               | Introdu | ction to the Research Area                                 | 14 |  |

|     | 1.2               | Resear  | ch Motivation and Context for This Project                 | 16 |  |

|     | 1.3               | Resear  | ch Approach                                                | 18 |  |

|     | 1.4               | Resear  | ch Hypothesis                                              | 18 |  |

|     | 1.5               | Introdu | ction to the Methodology                                   | 19 |  |

|     |                   | 1.5.1   | Behavioural Modelling                                      | 19 |  |

|     |                   | 1.5.2   | Statistical Blockade                                       | 20 |  |

|     |                   | 1.5.3   | Low-Discrepancy Sampling with Quasi MC Methods             | 21 |  |

|     |                   | 1.5.4   | Originality                                                | 21 |  |

|     |                   | 1.5.5   | Software Development                                       | 21 |  |

|     |                   | 1.5.6   | RandomSPICE                                                | 22 |  |

|     | 1.6               | Resear  | ch Aims and Objectives                                     | 22 |  |

|     | 1.7               | Structu | re of This Thesis                                          | 23 |  |

| 2   | Nan               | o-CMC   | OS Technology and the Causes and Effects of Variability in |    |  |

|     | Inte              | grated  | Circuits                                                   | 26 |  |

|     | 2.1               | Introdu | iction                                                     | 26 |  |

|     | 2.2               | CMOS    | Technology for Integrated Circuits                         | 28 |  |

|     |                   | 2.2.1   | MOS Transistors                                            | 28 |  |

|     |                   | 2.2.2   | MOS Transistor Models                                      | 32 |  |

|     |                   | 2.2.3   | CMOS Logic                                                 | 34 |  |

|     |                   | 2.2.4   | CMOS Circuit Design                                        | 36 |  |

|     |                   | 2.2.5   | CMOS Technologies                                          | 37 |  |

|   |     | 2.2.6    | MOSFET Scaling and the Adaptations on Design         |    |

|---|-----|----------|------------------------------------------------------|----|

|   |     | 2.2.7    | Synchronous and Asynchronous ('Self-Timed') Circuits | 40 |

|   |     |          | 2.2.7.1 Introduction                                 | 40 |

|   |     |          | 2.2.7.2 Synchronous Circuits                         | 41 |

|   |     |          | 2.2.7.3 Asynchronous circuits                        |    |

|   | 2.3 | Nano-(   | CMOS Variability and Effects on Integrated Circuits  |    |

|   |     | 2.3.1    | Introduction                                         |    |

|   |     | 2.3.2    | Sources of Variation                                 | 44 |

|   |     | 2.3.3    | Classification of Variation                          |    |

|   |     | 2.3.4    | Intrinsic MOSFET Variability                         |    |

|   |     |          | 2.3.4.1 Random Discrete Dopant Fluctuations          |    |

|   |     |          | 2.3.4.2 Line Edge Roughness                          | 50 |

|   |     |          | 2.3.4.3 Gate Oxide Thickness Variation               | 51 |

|   |     | 2.3.5    | Effects of Variability on Performance                | 51 |

|   | 2.4 | Conclu   | isions                                               | 53 |

| 3 | Ana | lysis of | the Effect of Variability on Integrated Circuits     | 54 |

|   | 3.1 | Introdu  | action                                               | 54 |

|   | 3.2 | Effects  | s of Variability                                     | 54 |

|   |     | 3.2.1    | Modelling Variability                                | 55 |

|   |     | 3.2.2    | Simulating Variability                               | 55 |

|   |     | 3.2.3    | 'Worst case' Analysis of Variability                 | 56 |

|   | 3.3 | Worst    | Case Analysis in Practice                            | 57 |

|   |     | 3.3.1    | Illustration of Concept of Worst Case Analysis       | 58 |

|   |     | 3.3.2    | Corners                                              | 59 |

|   | 3.4 | Introdu  | action to Monte Carlo Simulation                     |    |

|   | 3.5 | Statisti | ical Static Timing Analysis (SSTA)                   | 63 |

|   | 3.6 | Integra  | ated Circuits (IC) Design Flow                       | 65 |

|   |     | 3.6.1    | IC Design Flow                                       | 65 |

|   |     | 3.6.2    | Asynchronous Circuit Design Flow with Balsa          | 68 |

|   |     |          | 3.6.2.1 The Balsa Development System                 | 68 |

|   |     |          | 3.6.2.2 Analysing Reasons for Failure                |    |

|   |     |                                 | e Balsa Circuit Description to Increase the |

|---|-----|---------------------------------|---------------------------------------------|

|   |     | yield                           |                                             |

|   | 3.7 | Simulation of ICs by EDA To     | ols72                                       |

|   |     | 3.7.1 Encounter                 |                                             |

|   |     | 3.7.2 Introduction to HSPIC     | °E                                          |

|   |     | 3.7.3 Introduction to NGSP      | ICE                                         |

|   |     | 3.7.4 RandomSPICE               |                                             |

|   |     | 3.7.4.1 The Random              | nisation                                    |

|   |     | 3.7.4.2 Restrictions            |                                             |

|   |     | 3.7.4.3 RandomSPIC              | CE Transistor Model Libraries               |

|   |     | 3.7.5 Statistical Analysis wi   | th RandomSPICE78                            |

|   | 3.8 | Conclusions                     |                                             |

| 4 | Mo  | nte Carlo Simulation for the l  | Design of Nano-Scale Integrated Circuits 82 |

|   | 4.1 | Introduction                    |                                             |

|   | 4.2 | Monte Carlo Methods             |                                             |

|   | 4.3 | Monte Carlo Simulation          |                                             |

|   | 4.4 | Monte Carlo Simulation Appl     | ied to Integrated Circuits93                |

|   |     | 4.4.1 Using HSPICE Direct       | ly93                                        |

|   |     | 4.4.2 Using NGSPICE             |                                             |

|   |     | 4.4.3 Using RandomSPICE         |                                             |

|   |     | 4.4.4 Using a New Harness       |                                             |

|   | 4.5 | Introducing intra-die correlati | on107                                       |

|   |     | 4.5.1 Results from introduct    | ng intra-die correlation into a CMOS NAND   |

|   |     | gate                            |                                             |

|   |     | 4.5.2 Results from the analy    | sis of a binary full adder with behavioural |

|   |     | models of gates                 |                                             |

|   | 4.6 | Conclusions                     |                                             |

| 5 | Din | nension Reduction of Monte (    | Carlo Circuit Simulation 119                |

|   | 5.1 | Introduction                    |                                             |

|   | 5.2 | Principal Component Analysis    | s (PCA)                                     |

|   |     | 5.2.1 Introduction to the Co    | ncept 120                                   |

|   |     |                                 |                                             |

|   |     | 5.2.2    | Performing the Analysis                                | 120 |

|---|-----|----------|--------------------------------------------------------|-----|

|   |     | 5.2.3    | Application of PCA to Modelling Statistical Variation  | 122 |

|   |     | 5.2.4    | Applying PCA to Reduce Dimensionality in MC Simulation | 124 |

|   | 5.3 | Behavi   | ioural Modelling                                       | 125 |

|   |     | 5.3.1    | Introduction to the concept                            | 125 |

|   |     | 5.3.2    | How SPICE Implements Behavioural Model Components      | 126 |

|   |     | 5.3.3    | Using E, F, G or H Elements with Look-up Tables        | 127 |

|   |     | 5.3.4    | Tau Models of Devices                                  | 128 |

|   |     | 5.3.5    | Using Verilog-A in SPICE for Behavioural Modelling     | 132 |

|   |     | 5.3.6    | Behavioural Models for MC Simulation                   | 133 |

|   |     | 5.3.7    | Statistical Behavioural Circuit Blocks (SBCB)          | 134 |

|   |     | 5.3.8    | Improving the Accuracy of SBCB                         | 138 |

|   | 5.4 | Conclu   | isions                                                 | 138 |

| 6 | Cor | nputati  | on Reduction by Extreme Value Theory                   | 140 |

|   | 6.1 | Introdu  | action                                                 | 140 |

|   | 6.2 | Statisti | ical Blockade                                          | 140 |

|   | 6.3 | Classif  | fication Techniques for Machine Learning               | 143 |

|   | 6.4 | A Line   | ar Estimator for Statistical Blockade                  | 143 |

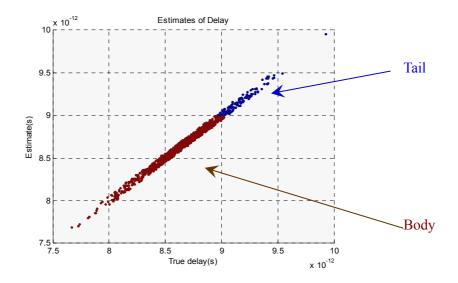

|   | 6.5 | Applic   | ation of the Linear Estimator                          | 147 |

|   | 6.6 | Execut   | tion Phase of Statistical Blockade                     | 150 |

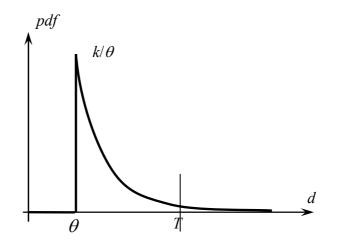

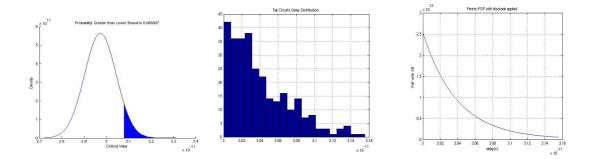

|   | 6.7 | Fitting  | a Pareto Distribution                                  | 153 |

|   | 6.8 | Measu    | rements and Evaluations                                | 155 |

|   | 6.9 | Conclu   | isions                                                 | 160 |

| 7 | Cor | nputati  | on Reduction by Quasi Monte Carlo Techniques           | 162 |

|   | 7.1 | Introdu  | action                                                 | 162 |

|   | 7.2 | Quasi-   | Monte Carlo Simulation                                 | 163 |

|   | 7.3 | Low-D    | Discrepancy Sequences                                  | 164 |

|   | 7.4 | MC an    | d QMC Convergence rates                                | 168 |

|   | 7.5 | Implen   | nentation of QMC Circuit Simulation                    | 168 |

|   | 7.6 | Conclu   | isions                                                 | 171 |

| 8  | <b>Results and Evaluation with SRAM Arrays</b> |                                                         | 172             |

|----|------------------------------------------------|---------------------------------------------------------|-----------------|

|    | 8.1                                            | Introduction                                            |                 |

|    | 8.2                                            | Description of the Simulations and Evaluation           |                 |

|    |                                                | 8.2.1 Single SRAM Cell                                  |                 |

|    |                                                | 8.2.2 SRAM Arrays                                       |                 |

|    |                                                | 8.2.2.1 SRAM8×1 Array                                   |                 |

|    |                                                | 8.2.2.2 SRAM32×1 Array                                  |                 |

|    |                                                | 8.2.2.3 SRAM32×8 Array                                  |                 |

|    | 8.3                                            | Conclusions                                             |                 |

| 9  | Con                                            | clusions and Further Work                               | 191             |

|    | 9.1                                            | Introduction                                            |                 |

|    | 9.2                                            | Review of Research Aims, Objectives, and Achievements.  |                 |

|    |                                                | 9.2.1 Design and Implementation of a Statistical Simula | tion Method 191 |

|    |                                                | 9.2.2 Dimension Reduction Techniques                    |                 |

|    |                                                | 9.2.3 Further Computation Reduction Methods             |                 |

|    |                                                | 9.2.4 Overall Conclusions                               |                 |

|    | 9.3                                            | Further work                                            |                 |

| Re | feren                                          | ces                                                     | 198             |

## List of Figures

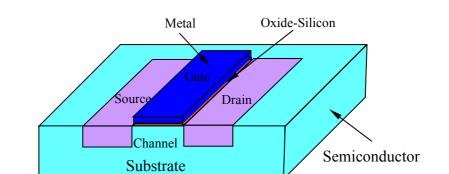

| Figure 2.1: MOSFET structure                                                             |

|------------------------------------------------------------------------------------------|

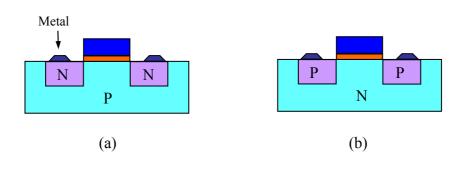

| Figure 2.2: Two types of MOSFET                                                          |

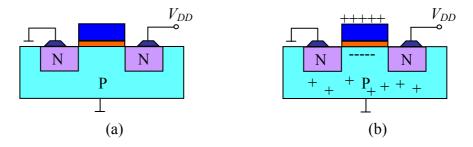

| Figure 2.3: Enhancement mode MOSFET (a) turned off, (b) turned on                        |

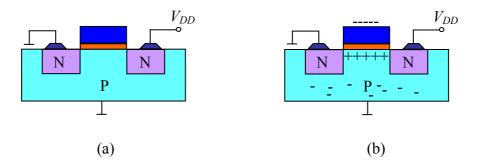

| Figure 2.4: Depletion mode MOSFET: (a) turned off (b) turn on                            |

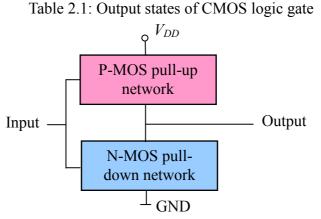

| Figure 2.5: General logic gate using CMOS pull-up and pull-down networks                 |

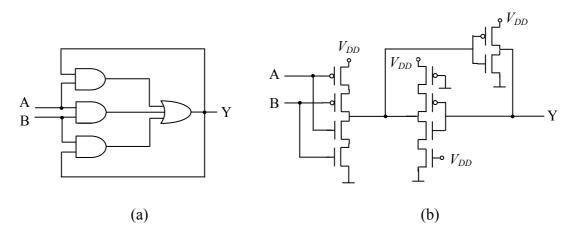

| Figure 2.6: Muller C-element: (a) gate-level, (b) transistor-level                       |

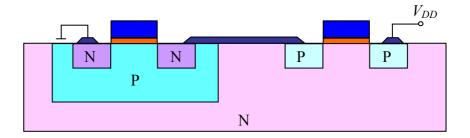

| Figure 2.7: A CMOS inverter and its switch equivalent                                    |

| Figure 2.8: CMOS inverter in cross-section                                               |

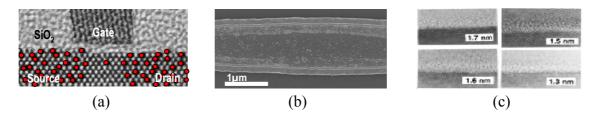

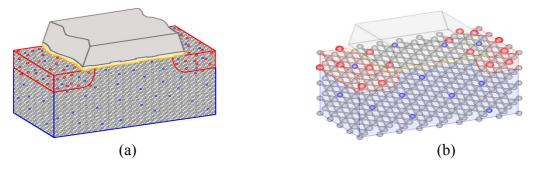

| Figure 2.9: Intrinsic variability                                                        |

| Figure 2.10: The atomistic structures of stylized transistors illustrating random        |

| discrete dopant placement                                                                |

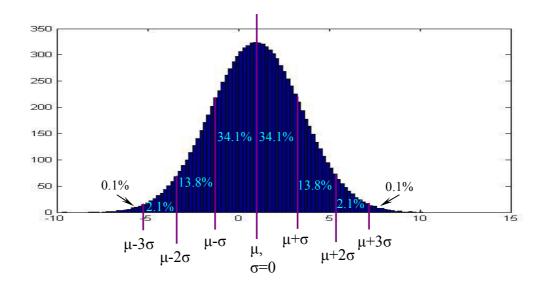

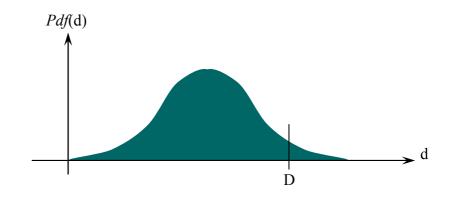

| Figure 3.1: Gaussian probability density function about nominal value (mean $\mu$ ) of a |

| parameter when standard deviation is $\sigma$                                            |

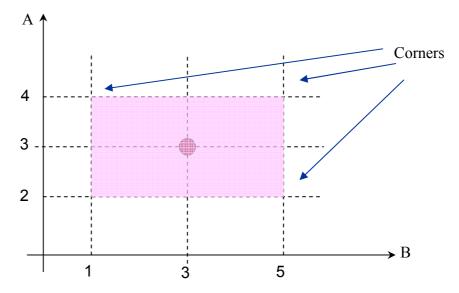

| Figure 3.2: Illustration of 'worst case corners' for two variables                       |

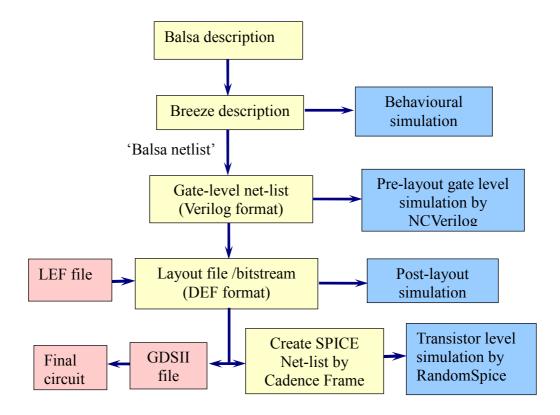

| Figure 3.3: Asynchronous Circuit Design Flow based on 'Balsa'                            |

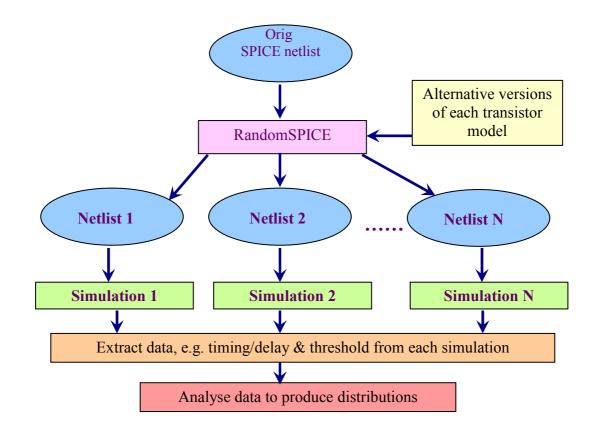

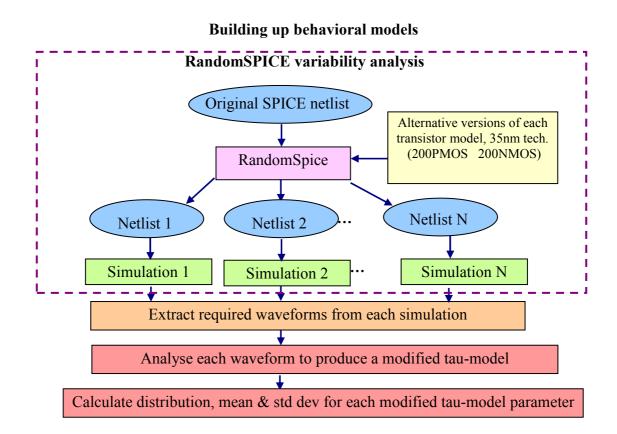

| Figure 3.4: Functional block diagram for RandomSPICE                                     |

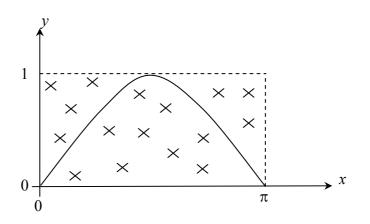

| Figure 4.1: MC integration of $sin(x)$ , $0 \le x \le \pi$                               |

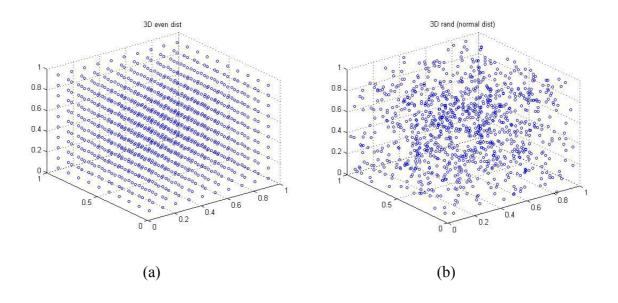

| Figure 4.2: Point-sets for three-dimensional integration                                 |

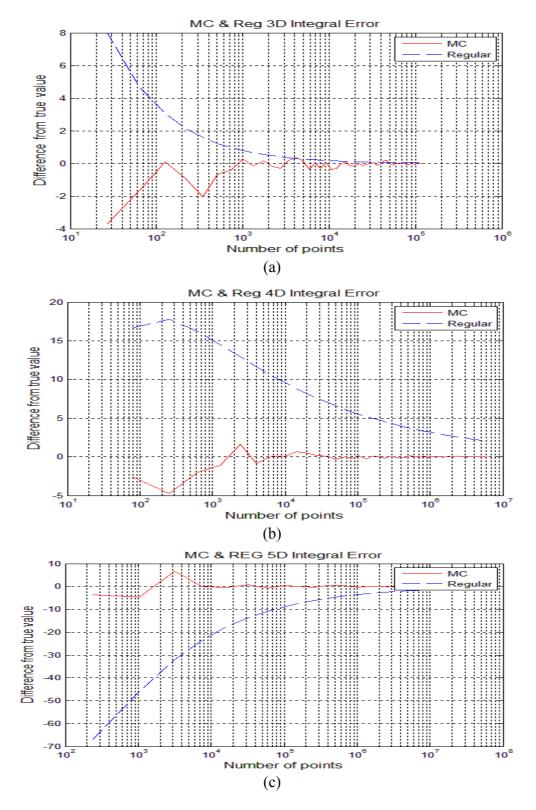

| Figure 4.3: Convergence of MC and regular integration for (a)3D integral, (b) 4D         |

| integral, and (c)5D integral                                                             |

| Figure 4.4: Gaussian probability density function of a circuit propagation delay and     |

| delay threshold D92                                                                      |

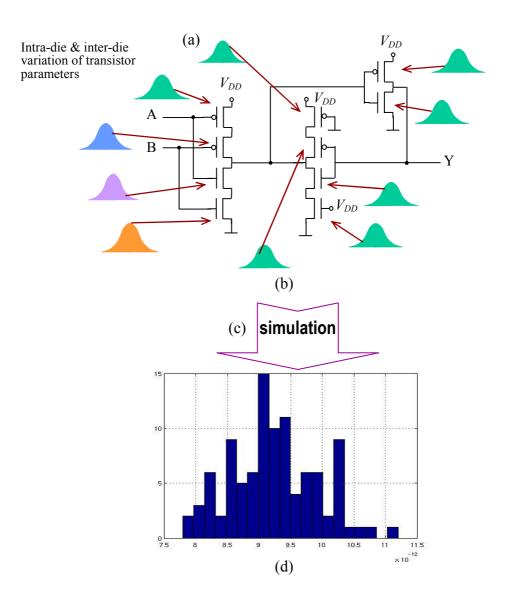

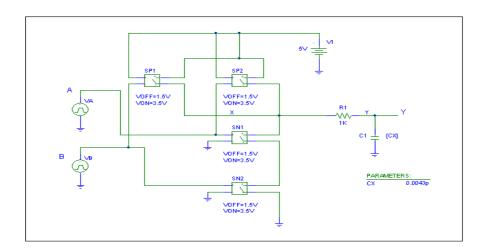

| Figure 4.5: Transistor level MC simulation to C-element circuit                          |

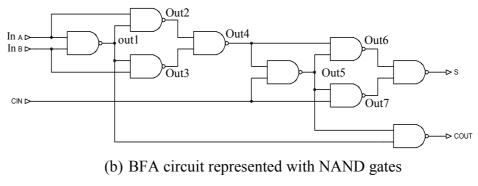

| Figure 4.6: Binary Full Adder (BFA) circuit                                              |

| Figure 4.7: MC simulation results for delay time of carry out signal101                  |

| Figure 4.8: MC simulation results for delay time of carry out signal in BFA circuit      |

| with randomisation of transistor parameters                                              |

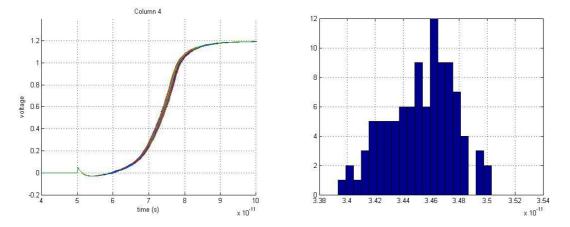

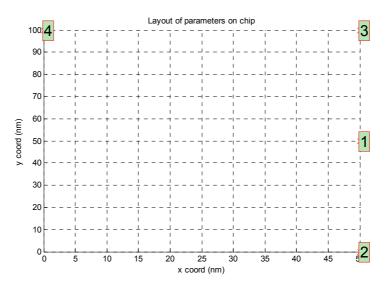

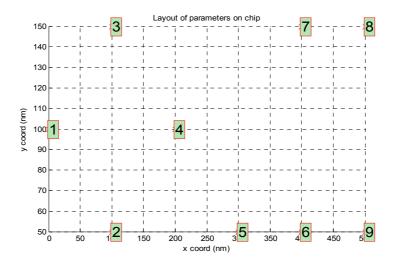

| Figure 4.9: CMOS NAND gate on-chip layout assumption 111                                 |

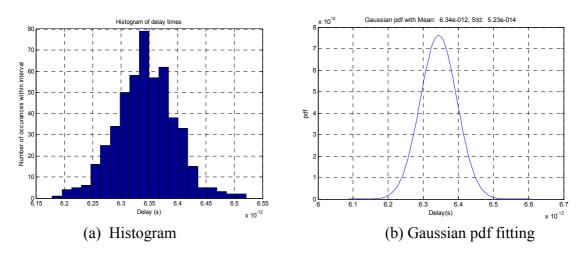

| Figure 4.10: Gaussian pdf fitted to data for 500 NAND gate circuits (lambda =              |

|--------------------------------------------------------------------------------------------|

| 0.007)                                                                                     |

| Figure 4.11: Gaussian pdf fitted to data for 500 NAND gate circuits (lambda = 1) 113       |

| Figure 4.12: On-chip layout assumption for BFA circuit represented with NAND               |

| gates                                                                                      |

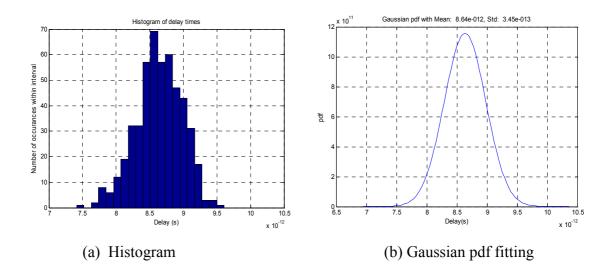

| Figure 4.13: Gaussian pdf fitted to data for 500 BFA circuits (lambda = $0.007$ ) 115      |

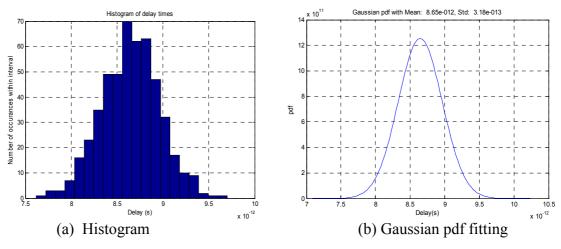

| Figure 4.14: Gaussian pdf fitted to data for 500 BFA crts (lambda = 10) 116                |

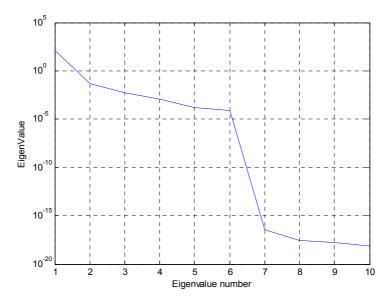

| Figure 5.1: Values of first ten ordered eigenvalues for Toshiba NMOS data                  |

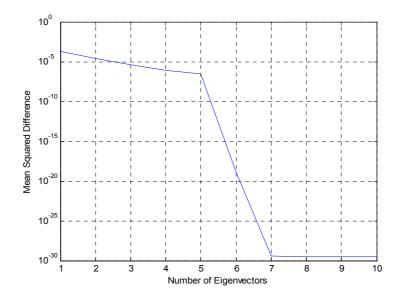

| Figure 5.2: Mean square difference between original (mean-subtracted) data and             |

| PCA approximated data as number of eigenvectors increases                                  |

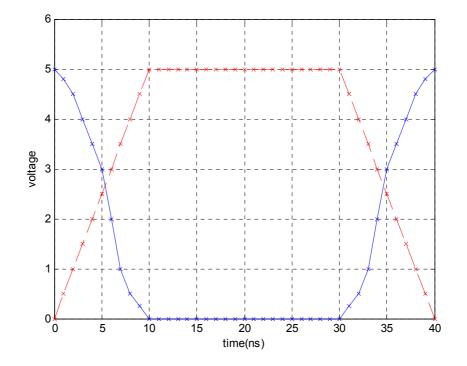

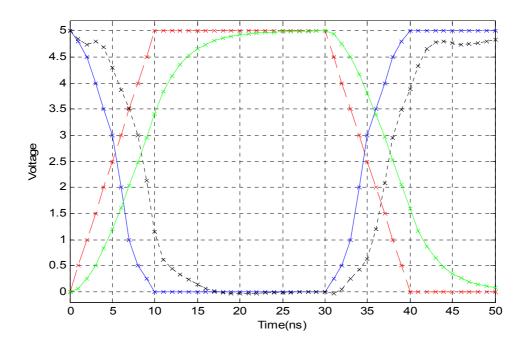

| Figure 5.3: Response of 2-input NAND gate as defined in Table 5.2                          |

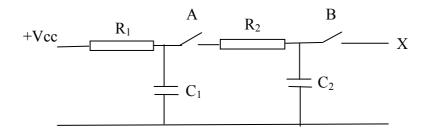

| Figure 5.4: Tau model for CMOS 'pull down' sub-circuit                                     |

| Figure 5.5: Effect of combining look-up table and simple tau model130                      |

| Figure 5.6: Flow chart for building up SCSB circuit blocks                                 |

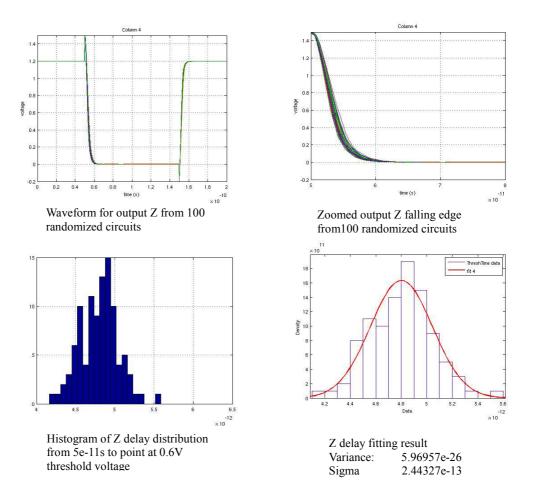

| Figure 5.7: MC simulation on a 2-input NAND gate implemented with 35nm                     |

| CMOS                                                                                       |

| Figure 5.8: NAND SBCB model                                                                |

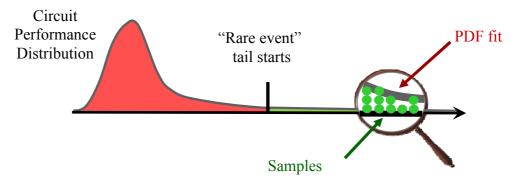

| Figure 6.1: Illustration of 'rare events' in distribution tail (as in [28]) 141            |

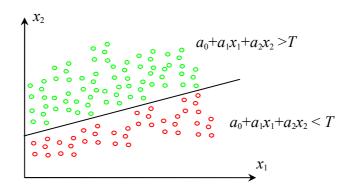

| Figure 6.2: Linear classifier dividing 2-D parameter space $(x_1, x_2)$ into 'tail' region |

| (red) and 'body' (green) where threshold is T148                                           |

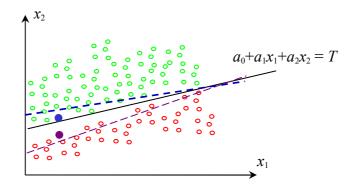

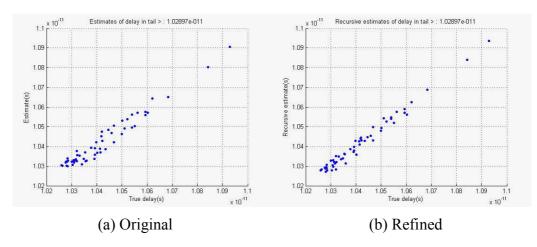

| Figure 6.3: Effect of recursive adaptation of estimator coefficients                       |

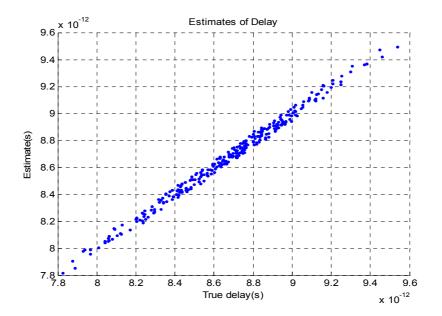

| Figure 6.4: Evaluation of 9th order linear estimator of delay in a BFA150                  |

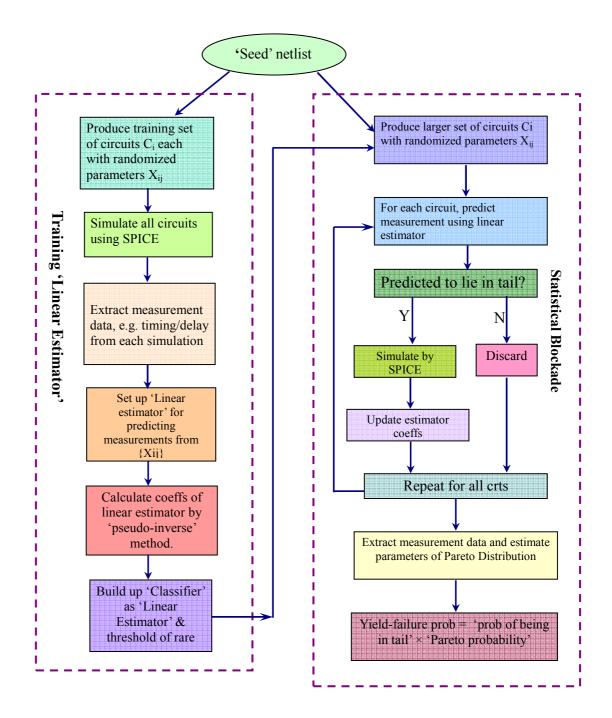

| Figure 6.5: Complete SB procedure as implemented by RandomLA151                            |

| Figure 6.6: PDF of Pareto distribution                                                     |

| Figure 6.7: Illustration of Pareto fitting procedure                                       |

| Figure 6.8: Accuracy of linear estimator . Tail defined to start at 9e-12s.                |

| Classification errors out of 1000                                                          |

| Figure 6.9: Refining linear estimator by recursion                                         |

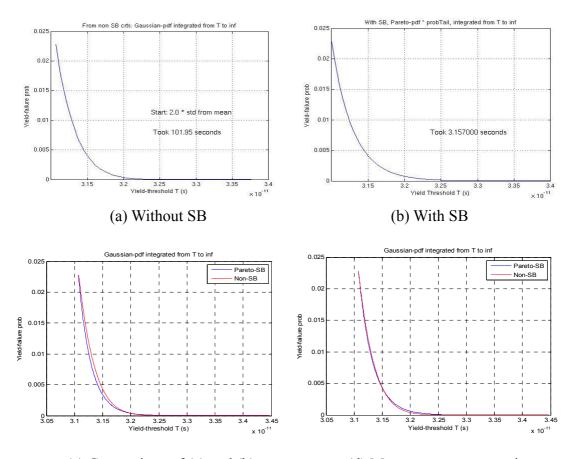

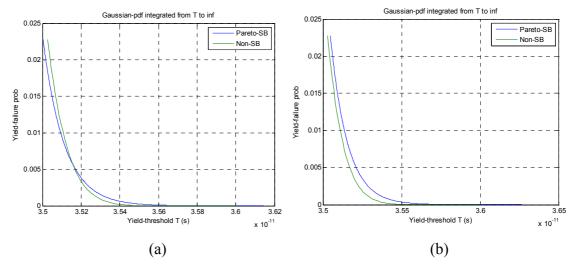

| Figure 6.10: Failure probability for a 'C-element' realisation from 500 versions: (a)      |

| without SB, (b) with SB ( $2\sigma$ from mean), (c) Comparison of (a) and (b),             |

| and (d) Comparison with more accurate estimates of mean and std-dev                        |

##

| used for Pareto-SB                                                                       |

|------------------------------------------------------------------------------------------|

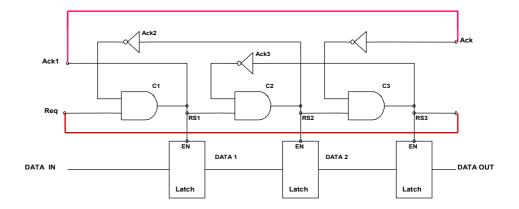

| Figure 6.11: 4-Phase 3-stage Bundled Data Muller pipeline 'ring'                         |

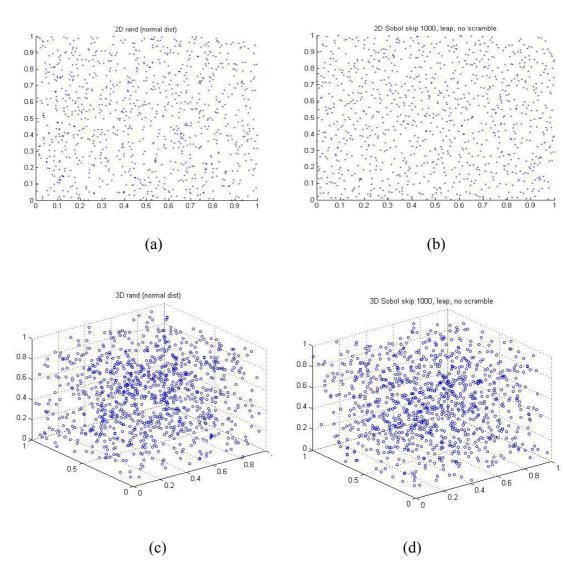

| Figure 7.1: Distributions of point-sets, (a) 2D pseudo-random points, (b) 2D Sobol'      |

| points, (c) 3D pseudo-random points, (d) 3D Sobol' points 165                            |

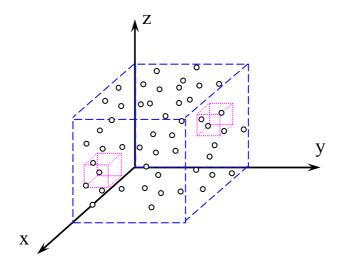

| Figure 7.2: 3-dimensional hypercube and sub-hypercube with scattered points 166          |

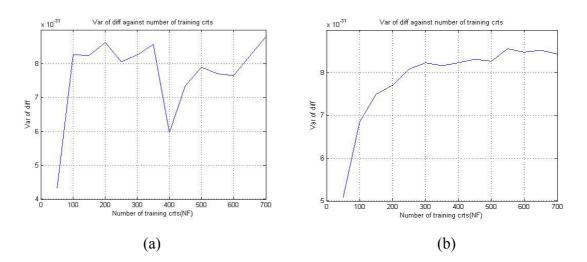

| Figure 7.3: Error analysis of linear estimators in RandomLA training phase,              |

| (a) MC simulation, and (b) QMC simulation170                                             |

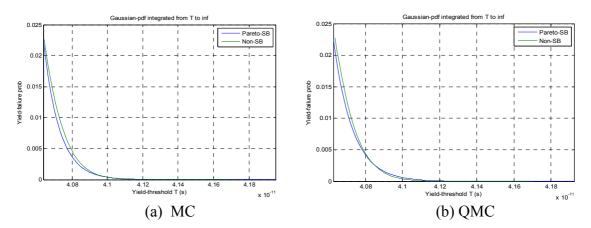

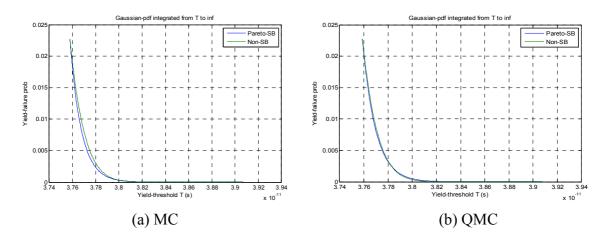

| Figure 7.4: (a) MC-SB compared to MC-non-SB for BFA (3000 circuits), (b) QMC-            |

| SB compared to MC-non-SB for BFA (3000 circuits)                                         |

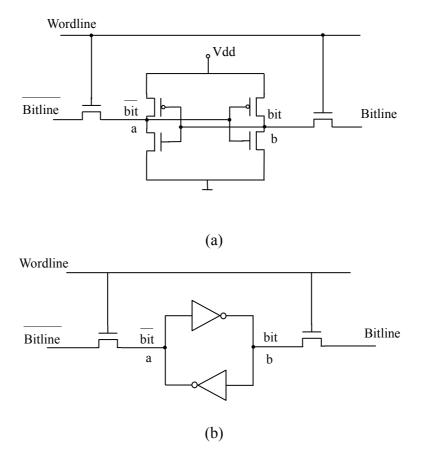

| Figure 8.1: Single SRAM cell hierarchy circuits, (a) transistor level and (b) transistor |

| - logic gate level                                                                       |

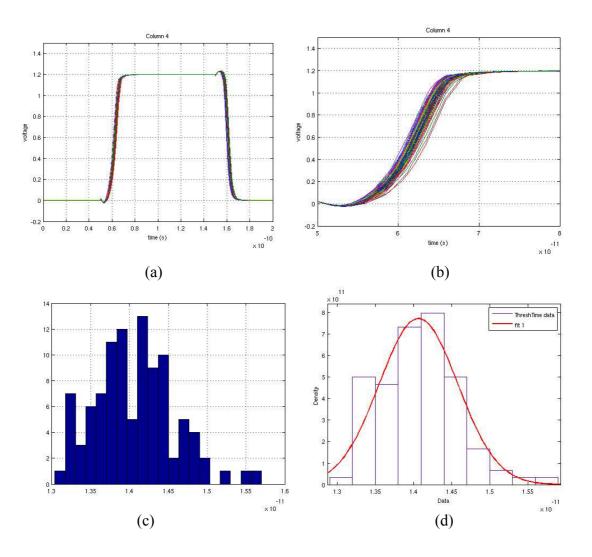

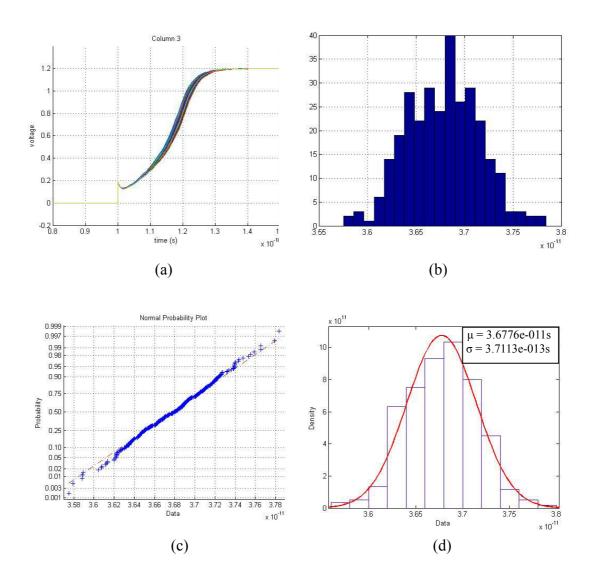

| Figure 8.2: Single transistor model SRAM cell 'write 1' delay MC simulation, (a)         |

| 'write 1' signal waveforms, (b) delay time distribution histogram, (c)                   |

| normal distribution evaluation, (d) Gauss fit and statistics obtained 174                |

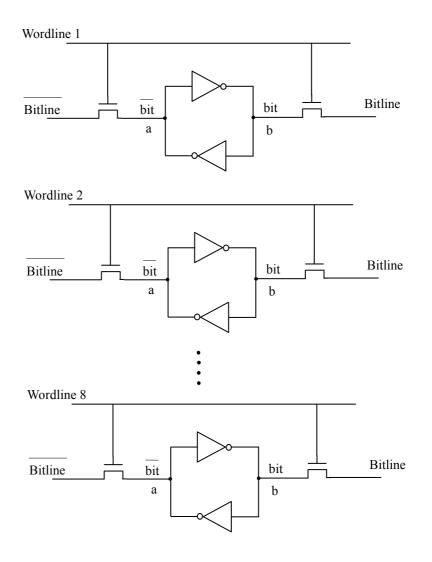

| Figure 8.3: SRAM8×1 array circuit                                                        |

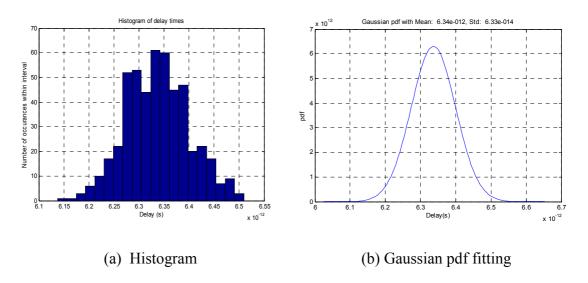

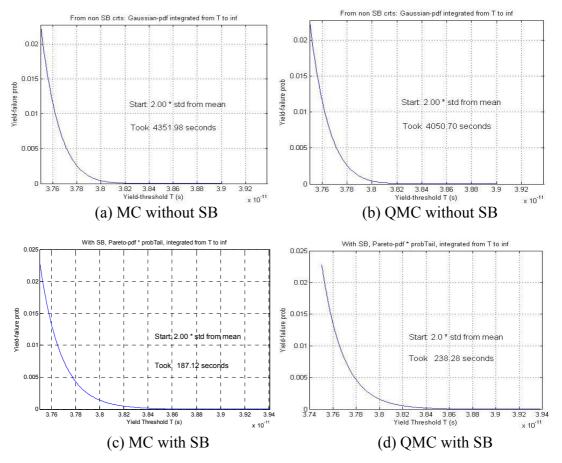

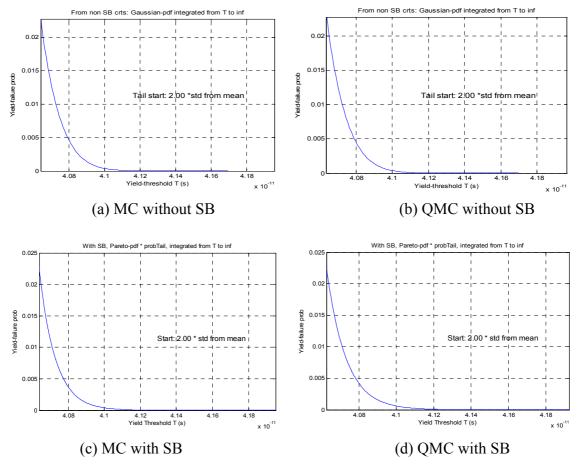

| Figure 8.4: Yield obtained from 3000 transistor level simulations of SRAM8×1 for         |

| strongly correlated case                                                                 |

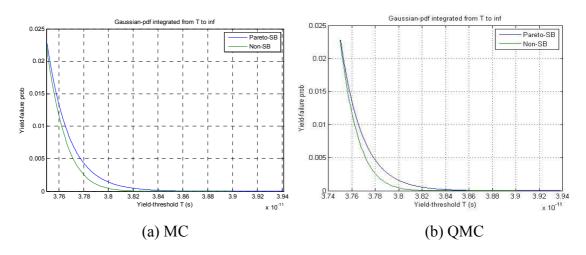

| Figure 8.5: Comparison of yield analysis results of SB and non-SB for transistor         |

| level SRAM8×1 simulations for strongly correlated case                                   |

| Figure 8.6: Yield obtained from 3000 transistor level simulations of SRAM8×1 for         |

| non-correlated case                                                                      |

| Figure 8.7: Comparison of yield analysis results of SB and non-SB for transistor         |

| level SRAM8×1 simulations for non-correlated case                                        |

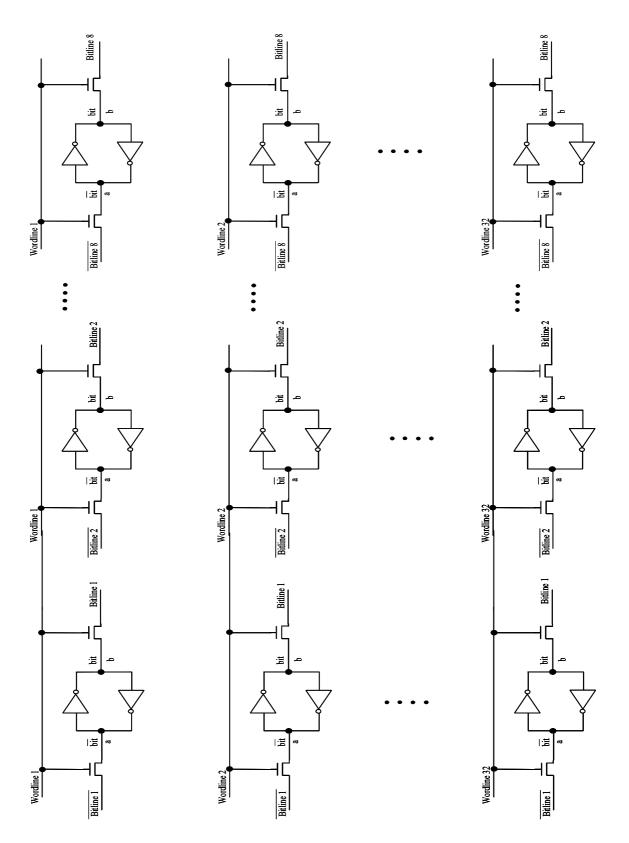

| Figure 8.8: SRAM32×8 array circuit                                                       |

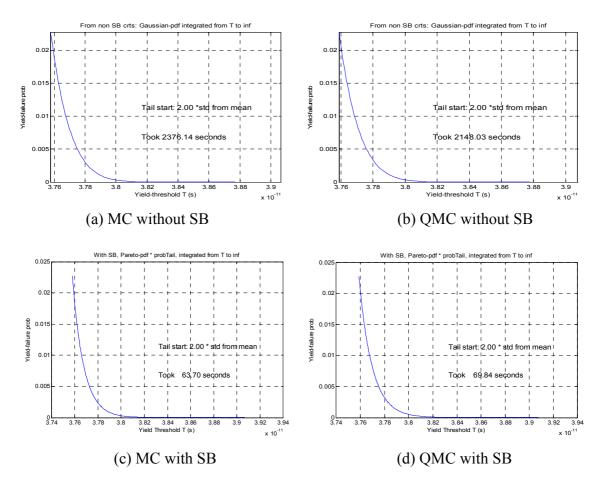

| Figure 8.9: Yield obtained from 3000 behavioural level simulations of SRAM32×8           |

| for strongly correlated case                                                             |

| Figure 8.10: Comparison of yield analysis results of SB and non-SB for behavioural       |

| level SRAM32×8 simulations for strongly correlated case                                  |

## Abstract

The intrinsic atomistic variability of nano-scale integrated circuit (IC) technology must be taken into account when analysing circuit designs to predict likely yield. These 'atomistic' variabilities are random in nature and are so great that new circuit analysis techniques are needed which adopt a statistical treatment of the variability of device performances. Monte Carlo (MC) based statistical techniques aim to do this by analysing many randomized copies of the circuit. The randomization can take into account correlation between parameters due to both intra-die and inter-die effects. A major problem is the computational cost of carrying out sufficient analyses to produce statistically reliable results.

The use of principal components analysis (PCA) and 'Statistical Behavioural Circuit Blocks (SBCB)' is investigated as a means of reducing the dimensionality of the analysis, and this is combined with an implementation of 'Statistical Blockade (SB)' to achieve significant reduction in the computational costs. The purpose of SBCBs is to model the most important aspects of the device's or circuit building block's behaviour, to an acceptable accuracy, with a relatively small number of parameters. The SB algorithm applies Extreme Value Theory (EVT) to circuit analysis by eliminating randomised parameter vectors that are considered unlikely to produce 'rare event' circuits. These circuits are needed for circuit yield failure predictions and occur on the 'tails' of Gaussian-like probability distributions for circuit performances.

Versions of the circuit analysis program 'SPICE' with a Python harness called RandomSPICE are used to produce SBCBs by generating and statistically analysing randomized transistor-level versions of the sub-blocks for which behavioural models are required. The statistical analysis of circuits employing these sub-blocks is achieved by a new MATLAB harness called RandomLA. The computational time savings that may be achieved are illustrated by the statistical analysis of representative circuits. A computation time reduction of 98.7% is achieved for a commonly used asynchronous circuit element.

Quasi-Monte Carlo (QMC) analysis with 'low discrepancy sequences (LDS)' is introduced for further computation reduction. QMC analysis using SBCB behavioural models with SB is evaluated by applying it to more complex examples and comparing the results with those of transistor level simulations. The analysis of SRAM arrays is taken as a case study for VLSI circuits containing up to 1536 transistors, modeled with parameters appropriate to 35nm technology. Significantly faster statistical analysis is shown to be possible when the aim is to obtain predictions of the yield for fabrication. Saving of up to 99.85% in computation time was obtained with larger circuits.

## Declaration

No portion of the work referred to in the thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and she has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://www.campus.manchester.ac.uk/medialibrary/policies/intellectualproperty.pdf), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses.

### Acknowledgements

I would like to express my thanks to my supervisor, Dr. Doug Edwards, for valuable guidance and support during my Ph.D. research and thesis writing. I especially appreciated the free research space Doug provided, which enabled me to develop my research interests in this interdisciplinary field.

Thanks also to the people of the Advanced Processor Technologies group for those inspiring and interesting seminars. The author acknowledges the financial support from EPSRC and the collaboration among the people of the Nano-CMOS pilot project – Meeting the Design Challenges of Nano-CMOS Electronics.

The encouragement and inspiration from my parents and family in China have been a major driving force and source of comfort.

Finally, and certainly not least, the encouragement, help and support of my husband Philip and my family in England are lovingly acknowledged as the source of any success this thesis brings. Without Philip, I could never have undertaken this work.

### **Chapter 1**

### Introduction

#### **1.1 Introduction to the Research Area**

Variability has always been a problem in electronic circuit design, especially in integrated circuit design. Anticipating the impact of variability on performance is a critical aspect of design procedures. Before nano-scale technology, the variability came mainly from imperfect control of the fabrication processes which caused device performance to vary from wafer to wafer, and from die to die within each wafer. This 'inter-die' variability could be assumed to have a global nature for each die and was catered for in the design process by making sure that the circuit would work when all the parameters of each of its devices were at the 'worst case' extremes of their anticipated values. The result of a circuit design procedure would therefore be analysed with the set of parameters for each copy of a given device, for example a MOS transistor, at the 'worst case corners' of possible values. The results from the analysis could then be used as feedback in an optimization process leading to the finalised circuit.

As technology scaling has reached the nano-scale region, variability in device performance within each die, that is 'intra-die' variability, is becoming a much more important consideration in the design of integrated circuits [1]. Now that CMOS technology has reduced gate sizes to 90nm and below, and some dimensions are approaching atomic scales, intrinsic atomic scale variations such as line edge roughness and dopant granularity have become the main sources of variation [2]. Those 'atomistic' variabilities are random in nature and result in random 'within-die' fluctuation which cannot be disregarded. The potential variations are so great that traditional variability analysis, based on 'worst case' corner-models [3] and guard-bands for parameter variations, is likely to be very pessimistic in its estimations of the effects of the variability. Consequently, new circuit analysis techniques are needed which adopt a statistical treatment of the intra-die variability of device performances.

As the significance of process variations has grown with decreasing device sizes, it has become clear that traditional design methodologies, both for analysis and optimization, are no longer acceptable [3]. This has led to much interest in statistical modelling techniques that can be used to enable statistical analysis and optimization. Statistical analysis can take into account parameter variation on all portions of a design in a single comprehensive computational procedure, allowing the impact on yield to be efficiently estimated.

Because of the high dimensionality of the parameter space, it is very difficult to derive analytical models of large scale ICs for analysis. Sets of ordinary or partial differential equations describing specific circuit performance parameters, like timing or yield, in terms of the huge number of parameters would be very difficult to derive analytically. Therefore the use of conventional statistical methods, based on the analysis of such equations, has restricted applicability for the variability analysis of nano-scale ICs. With Monte Carlo simulations, the integrated circuits are simulated directly, and there is no need to derive differential equations that describe the dependency of the properties of interest on circuit parameters. The only requirement is that the circuit properties that are to be modeled are capable of being described by probability density functions (pdf's) that are dependent on the pdfs of circuit parameters and input variables. Monte Carlo simulation proceeds by generating a random sample of the value of each circuit parameter and input variable, based on the known pdf's. It then simulates the circuit thus obtained, using a package such as SPICE, to compute a random sample of the circuit property of interest. The process is repeated many times to obtain a sequence of samples of the property of interest from which statistical models can be derived. For example, the shape of the

property's pdf may be inferred and its mean and standard deviation can readily be derived, assuming there are sufficient observations. In some cases the circuit parameters may be assumed to be statistically independent; meaning that there is no correlation between the samples of one circuit parameter and any other. This assumption may be reasonable for some aspects of atomistic variations. However, there is good reason to believe that the variation that occurs in each component will be to some extent correlated to that of other devices on the same IC especially when they are close to each other. The effect of this correlation is 'intra-die' variation which must be given consideration.

Monte Carlo analyses are particularly suitable to nano-scale IC statistical simulation to achieve statistical estimates of properties of interest. Conclusions may be drawn that are representative of the true behaviour of the circuit. To quantify these conclusions, statistical averages may be produced based on many randomised examples. The statistical reliability of the conclusions generally improves as the number of examples increases, though the rate of improvement can often be increased by carefully choosing the examples. For such applications, MC techniques are simple, flexible, robust and scalable to exceptionally large numbers of parameters. In principle, they allow arbitrary accuracy given sufficient computation. The statistical distribution of circuit performances in response to carefully randomised vectors of device parameters may be used for estimating anticipated circuit yield, failure probability and other performance measures.

A major problem is the computational cost of carrying out sufficient simulations to produce statistically reliable results for all but the most trivial circuits. For circuit simulation at transistor level, each transistor model may have many parameters and there may be a large number of transistors in the circuit or sub-circuit being simulated. A very large number of MC analyses may be required because of the large number of parameters.

#### **1.2 Research Motivation and Context for This Project**

The research motivation and context for this PhD project is the EPSRC pilot project:

'Meeting the design challenges of nano-CMOS electronics' [7]. The aim of the pilot study is to propose new design styles that cope better with device variability. We aim to demonstrate that it is possible to produce circuit designs that are optimized or improved in their suitability for sub-45 nanometre technology by using statistical models of variability, and that the computation costs required for the statistical analysis can be made feasible.

There are five university partners working on the development of various elements of statistical simulation using approaches which will be suitable for grid implementation. Their efforts are interlinked [7]. The Device Modelling Group of Glasgow University focus on process and device simulation. One outcome of their work so far is the RandomSPICE package which is used in this PhD project. The Microsystems Technology Group of Glasgow University develop integrated circuit/device simulators, circuit level compact models and parameter extraction strategies. Their results include the sets of randomized mosfet parameters that are used by the RandomSPICE circuit randomization process. The Electronic Systems Design Group of Southampton University produce behavioural models for standard cell libraries. Their work will be studied to find accurate ways of producing low complexity models of sub-circuits with parameters that may be randomised from knowledge of their statistical properties, as extracted by RandomSPICE analyses. The Mixed-Mode Design Group of Edinburgh have been developing techniques for circuit-level noise simulation, and the Intelligent System Group of York University have developed evolutionary circuit and system design techniques.

The Advanced Processor Technology of Manchester University group has traditionally focused on the development and use of statistical analysis tools for use in the design and optimization of asynchronous (self-timed) circuits and chip multiprocessors. This has led us to investigate new design techniques that cope better with device variability and reliability. To be able to do this, we firstly need to investigate how to estimate the likely effect of the parameter variations predicted by device level models on the performance of clocked and self-timed implementation styles. Then we can consider how the ability to obtain these estimates can be used to improve future synthesis tools for nano-scale ICs.

#### **1.3 Research Approach**

Statistical variability analysis has been available in the commercial package 'HSPICE' for some time. HSPICE offers an approach to MC simulation that is professionally designed and well adapted to the demands of commercial manufacturers and circuit design companies. However it does not cater for all the computation reduction techniques we wish to investigate (e.g. Statistical Blockade) and is not ideally suited to a research project because it implements proprietary approaches and does not have the flexibility needed to investigate new research ideas. NGSPICE is a mixed-signal (analogue and digital) circuit simulator combining three open source software packages: SPICE3, Cider and Xspice. It is under continuing development as part of the 'gEDA' project [37] for developing a full GNU public licensed suite of electronic circuit design (EDA) tools. It did not have any MC simulation facilities when this project began, though rudimentary ones have very recently been introduced in version 23 which was released in June 2011 [37]. Researchers are still contributing to the 'gEDA' project, and it is intended that the work in this thesis will be relevant to the project. The same analysis engine is the basis of many different versions of SPICE including HSPICE and NGSPICE.

A software package called 'RandomSPICE' [14] was employed initially for the randomization process, though an early objective was to adapt this and eventually to develop a new randomization package called "RandomLA" (Randomisation for LSI). A major consideration was the need to perform the simulations and analyses with reasonable computation and to allow the use of parallel computation as provided by MATLAB and CONDOR [39] [40] for circuits of realistic complexity. Hence the need for a variety of complexity reduction techniques and the use of NGSPICE are explored and evaluated in the thesis.

#### **1.4 Research Hypothesis**

The research hypothesis is that it is possible to analyse circuit designs for sub-45 nanometre technology by the use of SPICE simulation with statistical models of

variability with computation cost significantly reduced from that required if traditional MC methods are employed.

#### **1.5 Introduction to the Methodology**

The tools developed by this project may be described as forming a test-harness which allows SPICE simulation to be used for particular forms of statistical analysis, based on the SPICE simulation of many randomised copies of a circuit. The randomisation must be capable of reflecting both intra-die and inter-die variation of devices and other circuit components such as wires. Intra-die transistor parameter variation can be based on published measurements of devices as provided by manufacturers or researchers. Alternatively, the results of 3D device modelling as carried out by our collaborators in Glasgow University [20] may be used. Applying principal components analysis (PCA) to such sets of representative parameters reduces their dimensionality and provides a convenient way of introducing intra-die correlation. The subsequent computation reduction methods to be investigated in this thesis are the use of behavioural modelling, a technique known as 'Statistical Blockade' based on published ideas of 'extreme value theory' [15], and quasi-random parameter variation with the use of 'low discrepancy sequences'.

#### **1.5.1 Behavioural Modelling**

The use of 'behavioural' or 'functional' models of sub-circuits derived by previous statistical analysis of the sub-circuit separately has great potential. For example a behavioral NAND gate model could consist of four 'look-up table' switches each with a statistically variable 'Tau model' of delay [16]. SPICE switches are dependent sources (such as voltage-dependent current sources) whose input-output relationships may be defined by simple look-up tables. These cannot implement delay. However, a simple Tau model which introduces a single RC time-constant can introduce delay, but with a characteristic exponential rising or falling RC wave-shape that may not be appropriate. The true switching behaviour of each gate output, may be therefore modeled by a combination of the switch and the Tau model, with the look-up table

elements optimized (by a simple MATLAB procedure within the harness) to match the RC waveform to the required switching waveform. This simple approach is well suited to the computational methods adopted by SPICE and the demands of simulating asynchronous circuits whose behaviour relies on many 'C-elements' switching at slightly different instants of time. C-elements are widely used asynchronous logic components with a highly non-linear bistable operation. The approach is complementary to the behavioral modelling proposed by Southampton University [7].

#### **1.5.2 Statistical Blockade**

Extreme value theory (EVT) offers statistical methods for analysing the behaviour of systems in situations that rarely occur. Such analysis is clearly problematic with traditional MC techniques which require a large sample, therefore extensive computation, for rare events to be observed. The Statistical Blockade (SB) algorithm applies Extreme Value Theory (EVT) to circuit analysis by eliminating randomised parameter vectors that are considered unlikely to produce rare event circuits. In our application, the rare events are the circuit yield failure predictions which are extreme in the sense that they are on the 'tails' of Gaussian-like probability distributions for circuit performances. Since they are designed to be rare, reliable estimates of these failures by conventional MC techniques require very large numbers of randomised input vectors. SB performs 'biased' or 'partial' sampling of the performance distributions which is the basis of EVT. Many input vectors are generated, but only the ones likely to produce 'rare events' are simulated. The process requires a classifier which, in this thesis, will be implemented as a 'least squares' trained linear estimator combined with a threshold comparator. After a period of initial training, the classifier can be trained recursively as the simulation proceeds. The computational complexity involved in introducing the bias, and compensating for it, is much less expensive than performing lots of uninteresting circuit simulations.

#### 1.5.3 Low-Discrepancy Sampling with Quasi MC Methods

The term 'Quasi Monte Carlo' (QMC) describes Monte Carlo methods where the input vectors are not totally random, but are to a degree deterministic in that they conform to 'low-discrepancy sequences' [15][21][36]. A low discrepancy sequence is a sequence of N-dimensional vectors which covers a finite space more uniformly than is achieved by N-dimensional vectors of independent uniformly distributed random elements. It is known that the use of low discrepancy vector sequences can achieve significant speed gains over standard Monte Carlo integration techniques by reducing the number of input vectors needed for a given accuracy [17]. Similar gains are anticipated when QMC is used for statistical circuit simulation.

#### 1.5.4 Originality

All the techniques introduced above are generally well known and have previously been applied in some form to circuit simulation. The originality here is in the way we have applied them and the evaluation and insight that has resulted. Although the principles may be known, the implementation of them has required some innovation such as:

- (i) The application of PCA to the introduction of correlation.

- (ii) The combination of optimized Tau models and 'look-up table' switches in behavioural modelling.

- (iii) The implementation of recursive SB using 'pseudo-inverse' least squares optimization.

- (iv) The application of 'SOBOL' LD vector sequences to SPICE simulation (though others have been used) and to SB classifier training and the implementation of recursive SB.

#### 1.5.5 Software Development

This work has resulted in the development of four phases of a MATLAB harness for SPICE called RandomLA (LSI circuit analysis) and some supporting MATLAB programs not yet integrated into RandomLA. The harness works equally well for

HSPICE and NGSPICE and is adaptable to a parallel implementation. The four phases of RandomLA are:

RandomLA-Nonblockade (either MC or QMC) RandomLA-Training (either MC or QMC) RandomLA-Evaluation (either MC or QMC) RandomLA-RecursiveSB (either MC or QMC)

All of these versions implement both MC and QMC (with 'Sobol' sequences) will allow correlation to be introduced, based on PCA, to model intra-die variation. All the results presented were generated by these scripts apart from some of those in Chapter 4 which required the use of RandomSPICE.

#### **1.5.6 RandomSPICE**

RandomSPICE is a randomisation package developed by collaborators in the EPSRC nano-CMOS project [7]. Currently it is supplied to collaborators with two transistor models, an nmos and a pmos transistor representing a 35nm technology by Toshiba. The parameters of each model have been randomised to produce 200 copies, where the variations from copy to copy are based on the results of three-dimensional atomistic simulations [18]. The geometrical and quantum physics based simulations were carried out [20] to reflect the statistical nature of 'atomistic' variations due to, for example, the effects of random discrete dopant levels, line edge roughness and oxide thickness variations as would be expected to occur from device to device on a single die. Therefore these are intra-die variations. They are intending to reflect truly what will be observed in real circuits. Intra-die correlation between the parameters of adjacent devices should be taken into account.

#### **1.6 Research Aims and Objectives**

The aims of this thesis are to reduce the computational complexity of traditional Monte Carlo (MC) methods for modelling the effects of variability in deep submicron CMOS circuits, and to enable a deeper understanding of these effects.

The first objective was the design and implementation of a statistical simulation

method, capable of predicting the effect of parameter variations on the performance and yield of a nano-CMOS circuit, by using traditional MC methods with facilities for including the effect of inter-die and intra-die correlation in the variability. To allow the research to be disseminated in reproducible form, all software was required to be compatible with 'NGSPICE' and the associated GNU public licensed suite of electronic circuit design (EDA) tools. The software was required to be suitable for distributed or parallel computation.

The second objective was to investigate dimension reduction techniques for MC simulation, focusing on the use of Principal Components Analysis (PCA), and the use of behavioural modelling for replacing device level analogue sub-circuits by computational simpler circuit models.

The third objective was to investigate two further computation reduction methods which are a technique known as 'Statistical Blockade' based on published ideas of 'extreme value theory' [15], and the use of Quasi MC techniques based on the use of 'low discrepancy sequences' [98] [99] [123]. It was required to be discovered to what extent computation reduction can be achieved by these two methods both individually and in combination.

All three objectives were approached within the context of the aims stated above, and were designed to achieve the greater understanding and reduced computational complexity required, with illustrations of what is achievable.

#### 1.7 Structure of This Thesis

This thesis contains nine chapters. The first is an introduction to the general research area and the research aims. It defines the problem and some terms. The context, research hypothesis, aims and objectives are stated with a brief introduction to the methodology. Finally, the structure of the following chapters is surveyed.

The second chapter is a background and literature survey covering the sources and classifications of variability. A discussion of the effect of variability on clocked and self-timed circuits is included.

Chapter 3 describes the current state-of-the-art in statistical simulation

techniques for current and next generation integrated circuits. The widely used design tools provided by Synopsis (HSPICE), Cadence (Encounter) and NGSPICE are discussed. Their relevance to IC design and simulation is explained with some examples.

Chapter 4 deals with the use of Monte-Carlo (MC) techniques for the statistical analysis-by-synthesis of nano-scale technology. The existing MC features of HSPICE and the randomization package called RandomSPICE, which is one of the outcomes of the EPSRC Pilot project [7], are outlined and considered for adaptation to the requirements of this PhD project. The reasons for adopting NGSPICE with a new harness called RandomLA, are outlined. Some of the basic features of RandomLA are discussed and the use of traditional MC simulation using RandomSPICE and RandomLA is illustrated with a sample circuit.

Chapter 5 discusses two method of reducing the dimensionality of the input parameter space to achieve computational efficiency in MC simulations. The first of these, principal components analysis (PCA), also provides a convenient way of introducing intra-die correlation between parameters. The second method introduces the use of statistical behavioural circuit blocks (SBCB) which substitute functional but computationally simpler circuit models for device level analogue sub-circuits

Chapter 6 introduces the concept of Extreme Value Theory (EVT) and explores an algorithm known as 'Statistical Blockade' (SB) [28] which applies EVT to statistical circuit analysis by eliminating or 'blocking out' randomised parameter vectors that are classified as being unlikely to produce circuits that fall in the lowprobability tails of the distributions of measurements of interest. The potential for using this technique to achieve major computational savings is explored and illustrated by examples.

Chapter 7 investigates the use of Quasi Monte Carlo (QMC) techniques and 'low-discrepancy' sampling to achieve further efficiency improvements, over what was achieved in earlier chapters, with Monte Carlo circuit simulation. The effect of using a 'Sobol' low discrepancy sequence generator to replace the uniformly distributed pseudo-random number generator previously used to produce the required Gaussian variation is discussed and illustrated by example.

Chapter 8 evaluates the results obtained with VLSI SRAM circuits. This chapter considers the significance and reliability of the results obtained, how to decide how many randomized circuits are needed and how best to populate the transistor model sets, taking advantage of QMC and PCA.

Chapter 9 presents conclusions and suggestions for further work in this area. The use of parallel processing for efficiently undertaking the intensive computation required will be discussed, taking into account the intrinsically parallel nature of massive Monte Carlo simulations.

### **Chapter 2**

## Nano-CMOS Technology and the Causes and Effects of Variability in Integrated Circuits

#### 2.1 Introduction

The International Technology Roadmap for Semiconductors (ITRS) [8] and Moore's Law [9] demonstrate how progressive scaling of CMOS integrated circuit technology has driven the phenomenal success of the semiconductor industry in delivering larger, faster and cheaper integrated circuits. Scaling is measured in terms of the size of each 'metal–oxide–semiconductor field-effect transistor' (MOSFET) on the integrated circuit; specifically the length of the silicon channel between the source and drain terminals of the MOSFET which would, for example, be 90 nm in '90 nm CMOS technology'. Considering the current status of nano-CMOS technology, integrated circuits with 45nm MOSFETs have been in mass production for some time and circuits with sub-10nm MOSFETs are expected to be available in 2016. This is well ahead of the 2006 version of the ITRS road-map [8] which predicted that 22nm devices would be scheduled for production only in 2018. Further, 4 nm transistors have already been demonstrated experimentally, highlighting silicon's potential for scaling beyond the end of the current ITRS prediction [7].

Size reduction of MOSFETs brings several advantages, such as the ability to pack more and more transistors into a given area of silicon, which results in more functionality per unit area. In fabricating chips of a certain complexity, smaller integrated circuits are therefore required and more chips per wafer can then be fabricated. Since the cost of wafers remains more or less constant, this reduces the price per chip. It may also be expected that smaller transistors can be made to switch faster.

The main device dimensions of MOSFETs are the transistor length, width, and the oxide thickness. One approach to size reduction is a scaling that requires all device dimensions to reduce proportionally. In older technologies, if each of these dimensions was scaled by a factor of 0.7, the transistor channel resistance would not change, while the gate capacitance would reduce by a factor of 0.7. Hence, the RC time-constant which determines the delay of the transistor would reduce by a factor of 0.7. In more recent technologies, this proportionality relationship does not apply and the effect of scaling is rather more complicated. Some of the complications in scaling state-of -the art MOSFETs arise because of the delay due to interconnections.

Along with the advantages gained by reductions of size, some difficulties also arise. MOSFETs whose sizes are below a few tens of nanometers create operational problems, since they tend to have higher sub-threshold conduction, increased gateoxide leakage, increased junction leakage, lower output resistance, lower transconductance, interconnect capacitance, heat production and process variations.

When integrated circuits are fabricated, the dimensions and characteristics of the MOSFETs will not be exactly as assumed in the design process and there will be variations from device to device arising from many different sources. As MOSFET sizes become smaller, these variations have a more and more significant effect on the overall behaviour and viability of circuits. They may cause a particular design of MOSFET to be unusable, hence new device architectures may have to be devised. Also, the variations in device parameters that will be observed after fabrication must be anticipated by the design process. In large-scale circuits, they are too complex to be considered in a deterministic manner and therefore the variability must be modeled by appropriate statistical processes.

Variability in the characteristics of fabricated devices, and the need to introduce new device architectures, are vital considerations for the current and the next generations of nano-CMOS based integrated circuits. Fundamental changes in the way these integrated circuits and systems are designed are now necessary. Adapting to new device architectures and the variability of fabricated device characteristics will increase the complexity of integrated circuit design processes. For example, statistical models of the intrinsic parameter variations which cause devices on integrated circuits to behave differently from the manufacturer's specification, and from each other, must be used. Failure to accommodate these manufacturing tolerances will challenge the achievable power efficiency, yield and reliability of digital circuits.

In the EPSRC pilot project: 'Meeting the design challenges of nano-CMOS electronics' [7], the APT (Manchester) group's role is to study new design styles that cope better with device variability and reliability. To be able to devise new design styles, we firstly need to investigate how the parameter variations predicted by device level models will affect the performance, power requirements and area of clocked and asynchronous implementation styles, what this will imply for digital microelectronics design, and how these results will affect future synthesis tools.

#### 2.2 CMOS Technology for Integrated Circuits

#### 2.2.1 MOS Transistors

MOSFET transistors are the main building blocks used to design large scale integrated circuits, both analogue and digital. The traditional metal-oxidesemiconductor (MOS) structure which can fabricate a field effect transistor (FET) consists of a layer of silicon-dioxide sandwiched between a layer of metal on top and the semiconductor substrate below, as illustrated in figure 2.1. The silicon-dioxide acts as an insulator, and only a very thin layer is required, often with the thickness of a few hundred molecules. 'Polysilicon gate' FET's, with highly conductive polycrystalline silicon layers replacing the metal layers, are nowadays used in place of traditional MOSFETs, though they are generally still referred to as MOSFETs. Metal and polysilicon FETs are more correctly referred to as 'insulated gate field effect transistors' (IGFETs).

Chapter 2. Nano-CMOS Technology and the Causes and Effects of Variability...

Figure 2.1: MOSFET structure

The transistor has a "source" and "drain consisting of semiconductor material which has been modified by being "doped" with a different type of material than exists in the region under the gate. The metal or conducting polycrystalline material forms the "gate". An NPN or PNP type structure exists between the source and drain regions and electrical current can flow from the source to the drain depending on the degree and polarity of a charge applied to the gate. Figure 2.2 shows two types of MOSFET :

(a) "N-channel" where the source and drain regions have been doped with N type material and the substrate has been doped with P-type material.

(b) "P channel" where the source and drain regions have been doped with P type material and the substrate has been doped with N-type material.

Figure 2.2: Two types of MOSFET.

When either type of MOSFET is operating within a circuit, the source must be connected to a supply of charge carriers which travel towards the drain. For an N channel MOSFET, the source voltage must be negative with respect to the drain voltage to allow charge to flow. For a P-channel device, the source must have the more positive voltage to allow current to flow. The area under the gate is the "channel" through which the current flows.

Either type of MOSFET can be made to act as a switch. Figure 2.3(a) shows an N-channel MOSFET with N-type source and P-type substrate connected to ground and drain connected to a positive voltage  $V_{DD}$ . There are two reverse-biased PN junctions between the two N wells and the substrate, therefore no current can flow and the MOSFET is turned off.

Figure 2.3: Enhancement mode MOSFET (a) turned off, (b) turned on

If a positive charge is applied to the gate as shown in Figure 2.3(b), electrons will be attracted from the substrate into the channel region between source and drain. If the positive charge is enough, sufficient electrons will be attracted into the channel to ensure that there are more electrons than 'holes'. Then the channel will become N-type rather than P-type, current will be allowed to flow from source to drain and the MOSFET will have been turned on. The minimum gate voltage needed to ensure that the gate has sufficient charge to attract enough electrons to allow current to flow is the "threshold voltage"  $V_{th}$ . This is an N-channel "enhancement mode" MOSFET because the charge is applied to the gate to enhance the channel conduction. A P-channel enhancement mode MOSFET has P-type source and drain and an n-type substrate. The conduction in the channel is now induced by applying a negative voltage between gate and substrate to create a negative charge and thus attract P-type

charge carriers (holes) into the channel. CMOS technology is based on the use of both N-type and P-type enhancement mode MOSFETs.

"Depletion mode" MOSFETs acting as normally closed switches, are feasible, but not used in CMOS designs. Figure 2.4 shows an N-channel depletion mode MOSFET.

Figure 2.4: Depletion mode MOSFET: (a) turned off (b) turned on

A thin layer of semiconductor immediately beneath the gate oxide is doped with the same type material as the source and drain. Current can flow across the channel when no charge is applied to the gate, but when a negative charge is applied, the electrons beneath the gate oxide will be repelled leaving no free charge carriers. Therefore conduction will cease and the transistor turns off. P-channel depletion layer MOSFETs can similarly be fabricated. Depletion mode MOSFETs are commonly used as resistors rather than switches. A permanently "on" transistor, has a much higher resistance than doped semiconductor material, and the value of resistance can be determined simply by its dimensions or the number of ions which are implanted in the gate region.

Both enhancement and depletion mode MOSFETs are used in IC design. Conventional NMOS technology uses both enhancement and depletion mode devices; the former as switches and the latter as resistors. CMOS technology uses enhancement mode MOSFETs. Chapter 2. Nano-CMOS Technology and the Causes and Effects of Variability...

#### 2.2.2 MOS Transistor Models

The design and analysis of ICs requires complex devices such as MOSFETs to be represented by circuits consisting of simpler elements. These are models which are needed for the design of the devices themselves as well as the circuits they populate. The design of devices requires the use of 'process models' which reflect how manufacturing processes such as ion implantation, oxide growth, impurity diffusion, etching and annealing affect their characteristics. Process models translate the device "geometry" into circuit parameters. The effects of readily identified geometrical features and also details such as the doping profiles must be accurately represented.

Transistor models used for circuit design are called "compact models" because ideally they should use as few circuit elements as possible to keep the analyses as simple and computationally efficient as possible.

Enhancement mode MOSFETs can be modeled as simple switches which are on or off, in effect acting as variable resistors controlled by capacitor charges. More sophisticated models can be used, but this simple approach is useful for logic verification and approximate timing simulations.

Many important aspects of the performance of modern integrated circuits are difficult to predict without accurate models of the devices used and their interconnections. Ideally, the models must take into account the circuit layout: length, width, interdigitation, proximity to other devices; transient and DC currentvoltage characteristic; parasitic device capacitance, resistance, and inductance latencies and temperature effects. For digital design, large-signal non-linear models are required which may be classified as 'physical', 'empirical' or 'tabular' models.

Physical models are based on device physics and the approximate modelling of physical phenomena within a transistor. Parameters are physical properties such as oxide thicknesses, substrate doping concentrations, carrier mobility, etc. The complexity of modern devices often makes physical models too computationally complex for circuit design purposes.

Empirical models are based on curve fitting to produce functions that recreate known responses to particular stimuli and interpolate this behaviour appropriately for

32

any given stimuli. An empirical model need have no physical basis and can be considered in purely mathematical terms.

Tabular models use look-up tables containing large numbers of values for common device parameters such as drain current and device parasitics. The use of tabular models can greatly reduce the computational complexity of analysis and simulation software. They can work well in operating conditions whose parameters may be interpolated from entries within the table. However, they tend to be unreliable for operating conditions whose parameters fall outside the table and require extrapolation.

Commercial programs for simulating the behaviour of MOS integrated circuits generally offer a wide range of different transistor models, often with many parameters. The SPICE circuit simulation program [82] is probably the most widely used. The transistor models in SPICE are a hybrid of physical and empirical models. Such models require a specification of how their parameters are to be obtained for real devices, since there is the danger that totally inappropriate parameters can be made to fit measured data for given devices resulting in quite unsuitable models for interpolating or extrapolating the data.

As devices become smaller, new models are needed to accurately represent their behaviour. Simulation packages such as SPICE are continually introducing new device models. A working group called the Compact Model Council [43] has been set up to try to standardize such models across different simulators. This group must consider how the next generation of devices will work by identifying technology trends and motivations. The aim must be to have models available before the devices themselves become available. The BSIM models, developed at U. C. Berkeley already provide such standardized models which include BSIM3, BSIM4, and BSIMSOI.

The BSIM (Berkeley Short-channel IGFET Model) [42] is a family of MOSFET models suitable for integrated circuit design, analysis and simulation. The models represent current flow and capacitance as functions of the control voltages on gates, sources, drains and substrate and other parameters which include channel dimensions and operating temperature. The models are claimed to have features that improve the Chapter 2. Nano-CMOS Technology and the Causes and Effects of Variability...

convergence rates and accuracy of circuit simulations. They are compact semiempirical models [47] comprising sets of equations originally derived from physical analysis though subsequently modified empirically to better match available measured data. A 'two-stage' modelling approach is used which first pre-processes the various temperature and device geometry specifications to produce circuits whose elements are suitable for a circuit simulator such as SPICE, and then computes the required component values for such circuits. For each semiconductor manufacturing process, a single geometry-independent parameter set allows the circuit simulator to adapt the model to the dimensions of particular devices. The geometry-independent BSIM parameter sets are therefore functions of the semiconductor processing only and are referred to as "process" models. The actual parameters are extracted using an automated test and data analysis system which provides the means of acquiring large amounts of parameter data as required for statistical modelling of integrated circuit variability. Software which performs cycles of testing and with parameter extraction calculations was developed at U. C. Berkeley [48].

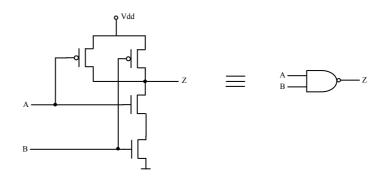

#### 2.2.3 CMOS Logic

N-channel MOSFETs are smaller than P-channel MOSFETs and producing only one type of MOSFET on a silicon substrate is cheaper and technically simpler. NMOS logic uses N-channel MOSFETs exclusively but has the disadvantage of consuming power even when no switching is taking place. In principle, "complementary" MOS (CMOS) logic gates only consume power when switching and have the further advantage over NMOS that both low-to-high and high-to-low output transitions are faster since the load resistors in NMOS logic are replaced by pull-up transistors which have low resistance when switched on. In addition, the output signal swings the full voltage between the low and high rails. This strong, more nearly symmetric response also makes CMOS more resistant to noise. CMOS logic has, since the mid 1980s, displaced NMOS to become the preferred technology for digital ICs.

A CMOS gate has a pull-down circuit of N-MOSFETs for connecting the output

Chapter 2. Nano-CMOS Technology and the Causes and Effects of Variability...

to "0" (GND) and a pull-up circuit of P-MOSFETs for connecting the output to "1"  $(V_{DD})$ , as shown in Figure 2.5. One circuit is intended to be ON while the other is OFF. Two or more MOSFETs in parallel are ON if any one of them is ON. Two or more MOSFETs in series are ON only if all of them are ON. CMOS logic gates can be constructed by using appropriate combinations of parallel and series MOSFETs in each circuit. A CMOS inverter, for example, has a 'pull-up' circuit consisting of one P-MOSFET, and a pull-down circuit with one N-MOSFET. The output of a CMOS logic gate can be in four states as summarised in table 2.5. The "1" output level occurs when the pull-up circuit is on with the pull-down off, and vice versa for the "0" output level. When both pull-up and pull-down circuits are OFF, the output level becomes indeterminate or 'floating' with only a very high-impedance connection to the input. This is referred to as the 'floating Z' output state and is used in multiplexers, memory elements, and bus drivers. When both pull-up and pull-down circuits are simultaneously turned ON, an indeterminate level again results but with power being dissipated. This 'crowbarred X' condition is avoided as much as possible in a CMOS gate.

|               | pull-up OFF | pull-up ON     |

|---------------|-------------|----------------|

| pull-down OFF | Z           | 1              |

| pull-down ON  | 0           | Crowbarred (X) |

Figure 2.5: General logic gate using CMOS pull-up and pull-down networks

#### 2.2.4 CMOS Circuit Design

Particular logic functions can often be implemented with many different combinations of AND, OR and other gates. When designing ICs, there are many aspects other than the correct logical operation to consider. For example, the fan-in and fan-out of each gate, and the transistor sizes to be used, must be decided. Such decisions affect the speed, power consumption, area and many other potentially important characteristics of the IC being designed.

Logic circuit design tools can make these decisions automatically. Such tools can search through available libraries of logic cells for the best implementation. The resulting circuits are often quite acceptable. However, when there are critical requirements, maybe for low power consumption or high speed, customised circuit design may be needed for the whole IC or for critical portions of it. Customised design effort can also be cost-effective as a means of reducing the surface area required for ICs that are expected to be manufactured in large volumes.

Figure 2.6(a) shows a logic circuit for the Muller C-element. Implementing a non-customised 'gate level' design would require 26 transistors and four stages of gate delay, since the AND and OR gates would be implemented by library cells each consisting of a NAND or NOR gate followed by an inverter. The 'transistor level' design in Figure 2.6(b) requires only 10 transistors and two stages of gate-delay. This example illustrates the advantages to be gained by customised design, at transistor level, based on a direct knowledge of the properties of CMOS technology.

Figure 2.6: Muller C-element: (a) gate-level, (b) transistor-level

Either of the schematics in figure 2.6 may be converted to a 'netlist' description using 'HDL (hardware description language)' terminology which caters for 'gatelevel' and 'transistor-level' schematics. A gate-level netlist is a technologyindependent structure description, because standard logic gates may be referred to without the need to specify the implementation technology. The electrical characteristics of the gates, speed, fan in, fan out etc. are not yet part of the description. At transistor level, a circuit description will include this type of information and specify the size of the transistors and the levels of stray capacitance. However, the Verilog HDL language was designed primarily as a gate-level language and is not well suited to transistor level descriptions.

The circuit simulator SPICE uses another common structural language whereby internal models represent the electrical characteristics of the MOS devices. SPICE calculates appropriate values of, for example parasitic capacitance inherent in the MOS transistor, using parameters such as device dimensions that are specified in the netlist. Capacitance, resistance and other phenomena can be introduced independently from the transistor models by including appropriate statements in the SPICE netlist. Thus additional routing capacitance and resistance can be included to accurately model the physical characteristics of the circuitry for each gate and the interconnections between gates. The SPICE netlist has all the information necessary to fully characterize a transistor level circuit description, in terms of its speed, power, and connectivity.

#### 2.2.5 CMOS Technologies

Complementary MOS (CMOS) gates employ both P and N channel MOSFETs to allow a signal which turns *on* one transistor to turn off another. This eliminates the need for pull-up resistors and the power they would dissipate. Figure 2.7 shows a CMOS inverter and its switch equivalent.

Chapter 2. Nano-CMOS Technology and the Causes and Effects of Variability...

Figure 2.7: A CMOS inverter and its switch equivalent

The substrate for the N-channel device is connected to ground, while that for the P-channel device is connected to the positive voltage supply. Figure 2.8 shows the arrangement of channels for an IC implementation of the inverter.

Figure 2.8: CMOS inverter in cross-section

In principle CMOS gates consume no power when not changing state since there is no resistive path to ground. Outputs can be made symmetrical in the way they switch from 0 to 1 and vice-versa, by making the pull-down and pull-up resistances of the N-channel and P-channel transistors equal. This will equalize the delays for each direction. CMOS technology is more complex than NMOS since it requires two different types of transistor to be fabricated on a single substrate.

## 2.2.6 MOSFET Scaling and the Adaptations on Design

The ITRS Roadmap [8] forecasts a major new technology generation every three years. Each new generation is expected to double the number of transistors per unit

area and increase their operation speed by a factor S equal to the square root of two. Constant field scaling by the factor S multiplies channel length, width, oxide thickness, supply voltage and all threshold voltages by 1/S with substrate doping level increased by the factor S. Scaling dimensions, voltages and dopant levels in this way keeps the electric field strength unaffected and the gate capacitance per unit width of channel also remains approximately constant since channel length and oxide thickness scale in proportion. If only the gate length is scaled, leaving other dimensions, voltages, and doping levels unchanged, this is 'lateral scaling' or 'gate shrink' which can be easily applied to existing masks. In theory this results in a decrease in gate delay by a factor proportional to S squared. In practice, the decrease factor will be approximately proportional to S, rather than S squared, because 'velocity saturation' will cause there to be a constant relationship between channel current and resistance.

The improved device density and IC performance improvements over the past 40 years have been remarkable in providing ever-increasing functionality and speed. They have also led to reductions in manufacturing costs since the silicon die area for given functionality is reduced. Therefore, more dies can be fabricated on a silicon wafer of fixed size and cost of manufacture. Smaller die sizes also lead to higher yields since a given density of imperfections will affect fewer dies [49].