# SEVENTH FRAMEWORK PROGRAMME THEME ICT-2007-1-3.3 Embedded systems

Grant agreement for: Collaborative Project

Small of medium-scale focused research project

# Annex I - "Description of Work"

Project acronym: GALAXY

Project full title: GALS InterfAce for CompleX Digital SYstem Integration

Grant agreement no.: 214364

Date of preparation of Annex I: 23/10/2007

Date of approval of Annex I by Commission: 26/10/2007

#### List of Beneficiaries

| Beneficiary<br>Number | Beneficiary name                                                                                                | Beneficiary short name | Country     | Date enter project | Date exit<br>project |

|-----------------------|-----------------------------------------------------------------------------------------------------------------|------------------------|-------------|--------------------|----------------------|

| 1 (coordinator)       | IHP GmbH - Innovations for High<br>Performance Microelectronics/<br>Institut fuer Innovative<br>Mikroelektronik | IHP                    | Germany     | 1                  | 36                   |

| 2                     | The University of Manchester                                                                                    | UNIMAN                 | UK          | 1                  | 36                   |

| 3                     | Ecole Polytechnique Fédérale de<br>Lausanne                                                                     | EPFL                   | Switzerland | 1                  | 36                   |

| 4                     | Alma Mater Studiorum - Università di Bologna                                                                    | UNIBO                  | Italy       | 1                  | 36                   |

| 5                     | Silistix UK Limited                                                                                             | STX                    | UK          | 1                  | 36                   |

| 6                     | Infineon Technologies AG                                                                                        | INFINEON               | Germany     | 1                  | 36                   |

# **Table of Contents**

| PART A                                                                              |    |

|-------------------------------------------------------------------------------------|----|

| A1. Budget breakdown and project summary                                            | 4  |

| A.1 Overall budget breakdown of the project                                         | 4  |

| A.2 Project summary                                                                 | 5  |

| A.3 List of beneficiaries                                                           | 6  |

| PART B                                                                              |    |

| B1. Concept and objectives, progress beyond state-of-the-art, S/T methodology and v |    |

| plan                                                                                | •  |

| B.1.1 Concept and project objectives                                                |    |

| B.1.1.1 Objectives of GALS architecture for target applications                     |    |

| B.1.1.2 Scientific and technical project objectives                                 |    |

| B.1.1.3 ASIC implementations within the GALAXY Project                              |    |

| B.1.1.4 Dissemination and exploitation of results                                   | 10 |

| B.1.1.5 Relevance to the challenge 3 call topics                                    | 10 |

| B.1.2 Progress beyond the state of the art                                          |    |

| B.1.2.1 GALS design as a system integration solution                                | 1  |

| B.1.2.1.1 GALS with pausible clocking                                               | 1  |

| B.1.2.1.2 GALS based on the boundary synchronization                                | 1  |

| B.1.2.1.3 FIFO-based GALS solutions                                                 | 1  |

| B.1.2.2 Patent search on GALS                                                       | 1  |

| B.1.2.3 Applicability and possible problems with state-of-the art GALS design       | 1  |

| B.1.2.3.1 Power saving with GALS                                                    | 1  |

| B.1.2.3.2 EMI reduction with GALS                                                   | 1  |

| B.1.2.3.3 GALS and Networks on Chip (NoC)                                           | 1  |

| B.1.2.4 GALS design improvements within the project                                 | 1  |

| B.1.2.5 Baseline of the project                                                     | 2  |

| B.1.2.6 Performance research indicators                                             | 2  |

| References                                                                          | 2  |

| B.1.3 S/T methodology and associated work plan                                      | 2  |

| B.1.3.1 Overall strategy and general description                                    | 2  |

| B.1.3.2 Timing of work packages and their components                                | 3  |

| B.1.3.3 Work package list                                                           | 3  |

| B.1.3.4 Deliverables list                                                           | 3  |

| B.1.3.5 Work package descriptions                                                   | 3  |

| B.1.3.6 Efforts for the full duration of the project                                | 5  |

| B.1.3.7 List of milestones and planning of reviews                                  | 5  |

| B2. Implementation                                                                  | 6  |

| B.2.1 Management structure and procedures                                           | 6  |

| B.2.1.1 Overall approach to management                                              | 6  |

| B.2.1.2 Decision making mechanisms                                                  | 6  |

| B.2.1.3 Funding flow                                                                                                     | 61 |

|--------------------------------------------------------------------------------------------------------------------------|----|

| B.2.1.4 Communication among the project partners                                                                         | 61 |

| B.2.1.5 Changes to the project plan                                                                                      | 62 |

| B.2.1.6 Resolution of conflicts                                                                                          | 62 |

| B.2.1.7 Legal aspects                                                                                                    | 62 |

| B.2.2 Beneficiaries                                                                                                      | 63 |

| B.2.2.1 IHP GmbH - Innovations for High Performance Microelectronics/ Institut fuer Innovative Mikroelektronik (Germany) | 63 |

| B.2.2.1.1 Short resume of key persons to be involved                                                                     | 63 |

| B.2.2.2 The University of Manchester (UK)                                                                                | 64 |

| B.2.2.2.1 Short resume of key persons to be involved                                                                     | 64 |

| B.2.2.3 Ecole Polytechnique Fédérale de Lausanne (Switzerland)                                                           | 65 |

| B.2.2.3.1 Short resume of key persons to be involved                                                                     | 65 |

| B.2.2.4 Alma Mater Studiorum - Università di Bologna (Italy)                                                             | 66 |

| B.2.2.4.1 Short resume of key persons to be involved                                                                     | 66 |

| B.2.2.5 Silistix UK Limited (UK)                                                                                         | 67 |

| B.2.2.5.1 Short resume of key persons to be involved                                                                     | 67 |

| B.2.2.6 Infineon Technologies AG (Germany)                                                                               | 67 |

| B.2.2.5.1 Short resume of key persons to be involved                                                                     | 67 |

| B.2.3 Consortium as a whole                                                                                              | 68 |

| B.2.3.1 Sub-contracting                                                                                                  | 69 |

| B.2.4 Resources to be committed                                                                                          | 70 |

| B3. Potential impact                                                                                                     | 73 |

| B.3.1 Strategic impact                                                                                                   | 73 |

| B.3.1.1 Impact expected from GALAXY project                                                                              | 73 |

| B.3.1.2 Necessity for European level project                                                                             | 74 |

| B.3.1.3 Other research activities tackling the GALS paradigm                                                             | 74 |

| B.3.1.4 Factors affecting impact of the GALAXY project                                                                   | 75 |

| B.3.2 Plan for the use and dissemination of foreground                                                                   | 77 |

| B.3.2.1 Popularization of GALS methodology                                                                               | 77 |

| B.3.2.2 Publication of achieved results                                                                                  | 78 |

| B.3.2.3 GALS applied in NoC environment                                                                                  | 78 |

| B.3.2.4 Plan for the exploitation of the project results                                                                 | 79 |

| B3.2.5 Exploitation of results by project partners                                                                       | 80 |

| B.3.2.5.1 IHP                                                                                                            | 80 |

| B.3.2.5.2 University of Manchester                                                                                       | 80 |

| B.3.2.5.3 Ecole Polytechnique Fédérale de Lausanne                                                                       | 80 |

| B.3.2.5.4 Università di Bologna                                                                                          | 81 |

| B.3.2.5.5 Silistix                                                                                                       | 81 |

| B.3.2.5.6 Infineon Technologies                                                                                          | 81 |

| B.3.2.6 Management of intellectual property                                                                              | 81 |

| B.3.2.7 Contributions to standards                                                                                       | 83 |

| Abbreviations                                                                                                            | 84 |

# PART A

# A1. Budget breakdown and project summary

# A.1.1 OVERALL BUDGET BREAKDOWN OF THE PROJECT

| A3.2                                              | What it costs                                                            |                      |                                                          | Requested<br>EC<br>contribution | 638.073,97 | 569.502,50 | 409.680,00 | 381.100,00 | 508.024,63 | 393.618,90 | 2.900.000,00 |

|---------------------------------------------------|--------------------------------------------------------------------------|----------------------|----------------------------------------------------------|---------------------------------|------------|------------|------------|------------|------------|------------|--------------|

|                                                   | W                                                                        |                      |                                                          | Total<br>receipts               | 00'0       | 00'0       | 00'0       | 00'0       | 00'0       | 00'0       | 0,00         |

| orms                                              | GALAXY                                                                   |                      |                                                          | TOTAL<br>A+B+C+D                | 816.073,97 | 753.388,00 | 545.440,00 | 503.800,00 | 673.549,50 | 787.237,80 | 4.079.489,27 |

| Grant agreement Preparation Forms Collaborative   | <u>(0</u>                                                                |                      | project)                                                 | Other<br>(D)                    | 00'0       | 00'0       | 00'0       | 00'0       | 00'0       | 00'0       | 00'0         |

| ent Prep                                          | Proposal acronym (2)                                                     | ONE FORM PER PROJECT | ole duration of the                                      | Management<br>(C)               | 104.073,97 | 17.846,00  | 2.400,00   | 13.000,00  | 11.450,00  | 00'0       | 148.769,97   |

| rant agreem<br>Collaborative                      | Project                                                                  | NO                   | Estimated eligible costs (whole duration of the project) | Demonstration<br>(B)            | 00'0       | 00'0       | 00'0       | 00'0       | 00'0       | 00'0       | 0,00         |

| 100.0                                             |                                                                          |                      | Estimated                                                | RTD /<br>Innovation<br>(A)      | 712.000,00 | 735.542,00 | 543.040,00 | 490.800,00 | 662.099,50 | 787.237,80 | 3.930.719,30 |

| EUROPEAN COMMISSION<br>7th Framework Programme on | Research, Technological Development and Demonstration Development 214364 |                      |                                                          | Short<br>name                   | HP         | UNIMAN     | EPFL       | UNIBO      | STX        | INFINEON   | TOTAL        |

| ***                                               | Proposal number (1)                                                      | -                    | Participant                                              | this<br>project                 | -          | 2 0        | е          | 4          | 5<br>S     | 9          |              |

Annex I: page 4 of 85

#### **A.1.2 PROJECT SUMMARY**

# Grant agreement Preparation Forms EUROPEAN COMMISSION 7th Framework Programme on Research, Technological Development and Demonstration Collaborative Project Project Our Project

Project number (1) 214364 Project acronym (2) GALAXY

ONE FORM PER PROJECT

GENERAL INFORMATION

GALS InterfAce for CompleX Digital SYstem Integration

01/01/1900

Starting Date (4)

Duration in months (5)

Activity code(s) most relevant to your topic (7)

Free keywords (8)

GALS, asynchronous design, system integration, NoC, EMI reduction,

deep-nanometer technologies

Abstract(9) (max. 2000 char.)

This project builds on a technology approach in which the EU currently has world leadership, thanks to previous pan-European funding, and in which the participants are recognised centres of excellence. We propose to provide an integrated GALS (Globally Asynchronous, Locally Synchronous) design flow, together with novel Network-on-Chip capabilities, that will materially aid embedded system design for a significant class of problems. We aim to remove existing barriers to the adoption of the technology by providing an interoperability framework between the existing open and commercial CAD tools that will support development of heterogeneous systems at the different levels of abstraction. The project will evaluate the ability of the GALS approach to solve system integration issues and, by implementing a complex wireless communication system on an advanced 45nm CMOS process, explore the low EMI properties, inherent low-power features and robustness to process variability problems in nanoscale geometries.

#### **A.1.3 LIST OF BENEFICIARIES**

# List of Beneficiaries

| Beneficiary<br>Number | Beneficiary name                                                                                                | Beneficiary short name | Country     | Date enter project | Date exit<br>project |

|-----------------------|-----------------------------------------------------------------------------------------------------------------|------------------------|-------------|--------------------|----------------------|

| 1 (coordinator)       | IHP GmbH - Innovations for High<br>Performance Microelectronics/<br>Institut fuer Innovative<br>Mikroelektronik | IHP                    | Germany     | 1                  | 36                   |

| 2                     | The University of Manchester                                                                                    | UNIMAN                 | UK          | 1                  | 36                   |

| 3                     | Ecole Polytechnique Fédérale de<br>Lausanne                                                                     | EPFL                   | Switzerland | 1                  | 36                   |

| 4                     | Alma Mater Studiorum - Università di Bologna                                                                    | UNIBO                  | Italy       | 1                  | 36                   |

| 5                     | Silistix UK Limited                                                                                             | STX                    | UK          | 1                  | 36                   |

| 6                     | Infineon Technologies AG                                                                                        | INFINEON               | Germany     | 1                  | 36                   |

#### PART B

# B1. Concept and objectives, progress beyond state-of-the-art, S/T methodology and work plan

#### **B.1.1 CONCEPT AND PROJECT OBJECTIVES**

#### **B.1.1.1 Objectives of GALS architecture for target applications**

It is envisioned by the European Nanoelectronics Initiative Advisory Council (ENIAC) that during the course of the FP7 the CMOS technology miniaturisation will continue, even if increasing difficulties may slow down the pure technological progress. And in fact, the increased complexity, performance requirements, and the need for power and EMI reduction present almost unsolvable challenges to designers of complex embedded systems. The continued technology improvement towards nanoscale dimensions generates additional problems for embedded system design. The combination of complex application requirements and technology imperfections (e.g. process variability and reliability) exacerbate the problems of timing closure and clock tree generation requiring additional design iterations and extended design-to-market time. It is imperative to deal with these issues; one very promising option is the use of a Globally Asynchronous Locally Synchronous (GALS) design methodology.

The idea of GALS system design is not entirely novel. However, despite significant research effort, the number of industrial GALS applications is currently relatively low.

When analyzing why a GALS approach has not been adopted by industry we observe that several issues have not been fully addressed until now. Firstly, the design-flow for GALS chip interconnect is not mature enough to guarantee reliable and comfortable chip design. Secondly, the main strengths of GALS design, such as improvement of system integration, better EMI characteristics and power reduction, were never completely exploited and proven in practice. Lastly, the targeted GALS applications were sometimes not a perfect match with the GALS techniques.

From our perspective, a GALS solution needs to have the following properties in order to be widely used: standard interfaces should be defined that will be widely adopted (rather than the existing situation in which numerous GALS proposals have each suggested their own interfaces to the synchronous world); the GALS design flow should be based on standard EDA tools extended with an additional reliable and user-friendly asynchronous tool-set; the GALS interface architecture should be based on high-throughput, low complexity solutions; the GALS interface proposal and source code should be offered free-of-charge within an open core framework to gain popularity and to break the prejudices that exist to mixed asynchronous/synchronous approaches.

An important aspect of GALS success or failure is the target application. It is expected that a GALS based chip interconnect will be a good choice for applications in certain fields while in others it will be used very rarely. We think that GALS can show the best results for designs with moderate performance and very complex structure. Another aspect is the design cost. GALS design methodology offers advantages in system integration and consequently GALS can be an extremely useful approach for submicron systems with a short time to market as long as it is supported by an automated design flow based on commercial CAD tools.

In this project, we address these problems and intend to prove that the GALS methodology offers powerful solutions for modern embedded system design integration. We aim at promoting the development of GALS system design by providing an interoperability framework between the existing open or commercial CAD tools for rapid design and prototyping. This framework will support development of heterogeneous systems at the different levels of abstraction. We will explore and evaluate the ability of GALS to solve system integration issues as well as building on its reduced EMI and low-power properties. A promising target platform can be seen in the area of Networks on Chip (NoC) [DEM06]. The NoC paradigm seems to be very attractive solution for the future chip interconnect. There are already a few NoC platforms based on the GALS architecture [DOB05, BEI05,

BJE05]. In this project we intend to investigate different approaches of implementing GALS-enabled NoC platforms, comparing them with fully synchronous implementations, and of integrating the NoC design flow into the GALS design flow.

Finally, with further process miniaturization and increases in system complexity, we see the emerging need for a powerful system integration technique. Furthermore, nanoscale technologies have their own issues such as process variability and reliability. The ENIAC strategic research agenda indicates system integration and parametric variation concerns as two causes that are pushing us closer to the limits of CMOS scaling. In the framework of this project we will explore these critical issues in the context of GALS. Additionally we intend to evaluate the effectiveness of a GALS system design for a highly complex wireless communication application in a very advanced 45 nm CMOS process. We intend a true evaluation of the improvements offered by GALS methods by implementing in parallel a GALS and a pure synchronous version of the example design. With this approach we should be able to present a fair comparison of the effort needed for system integration and for finishing the design process for both cases. We plan to fabricate a separate second chip in order to compare the effectiveness of the GALS technique of dealing with EMI and of reducing the power without harming performance.

#### **B.1.1.2** Scientific and Technical Project Objectives

On the basis of the previous discussion, we are planning to analyse existing GALS solutions with stretchable or data-driven clocking, and GALS solutions with an asynchronous FIFO interconnect and independent local clocking. During the project we will select optimal GALS architectures for the target applications and define the communication interfaces (8th month of the project). The suggested "optimal" solutions should be based on the existing GALS architectures. However, it is expected that selected the GALS design could incorporate several optimized features in terms of hardware complexity, performance, power dissipation and EMI. We will consider also integration of the GALS interfaces into the NoC application scenario. The criteria for selecting and generating the optimal GALS architecture are based on conformity to the rules and directions and to the probable target application named in Section B1. The proposed solution should have scalable interfaces and, where possible, its source code will be offered as an open core.

In this project, a GALS framework providing interoperability between design tools for rapid design and prototyping will be proposed. This design flow will be based on commercial CAD tools and on the existing Balsa framework [BAR00] with extensions to mixed synchronous-asynchronous systems. Balsa has until now been used for designing pure asynchronous circuits. The main idea is to integrate the Balsa language and tools in a system level design environment, where Balsa will be seen just as any other language, in order to allow mixed descriptions of synchronous and asynchronous circuits. Consequently, we will generate a system level design tool that is able to handle IP blocks referring to Balsa, Verilog, VHDL and SystemC specifications with an open plug-in interface to easily accept new languages and tool flows. The emphasis will be on a graphical system-level design environment acting as a controller and interoperability layer between conventional CAD tools. Firstly, a tool flow will handle the dependencies, file format requirements and incompatibilities between tools, and will control the sequential execution of format conversion, compilation, synthesis and simulation tools. A cosimulation back-plane will provide interoperability between the simulators and emulators from different vendors, enabling the co-simulation and co-debugging of unrelated languages and hardware targets (internal version 19th month of the project, final version 36th month of the project). Finally, a covisualization back-plane will provide the ability to control and visualise in real-time the activity of external simulators, emulators and software tasks and the simulated circuit's properties (such as its EMI), thereby providing a framework for distributed simulation/emulation of hardware-software electronic systems together with a multi-target debugging environment (internal version 22nd month of the project, final version 37th month of the project). We will completely automate the simulation and synthesis flows for heterogeneous applications. Preliminary, unpublished, work at UNIMAN has produced a co-simulation prototype. A GALS hardware-software prototyping flow will also be provided that will target FPGA devices. This proposed GALS framework will be user-friendly for designers without experience in asynchronous design in order to ease adoption of the GALS methodology. The target is a cheap and simple design flow. Although we could have just integrated Balsa support into existing commercial frameworks, this kind of integration is unsatisfactory: proper interoperability of multiple SME and open-source tools is extremely difficult to achieve, and the subtleties of asynchronous and GALS design (such as meta-stability and pausible clocking) are complex to deal

in order to consolidate asynchronous IPs dissemination and re-use (5th month of the project). The IP format will be able to describe hardware/software entities at multiple levels of abstraction in multiple languages (SystemC, C, Verilog, VHDL, Balsa, gate-level netlist etc.), with both synchronous and asynchronous interfaces. The IP format will contain enough information to transparently convert signals between varying levels of abstraction enabling: a transparent co-simulation of IPs at different levels of abstraction, the visualisation of signals at levels of abstraction independently of the simulated level of abstraction, and exploitation of transaction level structures during hardware-software codesign and visualisation. The IP-XACT IP packaging format proposed by the SPIRIT consortium satisfies most of these specifications, but does not include any support for asynchronous-specific structures. Rather than creating a new packaging format altogether, we will work towards extending the IP-XACT format, hopefully integrating these ideas in a future version of their work.

Based on this open IP packaging format, we will establish a library of the important GALS components scalable to different applications (24th month of the project). This library of GALS interface IPs should enable a plug-and-play type of approach when designing a system with a heterogeneous mixture of synchronous and asynchronous IPs. Additionally, we plan to generate a library of asynchronous IPs allowing new users to easily build a functional asynchronous or GALS system. This will be, at least in the beginning, a relatively simple library limited to basic components. However, we expect that this library will be further extended by encouraging community sharing of IPs via a website (similarly to, or in collaboration, with opencores.org). The library will include a full design support including necessary additional cells such as Mutex and Muller-C elements for the IHP CMOS process (14th month of the project). IHP design kits and fab services are already available for academic and research institutions over Europractice program. We plan to extend this support to the GALS design flow and an extended set of standard cells. During the project we will also promote the GALS methodology by organizing training events, summer schools and preparing tutorials and documentation for the tools and libraries.

We will consider challenges for establishing an effective test flow for the GALS systems. In our opinion, since the GALS design is dominated by local synchronous blocks, the test flow will be based on existing synchronous test methodology (a scan approach). For the asynchronous components, implemented we propose a limited implementation of functional tests to give sufficient test coverage (23rd month of the project).

It is planned to investigate the possibilities for lowering EMI and power with a GALS methodology. We plan to build an abstract model of the GALS circuit and generate the optimal algorithms for reducing the EMI. Additionally, the developed EMI reduction algorithms will be evaluated theoretically and in practice (20th month of the project). We will investigate application of dynamic voltage and frequency scaling in conjunction with GALS in order to reduce power in comparison with standard synchronous low-power solutions (20th month of the project).

The project also intends to deploy the power-aware nature of GALS technology to bring NoC architectures to maturity. Network-on-chip (NoC) is the candidate technology to provide scalable communication bandwidth through a modular interconnect design. The lesson learned from state-ofthe-art NoC prototypes is that almost 50% of total NoC power is drained by the clock tree (clock distribution and flip-flops). Moreover, the problem of distributing the global clock in a chip with minimal clock skew is getting difficult to solve due to increases in clock frequencies, smaller feature sizes and growing design complexities, which indicates that a global timing notion will not be feasible for highlyintegrated nanoscale designs. GALS technology is generally viewed to be a breakthrough technology for future system interconnect designs. GALS-based NoCs would allow the synchronous design of network nodes at their optimum clock frequency, while facilitating asynchronous communication between modules. This would reduce the timing convergence constraints during back-end physical design steps, remove the power-hungry global clock tree and pave the way for new variation-tolerant on-chip interconnection schemes. Unfortunately, although these considerations would appear to be common sense, they have not been enough to remove the barriers to the adoption of GALS interconnects due to the lack of convincing analysis and exploration frameworks, crossbenchmarking with synchronous solutions, proven robustness against nanoscale physics effects and tool support. The project intends to bridge this gap, and consolidate GALS-NoCs as the enabling technology for widespread adoption of network-centric architectures for highly integrated MPSoC platforms in the nanometer regime (31st month of the project).

#### **B.1.1.3** ASIC implementations within the GALAXY Project

Practical IC implementations will be the key issue of the GALAXY project, as it will provide the best

way to evaluate the developed GALS solutions and compare them against traditional circuits. We plan to have two separate ASIC implementation runs within the GALAXY project.

The first chip will be specifically designed to be a test chip containing structures to evaluate GALS components(17th month of the project). As part of WP7 we will investigate the advantages of GALS-based design in reducing power consumption, reducing EMI, and improving process variation tolerance. The first chip will contain test structures that will allow us to quantify these advantages by direct measurements. Additional test structures will be included to test new library components developed in WP3. Most importantly, a set of specially designed test circuits will be developed in order to investigate scaling effects. The same test structures will be replicated in the second chip (which will use a much more aggressive technology). Comparative measurements on both chips will provide us with invaluable, and currently non-existent, data on the suitability of GALS for aggressively scaled technologies. We expect to use the IHP 130 nm technology for the first chip, as the advanced 45nm technology we plan to use for the second chip will not be fully available during the first part of the project. Using two different manufacturing technologies will also give us more reliable results for scaling effects. In addition it will allow us to explore application of GALS techniques to low-cost processes

Finally, we plan to build a complex target system using both a standard synchronous CMOS design flow and the GALS design flow developed in this project (WP3, WP4, WP5) in a cutting edge 45 nm CMOS process (32nd month of the project). First product samples in 45 nm process are announced for early 2008, full production in 09/10. For 32 nm we do not expect early samples before 2009/10. Ramp-up and technology access for our projects would not be available before 2011/12. Therefore, the most advanced process to which we can have access and actually produce chips in the time frame of the project is 45 nm. However, during the project span and particularly in the activity 7.3 (Circuit and architecture level techniques) we will investigate how further technology scaling (32 nm and beyond) will affect GALS topic. Implementing the same system using two separate methodologies (GALS and synchronous) is the only "fair" way to evaluate the GALS design flow. As mentioned earlier, this second design will also contain a set of test structures to investigate scaling effects. With this approach we will be able to estimate and show the viability of the concepts, techniques, architectures and tools developed within the project.

Selecting a suitable target platform for the second design is important. Since wireless communication is an application domain which is gaining more and more popularity and which poses significant technical challenges to system designers (performance- and power-wise), and since several group members have prior experience in this field, we will consider target platforms from this field. For example, one candidate will be an accelerator for an OFDM baseband processor with data rates up to 1 Gbps for communication systems in 60 GHz range which is currently under development in IHP [GRA07b]. Currently, the full processor integrates several Viterbi decoders, 256-FFT and IFFT, many complex interleavers/deinterleavers. We will also consider the application of GALS-enabled Network-on-a-Chip architectures (as developed in WP6) in this target system as well.

The designed chips will be the result of close cooperation between all project partners and will rely on results of several WPs. Building chips is recognised as risky, but all partners have experience in successful, right-first-time, chip design. This work will be a real challenge, but the experience of the project team, and the fact we have worked closely together in the past, gives us complete confidence this can be achieved, and that the results will confirm the initial expectations as to the real value and long-term viability of the GALS and NoC techniques.

#### **B.1.1.4** Dissemination and exploitation of results

Our strategy for the dissemination of results is to place as much as is possible in the public domain to encourage the uptake and further development of the methodology by industry. However, necessarily some IP will remain confidential to be exploited by the project partners. The precise status of the deliverables is given in section B.1.3.4, however in general the design framework and interface definitions will be publicly available. An abbreviated guide to the status of results generated in the project is given in section B.3.2.6 Management of intellectual property.

#### **B.1.1.5** Relevance to the Challenge 3 call topics

In this project we are targeting ICT objective 3.3: Embedded systems design. The first target of this call is "Theory and methods for system design: Methods that can increase system development productivity while achieving predictable system properties". It is quite clear that GALS techniques based on asynchronous interfaces can lead to a system design framework that will improve system

Annex I: page 10 of 85

development and simplify design process. This target states that "key issues encompass heterogeneity (building embedded systems from components with different characteristics); composability; predictability of extra-functional properties such as performance and robustness (e.g. safety, security, timing and resources); concepts and tools for specifying and evaluating security properties; adaptivity for coping with uncertainty". It is expected that a GALS methodology will become the basis for the integration of heterogeneous components (synchronous, asynchronous, components supplied from different voltages and running at different frequencies). Also a GALS methodology could be a key driver for the integration of different IP components from different vendors. Additionally, a GALS approach will increase the robustness of the system, reduce the probability metastability problems, and relax the timing of the system. GALS methodology is also quite effective in the area of secure applications since the asynchronous behaviour of GALS components disables to a significant level Differential Power Analysis (DPA) of system behaviour. Finally, in the context of this project we want to target nanoscale issues such as uncertainty and variability. It is expected in this respect that GALS techniques will also show significant improvement in comparison with classical approaches for system integration.

The second target of the call is "Suites of interoperable design tools for rapid design and prototyping". A large part of our project is dedicated to the construction of a framework able to control the interoperability of compilation, simulation and synthesis tools from SME vendors and from the open-source community. Parallel compilation and synthesis will be made possible by a dependency and file format checker, able to start tools and file conversions when appropriate. Parallel simulation will be made possible by a co-simulation backplane interfacing any number of simulators, emulators and software modules together. A co-visualization backplane merges the simulation traces, emulation feedbacks and software execution results together for efficient debugging of components from different origins. The visualization of circuit properties (such as performance, power, EMI) from multiple tools in a common view will ease circuit optimization. This framework and plug-in interfaces will be released as an open tool framework, therefore facilitating new entrants. Our GALS IP format is expected to be proposed as an extension to the standardized (synchronous) IP packaging format from the SPIRIT consortium. It should be noted that the consortium includes partners experienced in previous open-source projects and an SME whose business is dependent on tool interoperability.

#### **B.1.2 PROGRESS BEYOND THE STATE OF THE ART**

#### **B.1.2.1 GALS design as a system integration solution**

System on Chip (SoC) integration imposes a number of technical challenges on designers and tools. There are further difficulties for a SoC implementation in the area of wireless communication systems. The methods and tools for reducing power consumption and minimizing crosstalk between analog and digital parts of the system are very limited and often inefficient.

Many of the challenges are associated with the design of the clock network in digital systems. Clock skew appears to be a severe bottleneck for complex digital circuits. The synchronous transitions of the clock lines are a strong source of noise and electro-magnetic interference (EMI). Additionally, the power spent just running the clock tree is comparable to the power consumed in the functional blocks of the system. It is conceivable to conclude that splitting a complex digital system into several independent subsystems, will relax problems significantly. Dealing with smaller blocks is much simpler, and power saving techniques could be more successfully applied. Crosstalk and EMI are suppressed due to the uncorrelated operation of the autonomous blocks. However, synchronisation between blocks operating at different speeds could be very complicated.

Several existing approaches address the problem of block partitioning and data synchronisation between independent blocks. Some of them are used to deal with increased power consumption and EMI. Today, these techniques are mainly referred to as Globally Asynchronous Locally Synchronous (GALS) methods. Many of them are not generally applicable. However, some of the techniques are currently used in design practice. Choosing between different proposed strategies depends very much on the particular system architecture.

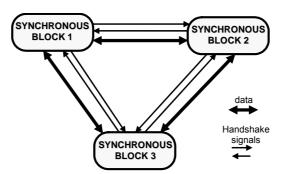

GALS systems have a unique structure that is similar for all the different proposals. The principle architecture of GALS for point to point dataflow structures is given in Figure 1. The basic GALS paradigm is based on a system composed of number of synchronous blocks designed in a traditional way. However, it is assumed that clocks of such synchronous systems are not necessarily correlated and consequently that those synchronous systems communicate asynchronously using handshake channels. Locally synchronous modules are usually surrounded by asynchronous wrappers providing such inter-block data transfer. The principle architecture of GALS for point to point dataflow structures is given in Figure 1. Practical GALS implementations may form much more complex structures, such as bus or NoC structures for inter-block communications and use different data synchronization mechanisms, but all proposals are based on the simple structure shown in Figure 1.

Figure 1. GALS architecture

GALS as a technique was mentioned for the first time in [CHAP84]. This work gives the fundamental basis of globally asynchronous locally synchronous systems. Many years after the first proposal, the GALS idea was reactivated and a working architecture was described in [YUN96]. Following that, there has been revived interest in the GALS idea which has continued to increase until today.

The major differentiator between the different GALS techniques is the strategy used to safely transfer data between the locally synchronous blocks and avoid metastability. In principle, a GALS approach can be implemented in three different ways: using pausible clocking, boundary synchronization or FIFO-like interface structure.

#### **B.1.2.1.1 GALS** with pausible clocking

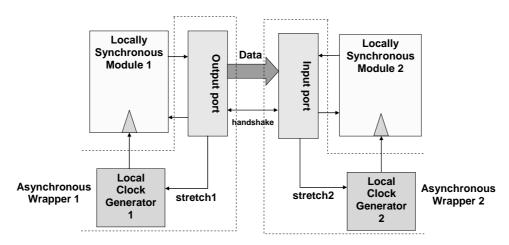

Many GALS systems presented in the last few years are based on pausible (or stretchable) clocking [MUT00, KRS06, ZHU02, MOO02]. This GALS method relies on the application of the local clocks that drive synchronous circuit blocks. In this case, stoppable ring oscillators are used to generate the local clocks. The strategy to avoid metastability is very simple. All local clocks for the blocks involved in a single data transfer are stopped until data is transferred. Therefore, the asynchronous wrappers are performing all necessary activities for safe data transfer between the blocks. A general structure of the typical GALS system with pausible clocks is shown in Figure 2. The asynchronous wrapper contains input and output ports that perform the handshake process between the LS modules and it generates a stretch signal for stopping the activity of both clocks. The basic GALS proposal focused on point-to-point communication between blocks. However, as shown in [VIL03] the idea can also be extended to more advanced solutions that support bus or crossbar structures for data communication.

Figure 2. Block diagram of a GALS system with pausible clocking

#### **B.1.2.1.2 GALS** based on the boundary synchronization

To avoid metastability and to perform safe data transfer between asynchronously communicating blocks, it is possible to implement synchronisation mechanisms. Many of these schemes are already known and have been successfully used for decades. For example it is possible to use two-flop synchronisers or one-flop synchronisers [GIN03]. As an alternative, the adaptive synchronisation techniques [KOL98] could be used for mesochronous systems. However, this approach does not offer any power saving mechanism and introduces a relatively large hardware overhead, because a separate delay line is needed for every single data line. Also, the time overhead needed for statistical analysis of the data could be important. The problem of mesochronous system integration can be also addressed with application of an adaptive predictive synchroniser [FRA04]. In this case, the synchronisation latency is smaller than one clock cycle.

Another interesting approach is concept of locally delayed latching [DOB04]. This is a complete GALS solution with the set of the synchronizing registers at the boundaries of the synchronous blocks. The major disadvantage of this architecture is that the data cannot be transferred every clock cycle due to the synchronous handshake that is performed at the boundaries of the synchronous part of the output port. Actually, one data transfer usually needs several clock cycles. This property of the proposed architecture restricts the application of the proposed circuitry to low speed data-transfer applications.

#### **B.1.2.1.3 FIFO-based GALS solutions**

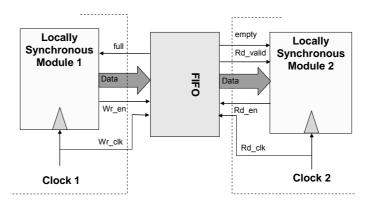

While designing GALS systems it also possible to interface blocks with specially designed asynchronous FIFO buffers as described in [CHAK03, CHE00, BEI06]. With this approach, the hardware redundancy of the FIFO is hiding the problem of the synchronisation in the system. FIFO-based GALS systems can tolerate very large interconnect delays and are quite robust with regard to metastabillity. This type of interface can be used not only for interconnection of heterogeneous (asynchronous and synchronous) systems, but also for classical synchronous-synchronous and asynchronous connections. Practical results confirmed that an acceptable data

throughput via such an interface can be achieved [CHE00]. The advantage of this GALS approach is that the operation of the locally synchronous module is not affected by synchronisation. However, for very wide interconnect data buses, FIFO-based GALS structures could be very expensive in terms of area. Also, the introduced latency might be significant and possibly not acceptable for some applications.

Alternatively, a GALS system can be based on a classical FIFO design using gray code. In [BEI06] such an interface is presented for the specific case of an Asynchronous Network on Chip (NoC) system. In this work, the compatibility with existing design solutions has been retained which has allowed the utilization of standard CAD tools. However, some price is paid with some performance degradation and a suboptimal architecture.

Figure 3. Typical FIFO-based GALS system

#### **B.1.2.2 Patent search on GALS**

In the previous section we introduced several architectures for GALS chip interconnect. However, most of them are developed at academies and not legally protected with patent rights. According to our knowledge, there are only few patent applications directly dealing with GALS interconnects. Two patents are submitted from Philips [CHO05, KES04], one dealing with ring-oscillator calibration and the other with "mouse-trap" pipeline synchronization. Additionally, there is a patent from University Rochester [ALB04] about GALS microprocessor. However, none of those patents are affecting significantly the work that we want to perform within the GALAXY project. Two additional patent applications are submitted from IHP [KRS04, GRA07], dealing with IHP-developed request-driven GALS technique and possibilities for EMI reduction with GALS interconnect. The circuits and methods covered by those two IHP patents may be utilized in the framework of this project and made available for non-commercial application. However, a commercial exploitation of those IHP proprietary patents is subject to licensing.

#### B.1.2.3 Applicability and possible problems with state-of-the art GALS design

Although GALS systems still have a great popularity among the scientific community they are not very frequently used in the commercial systems. There are different reasons for that, and our project aims to overcome those issues and offer effective solutions for a GALS design flow.

GALS is already confirmed as a powerful vehicle for improving system integration. It is clear that by partitioning a complex synchronous system into a number of the independent subsystems we can immediately profit from reduced clock skew, simpler clock tree, and easier timing closure. Eventually, this should result in a shorter design process and improved time-to-market of the product. However, there are still some challenges that must be resolved before the GALS design is established as a main-stream design technique.

In the previous subsection we have introduced three main GALS strategies. Each of them has its own properties and there is a certain price to be paid for the system integration improvement offered by any of them. In general, the designer must make a trade-off depending on IP blocks and communication requirements of the application, and choose the methodology that is most suitable. Three main parameters can be affected by this choice: latency, throughput and area [SCO07]. Generally, in the case of the boundary synchronization a major price is paid with reduced data throughput. For the FIFO-based GALS, throughput is preserved but for some applications increased data latency can be unacceptable. GALS with pausible clocking, on the other hand, introduces very

low latency but the performance loss can be significant.

One of the issues that has slowed the practical adoption of the GALS methodology is that of debugging and test flows. The classical synchronous design methodology is well supported by a number of very mature CAD tools which are constantly being improved. Commercial CAD tools (with the sole exception of asynchronous CAD provider Handshake Solutions [HS]) do not support asynchronous design. Consequently, the asynchronous design technique is followed by tools developed in academia. Such tools are usually uncoordinated, incomplete and their improvement is erratic – although the Balsa system at the University of Manchester has synthesised a complete ARM compatible processor core [PLA03]. Therefore, many steps in the design process for asynchronous circuits are still manual and there is no consistent design flow from behavioural modelling to tape-out of the circuit. For GALS systems the situation can be even worse. Although for synchronous parts of the system the support from standard tools can be used, there is no support either on the synchronous or on the asynchronous side for the mixed asynchronous-synchronous behaviour. On top of this, additional library cells such as C-elements, mutual exclusion elements, programmable delay lines or even complete handshake circuitry, need to be developed for an asynchronous design flow. A recent problem, with the advent of system level design environments using IP blocks. is the absence of a specification format for asynchronous IPs. This means that these new system level tools are unable to handle asynchronous circuits unless they are provided inside a synchronous wrapper, which would deprive them from most of the benefits obtained through an asynchronous design style. This situation contributes to the absence of asynchronous IP libraries and GALS interface libraries, which is currently the main driver in synchronous developments.

A similar problem appears with the test flow. The usual test-flow for synchronous circuits is based on the application of well-known scan-chains that can be used to control and observe all sequential elements within a design. The scan-chain approach requires a centralized clock, which is not available in standard asynchronous circuits. There are some solutions which offer a similar approach for asynchronous circuits [BER02]. However, there is significant overhead involved in such solutions. There has been some research on the test-flow for the GALS circuits. One approach is to use functional test for the asynchronous part of the system [GUR02]. Alternatively, BIST approach can be used as presented in [KRS05b]. Another problem in testing is the non-cycle accurate behaviour of some asynchronous designs. The responses of an asynchronous circuit under test may not be aligned with the test clock cycles of the automated test equipment. This can be a when mutual exclusion circuits for arbitration are used. In this case, the application of the usual hardware testers is limited due to their strictly cycle based non-reactive nature.

Most digital designers have experience limited to synchronous design. Asynchronous and GALS designs have their own properties sometimes not easily adoptable by a synchronous designer. The asynchronous interfaces frequently request small but non-standard modifications of the locally synchronous blocks.

GALS solutions based on the pausible clocking usually imply the application of ring oscillators. A ring oscillator is usually composed of an inverter chain. This structure naturally leads to the susceptibility to PVT (Process, Voltage, Temperature) variations. In many cases this property is in fact useful, since the PVT variation in the clock generator, which is located close to the actual circuit, will follow the PVT changes of the circuit as well. The application of the ring oscillators is particularly well suited for dynamic frequency scaling (DFS) in order to reduce the power consumption. On the other hand, for applications that require strict and accurate clocking of the system (as for communication systems), sensitivity to PVT introduces the need for delay line calibration as proposed in [MOO00]. Additionally, significant power is needed to run the ring oscillators.

Handshake solutions [HS] has recently released a clockless multilayer AMBA Advanced High-performance Bus (AHB). The new interconnect is a clockless implementation of the well-known multilayer ARM AMBA AHB — an interconnect scheme that enables parallel access paths between multiple masters and slaves. Although this product seems to confirm that power and EMI improvements can be expected by leveraging clockless technology, it is still far from providing a scalable solution to the problem of on-chip communication. In fact, the clockless multilayer AHB is aimed at medium performance applications. It is particularly well-suited to event- or interrupt-driven applications where its instant response and zero standby power consumption are particularly useful. However, the newly released clockless interconnect still relies on multi-layer architectural solutions that are well known to have severe scalability limitations. Our project aims at coupling the benefits of a scalable interconnect fabric (Networks-on-chip) with those of GALS design techniques.

#### **B.1.2.3.1 Power Saving with GALS**

Power saving was always considered an inherent property of asynchronous design. Therefore, the expectations from GALS designs were always very high. On the other hand, most of the practical GALS demonstrators have showed only marginal improvement in this direction. For example, the GALS baseband processor for WLAN [KRS06] showed an improvement of only 1% in comparison to the respective synchronous chip.

In retrospect, it is easy to understand this result. The inherent power reduction obtained by using a GALS-based system is essentially based on the same paradigm as the low-power techniques for synchronous circuits: trigger the locally synchronous block only when it is needed and lower the switching activity to minimum. Therefore, the achieved results are very similar.

We can expect more if the GALS approach is applied in conjunction with voltage and frequency scaling. GALS architecture is very well suited for such technique since the mutual communication between blocks is asynchronous. The boundaries of the GALS blocks are defined and the partitioning naturally leads to a hierarchical layout process. Therefore, the introduction of different power rings in the layout and insertion of DC-DC converters are easier. Theoretical investigations presented in [TAL05] show that even for GALS-based high-performance processors, which are generally not very suitable for GALS implementations, an average energy reduction of up to 33% can be obtained with only a slight performance drop of 10%.

#### **B.1.2.3.2 EMI reduction with GALS**

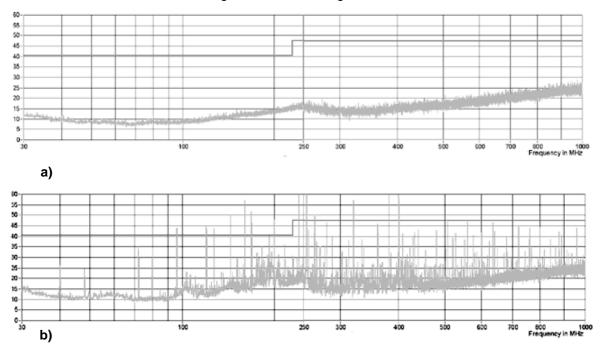

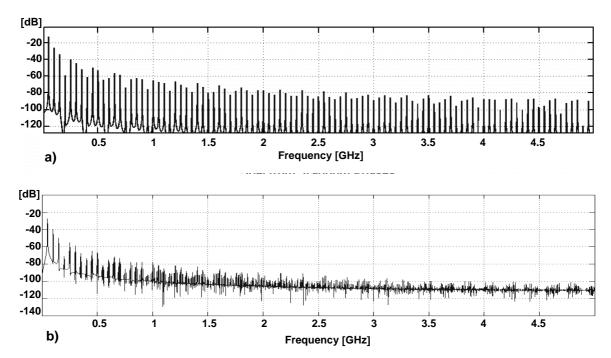

Another very important property of GALS designs is the reduction of electro-magnetic interference (EMI). It has been several times demonstrated that asynchronous circuits expose significantly lower level of EMI than their synchronous counterparts. One example is shown in Fig. 4 which compares the Amulet 2 asynchronous processor with an ARM9 [FUR99]. However, we believe that this property has not yet been completely explored in GALS systems. Lowering the noise generated from the digital part of the system is an important issue of complex SoC (System on Chip) integration. We have performed an initial simple study and the results are published in [GRA05]. The results, given there and shown in Figure 5, show the possibility of reducing the noise spectral components on the power supply line up to 20 dB in comparison with synchronous design. Additionally, reduction of the noise peaks can be expected up to 40%. The practical measurement given in [KRS05a, KRS06] shows lower values (5 dB) achieved in reducing the EMI. However, there is a great research opportunity in generating a reliable noise model and effective algorithms for lowering the EMI.

Figure 4. Comparing EMI of async. Amulet 2 (a) and compatible sync. ARM9 processor (b)

Figure 5. Power supply line spectrum of the synchronous (a) and GALS system (b)

This property can be also very useful for security application. GALS circuits have the potential to increased immunity toward Differential Power Analysis (DPA) attacks [GUR05]. The power spectrum of an asynchronous circuit does not contain large peaks at multiples of a global clock frequency and therefore is expected to present potential attackers with less information about the circuit operation. Furthermore, due to their asynchronous components GALS chips are less controllable and their timing is more non-deterministic. This is a very important feature for smart-card applications.

#### **B.1.2.3.3 GALS and Networks on Chip (NoC)**

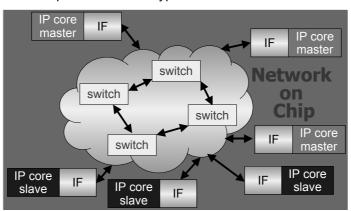

The ENIAC strategic research agenda points out that in the "More Moore" domain, although transistor performance will continue increasing, the performance of the interconnection network is not expected to match this progress. Employing totally self-timed techniques for the interconnect is a promising means to tackle a number of on-chip interconnection issues, from power and EMI reduction to clock skew management, and modularity of design. However, only a few proposals for an asynchronous NoC have been published so far. This section gives an overview of the state-of-the-art research in asynchronous on-chip networks. The typical NoC architecture is illustrated in Fig. 6.

Figure 6. Typical NoC architecture

The CHAIN network [BAI02], developed at the University of Manchester, is interesting in that it is implemented entirely using asynchronous, or *clockless*, circuit techniques. It makes use of delay insensitive 1-of-4 encoding, and source routed BE (Best Effort) packets. An easy adaptation along a path consisting of links of different bit widths is supported. CHAIN is targeted for heterogeneous low power systems, in which the network is system specific. It has been implemented in a smart card,

Annex I: page 17 of 85

which benefits from the low idle power capabilities of asynchronous circuits. Work from the group involved with CHAIN concerns prioritization in asynchronous networks. In [FEL03] an asynchronous low latency arbiter was presented, and its use in providing differentiated communication services in SoC was discussed, and in [FEL04] a router implementing the scheme was described.

NEXUS is another asynchronous on-chip network developed at Fulcrum Microsystems, USA [NEX04]. Their approach is based on a 16-port, 36-bit asynchronous crossbar that connects synchronous modules through asynchronous channels and clock-domain converters. Nexus is a quasi-delay-insensitive (QDI) on-chip interconnect infrastructure using one-of-four encoding and precharge domino logic. It also supports a split transaction protocol with a request burst going out and a completion burst returning.

Liljeberg et al., from the University of Turku, Finland, propose a self-timed ring architecture as a replacement for on-chip buses [LIL03]. They implemented a 12-stage bi-directional ring network with 36 pipeline sections. The network employs a two-phase signaling protocol between stages to accommodate relatively long wire segments with fewer transitions within a transaction cycle, and a four-phase signalling protocol for internal control within a stage to enable the design of fast and relatively simple control logic circuitry. The data path is encoded using a standard single-encoding scheme.

The MANGO network (*Message-passing Asynchronous Network-on-chip providing Guaranteed services over OCP interfaces*), developed at the Technical University of Denmark, is another clockless NoC, targeted for coarse-grained GALS-type SoC. MANGO provides connection-less BE routing as well as connection-oriented guaranteed services (GS) [BJE05a]. In order to make for a simple design, the routers implement virtual channels (VCs) as separate physical buffers. GS connections are established by allocating a sequence of VCs through the network. While the routers themselves are implemented using area efficient bundled-data circuits, the links implement delay insensitive signal encoding. Network adapters provide OCP-based standard socket interfaces, based on the primitive routing services of the network [BJE05]. This includes support for interrupts, based on virtual wires. The adapters also synchronize the clocked OCP interfaces to the clockless network.

A network-on-chip architecture, called ANOC, has been proposed by Beigné et al.[BEI05], which provides low-latency services. The methodology used to design the node is based on Quasi-Delay-Insensitive circuit designs. A 4-phase protocol handshaking is used for asynchronous channels, associated to a WCHB protocol for pipeline stages. Data are encoded using an n-rail code. The on-chip network interfaces are discussed in [BEI06]: they do not just handle resynchronization between synchronous and asynchronous NoC domains, but also implement NoC communication priorities and are adapted to standard implementation tools. Interestingly, a complete multi-level design framework has been developed to address the modeling challenges.

Some contributions from the open literature focus on specific network building blocks. The QNoC router designed at Technion [DOB05] features fully asynchronous implementation and supports multiservice levels, thus targeting quality-of-service provisioning. A comparison with a synchronous router also indicates that the asynchronous variant requires less area while delivering comparable data rates.

Finally, much research effort is being devoted to the electrical-level design of asynchronous links [ISO06, VIV07]. The focus is on delay-insensitivity through proper encoding techniques (e.g. dual-rail, m-of-n, Berger code), variation-tolerance, transceiver-circuits and signaling techniques.

While much research is being undertaken, there are not many demonstrations of clockless NoCs in real applications. A small, source-routed NoC for a commercial DSP audio chip is presented in [DSP06].

A working chip, called FLEETzero, to test an asynchronous switch fabric is described in [FLE01]. The switch fabric transports 8-bit data items from any of eight sources to any of eight destinations. Finally, the smart-card implementation of the CHAIN clockless network has already been discussed [PLA02].

A number of challenges lie ahead to make GALS-based NoC technology become mainstream.

Most current NoC technology assumes that on-chip logic and wires are reliable. In the best case, it is tolerant to delay variations, but it is not designed to recover from logic faults, failures or to deal with communication errors. Nanoscale technologies force a design paradigm shift, wherein fault tolerance becomes a requirement for all on-chip functions, including interconnect. Interconnect could be made fault-tolerant by building redundancy into the fabric, but it is likely to be more cost-effective to

implement error detection and retry capabilities. Another technology-related issue concerns the impact of process, supply voltage and temperature variations on the performance and reliability of long onchip links. These variations cause the signal propagation delay through interconnects to be uncertain which in turn affects the performance and reliability of the system significantly. Fault-tolerance and process variation-immunity are two explicit objectives of this project.

Moreover, while GALS schemes provide more independence between system IP blocks, in that the overall performance need not be determined by the slowest stage, they may exhibit meta-stability, thus resulting in potentially unpredictable performance. When it comes to truly asynchronous NoCs, on one hand, they exhibit promising power and performance metrics, but on the other hand they are often less efficient in terms of area, due to the lack of established logic optimization tools for asynchronous gate-level netlists.

Even the early design steps of GALS-based networks are not yet supported by mature synthesis tools. This is key to industrial interest for this kind of solution, which is currently mostly pushed by academia in spite of the widely acknowledged potential benefits. A significant evolution of design technology for GALS systems is expected from this project.

Finally, until now all implementation examples of GALS NoCs have been limited to low-end systems and are not available in both synchronous and asynchronous variants for comparison. Hence, they are not really able to make the case for clockless NoC design. Our project targets an explicit crossbenchmarking activity between synchronous and GALS communication architectures and explores GALS interconnect design for a high-end wireless communication system.

In general, while progress in clocking structures within NoCs continues in the short term (e.g. advanced backend synthesis tools, aggressive clock-gating), this project aims at proving that a complete paradigm shift would ensure significant advantages and at making such advantages available for real-chip realizations.

#### **B.1.2.4 GALS design improvements within the project**

As described in the previous subsections, there are different GALS architectures available and there is a variety of applications where GALS can be used. In the research community most practical realizations were based on pausible clocking and the majority of theoretical work was published on applications orientated towards high-performance CPUs. We believe that that there are other implementation methods and application fields that need to be considered as well. Therefore, during the project time we plan to evaluate different GALS techniques and their applicability. As a result of this, we want to propose certain improved GALS architectures. We plan also to optimize and standardize the interfaces in order to relax the design efforts when introducing GALS design. The industry is going in the similar direction. For example, Handshake Solutions have recently announced their new product clockless HTmAHP interconnect compliant to ARM AMBA AHP protocol [HS]. This product is suitable only for the compliant systems and its runs up to the moderate 100 MHz speed. Additionally, this product is available only to HS customers and it is not open source.

The major roadblock that is stopping broader uptake of GALS within commercial applications is the design flow. In this respect we plan to facilitate the development of new mixed synchronousasynchronous design flows by developing a framework able to coordinate the multiple tools various vendors and universities. This interoperability framework is primarily based on a co-simulation and covisualization architecture, and will also include synthesis and layout flows. Asynchronous descriptions will be based on the existing Balsa language and simulation/synthesis flow developed at the University of Manchester and widely recognized by the asynchronous community. The other usual design languages (Verilog, VHDL, SystemC, etc.) will be supported at the system level, making it possible to model heterogeneous GALS systems in a single environment providing a suitable layout flow. The primary interoperability layer is a co-simulation backplane with plug-in system and a well-specified interface to which any simulator or emulator can be attached. This backplane will allow the cosimulation of mixed languages (especially of those asynchronous languages unsupported in traditional CAD simulation tools), mixed vendors, mixed levels of abstraction, and mixed targets (such as the cosimulation between a Verilog test harness and a software module running on an emulator board). The ability of the framework to coordinate various simulators will also enable, without any additional effort, multiple instances of the same simulator to run simultaneously on different parts of the system. This will therefore allow distributed simulations over clusters of computers. Preliminary work at UNIMAN has established the feasibility of this approach [JAN07].

The co-simulation backplane will be attached to a co-visualization environment able to merge the

information processed by the various tools in a common graphical representation, ideal for debugging large-scale system level designs. The synthesis will be controlled by the framework to handle heterogeneous GALS flows and the process will be completed by including asynchronous components in traditional synchronous net-lists able to be handled by traditional layout tools.

Test flow improvements will be carefully considered. We anticipate building a test model for GALS systems as the combination of a standard scan approach for locally synchronous blocks and functional or BIST test for the asynchronous components. However, we have to generate the fault model of asynchronous wrappers and to estimate the fault coverage of the generated tests to confirm the suggested approach. The goal is to reach the fault coverage for asynchronous wrappers comparable with the coverage of the synchronous part generated with scan methods. We will also try to propose suitable methods for functional testing the GALS systems in the classical hardware tester environment, and to overcome the problem of non-determinism.

In the previous subsection we have already suggested dynamic frequency and voltage scaling as the best option for power saving with GALS. However, until now there were no measurement results confirming this advantage. We want to model a GALS system and to investigate the possible power saving with GALS on for a typical low-power application (for example in the area of mobile communication systems).

The most promising feature of GALS can be EMI reduction. The members of consortium have done some initial research work in this direction [GRA05]. However, the developed MATLAB model is too simplified and it needs to be scalable to any GALS system and to be usable for EMI estimation at a behavioural level for any GALS system. It is already clear that the level of EMI reduction is dependant on switching scenario among the GALS blocks. We want to develop the suitable algorithms and mechanisms that will enable us to maximize the EMI reduction. Additionally, we want to explore the possibilities for estimating EMI on the RTL and gate level using the standard CAD tools such as Synopsys PrimePower. All results will be verified with the measurement on the fabricated complex GALS chip.

As regards GALS application to networks-on-chip, this project will make available a number of architectural solutions (from conservative mesochronous clocking to fully independent clock domains, from architecture variants where the links are the only asynchronous elements to those where the whole communication infrastructure is asynchronous) meeting the requirements of a large number of hardware platforms. Several GALS interfaces will be employed in the NoC context (e.g., pausible clocking, mixed-clock FIFOs) and will be analyzed from a performance, area and power viewpoint.

Moreover, architecture-level techniques as well as proper backend synthesis methodologies will be devised to account for the effects of nanoscale physics. Process variability is the most important one because it has a direct negative impact on yield and large impact on all characteristics of the system. Above all, it might locally jeopardize expected performance. We will also show how the use of NoCs helps designers to overcome the reliability issues of future technologies. On one hand, making NoCs themselves fault tolerant can be accomplished through link-level or end-to-end error detecting/correcting coding schemes. On the other hand, low-power techniques might be combined with communication reliability ones to come up with energy-efficient and reliable communication schemes. The full potentials of dynamic voltage and frequency scaling in the context of GALS-enabled NoC designs will also be explored, thus cutting down on the significant power overhead incurred by state-of-the-art NoC prototypes. In the nanometer regime, leakage power becomes a serious concern as well, and we will devise network building block architectures and synthesis methodologies able to address this problem and to effectively span the power-performance trade-off. Lastly, we will create a link between high-level tooling for GALS-based system design and the NoC backend synthesis flow, thus creating with a complete automated synthesis flow for GALS NoCs.

All architectural explorations will be based on a virtual platform, allowing accurate system-level functional simulation, and a mature synchronous NoC architecture (called xpipes) will serve as the reference infrastructure for migration to the GALS paradigm.

This modelling and simulation environment will also allow addressing the lack of real design examples that confirm proof of GALS concepts and methods and show the effectiveness of GALS. In this project we want to design a complex GALS system for the high-end communication application with supporting datarates up to 1 Gbps [GRA07b]. The purpose of this system implementation should be evaluation of the proposed novel GALS design flow, but also exploration of the GALS interfaces, and power and EMI reduction possibilities. To properly address this we will, in parallel, implement the purely synchronous version of the same system.

Annex I: page 20 of 85

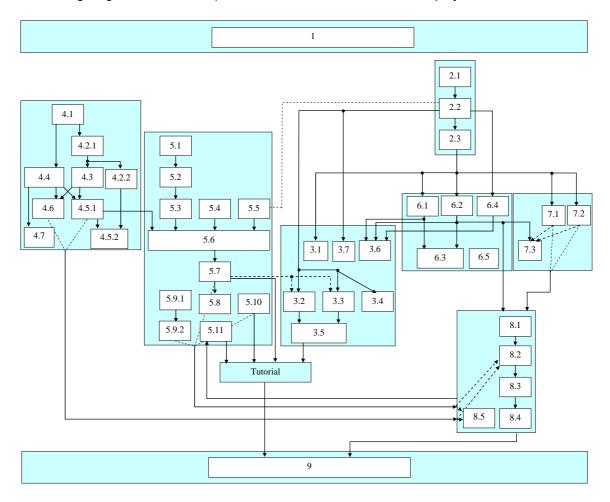

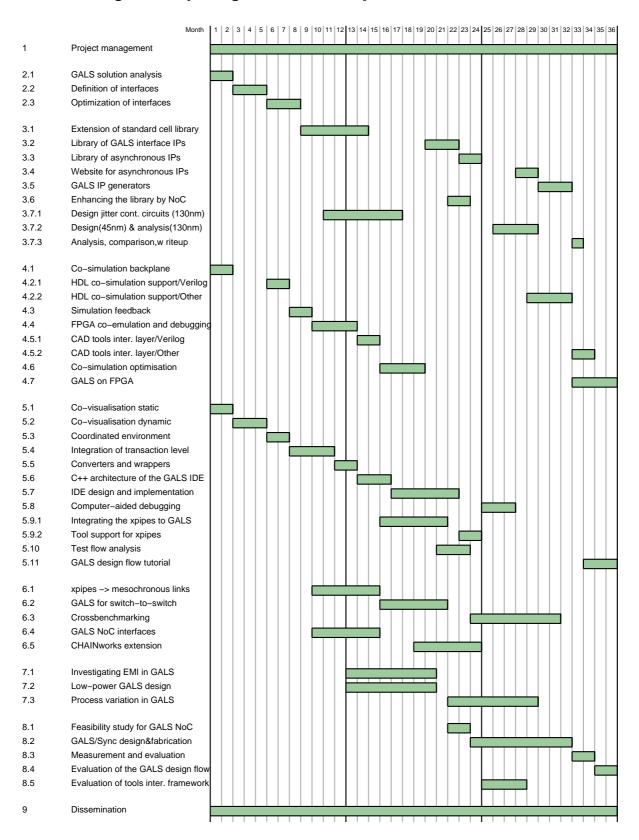

Until now there have been only relatively few complex GALS demonstrators developed, such as the WLAN baseband processor from IHP (0.25um CMOS) [KRS06], the FAUST processor developed at LETI (0.13um CMOS) [LAT07] and circuits fabricated in GALS group at ETHZ (0.25um CMOS) [GUR06]. We have to emphasise that this GALS system implementation is not the ultimate goal of the GALAXY project. We regard the GALS system implementation in this project a necessary vehicle to evaluate achieved improvements in the GALS design flow and architecture. However, the planned GALAXY GALS chip implementation will definitely have many competitive features in comparison with the previous approaches.