![]()

Self-timed Datapath Synthesis (SEDATE)

The SEDATE project is funded by EPSRC and is a collaborative project between the Universities of Manchester, Newcastle and Edinburgh.

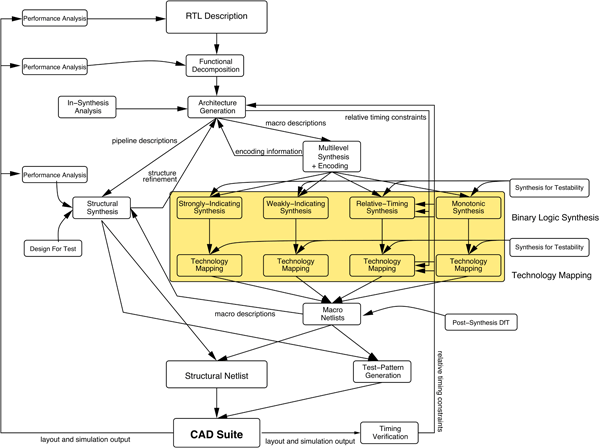

Process variation makes timing closure complex in DSM CMOS technologies. Consequently, synchronous circuits are often clocked at only 50% of their potential maximum operating speed. Self-timed circuits are data-driven and not controlled by external timing signals, making them tolerant of large variations in the arrival times of inputs. Datapaths are encoded so that function completion is signalled by the generation of a valid output. Several EDA tools exist to synthesise self-timed control circuits, but datapath synthesis methods are less developed. SEDATE is a complete EDA tool flow that provides a platform for research into all aspects of self-timed datapath synthesis from RTL functional decomposition to design-for-test and test pattern generation.

The complete SEDATE tool flow comprises the following components:

Functional Decomposition

Datapaths are modelled using Petri-nets. The causal relationship between processes is analysed to exploit relative-timing and early-evaluation techniques. The architecture is determined independently of its physical implementation allowing a range of circuit styles in a single design.

Multi-Valued Logic Synthesis and Encoding

MV-synthesis optimises operations prior to encoding and assigns codes to minimise the binary implementation of the operation. Encoding allows the selection of low power m-of-n codes which permit techniques such as weak-indication to be exploited more effectively

Structural Synthesis

The performance of self-timed datapaths is determined by the communication mechanisms between combinational logic blocks. Techniques such as slack-matching improve performance by adding stages to pipelines. Bit-level pipelining and anti-tokens exploit differences in the propagation delays of signals, increasing the effectiveness of relative-timing techniques

Binary Logic Synthesis

In self-timed design, signals must be indicated (acknowledged) by other signals to ensure they have occurred. Circuits are classified by the delay assumptions employed in their construction:

- Strongly-Indicating - Each output signal indicates all of its inputs.

- Weakly-Indicating - Output signals collectively indicate input signals.

- Relative-Timing - arrival time differences of signals are exploited to indicate signals implicitly.

- Monotonic - all internal signals are implicitly acknowledged

Design-for-Test

Many sequential elements within combinational logic blocks make testing of self-timed datapaths complex. DfT architectures are created by breaking feedback loops within pipelines and inserting a scan chain into the smallest subset of sequential elements that maintains test coverage.

Timing Validation

Two forms of validation are applied to timing constraints:

- In-synthesis - static performance estimators.

- Post-synthesis - dynamic constraint checking

Workplan

The orignal work plan can be found in the abbreviated

Case for Support.

The envisaged design flow is shown below: