The Advanced Processor Technologies Group Projects

The group is involved in a large number of research projects that cover a range of topics. (Amulet, Balsa, Galaxy, Cadre, Exact Arithmetic, Fire, Interconnect, Jamaica, JASPA, LARD, MUCS PCB, PREST, SPA)

Asynchronous Processors

- Amulet

-

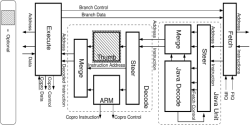

Since 1990 the AMULET group has been developing processors. This includes a series ARM-compatible general purpose asynchronous processors. The AMULET3 is the latest version.

Balsa

- Balsa

Balsa is both a framework for synthesising asynchronous (clockless) hardware systems and the language for describing such systems. The approach adopted is that of syntax-directed compilation into communicating handshaking components and closely follows the Tangram system of Philips. The advantage of this approach is that the compilation is transparent: there is a one-to-one mapping between the language constructs in the specification and the intermediate handshake circuits that are produced. It is relatively easy for an experienced user to envisage the architecture of the circuit that results from the original description. Incremental changes made at the language level result in predictable changes at the circuit implementation level. This is important if optimisations and design-tradeoffs are to be made easily and contrasts with a VHDL description in which small changes in the specification may make radical alterations to the resulting circuit.

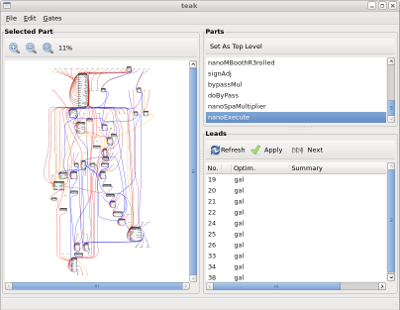

Teak

- Teak

Teak is a tool for creating asynchronous implementations of circuit descriptions written in the Balsa language. Like Balsa, Teak uses an intermediate representation in which networks of components (Teak networks) drawn from a fixed library of parameterisable templates (Teak components) are connected together using handshaking channels. Unlike Balsa, these networks are elastic.

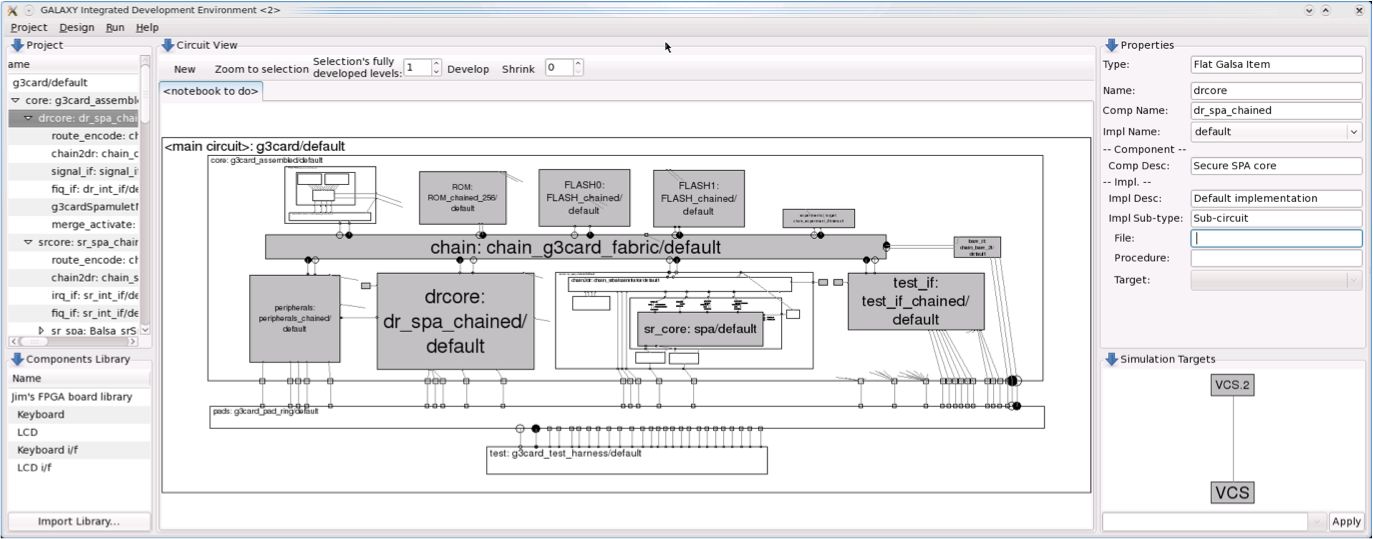

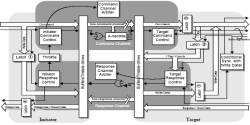

GALAXY

- Galaxy - AsipIDE

GALAXY provides an integrated GALS (Globally Asynchronous, Locally Synchronous) design flow, together with novel Network-on-Chip capabilities, that will materially aid embedded system design for a significant class of problems. We aim to remove existing barriers to the adoption of the technology by providing an interoperability framework between the existing open and commercial CAD tools that will support development of heterogeneous systems at the different levels of abstraction. The project will evaluate the ability of the GALS approach to solve system integration issues and, by implementing a complex wireless communication system on an advanced 45nm CMOS process, explore the low EMI properties, inherent low-power features and robustness to process variability problems in nanoscale geometries.

Low Power Digital Signal Processing

- CADRE

CADRE is an asynchronous embedded DSP for Mobile Phone Applications.

Exact Arithmetic

- Exact Arithmetic

-

Conventional representations of numbers within computer storage introduce errors. The exact arithmetic project aims to remove these errors while still attaining reasonable speed.

Large-scale neural network hardware

- FIRE

Asynchronous devices for implementing artificial neural networks using a device which emulates the firing behaviour of a biological neuron.

On-chip interconnect

- MARBLE, CHAIN, Network Modelling, QoS, GALS

-

Self-timed buses and delay-insensitive networks for SoC (System-on-Chip) interconnection.

Chip Multi-Processors

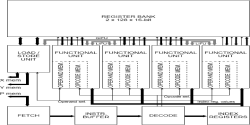

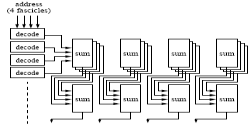

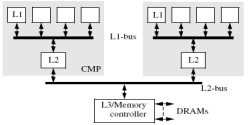

- Jamaica

The Jamaica project is investigating the design of next generation chip multi-processors and their accompanying parallel software environments. A high-performance parallel simulator supports experiments with processor design, operating system design and dynamic, parallelizing compiler optimizations.

Java Accelerator

- JASPA

Research is being carried out in the APT group to try and improve the execution speed of Java programs in embedded systems, with low memory requirements, by adding hardware support for Java execution.

LARD

- LARD

LARD is a hardware description language developed for describing asynchronous systems - though little is specific to that purpose, so you could use it to descibe synchronous systems if you wanted, or even as a general purpose programming language.

MUCS PCB

- MUCS PCB

The MUCS-PCB software was developed between 1985 and 1992 as part of a research project exploring PCB routing algorithms. The package is aimed at producing multilayer (2-16 layer) digital PCBs and was used for a number of years for routing boards designed in the department of computer science for production at our local PCB fab.

Power REduction for System Technology

- PREST

-

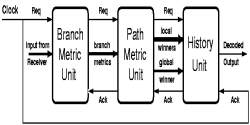

Research into a novel techniques for achieving low power electronic design, the PREST project designed a low power Viterbi decoder.

Synthesised Processor Architectures

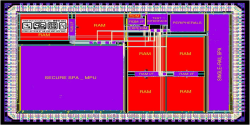

- SPA

-

Using a combination of commercial and self created tools, the group has designed the SPA processor. SPA forms part of two smart card projects to exploit the benefits of asynchronous design in security applications. The SPA processor forms part of the JASPA Java accelerator processor.