The G3CARD Project

G3CARD is an EU funded project (project number IST-1999-13515) under Framework Programme 5

The G3CARD project is intended to produce smartcards based around asynchronous processors. The motivation is to improve security against non-invasive attacks.

The greatest vulnerability of a smartcard is that a cycle-by-cycle energy analysis of operations can reveal internal data such as the number of "0"s and "1"s in a crypto-key. It is believed that an asynchronous processor will disguise this signature by blurring the definition of cycles and overlapping operations in a non-deterministic manner. In addition many of the delay insensitive codes used for implementation use the same energy to communicate a bit regardless of its state.

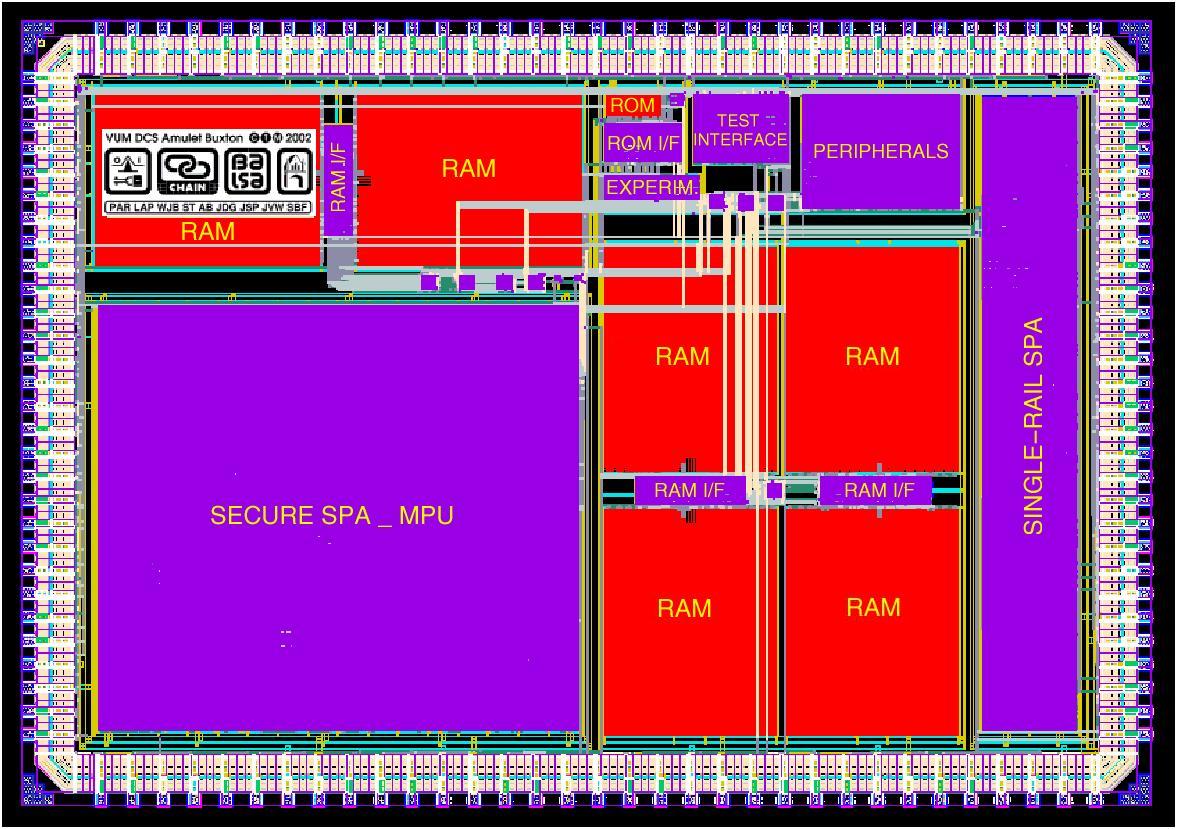

Manchester University's role in G3CARD is to produce a smartcard chip based around an asynchronous ARM microprocessor. This will be based on knowledge gleaned in earlier projects developing the AMULET microprocessors. Unfortunately these earlier processors show distinct power signatures due to some implementational decisions so SPA, a new, lower performance, completely synthesised asynchronous ARM has been developed and is currently being tested. This is the biggest project so far using Balsa, APT's own asynchronous synthesis system.

JASPA is a Java accelerated development of the SPA processor.