SpiNNaker Project

What are the Goals of the SpiNNaker Project?

SpiNNaker is a novel massively-parallel computer architecture, inspired by the fundamental

structure and function of the human brain, which itself is composed of billions of simple

computing elements, communicating using unreliable spikes.

The project's objectives are two-fold:

-

To provide a platform for high-performance massively parallel processing appropriate

for the simulation of large-scale neural networks in real-time, as a research tool for neuroscientists,

computer scientists and roboticists

- As an aid in the investigation of new computer architectures, which break the rules of conventional supercomputing, but which we hope will lead to fundamentally new and advantageous principles for energy-efficient massively-parallel computing

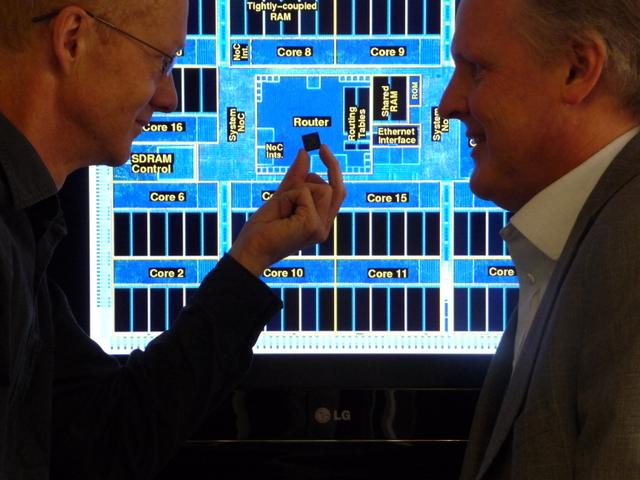

The prototype SpiNNaker chips were delivered in December 2009 and we were

very happy to discover that they were fully functional! A more detailed

description of the Spinnaker chip can be found

"The SpiNNaker Chip"

A 48-chip board has been developed to be the building block for SpiNNaker

machines in a range of different sizes. The goal is to be able to simulate

a single network consisting of one billion simple neurons, requiring a

machine with over 50,000 chips.

Information on development boards annd access to SpiNNaker machines can be found at: "SpiNNaker Access"

SpiNNaker Project, Partners & Timeline

Formally, the SpiNNaker project began in 2005, with funding from EPSRC, although some informal work on the architecture had been ongoing for several years before this. The project was a collaboration between several universities and industrial partners:

- University of Manchester

- University of Southampton

- University of Cambridge

- University of Sheffield

- ARM Ltd

- Silistix Ltd

- Thales

The APT group in Manchester were responsible for the system architecture and the design of the SpiNNaker chip itself. Southampton was responsible for software to map user's problems onto the processor array. Sheffield and Southampton developed demonstrators for the technology and Cambridge developed an FPGA-based alternative to SpiNNaker to act as a benchmark by which to evaluate the advantages of the SpiNNaker architecture.

ARM Ltd supplied the ARM 968 processor core that was used as the main computing

resource on the SpiNNaker chip. Silistix Ltd provided the asynchronous interconnect

fabric that is used on the chip to connect the processors to the external memory and

to the packet router.

The first design was a test chip, delivered late in 2009. It contained all of the basic

elements of the full chip: two ARM processors, the asynchronous interconnect, the

router and memory controller. With the success of this chip, we moved on to the

much larger full-chip with all eighteen processors, which was shipped for fabrication

in December 2010, parts arriving for testing in May 2011.

We are now on the follow-up project, called BIMPA, which focuses more on the construction of larger machines with SpiNNaker together with the software infra-structure and applications. One of our major goals is to see SpiNNaker being used by researchers in neuroscience, computer science and robotics and we are now making the hardware available to the research community, initially through four-chip development boards. Later in 2012 we expect to make larger 48-chip boards and multi-board racks available.

EPSRC support for the BIMPA project continues under the Human Brain Project and the ERC BIMPC project Engineering Research Council (ERC)