The Advanced Processor Technologies Research Group

Doug Edwards: publications

- De-Elastisation: From Asynchronous Dataflows to Synchronous Circuits

- Optimised Synthesis of Asynchronous Elastic Dataflows by Leveraging Clocked EDA

- Automatic data path extraction in large-scale register-transfer level designs

- Statistical Analysis Model of Nano-CMOS Variability with Intra-die Correlation Due to Proximity

- Computational Performance Optimisation for Statistical Analysis of the Effect of Nano-CMOS Variability on Integrated Circuits

- Self-Timed Section Carry Based Carry Lookahead Adders and the Concept of Alias Logic

- Redundant Logic Insertion and Latency Reduction in Self-Timed Adders

- Critical path analysis in data-driven asynchronous pipelines

- Survey of asynchronous networks-on-chip. (In Chinese)

- Area Efficient Asynchronous SDM Routers Using 2-Stage Clos Switches

- Routing of Asynchronous Clos Networks

- Indicating combinational logic decomposition

- Asynchronous spatial division multiplexing router

- Description-level optimisation of synthesisable asynchronous circuits

- Asynchronous Data-Driven Circuit Synthesis

- An Asynchronous Routing Algorithm for Clos Networks

- A Complete Synthesis Method for Block-Level Relaxation in Self-Timed Datapaths

- Self-Timed Realization of Combinational Logic

- M-of-N Code Decomposition for Indicating Combinational Logic

- Computation Reduction for Statistical Analysis of the Effect of nano-CMOS Variability on Asynchronous Circuits

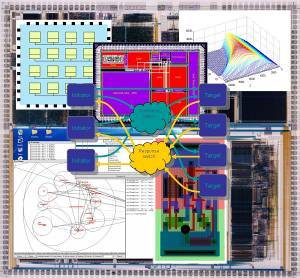

- Integrated Design Environment for Reconfigurable HPC

- A low latency wormhole router for asynchronous on-chip networks

- LLA: A low-latency asynchronous control with applications

- Building Asynchronous Routers with Independent Sub-Channels

- A Synthesisable Quasi-Delay Insensitive Result Forwarding Unit for an Asynchronous Processor

- Heterogeneously encoded dual-bit self-timed adder

- Teak: A Token-Flow Implementation for the Balsa Language

- HPAP: A High Performance Control Circuit for Asynchronous Pipeline Design

- Asynchronous Data-Driven Circuit Synthesis

- Prime Indicants: A Synthesis Method for Indicating Combinational Logic Blocks

- Dual-Sum Single-Carry Self-Timed Adder Designs

- Adaptive Stochastic Routing in Fault-tolerant On-chip Network

- Forward and Backward Guarding in Early Output Logic

- Self-Timed Full Adder Designs based on Hybrid Input Encoding

- Power, Delay and Area Efficient Self-Timed Multiplexer and Demultiplexer Designs

- A delay efficient robust self-timed full adder

- Automatic Compilation of Data-Driven Circuits

- Efficient realization of strongly indicating function blocks

- A new design technique for weakly indicating function blocks

- Adaptive routing strategies for fault-tolerant on-chip networks in dynamically reconfigurable systems

- Performance-driven syntax-directed synthesis of asynchronous processors

- CSP Transactors for Asynchronous Transaction Level Modeling and IP Reuse

- Speeding Up Verilog Gate-Level Simulation with Bi-Partitioning

- Low power synthesis of XOR-XNOR intensive combinational logic

- Synthesis of Power and Delay optimized NIG structures

- A Framework for Distributed Simulation for Asynchronous Handshake Circuits

- Synthesising Heterogeneously Encoded Systems

- Test Pattern Generation and Partial-Scan Methodology for an Asynchronous SoC Interconnect.

- Attacking Control Overhead to Improve Synthesised Asynchronous Circuit Performance.

- Software Visualisation Techniques Adapted and Extended for Asynchronous Hardware Design.

- DiSigncryption: An Integration of Agent-based Signature Delegation with Distributed Reputation Management Scheme.

- Asynchronous On-Chip Networks.

- Efficient Synthesis of Speed Independent Combinational Logic Circuits

- Synthesis of Asynchronous Circuits using Early Data Validity.

- Adding Testability to an Asynchronous Interconnect for GALS SoC.

- Automatic Scan Insertion and Pattern Generation for Asynchronous Circuits

- Simulation and Analysis of Synthesised Asynchronous Circuits

- Delay-Insensitive, Point-to-Point Interconnect using m-of-n codes

- A Burst-Mode Oriented Back-End for the Balsa Synthesis System

- Balsa: An Asynchronous Hardware Synthesis Language

- Towards a Framework for the Distributed Simulation of Asynchronous Hardware

- Synthesising an asynchronous DMA controller with Balsa

- AMULET3: a 100 MIPS Asynchronous Embedded Processor

- The Balsa Asynchronous Circuit Synthesis System

- AMULET3i - an Asynchronous System-on-Chip

- Compiling the Language Balsa to Delay Insensitive Hardware.

- Tools for Validating Asynchronous Digital Circuits

- Logic for Low Power Consumption in Asynchronous Circuits

- Pitfalls in Asynchronous Design.

This website will look much better in a web browser that supports web standards, but it is accessible to any browser or Internet device.