The Advanced Processor Technologies Research Group

Luis Plana: publications

- Fast Predictive Handshaking in Synchronous FPGAs for Fully Asynchronous Multi-Symbol Chip Links. Application to SpiNNaker 2-of-7 Links

- Analysis of FPGA and Software Approaches to Simulate Unconventional Computer Architectures

- ConvNets Experiments on SpiNNaker

- Accelerating Interconnect Analysis using High-Level HDLs and FPGA SpiNNaker as a Case Study

- Breaking The Millisecond Barrier On SpiNNaker: Implementing Asynchronous Event-Based Plastic Models With Microsecond Resolution

- A framework for plasticity implementation on the SpiNNaker neural architecture

- SpiNNaker: Enhanced multicast routing

- A framework for plasticity implementation on the SpiNNaker neural architecture

- SpiNNaker - programming model

- Event-based neural computing on an autonomous mobile platform

- The SpiNNaker Project

- On Generating Multicast Routes for SpiNNaker, a Massively-Parallel System for Neural Net Simulation

- A real-time simulator of a biological visual system composed of a silicon retina and SpiNNaker chips

- Overview of the SpiNNaker system architecture

- SpiNNaker: Fault Tolerance in a Power- and Area- Constrained Large-Scale Neuromimetic Architecture

- Real-Time Interface Board for Closed-Loop Robotic Tasks on the SpiNNaker Neural Computing System

- A location-independent direct link neuromorphic interface

- Live demonstration: Ethernet communication linking two large-scale neuromorphic systems

- SpiNNaker: A 1W 18-core System-on-Chip for Massively-Parallel Neural Network Simulation

- Managing Burstiness and Scalability in Event-Driven Models on the SpiNNaker Neuromimetic System

- Analytical Assessment of the Suitability of Multicast Communications for the SpiNNaker Neuromimetic System

- Event-Driven MLP Implementation on Neuromimetic Hardware

- SpiNNaker: A Multi-Core System-on-Chip for Massively-Parallel Neural Net Simulation

- Overview of the SpiNNaker system architecture

- An Asynchronous Fully Digital Delay Locked Loop for DDR SDRAM Data Recovery.

- A hierarchical configuration system for a massively parallel neural hardware platform.

- Scalable Communications for a Million-Core Neural Processing Architecture

- SpiNNaker: Design and Implementation of a GALS Multi-Core System-on-Chip

- Event-Driven SpiNNaker Simulation

- An Event-Driven Model for the SpiNNaker Virtual Synaptic Channel

- Managing Burstiness and Scalability in Event-Driven Models on the SpiNNaker Neuromimetic System

- Event-driven configuration of a neural network CMP system over an homogeneous interconnect fabric

- Description-level optimisation of synthesisable asynchronous circuits.

- Asynchronous Data-Driven Circuit Synthesis

- Modeling Spiking Neural Networks on SpiNNaker

- Algorithm for Mapping Multilayer BP Networks onto the SpiNNaker Neuromorphic Hardware

- SpiNNaker: Effects of Traffic Locality and Causality on the Performance of the Interconnection Network

- Scalable Event-Driven Native Parallel Processing: The SpiNNaker Neuromimetic System

- Efficient Parallel Implementation of Multilayer Backpropagation Network on Torus-connected CMPs

- A communication infrastructure for a million processor machine

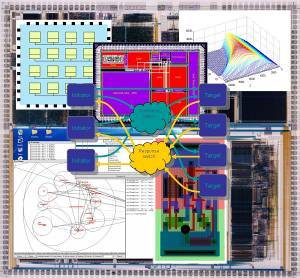

- System-on-Chip Design and Implementation

- Adaptive Admission Control on the SpiNNaker MPSOC

- A Synthesisable Quasi-Delay Insensitive Result Forwarding Unit for an Asynchronous Processor

- Understanding the Interconnection Network of SpiNNaker

- Asynchronous Data-Driven Circuit Synthesis

- A Token-Managed Admission Control System for QoS Provision on a Best-Effort GALS Interconnect

- Event-Driven Configuration of a Neural Network CMP System over a Homogeneous Interconnect Fabric

- A Universal Abstract-Time Platform for Real-Time Neural Networks

- Fault-Tolerant Delay-Insensitive Inter-Chip Communication

- System Level Modelling for SpiNNaker CMP System

-

SpiNNaker: The design automation problem

-

An Admission Control System for QoS Provision on a Best-effort GALS Interconnect

-

Automatic Compilation of Data-Driven Circuits

-

SpiNNaker: Mapping Neural Networks onto a Massively-Parallel Chip Multiprocessor

-

An On-Chip and Inter-Chip Communications Network for the SpiNNaker Massively-Parallel

Neural Net Simulator

- Performance-driven syntax-directed synthesis of asynchronous processors.

- A GALS Infrastructure for a Massively Parallel Multiprocessor.

- Attacking Control Overhead to Improve Synthesised Asynchronous Circuit Performance.

- The Design and Test of a Smartcard Chip Using a CHAIN Self-timed Network-on-Chip

- SPA - A Secure Amulet Core for Smartcard Applications

- An Investigation into the Security of Self-timed Circuits

- SPA - A Synthesisable Amulet Core for Smartcard Applications

This website will look much better in a web browser that supports web standards, but it is accessible to any browser or Internet device.