The Advanced Processor Technologies Research Group

Linda Brackenbury: publications

- Early stopping turbo decoders: a high-throughput, low-energy bit-level approach and implementation

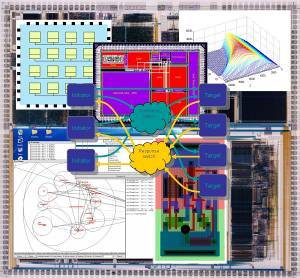

- System-on-Chip Design and Implementation

- Pre-processing of Convolutional Codes for Reducing Decoding Power Consumption

- No-Handshake Asynchronous Survivor memory Unit for a Viterbi Decoder

- Lowering power in an experimental RISC processor

- Design and implementation of an energy efficient, parallel, asynchronous DSP

- Energy efficient functional unit for a compute-intensive asynchronous DSP.

- Energy efficient functional unit for a parallel asynchronous DSP.

- An Asynchronous, Iterative Implementation of the Original Booth Multiplication Algorithm

- Design of asynchronous function unit & software development tools for a low-power DSP.

- Functional Unit for Low-Power DSP Architecture

- CADRE: an Asynchronous Embedded DSP for Mobile Phone Applications

- Low power asynchronous DSP for digital mobile phones.

- Applying asynchronous techniques to a Viterbi decoder design

- Combining SOI Technology and Asynchronous Design Techniques for Power Reduction.

- A simulation study to quantify the advantages of silicon-on-insulator (SOI) technology for low power

- CADRE: A Low-Power, Low-EMI DSP Architecture for Digital Mobile Phones

- A Low-Power Self-Timed Viterbi Decoder

- Exploiting Typical DSP Data Access Patterns and Asynchrony for a Low Power Multiported Register Bank

- The Optical Encryption of Digital Data

- Exploiting Asynchronous Self-Timed Techniques on SOI Technology for Low Power

- An Asynchronous Viterbi Decoder

- A low-power asynchronous DSP architecture for digital mobile phone chipsets

- An Instruction Buffer for a Low-Power DSP

- Power reduction in self-timed circuits using early-open latch controllers

- Reconfigurable Latch Controllers for Low Power Asynchronous Circuits

- Re-configurable Latch Controllers for Low Power Asynchronous Circuits

- Optical solution to the Lee algorithm by use of symbolic substitution

- Differential register bank design for self timed differential bipolar technology

- Design and modelling of a high performance differential bipolar self-timed microprocessor

- Transforming Architectural Models Into High Performance Concurrent Implementations

This website will look much better in a web browser that supports web standards, but it is accessible to any browser or Internet device.