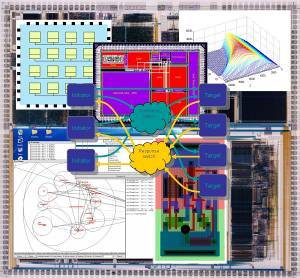

The Advanced Processor Technologies Research Group

Mikel Luján: publications

-

HAPPY: Hybrid Address-based Page Policy in DRAMs

- DReAM: Dynamic Re-arrangement of Address Mapping to Improve

- Optimizing Indirect Branches in Dynamic Binary Translators

- A Survey on Design Approaches to Circumvent Permanent Faults in Networks-on-Chip

- Analysis of FPGA and Software Approaches to Simulate Unconventional Computer Architectures

- AMON: Advanced Mesh-like Optical NoC

- Effective Barrier Synchronization on Intel Xeon Phi Coprocessor

- Introducing SLAMBench, a performance and accuracy benchmarking methodology for SLAM

- Accelerating Interconnect Analysis using High-Level HDLs and FPGA SpiNNaker as a Case Study

- SpiNNaker: Enhanced multicast routing

- An Empirical Evaluation of High-level Synthesis Languages and Tools for Database Acceleration

- On Generating Multicast Routes for SpiNNaker, a Massively-Parallel System for Neural Net Simulation

- SpiNNaker: Fault Tolerance in a Power- and Area- Constrained Large-Scale Neuromimetic Architecture

- Optimizing software runtime systems for speculative parallelization

- Managing Burstiness and Scalability in Event-Driven Models on the SpiNNaker Neuromimetic System

- Software transactional memories for Scala

- Reservation-based Network-on-Chip timing models for large-scale architectural simulation

- Architectural Support for Exploiting Fine Grain Parallelism

- A case for Exiting a Transaction in the Context of Hardware Transactional Memory

- SnCTM: Reducing False Transaction Aborts by Adaptively Changing the Source of Conflict Detection

- Analytical Assessment of the Suitability of Multicast Communications for the SpiNNaker Neuromimetic System

- The Economics of Garbage Collection

- Scalable Object-Aware Hardware Transactional Memory

- Clustering JVMs with Software Transactional Memory Support

- Improving Performance by Reducing Aborts in Hardware Transactional Memory

- Modeling Spiking Neural Networks on SpiNNaker

- Algorithm for Mapping Multilayer BP Networks onto the SpiNNaker Neuromorphic Hardware

- SpiNNaker: Effects of Traffic Locality and Causality on the Performance of the Interconnection Network

- Efficient Parallel Implementation of Multilayer Backpropagation Network on Torus-connected CMPs

- On the Performance of Contention Managers for Complex Transactional Memory Benchmarks

- Understanding the Interconnection Network of SpiNNaker

- Event-Driven Configuration of a Neural Network CMP System over a Homogeneous Interconnect Fabric

- Profiling Transactional Memory Applications

- Steal-on-Abort: Improving Transactional Memory Performance through Dynamic Transaction Reordering

- An Object-Aware Hardware Transactional Memory System

- DiSTM: A Software Transactional Memory Framework for Clusters

- Advanced Concurrency Control for Transactional Memory using Transaction Commit Rate

- A first insight into object-aware hardware transactional memory

- Lee-TM: A Non-trivial Benchmark for Transactional Memory

- Introducing Aspects to the Implementation of a Java Fork/Join Framework

- Adaptive Loop Tiling for a Multi-cluster CMP

- Speculative Parallelization - Eliminating the Overhead of Failure

- A Study of a Transactional Parallel Routing Algorithm

- Towards Intelligent Analysis Techniques for Object Pretenuring

This website will look much better in a web browser that supports web standards, but it is accessible to any browser or Internet device.