The Advanced Processor Technologies Research Group

Jim Garside: publications

-

HAPPY: Hybrid Address-based Page Policy in DRAMs

- DReAM: Dynamic Re-arrangement of Address Mapping to Improve

- Asynchronous Dataflow De-Elastisation For Efficient Heterogeneous Synthesis

- On-chip Order-Exploiting Routing Table Minimization for a Multicast Supercomputer Network

- AutoCLK: A Promising Approach Toward GALSification

- Optimizing Indirect Branches in Dynamic Binary Translators

- Network traffic explorationon a many-core computing platform: SpiNNaker real-time traffic visualiser

- Analysis of FPGA and Software Approaches to Simulate Unconventional Computer Architectures

- Accelerating Interconnect Analysis using High-Level HDLs and FPGA SpiNNaker as a Case Study

- Deadlock Recovery in Asynchronous Networks on Chip in the Presence of Transient Faults

- De-Elastisation: From Asynchronous Dataflows to Synchronous Circuits

- Optimised Synthesis of Asynchronous Elastic Dataflows by Leveraging Clocked EDA

- Exploiting Synchrony for Area and Performance Improvement in the Asynchronous Domain

- High-level Synthesis of GALS Systems

- SpiNNaker - programming model

- Protecting QDI Interconnects from Transient Faults Using Delay-Insensitive Redundant Check Codes

- On-Line Detection of the Deadlocks Caused by Permanently Faulty Links in Quasi-Delay Insensitive Networks on Chip

- An Asynchronous SDM Network-on-Chip Tolerating Permanent Faults

- Automatic data path extraction in large-scale register-transfer level designs

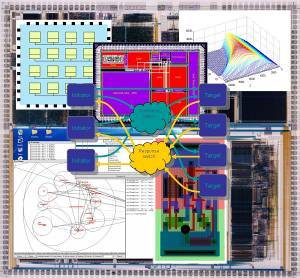

- Overview of the SpiNNaker system architecture

- SpiNNaker: Fault Tolerance in a Power- and Area- Constrained Large-Scale Neuromimetic Architecture

- Automatic controller detection for large scale RTL designs

- Transient fault tolerant QDI interconnects using redundant check code

- SpiNNaker: A 1W 18-core System-on-Chip for Massively-Parallel Neural Network Simulation

- SpiNNaker: A Multi-Core System-on-Chip for Massively-Parallel Neural Net Simulation

- Area Efficient Asynchronous SDM Routers Using 2-Stage Clos Switches

- Overview of the SpiNNaker system architecture

- An Asynchronous Fully Digital Delay Locked Loop for DDR SDRAM Data Recovery

- Scalable Communications for a Million-Core Neural Processing Architecture

- The Amulet chips: Architectural Development for Asynchronous Microprocessors

- Fault-Tolerant Delay-Insensitive Inter-Chip Communication

- A Programmable Adaptive Router for a GALS Parallel System

- Design and implementation of an energy efficient, parallel, asynchronous DSP

- Sensitive Registers: a Technique for Reducing the Fetch Bandwidth in Low-Power Microprocessors

- Modernisation of Teaching in Embedded Systems Design - An International Collaborative Project

- A Low-Power Processor Architecture Optimized for Wireless Devices.

- A Quasi-Delay-Insensitive Method to Overcome Transistor Variation.

- Energy efficient functional unit for a parallel asynchronous DSP.

- An Asynchronous, Iterative Implementation of the Original Booth Multiplication Algorithm

- A CAM with mixed serial-parallel comparison for use in low energy caches

- Designing Robust Asynchronous Circuits

- An asynchronous copy-back cache architecture

- Early

Output Logic using Anti-Tokens

- SPA - A Secure Amulet Core for Smartcard Applications

- Adaptive Pipeline Structures for Speculation Control

- Adaptive Pipeline Depth Control for Processor Power-Management

- An Asynchronous Victim Cache

- An Adaptive Serial-Parallel CAM Architecture for Low-Power Cache Blocks

- SPA - A Synthesisable Amulet Core for Smartcard Applications

- A Comparative Power Analysis of an Asynchronous Processor

- Power Management in the AMULET Microprocessors

- AMULET3i Cache Architecture

- A Practical Comparison of Asynchronous Design Styles

- AMULET3: a 100 MIPS Asynchronous Embedded Processor

- AMULET3i - an Asynchronous System-on-Chip

- AMULET3i - an Asynchronous System-on-Chip

- AMULET3 Revealed

- Memory Faults in Asynchronous Microprocessors

- Reconfigurable Latch Controllers for Low Power Asynchronous Circuits

- AMULET2e: An Asynchronous Embedded Controller

- Asynchronous Embedded Control

- Re-configurable Latch Controllers for Low Power Asynchronous Circuits

- AMULET3: A High-Performance Self-Timed ARM Microprocessor

- AMULET1: An Asynchronous ARM Microprocessor

- A Result Forwarding Mechanism for Asynchronous Pipelined Systems

- AMULET2e: An Asynchronous Embedded Controller

- The AMULET2e Cache System.

- AMULET2e.

- AMULET2e.

- A Comparison of Power Consumption in some CMOS Adder Circuits

- A Cache Line Fill Circuit for a Micropipelined Asynchronous Microprocessor

- AMULET1: A Micropipelined ARM

- The Design and Evaluation of an Asynchronous Microprocessor

- A CMOS VLSI Implementation of an Asynchronous ALU

- A Micropipelined ARM

- Register Locking in an Asynchronous Microprocessor

This website will look much better in a web browser that supports web standards, but it is accessible to any browser or Internet device.