The Advanced Processor Technologies Research Group

Steve Furber: publications

- Synapse-Centric Mapping of Cortical Models to the SpiNNaker Neuromorphic Architecture

- Bio-inspired massively-parallel computation

- The SpiNNaker project

- Large-Scale Neuromorphic Computing Systems

- Neuromorphic sampling on the SpiNNaker and Parallella chip multiprocessors

- Efficient SpiNNaker simulation of a heteroassociative memory using the Neural Engineering Framework

- Large-scale simulations of plastic neural networks on neuromorphic hardware

- Brain-inspired computing

- Fast Predictive Handshaking in Synchronous FPGAs for Fully Asynchronous Multi-Symbol Chip Links. Application to SpiNNaker 2-of-7 Links

- Network traffic exploration on a many-core computing platform: SpiNNaker real-time traffic visualiser

- Transport-Independent Protocols for Universal AER Communications

- An efficient SpiNNaker implementation of the Neural Engineering Framework

- Accuracy and Efficiency in Fixed-Point Neural ODE Solvers

- Robustness of spiking Deep Belief Networks to noise and reduced bit precision of neuro-inspired hardware platforms

- Real-time event-driven spiking neural network object recognition on the SpiNNaker platform

- Live demonstration: Real-time event-driven object recognition on SpiNNaker

- ConvNets Experiments on SpiNNaker

- Breaking The Millisecond Barrier On SpiNNaker: Implementing Asynchronous Event-Based Plastic Models With Microsecond Resolution

- Scalable Energy-Efficient, Low-Latency Implementations of Spiking Deep Belief Networks on SpiNNaker

- Reliable computation with unreliable computers

- Live Demonstration: Handwritten Digit Recognition Using Spiking Deep Belief Networks on SpiNNaker

- Introducing SLAMBench, a performance and accuracy benchmarking methodology for SLAM

- A framework for plasticity implementation on the SpiNNaker neural architecture

- SpiNNaker: Enhanced multicast routing

- Towards Real-World Neurorobotics: Integrated Neuromorphic Visual Attention

- SpinNNaker: The world's biggest NoC

- A framework for plasticity implementation on the SpiNNaker neural architecture

- Optimising the Overall Power Usage on the SpiNNaker Neuromimetic Platform

- Real-Time Million-Synapse Simulation of Rat Barrel Cortex

- SpiNNaker - programming model

- Engineering a thalamo-cortico-thalamic circuit on SpiNNaker: a preliminary study towards modelling sleep and wakefulness

- Event-based neural computing on an autonomous mobile platform

- The SpiNNaker Project

- On Generating Multicast Routes for SpiNNaker, a Massively-Parallel System for Neural Net Simulation

- A real-time simulator of a biological visual system composed of a silicon retina and SpiNNaker chips

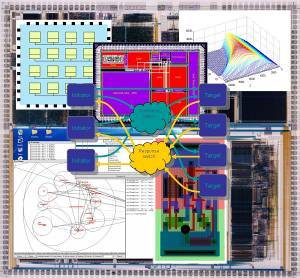

- Overview of the SpiNNaker system architecture

- SpiNNaker: Fault Tolerance in a Power- and Area- Constrained Large-Scale Neuromimetic Architecture

- Real-Time Interface Board for Closed-Loop Robotic Tasks on the SpiNNaker Neural Computing System

- Modeling Populations of Spiking Neurons for Fine Timing Sound Localization

- A location-independent direct link neuromorphic interface

- Spike-based learning of transfer functions with the SpiNNaker neuromimetic simulator

- Power analysis of large-scale, real-time neural networks on SpiNNaker

- Correctness and Performance of the SpiNNaker Architecture

- Live demonstration: Ethernet communication linking two large-scale neuromorphic systems

- SpiNNaker: A 1W 18-core System-on-Chip for Massively-Parallel Neural Network Simulation

- TO BUILD A BRAIN-Getting to the bottom of how our brains work is a monumental task, but some innovative computational tricks and a million ARM processors could help

- Live Demo: Spiking ratSLAM: Rat hippocampus cells in spiking neural hardware

- A Real-Time, Event-Driven Neuromorphic System for Goal-Directed Attentional Selection

- Managing Burstiness and Scalability in Event-Driven Models on the SpiNNaker Neuromimetic System

- Creating, documenting and sharing network models

- Modelling normal and impaired letter recognition: Implications for understanding pure alexic reading

- Large-Scale On-Chip Dynamic Programming Network Inferences using Moderated Inter-Core Communication

- A forecast-based STDP rule suitable for neuromorphic implementation

- Power-efficient simulation of detailed cortical microcircuits on SpiNNaker

- Analytical Assessment of the Suitability of Multicast Communications for the SpiNNaker Neuromimetic System

- Managing a Massively-Parallel Resource-Constrained Computing Architecture

- Population-Based Routing in the SpiNNaker Neuromorphic Architecture

- Visualising Large-Scale Neural Network Models in Real-Time

- Real Time On-Chip Implementation of Dynamical Systems with Spiking Neurons

- Event-Driven MLP Implementation on Neuromimetic Hardware

- SpiNNaker: A Multi-Core System-on-Chip for Massively-Parallel Neural Net Simulation

- Overview of the SpiNNaker system architectur

- The Impact of Technology Scaling in the SpiNNaker Chip Multiprocessor

- An Asynchronous Fully Digital Delay Locked Loop for DDR SDRAM Data Recovery.

- A hierarchical configuration system for a massively parallel neural hardware platform.

- "Serial" Effects in Parallel Models of Reading

- A forecast-based STDP rule suitable for neuromorphic implementation

- Scalable Communications for a Million-Core Neural Processing Architecture

- SpiNNaker: Design and Implementation of a GALS Multi-Core System-on-Chip

- Modelling circuit performance variations due to statistical variability: Monte Carlo static timing analysis

- Concurrent heterogeneous neural model simulation on real-time neuromimetic hardware

- Event-Driven SpiNNaker Simulation

- A Novel Programmable parallel CRC Circuit

- An Event-Driven Model for the SpiNNaker Virtual Synaptic Channel

- A forecast-based biologically-plausible STDP learning rule

- Managing Burstiness and Scalability in Event-Driven Models on the SpiNNaker Neuromimetic System

- Event-driven configuration of a neural network CMP system over an homogeneous interconnect fabric

- Distributed Configuration of Massively-Parallel Simulation on SpiNNaker Neuromorphic Hardware

- Representing and Decoding Rank Order Codes Using Polychronization in a Network of Spiking Neurons

- Maintaining real-time synchrony on SpiNNaker

- A General-Purpose Model Translation System for a Universal Neural Chip

- Interfacing Real-Time Spiking I/O with the SpiNNaker neuromimetic architecture

- STDP pattern onset learning depends on background activity

- Modeling Spiking Neural Networks on SpiNNaker

- A Novel Programmable parallel CRC Circuit

- Biologically Inspired Means for Rank-Order Encoding Images: A Quantitative Analysis

- Algorithm and Software for Simulation of Spiking Neural Networks on the Multi-Chip SpiNNaker System

- Implementing Spike-Timing-Dependent Plasticity on SpiNNaker Neuromorphic Hardware

- The Leaky Integrate-and-Fire Neuron: A Platform for Synaptic Model Exploration on the SpiNNaker Chip

- Algorithm for Mapping Multilayer BP Networks onto the SpiNNaker Neuromorphic Hardware

- SpiNNaker: Effects of Traffic Locality and Causality on the Performance of the Interconnection Network

- Scalable Event-Driven Native Parallel Processing: The SpiNNaker Neuromimetic System

- Efficient Parallel Implementation of Multilayer Backpropagation Network on Torus-connected CMPs

- A communication infrastructure for a million processor machine

- The Amulet chips: Architectural Development for Asynchronous Microprocessors

- Adaptive Admission Control on the SpiNNaker MPSOC

- Biologically-Inspired Massively-Parallel Architectures - computing beyond a million processors

- A Multicast Routing Scheme for a Universal Spiking Neural Network Architecture

- Understanding the Interconnection Network of SpiNNaker

- A Token-Managed Admission Control System for QoS Provision on a Best-Effort GALS Interconnect

- Event-Driven Configuration of a Neural Network CMP System over a Homogeneous Interconnect Fabric

- Optimal Connectivity In Hardware-Targetted MLP Networks

- Evaluating Rank-order Code Performance Using A Biologically Derived Retinal Model

- A Universal Abstract-Time Platform for Real-Time Neural Networks

- Fault-Tolerant Delay-Insensitive Inter-Chip Communication

- A Programmable Adaptive Router for a GALS Parallel System

- System Level Modelling for SpiNNaker CMP System

-

SpiNNaker: The design automation problem

-

The Deferred Event Model for Hardware-Oriented Spiking Neural Networks

-

An Admission Control System for QoS Provision on a Best-effort GALS Interconnect

-

Virtual Synaptic Interconnect Using an Asynchronous Network-on-Chip

-

SpiNNaker: Mapping Neural Networks onto a Massively-Parallel Chip Multiprocessor

-

Efficient Modelling of Spiking Neural Networks on a Scalable Chip Multiprocessor

-

An On-Chip and Inter-Chip Communications Network for the SpiNNaker Massively-Parallel

Neural Net Simulator

-

The Future of Computer Technology and its Implications for the Computer Industry

-

A GALS Infrastructure for a Massively Parallel Multiprocessor

-

Neural systems engineering

-

Maximising Information Recovery from Rank-Order Codes

-

Sparse Distributed Memory using Rank-Order Neural Codes

-

The Design of a Dataflow Coprocessor for Low Power Embedded Hierarchical Processing.

-

Information Recovery from Rank-Order Encoded Images

-

On-Chip and Inter-Chip networks for Modelling Large-Scale Neural Systems.

-

High-Performance Computing for Systems of Spiking Neurons.

-

Future Trends in SoC Interconnect.

-

The Design of an Asynchronous Carry-Lookahead Adder Based on

Data Characteristics.

-

A spiking neural sparse distributed memory implementation for

learning and predicting temporal sequences.

-

An associative memory for the on-line recognition and prediction

of temporal sequences.

-

A system for transmitting a coherent burst of activity through a

network of spiking neurons.

- A low power

embedded dataflow coprocessor.

- Future

Trends in SoC Interconnect

- An Asynchronous On-Chip Network Router with Quality-of-Service (QoS) Support.

- A Sparse Distributed Memory based upon N-of-M Codes.

- The Design of a Low-Power Asynchronous Multiplier.

- Minimizing the Power Consumption of an Asynchronous Multiplier.

- Design and Analysis of a Self-Timed Duplex Communication System.

- The Design and Test of a Smartcard Chip Using a CHAIN Self-timed Network-on-Chip

- An Asynchronous Ternary Logic Signalling System

- An asynchronous low latency arbiter for Quality of Service (QoS) applications.

- Designing Robust Asynchronous Circuits

- An asynchronous copy-back cache architecture

- Quality of Service (QoS) for Asynchronous On-Chip Networks

- Prototyping a Digital Neural Network System-on-Chip using an Altera Excalibur Device

- A Low-Power Asynchronous Multiplier

- An Investigation into the Security of Self-timed Circuits

- Delay-Insensitive, Point-to-Point Interconnect using m-of-n codes

- CHAIN: A Delay Insensitive CHip Area INterconnect

- An Asynchronous Victim Cache

- Validating the AMULET Microprocessors

- Applying asynchronous techniques to a Viterbi decoder design

- Power Management in the AMULET Microprocessors

- Delay Insensitive System-on-Chip Interconnect Uning 1-of-4 Data Encoding

- A Low-Power Self-Timed Viterbi Decoder

- A Novel Area-Efficient Binary Adder

- AMULET3: a 100 MIPS Asynchronous Embedded Processor

- A Power-Efficient Duplex Communication System

- An Asynchronous Viterbi Decoder

- MARBLE: An Asynchronous On-Chip Macrocell Bus

- On-chip timing reference for self-timed microprocessor

- Kicking out the Clock

- AMULET3i - an Asynchronous System-on-Chip

- The design of the control circuit for an asynchronous instruction prefetch unit using signal transition graphs

- AMULET3 Revealed

- AMULET2e: An Asynchronous Embedded Controller

- The Design of an Asynchronous VHDL Synthesizer

- Asynchronous Macrocell Interconnect using MARBLE

- Asynchronous Embedded Control

- Modelling and Simulation of Asynchronous Systems using the LARD Hardware Description Language

- AMULET3: A High-Performance Self-Timed ARM Microprocessor

- Behavioural Modelling of Asynchronous Systems for Power and Performance Analysis

- AMULET1: An Asynchronous ARM Microprocessor

- Built-In Self-Test Design of Micropipelines

- AMULET2e: An Asynchronous Embedded Controller

- Britain needs Manufacturing

- Asynchronous Logic.

- Breaking Step - the Return of Asynchronous Logic.

- Design for Testability of an Asynchronous Adder.

- Dynamic Logic in Four-Phase Micropipelines.

- Four-Phase Micropipeline Latch Control Circuits.

- AMULET2e.

- Scan testing of asynchronous sequential circuits.

- Scan testing of micropipelines.

- Designing Asynchronous Sequential Circuits for Random Pattern Testability.

- Designing C-elements for Testability.

- AMULET1: A Micropipelined ARM

- Transforming Architectural Models Into High Performance Concurrent Implementations

- The Design and Evaluation of an Asynchronous Microprocessor

- Breaking Step - the Return of Asynchronous Logic.

- AMULET1 - An Asynchronous ARM Processor.

- Computing without Clocks.

- A Micropipelined ARM

- Register Locking in an Asynchronous Microprocessor

This website will look much better in a web browser that supports web standards, but it is accessible to any browser or Internet device.